# **UNIVERSITY OF CINCINNATI**

Date:\_\_\_\_\_

\_\_\_\_\_

hereby submit this work as part of the requirements for the degree of:

in:

It is entitled:

I,

This work and its defense approved by:

Chair: \_\_\_\_\_

### SCAN CHAIN FAULT IDENTIFICATION USING WEIGHT-BASED CODES FOR SOC CIRCUITS

A thesis submitted to the

### Division of Research and Advanced Studies of the University of Cincinnati

in partial fulfillment of the requirements for the degree of

### MASTER OF SCIENCE

in the Department of Electrical and Computer Engineering and Computer Science of the College of Engineering May 2004

#### by

Swaroop Ghosh

B.E.(E.E.), University of Roorkee, Roorkee, India, May 2000

Thesis Advisor and Committee Chair: Dr. Wen Ben Jone

# Dedication

To my dearest parents and brothers, Dr. Sanjay Ghosh and Manoj Kumar $\overset{O}{G}hosh$

## Abstract

Recently, it has been observed that embedded cores in a high-speed SoC circuit have the problem of broken scan chains that cannot shift properly. Also, scan chain intermittent faults caused by holdtime violations and crosstalk noises are pervasive. In this research, an efficient method is proposed to identify the faulty scan chain(s) at the core level. That is, the core where the scan chain is defective can be identified, even if the scan chain is broken. The result can be used to tune up the fabrication process or to guide the fine-grained scan cell identification process. Here, weight-based m-out-of-n codes, which can generate a large number of codewords, with small hardware overhead and high fault detection capability are used to generate the scan chain diagnostic patterns for permanent and intermittent faults. An efficient codeword generation method is proposed to maximize the number of codewords, minimize the aliasing probabilities and test application cost. Aliasing probabilities are analyzed thoroughly for code sequences that are shifted to the scan chain in an overlapped manner. The idea of *multiple* m-out-of-n codes is also proposed to guarantee that sufficient number of codewords are generated to perturb the scan chains and the associated combinational circuits. A test pattern broadcast architecture is incorporated to support the proposed testing method. The complexity of control signal generation and scan chain test is greatly reduced by adopting this architecture. Further, by adding a test pattern alignment scheme, it is possible to share the control signals for all checkers and to support the broadcast architecture as well. Therefore, the hardware overhead of the test architecture is also reduced. Finally, a totally self-checking checker is designed to support the application of multiple weight-based codes. Simulation results demonstrate the feasibility of the proposed method as the aliasing probability is zero in almost every code sequence.

## Acknowledgements

I wish to express my sincere gratitude to my advisor, Dr. Wen-Ben Jone, for the guidance, support and constructive inputs that he provided throughout this work. He was always ready to provide his guidance and help in solving problems. This work would never have taken shape without his encouragement and expertise. He gave me complete independence to think on the research problem. However, he corrected me whenever my thinking went in the wrong direction. He gave me the opportunity to participate in various research projects which helped me understand the issues related to VLSI design and testing. Apart from guiding my thesis, he has directly and indirectly imparted many qualities in me which would certainly help me in pursuing a research oriented career. Under his guidance, I have realized that I can really make some useful contributions to this field.

I would like to thank the members of my thesis committee, Dr. Ranga Vemuri and Dr. Karen Tomko, for spending their valuable time reviewing this work, raising important issues and suggesting future research work. Special thanks are also due to my close friends, Srivatsa, Sriram, Gaurav, Kishore, Xiong, Lu Fei, Dilip, Aditi, and others, for the wonderful time I have had in their company. I would always cherish those moments. I would also like to thank my senior Vikas Vijay, who helped me during the course of my experiments. My sincere thanks to Srivatsa Kalala who guided me through the toughest period of my life and always helped me make the right decisions. Last, but not the least, I would like to express my gratitude to my parents and my brothers, Dr. Sanjay Ghosh and Manoj Kumar Ghosh, who have helped mould me into what I am today.

# Contents

| <ul> <li>2.2 Self-Checking Checker</li> <li>2.3 Applications of Weight-Based Codes</li> <li>3 Codeword Generation for Scan Chain Testing</li> <li>3.1 Codeword Generation</li> <li>3.2 Analysis for the Number of Codewords</li> <li>4 Codeword Ordering</li> <li>4.1 Coalesced Simple Paths Algorithm</li> <li>5 Aliasing Probability Analysis for Overlapped Codewords</li> <li>5.1 Bidirectional Aliasing Analysis</li> <li>5.1.1 Total Number of Undetected Bidirectional Errors</li> <li>5.1.2 Total Number of Two-Bit Errors</li> <li>5.1.3 Bidirectional Aliasing Probability</li> <li>5.1.4 Results</li> <li>5.2 Multidirectional Aliasing Analysis</li> <li>5.2.1 Total Number of Undetected Multi-directional Errors</li> <li>5.2.2 Total Number of Undetected Multi-directional Errors</li> <li>5.2.4 Results</li> <li>5.2 Multidirectional Aliasing Probability</li> <li>5.2.4 Results</li> <li>6 Multiple Weight-Based Codes and Checker Design</li> <li>6.1 Multiple Weight-Based Code Sequences</li> <li>6.2 Checker Implementation</li> <li>6.2.1 Variable Weight m-out-of-n Checker</li> <li>7 Test Architecture</li> <li>7.1 Test Pattern Alignment</li> <li>7.2 Test Architecture and Control Signal Sharing</li> </ul> | 1 | Introduction 1                                                                       |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---|--------------------------------------------------------------------------------------|

| <ul> <li>3.1 Codeword Generation</li></ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 2 | 2.1       Weight-Based Codes       4         2.2       Self-Checking Checker       4 |

| <ul> <li>4.1 Coalesced Simple Paths Algorithm</li></ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 3 | 3.1 Codeword Generation                                                              |

| <ul> <li>5.1 Bidirectional Aliasing Analysis</li></ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 4 |                                                                                      |

| <ul> <li>6.1 Multiple Weight-Based Code Sequences</li></ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 5 | <ul> <li>5.1 Bidirectional Aliasing Analysis</li></ul>                               |

| <ul> <li>7.1 Test Pattern Alignment</li></ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 6 | 6.1Multiple Weight-Based Code Sequences466.2Checker Implementation48                 |

| 8 Conclusions and Future Work                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | - | 7.1 Test Pattern Alignment                                                           |

# List of Figures

| 1.1                                       | A SoC design with self-checking checkers.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 2                                       |

|-------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------|

| 2.1                                       | Illustration of the concepts of self-testing, fault-secure, and totally self-checking [19].                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 5                                       |

| 3.1                                       | Flow for codeword enumeration.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 9                                       |

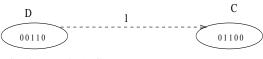

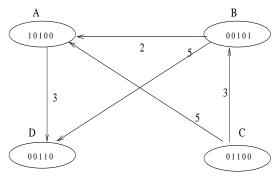

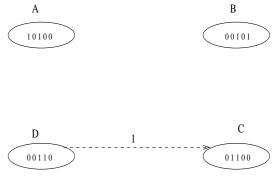

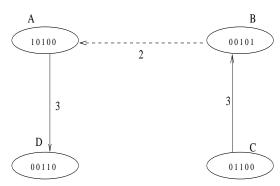

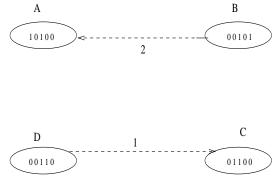

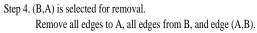

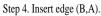

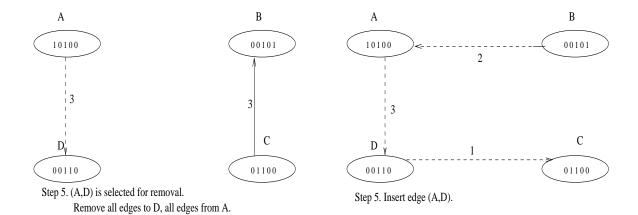

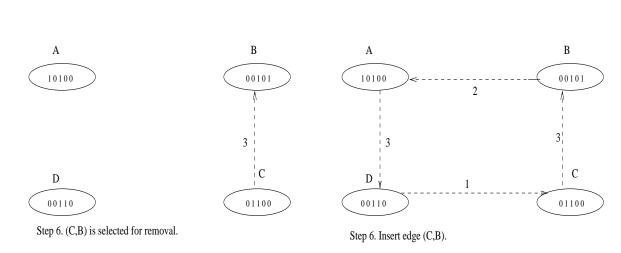

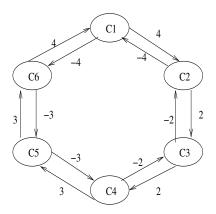

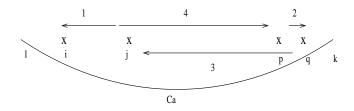

| $4.1 \\ 4.2$                              | Transitive edge removal due to partial tour                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | $\begin{array}{c} 16 \\ 19 \end{array}$ |

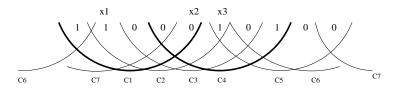

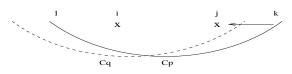

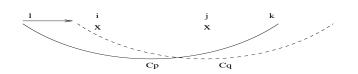

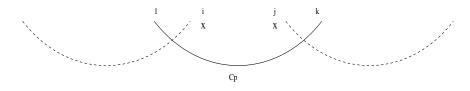

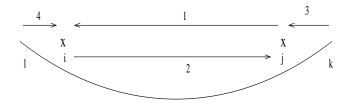

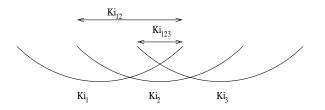

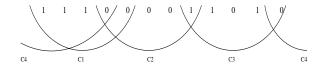

| $5.1 \\ 5.2 \\ 5.3$                       | Example illustrating bidirectional error. $\dots \dots \dots$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 21<br>22<br>23                          |

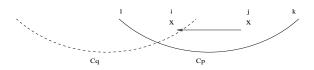

| 5.4                                       | Bidirectional error detected by cone $c_q$ (RSC)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 23                                      |

| $\begin{array}{c} 5.5 \\ 5.6 \end{array}$ | Bidirectional error detected by cone $c_q$ (LDC)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 23<br>24                                |

| $5.7 \\ 5.8$                              | Bidirectional error not covered by a neighboring cone                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | $\begin{array}{c} 24 \\ 24 \end{array}$ |

| $5.9 \\ 5.10$                             | Codewords of a 3-out-of-8 code                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | $\begin{array}{c} 25\\ 25\end{array}$   |

|                                           | Equivalent errors in two cones.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | $\frac{25}{29}$                         |

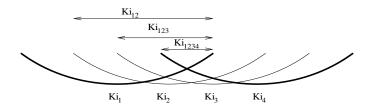

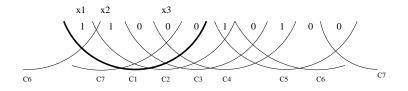

| 5.13                                      | Overlapping cones.       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       . | $\frac{30}{30}$                         |

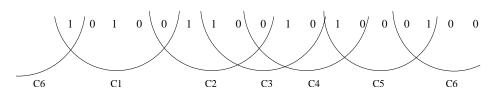

| 5.15                                      | 2-out-of-6 code sequence.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 36<br>36                                |

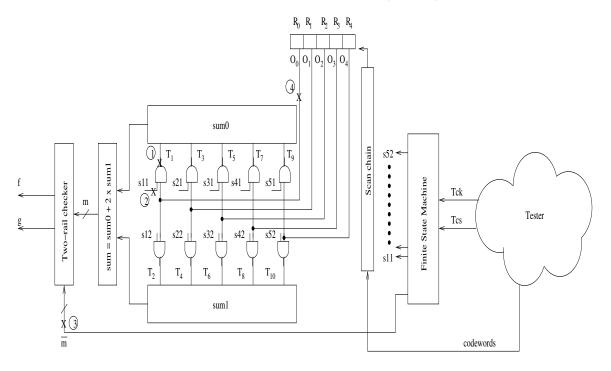

| <ul><li>5.10</li><li>6.1</li></ul>        | Different regions for searching a multi-directional error.       Self checking checker for variable weight line                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 30<br>48                                |

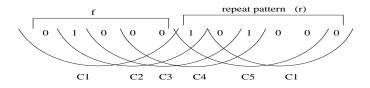

| 7.1                                       | 2-out-of-7 code sequence.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 51                                      |

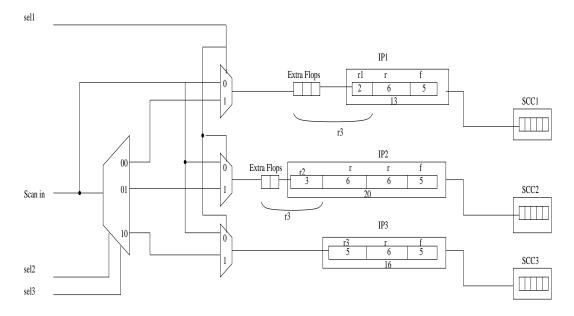

| $7.2 \\ 7.3$                              | Extra hardware to support broadcast test architecture                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | $\frac{52}{54}$                         |

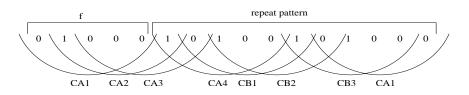

| 7.4                                       | Combined 3-out-of-11 and 4-out-of-11 code sequence                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 54                                      |

# List of Tables

| 3.1  | Results for weight set $\{1,2\}$                                 | 10 |

|------|------------------------------------------------------------------|----|

| 3.2  | Results for weight set $\{2,3\}$                                 | 11 |

| 3.3  | Results for weight set $\{1,2,3\}$ .                             | 13 |

| 3.4  | Results for weight set $\{1,2,3,5\}$                             | 14 |

| 4.1  | Comparison of CSP over optimal ordering                          | 17 |

| 5.1  | 1                                                                | 26 |

| 5.2  | Results for weight set $\{1,2\}$                                 | 32 |

| 5.3  |                                                                  | 33 |

| 5.4  | Results for weight set $\{1,2,3\}$ .                             | 34 |

| 5.5  | Results for weight set $\{1,2,3,5\}$                             | 35 |

| 5.6  | Percentage of bidirectional errors detected by Cases 1 and 2     | 35 |

| 5.7  | Summary of multi-directional aliasing example.                   | 37 |

| 5.8  | Results for weight set $\{1,2\}$                                 | 42 |

| 5.9  | Results for weight set $\{2,3\}$                                 | 43 |

| 5.10 | Results for weight set $\{1,2,3\}$ .                             | 44 |

| 5.11 | Results for weight set $\{1,2,3,5\}$ .                           | 45 |

| 5.12 | Percentage of multi-directional errors detected by Cases 1 and 2 | 45 |

## Chapter 1

## Introduction

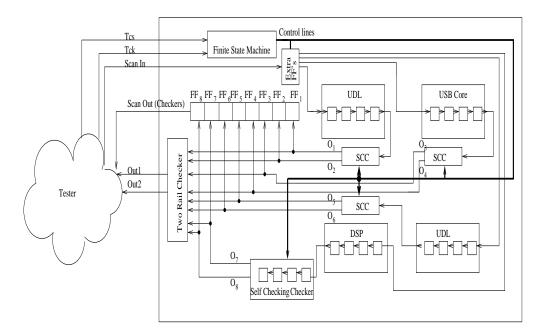

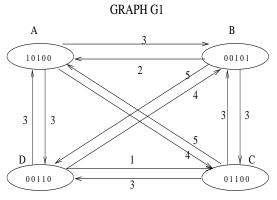

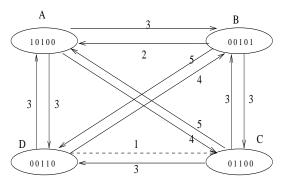

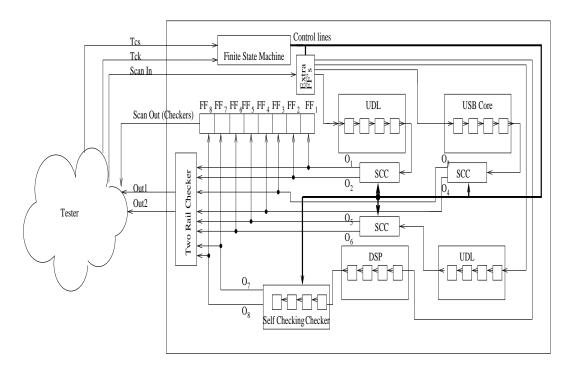

With the advent of deep sub-micron technologies, a large number of transistors can be integrated to a single chip. Hence, system-on-chip (SoC) design is becoming a more popular and cost-effective solution than traditional PCB designs. A modern SoC may contain memories, DSP cores, baseband controllers, analog components and peripherals, which are intellectual properties (IP's) bought from different vendors. A simple SoC is shown in Fig. 1.1 where UDLs are userdefined logic blocks, DSP is a digital signal processing core, and USB is a universal serial bus core [1]. These complex core blocks facilitate design reuse which results in shorter design cycles. Testing SoC circuits through scan chains is gaining popularity because scan testing gives core users flexibility to test the internal logic of each individual core. Since a core might be deeply embedded in the SoC circuit, a test access structure called *test access mechanism* (TAM) is generally designed to wrap the core [2]. The TAM circuit is used to transport test patterns from a pattern source to the scan chains of the core. Similarly, the test responses stored in the scan chains of the core are transported to a response monitor by the TAM circuit. It has been reported in [3] that the logic circuitry associated with the scan path may occupy as much as 30% of the total area of the circuit. Hence, it is of utmost importance to ensure the proper functioning of the scan chain before proceeding to test the associated combinational logic circuits. An internal fault in the combinational circuit can get masked due to a faulty scan chain. It is also possible that desired patterns to be applied to the combinational logic can never be shifted in.

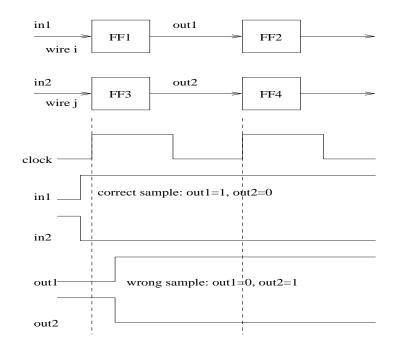

Basically, the faults that might occur at a scan chain can be categorized as *permanent* faults and *intermittent* faults. Scan chain fault diagnosis is the process of identifying the defective scan cell in a scan chain. Fault diagnosis for scan chain permanent faults assumes that the fault occurring in the scan chain is permanent, e.g., stuck-at fault, transition fault and hold-time fault. Fault diagnosis for scan chain permanent faults can be divided into *two* classes: (1) The scan chain is added extra circuits through special scan cell design or additional circuitry [4] [5] [6] [7], and (2) The scan chain is diagnosed by sequential test pattern generation or random test pattern simulation without adding any extra circuitry [3] [8] [9] [10]. In contrast to permanent fault diagnosis, intermittent fault diagnosis for scan chains are investigated only recently [11] [12]. Unlike permanent faults that can be modeled deterministically, intermittent faults occur stochastically and this makes fault diagnosis extremely difficult. According to [12], intermittent scan chain *hold-time* faults are pervasive in deep sub-micron technologies due to following reasons. *First*, in deep sub-micron technologies, it is very difficult to estimate the wire delay between the adjacent scan cells due to fabrication process variations. This might make the *hold-time margin* estimated too small. *Second*, noisy signals (at the wire between a pair of scan cells) caused by crosstalk

Figure 1.1: A SoC design with self-checking checkers.

or IR-drop might cause hold time fault in the scan cell especially when the hold-time margin is small. In summary, shrinking the feature size, increasing the operating speed, reducing the supply voltage etc. are the root causes of intermittent faults. In today's technologies, wire delays are becoming prominent as they are larger than gate delays. The problem with wire delay is that it is unpredictable, as it also depends on the signal running through it and through its adjacent wires. Even worse, inductive coupling between adjacent wires is taking over capacitive coupling, and its effect is hard to predict. The reason comes from the fact that the inductive coupling effect depends on the return current path, which in turn depends on the circuit topology as well as on the signal transition types (rising or falling) in victim and aggressor wires. The inductive coupling effect gives rise to overshoot/undershoot, oscillation, ringing and other transmission line effects that are hard to predict [13].

The challenging task is to activate and identify intermittent faults in the scan chain. This is possible only if proper test patterns, which can create maximum noises in the circuit, are fed to the scan chain at chip speed. Traditional permanent fault models and deterministic test methods cannot capture the uncertainties involved in the deep sub-micron scenario [12]. This work considers the fault diagnosis problem of scan chains for permanent and intermittent faults at the *core level*, instead of the scan cell level. That is, we try to identify the core whose scan chain(s) is faulty, even if the scan chain is broken and cannot shift properly. The basic idea is to add a self-checking checker to the tail of each scan chain in every core as shown in Fig. 1.1. The purpose of scan chain fault diagnosis at the core level are two-fold. First, identification of the defective scan chain in a specific core gives the manufacturer hints to tune-up the fabrication process. Since the cores of a SoC are purchased from vendors, the designer cannot modify the circuit layout. However, the manufacturer can fix some fabrication parameters such that the fabrication errors can be corrected. Second, identification of the defective scan chain in a specific core enables the test engineer to more efficiently identify the faulty scan cell. This can be achieved by restructuring the core wrappers such that scan chains of some cores can be bypassed. Thus, fine-grained scan cell identification techniques such as [11] [12] can be applied with shorter scan chains (thus shorter diagnosis time). Traditional 01010...10 or 00110011...0011 patterns are not suitable for activating the intermittent faults as the number of valid codewords for such codes are very small. For example, the 0101.. test pattern has only two valid codewords, namely 01 and 10. Similarly, 0011... has only four valid codewords, namely 0011, 0110, 1100, 1001. The small number of codewords cannot activate the intermittent faults due to a limited number of rising/falling transitions generated. In this work, weight-based m-out-of-n codes, which can generate a large number of codewords, with small hardware overhead and high fault detection capability are used to generate the scan chain diagnostic patterns for permanent and intermittent faults. A codeword generation method is proposed with the objectives of (1) maximizing the number of codewords, (2) minimizing the aliasing probabilities of *bidirectional* and *multi-directional* errors caused by permanent or intermittent defects, and (3) minimize the diagnostic pattern application time by codeword overlapping. The idea of *multiple* m-out-of-n codes is also proposed to guarantee that sufficient number of codewords are generated to perturb the scan chains and the associated combinational circuits. To further reduce the hardware overhead, a broadcast test architecture is adopted to enable all checkers to share the same control signals. Simulation results demonstrate the feasibility of the proposed method which achieves the above three objectives successfully.

#### This thesis is organized as follows:

Chapter 2 reviews the basic concepts of weight-based m-out-of-n codes, self-checking checkers, and their applications to on-line testing such as bus crosstalk faults and power supply noises.

Chapter 3 deals with the codeword generation method.

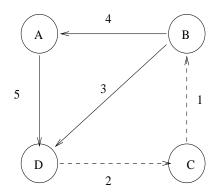

Chapter 4 discusses the order of codeword application to the scan chains using a graph model.

Chapter 5 analyzes the aliasing probabilities of both bidirectional and multi-directional errors.

**Chapter 6** discusses the merging of multiple m-out-of-n codes and the corresponding totally self-checking checker design.

**Chapter 7** is dedicated to the test architecture that can support the proposed testing method. The test pattern alignment problem is also dealt with so that shared control lines can be used for all checkers and the broadcast test architecture can be incorporated.

**Chapter 8** concludes the thesis with suggested future work on a more powerful test pattern alignment for broadcast test architecture, identification of fine-grained faulty scan cell, development of a built-in self-test methodology to exercise an at-speed test of the scan chain, and development of a simulator that can evaluate the power of codewords applied.

## Chapter 2

## Background

#### 2.1 Weight-Based Codes

The weight-based m-out-of-n coding method is a generalization of Berger codes [14]. Weightbased codes are obtained by assigning different weights  $w_i$  to the information bits. All codewords which belong to a weighted m-out-of-n code satisfies:

$$m = \sum_{i=1}^{l} w_i v_i, \text{ and } n = \sum_{i=1}^{l} w_i$$

where  $w_i \in W$  is the weight of  $i^{th}$  bit,  $v_i$  is the value of  $i^{th}$  bit, W is the the set of weights, and l is the *cone size* (i.e., the number of bits in each codeword). It should be noted that m may be larger than the n value of the ordinary m-out-of-n code, where the weight of each bit is one.

The weight-based m-out-of-n coding still possesses the property of detecting all unidirectional errors. Additionally, it can detect all bidirectional errors involving a pair of bits i and jif  $w_i \neq w_j$ . In fact, in the case of a bidirectional error involving such bits, we have  $m_{new} = m$  $\pm (w_i - w_j)$ , so that a checker can detect the error. If all  $w_i$  values differ from each other, it is evident that all single bidirectional errors can be detected. This constraint can be achieved if  $w_i$ = i, but such a large weight set will increase the hardware overhead of the checker circuit. As will be shown by the analysis presented in the next section, a small set of weights can be used without deteriorating the error detection ability in our case. Moreover, the value of each  $w_i$  should be kept small to reduce the checker design complexity.

#### 2.2 Self-Checking Checker

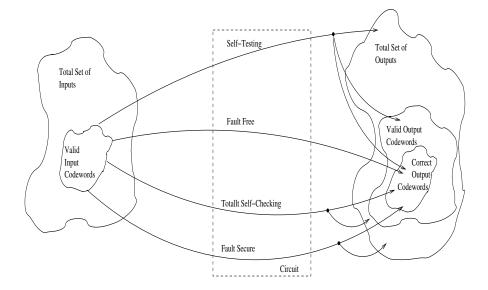

A self-checking checker basically verifies the correctness of the incoming code. It detects an error as soon as it occurs, and prevents the error propagation throughout the system [14]. For such a system, totally self-checking (TSC) is the main property to ensure reliable operations in the presence of faults. A TSC checker must have two outputs and, hence, four combinations (i.e., 00, 01, 10, 11). Two of these output combinations, (01,10), are considered *valid*. A *nonvalid* checker output, (00,11), indicates either a noncodeword at the input of the checker or a fault in the checker itself. The reason why a checker needs two outputs is: if there is only one output and the normal output value is 1 (0), then a stuck-at-1 (0) fault at the checker output cannot be detected during normal operation. Also, combinations (00,11) are not selected as valid outputs because a unidirectional multi-bit error may change 00 to 11 and vice versa (and cannot be detected) [15]. However, single-output TSC checkers have been proposed in [16], [17] and [18]. They generally work with the help of a clock signal. They produce 10 or 01 in one clock period during fault-free conditions, and 00 or 11 during faulty conditions. The main advantage of a single-output checker over its counterpart is low power consumption and small hardware overhead. In the following, we describe the properties that are used to define TSC circuits. Fig. 2.1 illustrates the properties of the following definitions.

**Fault-secure:** A circuit is *fault-secure* with respect to a set of faults F, if for any single fault in F, the circuit never produces an incorrect output codeword for any input codeword. That is, the circuit produces the correct codeword or a non-codeword for any valid input codeword.

**Self-testing:** A circuit is *self-testing* with respect to a set of faults F, if for every single fault in F, the circuit produces a noncodeword at the output for atleast one input codeword.

**Code-disjoint:** A circuit is *code-disjoint* if it maps codewords (noncodewords) at the input to codewords (noncodewords) at the output.

**Totally self-checking:** A circuit is *totally self-checking* if it is both fault secure and self-testing. So, a circuit is TSC if all single faults are detectable by at least one codeword, and when a given input does not detect the fault, the output is the correct codeword (i.e., 01 or 10).

Figure 2.1: Illustration of the concepts of self-testing, fault-secure, and totally self-checking [19].

#### 2.3 Applications of Weight-Based Codes

Weight-based codes are proposed in [20] to perform concurrent error detection of multilevel circuits. Each output bit of the multilevel combinational circuit is assigned a weight, and the check bits represent the sum of weights of the output bits which have logic value 1. Aliasing can be minimized by guidelines such as: (1) The weights should be mutually prime, and the sum of two weights should not be a multiple of the third; (2) Output bits are partitioned into clusters such that there is minimum sharing of logic between outputs in the same cluster, and outputs in the same cluster are assigned the same weight [20]. The aliasing probability is reported to be smaller than traditional error detection codes. An efficient design for the corresponding totally self-checking checker is also proposed. The idea of weight-based codes are extended to *modulo* weight-based

codes in [21] for concurrent error detection of arbitrary multilevel circuits. The major purpose of the modulo weight-based codes is to reduce the check bits required by taking the sum modulo of the weights for the output bits that have logic value 1. The algorithm to assign weights and the corresponding self-checking checker design are also presented. In [14], weight-based codes are applied to detect crosstalk faults by concurrent error detection of buses. Based on the knowledge of the layout structure, a graph can be generated to represent the most likely crosstalk faults in the bus. The problem of weight selection is then modeled as the well-known graph-coloring problem. By the weights selected, a low-cost weight-based m-out-of-n code can be found to detect the crosstalks that might cause bidirectional errors. Other self-checking detection and diagnosis schemes for different faults (e.g., transient, delay faults) and devices (e.g., buses, sequential circuits) can be found in [22] [23] [24].

## Chapter 3

# Codeword Generation for Scan Chain Testing

In this chapter, we will present the codeword generation methodology for weight-based m-out-of-n codes for scan chain testing.

#### 3.1 Codeword Generation

Before proceeding with the codeword generation method, we present few common terms that will be frequently used in this work.

• Weight set is a set of weights by which a weighted m-out-of-n code is generated.

• Number of codewords denotes the total number of codewords found for a given weighted m-out-of-n coding method.

• Cone size (i.e., l) is the number of bits in each codeword of a given weighted m-out-of-n code.

• Weight configuration represents a way of (repeatedly) selecting l weights from the weight set without permutation such that the required n can be satisfied. For example, if the weight set is  $\{1,2,3\}$  and n = 10, then we have two weight configurations: [1,2,2,2,3] and [1,1,2,3,3]. However, we have only one weight configuration for weight set  $\{1,2\}$  and n = 6, namely, [1,1,1,1,2].

• Weight sequence or distribution denotes the weight assigned to each bit of a codeword such that required n is satisfied. Consider an example with weight set = {1,2} and cone size = 5. One possible weight distribution to get n = 6 is 1-2-1-1. Here, we can verify that  $n = \sum w_i = 1+2+1+1+1 = 6$  based on the weight configuration [1,1,1,1,2]. Note that weight distribution is different from weight configuration. A new weight distribution can be obtained simply by permuting the weights of the current weight distribution, but the similar logic is not valid for weight configuration.

• Code sequence denotes the order by which codewords are shifted into the scan chain. Assume we have cone size = 5, weight set = {1,2}, n = 6, and weight sequence = 1-1-1-2-1. A valid code sequence for m = 2 can be  $11000 \rightarrow 10001 \rightarrow 00010 \rightarrow 00101 \rightarrow 10100 \rightarrow 01001 \rightarrow 01100$ . Note that each of the codewords has  $m = \sum w_i * v_i = 2$ . Generally, the codewords are ordered in such a way that there is maximum overlapping between each pair of adjacent codewords, hence all codewords can be shifted into the scan chain using the minimum number of clock cycles.

$(11000)-1 \rightarrow (10001) - 0 \rightarrow (00010) - 1 \rightarrow (00101) - 00 \rightarrow (10100) - 1 \rightarrow (01001) - 100 \rightarrow (01100) - 0 \rightarrow \text{back to first codeword.}$

• Transition count is the total number of  $0 \rightarrow 1$  or  $1 \rightarrow 0$  transitions generated by a particular m-out-of-n code sequence. Consider the example of 2-out-of-6 code again, the transition count for code sequence  $11000 \rightarrow 10001 \rightarrow 00010 \rightarrow 00101 \rightarrow 10100 \rightarrow 01001 \rightarrow 01100 \rightarrow 11000$  is 30. Note that, there is only one (left) shift between codeword 11000 & 10001 and that there are one  $0 \rightarrow 1$  (rightmost bit) and one  $1 \rightarrow 0$  (fourth bit from right) transitions generated when 10001 is applied after 11000. But, there are two shifts between codeword 00101 & 10100, and there are three words involved, namely, 00101, 01010 and 10100. The number of transitions generated between 00101 & 01010 is 4 and the number of transitions generated between 01010 & 10100 is again 4 giving rise to a total of 8 transitions between 00101 & 10100. The number of transitions between other codewords can be calculated similarly. The total *transition count* is the sum of transition counts generated by each pair of adjacent codewords.

• Test application cost denotes the total number of shifts required to apply all the codewords of a m-out-of-n code to the scan chain. In the above example for shift sequence, the test application cost is 1+1+1+2+1+3+1 = 10.

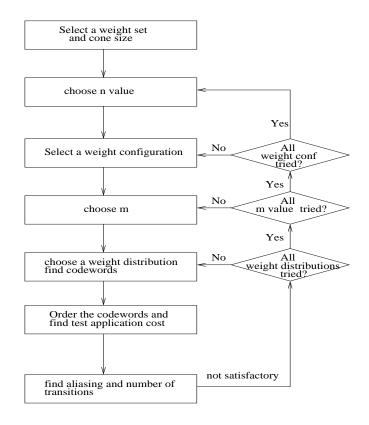

The function of the *codeword enumerator* (in software) is to select proper m, n, weight set and weight distribution, and to generate the corresponding codewords. A program is developed in C++ for finding the codespace, cost and aliasing for a specific weighted m-out-of-n coding scheme. The experimental steps are as follows:

- 1. Fix the weight set, e.g.,  $\{1,2\}$  and cone size.

- 2. Fix the n value.

- 3. Find a weight configuration and its weight distributions. For example, given n = 6 and cone size = 5, there in only one weight configuration [1,1,1,1,2] and the weight distributions are 1-1-1-1-2, 1-1-1-2-1, 1-1-2-1-1, 1-2-1-1-1 and 2-1-1-1-1. Another example is to have weight set = {1,2,3}, cone size = 5, and n = 10. The possible weight configurations are [1,1,2,3,3] and [1,2,2,2,3].

- 4. Fix a m value.

- 5. For the *m* value, find the codewords for a specific weight distribution. Following the above example, for m = 2 and weight sequence 1-1-2-1, the codewords are 11000, 10001, 00010, 00101, 10100, 01001, 01100.

- 6. Arrange the codewords such that the test application cost is minimum. The aim is to apply all codewords into the scan chain by minimum number of (left) shifts. In our experiments, exhaustive search is exercised to find the arrangement corresponding to the minimum test

application cost. For example, code sequence  $11000 \rightarrow 10001 \rightarrow 00010 \rightarrow 00101 \rightarrow 10100 \rightarrow 01001 \rightarrow 01100$  gives the minimum test application cost for the above example (step 4). For a weighted m-out-of-n code with N codewords, an algorithm to accomplish the codeword ordering with complexity  $O(l \cdot N^2)$  will be presented in Chapter 4. Note that l (i.e., cone size) is generally a small number compared to N.

- 7. Find the bidirectional and multi-directional aliasing probabilities for the weighted m-out-of-n code.

- 8. Rearrange the weight sequence and repeat steps 5 and 7 until all weight sequences are tried. For example, a new experiment with weight sequence 1-1-2-1-1 can be repeated.

- 9. Find a new m value and repeat steps 5 to 8 until all m values are tried.

- 10. Repeat steps 3 to 9 until all weight configurations are exhausted.

- 11. Among all weighted m-out-of-n codes generated, select the one which yields the maximum number of codewords, the minimum cost and aliasing probabilities. If there exists none which satisfies all requirements, try to trade-off among number of codewords, test application cost and test aliasing probabilities.

- 12. If necessary, try more n values and weight sets and repeat steps 3 to 11 until a satisfactory weighted m-out-of-n code is found.

Figure 3.1: Flow for codeword enumeration.

The entire flow for the selection of m, n and weight set is depicted in Fig. 3.1. We have performed software simulation with cone size of 5 and different weight sets. The simulation results

for different cardinalities of weight sets, m and n values are presented in Tables 3.1, 3.2, 3.3 and 3.4.

| m/n | # code-          | cost | Weight    | Code sequence                                                                   | Shift sequence                                          |

|-----|------------------|------|-----------|---------------------------------------------------------------------------------|---------------------------------------------------------|

| m/n | # code-<br>words | COSt |           | Code sequence                                                                   | Shint sequence                                          |

| 1/0 |                  | F    | sequence  | 10000 00010 00100 01000                                                         | 0 1 1 1                                                 |

| 1/6 | 4                | 5    | 1-1-1-2   | $10000 \rightarrow 00010 \rightarrow 00100 \rightarrow 01000 \rightarrow$       | $2 \rightarrow 1 \rightarrow 1 \rightarrow 1$           |

|     |                  |      |           |                                                                                 | $\rightarrow$                                           |

| 2/6 | 7                | 10   | 1-1-1-2-1 | $11000 \rightarrow 10001 \rightarrow 00010 \rightarrow 00101 \rightarrow 10100$ | $1 \to 1 \to 1 \to 2$                                   |

|     |                  |      |           | $\rightarrow 01001 \rightarrow 01100 \rightarrow$                               | $\rightarrow 1 \rightarrow 3 \rightarrow 1 \rightarrow$ |

| 3/6 | 8                | 12   | 1-1-2-1-1 | $10100 \rightarrow 00101 \rightarrow 01011 \rightarrow 01100 \rightarrow 11001$ | $3 \rightarrow 1 \rightarrow 2 \rightarrow 1$           |

|     |                  |      |           | $\rightarrow 10011 \rightarrow 00110 \rightarrow 11010 \rightarrow$             | $\rightarrow 1 \rightarrow 1 \rightarrow 2 \rightarrow$ |

|     |                  |      |           |                                                                                 | $1 \rightarrow$                                         |

| 1/7 | 3                | 4    | 2-1-1-1-2 | $01000 \rightarrow 00010 \rightarrow 00100 \rightarrow$                         | $2 \rightarrow 1 \rightarrow 1 \rightarrow$             |

| 2/7 | 5                | 6    | 1-2-1-2-1 | $01000 \rightarrow 10001 \rightarrow 00010 \rightarrow 00101 \rightarrow 10100$ | $1 \rightarrow 1 \rightarrow 1 \rightarrow 2$           |

| ,   |                  |      |           | $\rightarrow$                                                                   | $\rightarrow 1 \rightarrow$                             |

| 3/7 | 7                | 10   | 1-1-2-2-1 | $10100 \rightarrow 00011 \rightarrow 01100 \rightarrow 11001 \rightarrow 10010$ | $3 \rightarrow 2 \rightarrow 1 \rightarrow 1$           |

| ,   |                  |      |           | $\rightarrow 00101 \rightarrow 01010 \rightarrow$                               | $\rightarrow 1 \rightarrow 1 \rightarrow 1 \rightarrow$ |

| 1/8 | 2                | 4    | 2-1-1-2-2 | $01000 \rightarrow 00100 \rightarrow$                                           | $3 \rightarrow 1 \rightarrow$                           |

| 2/8 | 4                | 4    | 1-2-2-2-1 | $01000 \rightarrow 10001 \rightarrow 00010 \rightarrow 00100 \rightarrow$       | $1 \rightarrow 1 \rightarrow 1 \rightarrow 1$           |

| 3/8 | 6                | 10   | 2-1-1-2-2 | $11000 \rightarrow 00101 \rightarrow 01010 \rightarrow 10100 \rightarrow 01001$ | $3 \rightarrow 1 \rightarrow 1 \rightarrow 1$           |

| ,   |                  |      |           | $\rightarrow 00110 \rightarrow$                                                 | $\rightarrow 2 \rightarrow 2 \rightarrow$               |

| 4/8 | 6                | 10   | 2-1-2-1-2 | $10100 \rightarrow 10001 \rightarrow 00101 \rightarrow 01011 \rightarrow 01110$ | $2 \rightarrow 2 \rightarrow 1 \rightarrow 2$           |

| ,   |                  |      |           | $\rightarrow 11010 \rightarrow$                                                 | $\rightarrow 2 \rightarrow 1 \rightarrow$               |

| 1/9 | 1                | 3    | 2-2-1-2-2 | $00100 \rightarrow$                                                             | $3 \rightarrow$                                         |

| 2/9 | 4                | 5    | 1-2-2-2-2 | $01000 \rightarrow 00001 \rightarrow 00010 \rightarrow 00100 \rightarrow$       | $2 \rightarrow 1 \rightarrow 1 \rightarrow 1$           |

| ,   |                  |      |           |                                                                                 | $\rightarrow$                                           |

| 3/9 | 4                | 9    | 2-2-1-2-2 | $10100 \rightarrow 00110 \rightarrow 01100 \rightarrow 00101 \rightarrow$       | $3 \rightarrow 1 \rightarrow 3 \rightarrow 2$           |

| ,   |                  |      |           |                                                                                 | $\rightarrow$                                           |

| 4/9 | 6                | 10   | 2-1-2-2-2 | $10100 \rightarrow 10001 \rightarrow 00011 \rightarrow 00110 \rightarrow 10010$ | $2 \rightarrow 1 \rightarrow 1 \rightarrow 3$           |

| ,   |                  |      |           | $\rightarrow 00101 \rightarrow$                                                 | $\rightarrow 1 \rightarrow 2 \rightarrow$               |

|     |                  |      |           |                                                                                 | 1                                                       |

Table 3.1: Results for weight set  $\{1,2\}$ .

#### 3.2 Analysis for the Number of Codewords

Let the weight set be  $\{w_1, \ldots, w_r\}$ , where r = cardinality of the weight set. Given a m-outof-n code with a specific n value, we have following equation:

$$n = x_k^1 w_1 + x_k^2 w_2 + \dots + x_k^r w_r \tag{3.1}$$

where  $x_k^i = \text{integer coefficients for weight } w_i$ . This also means that there are  $x_k^i$  number of  $w_i$ 's in the weight distribution, and k = 1 to s where s represents the total number of possible configurations that satisfy the given n value. Similarly, we can have

$$m = y_{k,j}^1 w_1 + y_{k,j}^2 w_2 + \dots + y_{k,j}^r w_r$$

(3.2)

| m/n    | # code- | cost | Weight    | Code sequence                                                                   | Shift sequence                                |

|--------|---------|------|-----------|---------------------------------------------------------------------------------|-----------------------------------------------|

| 111/11 | words   | CODU | sequence  | eoue sequence                                                                   | Shine Sequence                                |

| 2/11   | 4       | 5    | 2-2-2-2-3 | $10000 \rightarrow 00010 \rightarrow 00100 \rightarrow 01000 \rightarrow$       | $2 \rightarrow 1 \rightarrow 1 \rightarrow 1$ |

| -/ 11  | Ŧ       | 0    | 22220     |                                                                                 | $\rightarrow$                                 |

| 3/11   | 1       | 3    | 2-2-3-2-2 | $00100 \rightarrow$                                                             | $3 \rightarrow$                               |

| 4/11   | 6       | 10   | 2-2-2-3-2 | $11000 \rightarrow 10001 \rightarrow 00101 \rightarrow 10100 \rightarrow 01001$ | $1 \rightarrow 2 \rightarrow 2 \rightarrow 1$ |

| -/     | °       | 10   |           | $\rightarrow 01100 \rightarrow$                                                 | $\rightarrow 3 \rightarrow 1 \rightarrow$     |

| 5/11   | 4       | 9    | 2-2-3-2-2 | $10100 \rightarrow 00110 \rightarrow 01100 \rightarrow 00101 \rightarrow$       | $3 \rightarrow 1 \rightarrow 3 \rightarrow 2$ |

| '      |         |      |           |                                                                                 | $\rightarrow$                                 |

| 2/12   | 3       | 4    | 3-2-2-3   | $01000 \rightarrow 00010 \rightarrow 00100 \rightarrow$                         | $2 \rightarrow 1 \rightarrow 1 \rightarrow$   |

| 3/12   | 2       | 4    | 2-2-3-3-2 | $00100 \rightarrow 00010 \rightarrow$                                           | $3 \rightarrow 1 \rightarrow$                 |

| 4/12   | 3       | 6    | 2-3-2-3-2 | $10100 \rightarrow 10001 \rightarrow 00101 \rightarrow$                         | $2 \rightarrow 2 \rightarrow 2 \rightarrow$   |

| 5/12   | 6       | 10   | 2-2-3-3-2 | $10100 \rightarrow 00011 \rightarrow 01100 \rightarrow 10010 \rightarrow 00101$ | $3 \rightarrow 2 \rightarrow 2 \rightarrow 1$ |

|        |         |      |           | $\rightarrow 01010 \rightarrow$                                                 | $\rightarrow 1 \rightarrow 1 \rightarrow$     |

| 6/12   | 2       | 2    | 2-3-2-3-2 | $01010 \rightarrow 10101 \rightarrow$                                           | $1 \rightarrow 1 \rightarrow$                 |

| 2/13   | 2       | 4    | 3-2-2-3-3 | $01000 \rightarrow 00100 \rightarrow$                                           | $3 \rightarrow 1 \rightarrow$                 |

| 3/13   | 3       | 4    | 2-3-3-3-2 | $01000 \rightarrow 00010 \rightarrow 00100 \rightarrow$                         | $2 \rightarrow 1 \rightarrow 1 \rightarrow$   |

| 4/13   | 1       | 2    | 3-2-3-2-3 | $01010 \rightarrow$                                                             | $2 \rightarrow$                               |

| 5/13   | 6       | 10   | 3-2-2-3-3 | $11000 \rightarrow 00101 \rightarrow 01010 \rightarrow 10100 \rightarrow 01001$ | $3 \rightarrow 1 \rightarrow 1 \rightarrow 1$ |

|        |         |      |           | $\rightarrow 00110 \rightarrow$                                                 | $\rightarrow 2 \rightarrow 2 \rightarrow$     |

| 6/13   | 3       | 6    | 3-2-3-2-3 | $10100 \rightarrow 10001 \rightarrow 00101 \rightarrow$                         | $2 \rightarrow 2 \rightarrow 2 \rightarrow$   |

| 2/14   | 1       | 3    | 3-3-2-3-3 | $00100 \rightarrow$                                                             | $3 \rightarrow$                               |

| 3/14   | 4       | 5    | 2-3-3-3-3 | $01000 \rightarrow 00001 \rightarrow 00010 \rightarrow 00100 \rightarrow$       | $2 \rightarrow 1 \rightarrow 1 \rightarrow 1$ |

|        |         |      |           |                                                                                 | $\rightarrow$                                 |

| 5/14   | 4       | 9    | 3-3-2-3-3 | $10100 \rightarrow 00110 \rightarrow 01100 \rightarrow 00101 \rightarrow$       | $3 \rightarrow 1 \rightarrow 3 \rightarrow 2$ |

|        |         |      |           |                                                                                 | $\rightarrow$                                 |

| 6/14   | 6       | 10   | 3-2-3-3-3 | $10100 \rightarrow 10001 \rightarrow 00011 \rightarrow 00110 \rightarrow 10010$ | $2 \rightarrow 1 \rightarrow 1 \rightarrow 3$ |

|        |         |      |           | $\rightarrow 00101 \rightarrow$                                                 | $\rightarrow 1 \rightarrow 2 \rightarrow$     |

Table 3.2: Results for weight set  $\{2,3\}$ .

where  $y_{k,j}^i$  = integer coefficients for weight  $w_i$ . This also means that, under weight configuration k, there are  $y_{k,j}^i$  number of  $w_i$ 's in each codeword, and j = 1 to t where t denotes the total number of possible configurations that satisfy the given m value.

Further, we have

$$x_k^1 + x_k^2 + \dots + x_k^r = l \text{ (i.e., the cone size)}$$

(3.3)

and

$$y_{k,j}^i \le x_k^i, \quad i = 1 \text{ to } r, \ j = 1 \text{ to } t, \ k = 1 \text{ to } s.$$

(3.4)

Let  $Q_k$  represent the total number of possible codewords for each weight sequence of the  $k^{th}$  configuration of the given n value. We have

$Q_k = \sum_{j=1}^{t}$  (total number of ways of choosing weights for  $j^{th}$  m configuration)

Assume we have weight configuration [1,1,1,2,2] (i.e., n = 7) and the cone size = 5. Given m = 3, there are two m configurations:  $m = 3 \cdot w_1 + 0 \cdot w_2$  and  $m = 1 \cdot w_1 + 1 \cdot w_2$  where  $w_i = i$ . Let

us concentrate on the second m configuration. There are three choices to assign 1 to  $w_1$  and two choices to assign 1 to  $w_2$ . That is, the total number of codewords for the second m configuration is  $C(3,1) \cdot C(2,1) = 6$ , and the codewords are 10010, 10001, 01010, 01001, 00101. Thus, the total number of codewords for each weight sequence under a specific weight configuration can be represented by

$$Q_k = \sum_{j=1}^t (\prod_{i=1}^r C(x_k^i, y_{k,j}^i)) \quad , \forall \ k = 1 \ to \ s.$$

(3.5)

Note that, for each configuration of n, we are concerned with only one weight sequence. For example, given a weight set =  $\{1,2\}$ , cone size = 5, and n = 6, there is only one weight configuration (i.e., [1,1,1,1,2]) for the specific n value. We are concerned with only one weight sequence (e.g., 1-1-1-1-2) from which a set of codewords can be generated. Note that the number of codewords generated by any other weight sequence (e.g., 2-1-1-1-1) is the same as the one selected.

#### Example 1:

Let us consider a 3-out-of-6 code with weight set = {1,2} (i.e., r = 2) and cone size = 5. From equation 3.1, we have  $n = 4 \cdot 1 + 1 \cdot 2 = 6$  and this is the only weight configuration that can satisfy the *n* value. This leads to  $x_1^1 = 4$ ,  $x_1^2 = 1$ , and k = 1. Thus, the weight distributions can be 1-1-1-2, 1-1-1-2, 1, 1-1-2-1, 1, 1-2-1-1-1, 2-1-1-1. We are interested in only (any) one of them, since all different weight distributions generated from the same weight configuration have the same number of codewords as will be proved later. From equation 3.2, there are two possible *m* configurations for m=3 (for any weight sequence). They are:  $m = 3 \cdot 1 + 0 \cdot 2 = 3$ , and  $m = 1 \cdot 1 + 1 \cdot 2 = 3$ . So, we have  $y_{1,1}^1 = 3$ ,  $y_{1,2}^2 = 0$ ,  $y_{1,2}^1 = 1$ ,  $y_{1,2}^2 = 1$ . From equation 3.5, we get  $Q_1 = \sum_{j=1}^2 (\prod_{i=1}^2 C(x_1^i, y_{1,j}^i)) = [C(4,3) \cdot C(1,0)] + [C(4,1) \cdot C(1,1)] = 4 + 4 = 8.$

| m/n                           | # code- | $\cos t$ | Weight    | Code sequence                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | Shift sequence                                                                                                                 |

|-------------------------------|---------|----------|-----------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------|

| 1 /0                          | words   |          | sequence  | 01000 00010 00100                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |                                                                                                                                |

| 1/8                           | 3       | 4        | 2-1-1-3   | $01000 \rightarrow 00010 \rightarrow 00100 \rightarrow$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | $2 \rightarrow 1 \rightarrow 1 \rightarrow$                                                                                    |

| 2/8                           | 4       | 6        | 1-2-1-3-1 | $01000 \rightarrow 10001 \rightarrow 00101 \rightarrow 10100 \rightarrow$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | $1 \to 2 \to 2 \to 1$                                                                                                          |

| 3/8                           | 5       | 10       | 1-1-3-1-2 | $00100 \rightarrow 10001 \rightarrow 00011 \rightarrow 11010 \rightarrow 01001$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | $2 \rightarrow 1 \rightarrow 3 \rightarrow 2$                                                                                  |

| 1/0                           |         | 10       | 1 1 0 0 1 | $\rightarrow$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | $\rightarrow 2 \rightarrow$                                                                                                    |

| 4/8                           | 6       | 12       | 1-1-3-2-1 | $10100 \rightarrow 00101 \rightarrow 01011 \rightarrow 01100 \rightarrow 10011$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | $3 \rightarrow 1 \rightarrow 2 \rightarrow 2$                                                                                  |

| 1 /0                          | 0       | 4        | 01110     | $\rightarrow 11010 \rightarrow$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | $ \begin{array}{c} \rightarrow 3 \rightarrow 1 \rightarrow \\ \hline 3 \rightarrow 1 \rightarrow \end{array} $                 |

| 1/9                           | 2       | 4        | 2-1-1-1-3 | $01000 \rightarrow 00100 \rightarrow 00100$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | $3 \rightarrow 1 \rightarrow$                                                                                                  |

| 2/9                           | 4       | 6        | 1-2-1-3-1 | $01000 \rightarrow 10001 \rightarrow 00100 \rightarrow 11000$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | $1 \rightarrow 2 \rightarrow 1 \rightarrow$                                                                                    |