# A MINIATURIZED BRAIN-MACHINE-SPINAL CORD INTERFACE (BMSI) FOR CLOSED-LOOP INTRASPINAL MICROSTIMULATION

by

### SHAHABEDIN SHAHDOOSTFARD

Submitted in partial fulfillment of the requirements for the degree of

Doctor of Philosophy

Thesis Advisor: Professor Pedram Mohseni

Department of Electrical Engineering and Computer Science

CASE WESTERN RESERVE UNIVERSITY

January 2018

# CASE WESTERN RESERVE UNIVERSITY

### SCHOOL OF GRADUATE STUDIES

We hereby approve the thesis/dissertation of

#### Shahabedin Shahdoostfard

candidate for the degree of Doctor of Philosophy\*.

Committee Chair

### **Pedram Mohseni**

**Committee Member**

Francis L. Merat

**Committee Member**

#### Soumyajit Mandal

**Committee Member**

Randolph J. Nudo

Date of Defense

July 06, 2016

\*We also certify that written approval has been obtained

for any proprietary material contained therein.

© Shahabedin Shahdoostfard All Rights Reserved 2018 This dissertation is dedicated to my father, my mom, and my brother

NASER & AZAM & SHAYAN

# **Table of Contents**

| Dedication i                                                                                     |  |  |  |  |

|--------------------------------------------------------------------------------------------------|--|--|--|--|

| List of Tablesv                                                                                  |  |  |  |  |

| List of Figures vi                                                                               |  |  |  |  |

| Acknowledgmentx                                                                                  |  |  |  |  |

| Abstract xi                                                                                      |  |  |  |  |

| CHAPTER                                                                                          |  |  |  |  |

| 1. Introduction1                                                                                 |  |  |  |  |

| 1.1 Background and Motivation1                                                                   |  |  |  |  |

| 1.2 Neural Interface Systems: Previous Work                                                      |  |  |  |  |

| 1.3 Proposed Research                                                                            |  |  |  |  |

| 1.4 References for Chapter 1 12                                                                  |  |  |  |  |

| CHAPTER                                                                                          |  |  |  |  |

| 2. Integrated Microsystem for Intracortical Neural Recording and Intraspinal<br>Microstimulation |  |  |  |  |

| 2.1 System Architecture                                                                          |  |  |  |  |

| 2.2 Integrated Circuit Architecture                                                              |  |  |  |  |

| 2.2.1 Recording Front-End 17                                                                     |  |  |  |  |

| 2.2.2 Stimulating Back-End                                                                       |  |  |  |  |

| 2.3 Benchtop and In Vivo Measurement Results                                                     |  |  |  |  |

| 2.4 References for Chapter 2                                                                     |  |  |  |  |

| CHAPTER<br>3. FPGA Implementation of Stimulus Trigger Generation from Intracortical              |  |  |  |  |

| Spike Activity                                                                                   |  |  |  |  |

| 3.1 Operation Concept                                                                                           | 31 |

|-----------------------------------------------------------------------------------------------------------------|----|

| 3.2 FPGA System Architecture                                                                                    | 33 |

| 3.2.1 Time and Data Manager                                                                                     | 34 |

| 3.2.2 Digital High-Pass Filter                                                                                  | 35 |

| 3.2.3 Neural Spike Discriminator                                                                                | 36 |

| 3.2.4 Decision Maker Circuitry                                                                                  | 37 |

| 3.2.5 Reset Synchronizer                                                                                        | 39 |

| 3.2.6 Stimulator Control                                                                                        | 39 |

| 3.3 Blanking Schemes                                                                                            | 40 |

| 3.3.1 Blanking Scheme for Individual Triggering                                                                 | 40 |

| 3.3.2 Blanking Scheme for Sequential Triggering                                                                 | 42 |

| 3.4 Implementation and Measurement                                                                              | 44 |

| 3.4.1 Benchtop Characterization                                                                                 | 45 |

| 3.4.2 In Vivo Experiments                                                                                       | 49 |

| 3.5 References for Chapter 3                                                                                    | 52 |

| CHAPTER                                                                                                         |    |

| 4. Miniaturized Brain-Machine-Spinal Cord Interface (BMSI) SoC for Closed-<br>Loop Intraspinal Microstimulation | 53 |

| 4.1 Integrated Microsystem: System Architecture                                                                 | 54 |

| 4.2 Integrated Microsystem: Circuit Architecture                                                                | 57 |

| 4.2.1 Analog Recording Front-End                                                                                | 57 |

| 4.2.2 DSP Unit                                                                                                  | 58 |

| 4.2.3 Stimulating Back-End                                                                                      | 59 |

| 4.2.4 Clock Generator                                                                                           | 60 |

| 4.2.5 RF-FSK Transmitter                                          |

|-------------------------------------------------------------------|

| 4.3 Electrical Measurements and Performance Characteristics       |

| 4.4 In Vivo Experiments                                           |

| 4.4.1 Individual ISMS69                                           |

| 4.4.2 Paired-Sequential ISMS70                                    |

| 4.4.3 Sequential ISMS71                                           |

| 4.5 References for Chapter 474                                    |

| CHAPTER                                                           |

| 5. Conclusions, Contributions, and Future Work75                  |

| 5.1 Contributions76                                               |

| 5.1.1 Design and Theory77                                         |

| 5.1.2 Development and Assembly77                                  |

| 5.1.3 Testing and Characterization                                |

| 5.2 Future Work                                                   |

| 5.2.1 Increasing the Number of Recording and Stimulating Channels |

| 5.2.2 Adaptive Spike Discriminators                               |

| 5.3 References for Chapter 5                                      |

| Dissertation Bibliography82                                       |

# List of Tables

| <b>Table 1.1:</b> | Summary of Target Performance Characteristics                | . 11 |

|-------------------|--------------------------------------------------------------|------|

| <b>Table 2.1:</b> | Summary of Measured Performance Characteristics for SCI_Gen1 | . 24 |

| Table 4.1:        | Summary of SCI_Gen2 Specifications and Measured Performance  | . 68 |

| Table 5.1:        | Summary of CMOS-Implemented Spike Detectors Performances     | . 80 |

# List of Figures

| Figure 1.1: | Conceptual illustration of a brain-machine-body interface (BMBI)                                                                                                                                                                                                                                                       |  |  |  |

|-------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|

| Figure 1.2: | Neurochip-II device inside the titanium casing                                                                                                                                                                                                                                                                         |  |  |  |

| Figure 1.3: | Conceptual illustration of our proposed brain-machine-spinal cord<br>interface (BMSI); closed-loop intracortical control of intraspinal<br>microstimulation (ISMS)                                                                                                                                                     |  |  |  |

| Figure 2.1: | System architecture and die microphotograph of the <i>SCI_Gen1</i> fabricated in 0.35µm AMS 2P/4M CMOS technology                                                                                                                                                                                                      |  |  |  |

| Figure 2.2: | Circuit schematic of one channel in the recording front-end and the SAR ADC architecture                                                                                                                                                                                                                               |  |  |  |

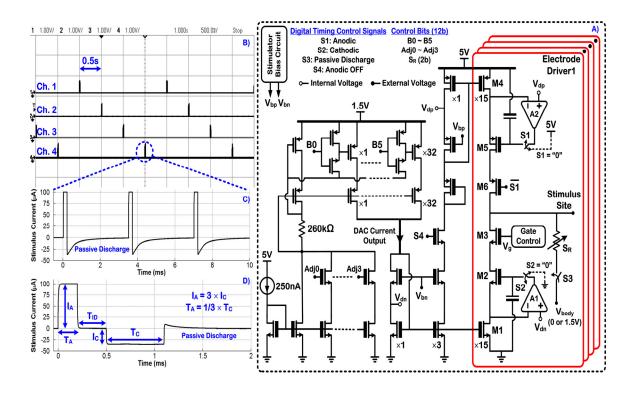

| Figure 2.3: | a) Circuit schematic of the stimulating back-end. b) Measured 4-channel sequential stimulation with a series resistive $(1k\Omega)$ -capacitive (20nF) load. c) Measured train of 3 monophasic current pulses with passive discharge used in sequential stimulation. d) Measured asymmetric biphasic current pulse. 20 |  |  |  |

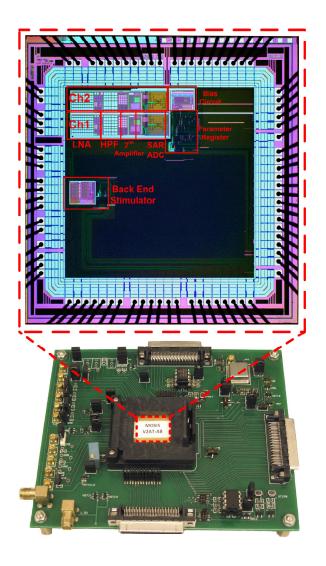

| Figure 2.4: | Top – Photograph of the custom PCB developed for biological tests and a die microphotograph of the $2.9 \times 2.9 \text{ mm}^2$ SoC fabricated in AMS $0.35 \mu \text{m}$ 2P/4M CMOS.                                                                                                                                 |  |  |  |

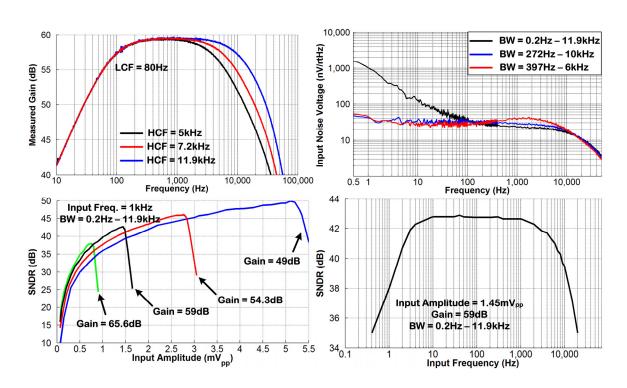

| Figure 2.5: | Top – Measured frequency response (left) and input noise (right) of the analog recording front-end. Bottom – Measured SNDR of the entire recording front-end vs. input amplitude (left) and frequency (right) 22                                                                                                       |  |  |  |

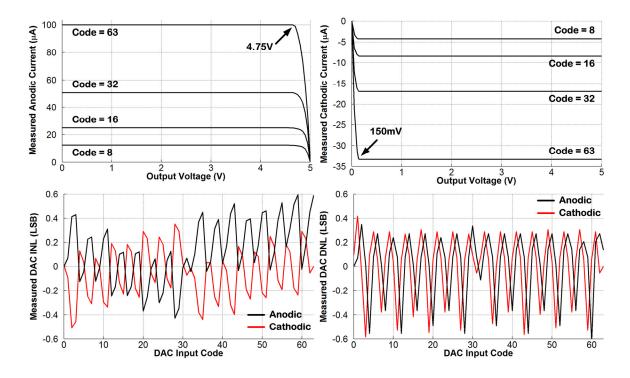

| Figure 2.6: | Top – Measured stimulator output current vs. output voltage in anodic (left) and cathodic (right) phases. Bottom – Measured DAC INL (left) and DNL (right) in both anodic and cathodic phases                                                                                                                          |  |  |  |

| Figure 2.7: | 2-second window of recorded data from the rat's cerebral cortex using the <i>SCI_Gen1</i> and an expanded view of 12 neural spikes discriminated offline                                                                                                                                                               |  |  |  |

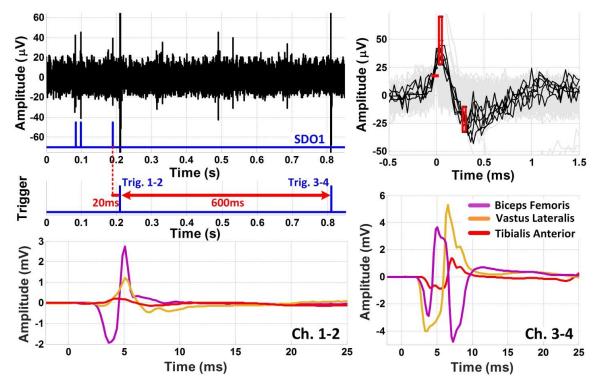

| Figure 2.8: | Recorded EMG signals from 3 hindlimb muscles activated via multichannel sequential ISMS in the rat's spinal cord using the <i>SCI_Gen1</i> 26                                                                                                                                                                          |  |  |  |

| Figure 2.9: | 1-second window of recorded data from the rat's cerebral cortex using the <i>SCI_Gen1</i> and an expanded view of six neural spikes discriminated offline                                                                                                                                                              |  |  |  |

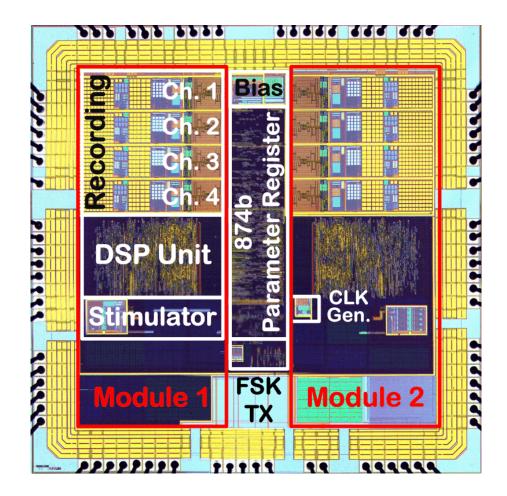

- **Figure 4.1:** Proposed system architecture and timing diagrams of the proposed *SCI\_Gen2* BMSI system. There are two identical four-channel modules in the BMSI that share a clock generator, biasing circuit, and a FSK-TX.... 56

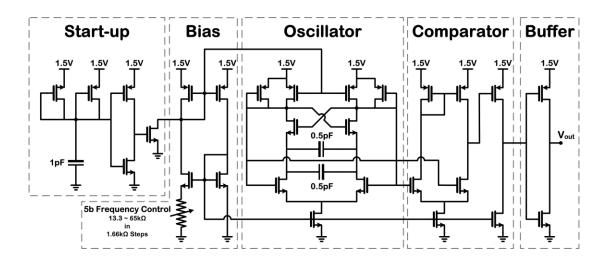

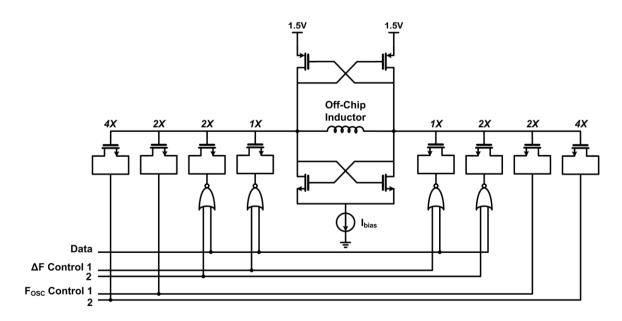

- Figure 4.3: Circuit schematic of the clock generator with nominal frequency at 1 MHz......60

- Figure 4.5:

Die microphotograph of the SCI\_Gen2 BMSI in 2P/4M AMS 0.35um CMOS.

62

## Acknowledgement

I would like to express my sincere gratitude and appreciation to my research advisor, Prof. Pedram Mohseni for his inspiration, guidance, mentorship, and full support throughout my Ph.D. study at Case Western Reserve University. This research work would not have been possible without his endless effort, extreme accuracy and enthusiastic dedication. I would also like to express my appreciation to my thesis committees, Prof. Randolph J. Nudo, Prof. Francis L. Merat, and Prof. Soumyajit Mandal for their participation, invaluable advice, thoughtful comments and suggestions to increase the quality of this research work.

I would also like to thank my previous and current colleagues in our research group, Bardia, Nok, Ali, Mehran, Mike, Debnath, Reza, Fatemeh, Hossein and from other research groups, Steve, for his help, useful discussions and technical support throughout the years. I should also acknowledge the hard work and contributions of my friends and colleagues in Prof. Nudo's lab at Kansas University Medical Center, Shawn, Scott, David, Stacey, Caleb, and Jordan in conducting biological experiments.

This work was supported by a generous gift from Ronald D. Deffenbaugh Foundation.

Finally, my profound gratitude goes to my family Azam, Naser, and Shayan. I have an amazing family, unique in many ways, and the stereotype of a perfect family in many others. Their support has been unconditional all these years; they have given up many things for me to be on the right track; cherished with me every great moment and supported me whenever I needed it.

## A Miniaturized Brain-Machine-Spinal Cord Interface (BMSI) for Closed-Loop Intraspinal Microstimulation

Abstract

by

#### SHAHABEDIN SHAHDOOSTFARD

This project has developed two integrated microsystems fabricated in a 0.35-µm two-poly four-metal CMOS process for closed-loop intraspinal microstimulation (ISMS) controlled by intracortical neural spike activity for functional recovery after spinal cord injury (SCI). In particular, first, a system-on-chip (SoC) has been developed for robust neural recording of intracortical activity in the motor cortex region of the brain, and intraspinal microstimulation of spinal cord below the injury level, both *in vivo*. This SoC uniquely integrated two recording channels in the front-end featuring a band-pass frequency response in the range of 0.2-460 Hz for low-cutoff and 5-12 kHz for high-cutoff frequencies with total input noise voltage of  $3.1\mu V_{rms}$  and noise efficiency factor (NEF) of 2.47, and four stimulating channels in the back-end for delivering charge balanced asymmetric biphasic or monophasic current pulses with passive discharge with output impedance of >100M\Omega to the spinal cord.

Next, the second SoC has been developed as a *first ever* miniaturized Brain-Machine-Spinal Cord Interface (BMSI) for cortical control of ISMS based on the level of spike activity *in vivo*. The fabricated SoC incorporated two identical four-channel modules, each compromising four neural recording channels, a DSP unit for on-the-fly stimulus trigger generation, and four stimulating channels for ISMS. The  $3.46 \times 3.46$  mm<sup>2</sup> BMSI device also integrates a clock generator circuitry and radio frequency frequency-shift-keying (RF-FSK) transmitter for autonomous operation as a stand-alone system. The DSP unit of BMSI generates stimulus triggering based on the level of spike activity on the recording channels with different patterns and controls the ISMS with programmable delay from the last discriminated spike to mimic the natural time-delay existing in the nervous system. Measured results from benchtop testing, in vitro analysis, and biological experiments with anesthetized spinal cord injured rats are presented.

# **Chapter 1**

# Introduction

The goal of this Ph.D. research work is to develop a Brain-Machine-Spinal Cord Interface (BMSI) system-on-chip (SoC) for cortical control of intraspinal microstimulation. In particular, the major focus of this research is to integrate neural recording, digital signal processing (DSP), and intraspinal microstimulation (ISMS) on a single chip for long term functional recovery after spinal cord injury (SCI) by conducting experiments *in vivo*.

## 1.1 Background and Motivation

Approximately 6 million people in the United States are currently living with paralysis in which 23% of the cases are related to spinal cord injury (SCI) with significant lifetime costs incurred (e.g., ranging from ~\$700K to >\$3M for a 25-year old SCI patient) [1.1]. Hence, research is being performed worldwide to find solutions for repairing injured spinal cords and returning function and mobility to the SCI patients for augmented quality of life [1.2]-[1.5].

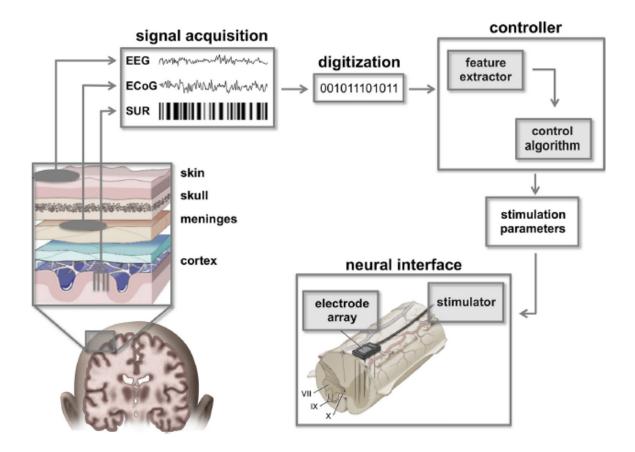

Figure 1.1: Conceptual illustration of a brain-machine-body interface (BMBI) [1.9]

Closed-loop neural interfaces have been shown to induce functional reorganization in both intact [1.6] and injured [1.7] nervous systems. These neuro-prosthetic devices, also known as brain-machine-body interfaces (BMBIs), as conceptually shown in Fig. 1.1, have evolved in the past several decades from simple, single-channel, wired devices to multifunctional, multichannel, wireless, closed-loop systems that are capable of bidirectional interfacing with the nervous system. Indeed, novel methodologies in low-power, low-noise integrated circuit (IC) design coupled with advancements in micro-electro-mechanical system (MEMS) technology have ushered in a new generation of implantable neuro-prostheses that aim to combine neural recording,

neural signal processing, and microstimulation functions in a single device for closedloop operation [1.8].

Most BMBIs operate in a so-called control-mode paradigm in which the user's intent to produce voluntary control of the user's own body (or an external device in the case of a brain machine interface (BMI)) is detected in cortical activity, and, after processing, activates the target to produce an action [1.9]. While control-mode BMBIs are promising, there are substantial challenges with regard to designing optimal signal-processing and control algorithms, as well as their efficient hardware realization, in particular in a miniaturized form, for real-time execution. Furthermore, control-mode BMBIs often require significant learning by the user, depending upon the complexity of the task, and need to be implanted throughout the user's lifetime, facing additional challenges related to long-term feasibility.

An alternative, conditioning-mode approach for BMBIs is based on mechanisms underlying neuroplasticity. The ability of the nervous system to alter the strength of synaptic efficacy underlies learning and memory in healthy organisms, and is a mechanism for recovery after injury as well [1.7]. Using the same cortical command signals of control-mode BMBIs, it is possible to condition neural connections that are remote from each other by timing the application of a small electrical pulse in the target region so that it occurs after a natural delay following cortical spike activity.

Hence one promising approach employs an activity-dependent stimulation (ADS) paradigm in which artificial connections in the nervous system are created by converting neural activity recorded from one cortical area to electrical stimuli delivered to another cortical area [1.7], muscles [1.10], or spinal cord [1.11] in real time.

In a spinal cord injury that is caused by trauma to the spine, the nerve axons that carry sensory-motor signals back and forth between the brain and the rest of the body are damaged, while the neural circuits above and below the lesion generally remain intact. This provides an opportunity for cortical control of intraspinal microstimulation (ISMS) below the level of the lesion to bridge the damaged corticospinal pathways, re-establish the lost communication channels between the cerebral cortex and the spinal cord, and facilitate functional recovery after SCI [1.12].

Such an approach would require developing a corticospinal interface integrated circuit (IC) capable of low-noise intracortical spike recording and ISMS, as well as including appropriate signal-processing algorithms (and hardware-efficient architectures for their real-time implementation) for the transformation between the cortically recorded data and stimulation parameters, which is the focus of this PhD research work.

### **1.2** Neural Interface Systems: Previous Work

In this section, a review of the previous works in terms of efficacy of spinal cord stimulation and also developing neuro-prostheses for spinal cord injury is presented.

Great strides have been made to show evidence for benefits of electrical stimulation after spinal cord injury. Stimulation within the spinal cord activates local spinal networks in specific patterns to evoke functional movements. In an extensive work, Mushahwar et al. [1.13]-[1.15] demonstrated the ability of ISMS within the lumbar spinal cord to evoke standing and stepping movements. Building on top of that, Moritz et al. [1.16] have demonstrated that fore-limb movements can also be evoked by ISMS delivered to the cervical spinal cord in non-human primates.

More recently Sunshine et al. [1.17] have explored the fore limb movements evoked by cervical ISMS both before and after injury in a clinically-relevant rodent model of mid-cervical contusion injury. A wide variety of somatotopically organized fore limb movements could be evoked prior to injury from throughout the cervical spinal cord. Following injury, there was a transient period lasting approximately 3 weeks where movement variety was dramatically reduced. By 6 and 9 weeks after injury, however, a variety of movements could again be evoked via cervical ISMS, which were not statistically different from the effects prior to injury.

To show the effectiveness of electrical stimulation of spinal cord for motor function improvements, Edgerton et al. [1.18] applied electrical stimulation to the epidural surface of the spinal cord showing great promise for directly improving motor function after SCI. Epidural stimulation of the lumbar spinal cord can facilitate stepping movements after complete spinal transection, especially when combined with serotonin agonists and movement of a motorized treadmill underfoot. Besides, Brand et al. [1.19] showed when epidural stimulation combined with robotic assistance and motor training over complex surfaces; it also appears to facilitate the formation of a relay circuit by passing a complex, staggered lesion in animal models.

To show the importance of persistent of electrical stimulation after injury, Brus Ramer et al. [1.20] showed that electrical stimulation applied to the cortex or brainstem after selective SCI promotes axon sprouting and improves motor function persisting beyond the period of stimulation.

In terms of neuro-prosthesis for patients with SCI, although devices that have the capability of some sort of recording, microstimulation, or limited signal processing functions, or a combination of them, have been previously developed for treating medically intractable epilepsy [1.21], [1-22], functional recovery after brain injury [1.23], [1.24], and deep brain stimulation treatment of Parkinson disease (PD) [1.25], [1.26], however a conditioning mode, miniaturized, and closed loop device has not been reported for spinal cord injury patients. Most of the mentioned devices were simple stimulators working in an open-loop fashion, e.g. PD devices. The other category of those devices have limited numbers of recording and stimulating channels while providing limited signal processing options which were basically a one to one recording to stimulation pairing scenario [1.24]. Also we have devices used for control mode recovery after SCI [1.11], which because of complicated algorithms and learning processes are not feasible for miniaturization and usually use desktop computers for their approaches.

A popular device that has been used for SCI-related experiments [1.27], [1.28] is a so-called Neurochip-II device first introduced by Stavros Zanos et al [1.29] as shown in Fig. 1.2.

Figure 1.2: Neurochip-II device inside the titanium casing [1.29].

This is a second generation of Nuerochip-I already introduced by the same group few years earlier [1.30]. Neurochip-2 device is made from commercially of the shelf (COTS) components and has two versions. Both versions have three recording and stimulation channels. The larger version, high output current version, has stimulation compliance voltage of  $\pm 50$ V, while the smaller version has stimulation compliance voltage of  $\pm 15$ V. The dimension of the smaller version is  $63 \times 63 \times 30$  mm<sup>3</sup>. Reported power consumption is 420 mW for the period of simultaneous recording and stimulating task and operation can last for maximum of 48 hours with a two-battery pack. This device is too big and too power hungry to be considered for any possible future implantable applications. Also, lack of wireless communication seems to be a great disadvantage of Neurochip-2. Besides, flexibility of the implemented algorithm is limited to single stimulation based on every single discriminated spike. Finally, in terms of stimulation pulses, no mechanism for draining accumulated charge in the stimulation site exists after biphasic stimulation.

### **1.3** Proposed Research

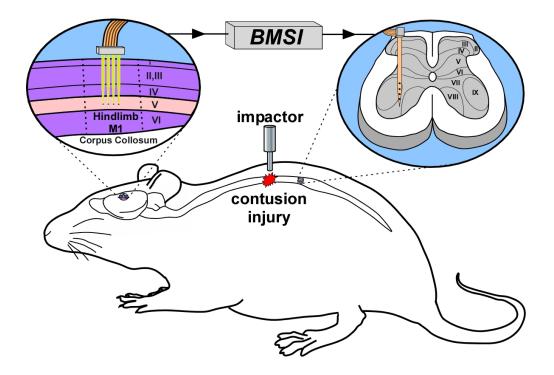

Based on the discussion presented in the previous sections, the goal of this Ph.D. research work is to develop conditioning-mode single-chip SoC for closed loop cortical control of intraspinal microstimulation *in vivo*. A conceptual illustration of such a miniaturized closed loop brain-machine-spinal cord interface is depicted in Fig. 1.3.

**Figure 1.3:** Conceptual illustration of our proposed brain-machine-spinal cord interface (BMSI); closed-loop intracortical control of intraspinal microstimulation (ISMS)

Throughout the course of this research project, two systems on chips (SoC) have been developed in 0.35-µm complementary metal-oxide-semiconductor (CMOS) technology, namely *SCI\_Gen1* and *SCI\_Gen2*. As an intermediate step between implementation of two SoCs, our proposed algorithm for the digital signal processing unit was first implemented on an FPGA and interfaced with first implemented chip (*SCI\_Gen1*) to prove the functionality of the algorithm. In the final step, second chip was implemented, *SCI\_Gen2*, which incorporated the expanded version of *SCI\_Gen1* and integrated the proposed algorithm for an autonomous operation as a stand-alone system.

In particular, *SCI\_Gen1* was developed for robust multichannel neural recording from motor cortex and intraspinal microstimulation on a single chip. *SCI\_Gen1* incorporated two neural recording channels in the front-end and four electrical stimulation channels in the back end for generation of asymmetric biphasic current pulses delivered to spinal cord. Electrical performances of the chip as well as *in vivo* functionality were verified for *SCI\_Gen1*. Intracortical neural activity were recorded from cortex of an anesthetized rat and saved on a home-based computer for offline filtering and neural spikes discriminations. For verification of stimulating back end, EMG signals were recorded from hind limb muscles of the rat while *SCI\_Gen1* was delivering current pulses to the spinal cord of the rat as a proof of effective intraspinal microstimulation.

Next, appropriate signal processing algorithms were developed on an FPGA platform for a meaningful translation from neural command signals to the ISMS pulses. In the proposed algorithm once a predetermined number of spikes are discriminated on each recording channel within pre-specified time bin duration, intraspinal microstimulation can occur based on any logic combination of those channels which have passed the criteria for spike activity. The proposed algorithm implemented on a Cyclone II FPGA device and interfaced with the *SCI\_Gen1* device. Performance and functionality of the interfaced IC and FPGA are verified *in vivo* by real time neural recording, digital signal processing, and intraspinal microstimulation. Again, EMG signals were recorded to show the efficacy of ISMS in real time.

Finally, *SCI\_Gen2* was developed which combines neural recording, digital signal processing (DSP), and ISMS in order to realize a closed loop brain machine spinal cord interface (BMSI) to improve the damaged corticospinal pathways, re-establish the lost communication channels between the cerebral cortex and the spinal cord, and facilitate functional recovery after SCI. For autonomous operation, new circuit blocks were also added to the *SCI Gen2* device as a stand-alone BMSI system.

Table 1.1 summarizes target performance characteristics and biological test goals for the proposed microsystem in this research. The remainder of this thesis presents a detailed report on the design, development, and performance characterization of these microsystems as organized in the following chapters:

- <u>Chapter 2</u> presents the *SCI\_Gen1* SoC. The system design procedure for singlechip neural recording and microstimulating is described and measured results from benchtop electrical characterization and biological experiments with anesthetized rats are presented.

- <u>Chapter 3</u> reports the field-programmable gate array (FPGA) implementation of a digital signal processing (DSP) unit for real-time generation of stimulus triggering from recorded neural activity. Measured results from benchtop and *in vitro* experiments as well as biological *in vivo* experiments on anesthetized rats by interfacing FPGA and *SCI Gen1* SoC are presented.

- <u>Chapter 4</u> combines our previous work in order to develop a BMSI SoC for closed-loop control of intraspinal microstimulation. Measured results from benchtop testing and biological experiments with anesthetized rats are presented.

- <u>Chapter 5</u> draws final conclusions and highlights the major contributions of this research, as well as identifies further research opportunities in this field.

| PERFORMANCE CHARACTERISTICS (BENCHTOP)                   |                                                                                                                             |                                                                                                               |  |  |  |  |

|----------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------|--|--|--|--|

| SoC Functionality                                        |                                                                                                                             | Neural Recording, Digital Signal<br>Processing, and Electrical Stimulation in a<br>Closed-loop fashion        |  |  |  |  |

| Number of Recording/Stimulating Channels                 |                                                                                                                             | 4/4                                                                                                           |  |  |  |  |

| Power Supply                                             |                                                                                                                             | Recording Front-End and DSP Unit: 1.5V<br>Stimulating Back-End (5V)                                           |  |  |  |  |

|                                                          | Voltage Gain                                                                                                                | 50 – 66 dB                                                                                                    |  |  |  |  |

| Recording Front-End<br>For Intracortical                 | ADC Resolution                                                                                                              | Effective > 9 bits                                                                                            |  |  |  |  |

| Recording                                                | Input Noise Voltage                                                                                                         | $< 5\mu V_{rms}$                                                                                              |  |  |  |  |

| Recording                                                | Bandwidth                                                                                                                   | LCF: 0~500Hz HCF: 5~10kHz                                                                                     |  |  |  |  |

| Digital Signal<br>Processing Unit                        | Functions                                                                                                                   | High pass filter, neural spike discriminator,<br>stimulation pattern generator, neural<br>recording blanking, |  |  |  |  |

|                                                          | Power Consumption                                                                                                           | < 60µW                                                                                                        |  |  |  |  |

| Stimulating Back-End                                     | Stimulus Waveform                                                                                                           | Asymmetric Biphasic with passive<br>discharge                                                                 |  |  |  |  |

| for Intraspinal                                          | Output Current                                                                                                              | $0-100\mu A$                                                                                                  |  |  |  |  |

| Microstimulation                                         | Stimulation Frequency                                                                                                       | > 200 Hz                                                                                                      |  |  |  |  |

|                                                          | Output Impedance                                                                                                            | > 50MΩ                                                                                                        |  |  |  |  |

| Other Functionalities                                    |                                                                                                                             | Wireless FSK Transmission (Uplink)                                                                            |  |  |  |  |

| Tech                                                     | nology                                                                                                                      | AMS 0.35µm CMOS                                                                                               |  |  |  |  |

| PER                                                      | FORMANCE CHARAG                                                                                                             | CTERISTICS (In Vivo)                                                                                          |  |  |  |  |

| Functionality Verificati<br>Phase w/ Anesthetized<br>Rat | <ul> <li>Multichannel</li> <li>Processing of I</li> <li>triggers</li> <li>Multichannel S</li> <li>Wirelessly sen</li> </ul> |                                                                                                               |  |  |  |  |

## Table 1.1: Summary of Target Performance Characteristics

## **1.4 References for Chapter 1**

- [1.1] Christopher & Dana Reeve Foundation. Available online at <u>www.christopherreeve.org</u>.

- [1.2] R. van den Brand, et al., "Restoring voluntary control of locomotion after paralyzing spinal cord injury," Science, vol. 336, pp. 1182-1185, June 1, 2012.

- [1.3] Y. K. Lo, et al., "A 176-channel 0.5cm3 0.7g wireless implant for motor function recovery after spinal cord injury," in Dig. Tech. Papers IEEE Int. Solid-State Circuits Conf. (ISSCC'16), pp. 382-383, February 2016.

- [1.4] L. R. Hochberg, et al., "Reach and grasp by people with tetraplegia using a neurally controlled robotic arm," Nature, vol. 485, pp. 372-375, May 2012.

- [1.5] C. E. Bouton, et al., "Restoring cortical control of functional movement in a human with quadriplegia," Nature, vol. 533, pp. 247-250, May 2016.

- [1.6] A. Jackson, J. Mavoori, and E. E. Fetz, "Long-term motor cortex plasticity induced by an electronic neural implant," Nature, vol. 444, pp. 56-60, 2006.

- [1.7] D. J. Guggenmos, et al., "Restoration of function after brain damage using a neural prosthesis," Proc. Natl. Acad. Sci. USA (PNAS), vol. 110, no. 52, pp. 21177-21182, December 24, 2013.

- [1.8] S. Stanslaski, et al., "Design and validation of a fully implantable, chronic, closed-loop neuromodulation device with concurrent sensing and stimulation," IEEE Trans. Neural Syst. Rehab. Eng., vol. 20, no. 4, pp. 410-421, July 2012.

- [1.9] P. J. Grahn, et al., "Restoration of motor function following spinal cord injury via optimal control of intraspinal microstimulation: toward a next-generation closed-loop neural prosthesis," Front. Neurosci., vol. 8, no. 296, pp. 1-12, September 2014.

- [1.10] C. T. Moritz, S. I. Perlmutter, and E. E. Fetz, "Direct control of paralyzed muscles by cortical neurons," Nature, vol. 456, pp. 639-643, 2008.

- [1.11] J. B. Zimmermann and A. Jackson, "Closed-loop control of spinal cord stimulation to restore hand function after paralysis," Front. Neurosci., vol. 8, no. 87, pp. 1-8, May 2014.

- [1.12] Mondello, S. E., Kasten, M. R., Horner, P. J., and Moritz, C. T., "Therapeutic intraspinal stimulation to generate activity and promote long-term recovery." Front. Neurosci. 8:21. doi: 10.3389/fnins.2014.00021, 2014.

- [1.13] Mushahwar, V. K., and Horch, K. W. "Selective activation and graded recruit- ment of functional muscle groups through spinal cord stimulation." Ann. N.Y. Acad. Sci. 860, 531–535, 1998.

- [1.14] Mushahwar, V. K., Gillard, D. M., Gauthier, M. J., and Prochazka, A. "Intraspinal micro stimulation generates locomotor-like and feedback- controlled movements." IEEE Trans. Neural Syst. Rehabil. Eng. 10, 68–81, 2002.

- [1.15] Mushahwar, V. K., Aoyagi, Y., Stein, R. B., and Prochazka, A. "Movements generated by intraspinal microstimulation in the intermediate gray matter of the anesthetized, decerebrate, and spinal cat." Can. J. Physiol. Pharmacol. 82, 702–714, 2004.

- [1.16] Moritz, C. T., Lucas, T. H., Perlmutter, S. I., and Fetz, E. E. "Forelimb movements and muscle responses evoked by microstimulation of cervical spinal cord in sedated monkeys." J. Neurophysiol. 97, 110–120, 2007.

- [1.17] Sunshine, M. D., Cho, F. S., Lockwood, D. R., Fechko, A. S., Kasten, M. R., and Moritz, C. T. "Cervical intraspinal microstimulation evokes robust forelimb movements before and after injury." J. Neural Eng. 10:036001. doi: 10.1088/1741-2560/10/3/036001, 2013.

- [1.18] Edgerton, V. R., and Harkema, S. "Epidural stimulation of the spinal cord in spinal cord injury: current status and future challenges. Expert Rev. Neurother. 11, 1351–1353. doi: 10.1586/ern.11.129, 2012.

- [1.19] Van Den Brand, R., Heutschi, J., Barraud, Q., Digiovanna, J., Bartholdi, K., Huerlimann, M., et al. "Restoring voluntary control of locomotion after paralyzing spinal cord injury." Science 336, 1182–1185. doi: 10.1126/sci- ence.1217416, 2012.

- [1.20] Brus-Ramer, M., Carmel, J. B., Chakrabarty, S., and Martin, J. H. "Electrical stimulation of spared corticospinal axons augments connections with ipsi- lateral spinal motor circuits after injury." J. Neurosci. 27, 13793–13801. doi: 10.1523/JNEUROSCI.3489-07, 2007.

- [1.21] K. Abdelhalim, H. Mazhab Jafari, L. Kokarovtseva, J. L. P. Velazquez, and R. Genov, "64-channel UWB wireless neural vector analyzer SOC with a closed-loop phase synchrony-triggered neurostimulator," IEEE J. Solid-State Circuits, vol. 48, no. 10, pp. 2494-2510, October 2013.

- [1.22] T. L. Skarpaas and M. J. Morrell, "Intracranial stimulation therapy for epilepsy," Neurotherapeutics, vol. 6, pp. 238-243, 2009.

- [1.23] D. J. Guggenmos, M. Azin, S. Barbay, J. D. Mahnken, C. Dunham, P. Mohseni, and R. J. Nudo, "Restoration of function after brain damage using a neural prosthesis," in Proc. Natl. Acad. Sci. USA, in press.

- [1.24] M. Azin, D. J. Guggenmos, S. Barbay, R. J. Nudo, and P. Mohseni, "A battery-powered activity-dependent intracortical microstimulation IC for brain-machine-brain interface," IEEE J. Solid-State Circuits, vol. 46, no. 4, pp. 731-745, April 2011.

- [1.25] A. T. Avestruz, W. Santa, D. Carlson, R. Jensen, S. Stanslaski, A. Helfenstine, and T. Denison, "A 5µW/channel spectral analysis IC for chronic bidirectional brain-machine interfaces," IEEE J. Solid-State Circuits, vol. 43, no. 12, pp. 3006-3024, December 2008.

- [1.26] S. Stanslaski, P. Afshar, P. Cong, J. Giftakis, P. Stypulkowski, D. Carlson, D. Linde, D. Ullestad, A. T. Avestruz, and T. Denison, "Design and validation of a fully implantable, chronic, closed-loop neuromodulation device with concurrent sensing and stimulation," IEEE Trans. Neural Syst. Rehab. Eng., vol. 20, no. 4, pp. 410-421, July 2012.

- [1.27] Nishimura, Y., Perlmutter, S.I., & Fetz, E. E., "Restoration of upper limb movement via artificial corticospinal and musculospinal connections in a monkey with spinal cord injury." Frontiers in neural circuits, 7, 2013.

- [1.28] Nishimura Y, Perlmutter SI, Eaton RW, Fetz EE, "Spike-timing-dependent plasticity in primate corticospinal connections induced during free behavior." Neuron 80(5):1301– 1309, 2013.

- [1.29] Zanos, S.; Richardson, A.G.; Shupe, L.; Miles, F.P.; Fetz, E.E., "The Neurochip-2: An Autonomous Head-Fixed Computer for Recording and Stimulating in Freely Behaving Monkeys," in Neural Systems and Rehabilitation Engineering, IEEE Transactions on , vol.19, no.4, pp.427-435, Aug. 2011.

- [1.30] J. Mavoori et al., "An autonomous implantable computer for neural recording and stimulation in unrestrained primates," J. Neurosci. Methods, vol. 148, no. 1, pp. 71–77, Oct. 2005.

# Chapter 2

# Integrated Microsystem for Intracortical Neural Recording and Intraspinal Microstimulation

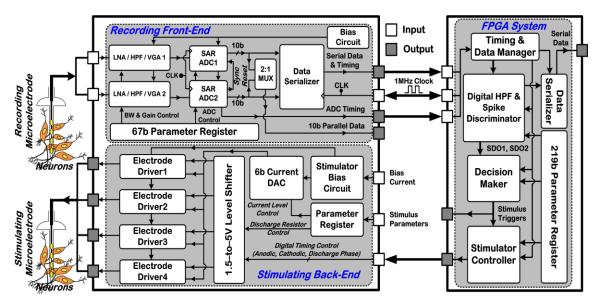

This Chapter describes our *SCI\_Gen1* system-on-chip (SoC) fabricated in AMS 0.35µm 2P/4M CMOS for reliably recording neural activity in the brain and delivering asymmetric biphasic current pulses as intraspinal microstimulation (ISMS) to the spinal cord *in vivo* as the first generation chip for functional recovery after SCI. The implemented SoC uniquely combines two neural recording in the front-end and four microstimulating channels in the back-end. In the following sections, system architecture of the neural recording and stimulating back end is described. Besides, measurement results of the bench-top characterization of the *SCI\_Gen1* device as well as *in vivo* experiments conducted on anesthetized rats are presented [2.1]-[2.3].

### 2.1 System Architecture

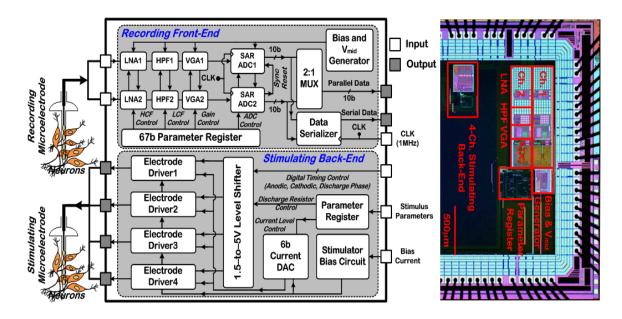

Fig. 2.1 shows the IC architecture designed to interface with the cerebral cortex and the spinal cord via a pair of implanted microelectrode arrays. The IC incorporates two identical recording channels with digitally programmable gain and bandwidth for ac amplification, dc baseline stabilization, high-pass filtering and 10b digitization of the recorded neural spikes. A 2:1 multiplexer and a data serializer block allow the user to access the digitized output of one channel in parallel or both channels in serial fashion, respectively. The IC also incorporates 4 identical stimulating channels to deliver ISMS trains of charge-balanced monophasic or asymmetric biphasic current pulses (0 to  $\sim$ 100µA) followed by passive discharge [2.4], [2.5].

**Figure 2.1:** System architecture and die microphotograph of the *SCI\_Gen1* fabricated in 0.35µm AMS 2P/4M CMOS technology.

In its nominal mode of operation for benchtop and *in vivo* testing purposes, the stimulating back-end is programmed to stimulate the spinal cord sequentially on all four channels with a programmable inter-channel delay to evoke four different limb movements in the subject. All current pulse parameters such as amplitude and duration as well as frequency and number within an ISMS train are also programmable for the IC.

### 2.2 Integrated Circuit Architecture

The system proposed in Fig. 2.1 has been realized using 0.35µm mix-mode CMOS process. Recording front-end was realized using thin-oxide transistors and operate at 1.5V whereas stimulating back-end was realized with thick-oxide transistors, usually used in IO cells, and operates at 5V. The following subsections describe designed circuitry for each individual block.

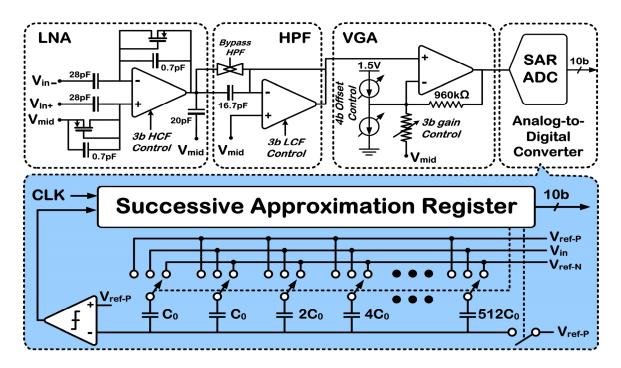

#### **2.2.1. Recording Front-End**

Fig. 2.2 depicts the circuit schematic of one channel in the recording front-end, operating from 1.5V and comprising a low-noise amplifier (LNA) with adjustable high cutoff frequency (HCF), high-pass filter (HPF) with adjustable low cutoff frequency (LCF), secondary amplifier with variable gain and adjustable offset, and 10b successive approximation register (SAR) ADC. The LNA provides fixed 32dB of ac gain via capacitive feedback, and dc baseline stabilization via a MOS-bipolar pseudo resistor in parallel with the feedback capacitor (0.7pF) [2.6]. An ultralow-transconductance operational transconductance amplifier (OTA) and a 16.7-pF capacitor form a 1<sup>st</sup>-order HPF with an adjustable low cutoff frequency from 0 to 525 Hz by varying the OTA tail current. The analog HPF is designed to attenuate 60 Hz and remove low-frequency LFPs that might be present in the recorded neural data. The analog recording front-end features a bandpass frequency response with eight different gain values in 49 dB - 65.6 dB at 1kHz, as well as LCF and HCF values digitally programmable in 0.2 Hz – 460 Hz and 5 kHz - 11.9 kHz by tuning the bias currents of the HPF and LNA, respectively. The secondary amplifier with a resistive feedback provides additional 3-bit gain in the range of 17-33.6 dB, and has a 4b offset adjustment mechanism by injecting a small dc current into the feedback path. The secondary amplifier provides a rail-to-rail output voltage swing and drives the 12-pF capacitor network of the subsequent ADC that converts the amplified neural data to a 10b digital code for further processing by the DSP unit [2.7].

Figure 2.2: Circuit schematic of one channel in the recording front-end and the SAR ADC architecture.

The 10b SAR ADC, whose capacitive network is driven by the preceding variable-gain amplifier (VGA), is nominally clocked at 1MHz, with each ADC conversion cycle taking 28 clock cycles in which 16 cycles are dedicated to sampling, 1 cycle to hold, 10 cycles to approximation and 1 cycle to reset, thus providing a sampling frequency of 35.7kSa/s that is adequate for recording single-unit neural spikes with frequency components in 100Hz–10kHz. The extended sampling period helps relax current drive requirements of the preceding VGA for low-power operation. The ADC

digitizes the amplified/filtered neural data with a signal-to-noise and distortion ratio (SNDR) of 56dB (i.e., ENOB of 9b) at a maximum sampling frequency of 65kSa/s.

#### 2.2.2. Stimulating Back-End

Fig. 2.3 shows the circuit schematic of the stimulating back-end, incorporating four identical electrode drivers that share a 6b current-based DAC. Each electrode driver operates from 5V and integrates a pair of pMOS (anodic) and nMOS (cathodic) current sources with thick-oxide transistors and boosted output impedance via negative feedback, provided by two op-amps  $(A_{1,2})$ , for constant-current stimulation [2.8]. The DAC operates from 1.5V and outputs a programmable current from 0 to 2.2µA with 6b resolution, which is then amplified to generate a maximum current of  $\sim 100 \mu A$  for the anodic phase. The cathodic-phase current is set to be 1/3 of that in the anodic phase via proper transistor sizing ratios to generate an asymmetric biphasic current pulse for optimal use of available voltage headroom (5V). The DAC also employs a 4b current-adjust mechanism to fine tune the desired output stimulus current in the presence of process and voltage (PV) variations. Additional circuitry is used in each electrode driver to control the gate voltage of transistor  $M_3$  in the nMOS current source and limit the drain-source voltage across  $M_{2,3}$  to  $\sim V_{DD}/2$  (i.e.,  $\sim 2.5V$ ) for avoiding hot-carrier effects when the stimulus site voltage is near the supply rail [2.9]-[2.11].

**Figure 2.3:** a) Circuit schematic of the stimulating back-end. b) Measured 4-channel sequential stimulation with a series resistive  $(1k\Omega)$ -capacitive (20nF) load. c) Measured train of 3 monophasic current pulses with passive discharge used in sequential stimulation. d) Measured asymmetric biphasic current pulse.

### 2.3 Benchtop and In Vivo Measurement Results

A prototype SoC was fabricated in AMS  $0.35\mu m$  2P/4M CMOS, measuring ~2.9mm × 2.9 mm including the bonding pads (see Fig. 2.4). Electrical performance of individual circuit blocks was characterized in benchtop measurements, and their *in vivo* functionality was verified in biological experiments with anesthetized laboratory rats.

**Figure 2.4:** Top – Photograph of the custom PCB developed for biological tests and a die microphotograph of the  $2.9 \times 2.9 \text{ mm}^2$  SoC fabricated in AMS  $0.35 \mu m 2P/4M$  CMOS.

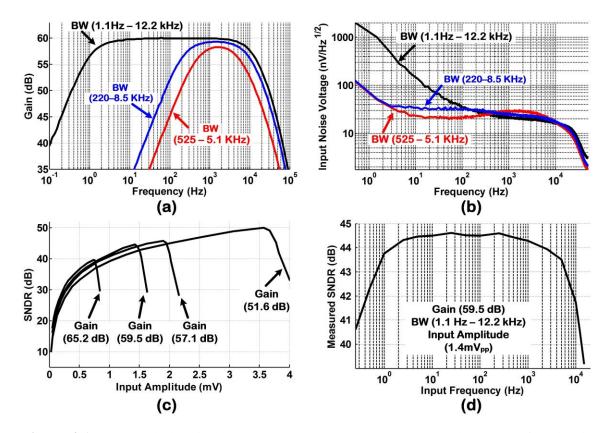

The top plots in Fig. 2.5 show the measured frequency response and input noise performance of the analog recording front-end. With the mid-band ac gain nominally set to 60dB and the LCF at 80Hz, the HCF could be varied from 5 to 11.9 kHz by changing the bias current of the LNA, as shown in the left plot. In the right plot, note how the HPF effectively removed the flicker noise contribution, when the LCF was digitally set to 272 and 397Hz (the HPF was bypassed for the case of the recording BW of 0.2Hz–11.9 kHz.) With the recording BW set to 272Hz–10kHz, the input-referred noise voltage measured

in 0.5Hz–50kHz was  $3\mu$ Vrms, leading to noise efficiency factor (NEF) of 2.47 for the LNA.

**Figure 2.5:** Top – Measured frequency response (left) and input noise (right) of the analog recording front-end. Bottom – Measured SNDR of the entire recording front-end vs. input amplitude (left) and frequency (right).

The bottom plots in Fig. 2.5 show the measured SNDR at the SAR ADC output versus the amplitude and frequency of a sinusoidal signal applied to the LNA input. The recording BW was digitally set to 0.2Hz-11.9 kHz. As can be seen in the left plot, lower gain values provided higher input dynamic range, whereas higher gain values provided better signal resolution. With a measured gain of 59dB, the recording front-end could provide peak SNDR of 42.6dB with input amplitude of 1.45mVpp at 1 kHz and >39.5dB within the frequency range of 100Hz-10 kHz of extracellular neural spikes.

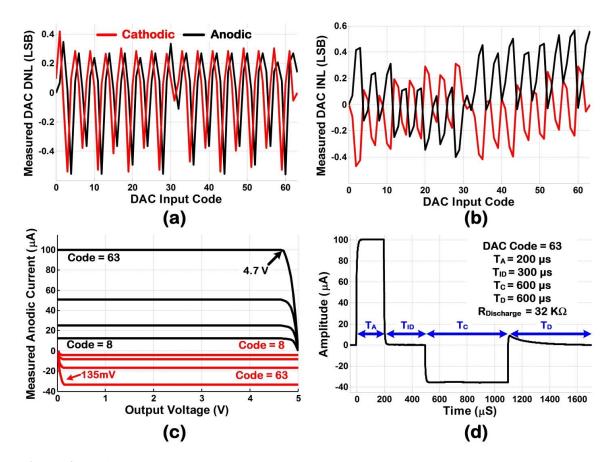

The top plots in Fig. 2.6 depict the measured stimulator output current versus its output voltage for four different DAC input codes when sourcing and sinking current in

the anodic and cathodic phases, respectively. The stimulator output voltage could reach at least 4.75V (going toward 5V) and 150mV (going toward 0V) when sourcing and sinking current, respectively, with a 5-V supply. The output impedance was measured to be  $>100M\Omega$  (limited by the precision of our measurement setup), sufficiently high for constant-current stimulation.

**Figure 2.6:** Top – Measured stimulator output current vs. output voltage in anodic (left) and cathodic (right) phases. Bottom – Measured DAC INL (left) and DNL (right) in both anodic and cathodic phases.

The bottom plots in Fig. 2.6 depict the current DAC INL and DNL that were measured to be less than  $\pm 0.62$  LSB (anodic) and  $\pm 0.58$  LSB (cathodic).

Table 2.1 tabulates measured performance of the recording and stimulating blocks of the IC.

| RECORDING FRONT-END    |                                                        | STIMULATING BACK-END                   |              |              |

|------------------------|--------------------------------------------------------|----------------------------------------|--------------|--------------|

| AC Gain @ 1kHz         | 49 - 65.6dB                                            |                                        | Anodic       | Cathodic     |

| HCF<br>LCF             | 5 – 11.9kHz<br>0.2 – 460Hz                             | Voltage                                |              |              |

| Input Noise<br>Voltage | $3\mu V_{rms}$<br>(0.5Hz – 50kHz)                      | Compliance<br>(Max. I <sub>OUT</sub> ) | 4.75 (of 5V) | 4.85 (of 5V) |

| NEF                    | 2.47<br>(272Hz – 10kHz)                                | Max. I <sub>OUT</sub>                  | 100µA        | 33.3µА       |

| CMRR/PSRR              | 56 / 63.4dB                                            | Output Imp.                            | > 100MΩ      |              |

| INL/DNL                | <±1.15 LSB                                             | INL (LSB)                              | < ±0.59      | < ±0.50      |

| SNDR/ENOB              | 56dB / 9b @ f <sub>s,max</sub> =<br>65kSa/s            | DNL (LSB)                              | < ±0.62      | <±0.58       |

| Power Dissipation      | $31.9\mu$ W<br>(0.2Hz - 11.9kHz;<br>$f_{CLK} = 1$ MHz) | Supply<br>Sensitivity                  | -69nA/V      | -10nA/V      |

|                        |                                                        | Current<br>Efficiency                  | 96.1%        | 94.7%        |

Table 2.1: Summary of Measured Performance Characteristics for SCI\_Gen1

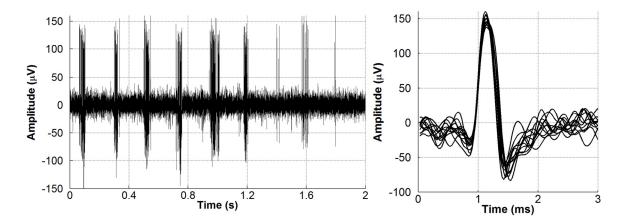

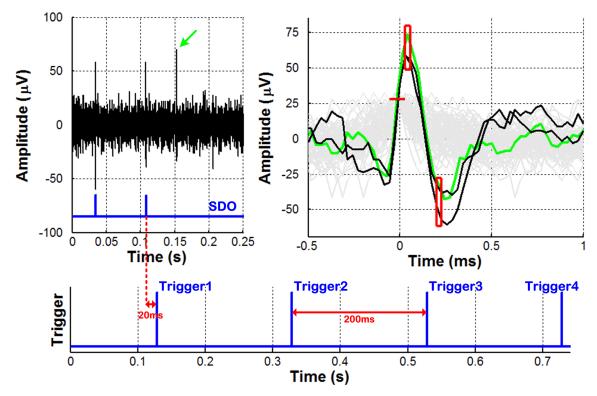

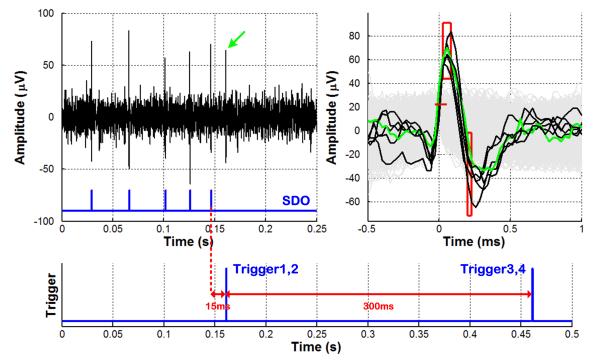

For *in vivo* tests, first a pair of recording and stimulating microelectrode arrays was acutely implanted in a healthy anesthetized rat's cerebral cortex and spinal cord respectively. Fig. 2.7 shows a 2-s window of recorded data from the rat's cerebral cortex and an expanded view of several extracellular neural spikes extracted from the data using offline spike discrimination. All amplitudes are shown as input-referred.

Next, the IC delivered 4-channel sequential stimulation with 1-s delay to the rat's spinal cord with a single monophasic current pulse ( $25\mu A$ ,  $200\mu s$ ) followed by passive discharge. Stimulus site impedance was in the range of 50–60k $\Omega$  at 1kHz.

**Figure 2.7:** 2-second window of recorded data from the rat's cerebral cortex using the *SCI\_Gen1* and an expanded view of 12 neural spikes discriminated offline.

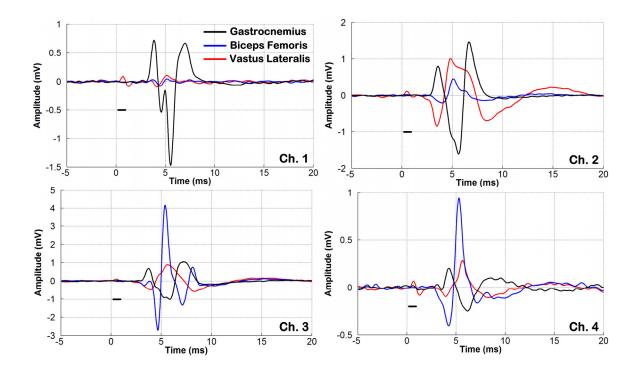

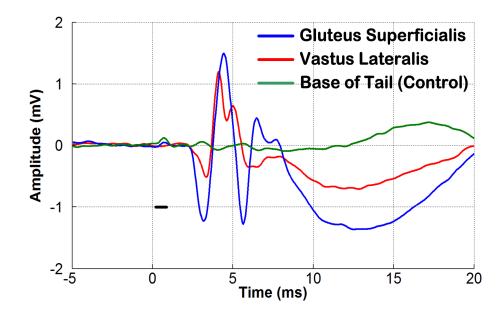

Fig. 2.8 depicts the fine-wire electromyography (EMG) signals recorded with benchtop equipment from 3 muscles in the rat's hind limb (with the black bar showing the onset and duration of stimulus current pulse), demonstrating distinct muscle pattern activation via multichannel ISMS in the rat's spinal cord.

**Figure 2.81:** Recorded EMG signals from 3 hindlimb muscles activated via multichannel sequential ISMS in the rat's spinal cord using the *SCI\_Gen1*.

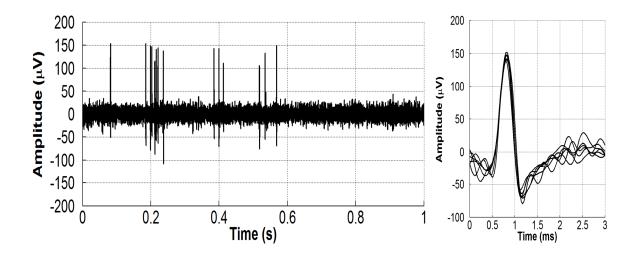

In another *in vivo* experiment, same procedure was followed in a spinal cord injured (SCI) rat. For *in vivo* tests, a recording microelectrode array was acutely implanted in the sensory cortex of a ketamine-anesthetized rat. Fig. 2.9 shows a 1-second window of recorded data from the rat's cerebral cortex and an expanded view of several evoked neural spikes extracted from the data using offline spike discrimination. All amplitudes are shown as input-referred.

**Figure 2.9:** 1-second window of recorded data from the rat's cerebral cortex using the *SCI\_Gen1* and an expanded view of six neural spikes discriminated offline.

Next, following the same procedure as previously described, a second rat was anesthetized with isoflurane and placed in a spinal stabilizer, and the thoracic and lumbar spinal column was exposed. This rat had also received a contusion injury to the thoracic spinal cord at level T8-T9 more than four weeks prior to the *in vivo* experiment.

Under ketamine anesthesia, a stimulating microelectrode array was acutely implanted in the rat's spinal cord below the level of the contusion injury, and the IC was used to deliver single-channel ISMS to the spinal cord with a single monophasic current pulse (anodic, 25µA, 200µs) followed by passive discharge.

Fig. 2.10 shows the fine-wire electromyography (EMG) signals recorded with benchtop equipment from two muscles in the rat's hindlimb (the horizontal black bar indicating the onset and duration of the stimulus current pulse), demonstrating successful muscle activation via ISMS in the SCI rat's spinal cord by the IC.

**Figure 2.10:** Recorded EMG signals from two hindlimb muscles of an SCI rat activated via ISMS in the rat's spinal cord using the *SCI\_Gen1*. The horizontal black bar depicts the onset and duration of the single stimulus current pulse (monophasic anodic with passive discharge).

# 2.4 References for Chapter 2

- [2.1] S. Shahdoost, S. Frost, R. Nudo, and P. Mohseni, "A multichannel corticospinal interface IC for intracortical spike recording and distinct muscle pattern activation via intraspinal microstimulation," in *Proc. 57th Annu. Int. IEEE Midwest Symp. Circuits and Systems* (MWSCAS'14), pp. 310-313, College Station, TX, August 3-6, 2014.

- [2.2] S. Shahdoost, S. Frost, G. Van Acker, S. DeJong, C. Dunham, S. Barbay, R. Nudo, and P. Mohseni "Towards a miniaturized brain-machine-spinal cord interface (BMSI) for restoration of function after SCI," 41th Neural Interfaces Conference (NIC), June 23-25, Dallas, Texas, 2014.

- [2.3] M. Azin, D. J. Guggenmos, S. Barbay, R. J. Nudo, and P. Mohseni, "A battery-powered activity-dependent intracortical microstimulation IC for brain-machine-brain interface," *IEEE J. Solid-State Circuits*, vol. 46, no. 4, pp. 731-745, April 2011.

- [2.4] T. G. Constandinou, J. Georgiou, and C. Toumazou, "A partial-current-steering biphasic stimulation driver for vestibular prostheses," *IEEE Trans. Biomed. Circuits and Systems*, vol. 2, no. 2, pp. 106-113, June 2008.

- [2.5] X. Liu, A. Demosthenous, and N. Donaldson, "An integrated implantable stimulator that is fail-safe without off-chip blocking capacitors," *IEEE Trans. Biomed. Circuits and Systems*, vol. 2, no. 3, pp. 231-244, September 2008.

- [2.6] R. R. Harrison, "The design of integrated circuits to observe brain activity," *Proceedings* of the IEEE, vol. 96, no. 7, pp. 1203-1216, July 2008.

- [2.7] M. D. Scott, B. E. Boser, and K. S. J. Pister, "An ultralow-energy ADC for smart dust," *IEEE J. Solid-State Circuits*, vol. 38, no. 7, pp. 1123-1129, July 2003.

- [2.8] M. Ghovanloo and K. Najafi, "A compact large-voltage-compliance high-outputimpedance programmable current source for implantable microstimulators," *IEEE Trans. Biomed. Eng.*, vol. 52, no. 1, pp. 97-105, January 2005.

- [2.9] Y. Tsividis, *Operation and Modeling of the MOS Transistor*, 2nd ed., New York, NY: Oxford University Press, 1999.

- [2.10] S. Guo, H. Lee, and P. Loizou, "A 9-bit configurable current source with enhanced output resistance for cochlear stimulators," in *Proc. Custom Integrat. Circ. Conf. (CICC'08)*, pp. 511-514, September 2008.

- [2.11] M. M. Ahmadi, "A new modeling and optimization of gain-boosted cascode amplifier for high-speed and low-voltage applications," *IEEE Trans. Circuits and Systems-II*, vol. 53, no. 3, pp. 169-173, March 2006.

# Chapter 3

# FPGA Implementation of Stimulus Trigger Generation from Intracortical Spike Activity

This chapter describes required digital signal processing (DSP) for closed-loop cortical control of spinal cord stimulations as a new approach for restoration of functional recovery after spinal cord injury. In the following sections, we describe the developed algorithm by which recorded neural activity in the recording front-end of *SCI\_Gen1* chip will control the electrical stimulation task of the stimulating back-end. The proposed DSP comprises a high-pass filter (HPF), spike discriminator unit, decision maker unit, and stimulator control unit as its core building blocks and includes auxiliary blocks for interfacing with *SCI\_Gen1* device.

The proposed algorithm for the DSP unit has been implemented on a fieldprogrammable gate array (FPGA), synthesized on to the Cyclone II FPGA, and interfaced with *SCI\_Gen1* SoC [3.1]-[3.5]. Benchtop measurements and *in vivo* experiments results show the functionality and performance of the proposed algorithm in action. In the following sections, first proposed algorithm is thoroughly described and then experimental results from interfacing FPGA implementation with *SCI\_Gen1* chip are presented.

# **3.1 Operation Concept**

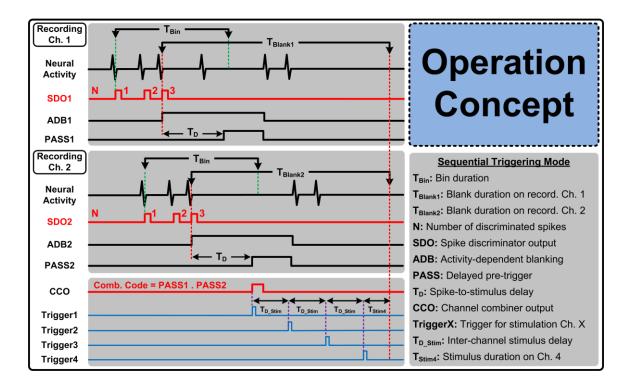

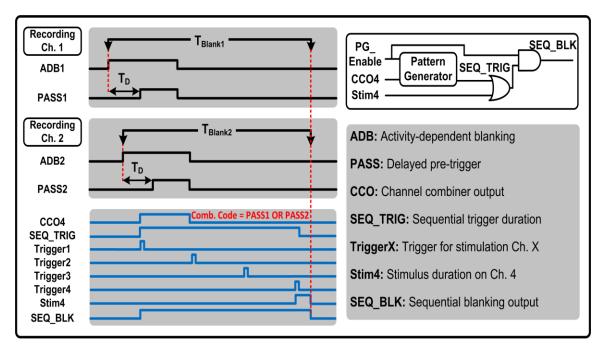

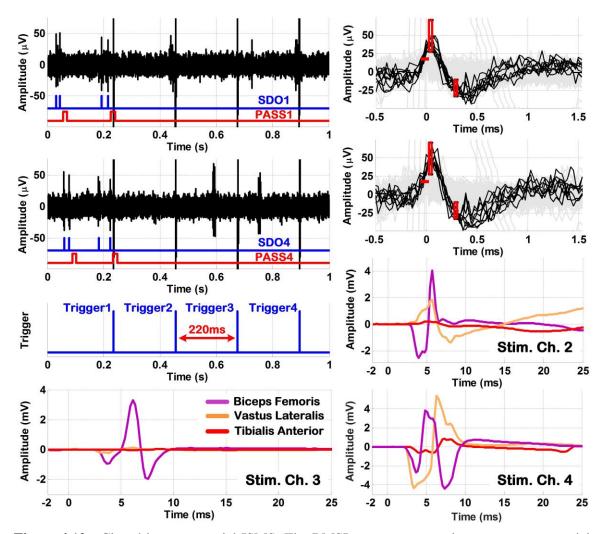

Fig. 3.1 illustrates our strategy for generating stimulus triggers from intracortical neural spike activity recorded and discriminated in real-time from cortical motor regions [3.1]. For simplicity, a representative case involving two recording and four stimulating channels is depicted, although the general approach can be expanded to incorporate more recording and stimulating channels as well.

**Figure 3.1:** Conceptual illustration of the strategy for stimulus trigger generation from intracortical neural spike activity. A representative case involving two recording and four stimulating channels in sequential triggering mode is illustrated.

As seen in Fig. 3.1, a spike discriminator output signal, SDO, is activated on each recording channel upon successful discrimination of each neural spike event. Once a predetermined number of neural spikes, N, are discriminated on each recording channel within a pre-specified time bin duration, T<sub>Bin</sub>, a PASS signal is activated on each channel after a programmable time delay, T<sub>D</sub>, following the discrimination of the last spike. The trigger signals for stimulation activation are then generated based upon any logic combination of the PASS signals. For example, Fig. 3.1 illustrates a representative case when sequential triggering is generated once trigger-generation criteria are simultaneously satisfied on both input data channels (i.e., trigger generation is based upon the logic AND function of the two PASS signals).

Implemented in hardware using an FPGA, all parameters in Fig. 3.1 are useradjustable within a pre-specified range that is guided by design considerations when the implementation is ultimately ported from the FPGA to an IC platform for full miniaturization of such BMSI systems.

While Fig. 3.1 depicts a four-channel, *sequential* triggering scenario with a programmable inter-channel delay,  $T_{D_stim}$ , the reconfigurable FPGA-based realization also supports other triggering scenarios, e.g., *individual* triggering where each trigger signal itself (i.e., *TriggerX*) is defined as a logic combination of the *PASS* signals using a 4b combination code.

As seen in Fig. 3.1, the strategy also provides an ability to blank (i.e., disregard) the neural data on a recording channel during  $T_{Blank}$  (i.e., from discrimination of the last spike until the end of stimulus duration on all four channels). The rationale and

implementation details of blanking for both sequential and individual triggering cases are further explained in Blanking Section.

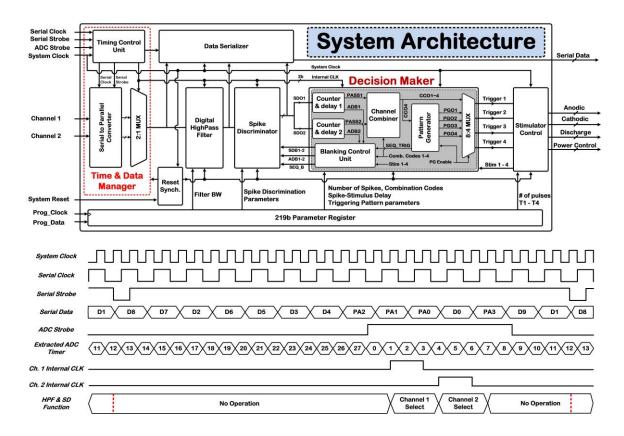

## 3.2 FPGA System Architecture

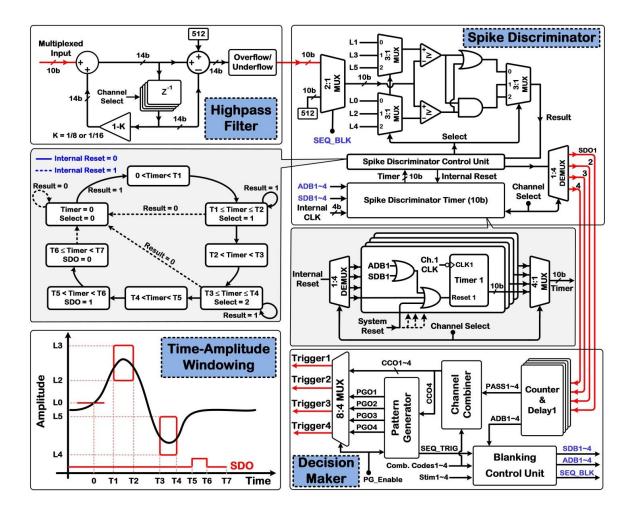

Fig. 3.2 depicts the system architecture and corresponding operation timing diagram for hardware realization of the stimulus trigger-generation strategy on an FPGA. The core building blocks of the system include a digital highpass filter (HPF), neural spike discriminator, and decision-making circuitry, whereas the auxiliary blocks include timing & data manager unit, data serializer, reset synchronizer, and a 219b latched shift register.

**Figure 3.2:** System architecture and timing diagram for hardware realization of the strategy for stimulus trigger generation from intracortical neural spike activity.

The embedded data serializer sends out the raw and filtered neural data as well as the *SDO* signal on each channel serially using an internally generated clock signal (500kHz) for external monitoring. The latched shift register provides all the programming and control bits for the FPGA operation. The other building blocks are described below in further detail.

#### 3.2.1 Time and Data Manager

The timing & data manager unit interfaces with the spike-recording front-end circuitry to prepare the data on each channel for processing and to manage the timing of the FPGA operation. Specifically, the timing control unit of this block, which receives a 1MHz system clock along with serial clock and strobe signals from the recording front-end, extracts the timing information of the incoming serial data on each recording channel and manages the operation of a serial-to-parallel converter and a 2:1 multiplexer in order to convert the incoming serial data per channel into 10b parallel data for further processing by the FPGA.

To manage the timing of the FPGA operation, the timing control unit also generates two internal clock signals (for Ch. 1 and Ch. 2) that are utilized by the 2:1 multiplexer, digital HPF, spike discriminator, and decision maker. The latter also uses the 1MHz system clock for operation flexibility.

The operation timing diagram in Fig. 3.2 is illustrated based on the premise that each conversion cycle of the analog-to-digital converter (ADC) in the spike-recording front-end takes 28 cycles of the 1MHz system clock. This design strategy helps reduce

the power consumption per channel in the recording front-end, while still providing a sampling frequency of ~35.7kSa/s/ch.

As seen in Fig. 3.2, each of the two internal clock signals lasts for two cycles of the 1MHz system clock, with one additional clock cycle as delay between the two channels. Hence, the processing of each data channel takes only three system clock cycles, enabling the same architecture to simultaneously handle up to nine recording channels in any future expansion of the system functionality.

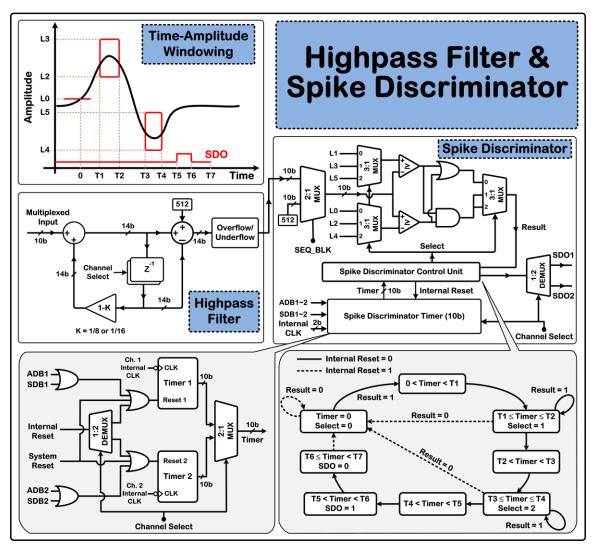

#### 3.2.2 Digital High-Pass Filter

A 1<sup>st</sup>-order, infinite impulse response (IIR), digital HPF removes any residual dc offsets or low-frequency noise/artifacts from the multiplexed/digitized input neural data prior to online spike discrimination. As shown in Fig. 3.3, the HPF has direct form II architecture and a transfer function that can be expressed as:

$$H(z) = \frac{1 - z^{-1}}{1 - (1 - K)z^{-1}},$$

(3.1)

where factor K is the user-set HPF coefficient that controls the filter bandwidth (BW). Specifically, factor K can be either 1/16 or 1/8, which results in a filter BW of 366Hz or 756Hz, respectively, from a 1MHz system clock. Moreover, the filter coefficients are judiciously selected to perform the filtering using arithmetic shifts, subtraction and addition only, obviating any need for digital multipliers or dividers.

**Figure 3.3:** Detail presentation of high pass filter and spike discriminator blocks. Conceptual illustration of the time-amplitude window discriminator is shown on top left. Negative threshold level  $L_1$  (not shown in bottom left) is used in the algorithm to discriminate waveforms with reverse polarity (i.e., negative-going initial portion), if necessary. The finite state machine (FSM) for spike discrimination algorithm is shown with illustration of timers and resets selection process, and the role of blanking related signals.

#### 3.2.3. Neural Spike Discriminator

As shown in Fig. 3.3, the system employs thresholding and two user-adjustable time-amplitude windows for real-time neural spike discrimination from noise and other artifactual signals. Once the signal waveform crosses a user-defined threshold level,  $L_0$ ,

the spike discriminator is activated to check whether the signal waveform subsequently passes through both time-amplitude windows (solid red boxes). If a spike event is accepted on any channel, the corresponding *SDO* signal is activated for the decisionmaking circuitry to generate the stimulus trigger signals, as described in further detail below. A negative threshold level,  $L_1$  (not shown), is also used to discriminate waveforms with reverse polarity (i.e., negative-going initial portion). The timing parameters  $T_{1\sim4}$  and  $T_{5\sim7}$  can be user-set up to ~ 7.2ms and 28.6ms, respectively, in steps of 28µs.

Fig. 3.3 also depicts the finite-state machine (FSM) diagram of the control unit of the neural spike discriminator along with the architecture of its timer block. When each internal clock signal is active, the 10b timer information of the corresponding recording channel is selected and sent to the spike discriminator control unit. The timer information of each channel can be individually reset either internally or externally via the system reset signal, or via the blanking-related signals, *ADB* and *SDB*, as explained in further detail in dedicated Blanking Section.

#### **3.2.4. Decision Maker Circuitry**

The decision maker uses the *SDO* signals as input and, based upon various useradjustable settings, generates the four trigger signals for either the individual or sequential stimulus-triggering scenario. Specifically, the counter & delay unit of this block counts a programmable number of discriminated neural spikes ( $N \le 15$ ) within a user-adjustable time bin duration,  $T_{Bin} \le -0.5$  second in steps of 56µs, and generates the *PASS* signal for each channel with a programmable delay,  $T_D \le -28.6$ ms in steps of 28µs, following the discrimination of the last spike. The trigger signals are then generated based upon the desired stimulus-triggering scenario, as selected by an 8:4 multiplexer at the output of the decision maker (see Fig. 3.2.)

In the individual triggering scenario, a channel combiner block, which is implemented as a programmable gate array, generates each trigger signal, *TriggerX*, independently as a logic combination of the two *PASS* signals using a 4b combination code that is unique for each stimulus channel. By de-activating the *PG\_Enable* signal, the 8:4 multiplexer uses the four channel combiner outputs, *CCO1~4*, as the four trigger signals in this case.

In the sequential triggering scenario, the four output trigger signals are obtained from a pattern generator block and can be nominally generated with a programmable, constant inter-channel stimulus delay,  $T_{D_stim} \leq \sim 1$  second in steps of 56µs, as previously shown in Fig. 3.1. The pattern generator also supports another sequential triggering scenario in which simultaneous triggering occurs on the first two stimulus channels (*Trigger1,2*) followed by simultaneous triggering on the next two channels (*Trigger3,4*) after a delay of  $3 \times T_{D_stim}$ . It should be noted that simultaneous, 4-channel triggering can also be supported by simply setting  $T_{D_stim}$  to zero.

By activating the  $PG\_Enable$  signal, the 8:4 multiplexer uses the four pattern generator outputs,  $PGO1\sim4$ , as the four trigger signals in this case. Also, to provide savings in the number of programming and control bits for the FPGA operation, the pattern generator utilizes the same 4b combination code used for the stimulating channel 4 in the individual triggering scenario to define the neural input-based criteria for sequential triggering.

## 3.2.5. Reset Synchronizer

In this design, based on the requirement of each block or sub-block, both synchronous and asynchronous reset signals have been used. Synchronous resets usually do not have meta-stability problems because they always occur at the active edge of the clock for each flip-flop. But this is not the case for asynchronous resets.

The main problem with asynchronous resets is that they are asynchronous both at the assertion and at the de-assertion of the reset. The assertion is a not problematic, but the de-assertion is. If the asynchronous reset is released at or near the active clock edge of a flip-flop, the output of the flip-flop could go metastable and thus the reset state of the ASIC could be lost. To avoid this meta-stability issue for asynchronous reset signals, reset synchronizer is used to make sure asynchronous reset signals are de-asserted on the opposite edge of active clock for each specific flip-flop.

#### 3.2.6. Stimulator Control

The stimulator control unit generates the requisite timing control signals for the stimulating back-end to control the anodic, cathodic, and passive discharge phases of the stimulus waveform. Asymmetric biphasic current pulse parameters such as duration of anodic phase, interphase delay, duration of cathodic phase, and duration of passive discharge as well as frequency and number of pulses within an ISMS train can be programmed for the BMSI via this block.

#### **3.3.** Blanking Schemes

As briefly mentioned in previous sections, our stimulus trigger-generation strategy also provides an ability to blank (i.e., disregard) the input neural data on some or even all of the recording channels for specific periods of time. There are two reasons behind the implementation of such blanking schemes. First, although the time-amplitude window discriminators (as opposed to simple spike thresholding) should be capable of discriminating neural spike waveforms from stimulus artifacts (by proper adjustment of parameters in the two windows), the blanking schemes further ensure that stimulus artifacts, if present in the BMBI system, will not lead to false-triggering.

Second, since neural spikes can occur asynchronously at any time during the BMBI system operation (e.g., during a period of stimulation), the blanking schemes provide a mechanism to prevent unwanted stimulus triggering during a period of stimulation, and to keep track of the trigger-generating spikes in any post hoc analysis of spike-stimulus pairs.

As seen in Fig. 3.2, the blanking schemes are implemented by a blanking control unit within the decision maker that provides additional inputs (ADB1~2, SDB1~2, SEQ\_BLK) to the neural spike discriminator. Different blanking schemes are devised for individual and sequential triggering scenarios and described in further detail below.

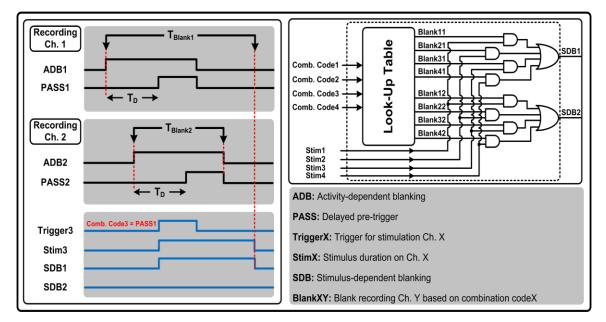

## 3.3.1. Blanking Scheme for Individual Triggering

In an individual triggering scenario, each trigger signal itself (i.e., TriggerX) is defined as a logic combination of the PASS signals using a 4b combination code. As a representative case, Fig. 3.4 illustrates various signals and their relative timings that are involved in blanking for individual triggering on stimulating channel 3, initiated when trigger-generation criteria are satisfied on the first input data channel only (i.e., Trigger3 is set to be PASS1 signal.) Once spike-discrimination criteria are satisfied on any recording channel, an activity-dependent blanking signal, ADB, is activated on that same channel that blanks its input data by resetting the timer information of the recording channel in the neural spike discriminator (see Fig. 3.3) Once the ADB signal is de-activated on the falling edge of the corresponding PASS signal, the recording channel is ready again to check the spike-discrimination criteria.

However, depending upon the user-set combination code to define TriggerX, only a subset of the recording channels might actually be involved in stimulus trigger generation in a given experiment (e.g., recording Ch. 1, but not Ch. 2, in Fig. 3.4). A second blanking signal, namely, stimulus-dependent blanking (SDB) is then employed to prolong the blanking duration only on those recording channels involved in trigger generation. Specifically, the blanking control unit incorporates a lookup table with the user-defined combination codes as its input in order to generate a series of static command signals, BlankXY, at the output. In conjunction with StimX signals, which indicate the duration of stimulation on channel X and are typically provided via the stimulator controller of the BMBI system, the two SDB signals are generated as shown in Fig. 3.4.

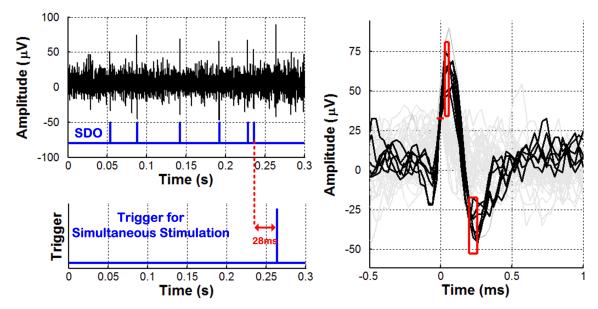

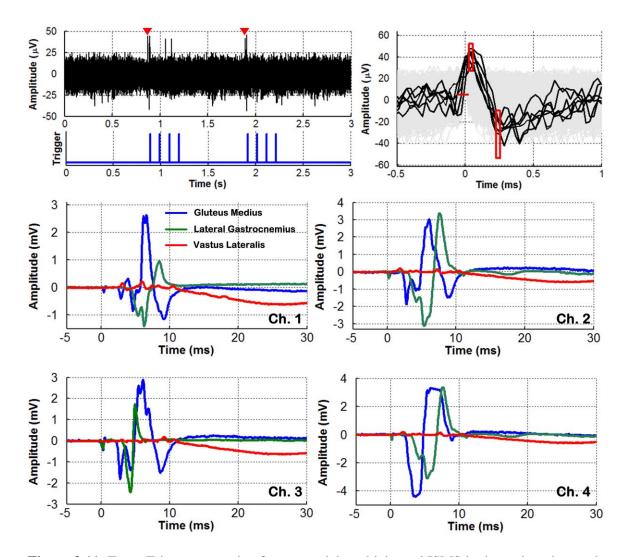

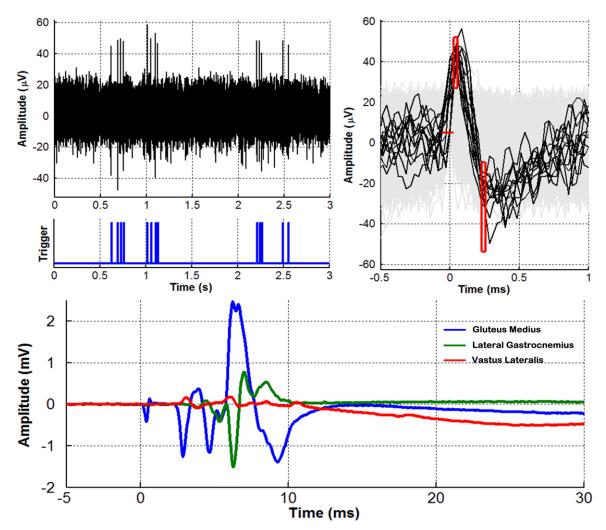

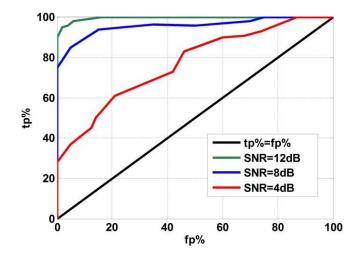

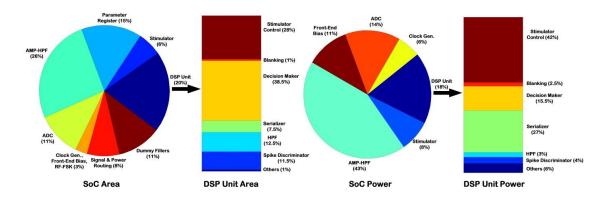

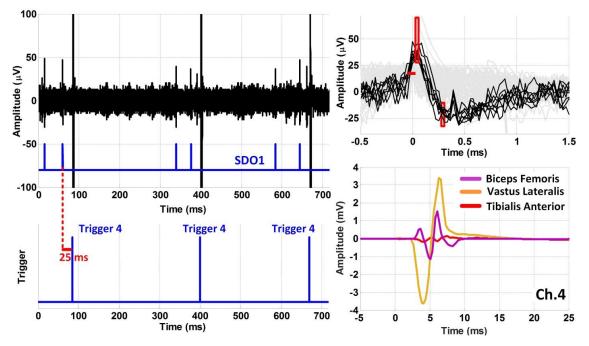

Specifically, in Fig. 3.4, Blank31 signal at the output of the lookup table, as well as Stim3 signal, will be active (all other BlankXY and StimX signals will be inactive), which will then activate the SDB1 signal only.