# Outline

- Motivation : Automotive ICs

- Smart Power Drivers Case Study : Squib Driver Unit

- Pin and Design FMEA

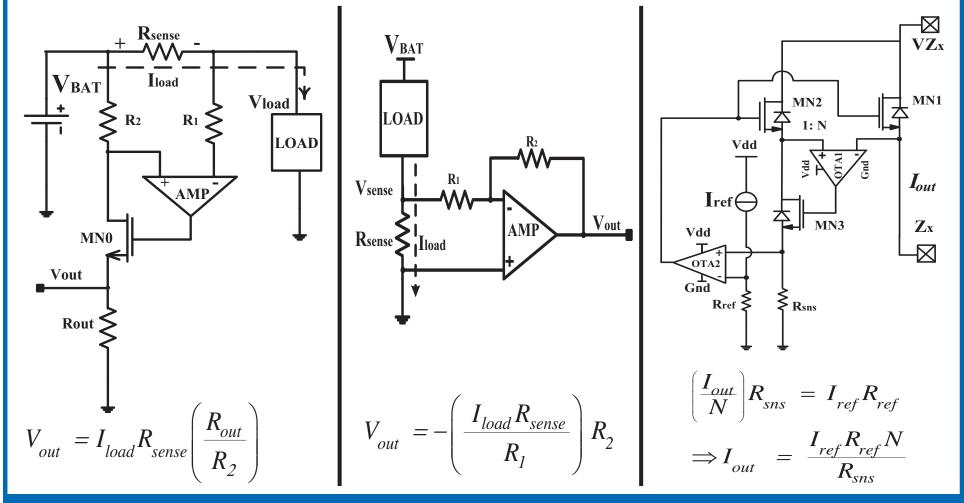

- High Side Current Sensing

- Low Side Current Sensing

- Biasing Schemes

- Diagnostics

- Additional Automotive Requirements

- Conclusion

## Motivation : Automotive ICs

- Motivation Automotive ICs

- Automotive SOCs Overview

- Automotive SBCs

- Power Semiconductors (LDMOS, DE-NMOS)

- Temperature, Reliability and Loads

- High Side and Low Side Configuration

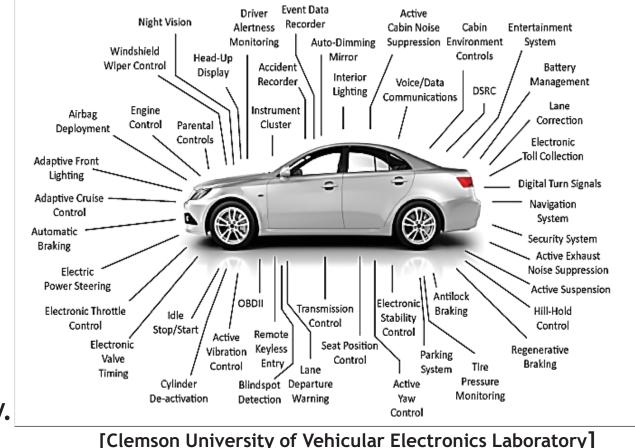

## **Motivation - Automotive ICs**

Electronic control in Automotive is increasing (less

hydraulics/mechanics). Power semiconductors are the key.

BenefitsLonger life

expectancy for vehicles.

Connected cars, higher road safety.

# **Automotive SOCs-Overview**

Electronic content in

Automotive => Integrated

circuits.

Trend

Larger integration.

Low Cost

Lesser Bill of Materials,

Smaller PCB size.

Large Scale integration -

**Challenges**

- Power dissipation, package, On chip Cross talk/Noise between modules.

- Longer time for release to market

(Longer validation time).

Larger die -> higher defect density

(0 dppm target is challenged !)

2019 Custom Integrated Circuits Conference - Education Sessions

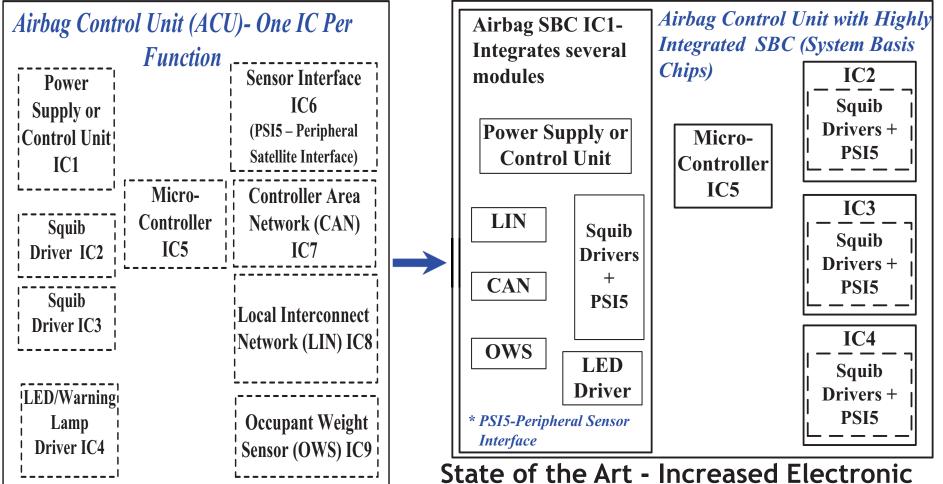

# Automotive System Basis Chips (SBC)- Airbag Control Unit (ACU) Example

Prior Electronic Content Individual ICs for each function State of the Art - Increased Electronic Content. More squib channels, sensors, increased functionality, smaller PCB.

# **Key Components**

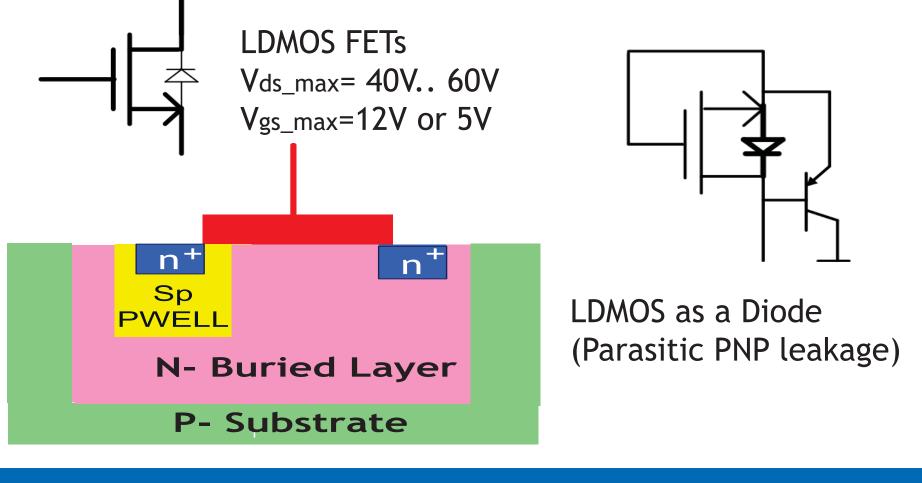

- Power ICs -> powerFETs and their drivers are the key.

- These high voltage components dissipate high power.

( Higher Vds\*Id ).

- LDMOS (Laterally Diffused Metal Oxide Semiconductors) is heavily used. Low Rds\_on, ~ 500m  $\Omega$  or lower @ smaller area.

- -2V to 40V requirements. Some applications need -18V.

#### **Technology**

Bipolar, CMOS and LDMOS (BCD) + Resistors, Capacitors.

LDMOS when replaced by Drain Extended NMOS => BiCMOS.

# **LDMOS Transistors and Body Diodes**

- Laterally Diffused MOS (LDMOS) is mainly used for powerFETs.

- In built body diode is effectively used in designs.

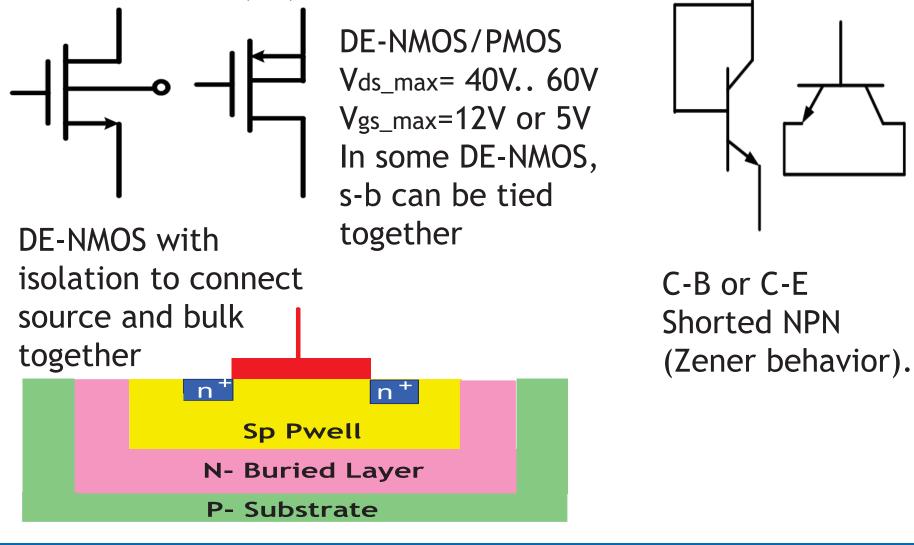

# High Voltage (HV) Components

Drain Extended (DE) NMOS and PMOS

2019 Custom Integrated Circuits Conference - Education Sessions Sli

# Temperature, Reliability and Loads

- High Power Dissipation, High Junction Temperature

- Junction temperature rise within powerFETs ~  $400^{\circ}$ C.

- No Vgs, Vds,Vsb rating violation. Operate within electrical Safe Operating Area (SOA).

- Multiple Supply Voltage (MSV), Power Supply faults

- No Inadvertent activation or de-activation of powerFETs, power stages.

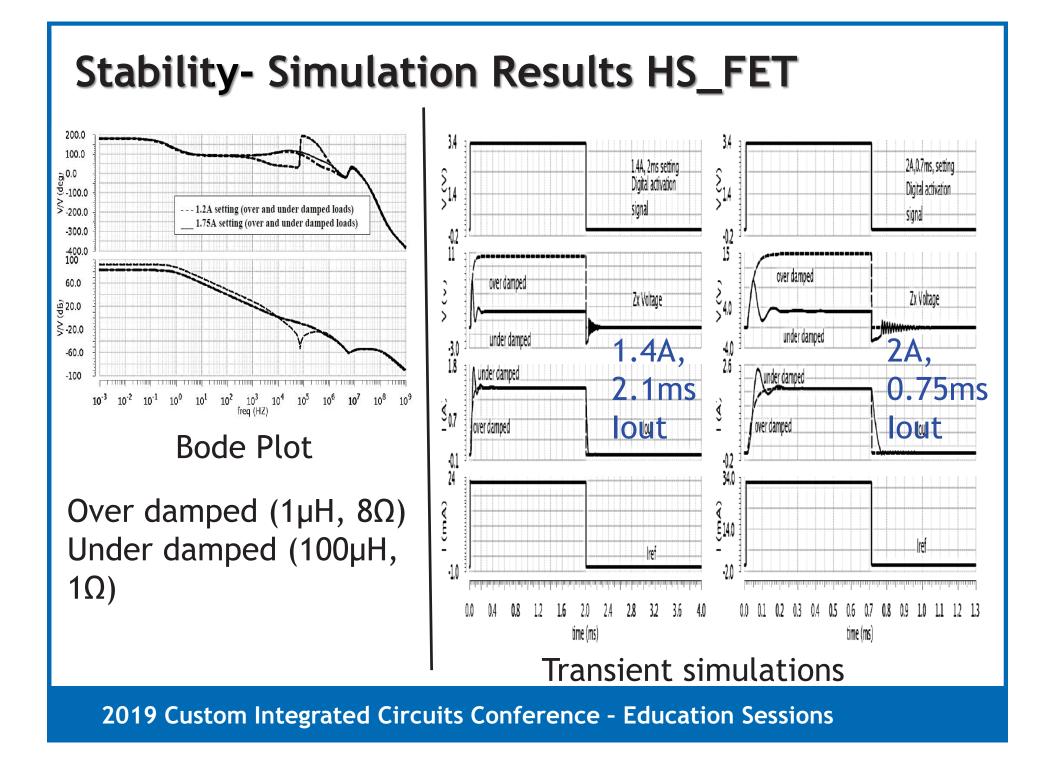

- Load : Inductance range (1µH to 3mH). Stability is critical.

- Diagnostic circuits : No false flags.

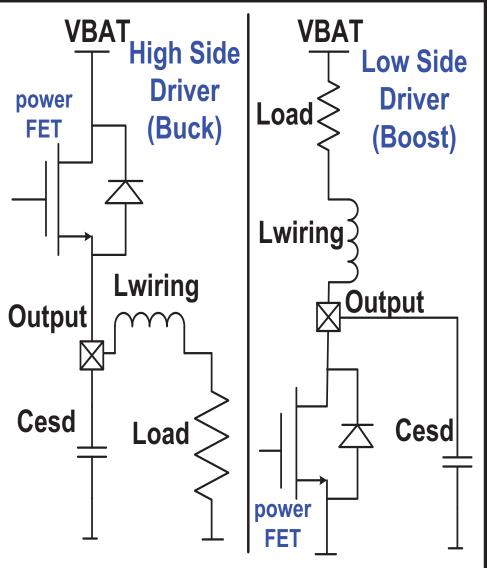

# High Side, Low Side Configuration

Automotive ICs need to Handle inductive loads without external freewheeling path. Withstand single fault ("Output" Short to battery (SCB) or ground (SCG)) multiple times. (0 Ohm Load).

2019 Custom Integrated Circuits Conference - Education Sessions S

# Smart Power Drivers Case Study - Squib Driver Unit (SDU)

- Introduction to ACU, SDU, PCU Terminologies

- SDU Requirements (Powered/Unpowered)

- SDU Specification

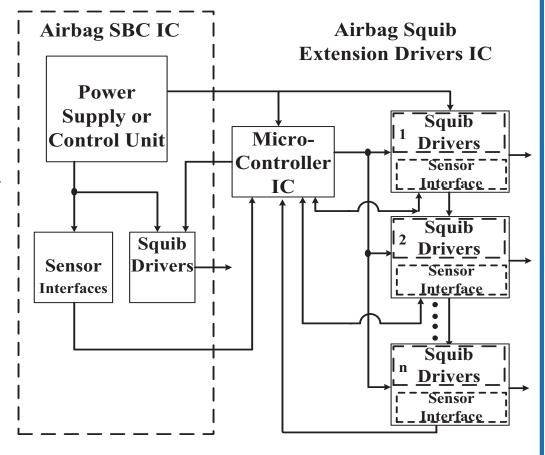

# Airbag Control Unit (ACU)

Airbag Control Unit (ACU) contains System Basis Chips (SBC), Squib Driver Extension ICs and Micro-Controller.

#### Airbag SBC

Power Control Unit (PCU), Squib Driver Unit (SDU) and Sensor Interfaces like PSI5.

#### Squib Driver Extension ICs

Extension ICs have Squib Drivers and PSI5.

2019 Custom Integrated Circuits Conference - Education Sessions

# Squib Driver Unit (SDU)

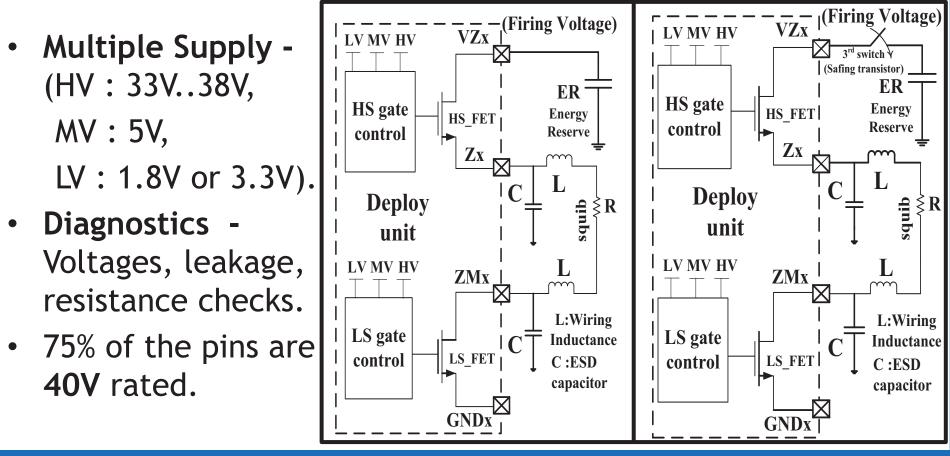

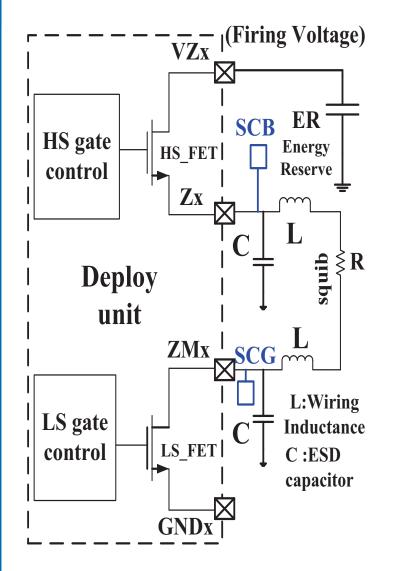

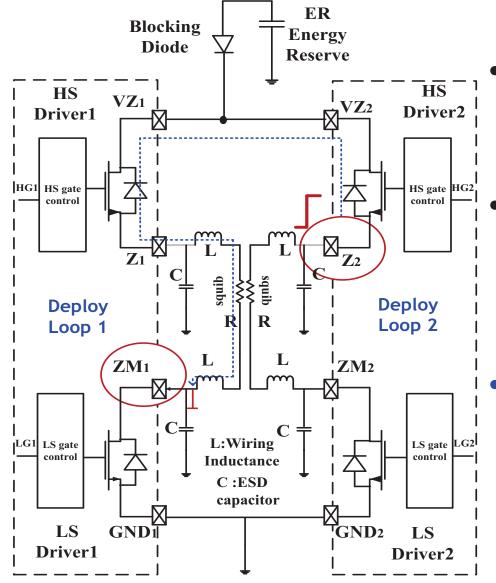

- SDUs provide current to ignite squibs for deploying airbags.

<u>Deployment loop : High Side (HS) FET + Low Side (LS)FET.</u>

- HS\_FET regulates the current. LS\_FET in Rds\_on mode.

2019 Custom Integrated Circuits Conference - Education Sessions

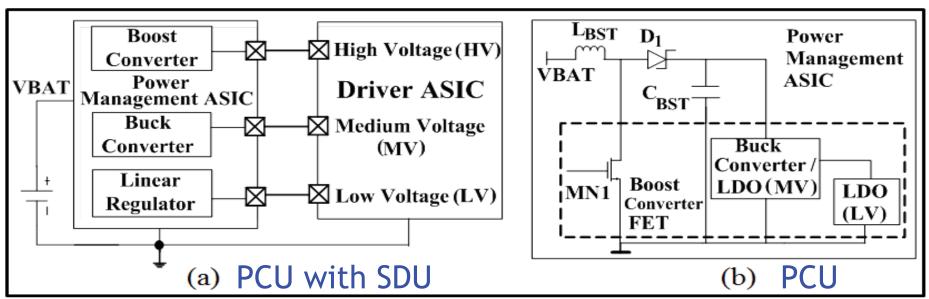

# Power Control Unit (PCU)

- Boost Converter\_HV (33V to 38V): Gate Driver Supply and Diagnostics.

- Buck Converter(5V to 6V)\_MV : Bandgap, Bias current generator, level shifters.

- Linear Regulator (3.3V)\_LV : Digital core supply and IO Buffers.

- Deployment voltage VZx can be either HV rail or regulated down to 25V.

# Squib Driver Requirement

#### **Powered State**

1 <sup>–</sup> A 1

1.33A

HV, MV, LV, VZx rails are available. HS, LS Drivers activated => Time limited regulated current (Energy<9mJ or 7mJ) from HS\_FET ignites the squib to deploy the airbag.

$$I^{2}RT = (1.47A)^{2}.(2\Omega).2ms = 8.64mJ$$

$I^{2}RT = (2.14A)^{2}.(2\Omega).0.7ms = 6.4mJ$

Firing Pulse ~ 2ms

1.47A

1.2A

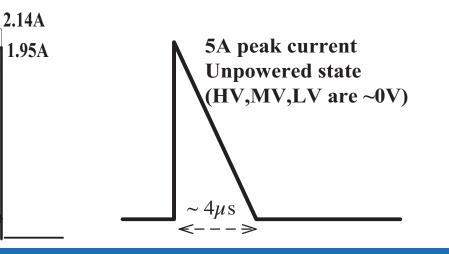

#### **Unpowered State**

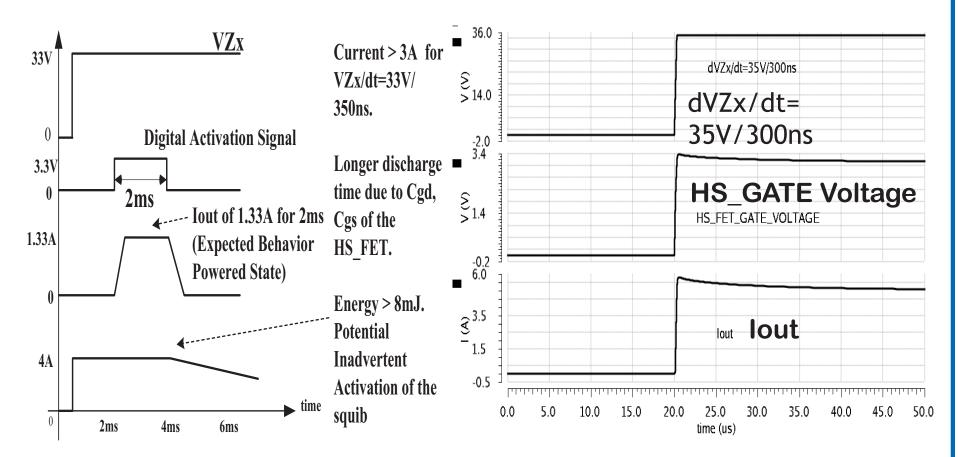

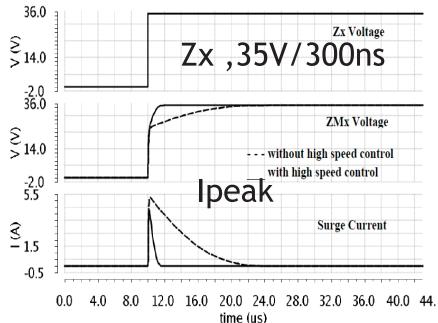

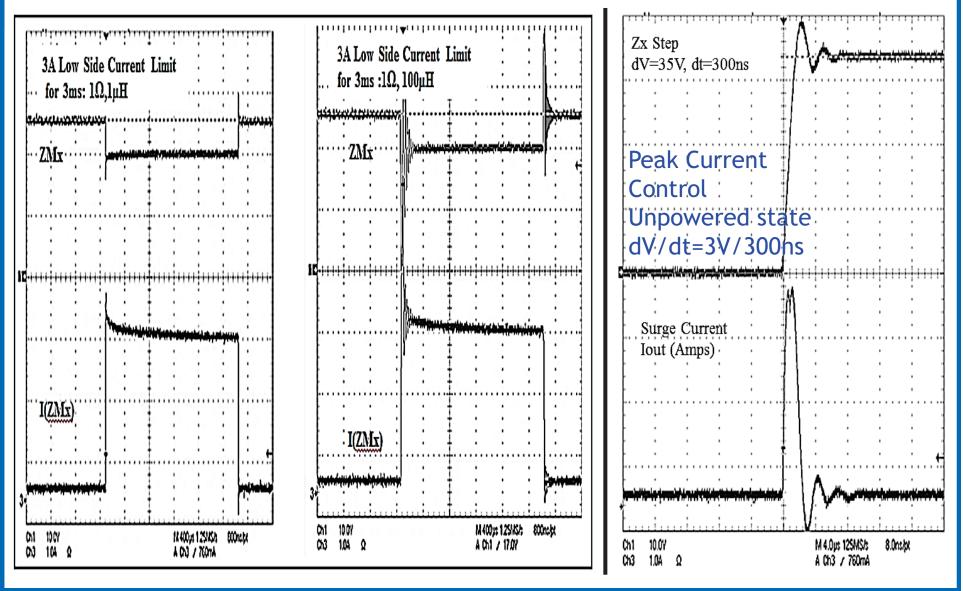

- When One of the rails is not available or Fast SCG or SCB during the unpowered state of SOC, high current or Energy ~6mJ is not allowed.

- Current should be limited to 5A for  $4\mu s$ . (No fire spec)

2019 Custom Integrated Circuits Conference - Education Sessions Slide 15

1.75A

Firing Pulse  $\sim 0.5/$

0.7ms

# **SDU Specification**

| Spec Parameter        | Target        | Comments                           |

|-----------------------|---------------|------------------------------------|

| HS_FET Current        | 2A +/-10% and | Airbag deployment currents.        |

| Regulation            | 1.35A +/-10%  | Inductance range 1µH to 3mH.       |

| LS_FET Current        | 3A +/- 15%    | Protection for LS in case of SCB.  |

| Regulation            |               | Inductance range 1µH to 3mH.       |

| HS/LS FETs Surge      | 5A,4µs        | To prevent inadvertent deployment  |

| Current Limitation    |               |                                    |

| Quiescent Current of  | 5mA           | No diagnostics current sources are |

| the Driver            |               | enabled                            |

| Diagnostic Reference  | 8.4V          | 100pF to 220nF cap range, Current  |

|                       |               | Limited Voltage Source (CLVS)      |

| Diagnostic Output Max | 5.4V          | Input can range 100mV to 30V       |

| Deployment Voltage    | 25V to 35V    | 35V (Energy Reserve Capacitor).    |

| Leakage Current on    | < 1µA         | Range 0 to 35V                     |

| Drain of HS/LS_FET    |               |                                    |

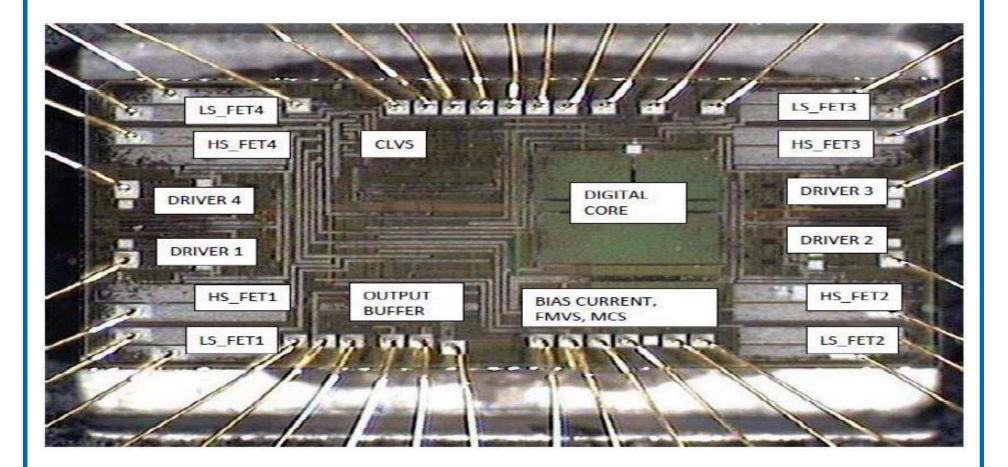

### **TI Quad Channel Squib Driver**

40V, TI BiCMOS Process. 0.35µm, quad channel airbag squib driver.

# Failure Mode Effect Analysis (FMEA) Pin FMEA (PFMEA) and Design FMEA (DFMEA)

- Introducing PFMEA and DFMEA

- Introduction to Current Sensing

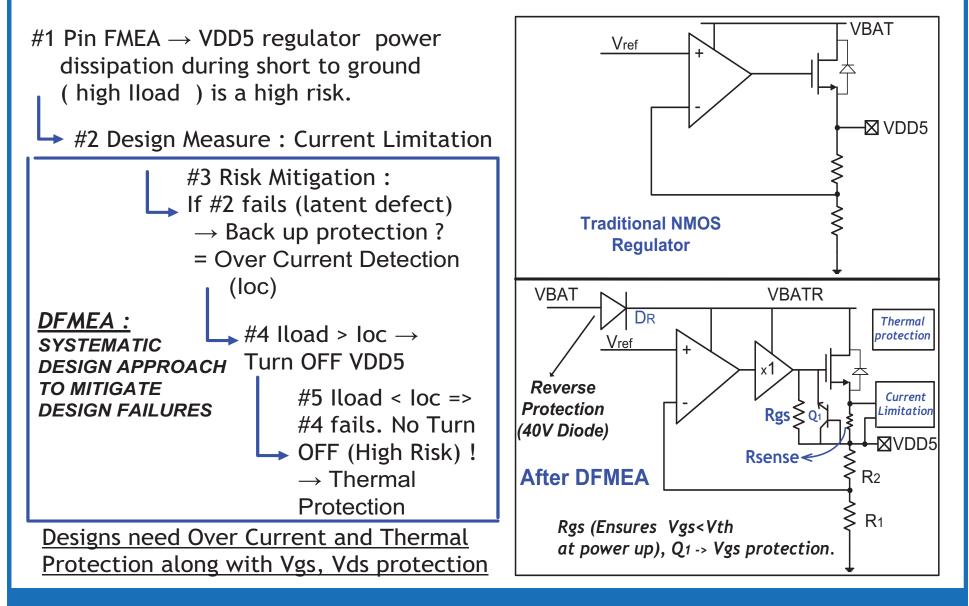

# Pin FMEA Example

- FMEA, Automotive IC designs go hand in hand.

- SOC pin fault Analysis @ PCB/system level is the <u>key</u> for design specifications.

- Occurrence and detection of faults are important.

Occurrence = 7 (chances of shorts during PCB manufacturing level is high)

Detection =1 (chances of detection of shorts are very high).

### Pin FMEA Example- VDD5 Regulator

| Pin<br>Num<br>ber | Pin<br>Name   | Potential<br>Fault Mode              | Potential Effect of Failure                                                       | Fault Cause                                                 | Occurrence | Detection |

|-------------------|---------------|--------------------------------------|-----------------------------------------------------------------------------------|-------------------------------------------------------------|------------|-----------|

|                   |               |                                      | SOC Level                                                                         | (During Design &<br>Manufacturing Levels)                   |            |           |

| 1                 | VDD5          | Pin Open                             | Output of the regulator IC is open.                                               | Open Bondwire                                               | 7          | 1         |

|                   |               | Short to GND                         | Too high current flowing through the output stage. High power dissipation.        | Bondwire/Wire short to<br>Ground line                       | 7          | 1         |

|                   | Short to VDat |                                      | Too high reverse current flowing through the output stage. High power dissipation | Bondwire/Wire short to<br>a high voltage <mark>l</mark> ine | 7          | 1         |

|                   |               | Short to GND<br>(Neighboring<br>pin) | Too high current flowing through the output stage. High power dissipation.        | Bondwire/Wire short to neigbouring line                     | 7          | 1         |

Current Sensing, limitation/regulation is the key to address faults.

2019 Custom Integrated Circuits Conference - Education Sessions

### Pin FMEA to Design FMEA- Design Approach

2019 Custom Integrated Circuits Conference - Education Sessions

# **Current Sensing Techniques**

| Topology      | Method                        | Description                                                                              | Advantages                                                                                                       | Disadvantages                                                                             |

|---------------|-------------------------------|------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------|

|               | Sense Resistor<br>Source Side | Poly resistor in series with the switch                                                  | Accurate. Regulation loop<br>stability is easier as the<br>architecture is similar to a<br>source follower type. | Sensitive to Substrate<br>Currents. Limited to<br>less than 300mA.                        |

|               | Sense Resistor<br>Drain Side  | Poly resistor in series<br>with the switch                                               | Accurate and insensitive to substrate currents                                                                   | Stabilizing the loop is<br>not straight forward as<br>the power stage is a<br>gain stage. |

|               | Power switch Ron              | $R_{ds_{on}}$ of the switch                                                              | Higher current limits can be<br>achieved                                                                         | Inaccurate                                                                                |

| MN0 MN0_Sense | Sense-FET                     | Scaled version of<br>powerFET for current<br>sensing (drain or<br>source tied together ) | Higher current limits can be<br>achieved                                                                         | Threshold voltage<br>Mismatch between<br>powerFET and senseFET                            |

2019 Custom Integrated Circuits Conference - Education Sessions

# **Current Sensing Fundamentals**

Sense the current (shunt resistor based or senseFET based). Limit the VBE or VGS of the Transistor to limit the current.

2019 Custom Integrated Circuits Conference - Education Sessions

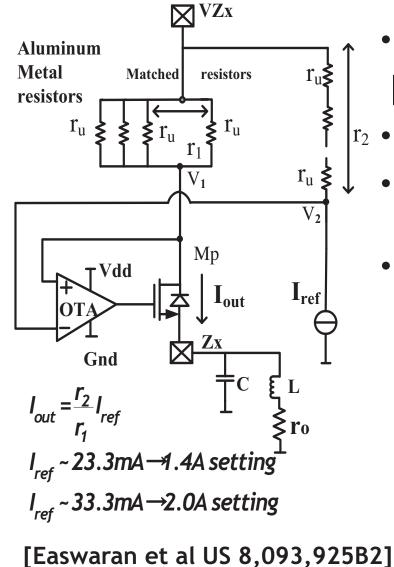

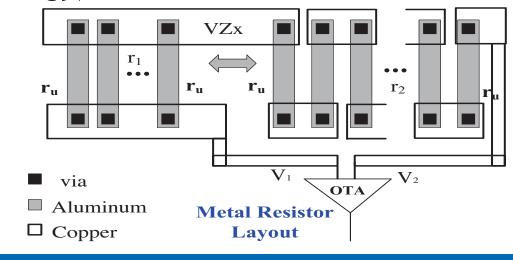

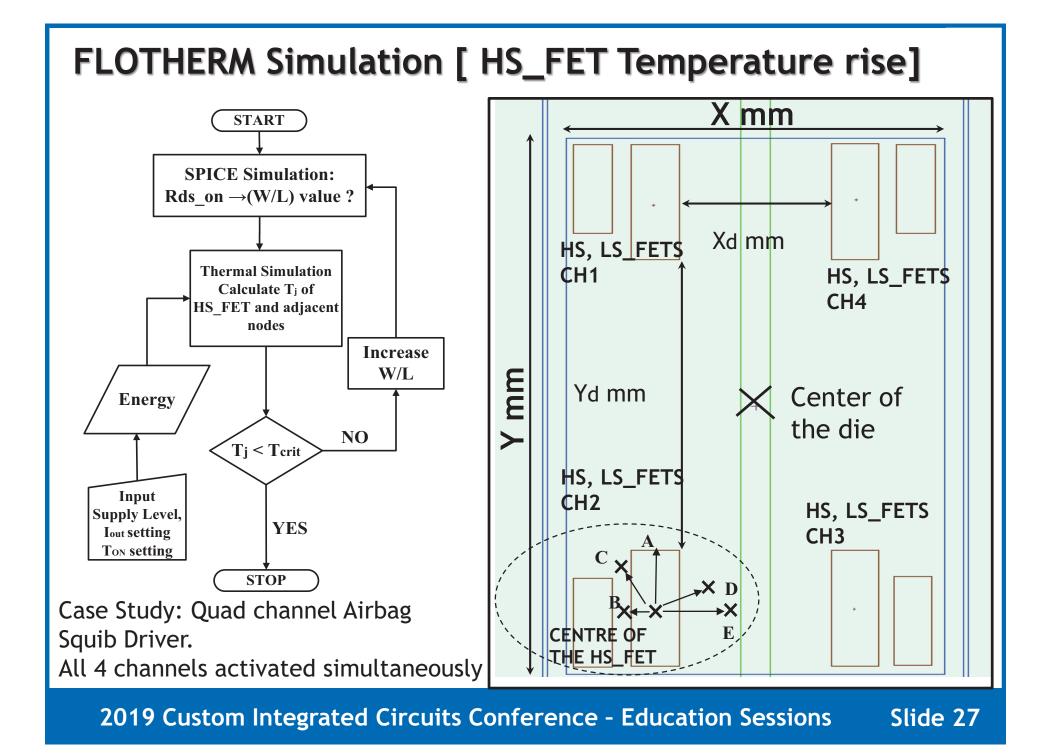

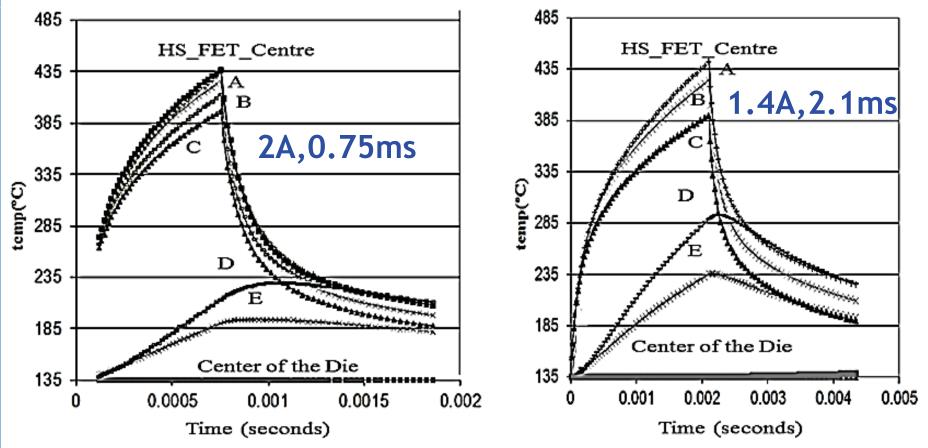

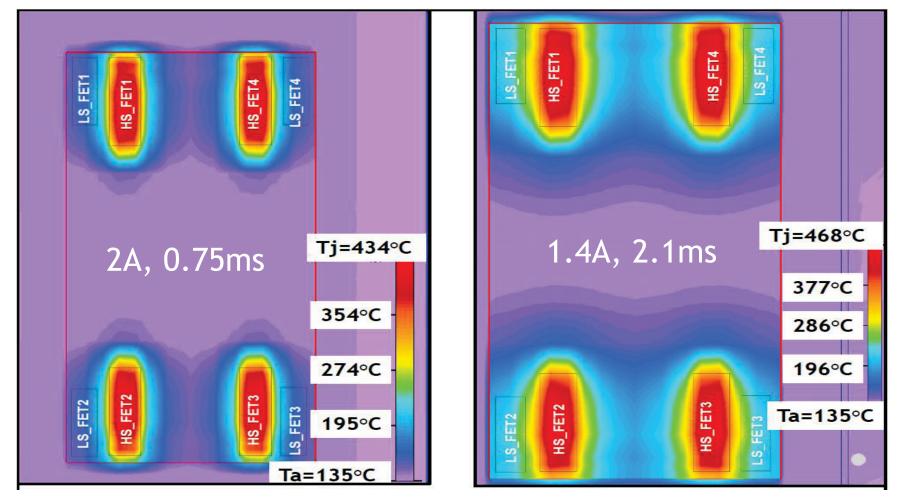

### High Side (HS) Current Sensing - Metal Resistor

- HS Current Regulation Concept

- FLOTHERM Simulations

- Isothermal Plots

- HS Layout Strategy

- Free-Wheeling Path

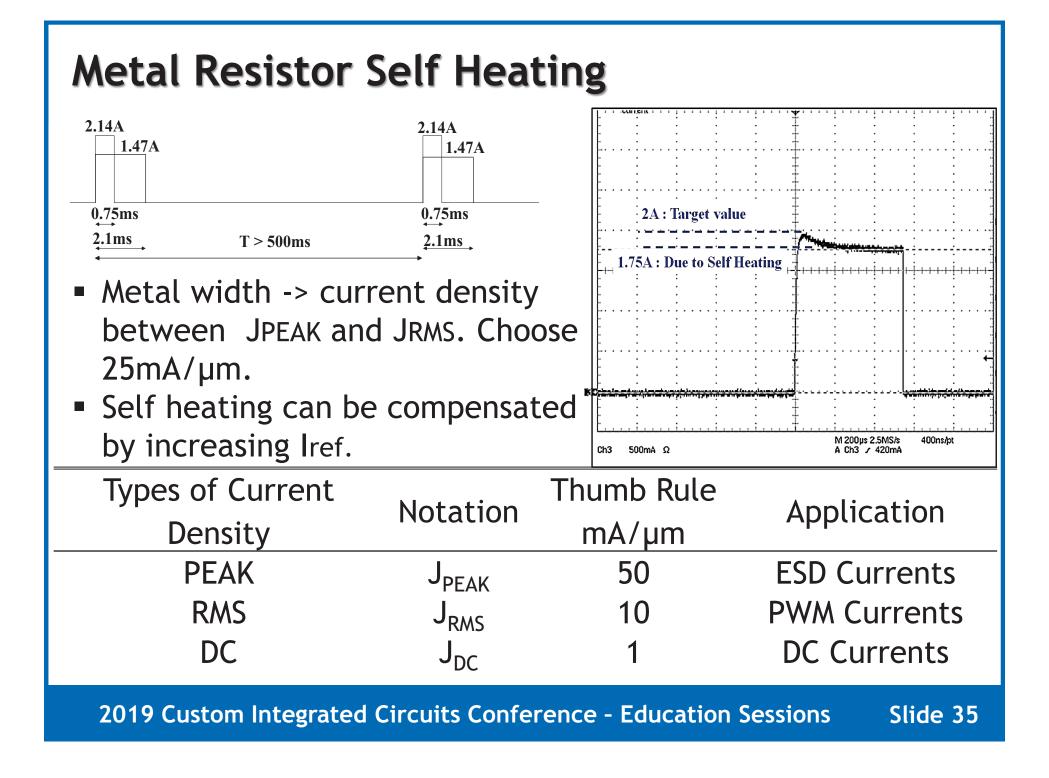

- Self Heating

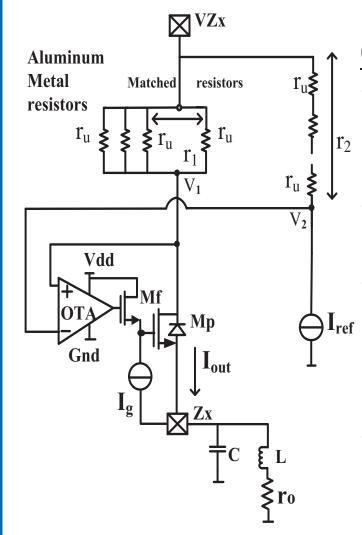

# **HS Current Regulation Loop Concept**

- Power Dissipation across Mp

- $[VZx- (lout.r_0)]^*$  lout. (VZx=38V)

- $r_2 \cdot r_0 = R_squib + Rds_on_LS \sim 1.8\Omega... 2\Omega.$

- 2A Case : ~64W to 68W for 0.75ms (48mJ energy)

- 1.4A case: ~49W for 2.1ms (98mJ energy).

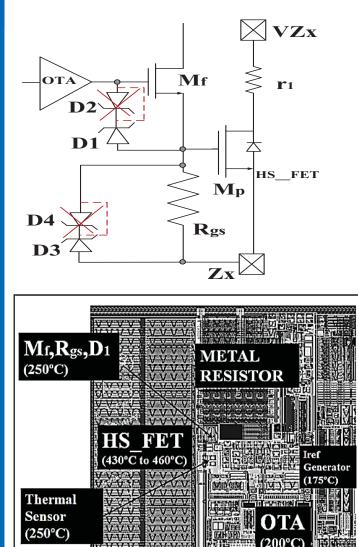

## Temperature rise around HS\_FET Gate Driver

Ambient Temperature = Ta = 135°C.

Deployment event : Junction temperature rise (Tj) monitored at the center and gate driver locations of the HS\_FET.

### **Isothermal Plots**

- Tj (Junction temperature of the HS\_FET reaches ~ <u>460°C</u>.

- No SPICE model for temperatures > 200°C

# HS\_FET Current Regulation, Layout Strategy

Layout Strategy Centre of HS\_FET is 460°C.

- OTA, Iref generator to be placed where Tj<200°C. (Simulatable !)

- Mf and Ig is a source follower.

- Size Mf such that it can drive 2lg => Place Mf and current source lg in the area where Tj is ~200°C to 300°C.

- Works even if we can simulate the whole circuit only till 200°C.

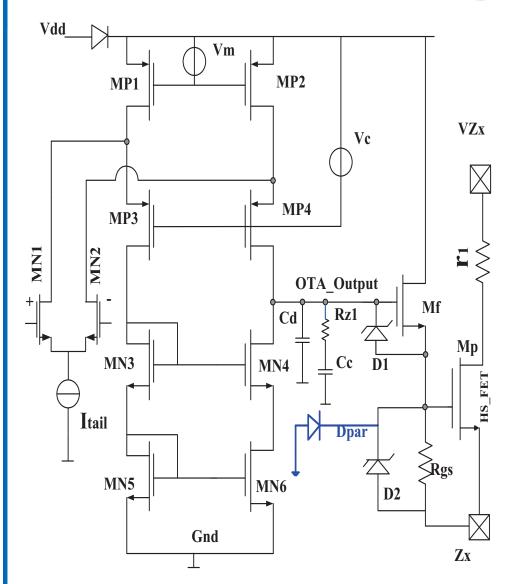

# **HS\_FET Current Regulation and DFMEA**

- Mf drives Rgs instead of Ig. Rgs ensures Vgs <Vth for Mp at power up. Mp not turned ON inadvertently.

- <u>Source follower with resistive load</u> <u>better than current source load.</u>

- Mf and Mp need Vgs protection. At 300°C, any forward leakage of D2 will reduce OTA's output impedance.

- ⇒ Avoid forward diodes D2 and D4 to mitigate risk based on DFMEA.

⇒ Off state leakage @ 5V is traded off. "µA" leakage still better than "nA".

### **Internal Free Wheeling Path**

- When the HS Driver turns OFF, <u>the free wheeling</u> <u>current will still flow</u> <u>through the HS\_FET</u>.

- This is feasible since the gate of the HS\_FET is clamped to -0.7V due to Dpar (N-diffusion connected at the gate)

- Eliminates external Schottky diodes.

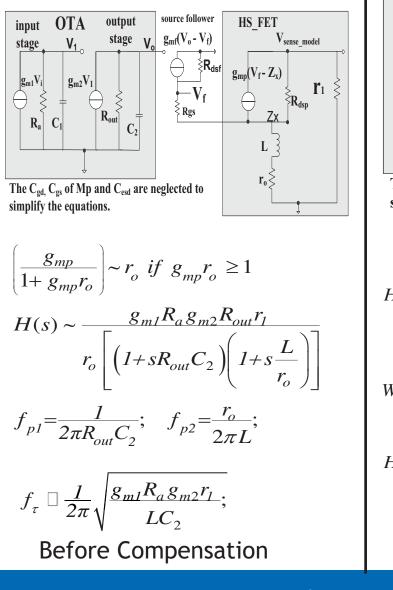

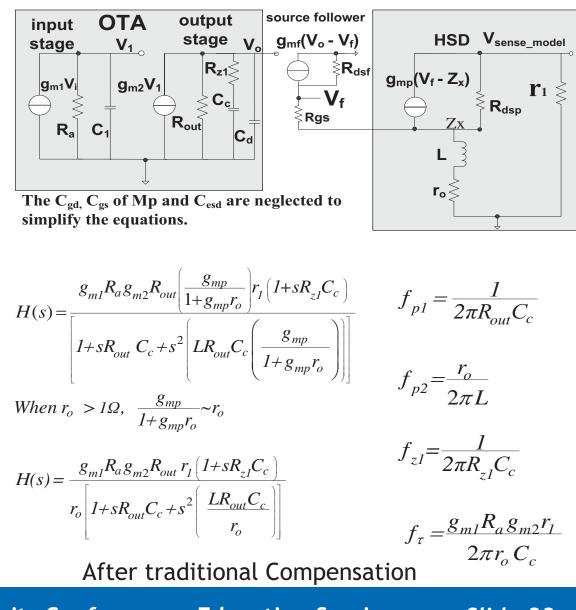

### Small Signal Analysis, HS\_FET with OTA

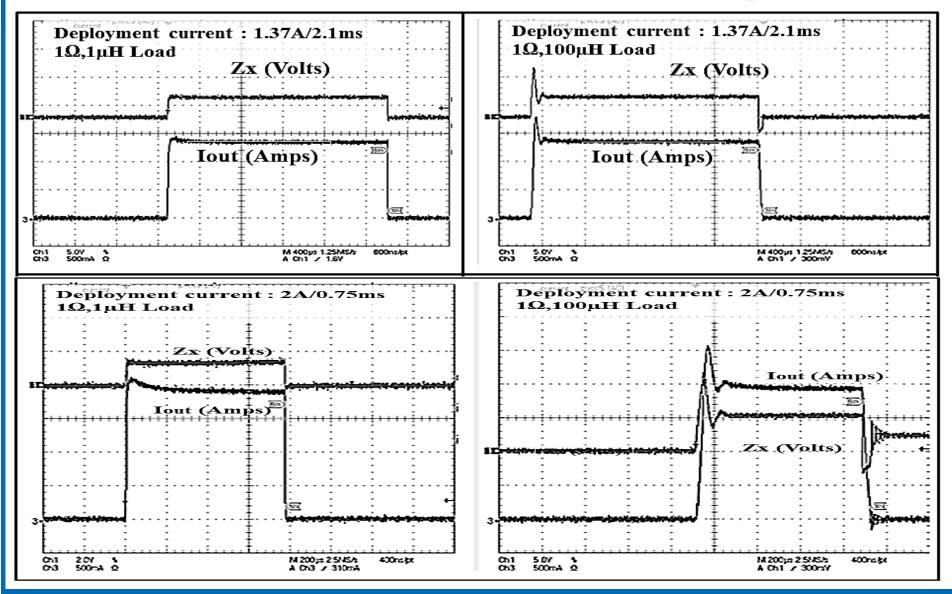

### Measurements : HS\_FET Current Regulation

2019 Custom Integrated Circuits Conference - Education Sessions

### Short to Ground, Battery Conditions

- Short to Ground (SCG), Short to Battery (SCB)

- CrossLink

- Energy Level Unpowered State

- Active Discharge Circuit

- Dynamic SCG and circuit improvements

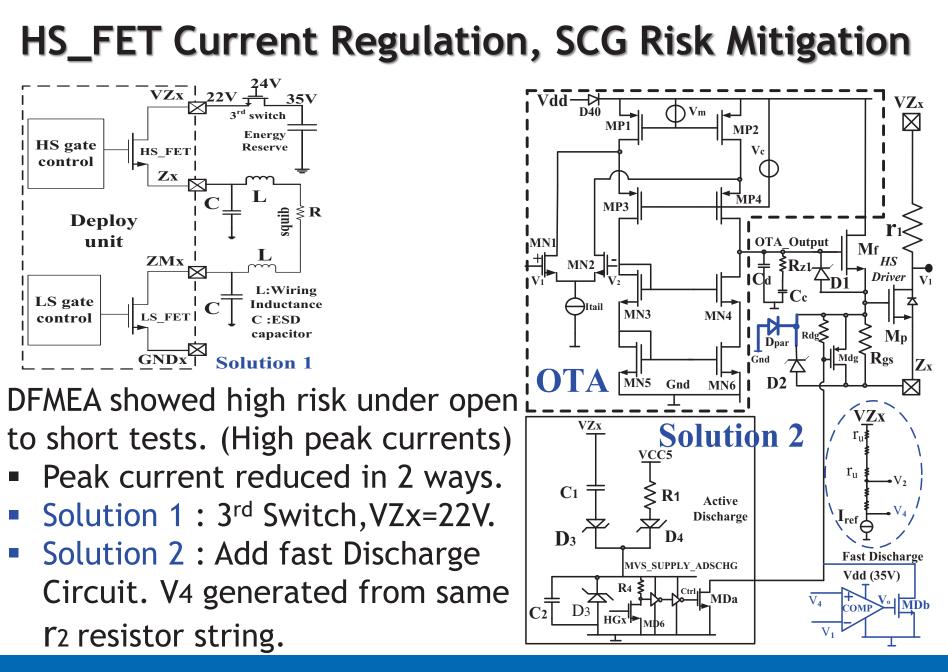

# HS\_FET Current Regulation, SCG, SCB Faults

- Probability of single faults (Short Circuit to Ground (SCG) or Battery (SCB)) is very high. Circuits have to be designed to tolerate this.

- Simultaneous faults on same channel (SCB and SCG) has low probability.

- SCG on the output of Driver 1 and SCB on the other Driver is highly probable.

# Cross Link (SCB, SCG on individual channels)

Z2 -> SCB & ZM1 -> SCG is a <u>High</u> <u>probability event.</u> Dynamic SCB on Z2

with ZM1 at ground is critical for the Deploy loop 1.

Energy level > 8mJ on Squib\_CH1 due to spike on Z2 (VZ1,VZ2) is not allowed.

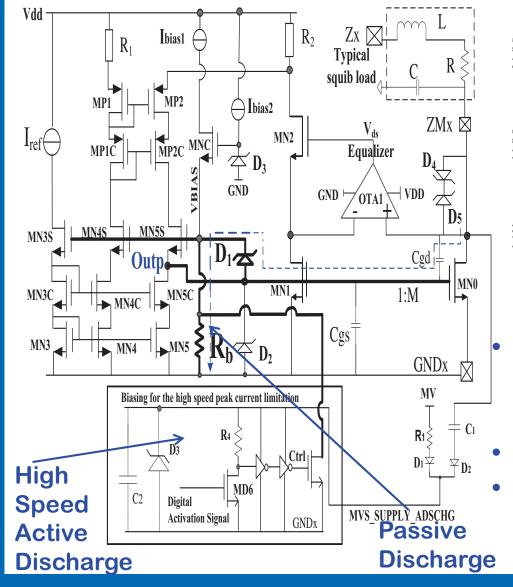

### Energy Level Violation - Unpowered state SCB

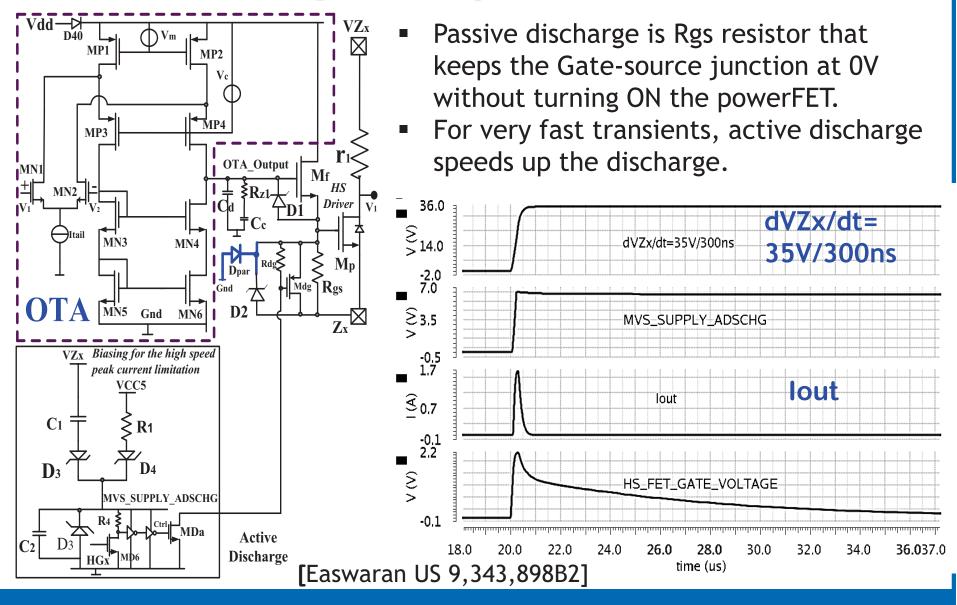

<u>Passive discharge</u>:  $R_{gs}$  resistor ensures gate is discharged (Vgs~0V). Fast transients need active discharge to quickly discharge the gate to meet 5A,4µs spec.

#### **Active Discharge in Unpowered State**

2019 Custom Integrated Circuits Conference - Education Sessions

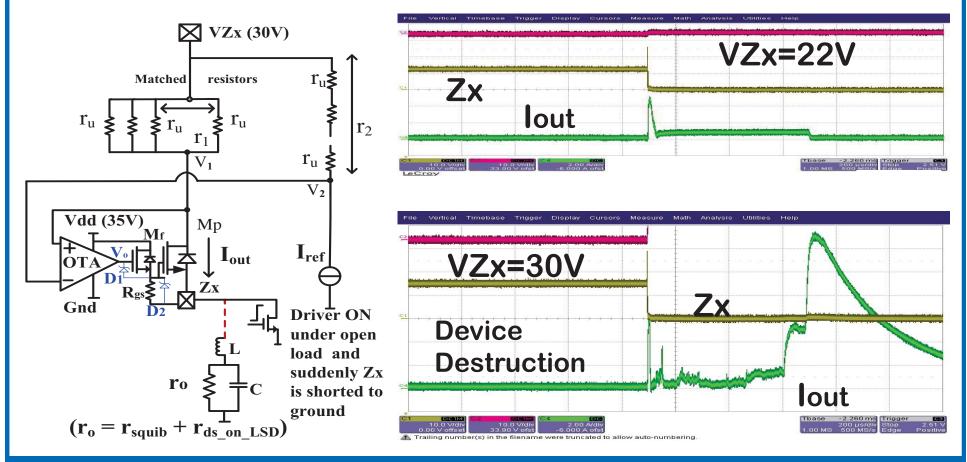

# HS\_FET Current Regulation, SCG Scenario

A dynamic SCG during deployment -> Open to Short test. VZx=22V, 6A,peak current. @ 30V VZx > 10A peak current is too high ? How to mitigate risk ?

2019 Custom Integrated Circuits Conference - Education Sessions

2019 Custom Integrated Circuits Conference - Education Sessions Slid

# Low Side (LS) Driver and Current Sensing

- LS Current Regulation

- Passive and Active Discharge

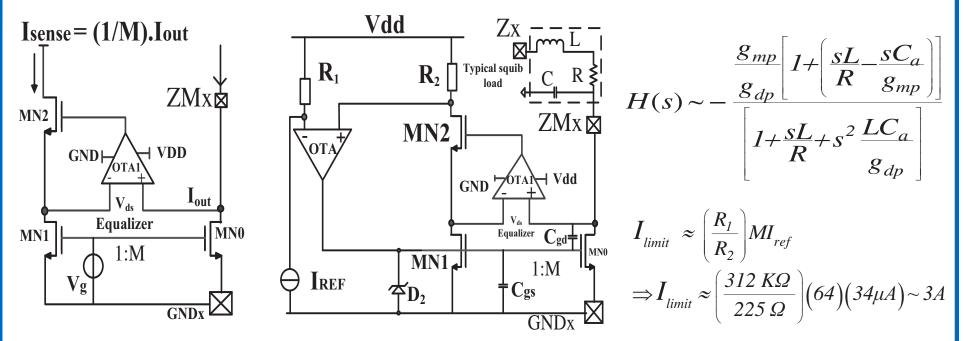

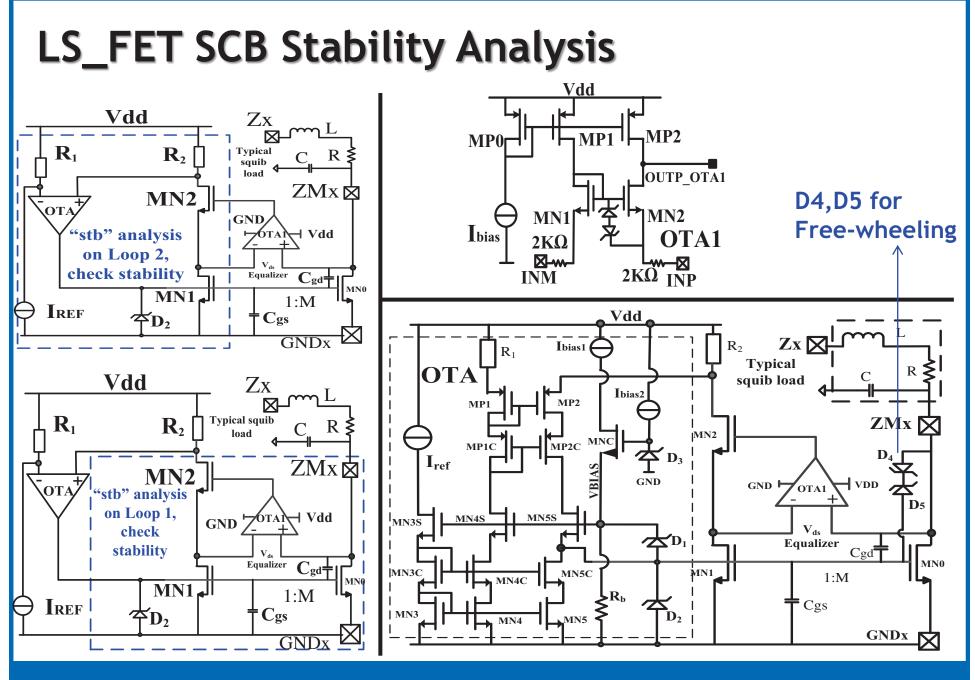

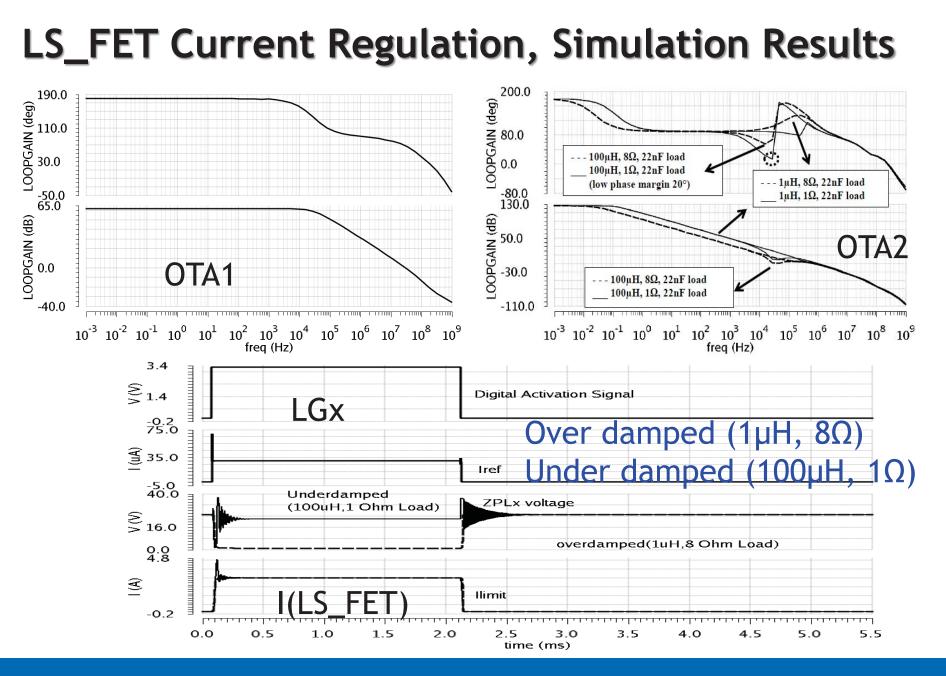

# LS\_FET Current Regulation

- LS\_FET needs current limit of 3A when Zx has a SCB.

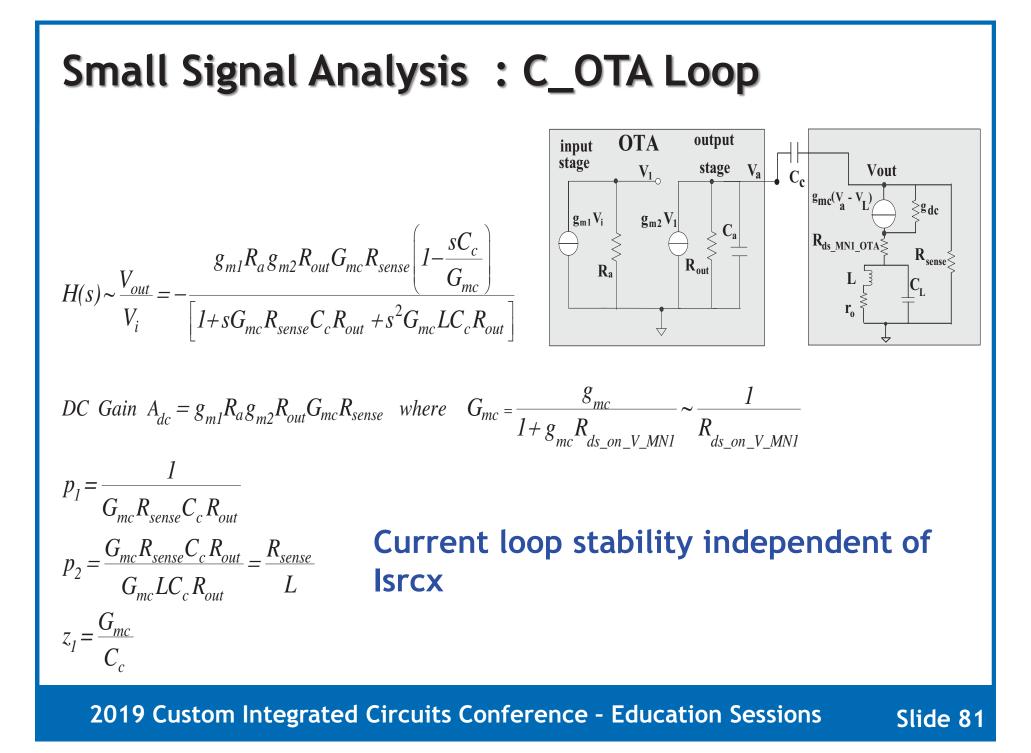

- A senseFET based current sensing and limiting/regulating circuit is needed. 2<sup>nd</sup> order transfer function H(s) from the gate to drain of MNO (gmp, gdp, Cgd=Cgs=Ca) for L-C loads.

- 2 OTAs involved. OTA needs higher gain than OTA1.

<u>End Result -> Stabilize the loop with Cg,eff of MN0.</u>

2019 Custom Integrated Circuits Conference - Education Sessions

2019 Custom Integrated Circuits Conference - Education Sessions

### LS\_FET Passive Discharge Concept

- Resistor at gate of MN0 not an option for passive discharge ("Outp" impedance is lowered).

- Rb at MN5 gate is the solution.

- Active Discharge speeds this up further.

[Easwaran US 8,553,388B2]

### Measurements : LS\_FET Current Regulation

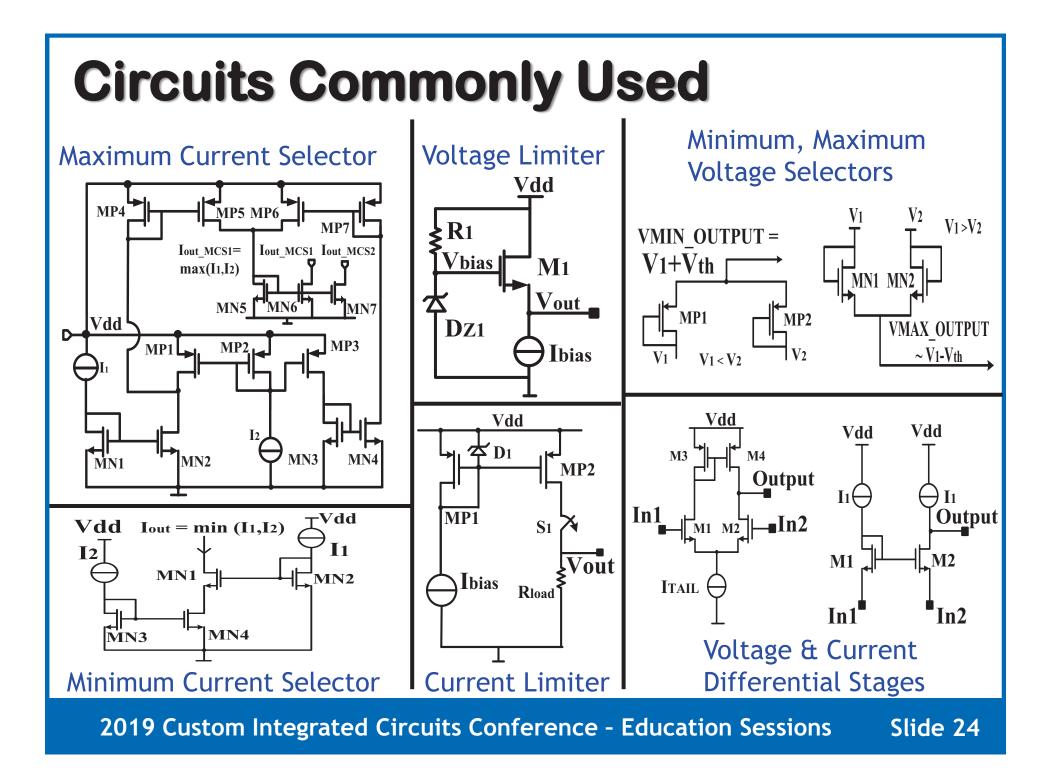

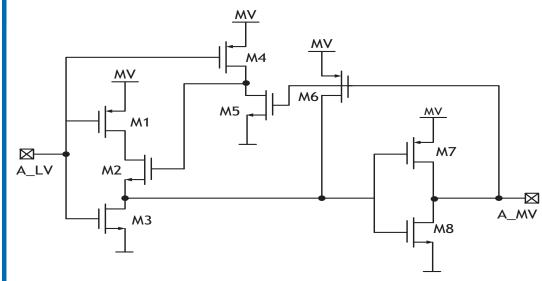

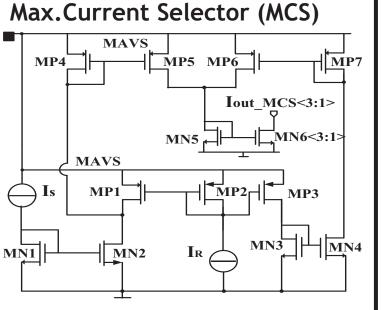

### **Biasing Schemes**

- Multiple Supply Voltage Designs

- Cross Coupled Level Shifters

- Maximum Current and Voltage Selectors

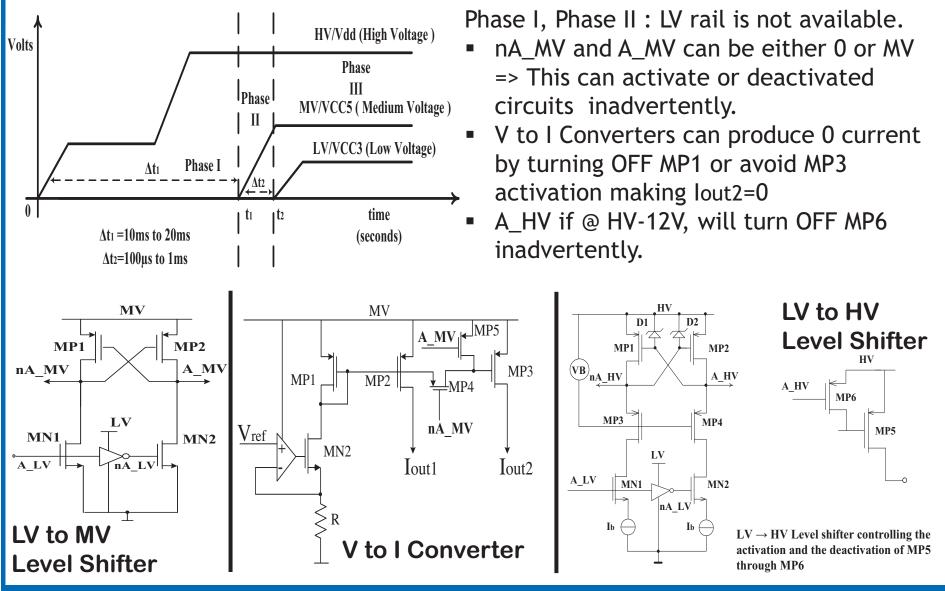

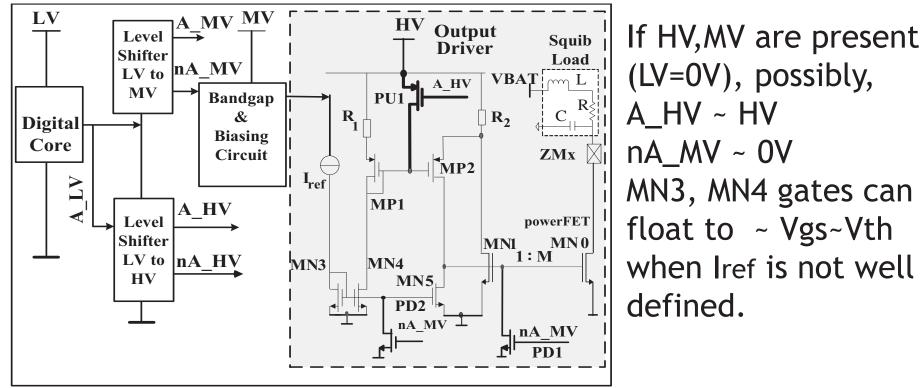

# Multiple Supply Voltage Design Challenge

2019 Custom Integrated Circuits Conference - Education Sessions Slid

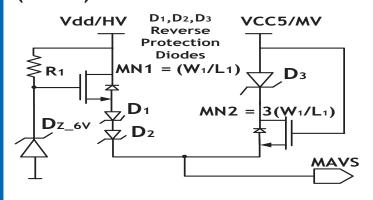

#### Levelshifters with voltage and current selectors

⇒MP1, MP2 turned ON, MN1, MN0 gates can be higher than Vth.

⇒Inadvertent activation/ current flow from VBAT and squib can be deployed.

$\Rightarrow$  Proper pull up/down is essential.

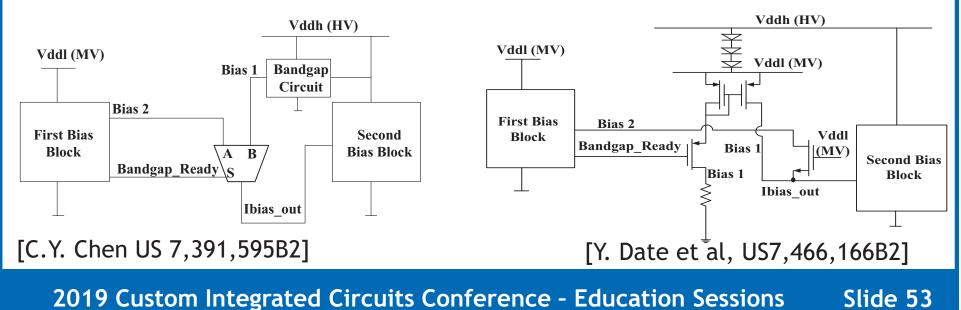

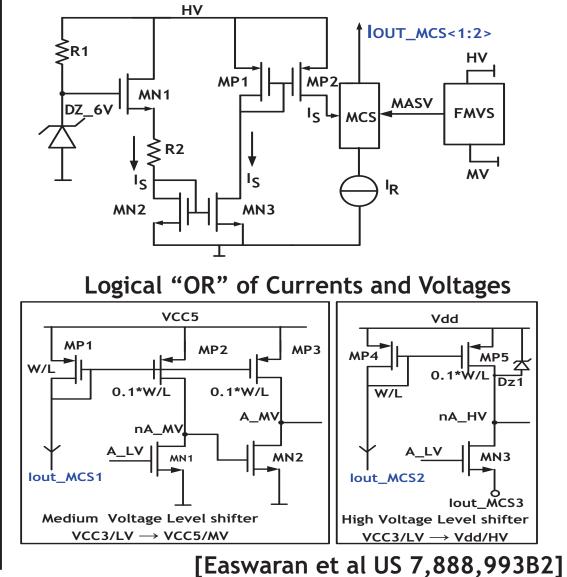

# **Prior Art**

LV Rail Independent level shifters. [M.H.Kim US7,683,667B2]

#### LV Rail Independent bias current generation

#### Levelshifters with voltage and current selectors

#### Fault Mode Voltage Selector (FMVS)

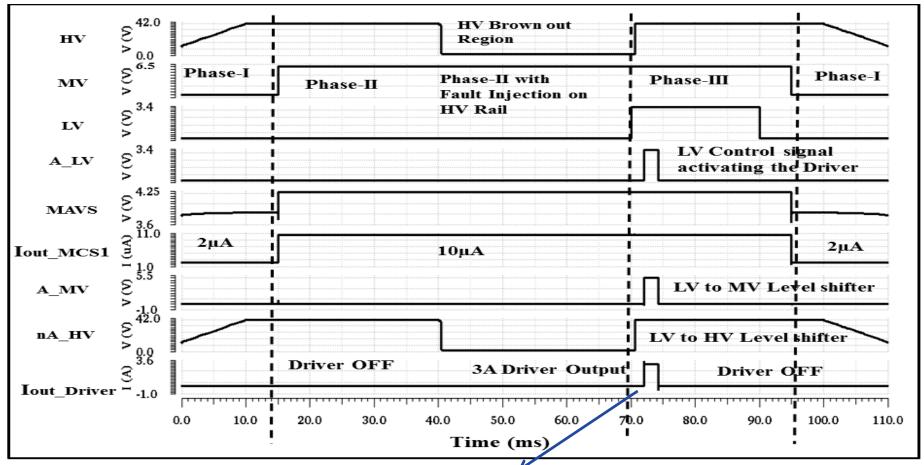

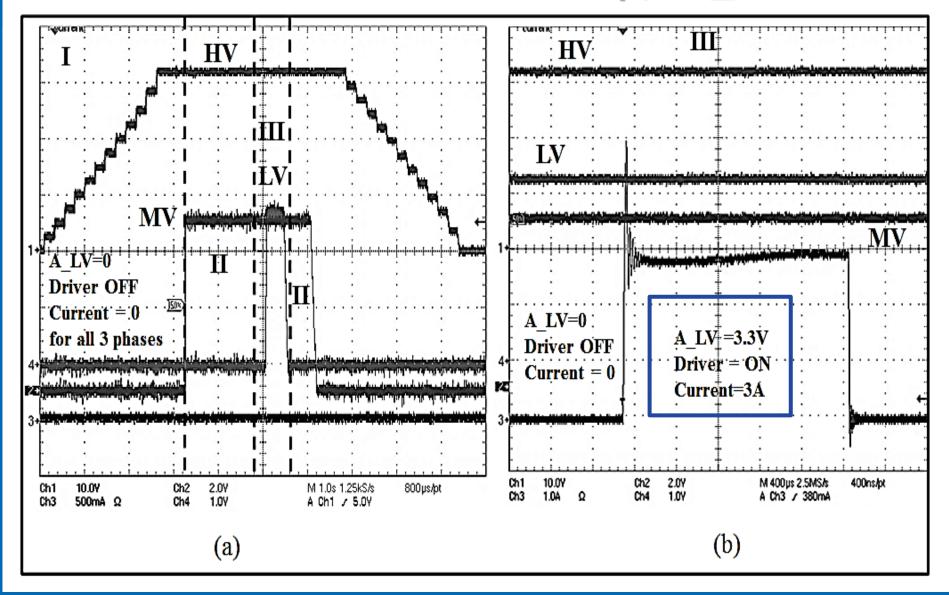

# **Simulation Methodology**

- Driver is active only when A\_LV toggles to 3.3V.

- Driver Regulates current to 3A when A\_LV is high.

Otherwise its output is 0A.

#### Measurement Results - Power Up, LS\_FET Test

2019 Custom Integrated Circuits Conference - Education Sessions

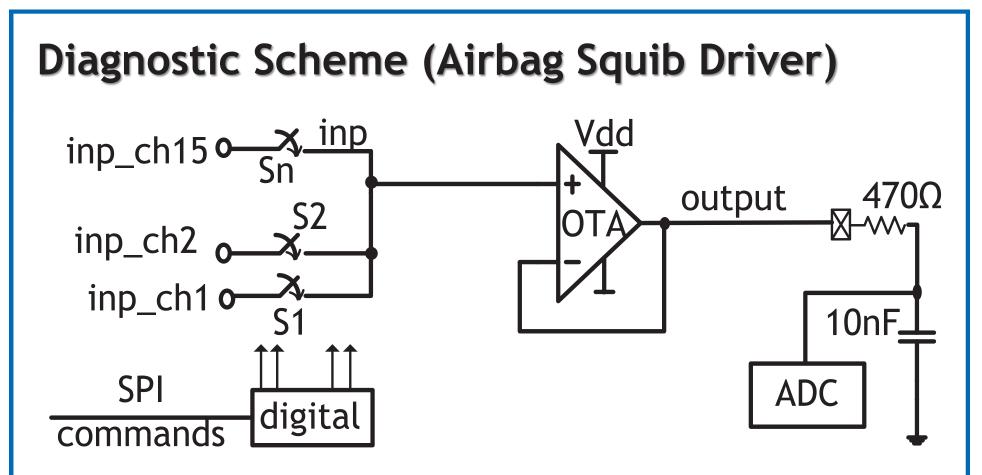

# Diagnostics

- Diagnostic Scheme

- High Voltage Switches

- Parasitic NPNs Mitigation

- HS, LS FET Diagnostics

- Output voltage clamping

# Goals

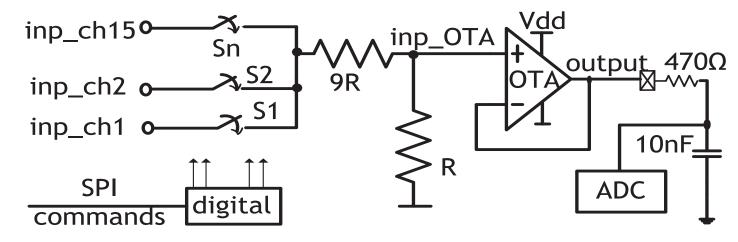

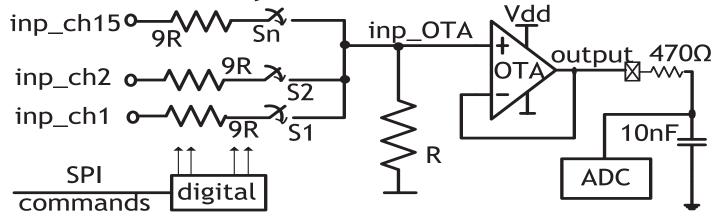

- Voltage, leakage, impedance measurements, checks on powerFETs are critical.

- Scaled version of high voltage inputs is measured through Analog output (AMX\_OUT) or converted to a digital value through ADC.

- HS and LS\_FETs are turned ON for 1-2ms duration.

Load ~10mA to 30mA and checked for leakage flags.

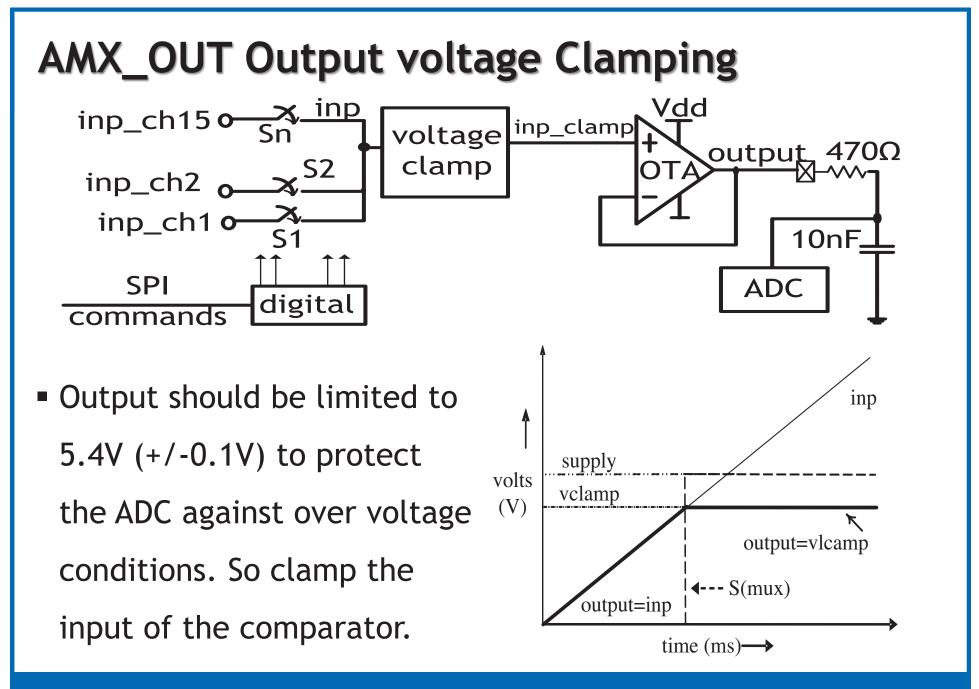

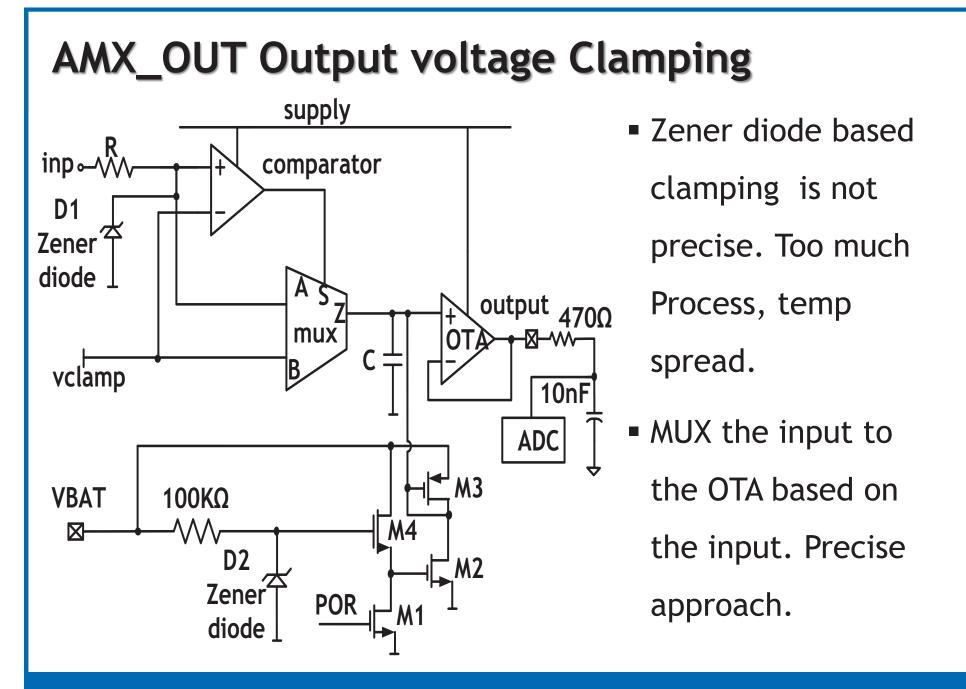

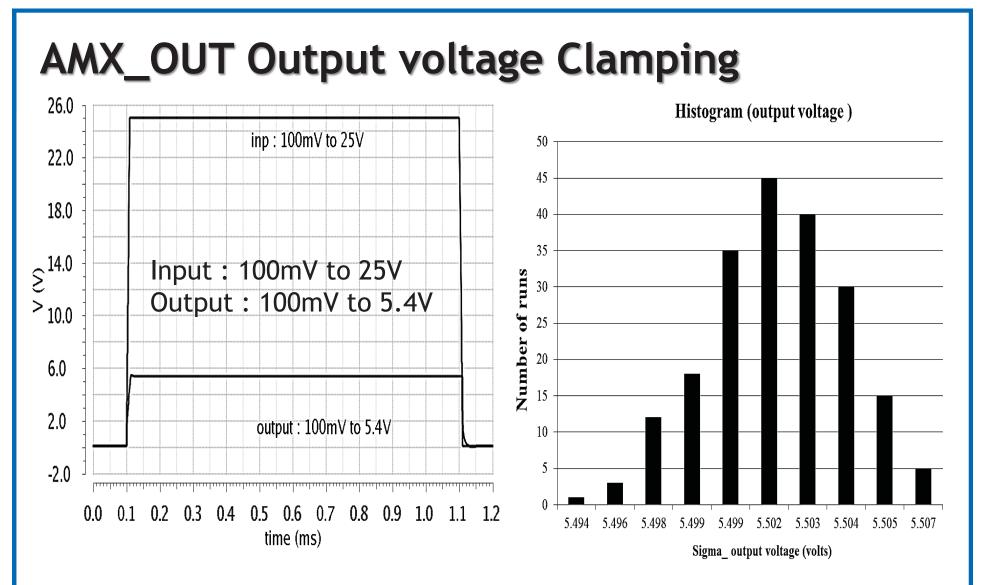

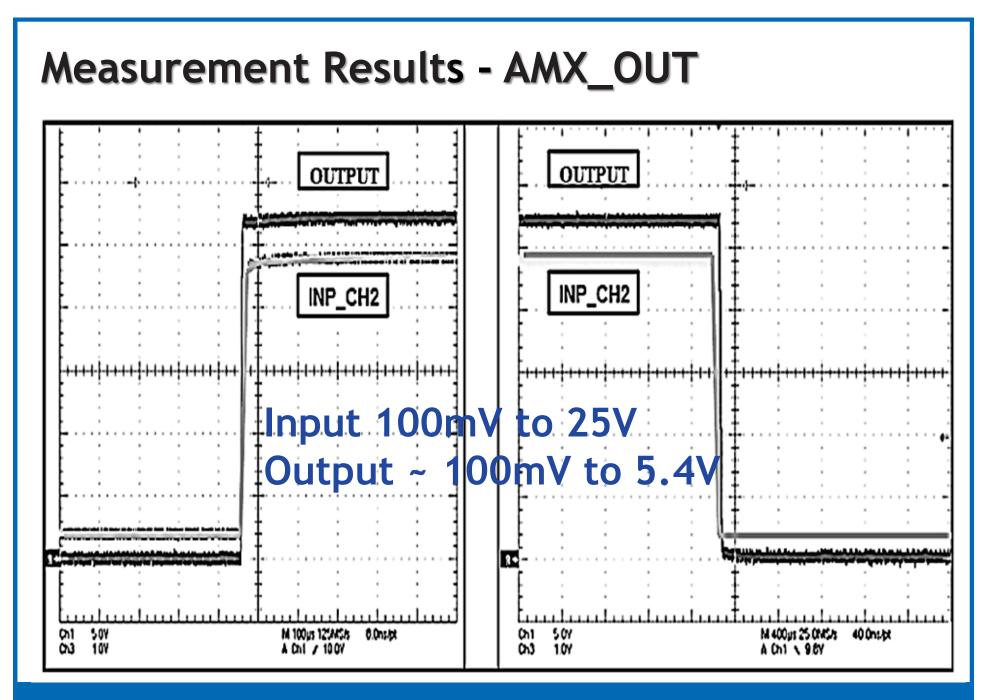

- inp\_chx (x=1..15) can range from 100mV to 15V.

- Output should be limited to 5.4V to protect the ADC against over voltage conditions.

#### **Scaled Down Voltage Measurements**

- inp\_chx (x=1..15) can range from 100mV to 15V.

- Output should be limited to 5.4V (+/-0.1V) to protect the ADC against over voltage conditions.

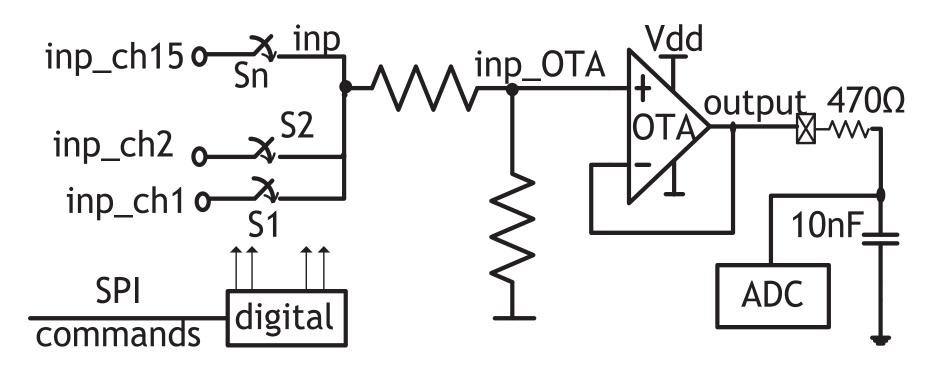

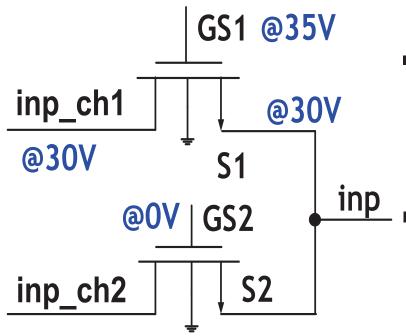

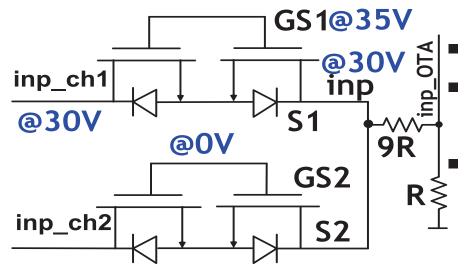

### Switches

- One switch is active. Rest are in OFF state.

- All Switches should be protected (No Vgs, Vds, Vsb violation).

- Vgs,Vds of S1 is within its max. ratings. Vsb of S1 is violated (30V vs 13.2V or 5.5V allowed).

- Protect Vsb for S1 by tie-ing s-b together (layout impact due to isolation from substrate).

- Vgs and Vsb of S2 are violated. Vsb protected by tie-ing s-b together but Vgs fix needs another approach.

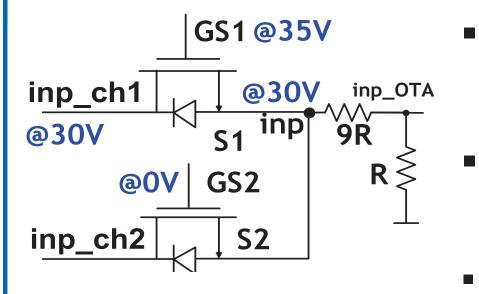

### **LDMOS Based Switches**

- Vgs,Vds of S1 is within its max. ratings. Vsb is not an issue for LDMOS.

- Vgs of S2 is impacted. Body diode of S2 is forward biased if inp > inp\_ch2.

- Reliability Concern.

- Fix back to back LDMOS FETs. G-S junctions are not directly exposed.

- G-D junctions withstand high voltage levels. Area impact high.

#### High Voltage Switch Architecture **HV** Supply MN3 MN4 <u>A</u> MP1 MP2 B В Rgs VIN+Vgs D1 Over VIN Drive lb

NMOS and PMOS HV Switches with their adaptive gate bias and protection

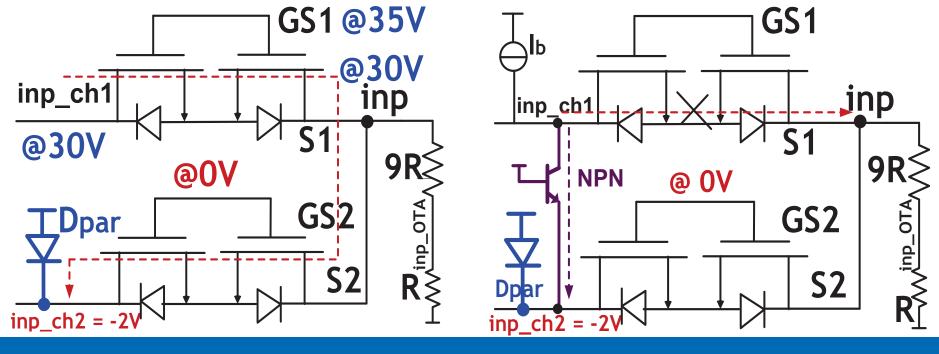

# **LDMOS Based Switches**

- When inp\_ch2 is below ground level (-2V), issues arise !

- Dpar (P-N junction from substrate to drain) is forward biased.

[ Clamped @-0.7V for current load. Too high current when forced to -2V ].

- GS2 turns ON =>cross talk between inp\_ch1 and inp\_ch2.

Potential NPN path will also exist and Ib never gets to "inp".

### **Design Improvements**

Intended design and robust design. If a signal is taken negative, then resistors limit the current.

No impact to functionality 9R >> Rds\_on of Sn

2019 Custom Integrated Circuits Conference - Education Sessions

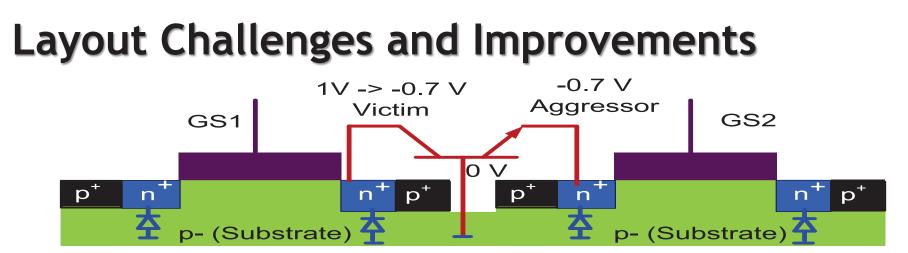

NPN action is dependent on the spacing between the two n+ regions. Lesser separation => higher NPN action.

- Larger separation is not area effective.

- Guard rings typically help to avoid potential NPN. Alternative is Deep trench.

2019 Custom Integrated Circuits Conference - Education Sessions

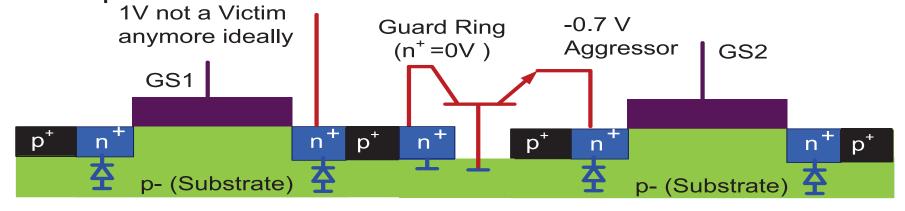

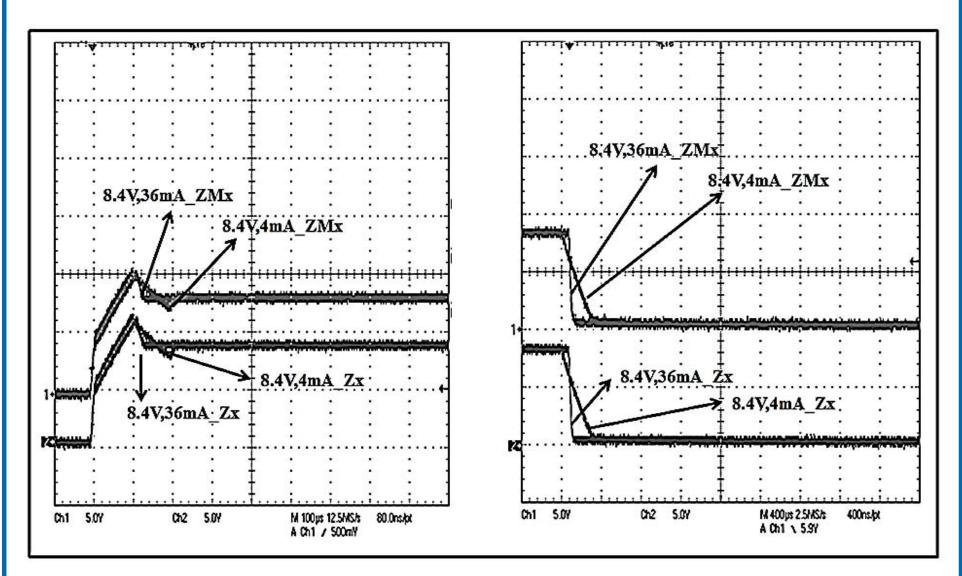

# **HS\_FET Test**

HS\_FET is turned ON in diagnostic mode. 1-2ms duration, 10 to 40mA current range. Check for leak to battery.  $v_{Z1}$   $v_{Z2}$

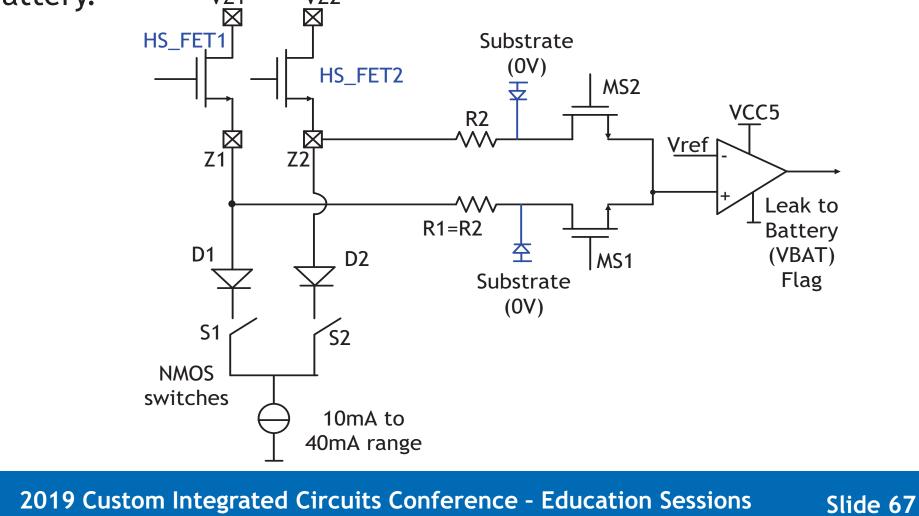

# LS\_FET Test

HS\_FET is turned ON in diagnostic mode.

1-2ms duration, 10 to 40mA current range. Check for leak to

2019 Custom Integrated Circuits Conference - Education Sessions

- Output voltage limited during any power up scenario

- Precise output voltage limitation due to precise input voltage limitation

2019 Custom Integrated Circuits Conference - Education Sessions

## **Additional Requirements**

- Automotive IC Design overhead

- Conducted Emission

- Portable Design

- References Current Limited Voltage Source

## Automotive IC Design Overhead

Concept/Topologies in Conventional (Consumer) and Automotive designs are not way different.

Faults, protection strategies, fast transients, unpowered state requirements lead to new topologies/additional circuits.

- 40V compliance is mandatory on several High Voltage pins.

- ESD -> Device level, system level (powered, unpowered state) requirements have to be met for Automotive designs.

- Passing DPI (Direct Power Injection), BCI (Bulk Current Injection), Mobile

Transmitter tests add an additional overhead to Automotive designs .

# ESD Requirements\_SDU\_Example

Traditional ICs: HBM : +/- 1KV, CDM : +/-500V -> JEDEC, IC Level.

Automotive ICs, AEC Q-100

- Max ESD Levels HBM : +/-2KV, CDM : +/-500V, +/-750V Corner Pins

- Max ESD Levels Unpowered, Powered ESD : For Zx, ZMx (squib lines), +/-8KV (with min.external protection (only capacitors))

- +/-25KV (with external protection (capacitors + Zener diodes).

- Pass Criteria : No destruction of ASIC. Part can't reset (powered state)

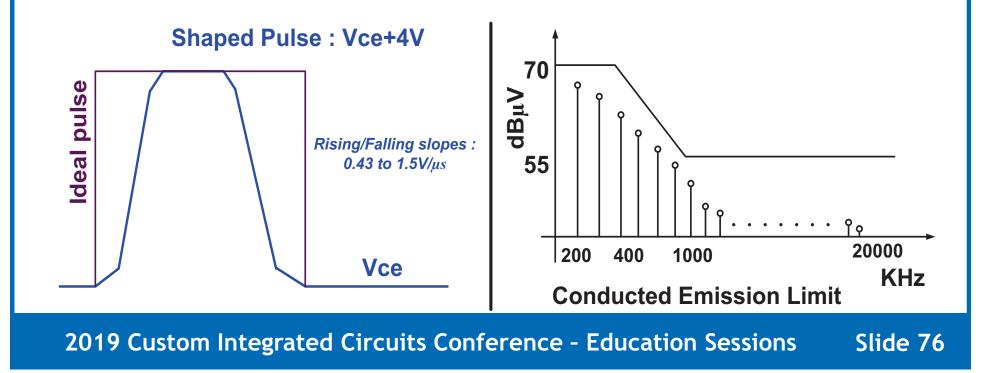

# **Conducted Emission Levels**

- Shaped pulse reduces EMI (Electro Magnetic Interference).

- Sharp pulse edges have higher harmonics and can interfere with sensor data, audio band.

- Sharp pulses generate supply & ground noise due to Parasitic Inductance that can affect the whole IC performance. So it is important to shape the pulse => No Fast Switching !!

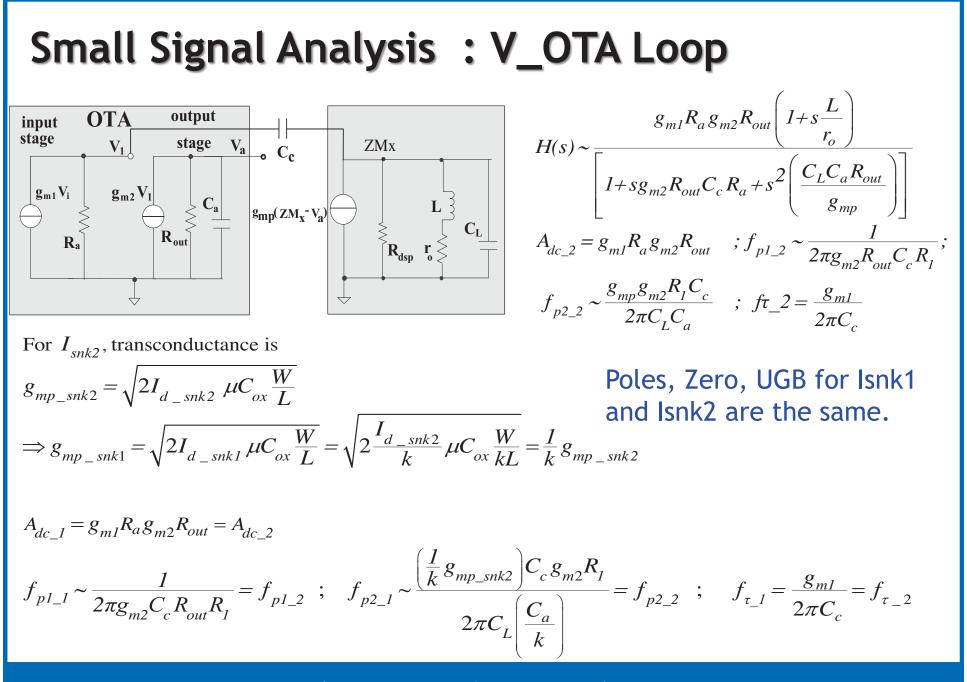

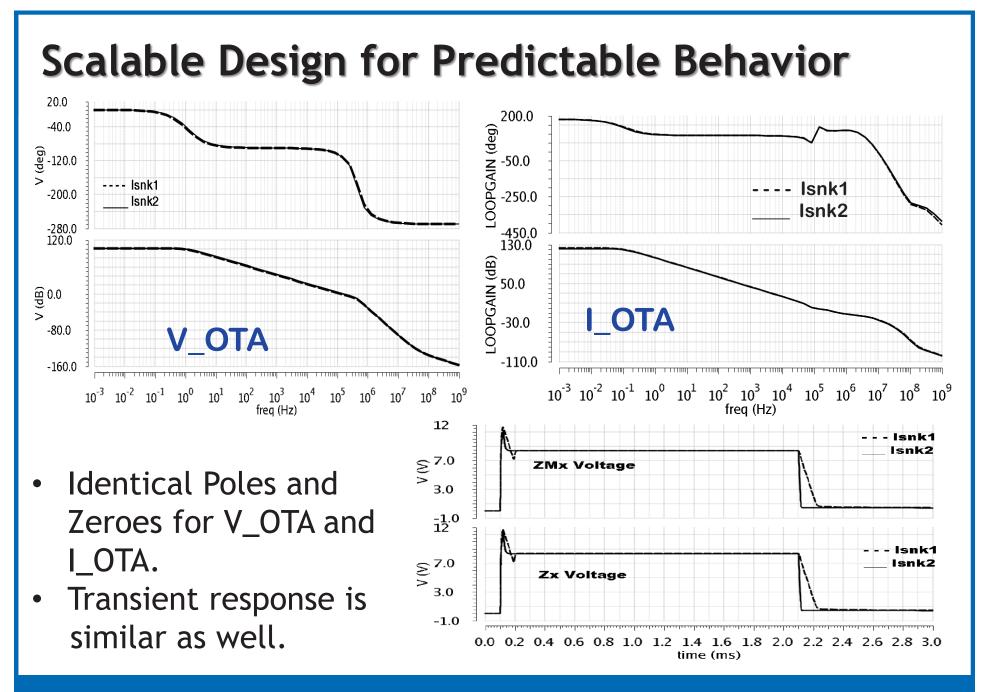

# **Portable Design**

- Design change from one BiCMOS node to another BiCMOS technology node involves first to check for Vgs protection.

- 40V device in two different technology nodes, Vds is still 40V but Vgs,max can be 13.2V vs 5V.

- Ensure that the Zener diodes reverse break down used for 5.5V gate oxide protection, is 5V.

- PowerFET W/L critical for Rds\_on and thermal SOA.

- Transfer function H(s) will be unchanged. => If Cox increased by a factor of 2 in new technology, W/L can be shrunk by 2, for same gm.

- Similar tricks for parameters like Rout.

$$H(s) = \frac{g_{m1}R_a g_{m2}R_{out} r_1 \left(1 + sR_{z1}C_c\right)}{r_o \left[1 + sR_{out}C_c + s^2 \left(\frac{LR_{out}C_c}{r_o}\right)\right]}$$

where  $g_{m1} = \sqrt{2I \mu C_{ox}} \cdot \frac{W}{L}$

$g_{m1\_new} = \sqrt{2I \mu 2C_{ox}} \cdot \frac{W}{2L} = g_{m1}$

2019 Custom Integrated Circuits Conference - Education Sessions

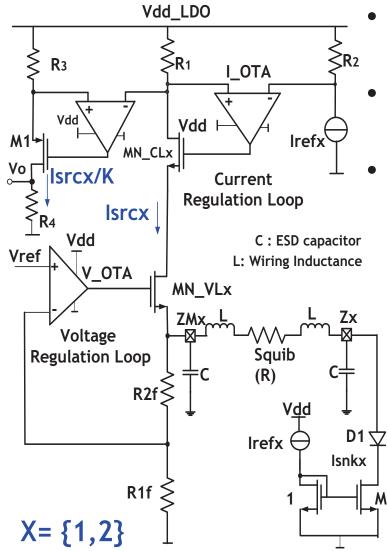

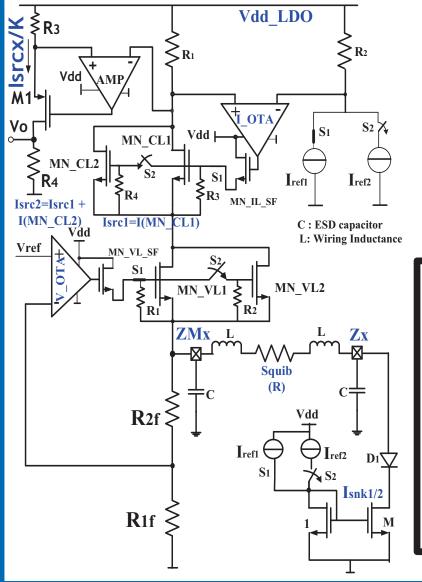

### **References - Current Limited Voltage Source**

- Current Limited Voltage Source (CLVS) regulates voltage on ZMx pin.

- When ZMx is shorted to ground, I\_OTA regulates/limits the current.

- Vo is the voltage equivalent of scaled version of Isrcx.

$$V_{ZMx} = \left(I + \frac{R_{2f}}{R_{1f}}\right) V_{ref}$$

$$I_{srcx} = \left(\frac{R_2}{R_1}\right) I_{refx}$$

$$I_{scl} = \left(\frac{I_{srcx}}{k}\right) = \left(\frac{R_1}{R_3}\right) I_{srcx}$$

2019 Custom Integrated Circuits Conference - Education Sessions

### **Implementation - Current Limited Voltage Source**

- Diagnostics is always a two point measurement.

- Isrc1/2 > Isnk1/2 so that V\_OTA regulates the voltage on ZMx.

- Vo, VZMx are measured through AMX\_OUT. R4 is a known resistor.

- (Vo/R4) calculation => Isrcx/K is known.

- R1, R3 known by design=> K,Isrcx is known.

- > VZMx/Isrcx calculation

provides leakage impedance on

ZMx pin.

2019 Custom Integrated Circuits Conference - Education Sessions

2019 Custom Integrated Circuits Conference - Education Sessions

2019 Custom Integrated Circuits Conference - Education Sessions

### **Measurement Results - CLVS**

2019 Custom Integrated Circuits Conference - Education Sessions

# Conclusion

- Automotive IC designs are not different from conventional (consumer/already well known) IC designs.

- Most of the Automotive ICs have to be 40V compliant. Some pins would have to tolerate negative voltages (-2V to -18V).

- Designs are portable from one technology to another. Circuits that are scalable have better predictable behavior.

- Additional circuits or modifications to conventional designs might be required to address fault conditions, powered and unpowered state, ESD, DPI requirements.(ESD and Immunity tests add additional burden to designers.)

- Level shifters have to be designed fail silent.

- Diagnostics, Cross link tests are critical and should be designed to avoid false warnings.

- Quality is a key factor in Automotive. 0 dppm is the expectation.

## References

[1] CVEL (Clemson University of Vehicular Electronics Laboratory), Automotive Electronics [Online]. Available FTP: http://www.cvel.clemson.edu/auto/systems/auto-systems.html

- [2] P.L. Hower, "Safe Operating Area A new frontier in LDMOS Design," *Proceedings 14<sup>th</sup> International Symposium on Power Semiconductor Devices and ICs*, Santa FE, New Mexico, June 2002, pp. 1-8, DOI: 10.1109/ISPSD.2002.1016159.

- [3] R.S. Wrathall, "A Study of AC and Switch Mode Coupling of Currents to Airbag Squib Ignitors," *Proceedings Workshop on Power Electronics in Transportation, IEEE*, pp. 111-116, 1996, DOI: 10.1109/PET.1996.565918.

- [4] Quad Channel Driver for Airbag Deployment. TPIC71004-Q1, Datasheet, Texas Instruments, SLVSAT2, Feb 2011.

- [5] V. Colarossi, "New Development in Autoliv Squib Driver Validation Process," 12<sup>th</sup> International Symposium and Exhibition on Sophisticated Car Occupant Safety Systems, Karlsruhe, Germany, December 2014.

- [6] *AK-LV-16*, Electrical Igniters for Pyrotechnical Systems, Requirements and Test Conditions. Specification of the Automotive Industry.

- [7] T. Regan, "Current Sense Circuit Collection," *Linear Technology*, Application Note 105, December 2005.

- [8] Current Loop Application Note, CLAN1495, B&B Electronics, 1995.

- [9] User Configurable Airbag IC. L9678, L9687-S, Datasheet, DocID025869, Rev 3.0, STMicroelectronics, May 2014.

- [10] V. Ivanov and I. Filanovsky. Operational Amplifier, Speed and Accuracy Improvement, Kluwer, 2004.

- [11] S.N.Easwaran. *Fault Tolerant Design Techniques for Smart Power Drivers and Diagnostic Circuits*, Ph.D. dissertation. University of Erlangen-Nuremberg, May 2017.

#### 2019 Custom Integrated Circuits Conference - Education Sessions Slide 85

### Thankyou for your attention

2019 Custom Integrated Circuits Conference - Education Sessions Slide 86