# A survey of FPGA-based LDPC decoders

Peter Hailes, Lei Xu, Robert G. Maunder, Bashir M. Al-Hashimi and Lajos Hanzo School of ECS, University of Southampton, SO17 1BJ, UK Corresponding author: lh@ecs.soton.ac.uk

Abstract—Low-Density Parity Check (LDPC) error correction decoders have become popular in communications systems, as a benefit of their strong error correction performance and their suitability to parallel hardware implementation. A great deal of research effort has been invested into LDPC decoder designs that exploit the flexibility, the high processing speed and the parallelism of Field-Programmable Gate Array (FPGA) devices. FPGAs are ideal for design prototyping and for the manufacturing of small-production-run devices, where their insystem programmability makes them far more cost-effective than Application-Specific Integrated Circuits (ASICs). However, the FPGA-based LDPC decoder designs published in the open literature vary greatly in terms of design choices and performance criteria, making them a challenge to compare. This paper explores the key factors involved in FPGA-based LDPC decoder design and presents an extensive review of the current literature. In-depth comparisons are drawn amongst 140 published designs (both academic and industrial) and the associated performance trade-offs are characterised, discussed and illustrated. Seven key performance characteristics are described, namely their processing throughput, processing latency, hardware resource requirements, error correction capability, processing energy efficiency, bandwidth efficiency and flexibility. We offer recommendations that will facilitate fairer comparisons of future designs, as well as opportunities for improving the design of FPGA-based LDPC decoders.

Index Terms—Digital communication, error correction codes, low-density parity check (LDPC) codes, field programmable gate array, iterative decoding

# I. INTRODUCTION

OW-Density Parity Check (LDPC) codes may be employed for correcting transmission errors in communication systems. They represent a class of Forward Error Correction (FEC) codes that are currently the focus of much research within the communications community. They were first proposed by Gallager in 1962 [1], but they were considered to be too complex for practical simulation and implementation at the time of their conception, hence they were left largely untouched for decades. Apart from their excellent performance, perhaps partially motivated by the fact that the turbo codes patented during the early 1990s attracted a license-fee, in 1996 LDPC codes were rediscovered by Mackay and Neal [2], and ever since have enjoyed a renaissance. Given the increased computing power available today they have become a key component of many commercialised communication systems,

The financial support of the PhD studentship provided by Altera, California USA, the grants EP/J015520/1 and EP/L010550/1 provided by EPSRC, Swindon UK, the grant TS/L009390/1 provided by Innovate UK, Swindon UK, as well as the Advanced Fellow grant provided by the European Research Council is gratefully acknowledged. The research data for this paper is available at http://dx.doi.org/10.5258/SOTON/384946.

including WiFi [3], WiMAX [4], DVB-S2 [5], CCSDS [6] and ITU G.hn [7].

LDPC codes benefit from a number of appealing features that make them very attractive for implementation. The LDPC decoding algorithm can be implemented using low-complexity calculations, resulting in a relatively low design and implementation cost for the processing hardware. Like turbo codes, LDPC codes are decoded iteratively, achieving an error correction performance that is close to the theoretical limit when decoding messages that have large block lengths [8]. However, in contrast to turbo codes, there is a wide variety of possible algorithms and levels of parallelisation that may be considered for the design of LDPC decoders, presenting designers with a range of options that may be relied upon to achieve the desired characteristics.

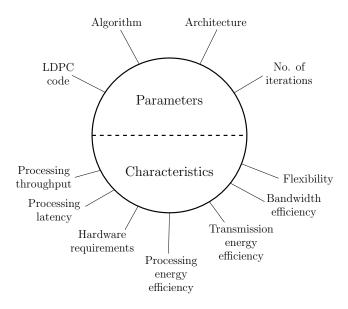

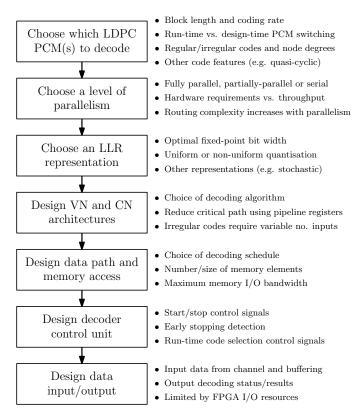

However, while the design of the individual processing components is relatively simple, the design of a complete LDPC decoder is subject to a complex interplay between a number of system characteristics, namely the processing throughput, processing latency, hardware resource requirements, error correction capability, processing energy efficiency, bandwidth efficiency and flexibility. These characteristics depend on a number of system parameters, namely the architecture, the LDPC code employed, the algorithm used and the number of decoding iterations. This relationship is shown in Fig. 1. Note that the bandwidth efficiency also depends on the modulation scheme chosen, as does the transmission energy efficiency, which furthermore depends on the coding gain and the error correction capability of the chosen LDPC code. To elaborate a little further in the context of Fig. 1, we can improve the error correction capability in many different ways, for example by using a stronger LDPC code or more decoding iterations. Naturally, increasing the number of iterations increases the complexity and hence reduces the processing energy efficiency, but increases the transmit energy efficiency. Hence the total energy dissipation should be considered holistically, when designing an LDPC decoder. Further similar trade-offs will emerge throughout our forthcoming discussions.

In order to fully characterise an LDPC decoder design, it is necessary to physically implement it. Perhaps the simplest way of doing so is to use a Field-Programmable Gate Array (FPGA) device, which facilitates rapid prototyping and fast parallel logic processing. This approach is especially useful for measuring the Bit Error Rate (BER) performance, since simulations that would take days on a computer can be completed in only hours when using a custom FPGA implementation [9]. These advantages are evident from the sheer number of published FPGA-based LDPC decoder designs that exist in the open literature, which will be compared

Fig. 1. FPGA-based LDPC decoder system parameters and characteristics

later in this paper. Furthermore, the decoding techniques and implementation-oriented research presented alongside these designs has been of significant benefit to the wider communications research community [10]–[15]. In particular, the implementational characteristics of these FPGA-based LDPC decoders are increasingly informing the holistic design of communication systems.

In addition to their suitability for prototyping, FPGAs constitute a viable alternative to Application-Specific Integrated Circuits (ASICs) for the LDPC decoders of small-production-run communication devices, while their programmability has made them attractive for software-defined radios. This paper focuses exclusively on FPGA implementations of LDPC decoders, since they cannot be fairly compared to ASIC implementations, which are designed at a significantly higher development cost to have particularly high performance for high-production-run applications. Indeed, ASIC implementations are even difficult to compare with each other, because some papers provide post-synthesis results, while others offer post-layout results. Meanwhile, some papers consider only the ASIC core, while others include both the memory and Input/Output (I/O) resources.

This paper has been conceived for achieving the following aims:

- Provide a tutorial on LDPC decoding, discussing both the parameters and characteristics that affect the performance of FPGA implementations.

- Accurately compare all implementations of FPGA-based LDPC decoders that we are aware of.

- Characterise the observed trade-offs and relationships between the system parameters and characteristics.

- Recommend good practice to aid future designs of FPGAbased LDPC decoders, and to make published designs more comparable with each other.

- Identify opportunities for the further enhancement of FPGA-based LDPC decoders.

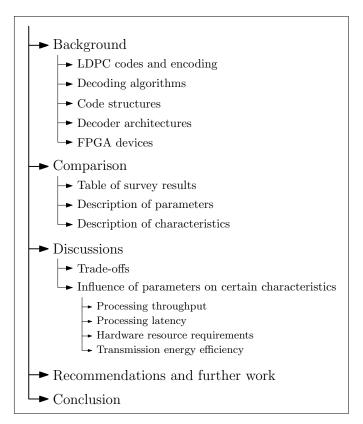

The structure of the paper is as follows. Section II presents

a brief tutorial on the LDPC code structure and encoding, as well as describing variations on the decoding algorithms, decoder architectures and FPGA devices. Section III provides our comparison of all FPGA-based LDPC decoders that we are aware of, whilst discussing the parameters and characteristics of an LDPC decoder in more detail. Section IV illustrates and characterises the observed trade-offs and relationships between the various parameters and characteristics of FPGA-based LDPC decoders. Recommendations for readers interested in developing their own FPGA-based LDPC decoders are offered in Section V, along with suggestions for further work in the area. Finally, we offer our conclusions in Section VI. This structure is depicted in Fig. 2.

Fig. 2. Structure of this paper

# II. BACKGROUND

This section presents a tutorial on FPGA-based LDPC decoders. Section II-A commences by discussing FEC, before LDPC codes are introduced in Section II-B. This is followed by a discussion of how LDPC codes are decoded and designed in Sections II-C and II-D, respectively. The practicalities of LDPC decoder implementations are then discussed in Section II-E, which is followed by a brief introduction to FPGAs in Section II-F.

## A. Forward error correction

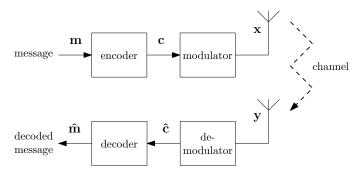

Fig. 3 shows a schematic of a simplified communications system, where the information message word  $\mathbf{m} = \{m_i\}_{i=1}^K$  is a vector of K bits, which is FEC encoded in order to obtain

the codeword  $\mathbf{c} = \{c_j\}_{j=1}^N$ , which is a vector of N > K bits. The FEC encoder converts the K-bit message word m into the N-bit codeword c by adding M = N - K parity bits to the message. The ratio of the message length K to the total codeword length N is referred to as the coding rate R,

$$R = \frac{K}{N} = \frac{N - M}{N}. (1)$$

The M additional parity bits are derived from the K message bits and hence they do not carry any information of their own. However, they are used during the FEC decoding process to allow transmission errors to be detected and even corrected, depending on the specific scheme used and on the severity of the corruption, as will be discussed below.

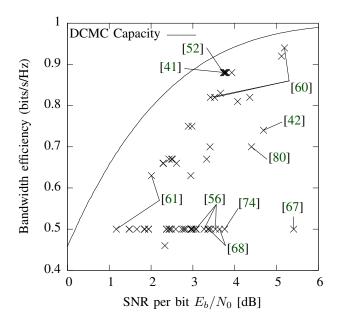

Fig. 3. A communications system

Various modulation schemes can be used for modulating the codeword c onto the channel. As we shall show in Section IV-B4, Binary Phase-Shift Keying (BPSK) modulation is assumed for nearly all FPGA-based LDPC decoder research. For this reason, we also assume the employment of BPSK modulation throughout this tutorial discussion. It is important to note however, that BPSK is a very simple modulation scheme, which is rarely employed alone in practical communication schemes. Therefore, considering BPSK modulation exclusively during the design phase could result in an LDPC decoder which does not necessarily work satisfactorily in practical systems, where higher-order modulation schemes are employed. Note that our analysis in Section IV will take the specific modulation scheme that was used into consideration, when comparing the error correction performance of various FPGA-based LDPC decoders.

BPSK generates the modulated symbol vector  $\mathbf{x} = \{x_j\}_{j=1}^N$ according to  $x_j = +\sqrt{E_s}$  when  $c_j = 0$  and  $x_j = -\sqrt{E_s}$  when  $c_i = 1$ , where  $E_s$  is the transmission energy per symbol. Similarly, there are several different ways of modelling the random corruption that is imposed by the channel upon the signal  ${\bf x}$ as it is transformed into the received signal  $\mathbf{y} = \{y_j\}_{j=1}^{\bar{N}}$ . In common with most FPGA-based LDPC research, we assume the Additive White Gaussian Noise (AWGN) channel model, in which a random noise signal is added to the transmitted signal,

$$y_i = x_i + \mathcal{CN}(0, N_0), \tag{2}$$

where  $\mathcal{CN}(\cdot)$  is the complex normal distribution and  $N_0$  is the noise power spectral density. The Signal to Noise Ratio (SNR) is given by  $E_s/N_0$ , and may also be expressed as the SNR per bit according to

$$\frac{E_b}{N_0} = \frac{1}{R} \times \frac{E_s}{N_0}. (3)$$

3

The corruption imposed by the channel causes y to differ from x in an unpredictable manner, potentially resulting in the demodulation of a perturbed received codeword  $\hat{\mathbf{c}}$ , potentially including some transmission errors. The decoder of Figure 3 is employed to recover the message word  $\hat{\mathbf{m}}$ , and without this there would be no way of correcting (or even detecting the presence of) these errors.

The error correction capability of a FEC decoder is affected by the form of the information provided by the demodulator. Rather than using hard decisions to convert received symbols into demodulated bits, superior error correction capability can be obtained if the demodulator provides soft decisions, which are commonly expressed using the Logarithmic-Likelihood Ratio (LLR) [16]. The sign of an LLR (positive or negative) expresses what the most likely value for the corresponding bit is (0 or 1, respectively). Meanwhile, the magnitude of an LLR expresses how likely this value is, where 0 represents complete uncertainty and  $\infty$  represents absolute certainty. The value of an LLR is calculated as

$$\tilde{c}_i = \log \frac{P(c_i = 0 \mid y_i)}{P(c_i = 1 \mid y_i)},$$

(4)

where  $\tilde{c}_i$  is the output LLR,  $c_i$  is the transmitted bit and  $y_i$  is the received symbol.

Here, the logarithm is used because it reduces the dynamic range of the likelihood ratio, tending to produce values in the range of -10 to +10, rather than 0.0001 to 10,000. This also allows probability intersections to be calculated using additions, rather than hardware-intensive multiplication operations. LLRs are extensively used throughout the LDPC decoding process, as will be detailed below.

When using BPSK modulation over an AWGN channel, the demodulator can convert the received signals into LLRs according to

$$\tilde{c}_i = 4 \times R \times \frac{E_b}{N_0} \times \text{Re}(y_i).$$

(5)

## B. LDPC codes

This section provides an introduction to LDPC codes, commencing with their structure and the encoding process in Section II-B1. Following this, the decoder's Parity-Check Matrix (PCM) is introduced in Section II-B2 together with its graphical representation using factor graphs in Section II-B3.

1) Encoding: Decoding an LDPC codeword is associated with a significantly higher complexity than the encoding process, because the decoder must consider every possible message word simultaneously, while operating on the basis of soft decision LLRs rather than hard decision bits. For this reason, we focus our attention on LDPC decoders in this paper, but the encoding process is explained briefly here for the sake of completeness.

As described previously, LDPC codes permit the correction of transmission errors by supplementing each K-bit message word with M parity bits in order to produce an N-bit codeword, where N=K+M [17]. Codes which include the K bits of the message word within the N bits of the codeword are referred to as systematic, while non-systematic codes have codewords which do not directly contain the original message bits. There are  $2^K$  possible permutations of the K-bit message word, each of which is mapped by the LDPC encoder to a corresponding one of  $2^K$  legitimate codeword permutations. The error correction capability of the LDPC code depends on the minimum Hamming distance between any pair of these  $2^K$  legitimate codeword permutations. Naturally high minimum distances are preferred, since these make it unlikely for a legitimate codeword to be transformed into another by the distortion introduced during transmission.

For example, a code with a message word length of K=6 and a codeword length of N=10 employs M=N-K=4 parity bits and has a coding rate of R=K/N=3/5. In the case where the code is systematic, each codeword  ${\bf c}$  may be of the form

$$\mathbf{c} = [c_1, c_2, c_3, c_4, c_5, c_6, c_7, c_8, c_9, c_{10}], \tag{6}$$

where  $c_1

ldots c_6$  are the K = 6 bits of the message word m and  $c_7

ldots c_{10}$  are the M = 4 parity bits. Each of the parity bits represents a parity check covering a specific subset of the message bits. As an example, the parity check bits may be obtained according to the following modulo-2 summations of message bits:

$$c_7 = c_4 \oplus c_6 \tag{7a}$$

$$c_8 = c_1 \oplus c_3 \oplus c_5 \oplus c_6 \tag{7b}$$

$$c_9 = c_2 \oplus c_5 \tag{7c}$$

$$c_{10} = c_1 \oplus c_2 \oplus c_6. \tag{7d}$$

The design of an LDPC code's parity check equations is subject to many complex factors, as will be briefly described in Section II-D. Using these equations, a  $(K \times N)$ -element generator matrix  ${\bf G}$  can be constructed to efficiently describe the encoding process. In a systematic code,  ${\bf G}$  may adopt the form

$$\mathbf{G} = \begin{bmatrix} \mathbf{I}_K & \mathbf{A} \end{bmatrix}, \tag{8}$$

where  $I_K$  is the  $(K \times K)$ -element identity matrix and the columns of A represent each of the parity checks. The generator matrix of the systematic code described above would therefore be

$$\mathbf{G} = \begin{bmatrix} 1 & 0 & 0 & 0 & 0 & 0 & 0 & 1 & 0 & 1 \\ 0 & 1 & 0 & 0 & 0 & 0 & 0 & 0 & 1 & 1 \\ 0 & 0 & 1 & 0 & 0 & 0 & 0 & 1 & 0 & 0 \\ 0 & 0 & 0 & 1 & 0 & 0 & 1 & 0 & 0 & 0 \\ 0 & 0 & 0 & 0 & 1 & 0 & 0 & 1 & 1 & 0 \\ 0 & 0 & 0 & 0 & 0 & 1 & 1 & 1 & 0 & 1 \end{bmatrix}. \tag{9}$$

Codewords can be calculated using this matrix by finding the modulo-2 matrix product of the message  $\mathbf{m}$  and the generator matrix  $\mathbf{G}$ , according to  $\mathbf{c} = \mathbf{m} \times \mathbf{G}$ . For example, it may be readily verified that the message  $\mathbf{m} = [0\ 1\ 1\ 1\ 0\ 1]$  has the corresponding codeword  $\mathbf{c} = \mathbf{m} \times \mathbf{G} = [0\ 1\ 1\ 1\ 0\ 1\ 0\ 1\ 0]$ .

2) Parity-check matrix: In the decoder, the parity checks are used to detect the presence of transmission errors in the

received codeword  $\hat{\mathbf{c}}$ . Since all of the codeword bits involved in a parity check (including the parity bit itself) should have a modulo-2 summation of 0, Equations (7a)–(7d) can be rewritten as follows:

$$c_4 \oplus c_6 \oplus c_7 = 0 \tag{10a}$$

$$c_1 \oplus c_3 \oplus c_4 \oplus c_6 \oplus c_8 = 0 \tag{10b}$$

$$c_2 \oplus c_5 \oplus c_9 = 0 \tag{10c}$$

$$c_1 \oplus c_2 \oplus c_6 \oplus c_{10} = 0.$$

(10d)

These equations are more commonly viewed as a PCM  $\mathbf{H}$ , which has N columns corresponding to the bits of the codeword and M rows corresponding to the parity checks. A non-zero entry in any position  $H_{ji}$  indicates that the i-th bit  $c_i$  takes part in the j-th parity check. In the case of systematic codes  $\mathbf{H}$  is related to  $\mathbf{G}$  according to

$$\mathbf{H} = \begin{bmatrix} \mathbf{A}^T & \mathbf{I}_M \end{bmatrix}. \tag{11}$$

Continuing our example from above, we have

$$\mathbf{H} = \begin{bmatrix} 0 & 0 & 0 & 1 & 0 & 1 & 1 & 0 & 0 & 0 \\ 1 & 0 & 1 & 0 & 1 & 1 & 0 & 1 & 0 & 0 \\ 0 & 1 & 0 & 0 & 1 & 0 & 0 & 0 & 1 & 0 \\ 1 & 1 & 0 & 0 & 0 & 1 & 0 & 0 & 0 & 1 \end{bmatrix}. \tag{12}$$

Upon obtaining a received codeword  $\hat{\mathbf{c}}$ , the syndrome  $\mathbf{s}$  can be calculated according to  $\mathbf{s} = \hat{\mathbf{c}} \times \mathbf{H}^T$ . In the case where  $\hat{\mathbf{c}}$  is a legitimate codeword permutation, the syndrome will equate to a vector of zeros. This may be demonstrated by re-using the codeword calculated in the previous subsection, which equates to a  $(1 \times M)$ -element vector of 0s when multiplied by  $\mathbf{H}^T$ .

Note however that an LDPC H matrix of the form shown in (12) is very unusual in practice. As it will be explained in Section II-C1, the decoder's error correction ability is dictated by the number of non-zero entries in each row or column, which is referred to as its *weight*. More specifically, columns with a weight of 1 can result in the decoder being unable to correct some transmission errors. This can be avoided by modifying the PCM H using elementary row operations (modulo-2 additions and swaps). In the case of the above example, this may lead to:

$$\mathbf{H} = \begin{bmatrix} 1 & 0 & 0 & 1 & 1 & 0 & 1 & 0 & 1 & 1 \\ 0 & 1 & 1 & 0 & 1 & 0 & 0 & 1 & 0 & 1 \\ 1 & 1 & 1 & 0 & 0 & 1 & 0 & 1 & 1 & 0 \\ 0 & 1 & 0 & 1 & 1 & 1 & 1 & 0 & 1 & 0 \end{bmatrix}. \tag{13}$$

This modified  ${\bf H}$  avoids any weight-1 columns, while still checking the same distribution of parity bits that was added to codewords by the generator matrix  ${\bf G}$  of (9). Note however that this toy-example PCM is still unusual for a realistic LDPC code. Specifically, the PCM used in LDPC decoding should be sparse, containing far fewer non-zero entries than 0s. Clearly, the  ${\bf H}$  of (13) does not satisfy this constraint, owing to its codeword length of N=10, which is very short compared to practical LDPC codewords, which tend to be hundreds or even thousands of bits long.

Owing to its significance in the decoding process, the PCM **H** is commonly used to define a particular LDPC code design. As discussed later in Section II-D, creating a **H** matrix that

achieves a strong error correction capability is a complex task, so this is usually the first aspect of the code to be designed. Following this, the generator matrix **G** can be derived from **H**, by following the reverse of the process described above.

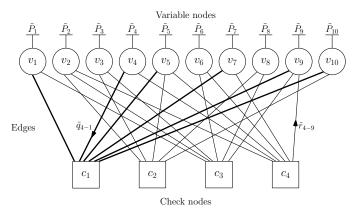

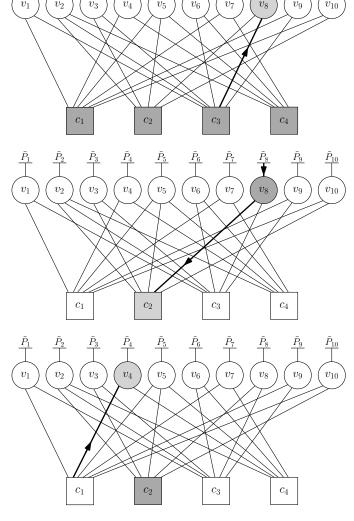

3) Factor graphs: The PCM  $\mathbf{H}$  can also be visualised graphically using a factor graph, which is also known as a Tanner graph [18]. This is exemplified in Fig. 4 for the PCM of (13). A factor graph is comprised of two sets of connected nodes, namely N Variable Nodes (VNs) for representing the columns of  $\mathbf{H}$  and M Check Nodes (CNs) for representing the rows.

Fig. 4. A factor graph for an example LDPC code

The connections  $\tilde{P}_i$  above each VN in Fig. 4 pertain to LLRs associated with the N codeword bits of  $\hat{\mathbf{c}}$ . An edge connects the i-th VN  $v_i$  to the j-th CN  $c_j$  if there is a nonzero element in the i-th column and j-th row of  $\mathbf{H}$ ,  $H_{ji}=1$ . To illustrate this, all of the edges that are connected to the  $1^{\rm st}$  CN  $c_1$  in Fig. 4 are shown with thicker lines. These edges are connected to the  $1^{\rm st}$ ,  $4^{\rm th}$ ,  $5^{\rm th}$ ,  $9^{\rm th}$  and  $10^{\rm th}$  VNs, in accordance to the position of the 1s in the top row of  $\mathbf{H}$  in (13).

The degree of a node is defined as the number of other nodes that it is connected to and is equal to the corresponding row or column weight in  $\mathbf{H}$ . The degree of the CNs  $D_c$  and the degree of the VNs  $D_v$  are important parameters in an LDPC code. If all CNs have the same degree  $D_c$  and all VNs have the same degree  $D_v$ , the LDPC code is said to be regular. If either value varies from node to node, the code is said to be irregular and  $D_c$  and  $D_v$  can be expressed as the average degree over all nodes. For example, the factor graph of Fig. 4 is irregular with  $D_c=5.75$  and  $D_v=2.3$ . In any case, the number of 1s in the PCM  $\mathbf{H}$  must be the same regardless, whether it is viewed row-by-row or column-by-column, giving  $D_c \times M = D_v \times N$ , with  $D_v=D_c \times (1-R)$ .

## C. LDPC decoding

LDPC codes are typically decoded using a belief propagation (BP) algorithm in which messages – typically in the form of LLRs – are iteratively passed in both directions along the edges between connected nodes [19]. For example, Fig. 4 illustrates a message  $\tilde{q}_{4-1}$  sent from the 4<sup>th</sup> VN  $v_4$  to the 1<sup>st</sup> CN  $c_1$ , while the message  $\tilde{r}_{4-9}$  is sent from the 4<sup>th</sup> CN  $c_4$  to the 9<sup>th</sup> VN  $v_9$ . The messages provided as inputs to a node are processed by activating that node, causing it to create new

output messages that are sent back to the nodes it is connected to. Thus the processing of the LDPC decoder is delegated to the many individual calculations performed by the individual nodes, rather than being a single monolithic global equation. An important facet of the belief propagation algorithm is that any message sent to a particular node does not depend on the message received from that node. For example, CN  $c_2$  is connected to VNs  $v_2$ ,  $v_3$ ,  $v_5$ ,  $v_8$  and  $v_{10}$ ; however, the message  $\tilde{r}_{2-5}$  it sends to  $v_5$  will be calculated based only on the messages it has received from  $v_2$ ,  $v_3$ ,  $v_8$  and  $v_{10}$ .

Nodes are activated in an order determined by the LDPC decoder's *schedule*. This has a significant effect upon the LDPC decoder's error correction capability, as well as on its other characteristics. Many different schedules exist and the most common options will be outlined in Section II-C1. Following this, variations of the specific calculations performed within CNs and VNs will be presented in Sections II-C2 and II-C3 respectively.

1) Scheduling: The schedule of the LDPC decoding process determines the order in which VNs and CNs are processed, as well as whether multiple nodes are processed in parallel. Many scheduling variations exist, but the three most common schedules are described here, namely flooding [20], Layered Belief Propagation (LBP) [21] and Informed Dynamic Scheduling (IDS) [22].

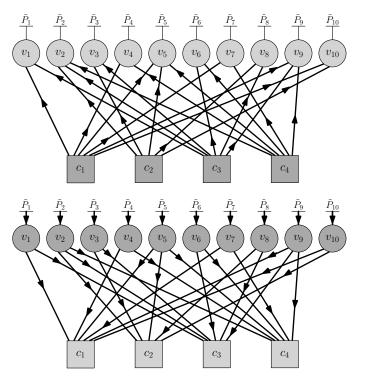

**Flooding** is perhaps the most conceptually simple LDPC decoding schedule. Here, the factor graph is processed in an iterative manner, where each iteration comprises the simultaneous activation of all CNs, followed by the simultaneous activation of all VNs [19]. An example of this schedule is depicted in Fig. 5. It can be seen that at first the CNs  $c_1$ – $c_4$  shown in dark grey calculate their messages, which are then

Fig. 5. An example of the flooding schedule

sent along every edge (in bold) to every receiving VN, shown in light grey. In the second half-iteration, the VNs are shown in dark grey to indicate that they are performing calculations, while the CNs are only receiving messages, so they are shown in light grey.

While Layered Belief Propagation also operates in an iterative manner, it processes the nodes more sequentially within each iteration, activating only one or a specific subset of nodes at a time [21]. LBP is commonly operated in a CNcentric manner, processing each CN in turn. Once a CN has been activated, all of its connected VNs are activated before moving on to the next CN. Once every CN has been processed, the iteration is complete. Using Fig. 6 as an example, LBP may commence each decoding iteration by activating CN  $c_1$ first, sending messages to each of its connected VNs:  $v_1$ ,  $v_4$ ,  $v_5$ ,  $v_7$ ,  $v_9$  and  $v_{10}$ . Each of these VNs may then be activated, sending new messages to each of their connected CNs, except  $c_1$ . Following this,  $c_2$  may be activated, allowing it to make use of the new information received from  $v_5$  and  $v_{10}$  alongside the information previously received from its other connected VNs. This process continues until every CN has been activated, which then marks the end of one decoding iteration.

LBP has the advantage that the information obtained during an iteration is available to aid the remainder of the iteration. Owing to this however, it does not have the same high level of parallelism as the flooding schedule, possibly resulting in a lower processing throughput and a higher processing latency. It can also be seen that M CN activations and  $D_c \times M$  VN activations occur per iteration, resulting in a higher computational complexity per iteration, when compared to the flooding schedule. However, it will also be shown in Section II-C2 that CN activations can be significantly more computationally expensive than the VN activations, hence the increased cost is manageable. Additionally, LBP tends to converge to the correct codeword using fewer iterations and therefore with lower computational complexity than flooding [17], resulting in lower complexity overall.

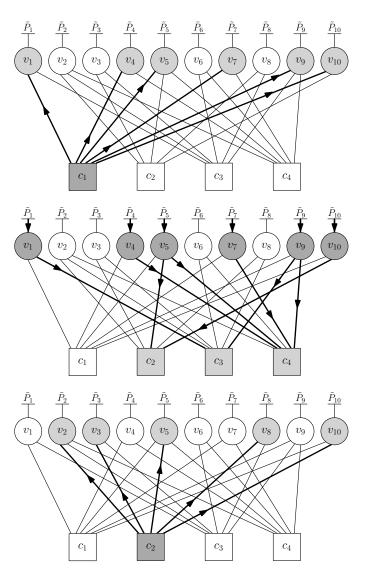

Informed Dynamic Scheduling inspects the messages that are passed between the various nodes, selecting to activate whichever node is expected to offer the greatest improvement in belief [22]. This requires IDS to perform additional calculations in order to determine which node to activate at each stage of the decoding process. However, IDS facilitates convergence using fewer node activations than in either flooding or LBP, which may lead to a lower complexity overall.

During IDS, the difference between the previous message sent over an edge and the message that is obtained using recently-updated information [23] is calculated. This difference is termed the *residual*, and represents the improvement in belief that is achieved by the new message. Like the LBP schedule, IDS is commonly centred on the CNs. At the start of the iterative decoding process, the residual for each output of each CN is calculated as the magnitude of the message to be sent over that edge. The message with the greatest residual is identified, and the receiving VN is then activated, sending updated messages to each of its connected CNs. These CNs then calculate new residuals for each of their edges as the difference between its new message and its previous message.

Fig. 6. An example of the layered belief propagation schedule

All of the residuals in the graph are then compared for the sake of identifying the new maximum, before the process is repeated.

Using Fig. 7 as before, suppose that at the start of the iterative decoding process, the message  $\tilde{r}_{3-8}$  from CN  $c_3$  is identified as having the highest magnitude of all the check-tovariable messages in the graph. Owing to this,  $\tilde{r}_{3-8}$  is passed to the VN  $v_8$ , which is then activated, in order to obtain the message  $\tilde{q}_{8-2}$  which is then passed to  $c_2$ . The CN  $c_2$ can then be activated to calculate new residuals for its other four edges, as the difference between their previous messages and their new messages that have been obtained using the updated information from  $v_8$ . These new residuals are then compared with the others from the previous step, allowing a new global maximum to be identified, to inform the next step of the decoding process. Note that the next highest residual within the factor graph does not necessarily have to originate from the most recently updated CN  $c_2$ . In the example seen in Fig. 7, it can be seen that  $c_2$  is activated to calculate residuals but it is  $\tilde{r}_{1-4}$  from CN  $c_1$  to VN  $v_4$  that is sent. This implies

Fig. 7. An example of informed dynamic scheduling

that there is no single straightforward concept of iterations in IDS, since it is possible for a particular CN to be updated several times before another is updated once.

2) Check node calculations: The calculations performed within the CNs vary between different LDPC decoding algorithms. Of the many that exist, the two most common LDPC decoding algorithms are the Sum-Product Algorithm (SPA) [24] and the Min-Sum Algorithm (MSA) [25].

When the j-th CN is activated, the LLR  $\tilde{r}_{j-i}$  that it passes to VN  $v_i$  is a function of the inputs gleaned from all other connected VNs, except for  $v_i$  [26]. In CN  $c_j$ , this message will represent the probabilities that the bit at  $v_i$  should be 0 or 1, which is determined by whether parity check j has already been fulfilled by the bits of the other connected VNs. This is achieved by calculating the probability that  $c_j$  is receiving an even number of 1s from its other edges. For two LLR operands  $\tilde{a}$  and  $\tilde{b}$  this equates to

$$\tilde{r}_{j-i} = \log \frac{P(a=0)P(b=0) + P(a=1)P(b=1)}{P(a=0)P(b=1) + P(a=1)P(b=0)}, \quad (14)$$

for which we use the notation  $\tilde{a} \boxplus \tilde{b}$ , referred to as the *boxplus* operator [27]. Inverting (4) and substituting into (14) yields:

$$\tilde{a} \boxplus \tilde{b} = 2 \tanh^{-1} \left( \tanh \frac{\tilde{a}}{2} \times \tanh \frac{\tilde{b}}{2} \right)$$

$$= \operatorname{sign} (\tilde{a}) \times \operatorname{sign} (\tilde{b}) \times \min \left( |\tilde{a}|, |\tilde{b}| \right)$$

$$+ \log \left( 1 + e^{-|\tilde{a} + \tilde{b}|} \right) - \log \left( 1 + e^{-|\tilde{a} - \tilde{b}|} \right). (16)$$

The SPA uses the full version of (15) given above, which leads to strong error correction performance but a high computational complexity. The MSA, on the other hand, is a reduced-complexity approximation of the SPA [28], using (16) without the correction factor terms, according to

$$\tilde{a} \boxplus \tilde{b} = \operatorname{sign}(\tilde{a}) \times \operatorname{sign}(\tilde{b}) \times \min(|\tilde{a}|, |\tilde{b}|).$$

(17)

Note however that the complexity reduction offered by the MSA is attained at the cost of a degraded LDPC error correction capability. This degradation may be mitigated by adding a low-complexity approximation to the correction factor terms to (17) or by multiplying (17) by a scaling factor, which may be optimised during the design of the LDPC decoder.

3) Variable node calculations: The calculations performed in the VNs do not generally vary between algorithms. As in the operation of the CNs, the message  $\tilde{q}_{i-j}$  passed from VN  $v_i$  to CN  $c_j$  is obtained as the sum of the LLRs received from all other edges, including the LLR  $\tilde{P}_i$  provided on the edge from the demodulator [26]. When using a schedule that requires the simultaneous update of the outputs provided to all of the VN's edges (such as the flooding schedule), the forward-backward algorithm [24] may be used to minimise the number of additions required by the VN. In other schedules, small internal memories may be used to store the results of some intermediate additions [21].

The VNs are also used for deciding the values of the reconstructed codeword bits. Each corresponding codeword LLR  $\tilde{L}_i$  is calculated as the sum of the LLRs received on the edges from all connected CNs, as well as on the edge from the demodulator. The polarity of the resultant LLR is then used to make a hard decision for the value of the corresponding bit of the reconstructed codeword  $\hat{\mathbf{c}}$ . More specifically, if  $\hat{L}_i < 0$ then  $\hat{c}_i$  is set to 1, whereas if  $\tilde{L}_i \geq 0$  then  $\hat{c}_i$  is set to 0. If the reconstructed codeword has a zero-valued syndrome  $\mathbf{s} = \hat{\mathbf{c}} \times \mathbf{H}^T$ , then the iterative decoding process may be considered to have been a success and the process may be terminated. If not, then the iterative decoding process may be continued until a zero-valued syndrome is obtained or until an affordable complexity limit is reached. Practical LDPC decoder designs may also include other stopping criteria, as discussed later in Section II-E3.

# D. LDPC code construction

In addition to the size of the factor graph and the degrees of its nodes, the position of the edges within the factor graph also has a significant impact on the associated error correction performance, as well as upon the decoding complexity. Some of the main objectives when designing the PCM H is to avoid

creating stopping sets [29] and short cycles [30] in the corresponding factor graph, which are associated with an eroded error correction performance. A number of techniques have been proposed for placing edges within the factor graph have been proposed, as summarised in the following subsections.

- 1) Random codes: Unstructured randomly-designed codes potentially achieve the best LDPC error correction performance, owing to the maximised degree of freedom that is afforded, when placing edges in this manner [31]. However, this is achieved at the cost of having to implement complex unstructured routing or memory lookup tables, in order to exchange LLRs between the variable and CNs. A straightforward recursive algorithm for creating unstructured PCMs of this form involves placing a 1 at a random unfilled location in H, then checking to see whether doing so has violated any design constraints, such as the maximum node degrees, stopping sets or cycle lengths. If the placement is valid, the algorithm will continue and repeat the process for the next randomly placed 1. This is repeated until the desired number of edges have been positioned. If a randomly placed 1 is not valid, then it will be rejected and a new location will be tried instead. This algorithm is conceptually very simple, but whether the process can successfully complete and how quickly is unpredictable.

- 2) Pseudorandom codes: The original LDPC code construction method proposed by Gallager [1] involves stacking  $D_c$  number of submatrices on top of each other. Each submatrix has the dimensions  $^M/D_c \times N$ , with each column having a weight of 1 and each row having a weight of  $D_v$ . The top matrix is pseudo-randomly generated, and random column permutations are applied to it in order to obtain all other submatrices.

Similarly to this, Mackay [2] proposed a code construction method, which involves constructing the PCM  ${\bf H}$  on a column-by-column basis, where the columns are generated pseudorandomly with appropriate weight, before being concatenated horizontally. Again, this process must be performed in a recursive manner, so that the row weights can be checked after each column is added. If  $D_c$  has been exceeded for any row, then the current column is regenerated.

3) Quasi-cyclic codes: An LDPC code wherein the cyclic shift of any legitimate codeword permutation by s places to the left or right yields another legitimate codeword permutation is termed Quasi-Cyclic (QC), while the code is termed cyclic in the special case of s = 1. The PCMs of QC codes are semi-structured, based on an upper matrix of elements which each represent an equally-sized square submatrix [32]. If a particular element in the upper matrix has a value of -1, then the corresponding submatrix is a null matrix. Otherwise, the submatrix is an identity matrix, which has been cyclically shifted a number of times according to the corresponding value in the upper matrix [33]. Adopting this structure facilitates low complexity memory addressing and routing for the hardware implementation, since the location of every edge in each submatrix can be determined using only knowledge of the relatively small upper matrix. This advantage can be achieved without incurring a significant sacrifice in error correction performance. Owing to this benefit, QC-LDPC codes are employed by a number of communications

standards, including DVB-S2 [5], IEEE 802.11 (WiFi) [3] and IEEE 802.16 (Mobile WiMAX) [4].

- 4) Repeat-accumulate codes: Repeat-accumulate (RA) codes constitute another type of semi-structured codes. Like QC codes, RA codes benefit from simpler encoding/decoding than random codes, without imposing an unacceptable loss in error correction performance. The PCMs of RA codes are composed of two horizontally-concatenated submatrices  $\mathbf{H}_1$  and  $\mathbf{H}_2$ , where  $\mathbf{H}_2$  is an  $(M \times M)$ -element dual-diagonal matrix. This structure allows each parity bit to be calculated using only the previous parity bit and a subset of the message bits, leading to the accumulation alluded to in the code's name.

- 5) Progressive edge growth algorithm: Whilst not a code structure itself, the Progressive Edge Growth (PEG) algorithm [34] is an important technique of constructing codes having an excellent error correction performance. The operation of the PEG algorithm is VN-centric, focusing on each VN in turn in order to place edges. The algorithm repeatedly constructs a set of CNs as candidates for the VN to connect to. From this set, the subset of nodes having the lowest degree is extracted and one of these is randomly selected. This approach results in LDPC codes that have approximately regular degree distributions.

The PEG algorithm constructs a tree structure, alternating between the connection of VNs to CNs and vice versa. At each stage only nodes that are not already in the tree are considered for inclusion. This process continues until there are no remaining options meeting this constraint. The PEG algorithm then places an edge in the location that is identified as maximising the length of the resultant cycle within the graph, before continuing the algorithm with the selection of a different VN. In this way, a factor graph having no short cycles can be created, yielding a strong error correction performance.

# E. LDPC decoding architectures

The implementation of a practical LDPC decoder is subject to numerous design decisions, such as the degree of parallelism, the representation of the LLRs and the stopping criteria. These three factors are discussed in the following subsections.

1) Parallelism: The inherent parallelism of the belief propagation algorithm facilitates the design of fully-parallel LDPC decoder architectures, in which every VN and CN in the factor graph is implemented separately in hardware [35]. Fullyparallel decoders can achieve very high processing throughputs by performing all of the VN updates and all of the CN updates simultaneously, using the flooding schedule of Fig. 5. However, this is achieved at the cost of excessive hardware resource consumption. For long codes comprising thousands of bits, the inter-node routing may require a greater area than the nodes themselves [36], rendering this architecture impractical for many decoder designs. Additionally, significant further hardware resources are required for implementing flexible routing, using a Beneš network [37], for example. Otherwise, fully-parallel decoders are completely inflexible, only supporting the single code that they are designed for.

By contrast, decoders associated with a fully-serial architecture implement just a single one of each node type in hardware. This hardware is time-multiplexed between the various

nodes of the LDPC decoder, using memories to store interim results [35]. Fully-serial decoders require few hardware resources but suffer from a very low processing throughput, since each decoding iteration could require thousands of clock cycles. However, since all of the factor graph edges are represented by memory addresses, fully-serial decoders can be readily adapted at run-time to implement a different LDPC factor graph, by rearranging the memory accesses.

In order to strike a compromise between the high processing throughput of fully-parallel architectures and the more modest hardware requirement of fully-serial architectures, many LDPC decoders implement a number of time-multiplexed nodes in a so-called partially-parallel fashion. This parametrizable degree of parallelism facilitates control over the tradeoff between processing throughput and hardware resource requirements. Furthermore, this approach is of particular benefit when any structure within the PCM H can be exploited in the configuration of the nodes implemented in hardware. For this reason, QC codes are particularly suited to partially-parallel implementations.

2) Representation of LLRs: Another architectural consideration is the digital representation of the LLRs passed between nodes. The algorithms described earlier can be modified to replace the LLRs with single-bit hard decisions, but this causes them to suffer from a significant error correction performance loss. In general, increasing the resolution and range of the two's complement fixed point LLR representation by using a greater bit width has a positive effect on the error correction performance [38], at the cost of increasing the hardware resources required.

It is therefore desirable for a designer to quantify the effect of the fixed-point bit width on the performance of a chosen decoding algorithm, in order to determine the smallest number of bits that are required in order to achieve a satisfactory error correction performance. This may be achieved using Extrinsic Information Transfer (EXIT) charts [39], which have been conceived by ten Brink for characterising the operation of iterative decoding algorithms. More specifically, EXIT charts visualize the quality of the LLRs output by the VNs and CNs as functions of the quality of the LLRs provided to the corresponding inputs. By plotting these EXIT functions for LDPC decoders employing a range of fixed-point bit widths, a designer can quantify at a glance, how each representation improves or degrades the quality of the LLRs and hence the resultant error correction performance of the LDPC decoder [40]. This eliminates the requirement to run multiple time-consuming BER simulations.

Further to this, some designs have demonstrated that the hardware requirement can be reduced by using non-uniform quantisation schemes [41], by sending the bits of the LLR in a serial fashion rather than in parallel [42], or by utilising stochastic [36] or non-binary [43] number representations. However, these methods can also have adverse effects on the node complexity and the decoding throughput, requiring yet further investigation.

3) Stopping criteria: The design of an LDPC decoder also has to consider how to terminate the decoding process. Commonly, checks are carried out following each decoding

iteration to determine whether the current state of the recovered codeword is a legitimate permutation or not, signalling whether or not decoding has been successful. These checks are performed based on the output of the VNs, as mentioned previously in Section II-C3.

Occasionally however, a received frame is corrupted in such a way that it can never be corrected. In this case, the iterative decoding process would loop infinitely, unless other criteria for stopping it were implemented. Owing to this, a maximum iteration or complexity limit may be imposed. When this limit is reached, the iterative decoding process is terminated and decoding is deemed to have failed. In implementations where a low hardware resource requirement is a greater priority than high processing throughput, the iteration limit may be the only stopping criterion imposed. Here, every received message is decoded using the same number of iterations, without early stopping. In this case, the parity checks are only used at the end of the iterative decoding process, in order to determine whether the recovered codeword is valid or not. Early stopping can also be used to detect that no error correction progress is being made with successive decoding iterations, allowing the decoding process to fail and terminate before the iteration limit is reached.

## F. FPGAs

FPGAs are digital logic devices that can be flexibly programmed to perform a variety of digital functions, using a Hardware Description Language (HDL). Their main advantages are their in-field-programmability, as well as their high-speed very-parallel logic processing. Owing to these benefits, FPGAs are desirable for a multitude of applications, including software-defined radio, ASIC prototyping, digital signal processing, cryptography and computer hardware emulation. This section presents a simplified view of their internal structure, followed by a discussion of the main differences and similarities between different makes and models of FPGAs, and how they may be compared to each other.

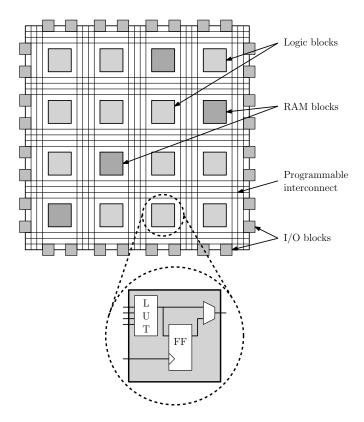

1) Structure: The internal structure of an FPGA typically comprises a variable number of three main programmable elements, namely logic blocks, RAM blocks and I/O blocks [44]. The inputs and outputs of these blocks are linked by programmable routing, as shown in the sample schematic of Fig. 8.

The most fundamental design of a logic block comprises a Lookup Table (LUT) and a Flip-Flop (FF), as shown in Fig. 8. A LUT is a digital structure that can be programmed to perform any combinatorial function of its inputs, thus mimicking any possible combination of logic gates. Typically, FPGA LUTs have 4–6 inputs, which are used to select a value for a single output bit. Increasing the number of LUT inputs typically allows the same HDL design to be implemented using fewer LUTs, therefore reducing the amount of FPGA routing required. However, the hardware resources required by a LUT increase exponentially with its number of input bits, hence very large LUTs are impractical [44]. The output of each LUT can optionally be connected to a corresponding FF, for facilitating synchronous operation. Alternatively, the LUT

Fig. 8. FPGA structure

output can be connected directly to the inter-block routing channels. These channels can be programmed to connect any set of logic block outputs to any set of logic block inputs, subject to the FPGA size constraints.

Instead of logic blocks, some locations within an FPGA structure may contain a RAM block for storing intermediate calculation results. The size of these RAM blocks depends on the particular FPGA being used, as does their access control. More specifically, some FPGAs provide dual-port RAMs, which allow reading and writing to two different locations simultaneously. Some FPGAs may also include additional heterogeneous blocks, such as hardware multipliers and embedded processor cores, alongside non-volatile memory for storing the FPGA configuration when it is turned off [44].

2) FPGA vendor conventions: The two main vendors of FPGAs are Xilinx and Altera. Their respective FPGAs share a number of similarities, but also exhibit some differences. Some Altera FPGAs, such as the first four generations of the Cyclone family, follow the structure outlined above, operating on the basis of so-called "Logic Elements" (LEs), each of which comprises one 4-input Lookup Table (4LUT) and one FF. However, more recent Altera FPGAs are structured around "Adaptive Logic Modules" (ALMs), each of which comprises two FFs and multiple small LUTs. These ALMs also contain extra logic that optionally allows the LUTs to be combined in a variety of ways, offering the functionality of larger LUTs.

By contrast, the logic resources of Xilinx FPGAs are quantified in terms of "slices", each of which contains several LUTs and FFs. The nature and quantity of the hardware resources available within each slice varies depending on the model and

generation of the FPGA. Earlier models of Xilinx FPGAs, such as the Virtex 2, employ a simple slice structure which is based on 4LUTs, while more recent models utilise 6-input Lookup Tables (6LUTs) and a more complex slice structure that allows them to be used in a larger number of configurations.

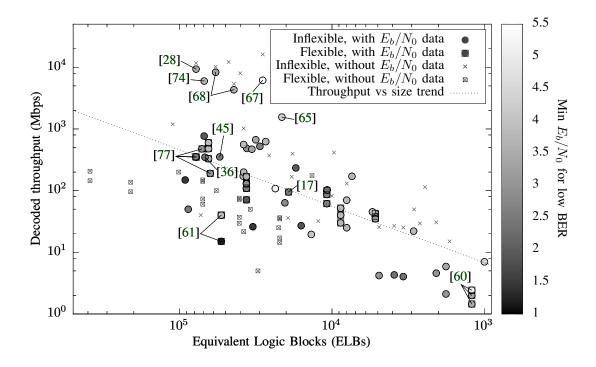

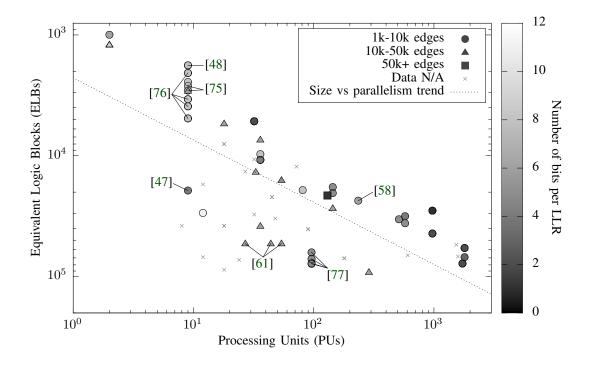

3) Comparing FPGAs: Due to the differences outlined above, comparing the hardware resources employed by the various designs implemented on different FPGAs is not straightforward. To this end, we propose an approximate metric based on the fundamental building blocks of FPGAs, namely the 4LUT and the FF [45]. We refer to this metric as equivalent logic blocks (ELBs), since it attempts to approximate the number of simple logic blocks comprising one 4LUT and one FF that would be required to implement each design. When calculating the number of ELBs, the LUT resources within each Altera ALM are considered to be equal to two 4LUTs, since this is one of the operating modes they offer. Similarly, to compensate for the increased size of 6LUTs compared to 4LUTs, and the additional logic that accompanies 6LUTs within Xilinx slices, each Xilinx 6LUT is considered to be approximately equal to two 4LUTs. Once this has been taken into consideration, we assume that the number of ELBs required by a design is given by the maximum of the number 4LUTs and the number of FFs that it requires.

Table I presents an overview of the main generations and models of FPGAs available from Altera and Xilinx, along with the year of their release and the maximum number of ELBs available within the largest FPGA from each family.

TABLE I: Comparison of FPGAs available from Altera and Xilinx

| Manufacturer | Model     | Year | Technology<br>scale (nm) | Max.<br>ELBs |

|--------------|-----------|------|--------------------------|--------------|

| Xilinx       | Virtex    | 1998 | 220                      | 24,576       |

| Xilinx       | Virtex E  | 1999 | 180                      | 64,896       |

| Xilinx       | Virtex 2  | 2000 | 150                      | 93,184       |

| Altera       | Cyclone   | 2002 | 130                      | 20,060       |

| Altera       | Stratix   | 2002 | 130                      | 79,040       |

| Xilinx       | Spartan 3 | 2003 | 90                       | 66,560       |

| Altera       | Cyclone 2 | 2004 | 90                       | 68,416       |

| Altera       | Stratix 2 | 2004 | 90                       | 143,520      |

| Xilinx       | Virtex 4  | 2004 | 90                       | 178,176      |

| Altera       | Stratix 3 | 2006 | 65                       | 270,000      |

| Xilinx       | Virtex 5  | 2006 | 65                       | 414,720      |

| Altera       | Arria     | 2007 | 90                       | 72,172       |

| Altera       | Cyclone 3 | 2007 | 65                       | 198,464      |

| Altera       | Stratix 4 | 2008 | 40                       | 650,440      |

| Altera       | Cyclone 4 | 2009 | 60                       | 149,760      |

| Altera       | Arria 2   | 2009 | 40                       | 278,800      |

| Xilinx       | Spartan 6 | 2009 | 45                       | 184,304      |

| Xilinx       | Virtex 6  | 2009 | 40                       | 948,480      |

| Altera       | Stratix 5 | 2010 | 28                       | 718,400      |

| Altera       | Cyclone 5 | 2011 | 28                       | 227,120      |

| Altera       | Arria 5   | 2011 | 28                       | 380,480      |

| Xilinx       | Artix 7   | 2011 | 28                       | 269,200      |

| Xilinx       | Kintex 7  | 2011 | 28                       | 597,200      |

| Xilinx       | Virtex 7  | 2011 | 28                       | 1,424,000    |

Note that the proposed ELB metric is by no means perfect, since it does not consider the overhead associated with routing between logic elements or the use of additional FPGA blocks, such as memory or embedded multipliers. However, it does serve as a functional approximation of the hardware requirements associated with each design considered, if they were all implemented on the same FPGA. Measuring the usage only in terms of these fundamental building blocks permits a comparison between modern FPGA models and much older designs, which would not otherwise be possible.

#### III. COMPARISON OF DECODERS

A comprehensive review of published FPGA-based LDPC decoder designs is presented in this section. The analysis of Table II considers both the parameters that are chosen by the designers, as well as the characteristics that may be measured based on the design. Each of these is discussed and characterised in Sections III-A and III-B, together with explanations and discussions of the symbols used in Table II where applicable. The entries in Table II have been sourced from both academic publications and commercially-available soft IP cores. Unfortunately, the licensers of these commercial designs were often unwilling to divulge many of the parameters and characteristics required for this analysis, resulting in several incomplete sets of results. Furthermore, none of the licensers were willing to provide pricing information for the purposes of this survey, preventing the comparison of this interesting but non-technical characteristic of their IP.

Note that Table II presents a condensed version of our findings, showing only the most significant parameters and characteristics. In the case of references that present multiple FPGA-based LDPC decoder designs, only a representative subset has been reproduced here. A full version of our survey results may be downloaded from [46].

## A. Parameters

In this section, we consider the parameters of FPGA-based LDPC decoders, which include all factors of the design that are specified by the designer. These include which LDPC PCMs to support, the decoding algorithm to employ and the number of decoding iterations used. These parameters are discussed in Sections III-A1, III-A3 and III-A4 respectively. Section III-A2 describes the architectural parameters, namely the degree of parallelism, LLR representation, clock frequency, flexibility and choice of FPGA.

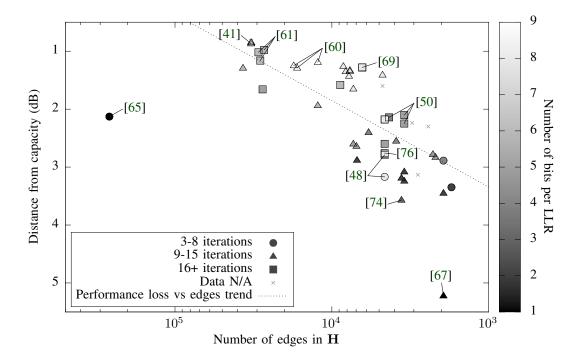

- 1) LDPC PCMs: One of the most fundamental features of an LDPC decoder is the selection of the PCMs that it is designed to support. Decoders may support just one PCM, be tailored to a family of related PCMs or may be designed to be completely flexible. As discussed in Section II-B, each PCM H has a number of parameters, namely  $N, M, D_c$  and  $D_v$ . However, the total number of edges in the corresponding factor graph can be considered to encompass all of these factors, representing the overall size and complexity of the code, as listed in Table II.

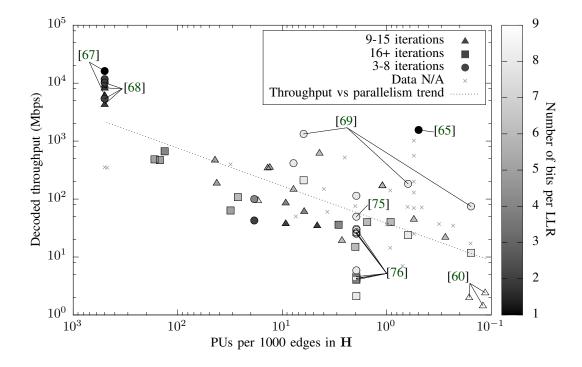

- 2) Architecture: Architectural decisions influence the physical implementation and hardware used by the decoder. As described in Section II-E, the primary architectural parameter

is the degree of parallelism, which may be classified as fully-parallel, partially-parallel or fully-serial. This parameter may be quantified by the total number of Processing Units (PUs) instantiated by the decoder, as listed in Table II. Frequently these processors perform the function of individual VNs and CNs, although some designs use a different approach.

The operand width of the LLR representation, as listed in Table II, is also a measurable parameter, which affects the LDPC decoder's error correction performance. Designs using a higher number of bits may be expected to have superior error correction performance than their counterparts employing fewer bits. However, this is typically achieved at the cost of a larger hardware resource requirement or a lower processing throughput.

The quantisation scheme used in the LLR representation may be either uniform or non-uniform, as denoted by a 'U' or an 'N' in Table II, respectively. In uniform quantisation schemes, the entire range of representable LLR values has a constant resolution, allowing the VN and CN functions to be implemented using straightforward binary arithmetic. By contrast, non-uniform quantisation schemes typically adopt a finer resolution for lower LLR magnitudes and a lower resolution for larger magnitudes. This facilitates a more beneficial trade-off between range and resolution, but makes the associated processing significantly more complex. Many authors (e.g. [42], [47], [48]) mention the number of bits used in their FPGA-based LDPC decoders, but do not detail the quantisation scheme employed. Since non-uniform schemes require significantly more details than uniform representations, these cases are assumed to employ uniform quantisation and are marked with an asterisk in Table II.

The maximum achievable clock frequency of an FPGA-based LDPC decoder depends largely on the capabilities of the FPGA employed, but also on some design decisions such as the critical path length. For example, designs that process entire VNs or CNs in a single clock cycle typically have long critical paths, while designs that only perform one arithmetic or logical operation per clock cycle typically have much shorter critical paths. Based on this observation, the clock frequency is included as a parameter in this analysis. The majority of authors have explicitly stated the clock frequency at which their decoder operates. However, in some cases (eg. [76]) we have derived the clock frequency from other data, as indicated by an asterisk in Table II.

Many decoder architectures are highly optimised to the specific characteristics of the single LDPC PCM that they are designed to support (eg. [43], [62], [74]). By contrast, some other designs instead adopt a more general architecture (eg. [57], [60], [66]), sacrificing performance for the flexibility to switch between several supported PCMs at run-time. A decoder's flexibility may be considered to be both a figure of merit and an architectural decision that is made by the designer, allowing it to be regarded as a characteristic or as a parameter. However, we show in Section IV-A that adding flexibility to a design can only be achieved as a trade-off against some other desirable characteristics. For this reason, we treat flexibility as a characteristic in this paper.

The selection of an FPGA for the implementation of an

TABLE II: Comparison of FPGA LDPC decoders

| Ref.      | H dimensions    | Edges (k) | PUs  | LLR bitwidth | Clock (MHz) | FPGA                | Algorithm                | Iterations | Throughput<br>(decoded bps) | Throughput (encoded bps) | ELBs (k)   | $ m E_b/N_0~(dB)$ | Bandwidth eff. | Run-time<br>flexibility    |

|-----------|-----------------|-----------|------|--------------|-------------|---------------------|--------------------------|------------|-----------------------------|--------------------------|------------|-------------------|----------------|----------------------------|

| [41]      | 1022 x<br>8176  | 32.7      | 36   | N<br>6       | 193         | Xilinx<br>Virtex 2  | Sum-product (modified)   | 15         | 172<br>M                    | 197<br>M*                | 38.3       | 3.78              | 0.<br>88       | None                       |

| [49]      | 4608 x<br>9216  | 27.6      | 54   | U*<br>5      | 56          | Xilinx<br>Virtex E  | -                        | 18         | 27<br>M*                    | 54<br>M                  | 15.9       | 1.85              | 0.<br>50       | None                       |

| [42]      | 125 x<br>480    | -         | 605  | U*<br>3      | 61          | Altera<br>Stratix   | Min-sum<br>(modified)    | 15         | 481<br>M*                   | 650<br>M                 | 66.6       | 4.69              | 0.<br>74       | None                       |

| [50]      | 432 x<br>1440   | 4.32      | 576  | U<br>4       | 138         | Altera<br>Stratix 2 | Min-sum                  | 16<br>**   | 668<br>M**                  | 954<br>M*                | 31.6       | 3.41              | 0.<br>70       | None                       |

| [51]      | 4044 x<br>8088  | -         | 24   | U<br>6       | 44          | Xilinx<br>Virtex 2  | Log-BP                   | 25         | 40<br>M                     | 80<br>M*                 | 72.6       | -                 | 0.<br>50       | None                       |

| [52]      | 1022 x<br>8176  | 32.7      | 18   | -            | 200         | Altera<br>Cyclone 2 | BP-based                 | 18         | 70<br>M                     | 80<br>M*                 | 8.0<br>*   | 3.8               | 0.<br>88       | None                       |

| [52]      | 1022 x<br>8176  | 32.7      | 18   | -            | 200         | Altera<br>Stratix 2 | BP-based                 | 18         | 560<br>M                    | 640<br>M*                | 38.0       | 3.8               | 0.<br>88       | None                       |

| [53]      | 648 x<br>1296   | 3.89      | 36   | U*<br>4      | 128         | Xilinx<br>Virtex 2  | Min-sum                  | 8.4<br>**  | 86.6<br>M**                 | 173<br>M*                | 10.8       | 2.74              | 0.<br>50       | 3 codes in<br>802.11 WiFi  |

| [54]      | 1728 x<br>3200  | -         | 32   | U*<br>5      | 180         | Xilinx<br>Virtex 4  | Turbo decoding algorithm | 10         | 103<br>M*                   | 223<br>M                 | 10.7       | 2.33              | 0.<br>46       | None                       |

| [55]      | 6144 x<br>12288 | 36.9      | 288  | U<br>6       | 96          | Altera<br>Stratix 2 | Min-sum                  | 15         | 149<br>M*                   | 298<br>M                 | 92.0       | 1.48              | 0.<br>50       | None                       |

| [56]      | 576 x<br>1152   | 3.46      | 32   | U<br>2       | 64          | Xilinx<br>Virtex 2  | Min-sum<br>(modified)    | 8.5<br>**  | 38<br>M**                   | 76.1<br>M*               | 5.2        | 3.27              | 0.<br>50       | 3 codes in<br>802.16 WiMAX |

| [45]      | 512 x<br>1024   | 3.07      | 1536 | NA           | 212         | Xilinx<br>Virtex 4  | Stochastic               | NA         | 353<br>M*                   | 706<br>M                 | 54.5<br>** | 2.43              | 0.<br>50       | None                       |

| [28]<br>T | 1022 x<br>8176  | 3.46      | 1728 | U<br>2       | 138         | Xilinx<br>Virtex 5  | Min-sum<br>(modified)    | 6.8        | 11.7<br>G                   | 23.4<br>G*               | 78.0<br>*  | -                 | 0.<br>50       | None                       |

| [28]<br>E | 1022 x<br>8176  | 3.46      | 1728 | U<br>2       | 138         | Xilinx<br>Virtex 5  | Min-sum<br>(modified)    | 8.5<br>**  | 9.35<br>G**                 | 18.7<br><b>G</b> *       | 78.0<br>*  | 3.43              | 0.<br>50       | None                       |

| [57]      | -               | -         | 8    | U*<br>6      | 160         | Xilinx<br>Virtex 5  | -                        | 20         | 21.6<br>M                   | 25.9<br>M*               | 38.0       | -                 | 0.<br>83       | Complete<br>802.16 WiMAX   |

| [58]      | 188 x<br>2209   | 8.84      | 235  | U*<br>6      | 50          | Altera<br>Stratix   | Min-sum (modified)       | 20         | 108<br>M*                   | 118<br>M                 | 23.5       | 5.12              | 0.<br>92       | None                       |

| [59]      | 1552 x<br>3104  | -         | 48   | N<br>6       | 98          | Altera<br>Cyclone 2 | Belief<br>propagation    | 30         | 26<br>M*                    | 52<br>M                  | 33.0       | 1.48              | 0.<br>50       | None                       |

| [60]      | 731 x<br>4161   | 16.6      | 2    | U<br>9       | -           | Xilinx<br>Virtex 2P | Min-sum with correction  | 10         | l N                         | 45<br>И                  | 1.2        | 3.52<br>**        | 0.<br>82       | Any code                   |

| [61]      | 4158 x<br>9036  | 27        | 54   | U<br>6       | 100         | Xilinx<br>Virtex 2  | Min-sum with correction  | 60<br>*    | 15<br>M                     | 30<br>M*                 | 53.3       | 1.17              | 0.<br>50       | 3 custom codes             |

| [17]      | 768 x<br>1536   | 4.61      | 144  | U<br>5       | 211         | Xilinx<br>Virtex 4  | Min-sum<br>with scaling  | ı          | 397<br>M                    | 794<br>M*                | 18.2       | ı                 | 0.<br>50       | None                       |

| [17]      | 432 x<br>1296   | 4.75      | 81   | U<br>8       | 160         | Xilinx<br>Virtex 4  | Min-sum with correction  | 15<br>*    | 95<br>M                     | 143<br>M*                | 19.3       | 2.49              | 0.<br>67       | Complete<br>802.11 WiFi    |

| [62]      | 2304 x<br>1152  | -         | 12   | U*<br>7      | 155         | Altera<br>Stratix 2 | Min-sum                  | 8          | 233<br>M                    | 465<br>M*                | 17.3       | 1.94              | 0.<br>50       | None                       |

| [62]      | 2304 x<br>1152  | -         | 12   | U*<br>7      | 128         | Altera<br>Stratix 2 | Min-sum                  | 8          | 768<br>M                    | 1.54<br>G*               | 69.1<br>*  | 1.94              | 0.<br>50       | None                       |

| [63]      | 3048 x<br>6096  | -         | 72   | -            | 64          | Xilinx<br>Virtex E  | -                        | 24         | 32<br>M*                    | 64<br>M                  | 12.3       | -                 | 0.<br>50       | None                       |

| [64]      | 3600 x<br>16200 | 45        | 45   | -            | 70.8        | Xilinx<br>Virtex 2P | Min-sum<br>with scaling  | 15<br>*    | 36.3<br>M*                  | 46.7<br>M                | 22.0       | -                 | 0.<br>78       | Complete<br>DVB-S2         |

| [64]      | 3600 x<br>16200 | 45        | 180  | -            | 73.2        | Xilinx<br>Virtex 2P | Min-sum<br>with scaling  | 15<br>*    | 149<br>M*                   | 191<br>M                 | 70.6<br>*  | -                 | 0.<br>78       | Complete<br>DVB-S2         |

| [47]      | 519 x<br>1038   | 3.11      | 9    | U*<br>4      | 26.3        | Xilinx<br>Virtex E  | -                        | 18         | 36<br>M*                    | 72<br>M                  | 19.4<br>*  | -                 | 0.<br>50       | None                       |

| [65]      | 4095 x<br>4095  | 262       | 130  | U<br>1       | 191         | Xilinx<br>Virtex E  | Soft majority logic      | 5          | 1.56<br>G*                  | 1.9<br>G                 | 21.3       | 4.36              | 0.<br>82       | None                       |

| [66]      | -               | -         | 32   | U<br>8       | 74          | Xilinx<br>Virtex 4  | Normalized<br>BP-based   | 15         | 5<br>M**                    | 10<br>M*                 | 30.6       | -                 | 0.<br>50       | Any code                   |

TABLE II: Comparison of FPGA LDPC decoders (continued...)

| Ref.      | H dimensions   | Edges (k) | PUs  | LLR bitwidth | Clock (MHz) | FPGA                | Algorithm                 | Iterations | Throughput<br>(decoded bps) | Throughput (encoded bps) | ELBs (k)  | $ m E_b/N_0$ (dB) | Bandwidth eff. | Run-time<br>flexibility |

|-----------|----------------|-----------|------|--------------|-------------|---------------------|---------------------------|------------|-----------------------------|--------------------------|-----------|-------------------|----------------|-------------------------|

| [67]<br>T | 324 x<br>648   | 1.94      | 972  | U<br>1       | 188         | Xilinx<br>Virtex 5  | Simplified<br>MP          | 3.8        | 16.2<br>G                   | 32.4<br>G*               | 28.5      | -                 | 0.<br>50       | None                    |

| [67]<br>E | 324 x<br>648   | 1.94      | 972  | U<br>1       | 188         | Xilinx<br>Virtex 5  | Simplified<br>MP          | 10         | 6.16<br>G**                 | 12.3<br>G*               | 28.5      | 5.41              | 0.<br>50       | None                    |

| [68]      | 600 x<br>1200  | 3.6       | 1800 | U<br>2       | 123         | Xilinx<br>Virtex 4  | Min-sum<br>(modified)     | 8.9        | 8.3<br>G**                  | 16.6<br>G*               | 58.1      | 3.38              | 0.<br>50       | None                    |

| [68]      | 324 x<br>648   | 1.94      | 972  | U<br>2       | 113         | Xilinx<br>Virtex 5  | Min-sum<br>(modified)     | 8.4        | 4.33<br>G**                 | 8.67<br>G*               | 44.0      | 3.64              | 0.<br>50       | None                    |

| [69]<br>T | 640 x<br>1920  | 6.4       | 40   | U<br>8       | 150         | Xilinx<br>Virtex 4  | Joint<br>row-column       | 8          | 1.33<br>G*                  | 2<br>G                   | -         | -                 | 0.<br>66       | None                    |

| [69]<br>E | 640 x<br>1920  | 6.4       | 40   | U<br>8       | 150         | Xilinx<br>Virtex 4  | Joint<br>row-column       | 50         | 211<br>M*                   | 320<br>M**               | -         | 2.29              | 0.<br>66       | None                    |

| [69]<br>T | 640 x<br>1920  | 6.4       | 1    | U<br>8       | 300         | Xilinx<br>Virtex 4  | Joint row-column          | 8          | 74.6<br>M*                  | 112<br>M                 | -         | -                 | 0.<br>66       | None                    |

| [69]<br>E | 640 x<br>1920  | 6.4       | 1    | U<br>8       | 300         | Xilinx<br>Virtex 4  | Joint<br>row-column       | 50         | 11.8<br>M*                  | 17.9<br>M**              | -         | 2.29              | 0.<br>66       | None                    |

| [43]      | 486 x<br>972   | 2.43      | 18   | -            | 131         | Xilinx<br>Virtex 4  | Min-sum<br>(nonbinary)    | 20         | l N                         | 0<br>M                   | 87.8<br>* | 2.49              | 0.<br>50       | None                    |

| [70]      | -              | -         | 27   | U<br>8       | 100         | Altera<br>Cyclone 2 | Min-sum<br>(modified)     | -          | 175<br>M*                   | 350<br>M                 | 13.5      | -                 | 0.<br>50       | Within code families    |

| [36]      | 528 x<br>1056  | 3.34      | 1584 | NA           | 222         | Xilinx<br>Virtex 4  | Stochastic                | NA         | 348<br>M*                   | 697<br>M**               | 68.2      | 2.45              | 0.<br>50       | None                    |

| [71]      | 1022 x<br>8176 | 4.75      | 12   | U<br>11      | 228         | Xilinx<br>Virtex 5  | Sum-product<br>(modified) | -          | l N                         | 22<br>M                  | 29.7      | 2.61              | 0.<br>66       | None                    |

| [72]      | 384 x<br>2048  | 12.3      | 33   | U<br>6       | 100         | Xilinx<br>Virtex 2P | Message passing           | 10         | 19.5<br>M*                  | 24<br>M**                | 13.7      | 4.07<br>***       | 0.<br>81       | None                    |

| [73]      | 768 x<br>1536  | 4.61      | 9    | U<br>8       | 162         | Xilinx<br>Virtex 2  | Min-sum                   | 3          | 114<br>M*                   | 229<br>M                 | 2.4       | -                 | 0.<br>50       | None                    |

| [73]      | 756 x<br>3969  | 16.8      | -    | U<br>6       | 200         | Xilinx<br>Virtex 4  | Normalized<br>min-sum     | 15         | 82.4<br>M*                  | 102<br>M                 | 10.0      | -                 | 0.<br>81       | None                    |

| [73]      | 1022 x<br>8176 | 32.7      | 144  | U<br>6       | 212         | Xilinx<br>Virtex 4  | Normalized<br>min-sum     | 15         | 625<br>M*                   | 714<br>M                 | 27.2      | 3.76              | 0.<br>88       | None                    |

| [74]      | 600 x<br>1200  | 3.6       | 1800 | U<br>3       | 100         | Xilinx<br>Virtex 4  | Min-sum                   | 10         | 6<br>G                      | 12<br>G*                 | 69.0      | 3.76              | 0.<br>50       | None                    |

| [75]      | 768 x<br>1536  | 4.61      | 9    | U<br>8       | 149         | Xilinx<br>Virtex 2  | Min-sum                   | 3          | 49.6<br>M*                  | 99.1<br>M                | 2.9       | -                 | 0.<br>50       | None                    |

| [48]      | 768 x<br>1536  | 4.61      | 9    | U*<br>8      | 100         | Xilinx<br>Virtex 2  | Min-sum                   | 7          | 5.88<br>M*                  | 11.8<br>M**              | 1.8       | 3.36              | 0.<br>50       | None                    |

| [76]      | 768 x<br>1536  | 4.61      | 9    | U<br>8       | 84<br>*     | Xilinx<br>Virtex 2  | Sum-product<br>(modified) | 20         | 4.3<br>M*                   | 8.59<br>M**              | 3.9       | 2.37              | 0.<br>50       | None                    |

| [76]      | 768 x<br>1536  | 4.61      | 9    | U<br>8       | 79.1        | Xilinx<br>Virtex 2  | Sum-product<br>(modified) | 20         | 4.04<br>M*                  | 8.08<br>M**              | 3.4       | 2.37              | 0.<br>50       | None                    |

| [76]      | 768 x<br>1536  | 4.61      | 9    | N<br>8       | 80.5        | Xilinx<br>Virtex 2  | Sum-product<br>(modified) | 20         | 4.21<br>M*                  | 8.42<br>M**              | 4.9       | 2.96              | 0.<br>50       | None                    |

| [77]      | 336 x<br>672   | 2.18      | 96   | U<br>5       | 100         | Xilinx<br>Virtex 5  | Min-sum with correction   | 10         | 475<br>M*                   | 950<br>M                 | 71.4      | 3.02              | 0.<br>50       | Within code families    |

| [78]      | -              | -         | -    | U*<br>4      | 27          | Xilinx<br>Virtex E  | -                         | -          | l N                         | 5<br>M                   | 1.7       | -                 | -              | None                    |

| [79]      | 768 x<br>1536  | 4.61      | 144  | U<br>5       | 121         | Xilinx<br>Virtex 2  | Min-sum<br>(modified)     | 20         | 63.5<br>M*                  | 127<br>M                 | 20.4      | 2.79              | 0.<br>50       | None                    |

| [80]      | 298 x<br>980   | 2.83      | 2    | U<br>6       | 136         | Altera<br>Cyclone   | Improved<br>BP            | -          | l N                         | 7<br><b>M</b>            | 1.0       | 4.4<br>**         | 0.<br>70       | None                    |

| [81]      | -              | -         | -    | -            | 140         | Xilinx<br>Virtex 5  | Min-sum                   | -          | l N                         | 06<br>M                  | 210       | -                 | 0.<br>67       | Complete<br>DVB-S2      |

| [81]      | -              | -         | -    | -            | 140         | Xilinx<br>Virtex 5  | Min-sum                   | -          | l N                         | 06<br>И                  | 388       | -                 | 0.<br>25       | Complete<br>DVB-S2      |

| [82]      | -              | -         | -    | U*<br>9      | 180         | Xilinx<br>Virtex 5  | Min-sum with correction   | 5          | 600<br>M                    | -                        | 64.6      | 3.84              | -              | Complete<br>CCSDS-C2    |

| Ref. | H dimensions    | Edges (k) | PUs | LLR bitwidth | Clock (MHz) | FPGA                | Algorithm               | Iterations | Throughput<br>(decoded bps) | Throughput<br>(encoded bps) | ELBs (k)   | $\rm E_b/N_0~(dB)$ | Bandwidth eff. | Run-time<br>flexibility    |

|------|-----------------|-----------|-----|--------------|-------------|---------------------|-------------------------|------------|-----------------------------|-----------------------------|------------|--------------------|----------------|----------------------------|

| [82] | -               | -         | -   | U*<br>9      | 150         | Altera<br>Stratix 2 | Min-sum with correction | 12         | 30<br>M                     | -                           | 8.8<br>**  | 3.71               | -              | Complete<br>CCSDS-C2       |