Design, Automation, and Test in Europe

The Most Influential Papers of 10 Years DATE

Rudy Lauwereins • Jan Madsen Editors

# Design, Automation, and Test in Europe

The Most Influential Papers of 10 Years DATE

Rudy Lauwereins IMEC vzw and Katholieke Universiteit Leuven Belgium Jan Madsen

Informatics and Mathematical

Modelling

Technical University of Denmark

Denmark

ISBN 978-1-4020-6487-6

e-ISBN 978-1-4020-6488-3

Library of Congress Control Number: 2007939398

#### © 2008 Springer Science + Business Media B.V.

No part of this work may be reproduced, stored in a retrieval system, or transmitted in any form or by any means, electronic, mechanical, photocopying, microfilming, recording or otherwise, without written permission from the Publisher, with the exception of any material supplied specifically for the purpose of being entered and executed on a computer system, for exclusive use by the purchaser of the work.

Printed on acid-free paper

9 8 7 6 5 4 3 2 1

springer.com

### Introduction

The Design Automation and Test in Europe, DATE, is Europe's leading international electronic systems design conference for electronic design, automation and test, from system level hardware and software implementation right down to integrated circuit design. It combines the conference with Europe's leading international exhibition for electronic design, automation and test.

To celebrate the tenth anniversary of DATE, we have compiled this book with the aim to highlight some of the most influential technical contributions from ten years of DATE. Selecting 30 papers, only 3 papers from each year, is a challenging endeavor. Although the impact of papers from the first years of DATE can be determined through various citation indexes, the impact from the later years still have to be seen. Together with all 10 Program Chairs, we have made a selection of the most influential papers covering the very broad range of topics which is characteristic for DATE.

#### Ten Years of DATE

DATE was formed in 1998 on the basis of two previous European conferences: The European Design & Test Conference (ED&TC) and EuroDAC. DATE inherited many of the structures and procedures from the ED&TC conference and from the EDAC exhibition. DATE inherited from ED&TC for example the particular style of the very big Technical Program Committee, which meets every year to put together the final technical program in one intensive day with the size of a small conference on itself. DATE has been alternating between Paris in France and Munich in Germany and since 2007 between Nice, France and Munich.

DATE has grown into a truly international event with paper submissions and participation from all over the globe. DATE has grown from 3 parallel tracks to the currently 7 tracks. From the very beginning, DATE has aimed at being a technical conference of high quality combined with a large exhibition. This is documented not only through the continuing increase of number of submissions and participants, but more importantly through an acceptance rate around 25% and close to 5 reviews per paper.

vi Introduction

One of the characteristics of DATE is its continuous innovation, i.e. DATE is constantly exploring new formats, such as Hands-on-Tutorials, Friday workshops, Executive Tracks, and Exhibition Programs. Successful experiments may turn into permanent conference events, such as the Embedded Software Forum. Introduced in 2003 to attract more software people, it was merged into a full Embedded Software track in 2005 with its own set of topics and subTPCs. Many of these innovations have been taken up or copied by other conferences.

Since its beginning, DATE has aimed at not only being the primary event for the researcher, but also for actual designers of chips and systems. Hence, DATE adopted the Designers Forum from ED&TC. The Designers Forum has grown from a parallel event with mainly invited contributions to a full integration within DATE, forming one out of four major areas: **D**esign methods and tools, **A**pplication designs, **T**est and verification and **E**mbedded software.

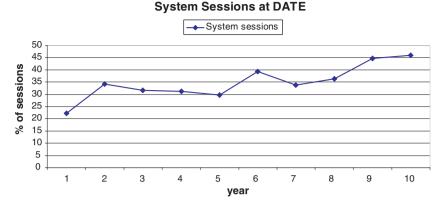

DATE covers not only chip-level topics, but also system-level design issues. It was an early decision to go system, and as can be seen from the graph below, the number of sessions dealing with system issues has grown in relative terms from 22% to close to 50% without reducing the chip-level design contributions in absolute numbers. The DATE steering group facilitated this move to system level by actively organizing special sessions, keynotes and special focus topic days highlighting various aspects related to systems applications, design and design technology. This has been instrumental in the effort to create a conference with a clear trend toward a holistic view on design, test and embedded software and a comprehensive system design focus.

#### How the Book was Formed

With more than 200 papers published every year over the last 10 years, selecting the 30 papers with the biggest impact has been a daunting task. Each of the 10 program chairs have been asked to provide a ranked list with around 6 papers from their respective years. For your reference and to acknowledge that they were nominated as candidates for the most influential papers of DATE, they are listed in the appendix at the end of this book. For the oldest years, selection has been mainly based on the number of citations these papers received over the years. For the more recent years, best paper awards and review evaluation figures have been taken into account as well. Needless to say that any selection will miss influential papers. We hence do not claim any completeness of the picture sketched in this book. Nevertheless, we are convinced it presents a fairly balanced view of the historical evolution of the design technology domain.

We then reduced this pre-selection of around 60 papers down to the final list of 30 papers, strictly 3 per year, which appear in this book. Apart from the priority ranking made by the respective program chairs, we used fair coverage of the various domains as a selection criterion. Those papers have been organized in 6 parts:

Introduction vii

Fig. 1 Relative evolution of the number of sessions allocated to system level design

- System Level Design

- Networks on Chip

- Modeling, Simulation and Run-Time Management

- Digital Technology for Advanced Digital Systems in CMOS and Beyond

- Physical Design and Validation

- Test and Verification

We then invited the winners of the prestigious EDAA Lifetime Achievement Award as well as some other recognized experts in their field to write an introduction to a section, summarizing the history in their domain and indicating how the selected DATE papers contributed to it.

We hope that you will enjoy reading the book as much as we enjoyed organizing DATE and preparing this book. We will like to explicitly thank the program chairs;

Prof. Dr. Franz Ramig, Program Chair 1998

Prof. Dominique Borionne, Program Chair 1999

Prof. Dr. Peter Marwedel, Program Chair 2000

Prof. Dr.-lng. Wolfgang Nebel, Program Chair 2001

Prof. Carlos Delgado Kloos, Program Chair 2002

Prof. Dr.-lng. Norbert Wehn, Program Chair 2003

Prof. Georges Gielen, Program Chair 2004

Prof. Luca Benini, Program Chair 2005

Prof. Donatella Sciuto, Program Chair 2006

We will also like to thank the experts who wrote the introductions, the authors of the selected papers and all attendees of the DATE conferences for their contribution and continued support of our community.

## **Contents**

| Introduction                                                                                                                                                     | V   |

|------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|

| Part I System Level Design                                                                                                                                       |     |

| System Level Design: Past, Present, and Future  D. D. Gajski                                                                                                     | 3   |

| Scheduling of Conditional Process Graphs for the Synthesis of Embedded Systems                                                                                   | 15  |

| EXPRESSION: A Language for Architecture Exploration Through Compiler/Simulator Retargetability A. Halambi, P. Grun, V. Ganesh, A. Khare, N. Dutt, and A. Nicolau | 31  |

| RTOS Modeling for System Level Design                                                                                                                            | 47  |

| Context-Aware Performance Analysis for Efficient Embedded System Design                                                                                          | 59  |

| Lock-Free Synchronization for Dynamic Embedded Real-Time Systems                                                                                                 | 73  |

| What If You Could Design Tomorrow's System Today?                                                                                                                | 87  |

| Part II Networks on Chip                                                                                                                                         |     |

| Networks on Chips                                                                                                                                                | 105 |

x Contents

| A Generic Architecture for On-Chip Packet-Switched Interconnections                                                                                                                                                     | 111 |

|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|

| Trade-offs in the Design of a Router with Both Guaranteed and Best-Effort Services for Networks on Chip.  E. Rijpkema, K. G. W. Goossens, A. Rădulescu, J. Dielissen, J. van Meerbergen, P. Wielage, and E. Waterlander | 125 |

| Exploiting the Routing Flexibility for Energy/Performance-Aware Mapping of Regular NoC Architectures                                                                                                                    | 141 |

| ×pipesCompiler: A Tool for Instantiating Application- Specific Networks on Chip                                                                                                                                         | 157 |

| A Network Traffic Generator Model for Fast Network-on-Chip                                                                                                                                                              |     |

| Simulation.  S. Mahadevan, F. Angiolini, J. Sparsø, M. Storgaard, J. Madsen, and R. G. Olsen                                                                                                                            | 173 |

| Part III Modeling, Simulation and Run-Time Management                                                                                                                                                                   |     |

| Modeling, Simulation and Run-Time Management                                                                                                                                                                            | 187 |

| <b>Dynamic Power Management for Nonstationary Service Requests</b> EY. Chung, L. Benini, A. Bogliolo, and G. De Micheli                                                                                                 | 195 |

| Quantitative Comparison of Power Management Algorithms YH. Lu, EY. Chung, T. Šimunić, L. Benini, and G. De Micheli                                                                                                      | 207 |

| Energy Efficiency of the IEEE 802.15.4 Standard in Dense Wireless Microsensor Networks: Modeling and Improvement Perspectives B. Bougard, F. Catthoor, D. C. Daly, A. Chandrakasan, and W. Dehaene                      | 221 |

| Statistical Blockade: A Novel Method for Very Fast Monte Carlo Simulation of Rare Circuit Events, and its Application                                                                                                   | 235 |

| Compositional Specification of Behavioral Semantics                                                                                                                                                                     | 253 |

| Part IV Design Technology For Advanced Digital Systems in CMOS and Beyond                                                                                                                                               |     |

| Design Technology for Advanced Digital Systems in CMOS and Beyond                                                                                                                                                       | 269 |

Contents xi

| Address Bus Encoding Techniques for System-Level Power Optimization                                  |

|------------------------------------------------------------------------------------------------------|

| L. Benini, G. De Micheli, E. Macii, D. Sciuto, and C. Silvano                                        |

| MOCSYN: Multiobjective Core-Based Single-Chip System Synthesis                                       |

| Minimum Energy Fixed-Priority Scheduling for Variable Voltage Processors                             |

| Synthesis and Optimization of Threshold Logic Networks with Application to Nanotechnologies          |

| Part V Physical Design and Validation                                                                |

| Physical Design and Validation. 347 J. A. G. Jess                                                    |

| Interconnect Tuning Strategies for High-Performance ICs                                              |

| Efficient Inductance Extraction via Windowing                                                        |

| Soft-Error Tolerance Analysis and Optimization of Nanometer Circuits                                 |

| A Single Photon Avalanche Diode Array Fabricated in Deep-Submicron CMOS Technology                   |

| Part VI Test and Verification                                                                        |

| The Test and Verification Influential Papers in the 10 Years of DATE                                 |

| •                                                                                                    |

| Cost Reduction and Evaluation of a Temporary Faults-Detecting Technique                              |

| An Integrated System-on-Chip Test Framework                                                          |

| Efficient Spectral Techniques for Sequential ATPG A. Giani, S. Sheng, M. S. Hsiao, and V. D. Agrawal |

xii Contents

| BerkMin: A Fast and Robust Sat-Solver                                                                                        | 465 |

|------------------------------------------------------------------------------------------------------------------------------|-----|

| Improving Compression Ratio, Area Overhead, and Test Application Time for System-on-Chip Test Data Compression/Decompression | 479 |

| An Effective Technique for Minimizing the Cost of Processor Software-Based Diagnosis in SoCs                                 | 497 |

| Appendix Shortlist of Most Influential Papers                                                                                | 511 |