# Hybrid Reduction Technique for Efficient Simulation of Linear/Nonlinear Mixed Circuits

Takashi MINE<sup>1</sup>, Hidemasa KUBOTA<sup>1</sup>, Atsushi KAMO<sup>2</sup>, Takayuki WATANABE<sup>3</sup>, and Hideki ASAI<sup>1</sup>

<sup>1</sup>Department of Systems Engineering, Faculty of Engineering, Shizuoka University,

3-5-1, Johoku, Hamamatsu-shi, 432-8561, Japan. E-mail: hideasai@sys.eng.shizuoka.ac.jp

<sup>2</sup>Sony LSI Design Inc. Gohdo-cho134, Hodogaya-ku, Yokohama, Kanagawa 240-0005, Japan.

<sup>3</sup>School of Administration and Informatics, University of Shizuoka, 52-1, Yada, Shizuoka-shi, 422-8526, Japan. E-mail: watanat@u-shizuoka-ken.ac.jp

### Abstract

In this paper, we propose a new method which makes transient simulation faster for the circuit including both nonlinear and linear elements. First, the method for generating the projection matrix with Krylov-subspace technique is described. The order of the circuit equation is reduced by congruence transformation with the projection matrix. Next, we suggest a method which can calculate the reduced Jacobian matrix directly in the each Newton-Raphson iteration. Since this technique does not need to calculate the original size of Jacobian matrix, the calculation cost is reduced drastically. Therefore, efficient circuit simulation can be achieved. Finally, our method is applied to some example circuits and the validity of the nonlinear circuit reduction technique is verified.

## 1. Introduction

With the progress of VLSI and PWB technologies, the LSIs and PCBs embedded in the electrical articles are required to have high-density and high-reliability. Therefore, they are designed with smaller devices, higher clock speeds, lower power consumption, and more integration of analog and digital circuits. As a result, interconnect effects such as signal delay, reflection, and crosstalk can severely degrade the signal integrity. In order to analyze these influences in detail, the method which can model interconnects and substrate with lumped elements has been widely used for the verification of circuit behaviors. However, it leads to increase the order of the circuit equation. As a result, conventional circuit simulator, such as SPICE, requires so much calculation time. One of the methods which reduces the calculation cost is the circuit reduction technique. For example, a number of model order reduction techniques, such as AWE (Asymptotic Waveform Evaluation)[1], PACT(Pole Analysis via Congruence Transformations)[2], and PRIMA (Passive Reduced-Order Interconnect Macromodeling Algorithm)[3], have been proposed. These methods make the circuit simulation faster, but, can be applied to only the linear networks such as interconnects and need to separate the nonlinear subnetworks from the given network[1]-[7].

Then nonlinear reduction techniques have been proposed[8]-[11]. In these methods, the order of the circuit equation is reduced by congruence transformation with the projection matrix without dividing nonlinear and linear elements. But, the methods[8], [10] can be applied only to the circuit which has a capacitor at every node.

In this paper, we propose a new nonlinear reduction technique for the rapid transient simulation of the circuit including both nonlinear and linear elements. The main idea which reduces the calculation cost drastically is generating a reduced Jacobian matrix directly. In order to perform accurate analysis, the proposed method remodels the projection matrix at each time point in the simulation. In our method can generate the projection matrices at low calculation cost.

Finally, our method is applied to some example circuits including linear and nonlinear elements and the validity of the proposed method is verified.

# 2. Generating the Reduced Model

In general, the modified nodal analysis(MNA) formulation of a given network can be represented as

$$f(\mathbf{x}) = \mathbf{C}\,\dot{\mathbf{x}} + \mathbf{G}\,\mathbf{x} + \mathbf{H}\,(\mathbf{x}) + \mathbf{b}\,(t) = 0\,, \qquad (1)$$

where  $\mathbf{x} \in \mathbb{R}^N$  is the unknown variable vector which consists of voltages and currents in the circuit,  $C \in \mathbb{R}^{N \times N}$ is the matrix which is constructed by capacitances and inductances,  $G \in \mathbb{R}^{N \times N}$  is the matrix which is constructed by conductances,  $H(\mathbf{x}) \in \mathbb{R}^N$  is the function describing the nonlinear characteristics of circuit,  $b(t) \in \mathbb{R}^N$  is the independent source vector, and *N* is the order of the circuit equation.

In order to generate the projection matrix, (1) is transformed by backward Euler method as

$$C \frac{\mathbf{x}^{i} - \mathbf{x}^{i-1}}{\Delta t} + G \mathbf{x}^{i} + H\left(\mathbf{x}^{i}\right) + b\left(t_{i}\right) = 0, \qquad (2)$$

where  $\Delta t$  is the step size used in the simulation and  $x_i$  is the unknown vector at the *i*th time point. From (2),

$$\left(\frac{C}{\Delta t} + G\right) \mathbf{x}^{i} = -\left\{ \mathbf{H}\left(\mathbf{x}^{i}\right) + \mathbf{b}\left(t_{i}\right) - \frac{C}{\Delta t} \mathbf{x}^{i-1} \right\}$$

(3)

is derived. Next,  $\mathbf{x}(t)$  is expanded as a Maclaurin series with respect to t as

$$\mathbf{x}(t) = \sum_{k=0}^{\infty} a_k t^k , \qquad (4)$$

where  $a_k = x^{(k)}(0)/k!$ ,  $k = 0, 1, 2, \cdots$  are the normalized time domain derivatives of x and are computed using

$$\left(\frac{C}{\Delta t}+G\right)a_{k}^{i}=-\left\{\boldsymbol{h}_{k}^{i}+\boldsymbol{b}_{k}^{i}-\frac{C}{\Delta t}a_{k}^{i-1}\right\},$$

(5)

where  $\boldsymbol{b}_k$  and  $\boldsymbol{h}_k$  denote the  $k^{th}$  derivatives of  $\boldsymbol{b}(t)$  and  $\boldsymbol{H}(\boldsymbol{x})$  respectively and  $\boldsymbol{a}_0$  is decided by the initial value which is obtained in DC analysis. The  $k^{th}$  derivative of  $\boldsymbol{H}(\boldsymbol{x})$ ,  $\boldsymbol{h}_k$  is computed as

$$\boldsymbol{h}_{k} = \sum_{j=0}^{k-1} \frac{(j+1)}{(k-j-1)!k} \left[ \boldsymbol{\xi}^{k-j-1}(0) \right] \boldsymbol{a}_{j+1}$$

(6)

[8], [10]. From (6), it is clear that  $a_k^i$  is needed for calculation of  $h_k^i$ . As an example of the calculation of the derivative, consider

$$H(x) = \exp(x). \tag{7}$$

Expansion of the exponential function gives

$$\boldsymbol{h}_{0} = \exp(\boldsymbol{a}_{0})$$

$$\boldsymbol{h}_{k} = \left(\frac{1}{k}\right) \sum_{i=0}^{k-1} \boldsymbol{h}_{i} \, \boldsymbol{a}_{k-i} \left(k-i\right).$$

(8)

$a_k^i$  in (5) is given by

$$\left(\frac{\boldsymbol{C}}{\Delta t} + \boldsymbol{G} + \boldsymbol{h}_{0}^{i}\right)\boldsymbol{a}_{k}^{i} = -\left\{\boldsymbol{h}_{k}^{i'} + \boldsymbol{b}_{k}^{i} - \frac{\boldsymbol{C}}{\Delta t}\boldsymbol{a}_{k}^{i-1}\right\},\qquad(9)$$

where  $\mathbf{h}_{k}^{i} = \mathbf{h}_{0}^{i} + \mathbf{h}_{k}^{i'}$ . This means that the left-hand side in (9) does not stay constant at each time point in the simulation.

Then, we propose a technique of approximating  $h_k^i$  in (5).  $h_k^i$  is approximated by  $h_k^{i-1}$ . Consequently, (5) becomes as follows

$$\left(\frac{C}{\Delta t}+G\right)\boldsymbol{a}_{k}^{i}=-\left\{\boldsymbol{h}_{k}^{i-1}+\boldsymbol{b}_{k}^{i}-\frac{C}{\Delta t}\boldsymbol{a}_{k}^{i-1}\right\}.$$

(10)

Since the left-hand side in (10) is constructed by linear elements, the coefficient matrix in the left-hand side is constant through the transient simulation and always invertible. Therefore, it is noted that computing  $a_k^i$  requires only once LU decomposition of the left-hand side matrix in (10). Then, forward/backward substitutions are performed at each time point in the simulation.

The Krylov-subspace K is formed by the derivatives computed in (10).

$$\boldsymbol{K} = \begin{bmatrix} \boldsymbol{a}_0 \ \boldsymbol{a}_1 \cdots \boldsymbol{a}_{q-1} \end{bmatrix} \quad : \quad \boldsymbol{K} \in \mathfrak{R}^{\dim \times q} \quad , \tag{11}$$

where  $q(\ll N)$  is the reduced order which is determined arbitrarily. In order to improve the accuracy of reduced model, an orthogonal decomposition on **K** is performed[3]. However, orthonormalization of  $a_0$  is performed after orthonormalization of  $a_{q-1}$ . As a result, orthonormalized matrix **Q** is obtained by

$$\boldsymbol{K} = \boldsymbol{Q}\boldsymbol{R} \quad : \quad \boldsymbol{Q} \in \mathfrak{R}^{\dim \times q}, \boldsymbol{R} \in \mathfrak{R}^{q \times q}$$

(12)

as the projection matrix, where  $Q^T Q = U_q$  and  $U_q \in \Re^{q \times q}$ is an identity matrix. Using the projection matrix Q, x in (1) is transformed by the congruence transformation as

$$\mathbf{x} = \mathbf{Q}\,\hat{\mathbf{x}} \qquad : \qquad \hat{\mathbf{x}} \in \mathfrak{R}^q \,. \tag{13}$$

Applying the change of variable  $(x \to \hat{x})$  in (1), and multiplying by  $Q^T$  from the left-hand side yields

$$\hat{f}(\hat{x}) = \hat{C}\,\hat{x} + \hat{G}\,\hat{x} + \hat{H}\,(\hat{x}) + \hat{b}\,(t) = 0,$$

(14)

where

$$\hat{\boldsymbol{G}} = \boldsymbol{Q}^T \boldsymbol{G} \boldsymbol{Q}, \ \hat{\boldsymbol{C}} = \boldsymbol{Q}^T \boldsymbol{C} \boldsymbol{Q} \qquad : \hat{\boldsymbol{G}}, \ \hat{\boldsymbol{C}} \in \mathfrak{R}^{q \times q} \\ \hat{\boldsymbol{H}}(\hat{\boldsymbol{x}}) = \boldsymbol{Q}^T \boldsymbol{H}(\boldsymbol{Q} \ \hat{\boldsymbol{x}}), \ \hat{\boldsymbol{b}}(t) = \boldsymbol{Q}^T \boldsymbol{b}(t) \qquad : \hat{\boldsymbol{H}}(\hat{\boldsymbol{x}}), \ \hat{\boldsymbol{b}}(t) \in \mathfrak{R}^q \ . \ (15)$$

It is clear, from (14) and (15), that the order of the reduced model is much less than that of the original system and the calculation cost for solving  $\hat{x}$  in (14) is reduced drastically.  $\hat{x}$  is solved by the iterative method such as Newton-Raphson method. Finally, the solution x in (1) is obtained using the congruence transformation given in (13)[8]-[10].

# 3. Calculation Method of the Reduced Jacobian Matrix

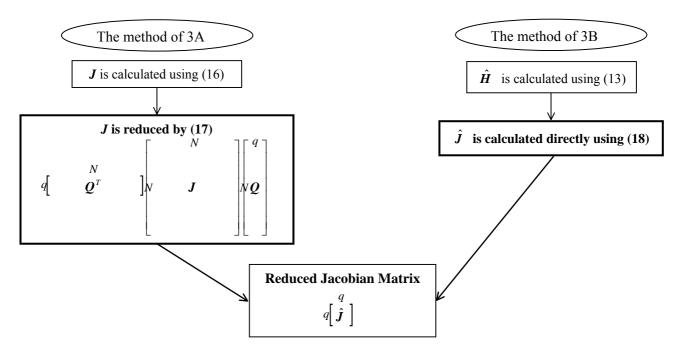

Here, we describe two calculation methods to derive the reduced Jacobian matrix. One is that the reduced Jacobian matrix is derived by reducing the original one with congruence transformation[8]-[10]. The other, which is the proposed method, is that the reduced one is derived directly without generating the original order of Jacobian matrix.

Fig.1 Comparison of the methods for calculating the reduced Jacobian matrices.

#### 3A. Previous Method

In the early works[8]-[10], the original Jacobian matrix is calculated using

$$J(\mathbf{x}) = \frac{\partial f}{\partial \mathbf{x}} = \frac{f(\mathbf{x}) - f(\mathbf{x} - \Delta \mathbf{x})}{\Delta \mathbf{x}} , \qquad (16)$$

where  $J(\mathbf{x}) \in \Re^{N \times N}$  is the original Jacobian matrix. However,  $\mathbf{x}$  in (16) is computed by (13) in the Newton-Raphson iteration. Next, the reduced Jacobian matrix  $\hat{J} \in \Re^{q \times q}$  is produced by multiplying the original size of Jacobian matrix J by projection matrices  $Q^T$  and Q[8]-[11].

$$\hat{\boldsymbol{J}} = \boldsymbol{Q}^T \, \boldsymbol{J} \, \boldsymbol{Q} \; . \tag{17}$$

In the case of computing the reduced Jacobian matrix using (17), the original order of Jacobian matrix must be calculated at each Newton-Raphson iteration. Consequently, this method is more efficient than the conventional SPICE-like method only from the viewpoint of calculation linear equation in the Newton-Raphson method. However, the simulation cost can be reduced by the double-stepped refreshing algorithm and the sparsity of the nonlinear part of the Jacobian matrix[10]. As a result, the efficiency of circuit simulation is improved more than 10 times.

#### **3B.** Proposed Method

In this section, we propose a new method which can calculate the reduced Jacobian matrix directly in the Newton-Raphson iteration. Our method does not require to calculate the original size of Jacobian matrix, that is to say, the reduced Jacobian matrix is calculated using  $\hat{x}$ . First, the nonlinear function vector  $H(Q\hat{x})$  is calculated, where

$\mathbf{x} = \mathbf{Q}\,\hat{\mathbf{x}}$  in (13), then  $\hat{\mathbf{H}}(\hat{\mathbf{x}})$  is computed by multiplying  $\mathbf{H}(\mathbf{Q}\hat{\mathbf{x}})$  by  $\mathbf{Q}^{T}$ . Therefore, it is possible to calculate the reduced Jacobian matrix  $\hat{\mathbf{J}}$  using only  $\hat{\mathbf{C}}$ ,  $\hat{\mathbf{G}}$ , and  $\hat{\mathbf{b}}(t)$  without using the original size of  $\mathbf{C}$ ,  $\mathbf{G}$ , and  $\mathbf{b}(t)$ . Finally, the reduced Jacobian matrix can be computed as

$$\hat{J}(\hat{x}) = \frac{\partial \hat{f}}{\partial \hat{x}} = \frac{\hat{f}(\hat{x}) - \hat{f}(\hat{x} - \Delta \hat{x})}{\Delta \hat{x}}.$$

(18)

As a result, the calculation cost is reduced drastically. This method can also reduce the CPU time which is spent for LU decomposition in solving the linear equation in the Newton-Raphson method same as the method 3A. Fig.1 shows the algorithms for derivation of the reduced Jacobian matrices in 3A and 3B.

### 4. Examples

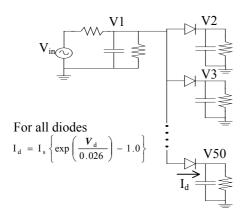

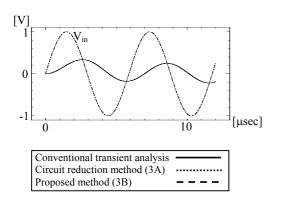

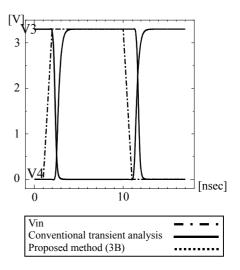

To verify the efficiency of proposed method, we have simulated the transient response of the nonlinear circuit shown in Fig.2[12], where the order of the circuit equation is 50. To compare the efficiency of circuit simulation, this circuit has been simulated by SPICE-like method, previous circuit reduction method(3A), and the proposed method(3B). However, generating the projection matrix in (3A) and (3B) is only once in this simulation and SPICE-like method does not use sparse techniques. Fig.3 and Fig.4 show the voltage waveforms at the nodes V1 and V50. They show the excellent agreement between transient responses obtained by the conventional method and the circuit reduction method. Table1 shows the comparison results of simulation costs, and indicates that the proposed method(3B) is more efficient than the previous method (3A). Especially, it seems that the previous method(3A) does not have the much advantage for the circuit including a number of nonlinear elements. On the other hand, although the interconnects are not contained and many nonlinear elements are included in this example circuit, the proposed method can achieve the efficient circuit simulation.

Fig.2 Example nonlinear circuit.

Fig.3 Transient response of V1.

Fig.4 Transient response of V50.

Table1 Comparison of simulation costs.

|                                 | Size | Time[sec] |

|---------------------------------|------|-----------|

| Conventional transient analysis | 50   | 147.412   |

| Circuit reduction method (3A)   | 4    | 137.688   |

| Proposed method (3B)            | 4    | 3.215     |

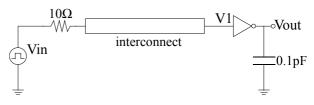

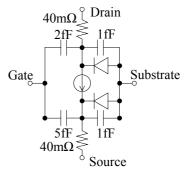

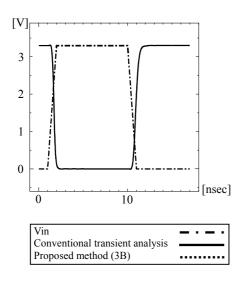

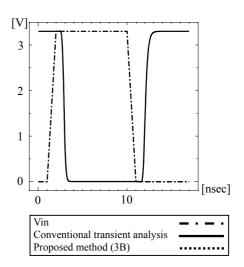

Next, we have simulated the transient response of an interconnect which is terminated with CMOS inverter as shown in Fig.5[6]. The interconnet is modeled by 30 lumped RLC sections, Rtotal=1.56[ $\Omega$ ], Ltotal=13.77[nH], and Ctotal=3.74[pF]. MOS transistor is modeled by Shichman-Hodges MOS model shown in Fig.6. Here, 4 capacitors in Fig.6, which are parasitic elements, are assumed to be constant. To compare the efficiency of circuit simulation, this circuit has been simulated by SPICE-like method and the proposed method (3B). Fig.7 and Fig.8 show the voltage waveforms at the nodes V1 and Vout. They show the excellent agreement between transient responses obtained by the conventional method and the proposed method with reduction to the very small order. Furthermore, Fig.7 represents that the circuit reduction technique can estimate accurately the effects of signal delay, reflection, and ringing. Table2 shows the comparison results of simulation costs. Here, SPICE-like method does not use sparse techniques.

Fig.5 Interconnect terminated with CMOS inverter.

Fig.6 Shichman-Hodges nMOS model.

Fig.7 Transient response of V1.

Fig.8 Transient response of Vout.

| Table2 Comparison | of simulation costs. |

|-------------------|----------------------|

|-------------------|----------------------|

|                                 | Size | Time[sec] |

|---------------------------------|------|-----------|

| Conventional transient analysis | 96   | 653.850   |

| Proposed method (3B)            | 3    | 8.262     |

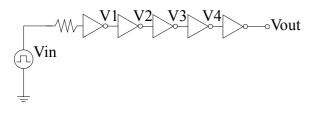

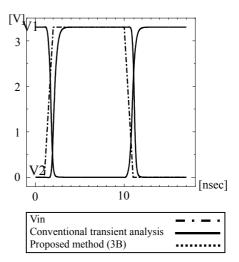

Finally, we have simulated the transient response of 5 inverter chain circuit shown in Fig.9. MOS transistor is also modeled by Shichman-Hodges MOS model. To compare the efficiency of circuit simulation, this circuit has been simulated by SPICE-like method and the proposed method (3B). Fig.10, Fig.11, and Fig.12 show the voltage waveforms at each node. They show the excellent agreement between transient responses obtained by the conventional method and the proposed method. Although this example circuit has relatively many nonlinear elements, the proposed method can achieve the accurate circuit simulation. Table3 shows the comparison results of simulation costs.

Fig.9 CMOS inverter chain.

Table3 Comparison of simulation costs.

|                                 | Size | Time[sec] |

|---------------------------------|------|-----------|

| Conventional transient analysis | 26   | 7.761     |

| Proposed method (3B)            | 5    | 3.565     |

Fig.10 Transient responses of V1 and V2.

Fig.11 Transient responses of V3 and V4.

Fig.12 Transient response of Vout.

# 5. Conclusions

In this paper, we propose the modified nonlinear circuit reduction technique based on congruence transformation. Since this method does not require to calculate the original order of Jacobian matrix, the calculation cost is reduced drastically. As a result, it has been shown that the efficiency and the accuracy of the proposed method are very well. It is expected that the efficiency of the proposed method increases for larger circuits.

# References

- L. T. Pillage and R. A. Rohrer, "Asymptotic waveform evaluation for timing analysis," IEEE Trans. Computer-Aided Design, vol. 9, pp. 352-366, Apr. 1990.

- [2] K. J. Kerns and A. T. Yang, "Stable and Efficient Reduction of Large, Multiport RC Networks by Pole Analysis via Congruence Transformations," IEEE Trans. Computer-Aided Design, vol. 16, pp. 734-744, July 1997.

- [3] A. Odabasioglu, M. Celik and L. T. Pileggi, "PRIMA: Passive Reduced-Order Interconnect Macromodeling Algorithm," IEEE Trans. Computer-Aided Design, vol. 17, pp. 645-654, Aug. 1998.

- [4] T. Watanabe and H. Asai, "Synthesis of Time-Domain Models for Interconnects Having 3-D Structure Based on FDTD Method," IEEE Trans. on Circuits and Systems – II: Analog and Digital Signal Processing, vol. 47, no. 4, Apr. 2000.

- [5] M.Suzuki, H. Miyashita, A. Kamo, T. Watanabe and H. Asai, "A Synthesis Technique of Time-Domain Interconnect Models by MIMO Type of Selective Orthogonal Least Square Method," IEEE Trans. Microwave Theory Tech, vol. 49, no. 10, Oct 2001.

- [6] H. Kubota, A. Kamo, T. Watanabe and H. Asai, "An Efficient Simulator for Multiport Interconnects with Model Order Reduction Technique," IEICE Trans. Fundamentals, vol. E85-A, no. 6, pp. 1214-1219, June. 2002.

- [7] B. N. Sheehan "ENOR: Model Order Reduction of RLC Circuits Using Nodal Equations for Efficient Factorization," in Proc. DAC'99, pp.17-21, 1999.

- [8] P. K. Gunupudi and M. S. Nakhla, "Model-Reduction of Nonlinear Circuits Using Krylov-Space Techniques," in Proc. DAC'99, pp.13-16, 1999.

- [9] E. Gad and M. S. Nakhla, "Model Reduction for DC Solution of Large Nonlinear Circuits," in Proc. ICCAD'99, pp.376-379, 1999.

- [10] P. K. Gunupudi and M. S. Nakhla, "Nonlinear Circuit-Reduction of High-Speed Interconnect Networks Using Congruent Transformation Techniques," IEEE Trans. Advanced Packaging, vol. 24, No. 3, Aug. 2001.

- [11] E. Gad, R. Khazaka, M. S. Nakhla and R. Griffith, "A Circuit Reduction Technique for Finding the Steady-State Solution of Nonlinear Circuits," IEEE Trans. Microwave Theory Tech, vol. 48, No. 12, Dec. 2000.

- [12] R. Griffith and M. S. Nakhla, "A New High-Order Absolutely-Stable Explicit Numerical Integration Algorithm for the Time-Domain Simulation of Nonlinear Circuits," in Proc. ICCAD'97, pp.276-280, 1997.