# Hardware Trojan Detection and Isolation Using Current Integration and Localized Current Analysis

Xiaoxiao Wang, Hassan Salmani and Mohammad Tehranipoor

ECE Department

University of Connecticut

Jim Plusquellic

CSEE Department

Univ. of Maryland, Baltimore Co.

## **Abstract**

This paper addresses a new threat to the security of integrated circuits (ICs). The migration of IC fabrication to untrusted foundries has made ICs vulnerable to malicious alterations, that could, under specific conditions, result in functional changes and/or catastrophic failure of the system in which they are embedded. Such malicious alternations and inclusions are referred to as Hardware Trojans. In this paper, we propose a current integration methodology to observe Trojan activity in the circuit and a localized current analysis approach to isolate the Trojan. Our simulation results show that with a very small number of clock cycles the method can detect hardware Trojans as small as few gates. However, for very small Trojan circuits with less then few gates, process variations could negatively impact the detection and isolation process.

### 1. Introduction

Chip design and fabrication is becoming increasingly vulnerable to malicious activities and alternations with globalization. This has raised serious concerns regarding possible threats to military systems, financial infrastructures and even household appliances. An adversary can introduce a Trojan designed to disable and/or destroy a system at some future time (we call it Time Bomb) or the Trojan may serve to leak confidential information covertly to the adversary. Trojans can be implemented as hardware modifications to application specific ICs (ASICs), commercial off the shelf (COTS), microprocessors, or digital signal processors (DSPs), or as firmware modifications, e.g., to field programmable gate arrays (FPGA) bitstreams [1][2].

Unfortunately, the detection of such inclusions is difficult for several reasons: 1) Nanometer IC feature sizes and system complexity make detection through physical inspection and destructive reverse engineering difficult and costly. Moreover, destructive reverse engineering does not guarantee that ICs not destructively inspected are Trojan-free. Additionally, the adversary may insert the Trojan randomly in a large batch of fabricated chips. 2) Trojan circuits are by design activated under very specific conditions, which makes it difficult to fully activate them using random stimuli and detect them using observation points (primary outputs and scan flip-flops). Moreover, existing automatic test pattern generation (ATPG) methods used in manufacturing test for detecting defects do so by operating on the netlist of the Trojan-free circuit specification. Therefore, existing ATPG algorithms cannot target Trojan activation directly.

Trojan detection methods can be applied immediately after the chip is returned to the customer, either as a die on a wafer or as a packaged chip, and/or they can be applied continuously during the lifetime of the system. For the latter case, board level support systems, such as trusted companions, are needed to carry out the monitoring. Although these types of approaches are of interest, the focus of this work is on 'time-zero' detection methods, i.e., methods applied before the chip is installed in the target system. This phase is referred to as *IC Authentication* that is done after manufacturing testing phase.

#### 1.1 Prior Work

Security has become a new concern in the design and test of chips recently [3][4][5][6]. This trend has become more apparent with the advent of Cryptochips, which implement encryption and decryption algorithms in hardware [7]. Many researchers have been able to show that these chips are highly vulnerable to various power analysis [8][9], timing [10][11], and fault injection [12][13] attacks if not specially designed with countermeasures. If not considered carefully, strong encryption algorithms that would take years to crack by brute force can otherwise be defeated in a manner of weeks, days, or even hours through these side channel attacks. Recently, scan test has become a security risk to the intellectual property on the chip [14][15][16][17]. Such non-invasive attacks have also been used for extracting secret information such as keys used within ICs [3][18]. The authors in [19] propose the use of side-channel signals, e.g., transient power supply currents, to identify Trojans in chips. We acknowledge that there has been little existing work that addresses the detection and localization of Trojans.

### 1.2 Contribution and Paper Organization

A Trojan inserted into a chip requires power supply and ground to operate. The Trojans can be of different types and sizes and their impact on circuit power characteristics would be very large or very small. In this paper, we first develop a current integration methodology to detect hardware Trojans in integrated circuits. We then develop a Trojan isolation method based on localized current analysis. We measure the current from various power pads or controlled collapse chip connections (C4s) on the die. To improve the efficiency of the detection method, random patterns are applied to increase the switching in the circuit.

The paper is organized as follows. Section 2 provides a taxonomy for Trojans. Section 3 presents the proposed current integration methodology. Section 4 present the Trojan insertion procedure. The process variations' importance when detecting Trojans will be discussed in Section 5. Section 6 presents the simulation results. Finally, Section 7 will conclude the paper.

## 2. Taxonomy

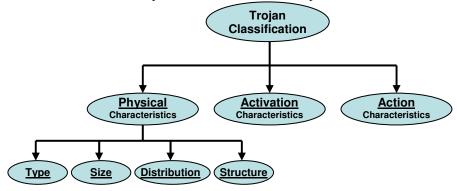

In order to develop methods designed to improve IC TRUST, it is essential to first define a taxonomy for Trojans. The Trojan classification scheme that we propose is derived from several fundamental characteristics of Trojans, including their physical, activation and action characteristics. Once a framework is established, we will be able to measure the effectiveness of the detection and isolation methods.

Malicious alternations to the structure and function of a chip can take many forms. We decompose the Trojan taxonomy into three principle categories as shown in Figure 1, i.e., according to their physical, activation and action characteristics. The physical characteristics of a Trojan are further partitioned into four categories; type, size, distribution, and structure. Our proposed taxonomy, therefore, describes Trojans using six attributes, including four physical, one activation and one action attribute. Although it is possible for Trojans to be hybrids of this classification, e.g., have more than one activation characteristic, we believe this taxonomy captures the elemental characteristics of Trojans and will be useful for defining the capabilities of various detection strategies.

**Trojan Physical Characteristics:** The *type* category partitions Trojans into *functional* and *parametric* classes. The functional class includes Trojans that are physically realized through the addition or deletion of transistors or gates, while parametric refers to Trojans that are realized through modifications of existing wires and logic. The thinning of a wire, the weakening of a transistor or any modification of a physical geometry designed to sabotage reliability or increase the likelihood of a functional or performance failure are examples of the latter.

Figure 1. Taxonomy of Trojans

The *size* category accounts for the number of components in the chip that have been added, deleted or compromised. Size of a Trojan can be an important factor during activation. A smaller Trojan has a higher probability for activation than a Trojan with larger number of inputs. The *distribution* category describes the location of the Trojan in the physical layout of the chip. For example, a *tight distribution* describes a Trojan whose components are topologically close in the layout while a *loose distribution* describes Trojans that are dispersed across the layout of the chip. Finally, the *structure* category describes the change in the layout structure. If the adversary is forced to regenerate the layout to be able to insert the Trojan in the circuitry, then the chip dimensions change. This change could result in different placement for some or all the design components.

*Trojan Activation Characteristics:* Activation characteristics refer to the criteria that causes the Trojan to become active and carry out its disruptive function. The adversary who inserted the Trojan will make it difficult for the user

of the chip to activate it, in an effort to prevent 'accidental' activation and detection during the testing phase(s) of the chip and system. Therefore, activation of a Trojan can be considered a 'rare event' from a statistical perspective.

We use the term *stealthy activation* to describe the adversary's objective in this regard. We partition Trojan activation characteristics into two sub-categories, labeled *Externally-activated* and *Internally-activated*. In Externally-activated category, the Trojan can be activated externally by adversary in his/her time of choosing. This can be done by embedding a receiver or antenna on chip and controlling it through external signals. This can also be done by accessing the internal registers and forcing them to specific date to extract secret keys or inject wrong processing data. The Internally-activated category is divided into two subclasses, labeled *Always-on* and *Condition-based*. Always-on, as the name implies, indicates that the Trojan is always active and can disrupt the function of the chip at any time. The Condition-based subclass includes Trojans that are 'inactive' until a specific condition is met.

**Trojan Action Characteristics:** Action characteristics identify the types of disruptive behavior introduced by the Trojan. We partition Trojan actions into three categories; *Modify-function, Modify-specification*, and *Transmit-info*. As the name implies, the Modify-function class refers to Trojans that change the chip's function through additional logic or by removing or bypassing existing logic. The Modify-specification class refers to Trojans that focus their attack on changing the chip's parametric properties, such as delay. The latter class represents parametric Trojans that modify wire and transistor geometries. Lastly, the Transmit-info class refers to Trojans that transmit key information from design mission mode to an adversary.

## 3. Current Integration Method

### 3.1 Trojan Detection

A Trojan, when inserted into a chip, will most likely consume power. However, the Trojan's contribution to the total power consumption of the circuit depends heavily on its size and type. It also depends on its activation, that is, fully activated Trojan can consume more power than that of partially activated. A Trojan inserted in a chip will draw leakage current if it is powered on. Creating switching in the Trojan can further increase the amount of current drawn by the Trojan circuitry. We acknowledge that fully activation of a Trojan will be extremely challenging and prohibitively expensive considering that the size and type of Trojan is unknown to us.

Partial activation of Trojans can be an effective way for Trojan detection and isolation using current-based side-channel analysis methods similar to our current integration method. A large number of transitions is generated when applying a pattern to the chip. Some of the Trojan inputs in the chip may also observe the transitions and in turn cause transitions in the Trojan circuitry as well. The switches in the Trojan will increase the local power consumption (i.e. current). The local power refers to the current drawn from the power port near the Trojan circuitry. The more the number of switching on the Trojan inputs and in the Trojan circuitry the larger the power consumption. Since small Trojan sizes are expected to be inserted in chips by adversary to reduce the detection capability, the local current impact by Trojan could be more significant than the global current that can be measured only by power pins.

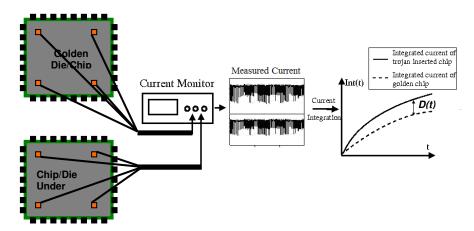

The amount of current a Trojan can draw could be so small that it can be submerged into envelop of noise and process variations effects, therefore, cannot be detected by measurement equipments. However, Trojan detection capability can be greatly improved when measuring currents locally and from multiple power pads. Figure 2 shows our current integration methodology for detecting hardware Trojans. The golden chip can be identified using an exhaustive test for few randomly selected chips. It can also be identified using the pattern set that will be used in our current integration method by comparing the results against each other for all the patterns. If the same results is obtained for all the selected chips, they can be identified as Trojan-free.

We assume that adversary will insert the Trojans randomly in a selected number of chips. After identifying the golden chips, an average current waveform will be formed in response to the pattern set. Next, the pattern set will be applied to each chip and the current will be measured locally via power pads or C4 bumps. By applying this current integration method the small current consumption difference between Trojan-inserted and Trojan-free circuits can be increased through the integration process. By applying more number of patterns to the chip over time, more current difference will be measured which may make Trojan detection task easier. When the current difference surpasses a pre-defined threshold, it results in detection of a Trojan and the pattern application will stop.

Note that in this work, we assume that the IC authentication phase is done after manufacturing test. Therefore, the likelihood of encountering a defect during IC authentication would be very small. The existence of defect depends on the DPPM level for the manufactured chip in the foundry.

Figure 2. Current Integration Method

If  $I_{trojan\_free}(t)$  and  $I_{trojan\_inserted}(t)$  denote the supply current drawn by Trojan-free and Trojan-inserted circuit at time t, respectively, then the integrated current at time t for Trojan-free and Trojan-inserted circuit ( $Int_{trojan-free}(t)$ ) and  $Int_{trojan-inserted}(t)$ ) can be expressed by equations (1) and (2):

$$Int_{trojan\_free}(t) = \int_{0}^{t} I_{trojan\_free}(t)dt$$

(1)

$$Int_{trojan\_insterted}(t) = \int_{0}^{t} I_{trojan\_inserted}(t)dt = \int_{0}^{t} [I_{trojan\_free}(t) + I_{trojan}(t)]dt$$

(2)

Where  $I_{trojan}(t)$  denotes the current drawn by Trojan. Since same pattern set is applied to both golden chips and chipunder-authentication, the difference between  $I_{trojan\_free}(t)$  and  $I_{trojan\_inserted}(t)$  comes from (1) the additional current drawn by Trojan gates and (2) changes in the circuit current due to process variations. By integrating the current along time axis for both chips, their cumulative difference at time t, denoted by D(t), can increase as more number of patterns are applied, i.e. Trojan detection time will increase.

$$D(t) = Int_{trojan\_insterted}(t) - Int_{trojan\_free}(t) = \int_{0}^{t} I_{trojan}(t)dt$$

(3)

When D(t) reaches the predefined Trojan detection threshold  $D_{th}$  ( $D(t) \ge D_{th}$ ), then the chip is identified as Trojan-inserted. It should be noted that this threshold is determined by Trojan detection timing budget as well as current measurement device resolution.

Our proposed current integration method is effective in detecting both tightly and loosely distributed Trojans. The effectiveness of the method does not necessarily depend on the location of a Trojan in a circuit since the current is measured through power pads or C4s. Since there are a large number of such nodes on the power distribution network, the Trojan circuitry will most likely impact the nearest power pad's current.

#### 3.2 Trojan Isolation

Trojan isolation process is done after detecting a Trojan in a chip. The Trojan isolation is essential in identifying the location of Trojan and possibly identifying the type of Trojan especially in terms of action characteristics. It is extremely valuable to find out what the adversary intended to carry out with the inserted Trojan.

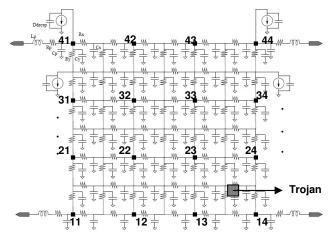

Trojan isolation process is based on the fact that Trojan gates (similar to circuit gates) will draw more current from their nearest power pad therefore more current difference occurs on the power pads near the Trojan gates. Figure 3 shows the power ground distribution network RLC model which will be used in Trojan detection and isolation process. The figure shows the power distribution with 16 power pads and a Trojan inserted close to power pad 14.

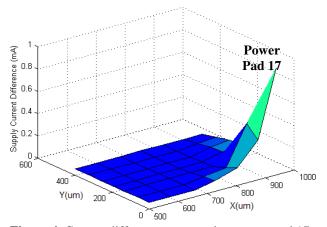

To further demonstrate the impacts on local power pads, we have inserted a Trojan (a 3-bit counter, tightly distributed) in ISCAS'89 s38417 benchmark which contains 8709 gates and 1636 FFs. In s38417 benchmark, we

have inserted 49 power pads using Synopsys physical tool [21]. The Trojan was inserted close to power pad 17 exactly at the coordinates of (950μm, 100μm) in the physical layout.

Figure 3. the power ground distribution network RLC model

We have generated the layout of the circuit and inserted the Trojan circuit in a dead space in the layout and connected the clock to the Trojan. Figure 4 shows the current difference of an array of power pads between Trojan-inserted and Trojan-free circuit obtained using post-layout simulation [21]. Figure 4 shows that the maximum supply current difference happens on power pad 17. The supply current difference falls drastically on neighboring power pads.

Figure 4. Current difference measured on power pad 17

During Trojan isolation process the current of each power pad is measured, integrated and compared with golden chip's current integration result separately for each power pad. When there is a clear difference (depending on the pre-defined threshold) between the two chips, then the Trojan is assumed to be near the power pad. However, if, for example, the Trojan is located right between power pads 13, 14, 23, and 24, then it will impact more than one power pad when switching (see Figure 3). By comparing the currents drawn by each power pad after applying the patterns, we will be able to identify the location of the Trojan between them. If the adversary distributes the Trojan in the entire circuit, the isolation process will be more difficult since the smaller portion of the Trojan will draw currents from different power pads.

## 3.3 Pattern Application

To detect and isolate a Trojan, a pattern set must be generated and applied to the chip during IC authentication step. Since the proposed method measures the current from various power pads, the patterns that generate localized switching would be most effective. However, generating such patterns will be computationally intensive. In this paper, we use random patterns that are effective in generating a large number of transitions in the circuit thus increasing the probability of partially activation of hardware Trojans.

The number of patterns required to detect Trojans depends on the size and type of Trojans. A sequential Trojan that uses clock continuously consumes more power compared to monitor-like Trojans. Therefore the detection depends on the number of clock cycles needed to reach Dth current difference between Trojan-free and Trojan-inserted circuits. Note that in this work, there are no logic observation points. The patterns should generate switching in the circuit and the power pads are in fact the observation point for the side channel signal, here current. Also note that we use primary inputs and scan cells to apply patterns to the circuit. The pattern application is similar to test-per-clock [20] where a pattern is applied in every clock cycle. A random bit is shifted into the scan chain to generate a new random pattern in addition to applying a random pattern to primary inputs in every clock cycle. In a test-per-clock approach, the pattern application time will be short. Imagine  $10^6$  patterns are applied to a chip to be used in current integration method to reach  $D_{th}$ . For a shift clock cycle of 10 MHz, it would only take about 0.1s to apply all the patterns.

## 4. Trojan Insertion Procedure

An adversary can exploit the dead spaces in the physical layout to insert small or large hardware Trojans. In this work, we generate the physical layout for ISCAS'89 s38417 benchmark. We then generate several copies of this benchmark to insert Trojans. In each layout, we use dead spaces to insert Trojan gates/circuitry. We insert two types of Trojans, Counter and Comparator, in a tightly and loosely distributed fashion, respectively. For distributed Trojan, we utilize small dead spaces to insert Trojan gates and connect them. When inserting counter, we use those already existed counters in standard cell library. We place them in available dead spaces in the physical layout. When designing a comparator, however, we intentionally distribute the gates in difference locations on the layout. In all cases, we ensure not to change the s38417's original layout.

Current integration method can be used for detecting both tight and loose distributed Trojans. During Trojan detection stage, the total supply current is integrated for chip-under-authentication and the golden chip separately. All Trojan gates located on chip will contribute to overall current consumption. Therefore, the total supply current's difference beyond the predefined threshold between the two chips will imply the existence of Trojan. We will show our simulation results in Section 6 for loosely distributed Trojans.

We assume that the adversary has the knowledge of IC fabrication and testing, so he/she can design the Trojan circuit such that it will not to be detected during manufacturing test. The adversary is expected to ensure the layout of Trojan-inserted and Trojan-free circuits remain same by avoiding re-designing the physical layout. Any modifications to the layout of the circuit will change the position of cells and makes it easier to be detected, for instance, using circuit delay analysis. Designing Trojan-inserted and Trojan-free is done in the following steps. First, a circuit without Trojan is synthesized and the layout will be generated. Second, the layout of the circuit is examined to identify dead spaces. Depending on the size of Trojan circuit some of dead spaces are selected. Third, the Trojan cells are added to the identified dead spaces in the circuit.

## **5. Process Variations Impact on Trojan Detection**

As technology scales to 45nm and below, the impact of process variations on current/power consumption is expected to be more significant than ever. Therefore, process variations should be considered during Trojan detection methods that rely on side-channel signals. Process variations can either help or harden the Trojan detection process. According to equation (4), which is current drawn by a single gate, decreasing voltage threshold  $V_{th}$ , channel length L, as well as oxide thickness  $T_{ox}$  will increase gate current. Conversely, increasing  $V_{th}$ , L and  $T_{ox}$  will decrease gate current consumption ( $I_D$ ).

$$I_{D} = \frac{\mu C_{ox} W}{2L} (V_{GS} - V_{th})^{2} (1 + \lambda V_{DS})$$

(4)

The following two scenarios will make the Trojan detection more difficult when considering process variations:

- 1. When process variations in Trojan-free circuit increase the current consumption. This will make the current measured from a Trojan-free circuit closer to that of the Trojan-inserted circuit.

- 2. When the process variations in Trojan-inserted circuit decrease the current consumption. This will also make the current measured from the Trojan-inserted circuit closer to that of the Trojan-free circuit.

Similarly, the two scenarios that help make the Trojan detection process easier are:

- 1. When process variations in Trojan-free circuit decrease the current consumption.

- 2. When process variations in Trojan-inserted circuit increase the current consumption.

Two types of process variations, i.e., inter-die and intra-die, will occur in a manufactured chip. When considering process corners using such variations, each transistor on die has the same or largest process variations. Therefore, process corners that increase current consumption of a Trojan-free chip and decrease current for Trojan-

inserted chip are the most difficult scenarios for Trojan detection. Although process variations may decrease the gap between current integration curves of Trojan-inserted circuit and Trojan-free circuit, the current integration method would still be effective in detecting small Trojans. The integration effect can successfully increase the gap between the two curves to the detectable threshold  $(D_{th})$ .

### 6. Simulation Results

The current integration method is applied for detecting Trojans inserted into s38417 benchmark. First we generate 7 layouts for original s38417 benchmark using Synopsys physical design tools [21] in 180nm technology node [22]. 1-bit, 3-bit, 7-bit, 9-bit counter and 3-input, 5-input, 20-input comparator Trojans are inserted to these seven layouts separately (i.e. only one Trojan in each layout). Table 1 shows the type, size, distribution and structure of the inserted Trojans in the layout. We also investigate the impact of process variations on threshold voltage  $(V_{th})$ , channel length (L) and oxide thickness  $(T_{ox})$  on Trojan detection. The process variations we consider during our simulation are shown in Table 2.

Table 1. Trojan Characterization

| Trojan     | Type     | Size  | Distribution | Structure |

|------------|----------|-------|--------------|-----------|

|            | 1-bit    | 0.04% | tight        | no-change |

| Counter    | 3-bit    | 0.10% | tight        | no-change |

|            | 7-bit    | 0.31% | tight        | no-change |

|            | 9-bit    | 0.42% | tight        | no-change |

|            | 3-input  | 0.02% | loose        | no-change |

| Comparator | 5-input  | 0.04% | loose        | no-change |

|            | 20-input | 0.15% | loose        | no-change |

**Table 2.** Process Variations Applied During Trojan Detection

|                              | Inter-die | Intra-die |

|------------------------------|-----------|-----------|

| Threshold Voltage $(V_{th})$ | 5%        | 20%       |

| Channel Length (L)           | 2%        | 8%        |

| Oxide Thickness $(T_{ox})$   | 1%        | 4%        |

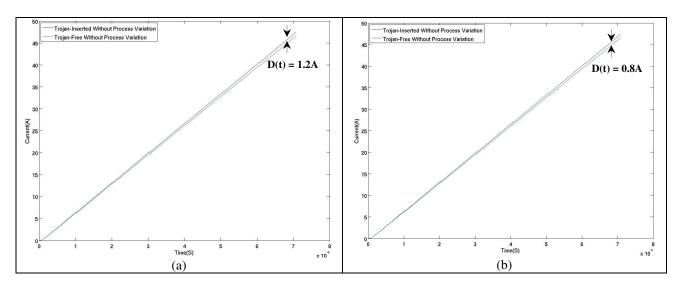

We first start with the results obtained from the circuits containing larger Trojans. Figure 5(a) shows the simulation results obtained using Synopsys Nanosim [21] for s38417 containing a 9-bit counter. The patterns are shifted into the scan chain with a frequency of 100MHz. As seen in the figure, after applying 700 clock cycles (7us pattern application time), D(t) > 1A, which is easily detectable using measurement devices. In fact, for such Trojan, depending on  $D_{th}$ , significantly shorter application time would be sufficient to detect the Trojan. The results obtained for s38417 with 7-bit counter as Trojan also confirm that such Trojan can be easily detected. The isolation method by measuring current on each power pad would also be effective in detecting such Trojans. In general, detecting a counter would be easier than a combinational Trojan since the counter continuously receive the clock and consumes power. No process variations were considered for the results shown in Figure 5, although the process variations would not be significant enough to change the detection outcome for such Trojans.

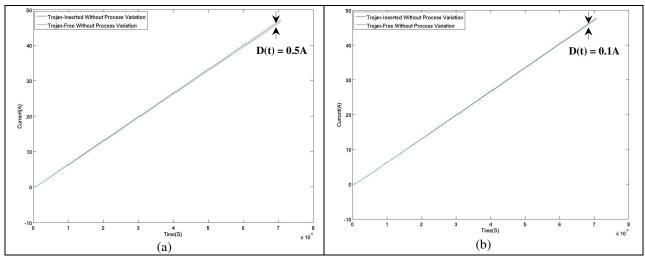

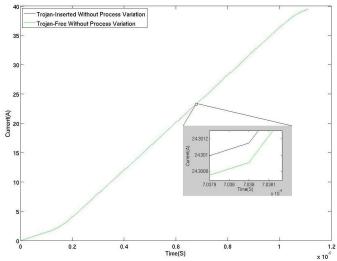

Figures 6(a) and (b) show the simulation results for the circuit when containing 3-bit and 1-bit counter, respectively without process variations. As seen in the figure, the smaller Trojans consumes significantly lower power (i.e. current) which in turn makes the detection more difficult. Note that the Trojan detection depends on two important factors: (1) process variations and (2) measurement device's resolution. We believe that the process variations would be the limiting factor in detection Trojans.

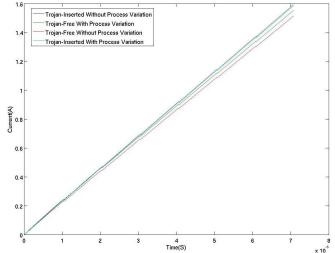

Figure 7 shows the simulation results for the circuit containing 3-bit counter while considering worst-case process corners for both Trojan-inserted and Trojan-free circuits. The process corner used in the Trojan-free circuit increases the current in the Trojan-free circuit while the process corner used in the Trojan-inserted circuit reduces the total current. This is done to measure the efficiency of the technique in detecting the Trojan. As seen, the Trojan-inserted circuit with process variations is still consuming more current when compared to the Trojan-free circuit with process variations. However, for the smaller Trojans, such as 2-bit and 1-bit counters the detection was not possible considering worst-case process variations. As seen in Figure 6(b), the current difference between Trojan-free and Trojan-inserted circuits when containing 1-bit counter is negligible. The existence of process variations will make the Trojan detection even more difficult.

Figure 5. Current measurement for s38417 with (a) 9-bit counter and (b) 7-bit counter

**Figure 6.** Current measurement for s38417 with (a) 3-bit counter and (b) 1-bit counter (a flip-flop with self loopback)

Figure 7. Current measurement for s38417 with 3-bit counter considering the two process corners

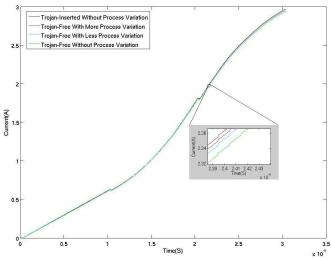

Figure 8 shows the simulation results when inserting a 20-input Trojan in s38417 benchmark. The comparator circuit is connected to 20 nodes in the circuit. This type of Trojan falls into the category of loose distribution and requires activation. Since fully activation is very time consuming and prohibitively expensive, we rely on partial activation of hardware Trojan by applying random patterns. Figure 8 shows the results after applying 300 random patterns to the circuit. As seen in the figure, the 20-input comparator can be easily detected even in presence of the two process corners. However, the results shown in Figure 9 demonstrate the difficulty of detecting a 5-input comparator even without process variations. This was the case for 3-input Trojan as well. To further increase the probability of detection, more test patterns must be applied. The application time depends where the Trojan-inserted circuit results falls outside the Trojan-free circuit with process variations. The total number of pattern to detect such small Trojans can be estimated from the result shown in Figure 9 based on  $D_{th}$ . This is outside the scope of this paper and is part of our future work.

Figure 8. Current measurement for s38417 with 20-input comparator and two process corners

Figure 9. Current measurement for s38417 with 5-input comparator and no process variations

#### 7. Conclusions and Future Work

We have presented a new current integration methodology for Trojan detection and isolation. The method measures the current locally from the on-die power pads. Comparing the results obtained for Golden chips against the chip-under-authentication, the Trojan can be detected if the current integration results fall outside the golden chip results. We have shown that our method can easily detect Trojans as small as 0.1% the circuit area. We plan to improve the quality of test patterns using the layout-aware test pattern generation procedure we are developing. We also plan to deal with process variation impact in more accurate way by performing Monte Carlo simulation for all Trojan-free and Trojan-inserted circuits and measure the effectiveness of the proposed method.

#### References

- [1] http://www.acq.osd.mil/dsb/reports/2005-02-HPMS\_Report\_Final.pdf

- [2] http://www.darpa.mil/mto/solicitations/baa07-24/index.html

- [3] B. Yang, K. Wu, and R. Karri, "Scan Based Side Channel Attack on Dedicated Hardware Implementations of Data Encryption Standard," in *Proc. of the IEEE Int. Test Conf. (ITC)*, pp. 339.344, 2004.

- [4] S. Ravi, A. Raghunathan, and S. Chakradhar, "Tamper Resistance Mechanisms for Secure Embedded Systems," in *Proc. of the 17th Intl. Conf. on VLSI Design*, pp. 605.611, 2004.

- [5] P. Kocher, R. Lee, G. McGraw, A. Raghunathan, and S. Ravi, "Security as a New Dimension in Embedded System Design," in *Proc. of the 41st Annual Conference on Design Automation*, pp. 753.760, June 2004.

- [6] K. Tiri and I. Verbauwhede, "A VLSI Design Flow for Secure Side-Channel Attack Resistant ICs," in *Proc. of Design, Automation and Test in Europe*, pp. 58.63, Mar. 2005.

- [7] K. Hafner, H. C. Ritter, T. M. Schwair, S.Wallstab, M. Deppermann, J. Gessner, S. Koesters, W.-D. Moeller, and G. Sandweg, "Design and Test of an Integrated Cryptochip," *IEEE Design and Test of Computers*, pp. 6.17, Dec. 1991.

- [8] P. Kocher, J. Jaffe, and B. Jun, "Differential Power Analysis," *Lecture Notes in Computer Science*, vol. 1666, pp. 388.397, 1999.

- [9] G. B. Ratanpal, R. D. Williams, and T. N. Blalock, "An On-Chip Signal Suppression Countermeasure to Power Analysis Attacks," *IEEE Transactions on Dependable and Secure Computing*, vol. 1, no. 3, pp. 179.188, 2004.

- [10] P. C. Kocher, "Timing Attacks on Implementations of Diffe-Hellman, RSA, DSS, and Other Systems," *Lecture Notes in Computer Science*, vol. 1109, pp. 104.113, 1996.

- [11] J. Kelsey, B. Schneier, D. Wagner, and C. Hall, "Side Channel Cryptanalysis of Product Ciphers," in *Proc. of the European Symposium on Research in Computer Security*, pp. 97.110, Sep. 1998.

- [12] D. Boneh, R. A. Demillo, and R. J. Lipton, "On the Importance of Checking Cryptographic Protocols for Faults," *Lecture Notes in Computer Science*, vol. 1233, pp. 37.51, 1997.

- [13] E. Biham and A. Shamir, "Differential Fault Analysis of Secret Key Cryptosystems," *Lecture Notes in Computer Science*, vol. 1294, pp. 513.527, 1997.

- [14] R. Goering, "Scan Design Called Portal for Hackers," Oct. 2004. [Online]. Available: http://www.eetimes.com/news/design/showArticle.jhtml?articleID=51200154

- [15] S. Scheiber, "The Best-Laid Boards," Apr. 2005. [Online]. Available: http://www.reed-electronics.com/tmworld/article-/CA513261.html

- [16] J. Lee, M. Tehranipoorand J. Plusquellic, "A Low-Cost Solution for Protecting IPs Against Side-Channel Scan-Based Attacks," in Proc. VLSI Test Symposium (VTS'06), 2006.

- [17] J. Lee, M. Tehranipoor, C. Patel and J. Plusquellic, "Securing Scan Design Using Lock & Key Technique," in *Proc. Int. Symp. on Defect and Fault Tolerance in VLSI Systems (DFT'05)*, 2005.

- [18] D. H´ely, M.-L. Flottes, F. Bancel, B. Rouzeyre, N. B´erard, and M. Renovell, "Scan Design and Secure Chip," in *Proc. of the 10th IEEE Intl. On-Line Testing Symposium*, 2004.

- [19] D. Agrawal, S. Baktir, D. Karakoyunlu, P. Rohatgi, B. Sunar, "Trojan Detection using IC Fingerprinting", Symposium on Security and Privacy, 2007, pp. 296 310.

- [20] M. Bushnell, V. Agrawal, Essentials of Electronics Testing, Kluwer Publishers, 2000.

- [21] Synopsys, "User Manual for SYNOPSYS Toolset Version 2005.09," Synopsys, Inc., 2005.

- [22] http://crete.cadence.com, "0.18m standard cell GSCLib library version 2.0," Cadence, Inc., 2005.