Received 19 June 2020; accepted 1 July 2020. Date of publication 9 July 2020; date of current version 7 August 2020. The review of this article was arranged by Editor L. Lukasiak.

Digital Object Identifier 10.1109/JEDS.2020.3008094

# Monolithically Integrated Catalyst-Free High Aspect Ratio InAs-on-Insulator (InAsOI) FinFETs for pH Sensing

MANEESHA RUPAKULA<sup>®</sup> <sup>1</sup>, JUNRUI ZHANG<sup>2</sup>, FRANCESCO BELLANDO<sup>1</sup>, FABIEN WILDHABER<sup>2</sup>, CLARISSA CONVERTINO<sup>®</sup> <sup>3</sup>, HEINZ SCHMID<sup>®</sup> <sup>3</sup> (Member, IEEE), KIRSTEN EMILIE MOSELUND<sup>®</sup> <sup>4</sup> (Senior Member, IEEE), AND ADRIAN MIHAI IONESCU<sup>1</sup> (Fellow, IEEE)

1 Nanoelectronic Devices Laboratory, École Polytechnique Fédérale de Lausanne, 1015 Lausanne, Switzerland

2 XSENSIO SA, EPFL Innovation Park, 1015 Lausanne, Switzerland

3 Materials Integration and Nanoscale Devices Group, IBM Zurich Research Laboratory GmBH, 8803 Rüschlikon, Switzerland

4 Department of Science and Technology, IBM Research GmBH, 8803 Rüschlikon, Switzerland

CORRESPONDING AUTHOR: M. RUPAKULA (e-mail: maneesha.rupakula@epfl.ch)

This work was supported by EU FP7/2007-2013 Project E2Switch under Grant 619509.

**ABSTRACT** In this work, we report a novel Indium Arsenide-on-insulator (InAsOI) FinFET platform designed with record high aspect ratio that favors the use of the devices as charge sensors. InAs has very high mobility among III-V semiconductors and an intrinsic surface accumulation layer yielding good ohmic contacts thus making it an interesting choice for chemical and biological sensing platforms. Template Assisted Selective Epitaxy (TASE) enables the integration of III-V highly scaled devices, monolithically integrated on Silicon, within a fully CMOS compatible fabrication scheme hence without any catalyst-induced growth. With a new geometry, high-aspect-ratio (HAR) InAs fins and a new application of pH sensing the versatility of TASE is exhibited. HAR InAs fins, fin height to fin width in excess of 4 for fin width down to 30 nm are fabricated on a Si substrate. The HAR InAs-on-insulator fins are characterized as pH sensors. A sensitivity of 38.8 mV per pH is extracted at 6  $\mu$ A drain current from a 40 nm wide 20 multi-finger array.

INDEX TERMS III-V, high-aspect ratio, FinFET, InAs, ISFET, pH Sensor.

### I. INTRODUCTION

Ion sensitive field effect transistors (ISFETs) have been proposed by Bergveld in 1970s and have evolved considerably since. ISFETs are modified MOSFETs where the gate metal electrode is replaced with a liquid under test via a reference electrode [1]. Recently three-dimensional (3D) structures, such as nanowires (NW) or FinFETs have become of interest for sensing applications rather than their planar counterparts [2]. In 3D structures, higher surface-to-volume ratios and sizes comparable to chemical/biological elements enable surface interactions to affect the bulk of semiconductor. Also, 3D architectures such as High Aspect Ratio (HAR) structures are known to be more favorable for sensing since they facilitate the capture of the species arriving from three different directions. This is perceptible especially

at very low analyte concentrations where a reasonably fast response time or short settling time may still be obtained [3]. The settling time is the time taken by a sensor to capture a certain number of analyte molecules and produce a stable shift in device characteristics. Indium arsenide (InAs) is an interesting material choice for chemical and biological sensing platforms due to high electron mobility and to the formation of a surface accumulation layer that enables high quality ohmic contacts. InAs NWs have been used in gas sensing [4], protein sensing [5], interfacing live mammalian cells [6] and also pH sensing [7]. Moreover, InAs NWs have been shown to exhibit charge dragging effect [8]. Charge dragging refers to a situation where ionic fluid flow energy can generate a voltage or current. This particularity of InAs NWs can potentially enable bio-sensing in

This work is licensed under a Creative Commons Attribution 4.0 License. For more information, see https://creativecommons.org/licenses/by/4.0/

VOLUME 8, 2020 773

combination with energy harvesting. For sensing, it is agreed that the fabrication of high density arrays enables detection of multiple target analytes. Moreover, a CMOS compatible process allows signal conditioning circuitry to be integrated along with the sensor for improved noise performance. However, in the afore-mentioned InAs platforms, invariably NWs are grown on a different substrate and then manually transferred to a Si substrate. The NW deposition is random and subsequent processing always needs customization. In some cases, high-density NW arrays were fabricated by the use of Au-catalyst particles, making the process non-CMOS compatible. This work addresses some of the shortcomings of these InAs NW sensing platforms. Using Template Assisted Selective Epitaxy (TASE) various III-V nanoscale devices are grown by means of metal organic chemical vapor deposition (MOCVD) on Si-substrate [9], [10]. In this work we demonstrate monolithically integrated, catalyst free High-Aspect-Ratio (HAR) InAs FinFETs for pH sensing.

### **II. DEVICE FABRICATION**

Device fabrication is explained first as template fabrication and next as the device processing where process steps to demonstrate sensing are carried out. Template fabrication begins with the definition of alignment markers and ends when InAs fins grown with TASE process on Si substrate. Device processing consists of the subsequent steps of source/drain metallization, gate oxide deposition and channel isolation.

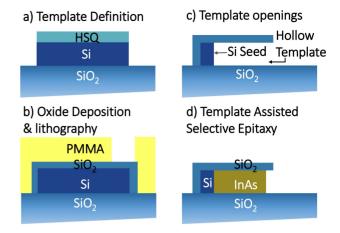

The starting substrate is a silicon-on-insulator wafer with 110 nm silicon device layer and 2  $\mu$ m buried oxide. The side view cross sections of the main template fabrication steps are illustrated in Fig. 1(a) to (d). In Fig. 1 (a) an array of fins with the width ranging from 20nm to 70nm are patterned into the silicon layer using a 2% diluted HSQ e-beam resist with Electron Beam Lithography (EBL). The fin pattern is transferred into silicon with an anisotropic HBr dry etch. Then in Fig. 1(b) template deposition steps consist of Atomic Layer Deposition (ALD) and Chemical Vapor Deposition (CVD) of 80nm oxide here on referred to as template oxide.

Further, access regions are patterned on one end of the template structure using PMMA e-beam resist. A short dilute HF (DHF) dip then exposes the underlying silicon as illustrated in Fig. 1(b). Next, using 2% diluted TMAH the silicon inside the template is emptied in a controlled manner such that a combination of a silicon seed segment and hollow region remain as shown in Fig. 1(c). Then a very short DHF step is carried out right before Metal Organic Chemical Vapor Deposition (MOCVD) to remove native oxide on Si seed. This step expands the inner dimensions of the template oxide in all directions and determines the difference between the InAs width of the fins and the designed Si fin width. Finally, InAs is selectively grown using MOCVD at 550°C using trimethylindium (TMIn) and arsine (AsH<sub>3</sub>) as precursors. As seen in Fig. 1(d) there is a template oxide on almost all sides of the grown InAs except the access region.

FIGURE 1. Side view of the main template fabrication steps- (a) Template definition using EBL and dry etching, (b) template deposition using ALD and LPCVD oxide & patterning access regions using EBL, (c) template openings in PMMA using EBL, (d) template assisted MOCVD growth of InAs from Silicon seed.

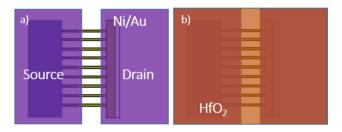

FIGURE 2. Top view of device processing steps- (a) Source/drain metallization using e-beam patterning and resist lift-off (b) ALD deposited HfO<sub>2</sub> behaves as gate oxide and isolation oxide.

Hence, a DHF dip partially removes this template oxide. Only 10nm of template oxide is left in order to preserve the structure integrity during the subsequent fabrication steps. Source & drain region definition is carried out with an EBL step as depicted in Fig. 2(a) using PMMA resist.

After EBL, the samples are dipped in DHF to remove the template oxide on the source/drain contact regions. Then the samples are transported quickly from the wet bench into the evaporation chamber using a vacuum transfer box to minimize re-oxidation of the surface. 20nmNi/150nmAu is evaporated to ensure good fin sidewall coverage. The samples are kept in solvent to lift-off the resist such that all residues are cleared away. Then the sample is loaded into an ALD reactor for 20nm HfO<sub>2</sub> deposition at 200°C as shown in Fig. 2 (b). HfO<sub>2</sub> functions as the gate sensing oxide and also isolates the channel region from source/drain metallized areas.

## **III. CHARACTERIZATION RESULTS**

### A. PROCESS CHARACTERIZATION

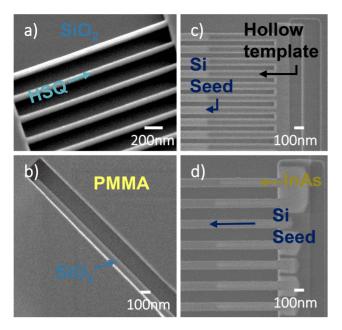

Scanning Electron Micrograph (SEM) images shown in Fig. 3 (a) to (d) correspond to those illustrated in Fig. 1 (a) to (d). Fig. 3 (a) is a tilted SEM image of etched Si fins with remaining HSQ resist; this step determines the fin template width and height. Next, Fig. 3 (b) shows access

FIGURE 3. SEM images taken at steps as shown in the fabrication schematic (a) tilted view of template definition (b) tilted view of Oxide template deposition using ALD and LPCVD oxide, (c) tilted view of PMMA resist opening underlying template, (d) top view of MOCVD grown 40 nm wide InAs fins inside SiO<sub>2</sub> template.

FIGURE 4. (a) Top view of multiple fin array of InAs grown uniformly from Silicon seed, scale bar =  $1\mu$ m (b) EDX elemental analysis of In, As, Si, O constituents.

windows in PMMA e-beam resist well aligned to the underlying template structure which underwent oxide deposition. In this step the SiO<sub>2</sub> covering the silicon fins is etched away in DHF dip.

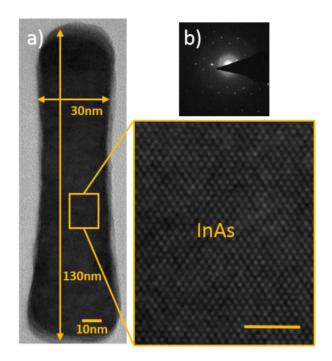

FIGURE 5. (a) HR TEM image of HAR fin with aspect ratio in excess of 4 and a zoom on the right of highly crystalline grown InAs, scale bar = 5nm (b) SEAD diffraction pattern at the center of the zoom confirms the monocrystalline nature.

Then PMMA resist is stripped and the sample is ready for the next step. After a controllable TMAH wet etch a partially hollow SiO<sub>2</sub> template remains with a Si seed as imaged in Fig. 3(c). Finally, as shown in Fig. 3(d) using MOCVD InAs is selectively grown from the silicon seed. The grown InAs region can be clearly distinguished as the lighter part in contrast to the darker silicon seed.

A device with grown fins is pictured in the scanning electron micrograph in Fig. 4(a). It consists of an array of 20 InAs fins with  $W_{FIN}=50$  nm each and a pitch of 250 nm grown uniformly inside the template to a length of  $1\mu m$ . Next in Fig. 4 b), using Energy Dispersive X-ray (EDX) spectroscopy an elemental material analysis map confirms selective growth of InAs inside the SiO<sub>2</sub> template. No dopants were intentionally introduced during the MOCVD growth.

Detailed high resolution microscopy enables us to examine the quality of InAs grown. In Fig. 5 (a) to (b) Transmission Electron Microscope (TEM) is used for characterization of the narrowest fins grown. The highest aspect ratio of the InAs fin is calculated as the height (H<sub>FIN</sub> = 130 nm) to width (W<sub>FIN</sub> = 30 nm) ratio of  $\sim$  4:1. Also we see in Fig. 5(b) that the Selective Area Electron Diffraction (SAED) image in the specific region shows bright spots that confirm mono-crystallinity of the InAs.

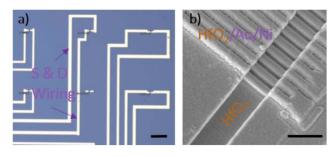

In Fig. 6 (a) an optical microscope image of the source/drain wiring on the devices is displayed. A very clean lift-off is indeed seen. In Fig. 6 (b), a SEM image shows the device after source/drain metallization and deposition of ALD oxide.

VOLUME 8, 2020 775

FIGURE 6. (a) Optical microscope image of source/drain metallization showing a clean lift-off step, scale bar = 50  $\mu$ m (b) Tilted SEM image after ALD oxide is deposited on the channel region and S&D isolation, scale bar = 500 nm.

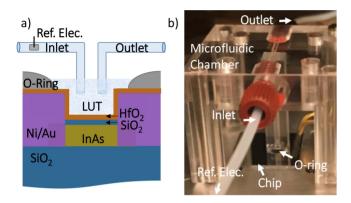

FIGURE 7. (a) Side view schematic of the main components in pH measurement setup (b) Photograph of pH measurement setup.

### **B. PH CHARACTERIZATION**

The setup for pH characterization is depicted and photographed in Fig. 7(a) and (b) respectively. A specially fabricated fluidic chamber is clamped to the sample. Hence, the Liquid under test (LUT) is contained in a 5mm diameter O-ring to cover devices of interest. A commercial external Ag/AgCl reference electrode in the inlet ensures a stable potential, i.e., reference voltage (V\_G) is applied to the gate of the device via LUT.

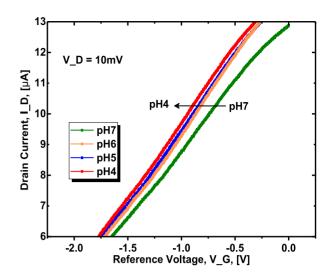

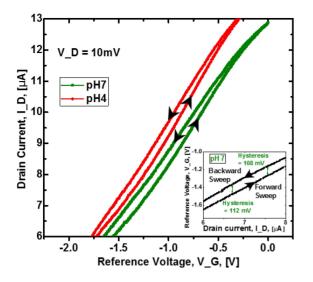

Fig. 8 to 10 show graphs and data analysis for the same device with 50 nm fin width. It is visible in Fig. 8 that there is a systematic shift in the drain current (I\_D) curves when the reference voltage is swept through various pH buffer solutions from pH 7 to pH 4, with a decrease in sensitivity near pH 4, which may indicate a limited buffer capacity of the oxide surface. It is worth noting that due to a partial fluid gate overlapping over the FinFET structure, the InAs Fin-ISFET is not fully depleted and the device is never completely turned OFF by gate action. Moreover, rest of the measurements taken were on devices with W<sub>FIN</sub>>50 nm, along with high doping levels contributing further to this problem. However, this does not prevent the use in sensing applications maintaining high linearity, a high ON current and high sensitivity.

It can be further seen in Fig. 8 that the ON current is a couple of microamperes even with a drain-source voltage as low as 10 mV. This is due to the presence of a surface

FIGURE 8. Drain current through the device as V\_G is swept through different pH buffers pH 7 to pH 4. Device fin width is 50 nm.

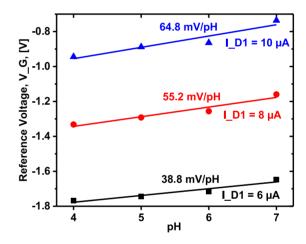

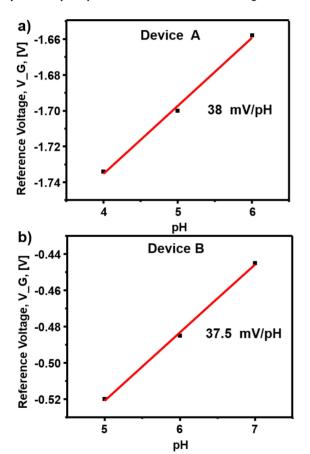

FIGURE 9. Linear pH response extracted at different current levels. Device fin width is 50 nm.

electron accumulation layer in InAs leading to good n-type contacts.

The shift in the drain current curves is further inferred in Fig. 9, where a highly linear response is observed in the reference voltage shift from pH 6 to pH 4 for all the extracted drain current values. When pH 7, is also taken into account the Nernstian sensitivity of 64.8 mV/pH is extracted at 10  $\mu$ A drain current whereas the difference from the Nernstian limit is probably an artifact of experimental linearity related to fitting the data. This sensitivity appears to be lower at a smaller level of the constant current used for extraction, where the sensor response is more linear. In this region we extract a sensitivity of 38.8 mV/pH at 6  $\mu$ A drain current.

In Fig. 10 a double sweep of drain current vs reference voltage is plotted for two pH values. The device displays hysteretic behavior. In the inset, the hysteresis value is calculated to be 108 mV for pH 7 and also lies in the same interval for pH 4.

FIGURE 10. Double sweep of drain current vs reference voltage for pH7 and pH4. Inset: pH7 hysteresis is calculated to be in the range of 0.1 V.

FIGURE 11. Linear pH response extracted at 19  $\mu$ A different current levels.

In Fig. 11 (a) – (b), data from two separate devices with the same fin width of 80 nm are compared. To show the reproducibility in same geometry, sensitivity is extracted at a common current level of 19  $\mu$ A drain current and plotted in Fig. 11 (a) – (b). The pH response is seen to be linear but also close to 40 mV/pH as for the previous device.

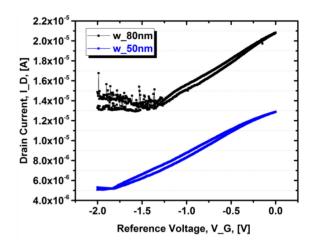

FIGURE 12. Modulation of the ON current for fins of different widths 50 nm and 80 nm.

In Fig. 12 we compare the I D vs V G characteristics from two devices with fin widths of 50 nm and 80 nm at pH 5. The reported curves are a double sweep showing also the hysteresis. From these characteristics, we see that for the wider fin (80 nm) the modulation of the ON current is about 30%, whereas in the case of the narrower fin (50 nm), the modulation of the ON current improves to about 60%. Clearly the devices are still only partially depleted.

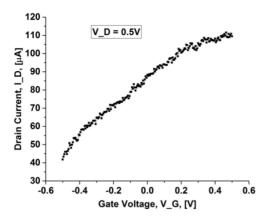

Further characterization was performed on selected devices. A metal gating was realized by means of electron beam induced deposition of platinum and subsequent patterning of this layer using the Focused Ion Beam (FIB) tool. The characteristics of a metal gate FinFET, used for the mobility extraction, are shown in Fig. 13.

A charge-based model for a junctionless transistor has been derived previously [11], [12], leading to an explicit formula describing the drain current. The current equation in the saturation region used for mobility calculation is taken from [12] and it is adapted to our symbol notation:

$$I_{DS} \approx \mu \frac{\beta t_{ox}}{2\varepsilon_{ox}} \frac{H_{Fin}}{L} (qN_{InAs}W_{Fin})^2$$

where  $\beta=1+\frac{\varepsilon_{ox}W_{Fin}}{4t_{ox}\varepsilon_{IpAs}}.$  From this equation the mobility is calculated to be 165 cm<sup>2</sup>/Vs.

### **IV. SIMULATION**

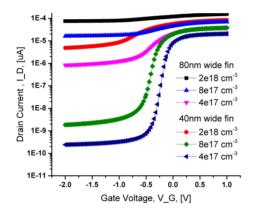

In order to verify the depletion condition for the FinFET structures, Sentaurus TCAD simulations were performed. The FinFET structure is entirely made of InAs with  $H_{Fin} =$ 130 nm and  $W_{Fin} = 40$  nm, 80 nm. It is entirely n-doped. The doping level is varied between 4e17 cm<sup>-3</sup> and 2e18 cm<sup>-3</sup> as the previously known doping limits possible with the MOCVD deposition tool. The gate length  $(L_G)$  is 200 nm. The gate oxide stack consists of 10 nm SiO<sub>2</sub> and 20 nm HfO<sub>2</sub> resembling the fabricated structures. The Shockley-Read-Hall recombination model was applied whereas no trap assisted tunneling models were included. The simulated transfer characteristics are shown in Fig. 14. For the

FIGURE 13. I\_D vs V\_G of the metal gate device with  $V_D = 0.5V$ .

FIGURE 14. TCAD simulation of I\_D vs V\_G transfer characteristics.

80 nm wide fin, even for doubling the doping level, i.e., 4e17 cm<sup>-3</sup> and 8e17 cm<sup>-3</sup>, the modulation of drain current varies much drastically from less than two orders of magnitude (pink curve) to a percentage of the modulated current (bright blue curve).

All the measured devices characteristics correspond to the modulation close to the ON current with high OFF current because there always remained a conducting channel in the FinFET due to a partial liquid gating. Hence, a better control of the non-intentional doping level, narrower fin width and easing pitch design are necessary to observe better modulation of drain current, as indicated by the simulation results obtained for the 40 nm fin.

# V. CONCLUSION

First of all, the proposed method allows for a large scale production of InAs based sensor devices compared to other state of the art platforms. Second, thanks to the inherent surface electron accumulation layer a good contact to InAs is obtained, which is confirmed by high drain current levels even at low drain-source voltages. Finally, from an explicit drain current model we extract mobility of the device to be 165 cm<sup>2</sup>/Vs enabling charge sensing with high level of output current. In this work, we explored and demonstrated, as a proof of concept, that TASE has the capability to achieve a new geometry of HAR InAs FinFETs difficult

TABLE 1. State of the art III-V fin geometry technologies.

| Ref         | Substrate | III-V<br>Type | Indium<br>Mole<br>Fraction | Etching<br>or<br>Growth    | H <sub>FIN</sub><br>(nm) | (nm) | Aspect<br>Ratio,<br>H <sub>FIN</sub> : W <sub>FIN</sub> |

|-------------|-----------|---------------|----------------------------|----------------------------|--------------------------|------|---------------------------------------------------------|

| [13]        | InAs      | InAs          | 1                          | Etching                    | 20                       | 25   | 4:5                                                     |

| [14]        | InAlAs    | InGaAs        | 0.53                       | Etching                    | 50                       | 30   | 5:3                                                     |

| [15]        | InP       | InGaAs        | 0.53                       | Etching                    | 20                       | 30   | 2:3                                                     |

| [16]        | InP       | InGaAs        | 0.7                        | Etching                    | 120                      | 38   | ~3:1                                                    |

| [17]        | InP       | InGaAs        | 0.53                       | MOVPE                      | 16                       | 40   | 2:5                                                     |

| [18]        | InP       | InGaAs        | 0.53                       | Etching<br>Digital<br>Etch | 170<br>170               |      | ~7:1<br>~20:1                                           |

| [19]        | Si        | InGaAs        | 0.7                        | Epitaxy                    | 25                       | 50   | 1:2                                                     |

| [20]        | Si        | InAs          | 1                          | Etching                    | 9                        | 40   | ~1:4                                                    |

| Our<br>Work | Si        | InAs          | 1                          | MOCVD                      | 130                      | 30   | ~4 :1                                                   |

to be achieved by other technologies serving pH sensing. In Table 1 the state- of-the-art geometrical parameters in various III-V FinFET technologies are compared to this work, where InAs FinFETs on Si substrates with one of the highest aspect ratios (4:1) are presented.

In summary, we demonstrated a monolithically integrated, scalable, catalyst-free, CMOS compatible, high aspect ratio InAs-On-Insulator FinFET platform for pH sensing. A good sensitivity of 38.8 mV/pH has been extracted for a couple of devices. The partial depletion is attributed to the high doping level.

### **ACKNOWLEDGMENT**

The Authors would like Interdisciplinary Center for Electron Microscopy at EPFL for the TEM characterization.

# REFERENCES

- [1] P. Bergveld, "The operation of an ISFET as an electronic device," Sensors Actuators, vol. 1, pp. 17–29, 1981.

- [2] F. Patolsky and C. M. Lieber, "Nanowire nanosensors," *Mater. Today*, vol. 8, no. 4, pp. 20–28, 2005.

- [3] P. R. Nair and M. A. Alam, "Performance limits of nanobiosensors," Appl. Phys. Lett., vol. 88, no. 23, 2006, Art. no. 233120.

- [4] J. Du et al., "InAs nanowire transistors as gas sensor and the response mechanism," Nano Lett., vol. 9, no. 12, pp. 4348–4351, 2009.

- [5] K. Rostgaard *et al.*, "Vertical nanowire arrays as a versatile platform for protein detection and analysis," *Nanoscale*, vol. 5, no. 21, pp. 10226–10235, 2013.

- [6] T. Berthing et al., "Intact mammalian cell function on semiconductor nanowire arrays: New perspectives for cell-based biosensing," Small, vol. 7, no. 5, pp. 640–647, 2011.

- [7] S. Upadhyay et al., "Indium arsenide nanowire field-effect transistors for pH and biological sensing," Appl. Phys. Lett., vol. 104, no. 20, 2014, Art. no. 203504.

- [8] Y. Chen, D. Liang, X. P. A. Gao, and J. I. D. Alexander, "Sensing and energy harvesting of fluidic flow by InAs nanowires," *Nano Lett.*, vol. 13, no. 8, pp. 3953–3957, 2013.

- [9] H. Schmid et al., "Template-assisted selective epitaxy of III-V nanoscale devices for co-planar heterogeneous integration with Si," Appl. Phys. Lett., vol. 106, no. 23, 2015, Art. no. 233101.

- [10] D. Cutaia, K. E. Moselund, H. Schmid, M. Borg, A. Olziersky, and H. Riel, "Complementary III-V heterojunction lateral NW Tunnel FET technology on Si," in *Proc. IEEE Symp. VLSI Technol.*, 2016, pp. 11–13.

- [11] A. Yesayan, F. Prégaldiny, and J.-M. Sallese, "Explicit drain current model of junctionless double-gate field-effect transistors," *Solid-State Electron.*, vol. 89, pp. 134–138, Nov. 2013.

- [12] J. P. Duarte, S.-J. Choi, and Y.-K. Choi, "A full-range drain current model for double-gate junctionless transistors," *IEEE Trans. Electron Devices*, vol. 58, no. 12, pp. 4219–4225, Dec. 2011

- [13] R. Oxland et al., "InAs FinFETs with H<sub>fin</sub>= 20 nm fabricated using a top-down etch process," *IEEE Electron Device Lett.*, vol. 37, no. 3, pp. 261–264, Mar. 2016.

- [14] M. Radosavljevic et al., "Electrostatics improvement in 3-D trigate over ultra-thin body planar InGaAs quantum well field effect transistors with high-K gate dielectric and scaled gate-to-drain/gate-to-source separation," in Proc. IEEE Int. Electron Devices Meeting, 2011, pp. 765–768.

- [15] T.-W. Kim et al., "L<sub>g</sub>= 80 nm trigate quantum-well In<sub>0.53</sub>Ga<sub>0.47</sub>As metal–oxide–semiconductor field-effect transistors with Al<sub>2</sub>O<sub>3</sub>/HfO<sub>2</sub> gate-stack," *IEEE Electron Device Lett.*, vol. 36, no. 3, pp. 223–225, Mar. 2015.

- [16] A. V. Thathachary et al., "Indium arsenide (InAs) single and dual quantum-well heterostructure FinFETs," in Proc. IEEE Symp. VLSI Technol. (VLSI Technol.), 2015, p. 417.

- [17] C. B. Zota, L.-E. Wernersson, and E. Lind, "In<sub>0.53</sub>Ga<sub>0.47</sub>As Multiple-Gate Field-Effect Transistors With Selectively Regrown Channels," *IEEE Electron Device Lett.*, vol. 35, no. 3, pp. 342–344, Mar. 2014.

- [18] A. Vardi, J. Lin, W. Lu, X. Zhao, A. Fernando-Saavedra, and J. A. del Alamo, "A Si-compatible fabrication process for scaled selfaligned InGaAs FinFETs," *IEEE Trans. Semicond. Manuf.*, vol. 30, no. 4, pp. 468–474, Nov. 2017.

- [19] L.Czornomaz et al., "Confined epitaxial lateral overgrowth (CELO): A novel concept for scalable integration of CMOS-compatible InGaAson-insulator MOSFETs on large-area Si substrates," in *Proc. Symp. VLSI Technol.*, 2015, pp. T172–T173.

- [20] S.-H. Kim et al., "High performance tri-gate extremely thin-body InAs-On-insulator MOSFETs with high short channel effect immunity and V\_th tunability," *IEEE Trans. Electron Devices*, vol. 61, no. 5, pp. 1354–1360, May 2014.

MANEESHA RUPAKULA received the B.S. degree in electronics and communication engineering in 2011 and the M.S. degree in nanotechnologies for ICTs from Politecnico di Torino, Italy, in 2015. She is currently pursuing the Ph.D. degree in microsystems and microelectronics with the École Polytechnique Fédérale de Lausanne, Switzerland. Her research focuses on nanofabrication of III-V nanostructures for sensing and electronic applications.

JUNRUI ZHANG received the B.S. degree in electronics and the M.S. degree in radio physics from the University of Electronic Science and Technology of China, Chengdu, China, in 2010 and 2013, respectively, and the Ph.D. degree in electronic engineering from EPFL in 2019. From September to December 2013, he was a Research Assistant with the Department of Electrical Engineering, City University of Hong Kong. He is currently a Research Scientist with Xsensio SA, Switzerland, working towards analog IC design

and wearable sensor system.

**FRANCESCO BELLANDO** was born in Torino, Italy, in 1989. He received the master's degree in nanotechnologies for the I.C.Ts from the Politecnico di Torino in 2015, and the Ph.D. degree from EPFL, Switzerland, in 2020, in the field of nanotechnologies for diagnostic applications.

**FABIEN WILDHABER** was born in Valais, Switzerland, in 1983. He received the B.Sc. degree in physics from the EPFL, Lausanne, Switzerland, in 2005, the M.Sc. degree in physics from the ETH Zurich, Switzerland, in 2007, and the Ph.D. degree in microsystem and microelectronics from the EPFL in 2014, for a thesis focused on nanofluidics. In 2016, he joined the startup company Xsensio SA to lead the research and development of microfluidics.

**CLARISSA CONVERTINO** received the B.S. and M.S. degrees in physical engineering and nanotechnologies for ICTs from Politecnico di Torino, Italy, and Paris Diderot University, France, in 2014 and 2016, respectively. She is currently pursuing the Ph.D. degree in microelectronics from EPFL, Switzerland, in collaboration with IBM Research Zurich, Switzerland. Her research focuses on III-V MOSFETs and tunnel-FETs integrated on silicon.

**HEINZ SCHMID** (Member, IEEE) joined the IBM Zurich Research Laboratory in 1984, where he is employed as Senior Engineer with the Science and Technology Department. His current research areas comprise epitaxy of III–V compounds on Si, design and fabrication of scaled III-V devices with a focus on tunnel field effect transistors, FETs, and optical devices.

KIRSTEN EMILIE MOSELUND (Senior Member, IEEE) received the M.Sc. degree in engineering from the Technical University of Denmark, Lyngby, Denmark, in 2003, and the Ph.D. degree in microelectronics from the Swiss Federal Institute of Technology, Lausanne, Switzerland, in 2008. In 2008, she joined the IBM Zurich-Research, where she is currently managing the materials integration and nanoscale devices group, which among other things focuses on the development of III–V on silicon monolithic integration

for novel electronic and photonic device concepts. Her research interests include nanofabrication technology, semiconductor physics, nanophotonics and novel electronic, and photonic device concepts.

ADRIAN MIHAI IONESCU (Fellow, IEEE) received the B.S., M.S., and Ph.D. degrees from the Polytechnic Institute of Bucharest, Romania, and the National Polytechnic Institute of Grenoble, France, in 1989 and 1997, respectively. He is a Professor with the Swiss Federal Institute of Technology, Lausanne, Switzerland. He has held staff and/or visiting positions with LETI-CEA, Grenoble, France, LPCS-ENSERG, Grenoble, and Stanford University, USA, in 1998 and 1999. He has published more than 400 articles in interna-

tional journals and conferences. He received many Best Paper Awards in international conferences, the Annual Award of the Technical Section of the Romanian Academy of Sciences in 1994 and the Blondel Medal in 2009 for remarkable contributions to the progress in engineering sciences in the domain of electronics. He is the 2013 recipient of the IBM Faculty Award in Engineering. He served the IEDM and VLSI conference technical committees and was the Technical Program Committee (Co) Chair of ESSDERC in 2006 and 2013.

VOLUME 8, 2020 779