# Electrothermal modeling of junctionless vertical Si nanowire transistors for 3D logic circuit design

Yifan Wang, Mukherjee Chhandak, Houssem Rezgui, Marina Deng, Cristell Maneux, Sara Mannaa, Ian O'connor, Jonas Müller, Sylvain Pelloquin, Guilhem Larrieu

# ▶ To cite this version:

Yifan Wang, Mukherjee Chhandak, Houssem Rezgui, Marina Deng, Cristell Maneux, et al.. Electrothermal modeling of junctionless vertical Si nanowire transistors for 3D logic circuit design. IEEE 53rd European Solid-State Device Research Conference (ESSDERC 2023), Sep 2023, Lisbon, Portugal. pp.57-60, 10.1109/ESSDERC59256.2023.10268560. hal-04231616

HAL Id: hal-04231616

https://hal.science/hal-04231616

Submitted on 6 Oct 2023

**HAL** is a multi-disciplinary open access archive for the deposit and dissemination of scientific research documents, whether they are published or not. The documents may come from teaching and research institutions in France or abroad, or from public or private research centers. L'archive ouverte pluridisciplinaire **HAL**, est destinée au dépôt et à la diffusion de documents scientifiques de niveau recherche, publiés ou non, émanant des établissements d'enseignement et de recherche français ou étrangers, des laboratoires publics ou privés.

# Electrothermal modeling of junctionless vertical Si nanowire transistors for 3D logic circuit design

Yifan Wang, Chhandak Mukherjee, Houssem Rezgui, Marina Deng, Cristell Maneux University of Bordeaux, Bordeaux INP IMS Laboratory, UMR CNRS 5218

Talence, France yifan.wang@u-bordeaux.fr

Sara Mannaa, Ian O'Connor Univ. Lyon, ECL, INSA Lyon, CNRS, UCBL, CPE Lyon INL, UMR CNRS 5270 Ecully, France Jonas Müller, Sylvain Pelloquin, Guilhem Larrieu University of Toulouse LAAS, UPR CNRS 8001 Toulouse, France

Abstract— This work presents a comprehensive analysis of electrothermal effects in emerging 3D vertical junctionless nanowire transistors (VNWFETs) using on-wafer measurements under a wide range of temperature and validated against numerical and compact model simulations. Experimental observations indicate an increase of the drain current with the temperature, conforming to the behavior of junctionless FETs. Multiphysics simulations reveal formation of temperature hot-spots that adversely affect thermal conductivity in smaller geometries. The VNWFET compact model was then modified to account for the underlying electro-thermal effects as well as dynamic self-heating. Model simulations and the experimental results at different measurement temperatures for different transistor geometries show good agreement. The developed SPICE-compatible compact model was then used for studying the impact of electrothermal effects on the performances of basic 3D logic circuits.

Keywords—electrothermal effects, self-heating, compact model, vertical junctionless nanowire transistors, 3D logic circuit

#### I. INTRODUCTION

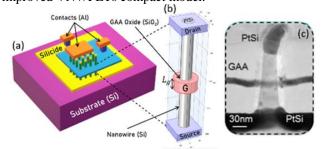

The increasing use of "deep learning" in various areas of computer systems, such as natural language processing, image classification, and speech recognition, has led to an increasing demand for data processing and functionality [1]. New computing paradigms such as neural networks (NN) and in-memory computing have the potential to overcome the bottlenecks of CPU and storage performance differences of traditional von Neumann architectures, but have high hardware requirements in terms of computational efficiency and energy consumption [2]. To develop low-power, lowlatency 3D NN compute cubes, beyond-CMOS technologies such as junctionless vertical nanowire transistors (VNWFET) are being considered as a solution. Its 3D vertical structure achieves a breakthrough in integration by vertically stacking several nanowires, thus increasing the number of devices accommodated per unit area. The transistor fabrication process is simplified due to the uniformly high doping in the junctionless channel, and gate-all-around (GAA) architecture (Fig. 1) offers better immunity against short channel effects (SCE) and improved gate control [3].

In order to exploit the full potential of this state-of-theart, inherently 3D technology, logic circuit design efforts must leverage physics-based, accurate and efficient compact models for realizing innovative 3D circuit architectures through Design-Technology Co-optimization (DTCO) [4]. In particular, the many advantages of compact models in the context of design includes compatibility with design tools and computational efficiency through the use of analytical equations to describe carrier transport in transistors for all possible operating regimes. However, thermal management remains a critical issue for this technology especially due to a lack of understanding of nano-scale heat transport. Moreover, considering the non-classical behavior of junctionless transistors under temperature, it is crucial to take electrothermal effects into account for modeling and design efforts especially to study the impact of these effects on performance metrics such as energy consumption and delay.

In this work, we present a modified VNWFET compact model with integrated electro-thermal and dynamic selfheating effects. Multiphysics simulations are used to investigate the underlying thermal phenomena and identify physical device parameters (such as threshold voltage) that are impacted by these effects. The compact model is then modified to incorporate the temperature dependence of these parameters and is validated against experimental data and numerical simulation. The impact of electrothermal effects on the performance of logic circuits is then predicted through circuit simulations of basic logic cells. The rest of this paper is structured as follows: section II details the compact model improvements, and in section III, validation of the compact model is presented followed by a circuit level analysis to study the impact of electrothermal effects on the basis of the improved VNWFETs compact model.

Figure. 1 Schematic representation of (a) Vertical array of GAA nanowires. (b) A single nanowire. (c) SEM image of a fabricated nanowire [3].

#### II. ELECTROTHERMAL MODELING

The VNWFET compact model is developed based on a unified charge-based control model (UCCM) formulation for junctionless devices while accounting for short-channel effects (SCE), gate-induced drain leakage (GIDL), drain-induced barrier lowering (DIBL), as well as access resistors and Schottky contacts at the source and drain sides [5]. The compact model has been extensively validated against experimental data from the fabricated VNWFETs from LAAS [3] for a wide range of geometries at room temperature. The characteristics of the VNWFETs are strongly impacted by temperature variation, but unlike conventional transistors, the drain current shows a constant increase with increasing temperature. It is understood that in junctionless devices, carrier mobility is quite low due to the high channel doping [6]. Moreover, the variation of mobility

with temperature is also quite weak due to a combination of phonon and impurity scattering [7] and can be thus considered negligible from the electrothermal modeling point of view. The steady increase in the current in junctionless devices is widely attributed to a shift in the threshold voltage [6] and with no significant mobility degradation to counter this effect, the device characteristics exhibit a contrasting temperature dependence with respect to classical FETs. Aided by the understanding of nanoscale thermal transport in VNWFETs through Multiphysics simulations, we analyzed DC temperature measurements to extract thermal parameters such as the temperature coefficients of physical parameters (threshold voltage etc.) and leveraged low-frequency Sparameter measurements [8] to extract the equivalent electrothermal network of the device (consisting of thermal resistance and capacitances) for model development considering (1) temperature dependence of relevant model parameters and (2) dynamic self-heating effect.

# A. Temperature dependence of threshold voltage

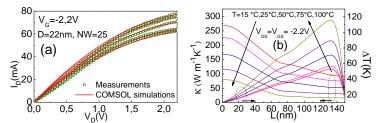

From the experimental observations, it was evident that increasing the temperature leads to a monotonically increasing drain current (Fig. 2(a)) conforming to prior observations in junctionless transistors [6]. To understand the nanoscale heat-transport in the VNWFETs at different temperatures, we investigated them through multiphyiscs simulations using COMSOL [9]. The COMSOL simulations were performed based on the GKE formulation [10] by solving the non-Fourier heat equation and coupling thermal and electrical transport equations. Simulation results showed good agreement with experimental data (Fig. 2(a)). Next, the thermal conductivity between the source and drain of a single nanowire at different temperatures was extracted from the numerical model as shown in Fig. 2(b). The gate-all-around (GAA) architecture of the VNWFET with a SiO<sub>2</sub> layer wrapped around the silicon nanowires makes it challenging to dissipate heat from the device [11]. A significant increase in the device temperature, reflected by an equivalent reduction in the thermal conductivity on the drain side, could be observed that indicated hot-spot formation and subsequent self-heating, even though the temperature rapidly falls off beyond the peak towards the drain contact, which may explain an efficient heat-evacuation through the nanowire. In addition to these observations, expectedly COMSOL simulations indicated a weak mobility variation and a strong variation of the threshold voltage with temperature, affirming that compact model formulation needs to translate these effects in terms of the electrical parameters of the device.

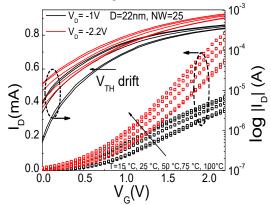

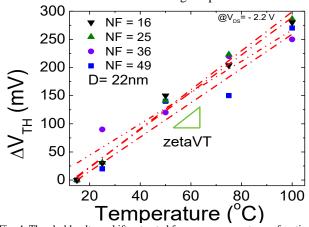

Next, to extract the temperature coefficients for the compact model, we leveraged on-wafer DC  $I_D\text{-}V_G$  measurements (Fig. 3) performed in the 15 °C-100 °C range and extracted the threshold voltage of the VNWFETs as a function of the temperature which showed a linear dependence (Fig. 4). The  $g_m/I_D\text{-}V_G$  method [12] was used for this extraction over the commonly used transconductance method, which is more sensitive to  $V_D$  variation. The  $g_m/I_D\text{-}V_G$  method, on the other hand, is expected to provide more accurate results and is particularly more reliable for junctionless transistors than other methods that may introduce additional uncertainty in threshold voltage extraction at different temperatures.

Fig. 2 (a)  $I_D$ - $V_D$  of a p-type VNWFET comparing COMSOL simulations with DC temperature measurements. (b) Thermal conductivity and internal device temperature under different temperature condition.

Fig. 3.  $I_D$ - $V_G$  measurements at  $V_D$ = -1V and -2.2V at different temperatures.

From the linear dependence of threshold voltage on the measurement temperatures for different device geometries (different nanowires in parallel), an analytical model equation is obtained for the shift of threshold voltage:

$\Delta V_{TH} = zetaVT \times (T_{dev} - T_{nom})$  (1) where zetaVT is the slope of the curves in (Fig. 4),  $T_{dev}$  is the internal device temperature, which is different from the measurement temperature and  $T_{nom}$  is the nominal temperature, in this case 300K, the reference measurement temperature. This analytical equation of  $\Delta V_{TH}$  is then embedded in the VNWFET compact model as an additional contribution to the threshold voltage expression.

Fig. 4. Threshold voltage shift extracted from measurements as a function of temperature.

Additional to this, temperature-induced variation in both access resistances and Schottky barrier height (SBH) [13] of drain and source are considered to be linear with temperature. The temperature coefficients (zetaR, zetaPhi) for these parameters are then introduced in the compact model in a similar manner and are integrated into the existing analytical equations for source-drain resistances ( $R_{S/D}$ ) and Schottky barrier heights ( $PhiSB_{S/D}$ ) as follows:

$$\Delta R_{S/D} = zetaR \times (T_{dev} - T_{nom}) \tag{2}$$

$$\Delta PhiSB_{S/D} = zetaPhi \times (T_{dev} - T_{nom}) \quad (3)$$

These new model parameters (*zetaR*, *zetaPhi*) are then extracted from the compact model calibration against the DC measurement data for temperature-dependent drain current.

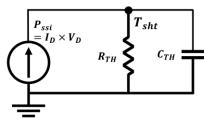

### B. Self-heating effects

In addition to the drift of certain parameter values with temperature, the increase of internal device temperature during device operation is influenced by the self-heating phenomenon. Under dynamic operating conditions, device thermal impedance plays an important role in governing the device temperature and eventually the performances at device and circuit levels. To investigate the self-heating of the VNWFETs, the COMSOL multiphysics model [14] is further exploited to extract the thermal resistance from the heat flux and the device temperature rise observed under high bias conditions [15]. The thermal resistance (R<sub>TH</sub>) can be simply represented by the following equation,

$$R_{TH} = \frac{\Delta T}{P_{ssi}} \tag{4}$$

Here,  $P_{ssi}$  is the dissipated electrical power in Watt, typically calculated by the product of drain voltage and current  $(V_D \times I_D)$ , and  $\Delta T$  is the increase of device temperature. Apart from DC conditions, dynamic self-heating can be modeled by considering the thermal impedance of the transistor. In [8], we extracted the thermal resistance  $(R_{TH})$  and thermal capacitance  $(C_{TH})$  of the VNWFET using low-frequency S-parameter measurements [15], which were then used to construct the equivalent RC filter-like circuit representing the electro-thermal network [16] to account for dynamic self-heating (Fig. 5). This required implementation of an additional fictitious node in the Verilog-A compact model that can be activated through a FLAG parameter when performing transient analysis of VNWFET logic circuits with electrothermal effects.

Fig. 5. RC filter-like electrical equivalent circuit for the implementation of self-heating effects.

Here,  $T_{sht}$  is the device temperature due to self-heating which is dynamically calculated from the voltage of the fictitious node (Fig. 5), through the following relation between its branch currents as implemented in the model,

$$Pssi = \frac{T_{sht}}{R_{TH}} + C_{TH} \frac{dT_{sht}}{d_t}$$

(5)

As indicated from Multiphysics simulations, the self-heating is more pronounced under higher temperature and bias conditions, which is why the extraction of thermal resistance and capacitances were performed at  $V_G$ ,  $V_D = -2.2~V$  to reduce extraction errors. The  $T_{sht}$  contribution was then calculated directly using the extracted values of  $R_{TH}$  (validated using COMSOL) and  $C_{TH}$ . The new device temperature is thus represented by

$$T_{dev} = T_{amb} + T_{sht} \tag{6}$$

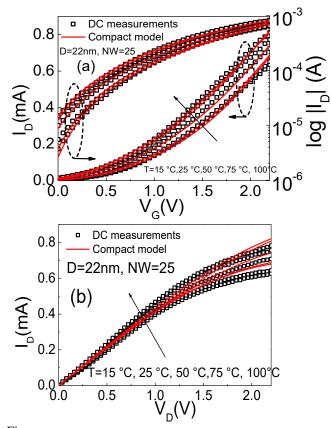

Fig. 6. (a)  $I_D$ - $V_G$  and (b)  $I_D$ - $V_D$  DC measurements at different temperatures compared with compact model simulations.

Finally, the modified compact model with the additional temperature-related and self-heating parameters was simulated under different measurement conditions ( $T_{amb}$ ) which demonstrated good model accuracy, consistent with experimental results, as shown in Fig. 6.

## III. LOGIC CIRCUIT SIMULATIONS

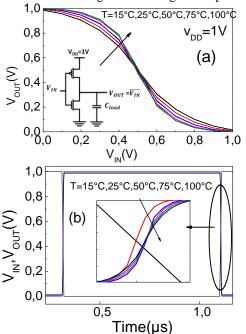

Based on the improved VNWFET compact model and model parameter set calibrated against measurements, we investigated the influence of temperature variation on standard logic circuits composed of VNWFETs. Firstly, a classical CMOS inverter (inset of Fig. 7(a)) consisting of two VNWFETs, a p-type and an n-type, with the same geometrical characteristics, is studied. Fig. 7(a) a shows the static transfer curves of the inverter for different temperatures, whereas Fig 7(b) shows the input (V<sub>IN</sub>) and output (V<sub>OUT</sub>) transient waveforms. From the results it can be observed that the output shows a symmetrical behavior with respect to the input with a balanced switching transition roughly around 0.5V<sub>DD</sub>. Moreover, as temperature increases, we observed a degradation in the logic levels and an increase in the delay time. This can be explained by the drift of threshold voltage caused by electrothermal effects, with which the off-state current (I<sub>OFF</sub>) increases significantly and the increase in the on current (I<sub>ON</sub>) is not sufficient to compensate for the effect of the temperature-induced degradation in the  $I_{\text{ON}}/I_{\text{OFF}}$  ratio, which in turn affects the switching characteristics of the logic cell.

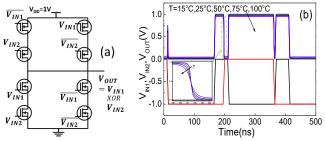

In more complex circuits, such as the XOR logic circuit consisting of eight VNWFETs (along with four additional transistors for the inverters) as shown in Fig. 8(a), the influence of electrothermal effects are visibly more

pronounced. The logic cell output in Fig. 8(b) indicates a classical XOR operation, but the output logic level degradation becomes more significant at higher temperatures.

Fig. 7 (a) Inverter logic circuit (inset) and transfer characteristics, (b) input  $(V_{IN})$  and output  $(V_{OUT})$  transient waveforms at different temperatures.

Fig. 8. (a) XOR logic circuit, (b) inputs  $(V_{IN1}, V_{IN2})$  and output  $(V_{OUT})$  transient waveforms; inset: Output degradation with temperature.

#### IV. CONCLUSION

In this work, we present, for the first time, a comprehensive physics-based compact modeling of electrothermal effects in vertical GAA junctionless nanowire transistors VNWFET. The compact model accounts for underlying electrothermal phenomena aided by in-depth analysis of experimental data and understanding of nanoscale heat transport studied through Multiphysics simulation. The developed model is validated against experimental results showing good agreement between simulation and measurements results at different temperature conditions for different VNWFET geometries. The calibrated compact model is then used for studying standard logic circuits that indicate performance degradation at high temperatures, mainly in terms of delay and a reduction of the output voltage swing, especially for complex logic circuits. As available on/off current ratio continues to decrease at higher temperatures, maintaining circuit functionality meaningful performance can become critical with the current

state of the technology. Hence special attention should be given when designing complex logic circuits using this technology generation and providing feedback to the fabrication process engineers through DTCO loop remains a crucial aspect in the value chain of 3D VNWFET-based 3D computational neuromorphic hardware design.

#### ACKNOWLEDGMENT

This work was supported by the project FVLLMONTI funded by European Union's Horizon 2020 research and innovation program under grant agreement N°101016776 and by the LAAS-CNRS micro and nanotechnologies platform, a member of the Renatech French national network.

#### REFERENCES

- [1] L. B. Letaifa and J. -L. Rouas, "Transformer Model Compression for End-to-End Speech Recognition on Mobile Devices," 2022 30th European Signal Processing Conference (EUSIPCO), pp. 439-443. 2022.

- [2] Javier del Valle, Juan Gabriel Ramírez, Marcelo J. Rozenberg, Ivan K. Schuller, "Challenges in materials and devices for resistive-switching-based neuromorphic computing". Journal of Applied Physics 124 (21): 211101,7 December 2018.

- [3] Y. Guerfi, G. Larrieu "Vertical silicon nanowire field effect transistors with nanoscale gate-all-around" Nanoscale Res Lett 11, 210 (2016).

- [4] C. Maneux et al., "Modelling of vertical and ferroelectric junctionless technology for efficient 3D neural network compute cube dedicated to embedded artificial intelligence," 2021 IEEE International Electron Devices Meeting (IEDM), San Francisco, CA, USA, pp. 15.6.1-15.6.4, 2021.

- [5] C. Mukherjee, P. Arnaud, O. Ian, G. Larrieu, C. Maneux, "Compact Modeling of 3D Vertical Junctionless Gate-allaround Silicon Nanowire Transistors Towards 3D Logic Design". Solid-State Electronics, 183, pp.108125, 2021.

- [6] R. Trevisoli Doria, M. de Souza, S. Das, I. Ferain, M. Antonio Pavanello; "The zero-temperature coefficient in junctionless nanowire transistors". Appl. Phys. Lett. 6 August 2012; 101 (6): 062101.

- [7] JP. Colinge, CW. Lee, A. Afzalian, ND. Akhavan, R. Yan, I. Ferain, P. Razavi, B. O'Neill, A. Blake, M. White, AM. Kelleher, B. McCarthy, R. Murphy. "Nanowire transistors without junctions". Nat Nanotechnol. 2010 Mar;5(3), 225-229. Epub 2010 Feb 21.

- [8] C. Mukherjee, H. Rezgui, M. Deng, A. Kumar, J. Muller, G. Larrieu, C. Maneux, "Nanoscale Thermal Transport in Vertical Gate-all-around Junction-less Nanowire Transistors- Part I: Experimental Methods", IEEE Trans. Electron Dev. 2023. (submitted)

- [9] COMSOL, Inc., COMSOL Multiphysics

- [10] H. Rezgui et al., "Design optimization of nanoscale electrothermal transport in 10 nm SOI FinFET technology node", J. Phys. D: Appl. Phys, vol. 53, 2020

- [11] E. Pop, R. Dutton and K. Goodson, "Thermal analysis of ultra-thin body device scaling [SOI and FinFet devices]", IEEE International Electron Devices Meeting 2003, Washington, DC, USA, pp. 36.6.1-36.6.4. 2003.

- [12] T. Rudenko, V. Kilchytska, M. K. Md Arshad, J. -P. Raskin, A. Nazarov and D. Flandre, "On the MOSFET Threshold Voltage Extraction by Transconductance and Transconductance-to-Current Ratio Change Methods: Part II—Effect of Drain Voltage," in IEEE Transactions on Electron Devices, vol. 58, no. 12, pp. 4180-4188, Dec. 2011.

- [13] S. Karataş, S. Altındal, A. Türüt, A. Özmen (2003). Temperature dependence of characteristic parameters of the H-terminated Sn/p-Si(1 0 0) Schottky contacts, 217(1-4), 250–260, 2003.

- [14] Y. Wang, H. Rezgui, C. Mukherjee, M. Deng, J. Muller, S. Pelloquin, G. Larrieu, C. Maneux, "Evidence of Trapping and Electrothermal Effects in Vertical Junctionless Nanowire Transistors", EuroSOI-ULIS, 2023.

- [15] C. Mukherjee et al., "Scalable Modeling of Thermal Impedance in InP DHBTs Targeting Terahertz Applications," in IEEE Transactions on Electron Devices, vol. 66, no. 5, pp. 2125-2131, May 2019.

- [16] G. J. Coram, "How to (and how not to) write a compact model in Verilog-A," Proceedings of the 2004 IEEE International Behavioral Modeling and Simulation Conference. BMAS 2004., San Jose, CA, USA, 2004, pp. 97-106,