## Design and Characterization of a Hardware Encryption Management Unit for Secure Computing Platforms

Anthony J. Mahar

Thesis submitted to the Faculty of the Virginia Polytechnic Institute and State University in partial fulfillment of the requirements for the degree of

> Master of Science in Computer Engineering

Peter M. Athanas, Chair Mark T. Jones Cameron D. Patterson

June 3, 2005 Blacksburg, Virginia

Keywords: secure computing, encryption, cryptography, secure processors Copyright 2005, Anthony J. Mahar

## Design and Characterization of a Hardware Encryption Management Unit for Secure Computing Platforms

Anthony J. Mahar

#### (ABSTRACT)

Software protection is increasingly necessary for a number of applications, ranging from commercial systems and digital content distributors, to military systems exposed in the field of operations. As computing devices become more pervasive, and software more complex, insufficiencies with current software protection mechanisms have arisen. Software–only and data–only protection systems have resulted in broken systems that are vulnerable to loss of software confidentiality and integrity.

A growing number of researchers have suggested that hardware encryption mechanisms be employed to enforce software protection. Although there are several competing architectures, few offer the necessary protection while remaining compatible with modern computing systems and models. The Virginia Tech Secure Software Platform is the first architecture to achieve both increased protection and usability.

This thesis presents the design and implementation of a fast, flexible Encryption Management Unit (EMU) for Virginia Tech Secure Software and compatible platforms. The design is capable of providing decryption of program instructions residing in page–sized sections of memory, without modification to the core processor. The effect of the EMU is modeled with varying application types and system loads. Lastly, a benchmark designed to measure actual performance was created to measure the actual performance of the EMU and validate the models.

## Acknowledgments

I would like to thank my committee chair, adviser and instructor Dr. Peter Athanas. I am extremely grateful for the mutual trust and respect that has developed during my time at Virginia Tech. His patience and continual review of this work has been instrumental in the development of this thesis.

I would like to thank Dr. Mark Jones as an adviser and committee member. His advice on academia and matters of life have proved extremely enlightening.

I would like to thank Dr. Cameron Patterson for serving as a committee member. I have learned much from Dr. Patterson on personal happiness in and outside of academia.

All three of these individuals have earned so much respect and admiration for the support and confidence they have offered over the years. Each of their own personal career paths and successes has provided much inspiration and demonstrates such exciting opportunities. It is an honor and pleasure to have worked with each of them.

Additionally, I would like to thank the members of the Virginia Tech Secure Software Project research group: Justin Stroud, Benjamin Muzal, and especially Joshua Edmison. It is a rare opportunity to work in a team with such incredible cohesion, individual responsibility, and communication.

I would like to thank Luna Innovations, especially Jonathan Graf and Barry Polakowski, for providing the joint research funding and objectives for the Virginia Tech Secure Software Project. I would like to thank the old crew from the Virginia Tech Configurable Computing Lab, who have made my time at Virginia Tech one of the most enjoyable and memorable. These true friends include Stephen Craven, David Lehn, Neil Steiner, Alex Poetter, and Jesse Hunter.

I would like to thank Barry Mapen for being a wonderful friend and mentor, Dr. Ian Greenshields for encouraging graduate studies and providing superb insight into academia, and Roger Leege for instilling an enjoyment of engineering and research disciplines.

Lastly, and most importantly, I would like to thank my parents, Christine and Joseph Mahar. Their unwavering support, love, and interest in my academic career has provided a continued source of strength and inspiration that I am eternally grateful for. I certainly would not have been successful without them.

## Contents

| Li            | st of | Figures                                    | x   |

|---------------|-------|--------------------------------------------|-----|

| $\mathbf{Li}$ | st of | Tables                                     | xii |

| 1             | Intr  | roduction                                  | 1   |

|               | 1.1   | Motivations                                | 1   |

|               | 1.2   | Contributions                              | 4   |

|               | 1.3   | Implementation Platform                    | 5   |

|               | 1.4   | Thesis Organization                        | 5   |

| <b>2</b>      | Bac   | kground                                    | 6   |

|               | 2.1   | Secure Computing                           | 6   |

|               | 2.2   | Software Threats                           | 9   |

|               | 2.3   | Virginia Tech Secure Software Architecture | 10  |

|               |       | 2.3.1 Paged Protection                     | 11  |

|               |       | 2.3.2 Primary Components                   | 12  |

|               |       | 2.3.3 Lifetime of a Secure Application     | 15  |

|   |     | 2.3.4  | Protections                                                                                         | 16 |

|---|-----|--------|-----------------------------------------------------------------------------------------------------|----|

|   | 2.4 | Relate | ed Memory Modification Units                                                                        | 18 |

|   |     | 2.4.1  | IBM CodePack                                                                                        | 18 |

|   |     | 2.4.2  | ХОМ                                                                                                 | 20 |

|   | 2.5 | Bench  | marking                                                                                             | 22 |

| 3 | Des | ign    |                                                                                                     | 25 |

|   | 3.1 | Encry  | ption Management Unit Requirements                                                                  | 25 |

|   |     | 3.1.1  | Scope                                                                                               | 25 |

|   |     | 3.1.2  | Functional Integration                                                                              | 26 |

|   |     | 3.1.3  | Operational Concept                                                                                 | 26 |

|   |     | 3.1.4  | Functional Requirements                                                                             | 27 |

|   | 3.2 | Encry  | ption Management Unit Specification                                                                 | 28 |

|   |     | 3.2.1  | Functional Constraints                                                                              | 28 |

|   |     | 3.2.2  | Primary Functional Units                                                                            | 29 |

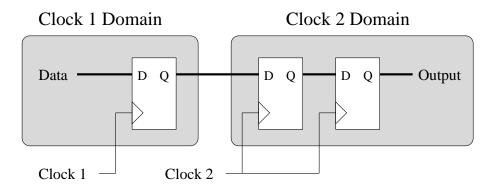

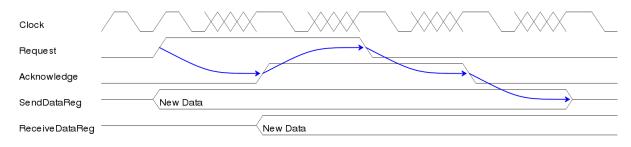

|   |     | 3.2.3  | Asynchronous Protocols                                                                              | 36 |

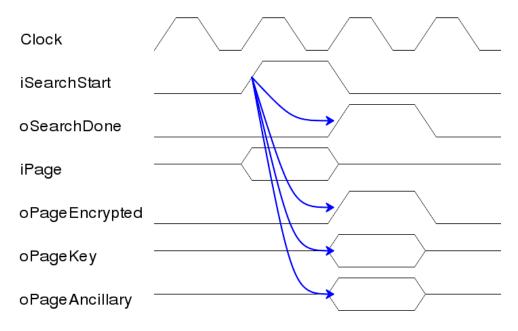

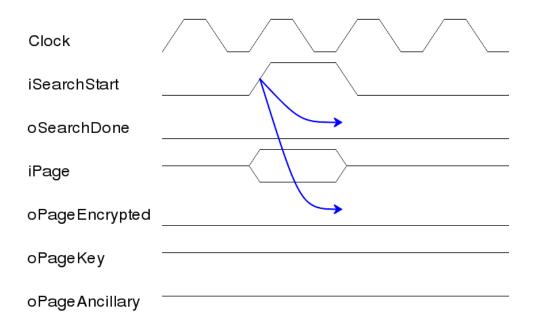

|   |     | 3.2.4  | Interface Protocols                                                                                 | 38 |

|   | 3.3 | Imple  | mentation $\ldots$ | 44 |

|   |     | 3.3.1  | Bus Modifier / Bridge Unit                                                                          | 44 |

|   |     | 3.3.2  | Table Unit                                                                                          | 53 |

|   |     | 3.3.3  | Control Units                                                                                       | 55 |

|   |     | 3.3.4  | OPB Control Interface Unit                                                                          | 57 |

| 4            | Mo                   | deling                     | 58 |

|--------------|----------------------|----------------------------|----|

|              | 4.1                  | Latency Modeling           | 58 |

|              | 4.2                  | Modeling Slow Down         | 60 |

| <b>5</b>     | Ben                  | chmarking                  | 62 |

|              | 5.1                  | Methodology                | 62 |

|              | 5.2                  | iBench Design              | 64 |

|              | 5.3                  | iBench Validation          | 66 |

| 6            | $\operatorname{Res}$ | ults                       | 70 |

|              | 6.1                  | Latency                    | 71 |

|              | 6.2                  | Slow Down                  | 74 |

| 7            | Fut                  | ure Directions             | 78 |

|              | 7.1                  | EMU Design Directions      | 78 |

|              | 7.2                  | EMU Performance Directions | 80 |

|              | 7.3                  | iBench Directions          | 81 |

| 8            | Con                  | clusion                    | 83 |

| Bi           | bliog                | graphy                     | 86 |

| $\mathbf{A}$ | Pag                  | e Table Control Registers  | 92 |

|              | A.1                  | Page Base Address Register | 92 |

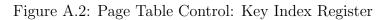

|              | A.2                  | Key Index Register         | 93 |

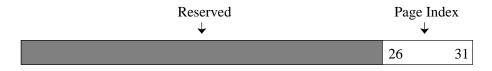

|   | A.3 | Page Index Register                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 94                              |

|---|-----|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------|

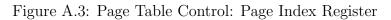

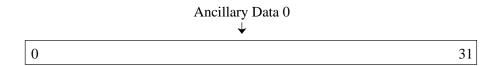

|   | A.4 | Ancillary Data 0 Register                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 95                              |

|   | A.5 | Ancillary Data 1 Register                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 96                              |

|   | A.6 | Ancillary Data 2 Register                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 97                              |

|   | A.7 | Ancillary Data 3 Register                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 98                              |

| В | Key | Table Control Registers                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 99                              |

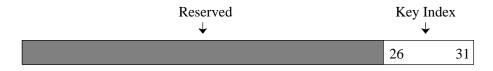

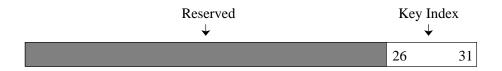

|   | B.1 | Key Index Register                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 99                              |

|   | B.2 | Key Word 0 Register                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 100                             |

|   | B.3 | Key Word 1 Register                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 101                             |

|   | B.4 | Key Word 2 Register                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 102                             |

|   | B.5 | Key Word 3 Register                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 103                             |

| С | Ben | chmark Results                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 104                             |

|   |     |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |                                 |

|   | C.1 | LMBench                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 104                             |

|   |     | LMBench       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       . </td <td></td> |                                 |

|   |     |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 104<br>107                      |

|   |     | iBench                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 104<br>107                      |

|   |     | iBench                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 104<br>107<br>107               |

| D | C.2 | iBench                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 104<br>107<br>107<br>110        |

| D | C.2 | iBench                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 104<br>107<br>107<br>110<br>113 |

|     | D.1.2  | Bridge_CPU_Interface.vhd                                                                              | 122 |

|-----|--------|-------------------------------------------------------------------------------------------------------|-----|

|     | D.1.3  | Bridge_Memory_Interface.vhd                                                                           | 125 |

|     | D.1.4  | Bridge_BlockModeDecrypt.vhd                                                                           | 128 |

|     | D.1.5  | Bridge_CounterModeDecrypt.vhd                                                                         | 136 |

|     | D.1.6  | Tables.vhd                                                                                            | 142 |

|     | D.1.7  | PageTableControl.vhd                                                                                  | 149 |

|     | D.1.8  | KeyTableControl.vhd                                                                                   | 155 |

|     | D.1.9  | OPB_ControlInterface.vhd                                                                              | 160 |

| D.2 | iBench | Assembly                                                                                              | 165 |

|     | D.2.1  | Compile and Execution                                                                                 | 165 |

|     | D.2.2  | walk.s                                                                                                | 165 |

|     | D.2.3  | append.c                                                                                              | 169 |

|     | D.2.4  | time_conv.c $\ldots$ | 170 |

|     | D.2.5  | makescripts.c                                                                                         | 171 |

# List of Figures

| 2.1  | Single Processor Secure Software Architecture | 12 |

|------|-----------------------------------------------|----|

| 2.2  | IBM CodePack Architecture                     | 19 |

| 3.1  | EMU Primary Functional Units                  | 30 |

| 3.2  | EMU Primary Clock Domains                     | 36 |

| 3.3  | Full Synchronization Unit                     | 37 |

| 3.4  | Base Asynchronous Protocol                    | 38 |

| 3.5  | Protocol: Table Search, Encrypted Return      | 40 |

| 3.6  | Protocol: Table Search, Unencrypted Return    | 41 |

| 3.7  | Control Interface Protocol: Read              | 43 |

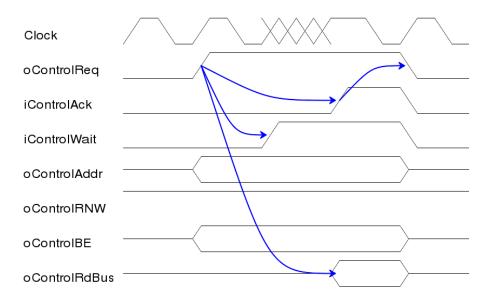

| 3.8  | Control Interface Protocol: Write             | 43 |

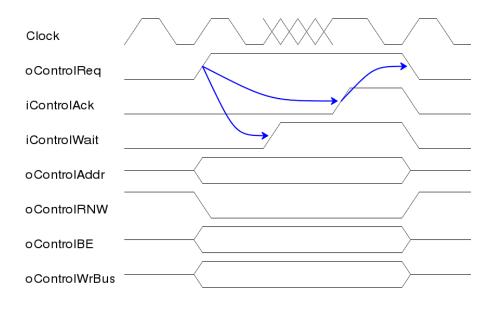

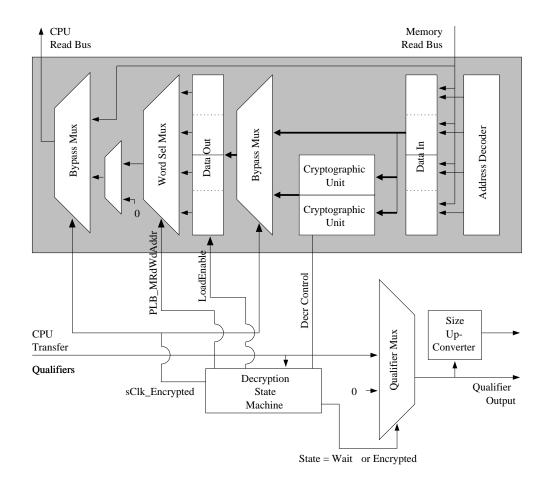

| 3.9  | Bridge Unit                                   | 46 |

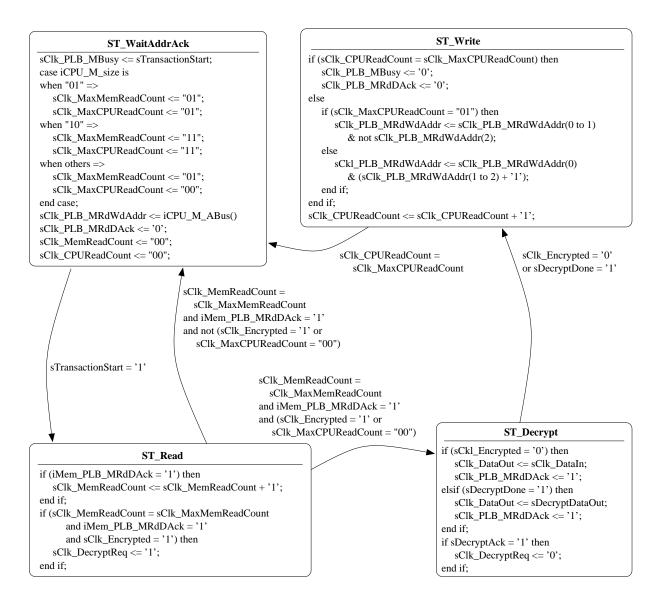

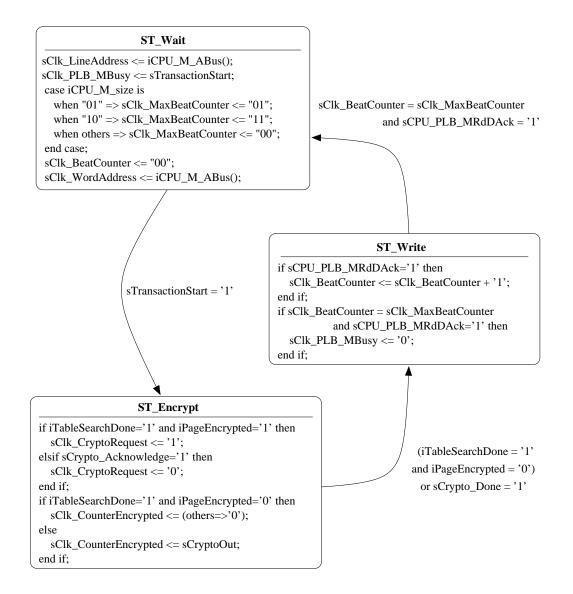

| 3.10 | Block Mode Decryption Finite State Machine    | 48 |

| 3.11 | Block Mode Decryption Module                  | 49 |

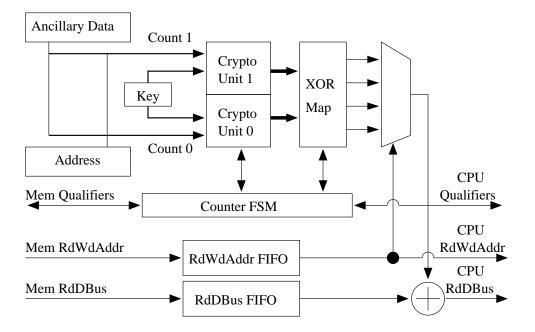

| 3.12 | Counter Mode Decryption Module                | 51 |

| 3.13 | Counter Mode Decryption Finite State Machine  | 52 |

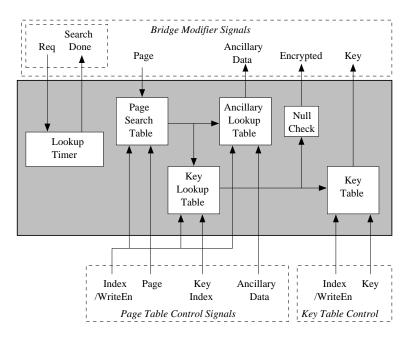

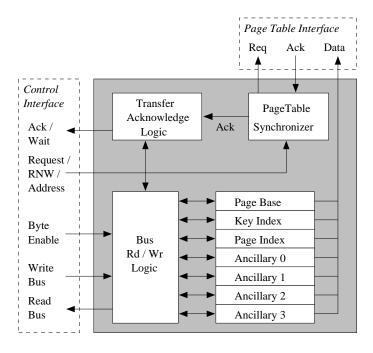

| 3.14 | Table Unit   5                                           | 3 |

|------|----------------------------------------------------------|---|

| 3.15 | Page Table Control Unit                                  | 6 |

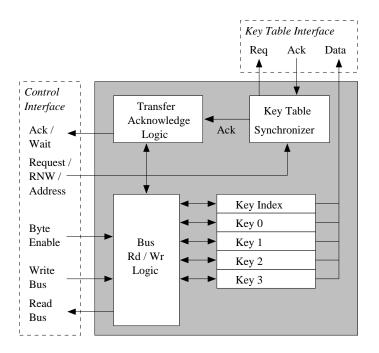

| 3.16 | Key Table Control Unit                                   | 6 |

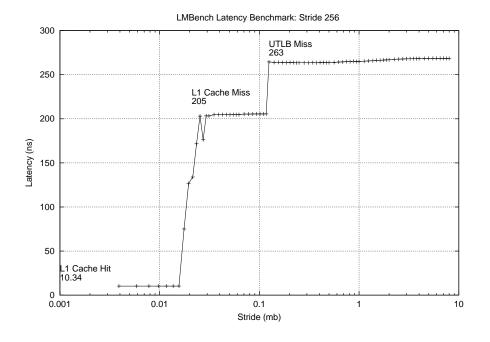

| 5.1  | LMBench Latency Benchmark: Data memory subsystem         | 3 |

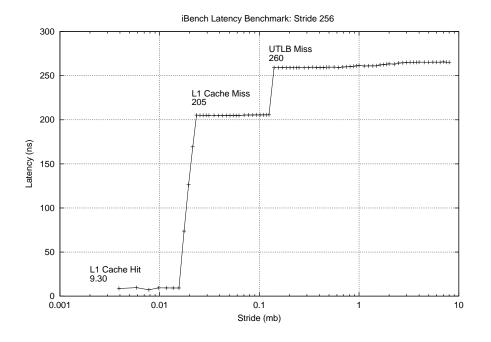

| 5.2  | iBench Latency Benchmark: Instruction memory subsystem 6 | 7 |

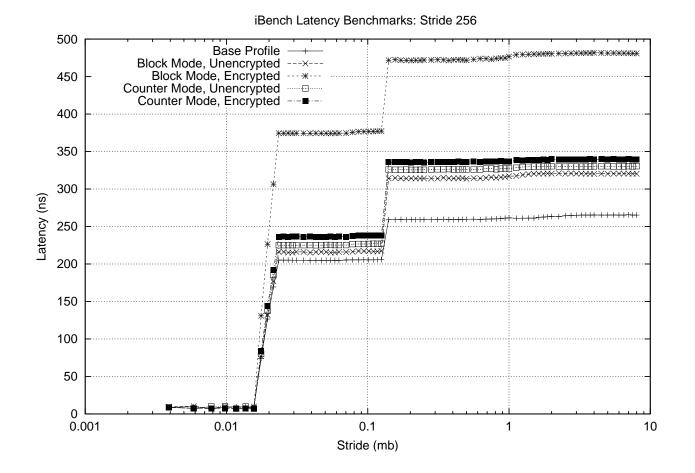

| 6.1  | Complete iBench latency measurements                     | 2 |

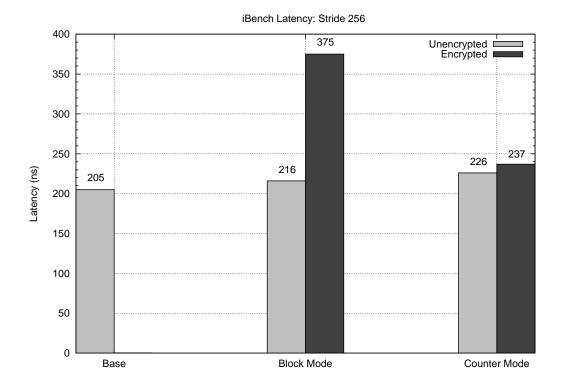

| 6.2  | iBench memory fetch latency measurements                 | 3 |

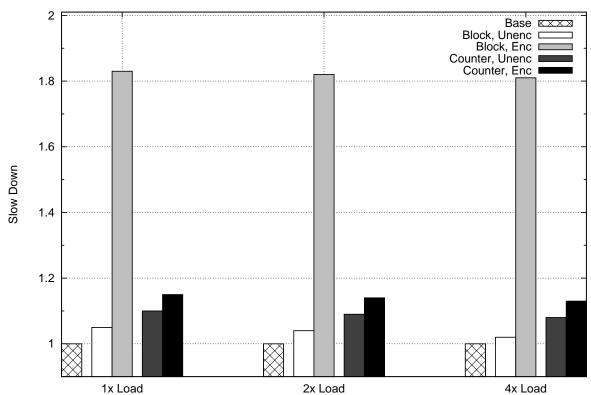

| 6.3  | Slow down over various loads and profiles                | 6 |

| A.1  | Page Table Control: Page Base Address Register           | 2 |

| A.2  | Page Table Control: Key Index Register                   | 3 |

| A.3  | Page Table Control: Page Index Register                  | 4 |

| A.4  | Page Table Control: Ancillary Data 0 Register            | 5 |

| A.5  | Page Table Control: Ancillary Data 1 Register            | 6 |

| A.6  | Page Table Control: Ancillary Data 2 Register            | 7 |

| A.7  | Page Table Control: Ancillary Data 3 Register            | 8 |

| B.1  | Key Table Control: Key Index Register                    | 9 |

| B.2  | Key Table Control: Key Word 0 Register                   | 0 |

| B.3  | Key Table Control: Key Word 1 Register                   | 1 |

| B.4  | Key Table Control: Key Word 2 Register                   | 2 |

| B.5  | Key Table Control: Key Word 3 Register                   | 3 |

## List of Tables

| 3.1 | Page Table Control Unit Registers          | 34 |

|-----|--------------------------------------------|----|

| 3.2 | Key Table Control Registers                | 35 |

| 3.3 | Used PLB Instruction–Side Bus Signals      | 39 |

| 3.4 | Page Table Control Protocol Data Signals   | 41 |

| 3.5 | Key Table Control Protocol Data Signals    | 42 |

| 5.1 | Memory Latency by Stage                    | 68 |

| A.1 | Page Base Address Register Bit Definitions | 92 |

| A.2 | Key Index Register Bit Definitions         | 93 |

| A.3 | Page Index Register Bit Definitions        | 94 |

| A.4 | Ancillary Data 0 Register Bit Definitions  | 95 |

| A.5 | Ancillary Data 1 Register Bit Definitions  | 96 |

| A.6 | Ancillary Data 2 Register Bit Definitions  | 97 |

| A.7 | Ancillary Data 3 Register Bit Definitions  | 98 |

| B.1 | Key Index Register Bit Definitions         | 99 |

| B.2 | Key Word 0 Register Bit Definitions       | 100 |

|-----|-------------------------------------------|-----|

| B.3 | Key Word 1 Register Bit Definitions       | 101 |

| B.4 | Key Word 2 Register Bit Definitions       | 102 |

| B.5 | Key Word 3 Register Bit Definitions       | 103 |

| C.1 | Base Profile Memory Fetch Latency         | 110 |

| 0.1 |                                           | 110 |

| C.2 | Block Mode Profile Memory Fetch Latency   | 111 |

| C.3 | Counter Mode Profile Memory Fetch Latency | 112 |

| C.4 | Base Profile Execution Time               | 113 |

| C.5 | Block Mode Profile Execution Time         | 114 |

| C.6 | Counter Mode Profile Execution Time       | 115 |

## Chapter 1

## Introduction

There are a number of key motivations for conducting this line of research. Reasons include opportunities to advance the state of the art in the field, to conduct research with a successful platform, and to solve deficiencies within the field. These motivations directly support the contributions presented in this work.

## 1.1 Motivations

The primary reason for conducting this research is to contribute to the Virginia Tech Configurable Computing Lab's Secure Software Project [1]. Software protection is currently an extremely active research area with proposed solutions coming from leaders in the computer industry and academic institutions. This research involves the development of methods for maintaining the confidentiality and integrity of software during distribution, in local storage and memories, and during execution.

While there exist other proposed architectures in this research, however most either lack complete protection protection or require mechanisms that do not integrate well in modern platforms. These systems often include required trust in parts of software, or requiring modifications, sometimes fundamental, to the operating system and processor. The inherited trust model used by many software protection systems [2] has already been demonstrated [3] as readily exploitable. When a trusted module is compromised it can become a staging point for further attacks.

Systems relying less on an inherited trust models [4] [5] typically require fundamental changes to the way software operates and how the processor and operating system interact with the software. This includes running software inside individual virtual machines, addition of secure instructions and registers, or lack of shared libraries, shared memory, and standard inter-process communication mechanisms. These systems may provide software protection, however they cannot easily incorporate into modern computer systems due to the fundamental changes and incompatibilities with current software models.

The Virginia Tech Secure Software architecture is the first platform to provide increased software protection while maintaining standard development and computing models. This architecture avoids using special instructions or special operations to interact with shared memory, libraries, or other applications. This permits the developer to maintain their compiler tool flow. To increase protection, selected groups of instructions in the executable are tagged and encrypted, and then distributed to systems that will run the application. As protected instructions remain encrypted, the software can be distributed over standard and potentially insecure channels. When the application is executed on a Secure Software architecture, partial credentials stored in the executable are merged with a set of user supplied credentials securely on the chip, producing a set of one or more decryption keys.

The Secure Software architecture enforces an execute–only policy on protected instructions. This is achieved in several ways, depending on the architecture configuration. In some cases, only the instruction–side bus interface has a decryption unit, in other instances, when there is also a data–side decryption unit, the system can forces the use of different keys for each side. Without a corresponding data–side decryption unit and key set, the CPU cannot directly read or write protected instructions. This secure support is achieved without modification to the processor core.

With the VT Secure Software architecture, trust is not required of the operating system or any other software module. Although the operating system (OS) associates groups of instructions, in the form of memory pages, with a key, it is only aware of a pointer to a key in a hardware key table, and can never access the keys under any circumstance. To establish this relationship between groups of instructions and key pointers, the system extends the memory page handling mechanisms already used in modern operating systems.

The second motivation for this work stems from additional deficiencies in the secure computing field of research. From the existing set of secure architectures, only a few attempt to model the performance effect of their protection mechanisms. When modeling is provided, there is not sufficient verification of the model, which is often due to lacking an actual implementation to verify with. Application-based benchmarks are performed in architectural simulators using assumed latencies of secure extensions. These simulations, however, do not properly reflect true latencies that are often discovered only during implementation. Additionally, these simulated benchmarks fail to represent certain non-deterministic processor behavior, or the variability found within modern multi-tasking operating systems.

The third motivation results from the necessity to properly benchmark and measure latencies associated with the instruction-side interface of processors. There are many benchmarks available, including benchmarks for parallel computing, operating system characteristics, disk I/O, memory bandwidth, memory latencies, and more. Memory latency benchmarks are the most important benchmark when characterizing software protection platforms. The software protection extensions can add delay when fetching instructions from memory, due to the cryptographic process. In the present implementation of the Secure Software Platform, protections are afforded primarily to instructions, therefore a benchmark is required to correctly measure the latency of memory fetch on the instruction-side bus. As an instruction-side benchmark does not exist either commercially or in the public domain, one such benchmark had to be developed.

### **1.2** Contributions

Within the Virginia Tech Secure Software Project there are several core components of research, each contributing to the increase of protected software execution. These research components include hardware encryption management, secure key management, operating system extensions, formal methods of security validation, and integration with parallel computing environments. The primary contribution of this work is the design and implementation of an Encryption Management Unit, or *EMU*, to support the execution of protected instructions.

During the development of the EMU, considerable effort was given to design, employing several important software and hardware engineering techniques. The goals in using these techniques were to focus on the overall design problem, while avoiding implementation details. A cohesive set of modules was created to permit reuse of the EMU and its internal modules, and to remain adaptable to continual changes in EMU requirements. This is necessary as the overall Secure Software architecture improves and develops. When the high– level design was complete, implementation of the EMU required that latency be reasonably minimized given the constraints on area and time of the prototype.

The second contribution of this work is modeling the behavior of the EMU within a standard multi-tasking platform. Mathematical models were derived to determine the effect on performance of the EMU under various decryption algorithms and modes. These models also account for variations in application type and operating system loads in a multi-tasking system.

To verify the accuracy of these models, a synthetic benchmark, called *iBench*, was created for measuring instruction–side bus memory latencies was researched, created, and verified for accuracy. With the validity of *iBench* established, the benchmark was used to directly evaluate the VT Secure Software platform under several system profiles. The results were also used in verification of the mathematical models previously derived.

### **1.3** Implementation Platform

The hardware platform used for implementation was a Xilinx Virtex–II Pro [6] Field Programmable Gate Array (FPGA). The Virtex–II Pro contains an IBM PowerPC 405 embedded processor [7] surrounded by reconfigurable logic. The FPGA is mounted on a Xilinx ML–310 [8] embedded development board, which contains a representative set of memory types and peripherals found on modern computers.

These features provide a comprehensive hardware/software platform running with a complete Linux operating system. The reconfigurable fabric of the FPGA allows the instantiation of the EMU and other components on the same physical chip of the the processor. The Xilinx Embedded Development Kit [9] (EDK) is a design tool that provides high level management of hardware component cores instantiated in the FPGA. With this tool, cores are easily added, removed, parametrized, and attached to standard bus structures within the system, creating a configurable system–on–chip (SoC). These features allow the rapid integration of VT Secure Software Project hardware extensions into the embedded SoC design.

### 1.4 Thesis Organization

This thesis is organized in the following manner. Chapter 2 presents background information on the secure software field of research, the Virginia Tech Secure Software Project, and related work. Chapter 3 details the design of the Encryption Management Unit and its interaction within the system. Chapter 4 provides mathematical models to determine the effect of the EMU with respect to multi-tasking environments. Chapter 5 describes *iBench*, the benchmark created to measure latency of the EMU and memory subsystem. Chapter 6 provides performance results of the EMU under several platform configurations. Chapter 7 discusses future directions of this work. Finally, Chapter 8 concludes this thesis with a summary of the contributions of this work.

## Chapter 2

## Background

This section provides a background required to provide proper context for the work presented in this thesis. Important areas include the history of secure computing, backgrounds on different types of software threats, systems with functional similarities to the EMU, and methods for benchmarking secure software systems.

## 2.1 Secure Computing

Security has maintained an important role in software since the beginning of digital computing. Computers are commonly used to perform operations on sensitive data where the data and the computational instructions must be protected. Initially, digital computing devices operating on sensitive information were physically isolated, and protection required physical security. These devices were operated by personnel with appropriate authorization, resulting in an implicit line of trust between secure software and authorized user. However, as computing devices became more pervasive and interconnected, the need for secure computing in insecure locations and without trusted users became necessary.

Initial attempts [10] into software protection produced processors augmented with various

protection mechanisms. Features included specialized instructions for cryptographic acceleration, encryption of instructions and data in external memory, physical package anti-tamper mechanisms, and external memory address obfuscation. At the time, it was thought that these processors could run a single application securely, providing encryption and obfuscation for any instruction or data placed into external memory. Only recently has other research shown [11] these protections were inadequate.

The fundamental task of a processor is to execute instructions. With the secure cryptoprocessor, instructions are decrypted as they are retrieved from memory and then executed. Even if instructions reside as encrypted in external memory, it is possible to randomly alter the contents of memory and observe the system reaction to executing the decrypted random value. Starting with the processor's boot instruction, an attacker can guess possibilities for encrypted instructions and place them at that initial boot location. If there is an observable effect, such as access to memory mapped I/O, the guesses can be refined until a complete instruction with a desired effect is determined. Iterating for several instructions allow a small encrypted program to be constructed by an attacker, which can then be used as a staging platform to access protected memory from within the processor.

A typical consumer of secure processors at the time, and one that highlights a common scenario in the era, were financial institutions. Remote computing nodes such as bank terminals and automated teller machines were located outside physically protected domains, and were potentially exposed to attacks by adversaries in possession of the devices. These machines did not need much processing power, but instead required extreme integrity and confidentiality of software instructions and data. As software distribution and installation was considered secure, and the processor ran a single dedicated program, attacks were limited to software in memory and memory buses. The intent of adversaries included modification of program data to alter transactions, or snooping a processor's buses for account theft. Software protection from these threats required software confidentiality and integrity of program data and instructions when in memory outside the processor core. Over the past decade there has been a growing push towards enabling secure computing in modern multi-tasking platforms. There are many reasons for this, such as the growth of software piracy [12] [13], protection of digital media in new content distribution markets, protection of intellectual property of proprietary algorithms, and more. Simply upgrading processor architectures and cryptographic macros from the first generation of secure processors does not provide a complete solution required of securing modern computing models. Encrypting all external memory with the same encryption key still leaves the system vulnerable to internal threats from other malicious software or faulty operating systems. Developers could not rely only on a specific set of trusted software to be running. Instead, there were many applications running concurrently, and many without user or developer trust.

Modern computing platforms are capable of running multiple applications concurrently. This is possible through features such as virtual memory and supervisory operating systems. Security had to be handled in a manner that would allow one application to be protected from external threats in addition to other software running on the processor, operating system or otherwise. This required that secure extensions to a multi–tasking platform must provide security mechanisms to isolate one secure application from any other application or operating system not sharing the same set of access rights.

One approach to solving this problem was through various forms of obfuscation. Obfuscation relies on the ability to confuse an adversary attempting to gather information about software operations. Techniques included code obfuscation, where program instruction execution flows and data formats are mangled, and bus protocols that would attempt to hide the execution flow or data access patterns of external memory. While both were easy to implement and did not impact performance much, these approaches were either rejected [14] on provable of insecurity, or quickly broken [3].

A number of secure multi–tasking architectures using hardware cryptographic protections were developed from the realization that these previous mechanisms were insufficient. Each one differed in their level of use in trusted software components, their method of hardware protection, and what protections were offered. The protections for software reduced into two primary classifications: software confidentiality and software integrity. Some architectures also define data confidentiality and integrity as part of software protection. [15] further discusses the area of research, the different secure mechanisms, and their security implications.

Although these architectures provide software protection through various mechanisms, another important metric for success is the difficulty of integration into actual hardware– software architectures. Some architectures, such as [16] and [17], require modification of the core processing unit with additional instructions and special registers. While the goals of these architectures offer state of the art capabilities, they are difficult to prototype and to implement; commercial off the shelf (COTS) processor cores are not easily be used with these systems. Furthermore, mechanisms for common abilities such as inter–process communication and shared memory are not sufficiently addressed.

At the time of this work, only two architectures are known to have demonstrated successful implementation. These include the Virginia Tech Configurable Computing Laboratory Secure Software architecture [1] and the Trusted Computing Group (TCG) Trusted Platform Module (TPM) specification [2]. The TCG architecture has already seen wide–spread adoption, mostly through backing from leaders in the operating system and processor markets. Unfortunately, it relies on the inherited trust model and is left vulnerable to attacks on external memory.

### 2.2 Software Threats

There are two primary threats to software applications that protective architectures must address. Although *software protection* is a term with many meanings, it is considered for the purposes of this work, and the Virginia Tech Secure Software Project, to offer confidentiality and integrity of an application's instructions from internal software and external physical threats. While data protection is a related area of research, it does not necessarily improve the protection of software instructions.

Software confidentiality offers protection from threats such as unauthorized or unlicensed copying of programs, including piracy and reverse engineering of algorithms. Providing software confidentiality has an impact on the protection of intellectual property, both in terms of copying and reverse engineering. Without confidentiality, a program running outside a developer's secure domain can be considered disclosure of private information to the public, competitors, and malicious users.

Software integrity provides protection from threats that modify program instructions. This ensures secure software is running the way the developers programmed it to. Furthermore, the user can maintain trust that the program has not been altered beyond what the developer created. Maintaining this integrity assists in the protection from software viruses, worms, or malicious uses that rely on code modification to mount attacks.

## 2.3 Virginia Tech Secure Software Architecture

Members of the Virginia Tech Configurable Computing Laboratory have been conducting research into secure architectures that provide software integrity and confidentiality in a modern computing system. Developed under the project title Secure Software, the goal is to provide these software protections in hardware, without placing trust in the operating system or any other software component. To ease integration, the security features extend and compliment development flows, operating systems, and processor architectures without fundamentally altering normal operation.

In the current phase of research, the VT Secure Software architectures provide software protection through increased confidentiality and integrity of program instructions. The single secure processor architecture is currently defined, however the project is extensible to multiprocessing and parallel processing environments. The granularity of this protection is provided to individual memory pages of an application, and protected instructions remain encrypted at all times, until they enter the processor's instruction-side interface. Instructions never reside in unencrypted form in external memory, secondary storage, or on the processor's local bus.

#### 2.3.1 Paged Protection

Most modern computing platforms operate using the concept of virtual paged memory. Pages are fundamental units of memory that both the operating system and the hardware memory management unit (MMU) recognize. Virtual paged memory allows a program memory space to be virtually represented in the physical system memory space. Using entries in a MMU translation table, the translation look-aside buffer (TLB), memory accesses to a program's memory space are translated from its virtual page address to the physical page address. Pages are mapped in and out of memory as necessary, with different pages from different programs populating the physical memory space. This allows many programs to exist in memory at the same time, and allows programs larger than system memory to have a subset of its pages loaded at one time.

It was determined in the Secure Software Project that page-level encryption was the best method for providing software protection, from a hardware and software perspective for several important reasons. First, different encryption keys can be used for different program pages. This can help strengthen the use of encryption for a secure program and prevent replay attacks between separate pages. Second, different secure applications can share memory pages while using different keys for the non-shared memory. This allows programs to support secure shared memories while maintaining their own private spaces.

Lastly, the mechanisms required to handle page level encryption directly extend operations in place in the operating system and MMU. The OS already provides on-demand paging, where an entry in the TLB is created after an attempt to access a virtual address not already present. Operations that load the TLB on demand can also load the page-key mappings in the Secure Software architecture at the same time. If the page-key associations are

Figure 2.1: Single Processor Secure Software Architecture

established when TLB entries are added, then the instructions requested on the bus are guaranteed to be in the page–key association tables.

#### 2.3.2 Primary Components

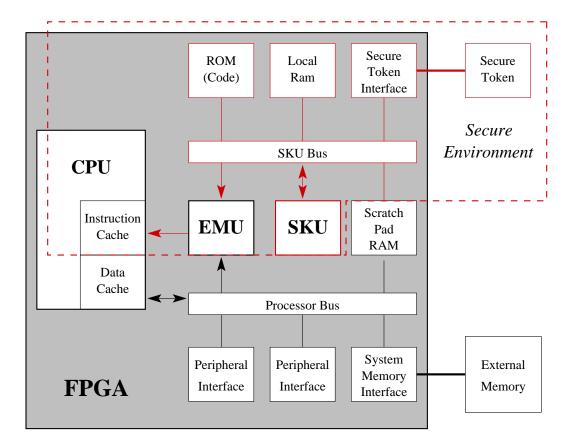

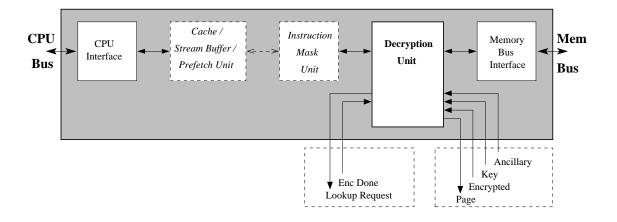

There are three primary components to the Virginia Tech Secure Software architecture. Figure 2.1 depicts the single secure processor architecture of the Virginia Tech Secure Software program, and the relationships between the primary components.

#### **CPU/Operating Systems**

The first component is the standard CPU with a memory management unit (MMU) to map virtual program address to the physical memory space. The operating system running on the CPU recognizes security tags and sections within each secure executable. The secure executable format use the same standard formats as a normal executable, but make use of the optional sections. Extra information in the secure executable indicates which executable instruction pages are encrypted, the cryptographic key identifiers for those pages, and partial security credentials for the keys. The operating system assigns page to key mappings at the same time it handles the virtual to physical address mappings in the translation look–aside buffer. Keeping these operations together ensures memory fetches on the bus will always reference up to date page encryption information.

#### Secure Key Management Unit

The second primary component of the Secure Software Project is the Secure Key Management Unit (SKU). This device is responsible for combining executable credentials and user credentials to create a proper cryptographic key. It is usually either a state machine or a small processor with its own private on-chip bus and memory. It receives information from the CPU containing partial executable credentials, a request for key generation, and where in a key table to place the generated key. An external secure token containing user credentials communicates with the SKU over a protected link. This provides the second half of the credentials used to create the keys.

The SKU resides on the same physical die as the processor but isolated from direct access by CPU. There is a set of intermediate buffers that the CPU and SKU use to communicate for key generation. This buffer isolates the SKU from the CPU. Similarly, the SKU is isolated from the external token. The secure token is accessed through a slave interface on the SKU bus. The SKU requests individual reads and writes from slave interface, which forwards them to the external token. It is not possible for the external token to access the internal SKU bus.

#### **Encryption Management Unit**

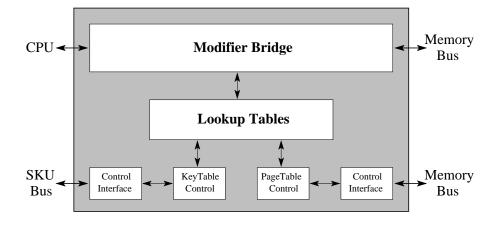

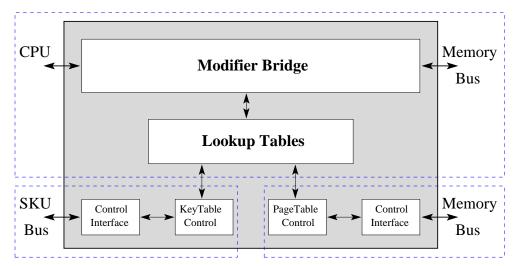

The third primary component is the Encryption Management Unit (EMU). The EMU extends the MMU behavior of page address translation. Similar in operation to the TLB, the EMU provides hardware physical page-to-key and page-to-ancillary data mappings and look-ups. These mappings are possible through a series of look-up tables and table search units. The EMU uses this information with an internal decryption unit to selectively decrypt the instruction stream.

Many modern processors support separate data and instruction-side bus interfaces at some level. These processors, including the latest architectures from Intel [18] and IBM [19] feature separate data and instruction caches. These features allow the EMU to work with each stream, data and instruction, together or on an individual basis depending on the performance and security objectives.

The EMU is supports various decryption methods and cryptographic engines by inserting a desired cryptographic unit into the EMU. Cryptographic modes, such as direct block or counter modes, can also be chosen based on application. The keys stored in the EMU reflect the cryptographic key for a particular page, while ancillary data contains supporting information for certain cryptographic modes, such as page counters for counter mode encryption. Information supplied to the decryption component in the EMU indicates if a page is encrypted in addition to the encryption key and ancillary data if encrypted.

Although the EMU provides software protection, it must also protect other sensitive operations of the Secure Software architecture from the CPU. The EMU does not allow access to keys by the CPU. The CPU writes to a set of search tables in the EMU that point a page to a particular key slot in a key table. The CPU is only able to create mappings. Likewise, the SKU can only write to the key table, but cannot access any part of the CPU– managed page search tables or to the CPU bus.

#### 2.3.3 Lifetime of a Secure Application

This section provides the lifetime of a secure executable. It is useful in the illustration of high–level interactions with the primary VT Secure Software components. Lifetime is defined here as the period in which an application is conceived to the point in which it is terminated by a user.

- 1. Program is compiled using standard developer tool-chains.

- 2. Developer encrypts desired code pages of the executable. Additional sections in executable are added to specify which pages are encrypted, and to provided partial credentials needed by the SKU to generate keys.

- 3. Secure executable is distributed in its encrypted form using secure or insecure channels.

- 4. Secure executable is executed on a VT Secure Software compatible architecture (from local storage, networked storage, RAM disk, etc).

- 5. OS recognizes security flags and credentials in executable file, flags internal process structures with identifiers indicating which key index is associated with which page.

- 6. Standard on-demand paging is performed. Encrypted pages also follow this on-demand operation, loading security tables in the EMU when the TLB is loaded. Pages that are encrypted remain encrypted in external memory.

- 7. OS provides run-time key replacement strategy if key table is too small for all keys of all encrypted applications running.

- 8. All instruction transactions are compared against page status information in the EMU to determine encrypted status, and associated key and ancillary data.

- 9. If status is encrypted, EMU decryption unit decrypts the instruction transaction and returns result to the CPU. Otherwise, the instructions pass directly to the processor.

- 10. On application termination and during execution, pages are replaced under normal operations as other pages are paged into memory. New pages will replace the memory contents and security flags in the EMU with ones that reflect the status of the new page.

#### 2.3.4 Protections

The primary goal of the Virginia Secure Software Project is to provide increased software protection. The software protections defined include instruction confidentiality and integrity. These protections are offered through the architecture's ability to keep instructions in encrypted form throughout the distribution, storage, and fetch process until entering the CPU instruction–side bus interface. This section describes how these methods provide each security measure.

#### Software Confidentiality

Instruction encryption helps enforce software confidentiality. Instructions, which are loaded into memory, can only be executed after proper decryption on the instruction-side bus. Without the key, deciphering the encrypted version of a program's instructions is not feasible when proper encryption techniques are used. In the initial Secure Software architecture the platform does not contain a data-side bus decryption unit, and therefore cannot directly read or write properly encrypted instructions.

Furthermore, the processor does not have read or write access to the decryption unit or the key table. Therefore, the processor access an unencrypted instructions located on or off chip, or access the cryptographic keys and decipher the instructions in software. As the EMU is located on the instruction–side bus interface, and not the data–side, even a secure application cannot read its own instructions in decrypted form.

#### Software Integrity

Software integrity is also supported through the use of instruction encryption. When properly using a modern symmetric block cryptographic routine, it is extremely difficult, and not computationally possible, to alter a single instruction with another encrypted instruction.

Block cryptographic modes operate on a group of data usually consisting of several instructions in one decrypt or encrypt operation. Robust cryptographic algorithms provide a large change in encryption or decryption output, regardless of how few bits change in the corresponding input. This prevents correlation between cryptographic pre–images and encrypted results. The initial Secure Software architecture uses direct block encryption modes.

An attacker trying to alter a subset of instructions within a cryptographic block, through internal software or external memory modification, could not cycle through a set of guesses and refine their attack to execute an instruction of their choosing. Any alteration to the encrypted instructions before execution, however small, would cause the corresponding block of instructions to decrypt into a pseudo-random set of bits likely consisting of invalid instructions. At the very least, execution flow would be completely altered and usually results in segment faults.

Furthermore, as instructions are decrypted on the instruction-side bus in this iteration, it is not possible for a secure application to meaningfully modify its own instructions, meaning if a technologically advanced adversary manages to break a single block of instructions, it does not open a back door into the protected instruction space of the program. The attack must be carried out on every other block of instructions as well.

### 2.4 Related Memory Modification Units

The design of the Encryption Management Unit has drawn inspiration from several systems and architectures. These units posses a set of protections and implementation strategies that are reflected in the EMU. The common characteristic of each system is to selectively apply a particular function on an instruction stream based on certain criteria. Related secure architectures to the Virginia Tech platform are described in [20].

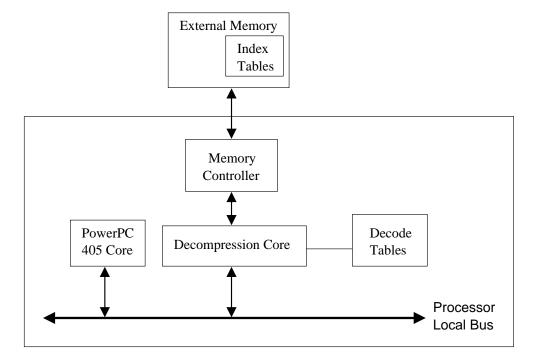

#### 2.4.1 IBM CodePack

The first system has a strong history with the processor used in the implementation of the Secure Software architecture. IBM CodePack [21] [22] is a hardware/software feature developed for reducing the size of code in memory for embedded applications. To reduce code size, application instructions are compressed after compilation. It uses architectural features of the IBM PowerPC processor [23] to support decryption. Notably, it uses a compression flag within the PowerPC memory management unit's (MMU) translation look-aside buffer (TLB). This flag is exported from the TLB to a dedicated line on the Processor Local Bus (PLB) during memory transactions.

A normal application running on the PowerPC consists of a series of 32–bit instructions, with each instruction containing an operator followed by one ore more operands. From one instruction to the next there is often little correlation between the 32–bit values. However, by splitting instructions into 16–bit halves, there is much higher correlation between the corresponding halves for each instruction. Separately compressing each half–instruction channel offers significant compression potential.

A substitution method based on frequency is used to replace repetitive 16-bit units with shorter bit alternatives. One drawback to this encoding method is that the least frequent units are represented by a set of bits longer than the original 16-bit format. These components do not occur often, and it is likely that the compressed instruction space will still

Figure 2.2: IBM CodePack Architecture

require less memory than the original uncompressed version.

With respect to address locations, the compressed version of the executable does not directly correspond to the original uncompressed version. Using variable length encoding produces a mismatch between the locations and sizes of instructions compared to the original set. To solve this problem, the IBM CodePack system uses an index table stored in external memory to find the base location of an instruction *group*. By representing large 128–byte groups of uncompressed instructions in the table, instead of maintaining each instruction address, the table size is significantly reduced. When a request for a compressed target arrives, the base location for the compressed block is looked up in the index table, the block is decompressed, and the target instruction is returned. The relation to the Encryption Management Unit is with the decompression strategy of the hardware portion of CodePack. The CodePack system retrieves information from tables in external memory, fetches the compressed memory block, and returns the requested decompressed values. In a similar fashion, the EMU retrieves information from tables in hardware in parallel with the encrypted memory fetch, and returns the decrypted version. CodePack differs with the EMU in its location in the processor bus structure. As CodePack is not concerned with security, it is located on the external memory controller, while the EMU is placed directly between the processor instruction–side bus interface and the processor bus.

Although CodePack utilizes the MMU and the *compressed* PLB signal to determine the compression status for a page, the EMU does not. First, the content addressable memories and tables used in the EMU are extremely fast, using the *compressed* bus signal to indicate encryption would offer very little performance advantage. Secondly, the EMU must remain reasonably flexible to various architectures, and the *compressed* flag is PowerPC specific.

As both systems modify instruction streams, it is natural to attempt to draw conclusions about EMU performance based on CodePack performance. However, these two systems do not have similar performance characteristics. The CodePack system has quite a large buffer, 16 instructions, and this buffer is completely filled when a requested instruction is not in the buffer. Furthermore, as the index tables are stored in external memory, there is a high penalty for instruction fetch look–ups.

Surprisingly, even with the external memory table look–up and decompression routines, there are still applications that exhibit performance gains when using CodePack [24]. This is likely attributed to high instruction execution locality within a block of instructions, which results in the CodePack unit performing as a small pre–fetching cache. The EMU, on the other hand, retrieves and modifies only the requested instructions. As shown in Chapter 4, the EMU is strictly a delay element in the memory pipeline, and can never contribute to a performance increase.

#### 2.4.2 XOM

The XOM architecture, or Execute Only Memory [25], provides similar instruction protections as the Secure Software Encryption Management Unit. It attempts to ensure instructions can only be executed, never read or modified, through decryption of instructions and data as they are passed through the cache system and into the processor. XOM uses application level cryptographic keys to isolate applications from each other. Each key creates what XOM refers to as cryptographic *compartments*. Unlike the EMU, these keys are stored in encrypted form in external memory and are verified against a private hash whenever a key is retrieved. Similar to the EMU, the cryptographic unit of the XOM system uses a symmetric cryptographic algorithm for decryption of instruction blocks.

Although both the Secure Software EMU and XOM provide similar execute–only instruction capabilities, their design and use within their respective systems are very different. First, XOM does not support page–level key associations. It takes the approach of application–level key associations. To identify what key should be used, or even if the application is encrypted, special instructions and registers were added to manually start and stop the XOM unit. As keys are stored in external memory, a further set of registers and instructions were added handle where in external memory the application key resides.

The Secure Software EMU uses a page-level encryption scheme that allows the hardware to efficiently mirror the TLB in establishing page-key relationships. This eliminates the manual start/stop triggering required by XOM, and the costly key look-up and decryption from external memory. Another problem involved with XOM start/stop triggering is with context switches and interrupts. When these occur, the XOM unit is still enabled and any instruction fetch of the interrupt handler will be incorrectly decrypted using the previous compartment key.

The XOM solution is to rewrite the interrupt vectors into a private XOM memory, and install a wrapper for interrupts. These wrappers disable the XOM unit before proceeding passing on to the true handler. This problem is avoided in the Secure Software system, as the EMU is aware of the encrypted status of a page, and if the interrupts are not flagged as encrypted the the cryptographic unit is bypassed.

### 2.5 Benchmarking

Software protection provides security for instructions, which likely requires alteration to the performance of the instruction-side bus of the processor. Additional latency from security mechanisms play a critical role in the overall performance of the secure application. To measure this effect, a benchmark capable of testing the instruction fetch performance is required.

In the realm of benchmarks there are two basic directions: synthetic benchmarks and application benchmarks. Synthetic benchmarks typically focus on testing particular features of a system, such as memory bandwidth, I/O latency, and more. They consist of applications designed specifically for performing the tests. Application benchmarks are entire programs, or representative code of programs, run on the test platform. Between different platform configurations, they illustrate how a particular application will perform. Furthermore, as parameters change, it is possible to the effect of that change, and how well targeted applications run with the new settings.

There are many effective application benchmarks available for an array of platforms. Many publications in the area of secure software favor the SPEC benchmark to demonstrate the effect their protection mechanisms have on performance. The SPEC CPU [26] suite of benchmarks consists of floating-point and integer based benchmarks that perform various functionality, such as chemistry and physics modeling, C/C++ and hardware description language (HDL) compilers, text interpreters, compression routines, and more. However, the problem with the SPEC benchmark suite is the selection of benchmarks do not effectively stress the instruction-side bus interface. Current research [27] reveals that the SPEC CPU suite is insufficient for analyzing systems that effect memory latency of instruction fetches.

Although an alternative set of application benchmarks have been recommended to more effectively stress the instruction–side bus, it was decided that if this work was to improve upon the existing benchmark standards a synthetic benchmark that could directly measure instruction-side latency was required.