## Scale-Free Graph Processing on a NUMA Machine

by

Tanuj Kr Aasawat

B. Engineering, Jadavpur University, India, 2015

## A THESIS SUBMITTED IN PARTIAL FULFILLMENT OF THE REQUIREMENTS FOR THE DEGREE OF

#### **Master of Applied Science**

in

### THE FACULTY OF GRADUATE AND POSTDOCTORAL

#### STUDIES

(Electrical and Computer Engineering)

The University of British Columbia

(Vancouver)

October 2018

© Tanuj Kr Aasawat, 2018

The following individuals certify that they have read, and recommend to the Faculty of Graduate and Postdoctoral Studies for acceptance, the thesis entitled:

#### **Scale-Free Graph Processing on a NUMA Machine**

submitted by **Tanuj Kr Aasawat** in partial fulfillment of the requirements for the degree of **Master of Applied Science** in **Electrical and Computer Engineering**.

#### **Examining Committee:**

Matei Ripeanu, Electrical and Computer Engineering *Supervisor*

Sathish Gopalakrishnan, Electrical and Computer Engineering *Examining Committee Member*

Karthik Pattabiraman, Electrical and Computer Engineering *Examining Committee Member*

## Abstract

The importance of high-performance graph processing to solve big data problems targeting high-impact applications is greater than ever before. Graphs incur highly irregular memory accesses which leads to poor data locality, load imbalance, and data-dependent parallelism. Distributed graph processing frameworks, such as Google's Pregel, that employs memory-parallel, shared-nothing systems have experienced tremendous success in terms of scale and performance. Modern shared-memory systems embrace the so called Non-Uniform Memory Access (NUMA) architecture which has proven to be more scalable (in terms of numbers of cores and memory modules) than the Symmetric Multiprocessing (SMP) architecture. In many ways, a NUMA system resembles a shared-nothing distributed system: physically distinct processing cores and memory regions (although, cache-coherent in NUMA). Memory accesses to remote NUMA domains are more expensive than local accesses. This poses the opportunity to transfer the know-how and design of distributed graph processing to develop shared-memory graph processing solutions optimized for NUMA systems (which is surprisingly little-explored).

In this dissertation, we explore if a distributed-memory like middleware that makes graph partitioning and communication between partitions explicit, can improve the performance on a NUMA system. We design and implement a NUMA aware graph processing framework that treats the NUMA platform as a distributed system, and embraces its design principles; in particular explicit partitioning and inter-partition communication. We further explore design trade-offs to reduce communication overhead and propose a solution that embraces design philosophies of distributed graph processing system and at the same time exploits optimization opportunities specific to single-node systems. We demonstrate up to  $13.9 \times$  speedup

over a state-of-the-art NUMA-aware framework, Polymer and up to  $3.7 \times$  scalability on a four-socket machine using graphs with tens of billions of edges.

## Lay Summary

Large-scale graphs processing introduces various performance and efficiency challenges due to the scale and inherent irregular topology of graphs. Distributed graph processing frameworks, like Google's Pregel, that employs multi-node platforms, have experienced tremendous success in terms of scale and performance. Modern single-node systems embrace Non-Uniform Memory Access (NUMA) architecture which is more scalable than other architectures. In many ways, a NUMA system resembles a distributed system: physically distinct CPUs and memory. This poses the opportunity to transfer the wisdom of distributed graph processing to NUMA systems.

In this dissertation, we design and implement a NUMA-aware graph processing framework that explores if a distributed-memory like middleware that makes graph partitioning and inter-partition communication explicit, can improve the performance on a NUMA system. We demonstrate up to  $13.9 \times$  speedup over a stateof-the-art NUMA-optimized framework and up to  $3.7 \times$  scalability on a four-socket machine using graphs with tens of billions of edges.

## Preface

This thesis is based on the research project done by me under the supervision and guidance of Professor Matei Ripeanu. I was responsible for the design, implementation, modeling, validation, evaluation and analysis of the results, along with taking the lead in publication writing effort. The research presented in this thesis have been either published or accepted for publication.

The work that this thesis extends and evaluates against, was selected based on the following preliminary study; Professor Ripeanu and Tahsin helped me in the analysis of the results and editing the publication.

**Tanuj Kr Aasawat**, Tahsin Reza, Matei Ripeanu, *How well do CPU, GPU and Hybrid Graph Processing Frameworks Perform?*, Pages 458-466, 2018 IEEE International Parallel and Distributed Processing Symposium Workshops (IPDPSW), May 2018.

The research presented herein has been accepted for publication. Professor Ripeanu and Tahsin helped me in the analysis of my design and the results, and editing the publication.

**Tanuj Kr Aasawat**, Tahsin Reza, Matei Ripeanu, *Scale-Free Graph Processing on a NUMA Machine*, IEEE Workshop on Irregular Applications: Architectures and Algorithms (IA3) in conjunction with SC18, The International Conference for High Performance Computing, Networking, Storage, and Analysis, Dallas, TX, USA, November 2018.

# **Table of Contents**

| Ał | ostrac  | et       | ••••      | ••    | ••• | •    | ••  | •    | ••  | •  | • • | •    | •  | •  | ••  | •   | •   | ••  | •  | •  | •  | • | • | • | iii |

|----|---------|----------|-----------|-------|-----|------|-----|------|-----|----|-----|------|----|----|-----|-----|-----|-----|----|----|----|---|---|---|-----|

| La | iy Sui  | nmary    | ••••      | ••    | ••  | •    | ••  | •    | ••• | •  | • • | •    | •  | •  | ••  | •   | •   | ••  | •  | •  | •  | • | • | • | v   |

| Pr | eface   |          | ••••      | ••    | ••  | •    | ••  | •    | ••  | •  | • • | •    | •  | •  | ••  | •   | •   | ••  | •  | •  | •  | • | • | • | vi  |

| Ta | ble of  | f Contei | nts       | ••    | ••  | •    |     | •    |     | •  | • • | •    | •  | •  | ••  | •   | •   | ••  | •  | •  | •  | • | • | • | vii |

| Li | st of [ | Fables . | ••••      | ••    | ••  | •    | ••  | •    |     | •  | • • | •    | •  | •  | ••  | •   | •   | ••  | •  | •  | •  | • | • | • | X   |

| Li | st of l | Figures  | • • • •   | ••    | ••  | •    | ••  | •    | ••  | •  | • • | •    | •  | •  | ••  | •   | •   | ••  | •  | •  | •  | • | • | • | xi  |

| Ac | cknow   | vledgme  | ents      | ••    | ••  | •    | ••  | •    |     | •  | • • | •    | •  | •  | ••  | •   | •   | ••  | •  | •  | •  | • | • | • | XV  |

| 1  | Intr    | oductio  | n         | ••    | ••  | •    | ••• | •    |     | •  | • • | •    | •  | •  |     | •   | •   |     | •  | •  | •  | • | • | • | 1   |

|    | 1.1     | Hypotl   | hesis .   |       |     |      |     |      |     |    |     |      |    |    |     |     |     |     |    |    |    |   |   | • | 2   |

|    | 1.2     | Contri   | butions   |       |     |      |     |      |     |    |     | •    |    | •  |     |     |     |     |    |    |    |   |   |   | 3   |

|    | 1.3     | Disser   | tation St | ruct  | ure | •    | ••• | •    |     | •  |     | •    | •  | •  |     | •   | •   |     | •  | •  | •  | • | • | • | 4   |

| 2  | Bac     | kground  | 1         | ••    | ••  | •    | ••  | •    | ••  | •  | • • | •    | •  | •  |     | •   | •   | ••  | •  | •  | •  | • | • | • | 5   |

|    | 2.1     | Graph    |           |       |     |      |     |      |     |    |     | • •  |    | •  |     |     | •   |     |    | •  |    |   | • | • | 5   |

|    | 2.2     | Graph    | Process   | ing   |     |      |     |      |     |    |     | • •  |    | •  |     |     | •   |     |    | •  |    |   | • | • | 7   |

|    | 2.3     | Hardw    | are Plat  | form  | s.  |      |     |      |     |    |     | •    |    | •  |     |     | •   |     |    |    |    |   |   | • | 8   |

|    |         | 2.3.1    | Shared    | -not  | hin | g c  | lus | ster | • • |    |     | •    |    | •  |     |     | •   |     |    |    |    |   |   | • | 8   |

|    |         | 2.3.2    | Symm      | etric | Mı  | ulti | -Pı | roc  | ess | or | (S  | Μ    | P) | A  | rch | ite | ect | ure | e. |    |    |   |   |   | 9   |

|    |         | 2.3.3    | Non-U     | nifo  | rm  | Me   | em  | ory  | Λ   | cc | ess | 1) 8 | NU | JM | (A) | ) A | rc  | hit | ec | tu | re |   |   |   | 9   |

|   | 2.4 | Bulk-Sy   | ynchronous Parallel (BSP) Processing Model    | 11 |

|---|-----|-----------|-----------------------------------------------|----|

|   | 2.5 | BSP-St    | yle Graph Processing                          | 12 |

|   | 2.6 | Graph A   | Algorithms                                    | 14 |

|   |     | 2.6.1     | PageRank                                      | 15 |

|   |     | 2.6.2     | Breadth-First Search                          | 15 |

|   |     | 2.6.3     | Single-Source Shortest Path                   | 17 |

|   | 2.7 | Related   | Work                                          | 18 |

| 3 | A B | SP-style  | NUMA-aware Graph Processing Framework         | 20 |

|   | 3.1 | Intuition | n                                             | 20 |

|   | 3.2 | Graph F   | Partitioning                                  | 21 |

|   | 3.3 | Design    | Opportunities for NUMA-aware Graph Processing | 22 |

|   |     | 3.3.1     | Data structures                               | 23 |

|   |     | 3.3.2     | NUMA 2-Box Design                             | 24 |

|   |     | 3.3.3     | NUMA 1-Box Design                             | 27 |

|   |     | 3.3.4     | NUMA 0-Box Design                             | 28 |

|   | 3.4 | Analyti   | cal Model for Estimating Performance          | 30 |

|   | 3.5 | Mappin    | ng GAS model to NUMA design                   | 32 |

| 4 | Exp | eriment   | Design                                        | 34 |

|   | 4.1 | System    | Implementation                                | 34 |

|   | 4.2 | TestBec   | 1                                             | 36 |

|   | 4.3 | Worklo    | ad                                            | 36 |

|   | 4.4 | Experin   | nental Methodology                            | 37 |

| 5 | Exp | erimenta  | al Results                                    | 39 |

|   | 5.1 | Impact    | of Graph Partitioning                         | 39 |

|   |     | 5.1.1     | Partitioning - Key Insights                   | 42 |

|   | 5.2 | Perform   | nance Evaluation of Designs                   | 42 |

|   |     | 5.2.1     | Performance of NUMA 2-Box design              | 43 |

|   |     | 5.2.2     | Performance of NUMA 1-Box design              | 44 |

|   |     | 5.2.3     | Performance of NUMA 0-Box design              | 47 |

|   |     | 5.2.4     | Communication Designs - Key Insights          | 48 |

|   |     | 5.2.5     | Strong Scaling Experiments                    | 49 |

|   |     |           |                                               |    |

| Bi | bliogr | aphy .  | •••      | • • •  |       |      |      |      |    | • | •• | • | • |    | • | ••• | • | • | • |     | • |   | 56 |

|----|--------|---------|----------|--------|-------|------|------|------|----|---|----|---|---|----|---|-----|---|---|---|-----|---|---|----|

| 6  | Con    | clusion | •••      | •••    | ••    | ••   | ••   | • •  | •• | • | •• | • | • | •• | • | ••  | • | • | • | • • | • | • | 54 |

|    | 5.4    | Compa   | arison v | with E | Exist | ing  | W    | ork  |    | • |    | • | • |    | • |     | • | • | • |     |   | • | 52 |

|    | 5.3    | Accura  | acy of t | he Ar  | naly  | tica | 1 M  | lode | el |   |    | • | • |    | • |     |   |   |   |     |   |   | 50 |

|    |        | 5.2.6   | Graph    | n500 s | subr  | nis  | sior | ns   |    |   |    | • | • |    |   |     | • |   |   |     |   |   | 49 |

# **List of Tables**

| Table 2.1 | Memory bandwidth characteristics of our Testbed (Four socket<br>Intel Xeon, E7-4870 v2; more description in Section 4.2). Mem-<br>ory bandwidth is measured with custom benchmark with arrays<br>of size 1 GB. Memory latency is measured using Intel Memory<br>Latency Checker.                                                                                     | 11 |

|-----------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

| Table 3.1 | Memory Access Pattern for different NUMA designs, for PageR-<br>ank algorithm. V/V' and E/E' represents number of local/re-<br>mote vertices and edges in the partition. N is the number of<br>partitions. Memory accesses are represented by $X_Y^Z$ , where X<br>is: read/write operation, Y is: sequential/random access, and Z<br>is: local/remote memory access | 31 |

| Table 4.1 | Workload used for evaluation.                                                                                                                                                                                                                                                                                                                                        | 36 |

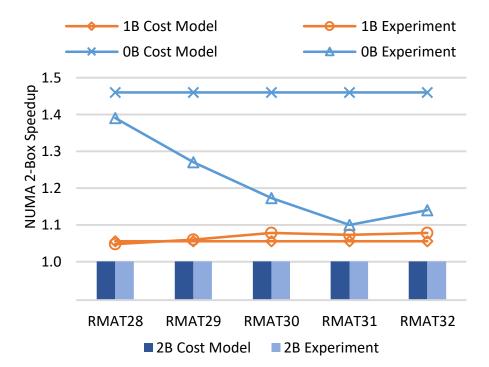

| Table 5.1 | Cost Model evaluation for PageRank algorithm. The numbers represent average speedup of NUMA 2-Box against other designs, for all workloads, as predicted by cost model and observed empirically from experiments.                                                                                                                                                    | 52 |

| Table 5.2 | Execution time (in second) and peak Memory consumption (in GB) of Polymer and our best performing NUMA design (NUMA-xB). We show peak memory consumption among all the NUMA designs. Missing data points means Polymer was out-of-memory.                                                                                                                            | 53 |

|           | designs, missing data points means i orymer was out-or-memory.                                                                                                                                                                                                                                                                                                       | 55 |

# **List of Figures**

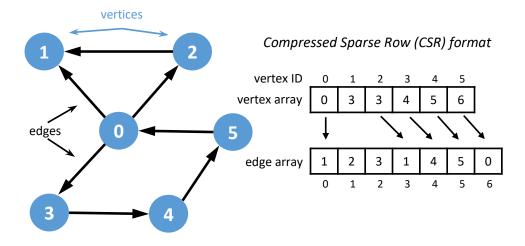

| Figure 2.1 | On left, a directed graph with 6 vertices and 7 edges. On right   |    |

|------------|-------------------------------------------------------------------|----|

|            | is the Compressed Sparse Row (CSR) representation of the          |    |

|            | graph. CSR format has two arrays, 'vertex array' (or offset ar-   |    |

|            | ray) and 'edge array'. 'vertex array' contains starting index of  |    |

|            | the outgoing edges originating from each vertex (represented      |    |

|            | by the indices of vertex array). 'edge array' contains only the   |    |

|            | destination vertices of the edges                                 | 6  |

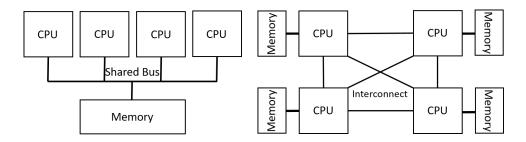

| Figure 2.2 | An illustration of SMP/UMA (left) and NUMA (right) archi-         |    |

|            | tectures                                                          | 9  |

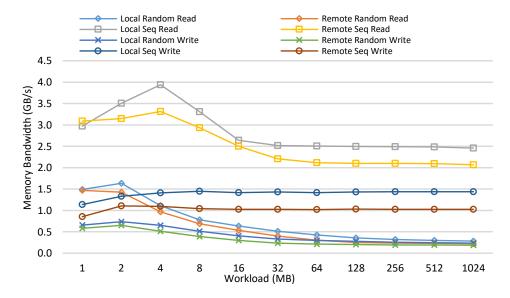

| Figure 2.3 | Local and remote memory bandwidth for read and write oper-        |    |

|            | ations on 4-Socket Intel Xeon (E7-4870 v2, Ivy Bridge) ma-        |    |

|            | chine, for different workloads (size in MB)                       | 10 |

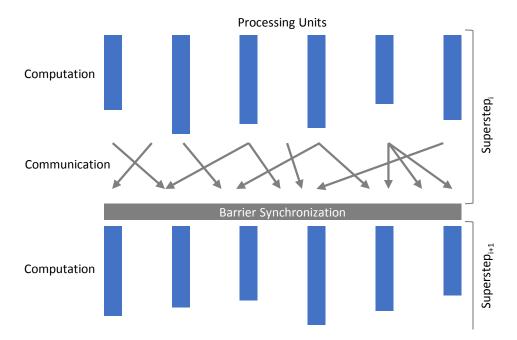

| Figure 2.4 | A high level illustration of the Bulk Synchronous Parallel Model. | 12 |

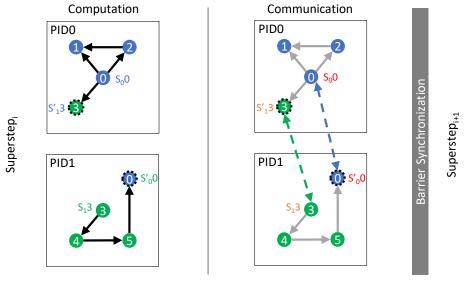

| Figure 2.5 | BSP graph processing depicting computation and communica-         |    |

|            | tion phases in a superstep. In the computation phase, the state   |    |

|            | of a vertex and its shadow copy (on a remote partition) are       |    |

|            | updated independently. In the communication phase, the ver-       |    |

|            | tex and its shadow copy communicate to determine the correct      |    |

|            | state. For example, in SSSP, after communication, both the        |    |

|            | vertex and its shadow copy commit to the minimum distance         |    |

|            | at that point in traversal.                                       | 13 |

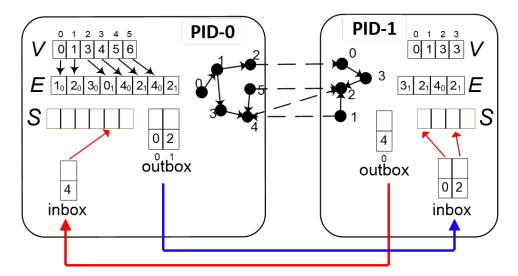

| Figure 3.1 | High-level illustration of inter-partition communication of NUMA     | 1  |

|------------|----------------------------------------------------------------------|----|

|            | 2-Box design. $V$ and $E$ are the buffers to represent the graph     |    |

|            | in CSR format (as mentioned in Section 2.1 and Figure 2.1). S        |    |

|            | is the state buffer for local vertices. Bottom blue and red solid    |    |

|            | lines depicts communication paths for NUMA 2-Box, where              |    |

|            | explicit memory copy through in - and out - boxes are re-            |    |

|            | quired. For push-based algorithms, during computation phase,         |    |

|            | each partition manipulates its local state buffer S for local ver-   |    |

|            | tices and updates for remote vertices are aggregated locally         |    |

|            | in the outbox buffer. During communication phase outbox is           |    |

|            | copied into the inbox of the respective remote partition, which      |    |

|            | are then applied to the respective local state buffers               | 24 |

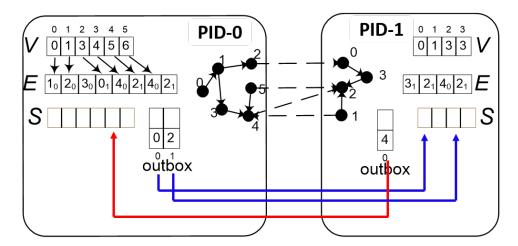

| Figure 3.2 | High-level illustration of NUMA 1-Box design. $V$ and $E$ are        |    |

|            | the buffers to represent the graph in CSR format (as mentioned       |    |

|            | in Section 2.1 and Figure 2.1). S is the state buffer for local ver- |    |

|            | tices. For push-based algorithms, during computation phase,          |    |

|            | each partition manipulates its local state buffer S for local ver-   |    |

|            | tices and updates for remote vertices are aggregated locally in      |    |

|            | the outbox buffer. During communication phase, updates in            |    |

|            | the remote outbox are sequentially accessed and applied to the       |    |

|            | respective local state buffers                                       | 26 |

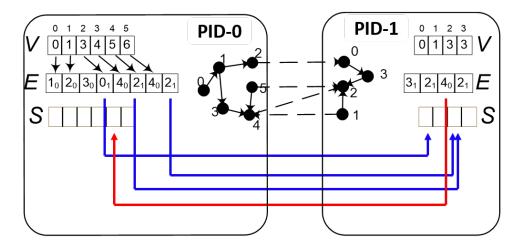

| Figure 3.3 | High-level illustration of NUMA 0-Box design, which over-            |    |

|            | laps computation with communication. $S$ is the state buffer for     |    |

|            | local vertices. Note that in this design we get rid of commu-        |    |

|            | nication infrastructure. During computation phase, each parti-       |    |

|            | tion manipulates its local state buffer $S$ for local vertices and   |    |

|            | remote updates are directly written to the respective local state    |    |

|            | buffer of the remote partition. Atomic writes are used to ensure     |    |

|            | correctness                                                          | 28 |

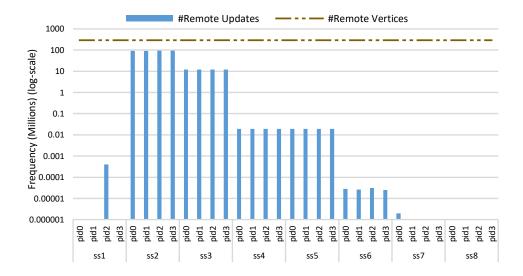

| Figure 3.4 | Number of Remote vertices vs number of remote updates in             |    |

|------------|----------------------------------------------------------------------|----|

|            | each partition in every superstep of Direction-Optimized BFS         |    |

|            | (BFS-DO) for RMAT31 in NUMA 2-Box design. The Y-axis                 |    |

|            | represents frequency (in millions), in log-scale, of the number      |    |

|            | of remote updates (per superstep) and the total number of re-        |    |

|            | mote vertices in each partition. The ss-' $x$ ' on X-axis represents |    |

|            | the sequence of supersteps. We observe that remote updates           |    |

|            | are $\sim 22 \times$ less than the number of remote vertices         | 29 |

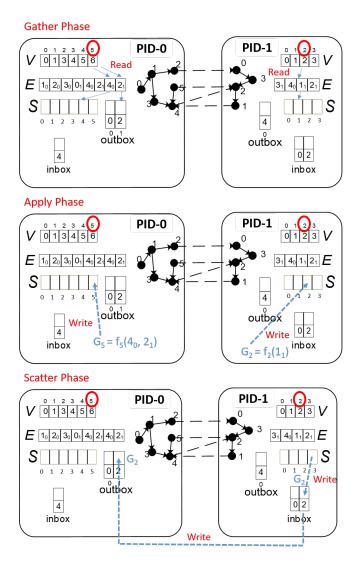

| Figure 3.5 | Gather, Apply and Scatter phases in NUMA 2-Box design, for           |    |

|            | a pull based algorithm. During computation phase, each local         |    |

|            | vertex gathers the state of its neighbors and applies the com-       |    |

|            | puted value to its state. In communication phase, it scatters its    |    |

|            | new state to the respective inbox buffer, which is then copied       |    |

|            | to the outbox buffer on remote partition. In this way, all the       |    |

|            | shadow copies of a vertex have the same state, before the start      |    |

|            | of next superstep                                                    | 33 |

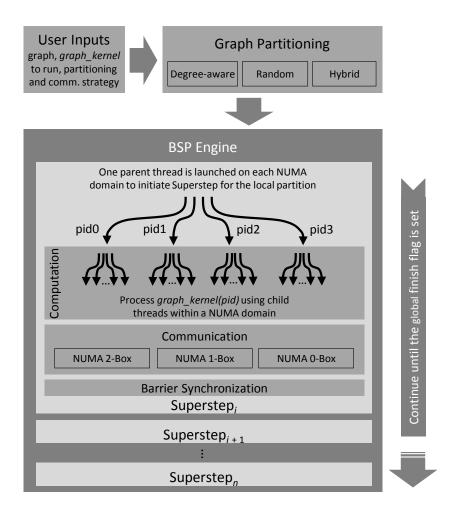

| Figure 4.1 | High-level design of our BSP-style NUMA-aware framework.             | 35 |

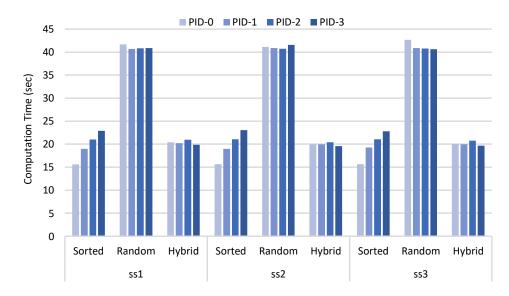

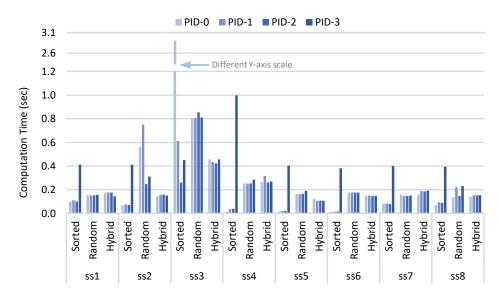

| Figure 5.1 | Load imbalance of traditional (Sorted and Random) and new            |    |

|            | Hybrid partitioning strategy for PageRank algorithm for RMAT31       |    |

|            | graph using NUMA 2-Box design. The x-axis is for supersteps          |    |

|            | (denoted by 'ss') required for execution. The y-axis is for com-     |    |

|            | putation time (lower the better) of the four partitions for the      |    |

|            | three partitioning strategies.                                       | 40 |

| Figure 5.2 | Load imbalance of traditional (Sorted and Random) and new            |    |

|            | Hybrid partitioning strategy for BFS-DO algorithm for RMAT31         |    |

|            | graph using NUMA 2-Box design. The x-axis is for super-              |    |

|            | steps (denoted by 'ss') required for execution. The y-axis is        |    |

|            | for computation time (lower the better) of the four partitions       |    |

|            | for Traditional and New partitioning strategies                      | 41 |

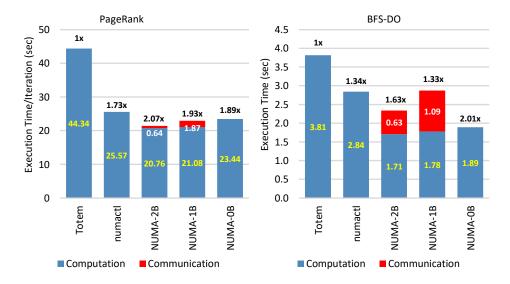

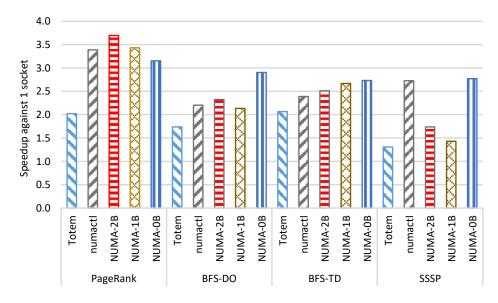

| Figure 5.3 | NUMA designs performance against Totem and numactl for            |    |

|------------|-------------------------------------------------------------------|----|

|            | PageRank (left) and BFS-DO (right) algorithms on RMAT31           |    |

|            | graph. The Y-axis is for execution time (lower the better). For   |    |

|            | NUMA-2B and NUMA-1B, where we do explicit communi-                |    |

|            | cation, we show the breakdown of execution time with com-         |    |

|            | putation and communication time.                                  | 44 |

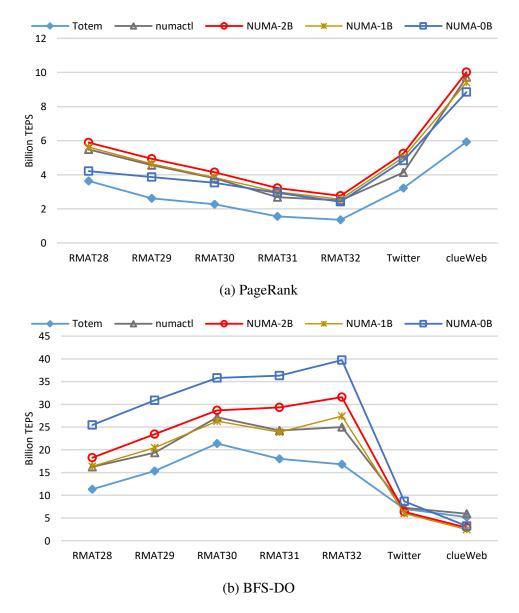

| Figure 5.4 | Billion Traversed Edges Per Second (TEPS) achieved by Totem,      |    |

|            | numactl and the NUMA designs, for (a) PageRank and (b)            |    |

|            | BFS-DO algorithms on RMAT[28-32] (synthetic), and Twit-           |    |

|            | ter and clueWeb (real-world) workloads. Note, the Y-axis is       |    |

|            | for Traversed Edges Per Second (TEPS) (higher the better)         | 45 |

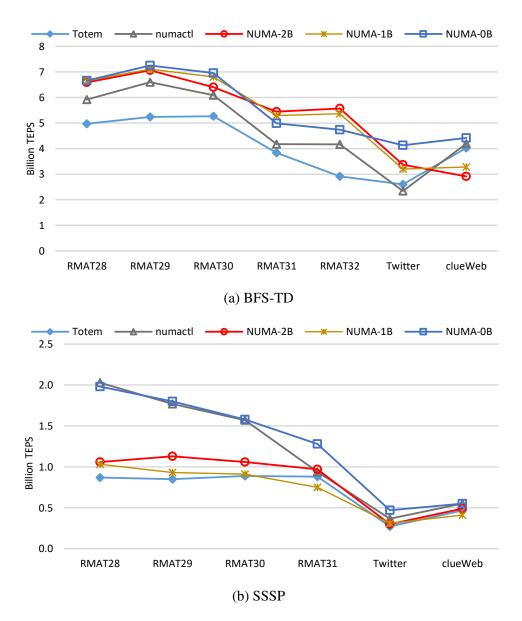

| Figure 5.5 | Billion Traversed Edges Per Second (TEPS) achieved by Totem,      |    |

|            | numactl and the NUMA designs, for (a) BFS-TD and (b) SSSP         |    |

|            | algorithms on RMAT[28-32] (up to RMAT31 for SSSP, since it        |    |

|            | requires weighted edge-list) (synthetic), and Twitter and clueWeb |    |

|            | (real-world) workloads. Note, the Y-axis is for Traversed Edges   |    |

|            | Per Second (TEPS) (higher the better)                             | 46 |

| Figure 5.6 | Strong Scaling of Totem, numactl and NUMA designs on our          |    |

|            | 4-socket machine compared to 1-socket (memory: 384GB).            |    |

|            | Weighted RMAT29 (weighted edgelist size: 192GB) is used           |    |

|            | for SSSP and unweighted RMAT30 (edgelist size: 256GB)             |    |

|            | was used for all other algorithms.                                | 49 |

| Figure 5.7 | Analytical Model prediction for PageRank algorithm. The Y-        |    |

|            | axis shows the speedup of NUMA 2-Box against NUMA 1-              |    |

|            | Box and NUMA 0-Box as predicted by cost model and calcu-          |    |

|            | lated empirically through experiments                             | 51 |

## Acknowledgments

I would like to sincerely thank my advisor, Professor **Matei Ripeanu** for giving me the opportunity to work on this high-quality research project and for his invaluable guidance, insightful feedback and support throughout this journey. I am grateful to him for encouraging and allowing me to do internships at IBM Almaden Research Center and Amazon Web Services.

I would like to thank my lab colleagues for providing their feedback during meetings and research presentations, and sharing their knowledge and experience with me.

Last but not the least, this journey would not have been possible without the consistent motivation from my brother **Manish**, and immense support and inspiration from my parents **Jawahar** and **Mohini**. My deepest gratitude to them.

To my parents and brother

## **Chapter 1**

## Introduction

Graph processing is at the core of a wide range of big data problems, such as online social networks analysis [11, 18], bioinformatics [19, 29], transport network analysis [37], financial and business analytics [20], to name a few. Additionally, graph processing has found new applications in machine learning and data mining.

Graph algorithms incur highly irregular data-dependent memory access patterns, which leads to poor data locality. Further, most of the graph algorithms have a low compute-to-memory access ratio, i.e., they are memory-bound. Many realworld graphs are massive: some have hundreds of billions of edges - hence have huge memory footprint. For example, the Facebook graph [8] and Web Data Commons, a hyperlink graph [4], have more than 100 billion edges, which requires over two terabytes of memory.

To process such huge graphs, traditionally frameworks like Google's Pregel [26] and GraphLab [17] running on large shared-nothing clusters have been used, as these platforms provide large aggregated memory. Most of these frameworks use the Bulk Synchronous Parallel (BSP) Processing Model [39]. Here, the graph is partitioned explicitly among the processing units and as these clusters are not cache-coherent, the communication between different processing units is explicit. This is in contrast with graph processing frameworks [30, 35] that target single-node shared-memory systems, and treat shared-memory system as if it is based on Symmetric Multi-Processor (SMP) architecture. In SMP architecture the access time to any location in memory is uniform, therefore, there is no need for data

partitioning.

Non-Uniform Memory Access (NUMA, a.k.a. distributed shared-memory) architecture machines introduce a dilemma: on the one side, they provide shared memory - thus graph processing frameworks that treat shared-memory system as SMP architecture, can be directly used. On the other side, the cost of memory accesses is non-uniform (i.e, a socket has faster access to the local memory associated with it, than to remote/non-local memory associated with other sockets), thus explicit data placement is needed to obtain maximum performance and a graph framework developed in the style of frameworks that target distributed systems may prove to offer advantages.

### 1.1 Hypothesis

Since NUMA architecture resembles distributed systems, our intuition is, a graph processing framework, targeting NUMA-architecture, developed in the style of frameworks that target distributed systems (explicit partitioning and communication), provides following three potential avenues for performance improvement: (i) control over data placement with explicit partitioning, which allows design and experimentation with different partitioning strategies to improve load balancing and overall performance, (ii) better locality, and (iii) explicit partitioning helps in exploring different communication trade-offs since NUMA is a shared-memory system. Based on these intuitions, we postulate the following hypothesis: *A distributed-memory like middleware that makes graph partitioning and communication between partitions explicit, can improve the performance on a NUMA system.*

To test this hypothesis, we design and implement a NUMA-aware graph processing framework that treats the NUMA platform as a distributed system, hence embraces its design principles; in particular explicit partitioning and communication, and evaluate it against the state-of-the-art NUMA-oblivious [15] and NUMAaware [42] graph processing frameworks. We further describe optimization techniques to reduce communication overhead. And finally, provide a set of practical guidelines for choosing the appropriate partitioning and communication strategies.

### **1.2** Contributions

The contributions of this dissertation are:

*1) Design Exploration:* Given their resemblance, there exist opportunities to transfer the know-how and design philosophies of distributed graph processing to develop shared-memory graph processing solutions optimized for NUMA systems. To this end, we explore a reference distributed design (Section 3.3). In particular, we evaluate the performance of a fully distributed (referred to as NUMA 2-Box design, \$3.3.2) and one shared-memory (referred to as NUMA 1-Box design, \$3.3.3) inter-partition communication strategies (where each partition belongs to a NUMA domain) and how they compare against a NUMA-oblivious implementation. We found that, on a NUMA platform, a graph processing solution based on the design philosophies that targets shared-nothing distributed system, consistently outperforms the state-of-the-art NUMA-oblivious shared-memory solution (Section 5.2). Additionally, we explore two distributed graph partitioning techniques for NUMA, and introduce a new partitioning technique (Section 3.2) that leads to load balance of up to 95% and overall performance improvement of up to  $5.3 \times$ .

2) A New NUMA-aware Design: Based on our design explorations, we propose a design (referred to as NUMA 0-Box design, §3.3.4), that takes into account *distributed shared-memory* nature of NUMA, and consists of explicit graph partitioning and implicit communication. It improves data locality through NUMA-aware partitioning and at the same time minimizes the overhead of remote accesses by overlapping remote memory operations with computation. (Section 3.3)

Evaluation shows, this new design offers, for BFS up to  $2.37 \times$ , SSSP up to  $2.27 \times$  and PageRank up to  $1.89 \times$  improvement in time-to-solution over the respective NUMA-oblivious implementations. This design, however, did not improve performance of PageRank over the NUMA 2-Box design (explained in Section 5.2).

*3) Analytical Model for Performance Prediction:* We present an analytical model for predicting algorithm performance for the three aforementioned NUMA designs (Section 3.4). We demonstrate the effectiveness of our prediction model for PageRank by comparing with empirical results. (Section 5.3)

4) Evaluation: We evaluate the aforementioned three NUMA-aware designs

for the following applications: PageRank, BFS and SSSP, using both real-world and synthetic graphs (with up to 128 billion undirected edges), on a Intel NUMA platform with four sockets and 1.5TB memory. Summary of our findings are the following:

(i) We compare the three graph partitioning strategies and find that our proposed approach offers up to  $5.3 \times$  speedup and 95% load balanced partitions. (Section 5.1)

(ii) We demonstrate scalability on up to four sockets on a NUMA platform: maximum speedup (over one socket) achieved by PageRank is  $3.7 \times$ , BFS is  $2.9 \times$  and SSSP is  $2.8 \times$ . (Section 5.2)

(iii) We show RMAT scaling using up to Scale 32 graph. Our BFS implementation achieves a maximum of 39 giga traversed edges per second (GTEPS). (Section 5.2)

(iv) We compare our work with a recent NUMA-aware graph processing framework, Polymer and demonstrate that our solution consistently outperforms Polymer, e.g. up to  $13.9 \times$  faster for BFS. Additionally, our solution is  $\sim 4.4 \times$  more memory efficient. (Section 5.4)

(v) Finally, we present the performance numbers we achieved in Graph500 competition, where we secured World Rank 2 (June, 2018 list) for SSSP kernel, and among top 3 single-node submissions for BFS kernel. (Section 5.2)m

### **1.3 Dissertation Structure**

The rest of this dissertation is organized as follows. Chapter 2 presents background and related work. Chapter 3 describes the design of our NUMA-aware graph processing framework. Chapter 4 presents the methodology used to implement and evaluate the designs introduced in Chapter 3. Chapter 5 evaluates the performance of our designs. And, Chapter 6 concludes the dissertation.

## **Chapter 2**

## Background

This section provides the necessary background information required to understand the contributions of this dissertation. First, this chapter presents a brief overview of graph (§2.1) and graph processing (§2.2). Then it describes three common CPU based hardware platforms (§2.3) used for graph processing. Next, this chapter describes Bulk-Synchronous Parallel (BSP) model (§2.4), a popular processing model among distributed systems, and explains thoroughly how it is leveraged in the context of graph processing (§2.5). Finally, it provides an overview of the graph algorithms that we have used (§2.6), followed by related work (§2.7).

### 2.1 Graph

A graph G = (V, E), as shown in Figure 2.1, consists of a set of vertices V and a set of edges E. If the edges of a graph are unidirectional, the graph is called a directed graph. While, if all the edges of the graph are bidirectional, then it is called an undirected graph. Edges of a directed graph are represented by arrows (pointing towards the destination vertex), as shown in Figure 2.1, while the edges in an undirected graph are typically drawn as lines.

**Graph Storage.** Graphs are stored, usually, using either linked-lists or arrays. For high-performance and to efficiently store large graphs in memory, array based formats like Compressed Sparse Row (CSR), Coordinate (COO), Compressed Sparse Column (CSC), or Doubly Compressed Sparse Column (DCSC) formats are used.

**Figure 2.1:** On left, a directed graph with 6 vertices and 7 edges. On right is the Compressed Sparse Row (CSR) representation of the graph. CSR format has two arrays, 'vertex array' (or offset array) and 'edge array'. 'vertex array' contains starting index of the outgoing edges originating from each vertex (represented by the indices of vertex array). 'edge array' contains only the destination vertices of the edges.

Figure 2.1, presents the CSR format, a popular format (that we have also used) used to achieve better performance and memory efficiency. CSR format targets directed graphs. To store undirected graphs, each edge of the undirected graph is represented by two direct edges (one in each direction). As shown in Figure 2.1, 'vertex array' and 'edge array' are the two CSR data structures. Size of the 'vertex array' is same as the number of vertices in the graph, and it contains the starting index of the neighbors list of each vertex. Indices of the 'vertex array' represents the vertex ID. 'edge array' contains the destination vertices of the edges originating from source vertex in 'vertex array', and its size equals the number of edges in the graph. For example, in Figure 2.1, vertex 2 has one outgoing edge, to vertex 1. The value, 3, at index 2 in 'vertex array', is the index value of the start of the neighbors list of vertex array. Size of the neighbors list of a vertex is determined by subtracting the current value at the index location in vertex array from the next value or from the edge count for the last vertex. Therefore, neighbors list size of vertex 2 is (value at index location 2+1) - (value at index location 2) i.e. 4-3 = 1.

### 2.2 Graph Processing

A wide set of big data problems, like analyzing online social networks, bioinformatics, financial and business analytics, transport network analysis, to name a few, can be modeled as graphs. For example, in online social networks, people are represented by vertices and an edge between the two represents their friendship. Further, domains like machine learning and data mining are also exploring graph processing at their core. In all these high impact applications, in order to get meaningful insights from the huge data, these massively large graphs need to be processed fast yet efficiently (w.r.t cost).

Graph algorithms and workloads pose following key characteristics that make them challenging to process efficiently.

- Iterative. A typical graph algorithm processes a graph in rounds, where in each round only a set of vertices is active and can be processed in parallel. For example, in BFS, processing starts from a source vertex and it activates its neighbor vertices only, which then iterate over their respective neighbor vertices in the next round, and so on.

- Highly irregular, data-dependent memory access patterns. Graph processing suffers from highly irregular data-dependent memory access pattern as the neighbors are scattered in memory. It leads to poor data locality and high random memory accesses.

- 3. *Low compute-to-memory-access ratio.* Most of the graph algorithms, like BFS and SSSP, have low compute-to-memory-access ratio, i.e. they do very less computation per memory access, thereby being memory bound. For example, in BFS, very little processing is done on the data associated with a vertex, and most of the time is spent in accessing the neighbors.

- 4. *Hard to obtain balanced partitions*. Many real-world graphs have heavily skewed, 'power-law' [14] vertex degree distribution: most of the vertices have low edge degree, while a few vertices have high edge degree (e.g., celebrities in online social networks) that connect to a large part of the graph. These type of graphs are also called as *scale-free graphs*.

If we process these graphs in a distributed system, their heavily skewed degree distribution makes it hard to obtain balanced partitions to achieve better load balance and over all performance. Further the partitioning algorithms developed specifically to obtain good partitioning are computationally expensive.

5. Large memory footprint. Many real-world graphs are massive: some have hundreds of billions of edges - leading to a huge memory footprint. For example, current Facebook graph (a social network graph with ~137 Billion edges) and Web Data Commons - Hyperlink Graph (a web graph with ~128 Billion edges) [3, 4], require more than 2TB of memory. To process such large graphs efficiently, the whole graph needs to be in the memory.

## 2.3 Hardware Platforms

This section aims at describing the three popular CPU-based hardware platforms.

#### 2.3.1 Shared-nothing cluster

A distributed system or a shared-nothing cluster consists of hundreds to thousands of processing units (also called as nodes), where each processing unit has access to only its own memory, that are connected with each other through fast interconnects, like OmniPath and InfiniBand.

Given the huge memory footprint of real-world graphs, traditionally these large shared-nothing clusters have been used, as they have large aggregated memory. These memory-parallel, shared-nothing clusters have experienced tremendous success in terms of scale and performance, as could be seen in Graph500 Competition [2] (which ranks supercomputers for data intensive applications), as well as been used by many distributed graph processing frameworks including Google's Pregel [26] and GraphLab [17].

These shared-nothing clusters are not cache-coherent. Here, the graph is partitioned explicitly (one partition on each of the nodes) and the communication between different nodes is explicit. Graph partitioning leads to having boundary edges that cross-over between nodes. The nodes run the graph algorithm kernel in-

Figure 2.2: An illustration of SMP/UMA (left) and NUMA (right) architectures.

parallel on their respective partition, and communicate with other processing units to share the remotely updated vertex state.

#### 2.3.2 Symmetric Multi-Processor (SMP) Architecture

In Symmetric Multi-Processor (SMP) architecture, memory is shared between processing units, and it provides uniform access time to any location in memory. It is, therefore, also termed as Uniform Memory Access (UMA) architecture. As shown in Figure 2.2 (left), the CPU cores share the same memory bus to access the memory. This leads to uniform access time from any core to any location in memory. In recent SMP architecture machines, the memory available could be up to few hundreds of gigabytes. This helps in processing mid-size graphs, that fit into memory, at a lower development cost compared to distributed system as there is no need of explicit partitioning and inter-partition communication.

The drawback of this architecture is, as the memory bus is shared among all the cores, this design leads to contention on the shared bus with increase in the number of CPU cores. Therefore, the design does not scales with number of CPU cores and memory.

#### 2.3.3 Non-Uniform Memory Access (NUMA) Architecture

NUMA is a shared-memory architecture consisting of a set of processors (often called sockets), each with their own local memory. Each socket is connected with other sockets through an interconnect (Quick-Path Interconnect in Intel systems). Accessing socket-local memory takes distinctively less time than accessing remote

Figure 2.3: Local and remote memory bandwidth for read and write operations on 4-Socket Intel Xeon (E7-4870 v2, Ivy Bridge) machine, for different workloads (size in MB).

memory over the interconnect. NUMA addresses the scalability issues of SMP architecture, and provides higher overall memory bandwidth.

NUMA distributes memory to each processors: (Fig. 2.2 - right) each processor has fast access to its local memory, while to access local memory of another processor, it has to traverse over the slow interconnect. This reduces contention over local memory bus as well as provides the opportunity to scale the system. Note that scalability comes at the cost of remote memory access. Obtaining maximum performance requires careful placement of data to avoid/minimize remote memory accesses with lower latency and higher bandwidth.

We benchmark our testbed, a four socket Intel Xeon system (more description in Section 4.2), by extending Stream [27] benchmark to measure local and remote, read and write memory bandwidth for both sequential and random accesses. We measure these access patterns, because they frequently occur in graph processing. We run the experiments for array size from 1 MB and double the array size until 1 GB (at which point it saturates the memory bandwidth). Table 2.1 presents the memory bandwidth achieved in different access modes for arrays of size 1 GB. We

|                         | Access     | Local | Remote |

|-------------------------|------------|-------|--------|

| Read Throughput (MB/s)  | Sequential | 2464  | 2069   |

|                         | Random     | 286   | 226    |

| Write Throughput (MB/s) | Sequential | 1438  | 1024   |

|                         | Random     | 238   | 188    |

| Latency (ns)            |            | 119   | 178    |

**Table 2.1:** Memory bandwidth characteristics of our Testbed (Four socket Intel Xeon, E7-4870 v2; more description in Section 4.2). Memory bandwidth is measured with custom benchmark with arrays of size 1 GB. Memory latency is measured using Intel Memory Latency Checker.

observe that non-local access throughput is up to 26% and 40% slower than local access throughput for read and write operations, respectively. Interestingly, remote sequential access throughput is as much as  $9 \times$  and  $6 \times$  more than local random access throughput for read and write operations, respectively. This observation is important for graph processing, which incurs highly irregular memory access patterns. On the other side, remote memory latency, as measured using Intel Memory Latency Checker, is 49% more than local memory latency.

## 2.4 Bulk-Synchronous Parallel (BSP) Processing Model

Bulk-Synchronous Parallel (BSP) model is a popular processing model targeting distributed systems. Therefore, BSP model implies that the data is partitioned and partitions are allocated on the processing elements. In the BSP model (Fig. 2.4), the processing consists of a sequence of rounds or *supersteps* (in BSP terminology). Each superstep consists of three phases (executed in order): computation, communication, and synchronization.

- In the *computation phase*, each processing unit processes their respective partition independently.

- In the *communication phase*, processing units exchange messages with respective remote partitions, as well as apply the remote updates to their local buffers.

Figure 2.4: A high level illustration of the Bulk Synchronous Parallel Model.

• The *synchronization phase* guarantees that the next cycle restarts only after all messages have been delivered.

This sequence of supersteps continues until convergence or termination conditions has been satisfied. Finally, if required, the results are aggregated from all the partitions.

## 2.5 BSP-Style Graph Processing

Graph computations can be modeled as Gather-Apply-Scatter (GAS) [17], where the graph processing follows sequences of **g**ather, **a**pply and **s**catter operations. In gather phase, vertices *gather* information from their neighbors to update their local state in *apply* phase, and then in *scatter* phase, they communicate their updated value to their neighbors. For example, in PageRank, a vertex computes its rank by gathering rank of its in-degree neighbors, and scatters its new rank to its outdegree neighbors. The BSP processing model inherently matches with this iterative nature of graph algorithms, where sequence of gather, apply and scatter operations

Shadow copy of the remote neighbor in the local partition

$S_{\rho}v$  – State buffer of a vertex v belongs to partition p; S' indicates the state buffer of a remote vertex

**Figure 2.5:** BSP graph processing depicting computation and communication phases in a superstep. In the computation phase, the state of a vertex and its shadow copy (on a remote partition) are updated independently. In the communication phase, the vertex and its shadow copy communicate to determine the correct state. For example, in SSSP, after communication, both the vertex and its shadow copy commit to the minimum distance at that point in traversal.

resembles the three phases of a superstep in BSP model.

Since BSP model implies that the data is partitioned and allocated on the processing elements, initial step is to partition the graph (partitions in Figure 2.5 are of the graph shown in Figure 2.1). Each partition has a set of local vertices and edges. Since an edge is associated with two vertices, which could be on different partitions, a map is maintained for the remote vertices (vertex 3 in PID0 and vertex 0 in PID1, in Fig. 2.5) in each partition. Further each partition maintains algorithm specific state buffer(s) (such as *rank* array in PageRank) for local vertices (buffer  $S_0$  in PID0 and  $S_1$  in PID1, in Fig. 2.5) as well as remote vertices (buffer  $S'_1$  for remote vertices in PID0 and  $S'_0$  for remote vertices in PID1, in Fig. 2.5). The three phases of a superstep of BSP model are performed as follows in the context of graph processing:

In *computation phase*, processing units work in parallel, and execute the graph algorithm specific kernel on the set of vertices belonging to their partition, and update their local state buffer (buffer  $S_0$  and  $S_1$  in Fig. 2.5). The local state of active remote vertices is also updated and aggregated locally in the respective buffer (buffer  $S'_1$  and  $S'_0$  in Fig. 2.5).

In *communication phase*, each partition exchange the messages for the boundary edges, and applies the remote updates received to their local state buffers. In Fig. 2.4, both the partitions transfer the state of remote vertices to make sure local and remote states of the vertices are same, i.e.  $S_0$  and  $S'_0$  are the same, and  $S_1$  and  $S'_1$  are the same.

Finally, *synchronization phase* ensures that all the partitions are updated with the latest state of the remote vertices, before the superstep cycle restarts.

Similar to the generic BSP model, the sequence terminates once every processing unit has finished processing their respective partitions. After termination, final result is aggregated from all the processing units through a global reduction.

### 2.6 Graph Algorithms

We consider PageRank, Breadth-First Search - Top Down (BFS-TD), Breadth-First Search - Direction Optimized (BFS-DO), and Single-Source Shortest Path (SSSP) algorithms. *We use these algorithms to evaluate our work because* (i) these algorithms have been widely studied in the context of high-performance graph processing systems and have been used in the past studies [5, 15, 17, 30, 35, 36, 42], (ii) BFS and SSSP are also used as benchmarks for the Graph500 competition [2], to rank supercomputers for data intensive applications, (iii) they are the building blocks of more complex graph algorithms (for example, BFS is used as a subroutine in complex graph algorithms like connected components, max flow, betweeness centrality and clustering), and (iv) these algorithms are good representation for studying the performance of any hardware platform for irregular memory access pattern.

A short description of the algorithms is described below.

#### 2.6.1 PageRank

PageRank [31] is a well-known algorithm used by search engines for ranking web pages. In PageRank, a vertex computes its rank based on the rank of its neighbors. The algorithm continues until the convergence of the rank of all the vertices, or a predefined number of iterations have been completed. *PageRank has a high compute-to-memory-access ratio, and the workload is stable in every iteration, since in each iteration it computes the rank of all its vertices*. It could be implemented as a pull-based or push-based algorithm [35]. In the pull-based approach, each vertex 'pulls' the rank of its neighbors, over the incoming edges, to compute its new rank. In the push-based approach, each vertex 'pushes' its rank to its neighbors, over the outgoing edges. Note that the push-based approach is less efficient, since, its parallel implementation requires atomic operations [30]. We implement pull-based approach and the algorithm kernel executes for predefined number of iterations [16].

#### 2.6.2 Breadth-First Search

BFS is a graph traversal algorithm which determines the level of each vertex, starting from a source vertex. It is a fundamental graph algorithm which is also used as a sub-routine in complex graph algorithms, like connected components, betweeness centrality, max flow, and clustering. *BFS has a low compute-to-memory-access ratio, and since it is a traversal based algorithm, workload is not stable in every iteration (or superstep).* Like other graph traversal algorithms, BFS presents the concept of a *frontier*, which consists of a set of active vertices that are processed in the current iteration, to build the *next frontier*. The *next frontier* can be manipulated in different ways. We explore three implementations of BFS algorithm.

#### BFS - Top-Down (BFS-TD)

It is the classic level-synchronous approach of doing BFS. In each iteration it processes all the edges of the vertices in the current frontier, to build the next frontier with the unvisited vertices that can be reached. For power-law graphs, it has been observed that this approach leads to (1) drastic increase in the frontier in initial few supersteps followed by steep decrease in frontier size in tailing supersteps, and (2) high write traffic, in the initial supersteps, since many edges in the current frontier tries to add the same vertex in the next frontier [10].

#### **BFS - Direction Optimized (BFS-DO)**

Direction Optimized BFS [10] addresses the above mentioned drawbacks of Top-Down version of BFS, by manipulating the next frontier in bottom-up way when the current frontier is large. In Bottom-Up step, it iterates over unvisited vertices and selects those for the next frontier which have a neighbor in the current frontier. This helps in drastically reducing the number of edges explored especially when the frontier is large, since once an unvisited vertex, that has a neighbor in current frontier, is explored, there is no need to explore its other edges. This, especially, reduces work for high-degree vertices. Further, this approach does not require any atomic operation as the write operation is done only to update the state of the unvisited vertex, to include it in next frontier, while rest of the accesses are read - to check if any of its neighbors are in the *current frontier*, thereby reduces the contention [10, 34]. Direction-Optimized BFS kernel starts with Top-Down step, and once the frontier size is large enough, it switches to Bottom-Up step. For the final supersteps, when the frontier size is again small, it switches back to Top-Down step. Note that switching between the steps (from Top-Down to Bottom-Up and from Bottom-Up to Top-Down) is heuristics based, and one needs to hand-tune them to attain maximum performance on a particular graph.

#### **BFS-Graph500**

Graph500 competition [2] has different requirements for measuring the performance. First, it counts an undirected edge as only one edge, while we represent an undirected edge as two directed edges, one in each direction. Therefore we have to half the number of edges traversed, while computing the performance. Second, it requires including algorithm initialization time as well in the algorithm execution time, not a standard practice in the literature. And finally, it requires the BFS tree as output rather than the level of each vertex in the BFS tree. We have implemented our BFS-DO as the kernel inside Graph500 skeleton, and modified its data structures with Graph500 requirements.

#### 2.6.3 Single-Source Shortest Path

SSSP is a traversal based graph algorithm and finds the shortest path from a source vertex to every vertex in the connected component. It has wide applications including IP routing, transportation networks, and social network analysis. In SSSP, each edge is associated with a predefined weight which, typically, is a measure of 'cost' to make a transition from one vertex to one of its neighbors. Weights increase the memory footprint of the graph by almost  $2\times$  (depending on the data type used). Following are the two implementations of SSSP algorithm that we use:

#### SSSP

We adapt Bellman-Ford algorithm [1] to implement SSSP, as it provides better scope of parallelism and the opportunity to allow the active vertices to perform relax operation on its edges within the same iteration [16]. *This reduces the number of supersteps, since more number of vertices become active per superstep.* The algorithm gives the distance of each vertex from the given source vertex.

#### Graph500-SSSP

Along with the distance buffer, containing distance of each vertex from the source vertex, for SSSP, Graph500 also requires sssp-tree containing parent of each vertex. This is expected to increase the communication overhead in every superstep by almost  $2\times$  because of communicating the parents for boundary edges among the partitions, along with the respective distance value. *We optimize this by not requiring to communicate the tree at all during supersteps, and aggregate the tree in only the aggregation phase.* In the computation phase, if the edge is a boundary-edge, we store the partition ID of the remote vertex and the local ID of the parent vertex in the tree buffer. Distance buffer is updated same as the above implementation of SSSP. During communication, if for the remote partition ID for the respective vertex in the local tree buffer. This way it knows that parent is in the respective remote partition. In aggregation phase, it iterates over the local tree buffers of all the partitions to aggregate the results. If the value in the local tree buffer corresponds to a remote partition, it determines the parent by looking at the

respective tree buffer in that remote partition, and gets the global id of the parent from the global map.

### 2.7 Related Work

Since their inception, NUMA architecture has been the source of performance issues, because of their distributed shared-memory, in performance critical applications targeting shared-memory systems.

This section describes the work done on addressing the performance issues on NUMA architecture, in general. Then it discusses the graph processing frameworks which targets single-node shared-memory systems, and are NUMA-oblivious. And, finally it discusses the graph processing framework that targets shared-memory NUMA architecture, followed by NUMA-aware graph kernels.

*NUMA-aware work.* As shared-memory NUMA architectures are becoming ubiquitous in today's commodity servers, many work have shown the performance issues on running the applications that were implemented for shared-memory (assuming SMP architecture), and have presented optimizations which improved their performance on NUMA-architecture based shared-memory systems. For Databases, works like [22, 25] have shown maximum performance gain in the range of  $3 \times - 6 \times$  on accelerating different data management primitives and in-memory storage operations, with NUMA optimizations. Further, NUMA effects are also severe in Machine Learning [28] and Deep Learning [33], where workload is regular. NUMA-Caffe [33] have shown that the convolution layer (the most significant and time consuming layer [21]) in Convolution Neural Network (a type of Deep Neural Network) leads to maximum remote memory accesses, and with NUMA optimizations they achieved performance gain of  $2 \times$  to  $14 \times$ .

Shared-memory Graph Processing Frameworks. Since shared-memory systems have up to few hundreds of gigabytes of memory available, which is enough to process mid-size graphs, frameworks like Galois [30], Ligra [35] and Totem [15] have been developed. These frameworks treats shared-memory system as if it is based on SMP architecture. And since NUMA architecture is also shared-memory based, these frameworks run on NUMA architecture as well. But, they suffer from the distributed nature of the shared-memory in NUMA, and hence do not perform and scale well [5].

*NUMA-aware Graph Processing Framework.* To the best of our knowledge, Polymer [42] is the only NUMA-aware graph processing framework. It embraces the design philosophy of distributed systems, and extends Ligra to improve performance on NUMA-architecture based shared-memory systems. (discussed in detail in Section 5.4) *NUMA-aware graph kernels.* There are work, like [40, 41], that have optimized specific graph kernels, primarily BFS for Graph500, for NUMA architecture. The NUMA-aware optimizations that they have done are specific to graph kernels. On the other hand, *all the NUMA optimizations in our work are graph algorithm agnostic.*

## **Chapter 3**

# A BSP-style NUMA-aware Graph Processing Framework

### 3.1 Intuition

The NUMA architecture resembles distributed shared-nothing platforms. As described in previous section, the BSP processing model naturally matches graph computation. Therefore, for distributed graph processing, BSP graph processing model is commonly used. On a NUMA machine, the expected benefits of using BSP model are: (i) Explicit data placement, which means data is processed at the node-local level - thus having the potential to reduce processing time through better *locality* as during processing no remote accesses are made, (ii) *Explicit partition*ing allows experimentation with different load balancing techniques, and (iii) as NUMA is a shared-memory system, we can explore different inter-partition communication trade-offs, to reduce communication overhead. The advantages obtained through explicit data placement and partitioning need to be greater than the overheads present in having BSP model on a shared-memory NUMA system. The expected overheads are: (i) inter-partition communication overhead, (ii) memory overhead - since we have to store the state of remote vertices on each partition, (iii) thread management, (iv) development overhead - designing and implementing partitioning, inter-partition communication and result aggregation, and (v) preprocessing overhead of partitioning.

The goal of this study is to evaluate if having a distributed-memory like middleware on a shared-memory NUMA machine provides performance advantages in spite of aforementioned overheads.

This chapter describes the design of our BSP-style, NUMA-aware graph processing framework, starting with graph partitioning strategies (§3.2), followed by describing the design opportunities for BSP-style graph processing on sharedmemory NUMA system (§3.3). Then it provides an analytical model to predict their performance (§3.4). Finally, it describes how the GAS model maps to our design (§3.5).

## **3.2 Graph Partitioning**

Distributed graph processing begins with partitioning the graph and allocates the partitions on the processing units. The goals of partitioning are: (i) to process large graphs - to leverage the large aggregated memory, (ii) to improve load balance, and (iii) to process the partitions in parallel.

Graph partitioning is an NP-complete problem [7], and having balanced partitioning on real-world power-law [14] graphs is challenging [6, 23, 24]. Popular distributed graph processing frameworks like Pregel [26] and GraphLab [17], do random partitioning, where vertices are distributed randomly among the processing units, as it leads to uniform vertex degree distribution. Heterogeneous distributed system like Totem [15] uses Sorted/Degree-aware partitioning and have shown that this strategy performs better than Random partitioning on a single-node hybrid system. *The* **success criteria** for a good partitioning strategy are: (i) better load balance, and (ii) most importantly, better overall performance.

In a NUMA system, explicitly partitioning the graph does not help in processing larger graphs, as the memory available is fixed, but it provides better locality (by serving all the accesses from local memory of the NUMA node where the partition is assigned to), and enables implementing and experimenting with different partitioning strategies, designed for distributed systems, to improve load balance and overall performance. We have implemented two graph partitioning strategies, random and Sorted/Degree-aware. We also introduce a new partitioning strategy that leads to better load balance and higher performance, than the above two partitioning strategies.

**Random Partitioning.** In this partitioning strategy, vertices are assigned randomly to the processing units. Random partitioning is a popular strategy among the distributed graph processing systems, like Pregel and GraphLab, targeting graphs having power-law vertex degree distribution [14]. It increases the probability of each partition having equal variability in terms of vertex degree.

*Sorted or Degree-aware Partitioning.* In this approach the vertices are first sorted by degree, and then they are assigned to the processing units as a contiguous chunk of vertices with even share of edges. This strategy leads to better locality since the likelihood of having most of the neighbors in the same partition increases. It has been shown to perform better than random partitioning in Totem [15], a heterogeneous distributed system. But, load imbalance increases significantly, as shown in Fig. 5.1, since few partitions get dense subgraph (chunk with high-degree vertices will have few vertices) while others get sparse subgraph (tailing chunk consist of low-degree vertices, thereby the subgraph will have most of the vertices).

*New Strategy - Hybrid Partitioning.* We observed that Random partitioning leads to better load balance but suffers from poor data locality. Sorted or Degree-aware partitioning on the other hand achieves better data locality, but leads to severe load imbalance. With these observations, we designed and implemented a hybrid partitioning technique that alleviates this problem. In the first step, we randomly assign the vertices to the processing units, same as random partitioning. And then, we sort the vertex list of individual subgraphs by degree. Randomly assigning the vertices to the processing units increases the probability that each partition has equal variability in terms of vertex degree (thereby increasing the chance that the generated load is well balanced). Sorting individual vertex lists improves data locality [15]. Later we discuss its performance compared to other two strategies in Fig. 5.1 and Fig. 5.2.

## 3.3 Design Opportunities for NUMA-aware Graph Processing

Since we partition the graph and place one partition on each NUMA node, it allows us to do computation in parallel with all the accesses served from the local memory, during the computation phase of a superstep. Since NUMA system is a sharedmemory system, we have the opportunity to explore shared-memory specific optimizations to reduce communication overhead. We explore three communication alternatives that address the motivation of this dissertation: *To what degree, designing for NUMA as for a distributed memory system can enable performance (by explicitly presenting locality), in spite of inherent overheads (message exchange), in an application agnostic way.*

In this section, we describe the data structures we have used in our framework, and the three design options to optimize communication overhead.

#### **3.3.1** Data structures

To store the graph in-memory, we use Compressed Sparse Row (CSR) format, as described earlier in Section 2.1 as well as in Figure 3.1 (arrays V and E). As presented in [16], the arrays V and E represent the CSR data structure, where  $V_i$  contains the start index of the neighbors of the vertex *i* in the edge array E. In each partition *p*, the vertex IDs range from zero to ( $|V_p| - 1$ ), where  $V_p$  is the set of local vertices belonging to a partition. Edge array E stores the destination vertex of an edge, which has partition ID encoded in high-order bits (shown in Fig. 3.1 as subscripts). For boundary (or remote) edges, value stored in E depends on the communication design we select. For NUMA 2-Box (§3.3.2) and NUMA 1-Box (§3.3.3) designs, value stored is the index to its entry in the outbox buffer (discussed later), not the remote neighbor ID. But, for NUMA 0-Box design (§3.3.4), value stored is the remote neighbor ID.

The array S, of length  $|V_p|$ , represents the algorithm-specific local state of each local vertex in the partition. The message (outbox and inbox) buffers allocation varies by the design options (discussed in details in every design options). The outbox buffer is for the messages for the remote neighbors, and has an entry for each remote neighbor. The inbox buffer is for the messages for the local vertices which are remote to other partitions, therefore has an entry for each local vertex that is remote to another partition. Both the message buffers have two arrays: one to store the remote vertex ID, and the other stores the corresponding message. More

**Figure 3.1:** High-level illustration of inter-partition communication of NUMA 2-Box design. *V* and *E* are the buffers to represent the graph in CSR format (as mentioned in Section 2.1 and Figure 2.1). *S* is the state buffer for local vertices. Bottom blue and red solid lines depicts communication paths for NUMA 2-Box, where explicit memory copy through in - and out - boxes are required. For push-based algorithms, during computation phase, each partition manipulates its local state buffer *S* for local vertices and updates for remote vertices are aggregated locally in the outbox buffer. During communication phase outbox is copied into the inbox of the respective remote partition, which are then applied to the respective local state buffers.

details are provided according to the design options described below.

#### 3.3.2 NUMA 2-Box Design

In this design, we fully embrace the design philosophy of a distributed system, thereby assuming NUMA as a shared-nothing distributed system - where nodes are independent and are connected through the interconnect. In this design, as shown in Fig. 3.1, for communication, it has two message buffers (outbox at source and inbox at destination partition). Further, as mentioned before, for remote edges, value stored in *E* is the index to its entry in the outbox buffer. So, the value in *E* for the entries  $0_1$  and  $2_1$  (in left partition - PID-0), and  $4_0$  (in right partition - PID-0).

1) is replaced by the index to its entry in respective outbox buffer, i.e. by  $0_1$  and  $1_1$  (where subscript 1 stands for the outbox for remote partition 1), and  $0_0$  (where subscript 0 stands for the outbox for remote partition 0), respectively.

Following is the BSP-style graph processing in this design for both push-based and pull-based algorithms (how we implement GAS model in our design is explained in §3.5).

For *push-based* algorithms like BFS and SSSP, in computation phase, each partition manipulates its local state buffer *S* for updates for its local vertices. *All the updates for remote vertices are aggregated and stored in respective outbox buffers.* In communication phase, as shown in Figure 3.1, the partitions transfer (blue and red arrows) the respective outbox buffer to the corresponding remote inbox buffer, and apply the remote updates, received from remote partitions in their corresponding inbox, to their local state buffers (red arrows from inbox to buffer *S*) if necessary conditions are met (for example, in SSSP, remote distance value is committed if it is lesser than the current value).

For *pull-based* algorithms, like PageRank, during compute phase, each local vertex updates its state by reading the state of its incoming-neighbors. The state of remote incoming-neighbors are accessed from respective outbox buffer. During the communication phase, the local vertices (which are remote in other partitions) update their new state in the respective inbox buffer, which is then copied to the outbox buffer of the remote partition. In the next superstep, this updated state is utilized to calculate the new state of the local vertices.

#### Advantages

(i) *Zero remote memory accesses.* This design leads to zero remote memory accesses, since all the accesses are local in both computation and communication phases, and the message buffer (out/in box) is explicitly copied to the remote partition's message buffer (in/out box).

(ii) *Message aggregation.* A vertex can be associated with many edges (as average degree of the vertices is 32 for synthetic workloads and  $\sim$ 75 for real-world graphs 4.3). Aggregating the remote updates for the remote vertices locally leads to sending only one message per remote vertex during the communication phase.

Figure 3.2: High-level illustration of NUMA 1-Box design. V and E are the buffers to represent the graph in CSR format (as mentioned in Section 2.1 and Figure 2.1). S is the state buffer for local vertices. For push-based algorithms, during computation phase, each partition manipulates its local state buffer S for local vertices and updates for remote vertices are aggregated locally in the outbox buffer. During communication phase, updates in the remote outbox are sequentially accessed and applied to the respective local state buffers.

This drastically decreases the inter-partition traffic and the communication time.

#### Drawbacks

(i) *Communication overhead.* Since remote vertices are marked and counted during partitioning step, the size of the message buffers remain unaltered during the algorithm execution. Though *message aggregation* leads to reducing the number of messages send, there is still communication overhead when the message buffer is mostly empty, which is often the case while processing for algorithms, like BFS and SSSP, where communication happens via selective edges only in every superstep.

#### 3.3.3 NUMA 1-Box Design

Since NUMA is a shared memory system, instead of having two explicit message boxes, one at source and another at destination, only one buffer can be physically allocated on the partition, and the pointer to the box could be swapped during communication phase. In this design we allocate only one message buffer, at the source, and assign it to outbox, because of the fact that outbox in source partition is inbox in the destination partition. Similar to NUMA 2-Box design, the value stored for remote-edges in E is the index to its entry in the respective outbox buffer.

Following is the BSP-style graph processing in this design for both push-based and pull-based algorithms.

The computation phase for both *push-based* and *pull-based* algorithms are same as NUMA 2-Box design, as in both the cases outbox is allocated on source partition, and only the communication phase differs.

For *push-based* algorithms, in communication phase, the partitions swap the pointer to the respective outbox message buffer with the corresponding remote inbox message buffer's pointer. It does remote sequential access to read the remote updates, and applies them to their local state buffer, as shown in Figure 3.2.

For *pull-based* algorithms, during the communication phase, it writes the new state of its local vertices (which are remote in other partitions), stored in local state buffer *S*, to the respective inbox buffer (which is a pointer in this design, and points to the outbox buffer in the remote partition - inbox in source partition is outbox in destination partition), by doing remote sequential writes.

#### Advantages

(i) *No explicit message transfer.* This design leads to zero remote memory accesses during computation phase, same as the previous design. In communication phase, it passes only the pointer to the address of physically allocated box, rather than the entire message buffer.

(ii) *Message aggregation*. Message aggregation advantage is same as in the NUMA2-Box design.

**Figure 3.3:** High-level illustration of NUMA 0-Box design, which overlaps computation with communication. *S* is the state buffer for local vertices. Note that in this design we get rid of communication infrastructure. During computation phase, each partition manipulates its local state buffer *S* for local vertices and remote updates are directly written to the respective local state buffer of the remote partition. Atomic writes are used to ensure correctness.

#### Drawbacks

(i) *Communication overhead.* Though this design leads to not transferring the message buffer explicitly in the communication phase, all the accesses to the message buffer are remote sequential, which in turn depends on the costly random access to update the local state buffer. Further, similar to NUMA 2-Box design, it suffers from the communication overhead when the message buffer is mostly empty.

#### 3.3.4 NUMA 0-Box Design

In this design we consider the fact that NUMA is a *distributed* shared-memory system. We do explicit partitioning as if NUMA is a distributed system, but we access the state buffers as if we are in a shared-memory system. As shown in Fig. 3.3, we do not use communication infrastructure.

During computation phase, for *push-based* algorithms, if a remote vertex is

**Figure 3.4:** Number of Remote vertices vs number of remote updates in each partition in every superstep of Direction-Optimized BFS (BFS-DO) for RMAT31 in NUMA 2-Box design. The Y-axis represents frequency (in millions), **in log-scale**, of the number of remote updates (per superstep) and the total number of remote vertices in each partition. The ss-'x' on X-axis represents the sequence of supersteps. We observe that remote updates are  $\sim 22 \times$  less than the number of remote vertices.

visited, the state is updated directly in the local state buffer of the respective remote partition, thereby *it overlaps computation with communication*. Atomic operation is used for updating shared states, to ensure consistency.

For *pull-based* algorithms, like PageRank, during compute phase, each local vertex updates its state (e.g. rank for PageRank) by gathering the state of its incoming-neighbors. For remote incoming-neighbors, it reads the state of the remote vertex from the local state buffer of the respective remote partition.

Note that, in this design, the state of **all the boundary edges** is accessed remotely.

#### Advantages

(i) *Overlapping computation with communication*. This design overlaps computation with communication. It performs better for algorithms like BFS and SSSP,