# Northumbria Research Link

Citation: Chiang, Ming-Feng, Ghassemlooy, Zabih, Ng, Wai Pang, Le Minh, Hoa and Abd El Aziz, Ahmad (2008) Multiple-Hop Routing in Ultrafast All-Optical Packet Switching Network Using Multiple PPM Routing Tables. In: 2008 IEEE International Conference on Communications. IEEE, Piscataway, NJ, pp. 5321-5325. ISBN 978-1-4244-2075-9

Published by: IEEE

URL: http://dx.doi.org/10.1109/ICC.2008.998 < http://dx.doi.org/10.1109/ICC.2008.998>

This version was downloaded from Northumbria Research Link: https://nrl.northumbria.ac.uk/id/eprint/7470/

Northumbria University has developed Northumbria Research Link (NRL) to enable users to access the University's research output. Copyright © and moral rights for items on NRL are retained by the individual author(s) and/or other copyright owners. Single copies of full items can be reproduced, displayed or performed, and given to third parties in any format or medium for personal research or study, educational, or not-for-profit purposes without prior permission or charge, provided the authors, title and full bibliographic details are given, as well as a hyperlink and/or URL to the original metadata page. The content must not be changed in any way. Full items must not be sold commercially in any format or medium without formal permission of the copyright holder. The full policy is available online: <a href="http://nrl.northumbria.ac.uk/policies.html">http://nrl.northumbria.ac.uk/policies.html</a>

This document may differ from the final, published version of the research and has been made available online in accordance with publisher policies. To read and/or cite from the published version of the research, please visit the publisher's website (a subscription may be required.)

# Multiple-Hop Routing in Ultrafast All-Optical Packet Switching Network Using Multiple PPM Routing Tables

M. F. Chiang, *Student Member*, *IEEE*, Z. Ghassemlooy, *Senior Member*, *IEEE*, Wai Pang Ng, *Member*, *IEEE*, H. Le Minh, *Student Member*, *IEEE*, and A. Abd El Aziz

Abstract-In this paper we present the modeling and simulation of multiple-hop routing in ultrafast all-optical packet switching based routers employing multiple pulse position modulation (PPM) formatted routing table. In multiple PPM routing tables (PPRTs) with reduced entry length, only a subset of the header address is converted into a PPM format in order to reduce the packet header recognition time. Packet header address correlation is carried out using only a single optical AND gate to improve the processing time. We show that the proposed offers unicast/multi-cast/broadcast scheme transmitting capabilities. The simulation results for the optical signal-to-noise ratio (OSNR) at each hop are presented and compared with the theoretical calculations.

*Index Terms*— Packet switching, pulse position modulation, address correlation, optical switch, OSNR.

# I. INTRODUCTION

Rapidly growing internet traffic volume necessitates the need for ultra-wideband networks. Photonic networks with alloptical packet routing are one such a network where packet header processing is entirely carried out in the optical domain [1, 2]. By replacing the slow optical/electrical/optical (O/E/O) conversion modules with optical processors a higher data throughput and lower power consumption can be achieved. Recently, the development of ultra high-speed Boolean logic gates [3-5] (such as AND, OR and XOR) with operating data rates higher than 40 Gbit/s have become the key enabling technology for realizing all-optical packet routing. At present packet header processing is carried out by sequentially correlating the incoming packet header address with each entry of a local routing table. For a small size network this is viable provided the routing table size is not too large. However, for a large size network with a routing table with hundreds or thousands of entries, the cost and complexity become a real issue. In addition a larger size routing table will lead to a conspicuous increase in packet header processing time at each router. In [6] it has been shown that packet header processing time (i.e. correlation time) can be considerably reduced by adopting PPM signal format for both the header address bits and the routing table entries. In this scheme the routing table entries contain multiple header address, thus considerably reducing its size.

In this paper we propose and investigate multiple PPM

based touting table with reduced entry length, where only a subset of the header address is converted into a PPM format. To avoid the low response-time of all-optical logic gates as in [6], a single bitwise AND gate is used to carry out header address correlation. The proposed scheme also offers multiple transmitting modes (unicast, multi-cast and broadcast) capability in an optical layer. In addition, we also investigate the multiple-hop routing in terms of the OSNR performance. The paper is organized as follows: after introduction, the principle of the multiple-hop OSNR are outlined in Section 2. In Section 3 simulation results and discussions are presented. Finally, Section 4 will conclude the paper.

#### II. ALL-OPTICAL ROUTER WITH MULTIPLE PULSE POSITION ROUTING TABLES

#### A. Optical Core Network

An all-optical network is composed of *K* edge nodes and *L* core nodes, see Fig. 1 with K = 32. Each edge node has its own specific address. Incoming low-speed electrical packets at a source edge node with the same destination (i.e. same target edge node) are combined and converted into a high speed optical packet. Optical packets are then routed to their destination via the core-network. When a packet arrives at proposed router (i.e. a core node), its header address is processed and correlated with all entries of the local multiple PPRTs in order to switch the packet to the correct output port. Depending on the network configuration and the local

Fig. 1. An optical core network with 32 edge nodes.

multiple PPRTs, the packet may propagate through a number of core routers before reaching its targeted edge node. In Figure 1, an illustration of a four-hop routing path is presented.

# B. Multiple Pulse Position Routing Tables

Assuming that the packet header has N bits address  $[a_{N-1}]$  $a_{N-2} \dots a_2 a_1 a_0$ ], where  $a_{N-1}$  is the most significant bit (MSB), the conventional routing table (RT) will have a maximum of  $2^{N}$  entries. In the worst case scenario i.e. checking all entries, the router will perform  $2^N$  N-bitwise correlations. Table I illustrates a routing table for N = 5, where 32 possible addresses are grouped into M groups based on the intended output ports. Here M = 3 representing the number of output ports. If a packet address match a pattern in a group, then it is switched to relevant output port, see the 1<sup>st</sup> and 2<sup>nd</sup> columns. The 3<sup>rd</sup> column shows the PPRT entries  $E_i$  (i = 1, 2, 3...) of length  $2^{N} \times T_{s}$  for each group of address bits, where  $T_{s}$  is the slot duration. The locations of the short pulses correspond to the decimal values of address patterns in  $i^{th}$  group. Note that the number of entries is reduced to 3 from 32 for the conventional RT. Further downsizing of PPRT could be accomplished by splitting each PPRT entry into sub-groups of  $E_{ii}$  (i = 1, 2, 3...and i = A, B, C..) with a reduced length of  $2^{N-X} \times T_s$ . N–X is the number of bits in the subset of packet header address, see the 4<sup>th</sup> column in Table I, and A, B, C and D represent address

TABLE I THE CONVERSION OF CONVENTIONAL RT TO SINGLE PPRT AND MULTIPLE PPRTS

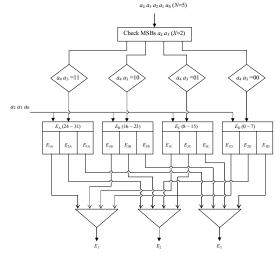

Fig. 2. A block diagram of multiple PPRT ( $E_{1A}$ ,  $E_{2A}$ ,  $E_{3A}$ , ...,  $E_{3D}$ ) for 5-bit packet header address.

patterns with decimal metrics in ranges of (24-31), (16-23), (8-15) and (0-7), respectively. E.g., for N = 5 the PPRT entry length is reduced from  $32 \times T_s$  to  $8 \times T_s$  when X = 2. The process is best explained with reference to Figure 2 (N = 5, X = 2). The two MSBs  $a_4$  and  $a_3$  of 5-bit header address are first checked to identify PPRT entry. Based on  $a_4$  and  $a_3$  pattern,  $E_{ij}$  is generated from the remaining  $a_2a_1a_0$  bits, which are then combined to generate  $E_1$ ,  $E_2$  and  $E_3$ .  $E_i$ s are then applied to the AND gates to carry out header address correlation [7].

# C. Node Architecture

The router based on the multiple PPRT with M-output ports

Fig. 3. A node structure with multiple PPRTs for 5-bits packet header address (N=5, X=2).

Fig. 4. Signal and ASE noise power propagation from the source edge node to the target edge node via H core nodes

is composed of a number of main modules based on symmetric Mach-Zehnder (SMZ) including a clock extraction module (CEM), a PPM address conversion module (PPM-ACM), a serial-to-parallel converter (SPC), a multiple PPRT generator, AND gates, all-optical switches (OS), an OS control module (OSC), and a number of 1×2 high extinction ratio optical switches (SW) [6], see Figure 3. The incoming packet P(t) is split and applied to the CEM, SPC and OS with the delays of 0,  $\tau_{CEM}$  (required time for clock extraction) and  $\tau_{tot}$  (total required time for PPM header processing), respectively. The extracted clock pulse c(t) with delays of 0,  $\tau_{AC}$  and  $\tau_{PPRT}$  is applied to the SPC [6-7], PPM-ACM and SW4, respectively. *N*-bit packet header addresses are extracted at the output of SPC. The PPM-ACM with the output defined by:

$$x_{PPM}(t) = x \left( t + \sum_{i=0}^{N-3} a_i \times 2^i \times T_s \right), \qquad a_i \in \{0, 1\}$$

(1)

where  $x(t) = \alpha c(t + \tau_{AC})$  and  $\alpha$  is the splitting factor.

SW4 is used to check  $a_4$ . for "1" or "0". If  $a_4$  is "1" then the first two groups  $E_A$  and  $E_B$  of multiple PPRTs are selected. Further selection of  $E_A$  and  $E_B$  is made using SW3. If  $a_3$  is "1" or "0" then  $E_A$  or  $E_B$  is selected, respectively. PPRTs with the same *i*<sup>th</sup> index are combined together and applied to the optical AND gates for address correlation. For example a header address of "11100" converted into a PPM format shows a pulse located at the 4<sup>th</sup> position (i.e. decimal value of "100") within an 8-slot PPM frame. The two MSBs ("11") are used to select one of the multiple PPRTs for correlation. Note that, only one multiple PPRT is used for correlation with an incoming packet header address. The outputs of the multiple PPRTs, see Figures 2 and 3, are given as [7]:

$$E_{k}\left(t\right) = E_{kA}\left(t\right) + E_{kB}\left(t\right) + E_{kC}\left(t\right) + E_{kD}\left(t\right)$$

(2)

Where each  $d_k$  element corresponds to the decimal values of header address bits (first (*N*-2)-bit) assigned to the node output  $k^{\text{th}}$  (k = 1, 2, ..., M).

The optical AND gates are based on the SMZ switches [8] with the logical outputs given by:

$$m_{k}(t) = x_{PPM}(t) \times E_{k}(t) = \begin{cases} 1 & if \quad d_{k} = \sum_{i=0}^{N-1} a_{i} \times 2^{i} \quad \forall k \\ 0 & if \quad d_{k} \neq \sum_{i=0}^{N-1} a_{i} \times 2^{i} \quad \forall k \end{cases},$$

$$k = 1, 2, ..., M \qquad d_{k} \in \left\{ 0 \sim (2^{N} - 1) \right\}$$

(3)

The matching pulse  $m_k(t)$  is subsequently applied to the OSC module to ensure that incoming packets  $P_{in}(t)$  are switched to the correct output ports. The signal at the output of switch is given as:

$$P_{out,k}(t) = P_{in}(t) \times m_{k}(t) = \\ = \begin{cases} G_{OS} \times (1 - 2\alpha) \times P_{in}(t + \tau_{tot}) & \text{if } m_{k}(t) = 1 \\ 0 & \text{if } m_{k}(t) = 0 \end{cases}$$

$$k = 1, 2, ..., M$$

where  $G_{OS}$  is the optical switch gain.

If more than one pulse is located at the same position in more than one (or all) PPRT entries, then the packet is broadcasted to multiple outputs (i.e. multicast) or all outputs (i.e. broadcast), respectively.

#### D. Multiple-hop OSNR

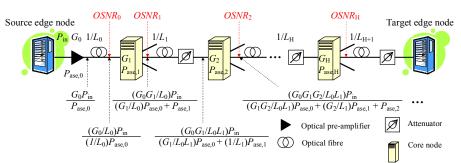

Figure 4 illustrate the path across the optical core network for packets with the average power  $P_{in}$  from source to the destination. The packet signal is first amplified and passed through a fiber span before being applied to a node.

The SOA unpolarized amplified spontaneous emission (ASE) noise is generally computed by [9]:

$$P_{ase,i} = 2n_{sp,i} h f_0 \left( G_{OS,i} - 1 \right) B_0 \quad , \quad i = 0, 1, \dots H$$

(5)

where  $n_{sp,i}$  and  $G_i$  are the spontaneous-emission factor and the gain, respectively, of the amplifier, where i = 0 represents the pre-amplifier and i > 0 denotes the SOA in OS modules.  $hf_0$  and  $B_0$  are the product of the Planck constant and the operating optical frequency, and the optical bandwidth of the system (i.e. filter optical bandwidth), respectively and *H* is the number of core nodes.

The OSNR at the target node is given as [6]:

(4)

Fig. 5. The VPI simulation setups for four-hop routing.

$$OSNR_{H} = \frac{\left(G_{H} \prod_{h=0}^{H-1} (G_{h}/L_{h})\right) P_{in}}{\sum_{h=0}^{H-1} \left(P_{ase,h} \prod_{k=h+1}^{H} (G_{k}/L_{k-1})\right) + P_{ase,H}}$$

(6)

where  $L_h$  is the total loss incurred between any two core nodes.

#### III. RESULTS AND DISCUSSIONS

#### A. Simulation Setup

The proposed router is simulated and its system performance is investigated by using the Virtual Photonics simulation package ( $VPI^{TM}$ ). Table II shows the main

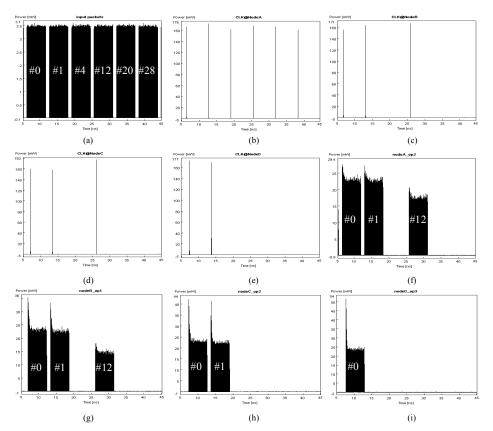

simulation parameters and Figure 5 depicts the simulation setup diagrams for multi-hop routing and an individual router. Six optical packets with addresses of #0, #1, #4, #12, #20 and #28 (decimal values) are transmitted sequentially at 80 Gb/s with 1 ns inter-packet guard interval. Each packet is composed of a 1-bit clock, a 5-bit address, and a 53-byte payload (ATM cell size) [10]. The input packet, with an average power of 3.5 mW, is amplified to compensate for the link loss (fibre attenuation and coupling losses). Each fibre span (link) comprises of 30 km single-mode fibre (SMF) and 5 km dispersion-compensating fibre (DCF). Note that PPRT for of the node A is given in Table I. Similarly, for nodes B, C, and D, the PPRT entries are  $E_1 \in \{0, 1, 2, 6, 10, 12, 15, 18, 23, 26,$  $29\}, E_2 \in \{0, 1, 3, 5, 9, 13, 16, 19, 21, 24, 28, 30\}$ , and  $E_3 \in \{0, 4, 7, 8, 11, 14, 17, 20, 22, 25, 27, 31\}$ , respectively.

Fig. 6. Time waveforms; (a) input packet at node A, (b)-(e) extracted clock at nodes A, B, C, and D, and (f)-(i) switched packets at nodes A – output2, B – output1, C – output2, and D – output3.

| TABLE II<br>Simulation Parameters             |                     |

|-----------------------------------------------|---------------------|

|                                               |                     |

| Data packet bit rate $-1/T_b$                 | 80 Gb/s             |

| Packet payload length                         | 53 bytes (424 bits) |

| Wavelength of data packet                     | 1554 nm             |

| Data & control pulse widths - FWHM            | 2 ps                |

| PPM slot duration $T_s(=T_b)$                 | 12.5 ps             |

| Average transmitted power Pin                 | 3.5 mW              |

| Average power of $C_k(t)$                     | 165 mW              |

| Optical bandwidth Bo                          | 300 GHz             |

| $G_h (h = 1, 2, \dots H)$                     | 20 dB               |

| Total loss of a hop $1/L_h$ ( $h = 1, 2, H$ ) | -7 dB               |

| Pre-amplifier gain G <sub>0</sub>             | 7 dB                |

| First span loss 1/L <sub>0</sub>              | -7 dB               |

| Pre-amplifier n <sub>sp</sub>                 | 2                   |

| SOA length                                    | 500 µm              |

| SOA $n_{sp}$                                  | 2                   |

| Inject current to SOA                         | 150 mA              |

| Splitting factor a                            | 0.4                 |

# B. Results and Discussions

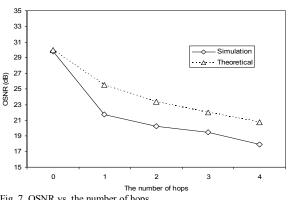

The time waveforms of six input packets and their switched versions at the outputs of four nodes (A, B, C and D) are illustrated in Figure 6. Figure 6(a) shows the input packets, whereas the extracted clock pulses observed at nodes A. B. C and D are presented in Figures 6(b)-(e), respectively, showing small intensity variations. At each hop, depending on the node's PPRT, the input packets are switched to their corresponding output ports. Packets with the target address of #0 are subsequently switched to the output ports of 2, 1, 2 and 3 of nodes A, B, C and D, respectively, as shown in Figures. 6(f), (g), (h) and (i). The intensity overshot observed at the start of switched packets is due to the gain saturation of the SOA within the OS when injected with a number of input packets, where the proceeding bits will experience a lower amplification gain. This can be minimized by decreasing the power of the input packet. Figure 7 depicts the theoretical and simulation for the OSNR against the number of hops. The disparity between the results is mainly due to the accumulated noise associated with matching pulses  $m_k(t)$  as in our simulation model. In the theoretical model, the accumulated noise due to the CEM and PPRT has not been considered. It is shown that  $\sim 2$  dB drop on the OSNR, after each hop is due to the accumulated ASE noise.

#### IV. CONCLUSION

In this paper, the node architecture, operation principle and the OSNR performance analysis of the proposed router with multiple pulse position routing tables were presented. In multiple PPRTs, the number and the length of entries are significantly shorter than the traditional RTs and PPM based RTs, respectively. As a result, the proposed router offers a faster processing time especially for packets with long address bits. The paper also presented simulation results to

Fig. 7. OSNR vs. the number of hops.

demonstrate the routing operation. It was shown that the OSNR decreases by ~2dB after each hop. The proposed router also is capable of operating in the unicast, multicast and broadcast transmission modes.

#### REFERENCES

- [1] D. J. Blumenthal, "Photonic packet switching and optical label swapping," Opt. Net. Mag., pp. 1-12, November/December 2001.

- Y. Chen, C. Qiao, and X. Yu, "Optical burst switching: a new area in [2] optical networking research," IEEE Network, vol. 18, no. 3, pp. 16-23, 2004.

- H. Dong, H. Sun, Q. Wang, N. K. Dutta, and J. Jaques, "All-optical [3] logic and operation at 80 Gb/s using semiconductor optical amplifier based on the Mach-Zehnder interferometer," Micro. & Opti. Tech. Lett., vol. 48, no. 8, pp. 1672-1675, 2006.

- J. Zhang, J. Wu, C. Feng, K. Xu, and J. Lin, "All-Optical Logic OR [4] Gate Exploiting Nonlinear Polarization Rotation in an SOA and Red-Shifted Sideband Filtering," IEEE Pho. Tech. Lett., vol. 19, no. 1, pp. 33-35, 2007.

- H. Sun, Q. Wang, H. Dong, Z. Chen, N. K. Dutta, J. Jaques, and A. B. [5] Piccirilli, "All-Optical Logic XOR Gate at 80 Gb/s Using SOA-MZI-DI," IEEE J. Quantum Electron., vol. 42, no. 8, pp. 747-751, 2006.

- H. Le-Minh, Z. Ghassemlooy, and W. P. Ng., "Multiple-Hop Routing Based on the Pulse-Position Modulation Header Processing Scheme in [6] All-Optical Ultrafast Packet Switching Network," Proc. GLOBECOM 2006, San Francisco, USA, Nov. 2006.

- M. F. Chiang, Z. Ghassemlooy, W. P. Ng, and H. Le-Minh., "Ultra-fast [7] all-optical packet-switched router with multiple pulse position routing tables," Proc. NOC 2007, Kista Stockholm, Sweden, pp. 571-578, 2007.

- S. Nakamura, K. Tajima, and Y. Sugimoto, "Experimental investigation [8] on high-speed switching characteristics of a novel symmetric Mach-Zehnder all-optical switch," Appl. Phys. Lett., vol. 65, pp. 283-285, 1994

- [9] G. P.Agrawal, Lightwave Technology: Telecommunication Systems. NewYork: Wiley-Interscience, 2005, ch. 6.

- L. Angrisani, A. Baccigalupi, and G. D'Angiolo, "A frame-level [10] measurement apparatus for performance testing of ATM equipment," Instrumentation and Measurement, IEEE Transactions, vol. 52, no. 1, pp. 20-26, 2003.