# A fully integrated 2.45 GHz 0.25 mu m CMOS power amplifier

Cijvat, Pieternella; Sjöland, Henrik

Published in:

Proceedings of the 10th IEEE International Conference on Electronics, Circuits and Systems, ICECS 2003.

DOI:

10.1109/ICECS.2003.1301701

2003

### Link to publication

Citation for published version (APA):

Cijvat, P., & Sjöland, H. (2003). A fully integrated 2.45 GHz 0.25 mu m CMOS power amplifier. In *Proceedings of the 10th IEEE International Conference on Electronics, Circuits and Systems, ICECS 2003.* (pp. 1094-1097). IEEE - Institute of Electrical and Electronics Engineers Inc.. https://doi.org/10.1109/ICECS.2003.1301701

Total number of authors:

#### General rights

Unless other specific re-use rights are stated the following general rights apply:

Copyright and moral rights for the publications made accessible in the public portal are retained by the authors and/or other copyright owners and it is a condition of accessing publications that users recognise and abide by the legal requirements associated with these rights.

- Users may download and print one copy of any publication from the public portal for the purpose of private study or research.

• You may not further distribute the material or use it for any profit-making activity or commercial gain

- You may freely distribute the URL identifying the publication in the public portal

Read more about Creative commons licenses: https://creativecommons.org/licenses/

Take down policy

If you believe that this document breaches copyright please contact us providing details, and we will remove access to the work immediately and investigate your claim.

# A FULLY INTEGRATED 2.45 GHz 0.25µm CMOS POWER AMPLIFIER

Ellie Cijvat and Henrik Sjöland

Dept. of Electroscience, Lund University, PO Box 118, 221 00 Lund, Sweden ellie.cijvat@es.lth.se, henrik.sjoland@es.lth.se +46-46 222 3020

#### ABSTRACT

A fully integrated differential class-AB power amplifier has been designed in a 0.25um CMOS technology. It is intended for medium output power ranges such as Bluetooth class I, and has an operating frequency of 2.45GHz. By using two parallel output stages that can be switched on or off, a high efficiency can be achieved for both high and low output power levels. The simulated maximum output power is 22.7 dBm, while the maximum poweradded efficiency is 22%.

#### I. INTRODUCTION

With the recent emergence of short-range communication standards such as Bluetooth, the research interest for highly integrated power amplifiers (PAs) has increased [1-13]. For frequencies up to several GHz and low to medium output power, CMOS may be an alternative to stand-alone power amplifiers, offering a higher level of integration in a relatively cheap technology, in exchange for less efficiency and a lower maximum output power.

In most communication systems transmitter output power control is required. In order to increase the battery lifetime, it is important to have a relatively high efficiency over the whole PA output power range, i.e. for both lower and higher output power, since the PA is more likely to operate at lower than higher output power.

For the Bluetooth standard the highest output power is 20 dBm (class I, [14]) which is feasible for CMOS implementation (see [1-13]). Moreover, a constant envelope modulation scheme is used, implying that linearity of the PA is not a critical issue for this standard.

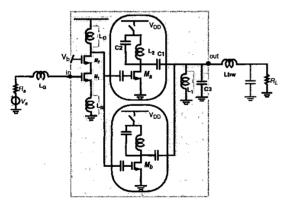

In this work a class-AB power amplifier is described that consists of two stages, with the output stage comprising two parallel blocks that may be switched on or off (see fig. 2). In this way the efficiency may be optimized for different output power settings. The output impedance transformation network is fully integrated.

The paper is structured as follows: First some PA theory is described, then the design itself is presented. Simulation results are shown in Section 4, and finally conclusions are presented.

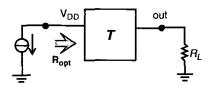

Figure 1. Principle of impedance transformation.

#### II. ANALYSIS

In fig. 1 a current source with impedance transformation network T is shown. This serves as a model for an ideal output stage, where the transistor operates as a controlled current source driving Ropt, the transformed load impedance R<sub>L</sub>. The maximum signal amplitude is V<sub>DD</sub>, and the ideal maximum output power is given by

$$P_{out, max, ideal} = \frac{V_{DD}^2}{2R_{opt}}$$

(1)

Thus, for a given  $V_{DD}$ ,  $R_{opt}$  determines  $P_{out,max}$  assuming a maximum voltage swing. For  $P_{out,max} = 22 \text{ dBm}$  and  $V_{\rm DD}$  = 3.3 V, the optimum load resistance  $R_{\rm opt}$  is equal to

The power added efficiency (PAE) is defined as

$$PAE = \frac{P_{out} - P_{in}}{P_{DC}} \tag{2}$$

where PDC is the power supplied by the battery, which is signal-dependent for most types of PAs. The PAE typically is maximum for an output power close to Pout,max and decreasing fast for lower output powers [5]. Therefore, for a high average efficiency, the PA may be designed to have different Pout,max by changing Ropt or V<sub>DD</sub>. In this work the former strategy is used.

#### Non-idealities

For high voltage swings the transistor will enter the linear region, and no longer behave as an ideal current source. This is commonly modeled with the knee voltage  $V_{knee}$ [15]. The output voltage swing is reduced to  $V_{DD}$  -  $V_{knee}$ , and the maximum output power may be written as  $P_{out, max} = \frac{\left(V_{DD} - V_{knee}\right)^2}{2R_{opt}}$  (3)

$$P_{out, max} = \frac{\left(V_{DD} - V_{knee}\right)^2}{2R_{out}} \tag{3}$$

0-7803-8163-7/03/\$17.00 © 2003 IEEE

**ICECS-2003**

Assuming an output stage with an integrated current-supplying inductor and a switch at  $V_{DD}$ , allowing the whole stage to be turned on or off, other non-idealities may be identified such as the series resistance of the inductor and the on-resistance of the supply switch, both reducing the bias voltage at the drain. Moreover, the finite output impedance of the transistor and the finite quality factor Q of the passives in the matching network will cause power loss. To compensate for these losses, a PA is generally designed for a higher  $P_{out,max}$  by reducing  $R_{opt}$  in Eq. 3.

#### III. DESIGN

A fully integrated 2.45 GHz PA was implemented in a 0.25um CMOS technology. In order to implement different output power settings and increase the average efficiency, two parallel output blocks were used (see fig. 2). Due to die size considerations the number of parallel blocks was limited to two.

The matching network was chosen so that a maximum output power of 22 dBm was achieved with both blocks on. When one stage is off, the matching network provides a higher  $R_{\rm opt}$  and thus a lower  $P_{\rm out,max}$ . In this way a relatively high average efficiency over the total PA output power range can be achieved.

**Figure 2.** Simplified single-ended schematic of the PA with two parallel output stages.

For the output stage no cascode transistors are used, since this would increase the knee voltage and thus decrease  $P_{out,max}$ . A switch in the signal path at the output would also have a negative impact on the output power and thus on the efficiency, and was therefore avoided as well.

The input capacitance of the output stage forms a large part of the total capacitance at the drain of  $M_2$  which is parallel to  $L_D$ , see fig. 2. When switching off one stage (by changing the gate bias to  $V_{DD}$  and opening the  $V_{DD}$  switch), the input capacitance will change significantly. In order to decrease the impact on input stage tuning, a rather small AC coupling capacitance is used between the input-and output stage.

By connecting the two output nodes as shown in fig. 2, the two parallel stages share  $L_1$ ,  $C_3$  and  $L_{bw}$ . Only  $C_1$ ,  $L_2$  and  $C_2$  are available to separately design  $R_{opt}$  for each stage. Moreover, due to numerous parasitic capacitances and size restrictions of integrated passives, the impedance transformation ratio cannot be varied over a wide range.

Generally when parallel output stages are used, power combining is implemented either through a transformer [3] or transmission lines [5]. In this design, however, the two stages are not isolated, meaning that the network of one stage has an impact on the impedance transformation of the other.

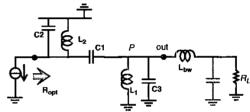

The matching network for one output stage may be drawn as shown in fig. 3. The two output stages are connected at point *P*.

**Figure 3.** The matching network for one stage, with the FET represented as an ideal current source.

When for example the lower stage in fig. 2 is switched off, FET  $M_b$  is brought into the linear region, thus providing a low impedance. Assuming this to be a short, one can see from fig. 2 that the equivalent capacitance parallel to  $C_3$  will be larger. This decreases the transformation ratio for the upper stage, thus increasing  $R_{\rm opt}$ , which is desirable when only one stage is on.

The two stages are unequal, having different FET widths and different capacitance and inductance values, and thus different transformation ratios and gains.

Comparing fig. 2 with fig. 3 one can see that the matching network includes parasitic capacitance at the drain of the FET (incorporated in  $C_2$ ), as well as the on-chip output node (in  $C_3$ ).

The 5M1P 0.25um CMOS technology offers thickmetal inductors with quality factors ranging from approximately 5 to 15. For  $L_2$  and  $L_S$  inductors provided by the manufacturer were used.  $L_D$  and  $L_1$  were designed using Fast Henry [16] and ASITIC [17]. For the integrated matching network, MOM (metal-oxide-metal) capacitors with highest quality (Q) factor available in this technology were used. The FETs  $M_a$  and  $M_b$  in fig. 2 do not have minimum gate length, but  $0.32\mu m$ , and have a higher breakdown voltage.

## IV. SIMULATION RESULTS

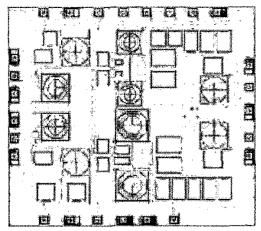

The above described design was simulated using SpectreRF, with BSIM3v3 models. Post-layout parasitics were taken into account. The layout is shown in fig. 4.

Figure 4. Plot of the PA layout.

A large area is occupied by the integrated passives, and a substantial area saving may be achieved by using differential inductors [18].

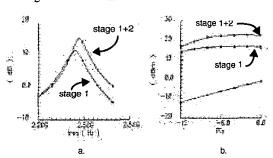

In fig. 5 some simulation results are shown.

Figure 5. Simulation results, a). Frequency response, b).

Pout as a function of P<sub>in</sub>.

The maximum PAE (22 %) is achieved for P<sub>out</sub> slightly below P<sub>out,max</sub> (which is about 23 dBm, see fig. 5.b). The center frequency for both cases (stage 1+2 and stage 1 only) is approximately 2.45GHz. The simulation results are summarized in table 1.

From table 2 a comparison can be made between this PA and previously published work. It can be seen that the PA presented in this work performs quite well, given the limitations of an on-chip matching network and class-AB. Moreover, the PA includes measures to improve the average efficiency.

### V. CONCLUSIONS

A 2.45 GHz power amplifier has been designed in a 0.25um CMOS technology. The PA is fully integrated, including output matching network. Simulations show

that an output power of 22.7 dBm may be achieved with a maximum PAE of 22%. The average efficiency has been improved by using two parallel output stages.

Table 1. Simulation results, summary

| PAE <sub>max</sub>              | 22%                  |                                 |

|---------------------------------|----------------------|---------------------------------|

| P <sub>out</sub> (differential) | 22.7 dBm             | @2.45GHz<br>@PAE <sub>max</sub> |

| power gain                      | 28 dB                | @PAE <sub>max</sub>             |

| total die area                  | 6.25 mm <sup>2</sup> | including pads                  |

| Pout (stage1 only)              | 17.2 dBm             | PAE=15.8%                       |

| Pout (stage 2 only)             | 12.4 dBm             | PAE=6.1%                        |

#### **ACKNOWLEDGEMENTS**

The authors are grateful to Niklas Troedsson, MSc (Dept. of Electroscience, Lund University) for help with integrated inductor design and modeling.

#### REFERENCES

- M. Rofougaran, A. Rofougaran, C. Ølgaard, and A.A. Abidi, "A 900 MHz CMOS RF Power Amplifier with Programmable Output", 1994 Symposium on VLSI Circuits Digest, pp. 133-134, June 1994.

- A. Giry, J-M. Fournier, and M. Pons, "A 1.9GHz Low Voltage CMOS Power Amplifier for Medium Power RF Applications", Proceedings of 2000 IEEE Radio frequency Integrated Circuits (RFIC) Symposium, pp. 121-124, May 2000.

- I. Aoki, S.D. Kee, D.B. Rutledge, and A. Hajimiri, "Fully Integrated CMOS Power Amplifier Design using the Distributed Active-Transformer Architecture", IEEE Journal of Solid-State Circuits, Vol. 37, no.3, March 2002.

- S. Luo and T. Sowlati, "A monolithic Si PCS-CDMA Power Amplifier with 30% PAE at 1.9GHz using a Novel Biasing Scheme", IEEE Transactions on Microwave Theory and Techniques, Vol. 49, no. 9, September 2001.

- A. Shirvani, D.K. Su, and B.A. Wooley, "A CMOS RF Power Amplifier with Parallel Amplification for Efficient Power Control", *IEEE Journal of Solid-*State Circuits, Vol. 37, no. 6, June 2002.

- T.C. Kuo and B.B. Lusignan, "A 1.5W Class-F RF Power Amplifier in 0.2um CMOS Technology", 2001 International Solid-State Circuits Conference (ISSCC) Digest, pp. 154-155, February 2001.

- C. Fallesen and P. Asbeck, "A 1W 0.35um CMOS Power Amplifier for GSM-1800with 45% PAE", 2001 International Solid-State Circuits Conference (ISSCC) Digest, pp. 158-159, February 2001.

- Y.J.E. Chen, M. Hamai, D. Heo, A. Sutono, S. Yoo, and J. Laskar, "RF Power Amplifier Integration in CMOS Technology", 2000 IEEE Microwave Symposium (MTT-S) Digest, pp. 545-548, May 2001.

- C.C. Hsiao, C-W. Kuo, and Y-J. Chan, "Integrated CMOS Power Amplifier and Down-Converter for 2.4GHz Bluetooth Applications", Proceedings of the 2001 IEEE Radio and Wireless Conference (RAW-CON), pp. 29-32, August 2001.

- T. Sowlati and D. Leenaerts, "A 2.4GHz 0.18um CMOS Self-Biased Cascode Power Amplifier with 23 dBm Output Power", 2002 International Solid-State Circuits Conference (ISSCC) Digest, pp. 294-295, February 2002.

- K. Mertens and M.S.J. Steyaert, "A 700MHz 1-W Fully Differential CMOS Class-E Power Amplifier", IEEE Journal of Solid-State Circuits, Vol. 37, no. 2, February 2002.

- K. Yamamoto, T. Heima, A. Furukawa, M. Ono, Y. Hashizume, H. Komurasaki, S. Maeda, H. Sato, and N. Kato, "A 2.4GHz-Band 1.8-V Operation Single-Chip Si-CMOS T/R-MMIC Front-End with a Low Insertion Loss Switch", *IEEE Journal of Solid-State Circuits*, Vol. 36, no. 8, august 2001.

- R. Gupta, B.M. Ballweber, and D.J. Allstot, "Design and Optimization of CMOS RF Power Amplifiers", *IEEE Journal of Solid-State Circuits*, Vol. 36 no. 2, February 2001.

- The Bluetooth Special Interest Group, "Specification of the Bluetooth System", Vol. 1, version 1.1. www.bluetooth.com. 2001.

- S.C. Cripps, "RF Power Amplifiers for Wireless Communication". Artech House, Norwood, MA, USA, 1999.

- M. Kamon, M.J. Tsuk, and J. White, "FastHenry: A Multipole-Accelerated 3-D Inductance Extraction Program", Proc. of the 30th ASM/IEEE Design Automation Conference (DAC), pp. 678-683, 1993.

- A.M. Niknejad, "Modeling of Passive Elements with ASITIC", Proc. of the 2002 IEEE Radio Frequency Integrated Circuits (RFIC) Symposium, pp. 303-306, May 2002.

- M. Danesh and J.R. Long, "Differentially Driven Symmetric Microstrip Inductors", *IEEE Trans. on Microwave Theory and Techniques*, Vol. 50, no. 1, January 2002.

Table 2. Comparison of medium power PAs

|              | Pout (dBm)               | frequency<br>(GHz) | efficiency (max)         | technology       | output<br>matching          | power<br>control     | class |

|--------------|--------------------------|--------------------|--------------------------|------------------|-----------------------------|----------------------|-------|

| [1]          | 15 (@P <sub>-1dB</sub> ) | 0.9                | <30% (η)                 | 1um CMOS         | off-chip                    | steps, 5dB           | С     |

| [2]          | 23.5 (max)               | 1.9                | 35% (PAE)                | 0.35 um (Bi)CMOS | off-chip                    | -                    | AB    |

| [3]          | 33.4 (@max PAE)          | 2.4                | 31% (PAE)                | 0.35um (Bi)CMOS  | on-chip                     | -                    | E/F3  |

| [4]          | 28.2                     | 1.9                | 30% (PAE)                | 30GHz BiCMOS     | off-chip                    | -                    | AB    |

| [5]          | 24.8 (max)               | 1.4                | 49% (PAE)                | 0.25um CMOS      | off-chip<br>(transm. lines) | 3 parallel<br>stages | F     |

| [6]          | 31.8 (max)               | 0.9                | 43% (PAE)                | 0.2um CMOS       | off-chip                    | -                    | F     |

| [7]          | 30 (@max. PAE)           | 1.8                | 45% (PAE)                | 0.35um CMOS      | off-chip                    | -                    | AB    |

| [8]          | 20 (max)                 | 1.9                | 16% (η)                  | 0.8um CMOS       | on-chip                     | -                    | F?    |

| [8]          | 22 (max)                 | 2.4                | 44% (η)                  | 0.25um CMOS      | off-chip                    | -                    | F?    |

| [9]          | 17.5 (max)               | 2.4                | 16.4% (PAE)              | 0.35um CMOS      | partly on-chip              | -                    | Α     |

| [10]         | 23 (max)                 | 2.4                | 42% (PAE)                | 0.18um CMOS      | off-chip                    | -                    | AB    |

| [11]         | 30 (max)                 | 0.7                | 62% (PAE max)            | 0.35um CMOS      | partly on-chip              | -                    | E     |

| [12]         | 9 (@P <sub>-5dB</sub> )  | 2.4                | 16% (P <sub>-5dB</sub> ) | 0.18um CMOS      | partly on-chip              | -                    | AB?   |

| [13]         | 18.6 (@max PAE)          | 0.9                | 30% (PAE max)            | 0.6um CMOS       | on-chip                     | -                    | С     |

| this<br>work | 22.7 (@max PAE)          | 2.45               | 22% (PAE max)            | 0.25um CMOS      | on-chip                     | 2 settings           | AB    |