# 379 N 81 NO. 7176

# ANALYSIS OF MEMORY INTERFERENCE IN BUFFERED MULTI-PROCESSOR SYSTEMS IN PRESENCE OF HOT SPOTS AND FAVORITE MEMORIES

# THESIS

Presented to the Graduate Council of the University of North Texas in Partial Fulfilment of the Requirements

For the Degree of

# MASTER OF SCIENCE

By

Sanjoy Kumar Sen, B.E. Denton, Texas August, 1995

# 379 N 81 NO. 7176

# ANALYSIS OF MEMORY INTERFERENCE IN BUFFERED MULTI-PROCESSOR SYSTEMS IN PRESENCE OF HOT SPOTS AND FAVORITE MEMORIES

# THESIS

Presented to the Graduate Council of the University of North Texas in Partial Fulfilment of the Requirements

For the Degree of

# MASTER OF SCIENCE

By

Sanjoy Kumar Sen, B.E. Denton, Texas August, 1995 Sen, Sanjoy Kumar, <u>Analysis of Memory Interference in Buffered Multiprocessor</u> Systems in Presence of Hot Spots and Favorite Memories. Master of Science (Computer Science), August 1995, 19 tables, 16 illustrations, bibliography.

In this thesis, a discrete Markov chain model for analyzing memory interference in multiprocessors, is presented. Each memory module is either hot or favorite or neither of these two. Since the state space of such a Markov model for an  $N \times M$  system, where N and M are respectively the number of processors and memory modules, becomes exorbitant for large N and M, we restrict our analytical solutions to  $2 \times M$ and  $N \times 2$  systems. The general case is analyzed using simulation. In all cases, the effective memory bandwidth, mean memory-queue-length and mean-waiting-time for a memory request are derived. A heuristic is presented, using a probabilistic model, which finds the number of hot modules beyond which there is hardly any bandwidth change.

#### ACKNOWLEDGEMENTS

I am immensely grateful to my advisor, Dr. Sajal K. Das, without whose unceasing support, encouragement and guidance this thesis could not have been written. The several months of fruitful discussions I had with him, helped me get a better understanding of the subject and also imparted the spirit of perseverance. My association with him had been a very rewarding experience which I will always treasure.

I am grateful to the members of my supervising committee, Dr. Weiping Shi and Dr. Farhad Sharokhi for their review and helpful suggestions. I am indebted to the Chair of the Department of Computer Sciences, Dr. Ken Godwin, as well as my advisor, Dr. Sajal K. Das, for the financial support during the period of my studies and for providing all neccessary computing facilities. Special thanks are due to Mr. Falguni Sarkar for his invaluable suggestions during the course of this work. I also thank all my friends in UNT for the wonderful time I had.

Finally, I express my deepest gratitude to my father, mother and sister, without whose endless affection, support and inspiration from a long distance, I could not imagine completing this work.

# TABLE OF CONTENTS

| 1 | INT | RODUCTION                                                                    | 1              |

|---|-----|------------------------------------------------------------------------------|----------------|

|   | 1.1 | Non-Uniform Memory Access Patterns                                           | <b>3</b>       |

|   | 1.2 | Contribution of this Thesis                                                  | $\overline{5}$ |

|   | 1.3 | Chapter summary                                                              | 6              |

| 2 | PRE | EVIOUS WORK                                                                  | 7              |

|   | 2.1 | Multistage Interconnection Networks                                          | 7              |

|   |     | 2.1.1 Unbuffered MINs                                                        | 8              |

|   |     | 2.1.2 Buffered MINs                                                          | 12             |

|   | 2.2 | Multiple Bus Interconnection Network                                         | 19             |

|   | 2.3 | Conclusion                                                                   | 31             |

| 3 | MA  | RKOV MODEL FOR MULTIPROCESSORS WITH HOT SPOTS AND                            |                |

|   | FAV | ORITE MEMORIES                                                               | 32             |

|   | 3.1 | $2 	imes M$ system, one hot spot without any Favorite memory $\ldots \ldots$ | 34             |

|   |     | 3.1.1 Bandwidth Analysis                                                     | 35             |

|   |     | 3.1.2 Mean Queue Length and Waiting Time                                     | 39             |

|   | 3.2 | $2 \times M$ system, K hot spots and no favorite memory                      | 40             |

|   | 3.3 | 2 	imes M system, one hot spot with favorite memory                          | 47             |

|   | 3.4 | N	imes 2 system, one hot and one non-hot non-favorite memory                 | 51             |

|   |     | 3.4.1 Solutions of the state transition equations                            | 53             |

|   | 3.5 | Conclusion                                                                   | 55             |

| 4 | SIM | ULATION OF PROCESSOR MEMORY INTERCONNECTION SYS-                             |                |

|   | TEI | M                                                                            | 57             |

|   | 4.1 | Simulation Environment                                                       | 57             |

|    | 4.2        | Simulation of $N \times M$ system with K hot and $M - K$ non-favorite    |    |

|----|------------|--------------------------------------------------------------------------|----|

|    |            | memories                                                                 | 58 |

|    | 4.3        | Simulation of $N \times M$ system with K hot spots and favorite memories | 64 |

|    | 4.4        | Conclusion                                                               | 66 |

| _  |            |                                                                          |    |

| 5  | PRO        | BABILISTIC MODEL WITH ONLY HOT SPOTS                                     | 68 |

|    | 5.1        | Conclusion                                                               | 73 |

| 0  | 0.01       |                                                                          |    |

| 6  | COI        | NCLUSIONS                                                                | 74 |

| RI | REFERENCES |                                                                          |    |

,

۰. · · ·

# LIST OF TABLES

| 3.1  | State Transition Matrix A of $2 \times M$ system $\ldots \ldots \ldots$                                                                               | 36 |

|------|-------------------------------------------------------------------------------------------------------------------------------------------------------|----|

| 3.2  | Memory bandwidth with varying $\lambda$ and $\mu$ for $M = 10$ and                                                                                    |    |

|      | m = 0.75                                                                                                                                              | 39 |

| 3.3  | State Transition Matrix of $2 \times M$ system with K hot spots                                                                                       | 42 |

| 3.4  | Memory bandwidth with varying $\lambda$ and $\mu$ for $K = 1, M = 10$                                                                                 |    |

|      | and $m = 0.75$ .                                                                                                                                      | 44 |

| 3.5  | Memory bandwidth with varying $\lambda$ and $\mu$ for $k = 5, M = 10$                                                                                 |    |

|      | and $m = 0.75$                                                                                                                                        | 45 |

| 3.6  | Memory bandwidth with varying $\lambda$ and $\mu$ for $k = 5, M = 10$                                                                                 |    |

|      | and $m = 0.95$                                                                                                                                        | 45 |

| 3.7  | State Transition Matrix of $2 \times M$ system with hot spot and                                                                                      |    |

|      | favorite memories                                                                                                                                     | 48 |

| 3.8  | Memory bandwidth for various $\lambda$ and $\mu$ , $M = 10, m = 0.75$ and                                                                             |    |

|      | $\alpha = 0.6. \qquad \dots \qquad $          | 49 |

| 3.9  | Memory bandwidth for various $\alpha$ and $\mu$ , $M = 10, m = 0.75$ and                                                                              |    |

|      | $\alpha = 0.9. \qquad \ldots \qquad $ | 50 |

| 3.10 | Memory bandwidths with various values of $m$ and $N$ for the                                                                                          |    |

|      | $N \times 2$ system                                                                                                                                   | 55 |

| 4.1  | Memory bandwidth for $K = 1, M = 10, N = 2$ and $m = 0.75$ .                                                                                          | 58 |

| 4.2  |                                                                                                                                                       |    |

| 4.3  |                                                                                                                                                       | 59 |

|      | Memory bandwidth for $K = 20, M = 50, N = 30$ and $m = 0.75$ .                                                                                        | 59 |

| 4.4  | Memory bandwidth for $k = 75, M = 100, N = 60$ and $m = 0.75$ .                                                                                       | 60 |

| 4.5  | Memory bandwidths for various values of K, with $\lambda = \mu = 1$ ,                                                                                 |    |

|      | using simulation                                                                                                                                      | 62 |

| 4.6 | Memory bandwidth for various $\lambda$ and $\mu$ , $k = 1, M = 10, N =$  |    |

|-----|--------------------------------------------------------------------------|----|

|     | $2, m = 0.75$ and $\alpha = 0.6$ .                                       | 65 |

| 4.7 | Memory bandwidth for various $\lambda$ and $\mu$ , $K = 1, M = 10, N =$  |    |

|     | $2, m = 0.75$ and $\alpha = 0.9$ .                                       | 65 |

| 4.8 | Memory bandwidth for various $\lambda$ and $\mu$ , $K = 20, M = 50, N =$ |    |

|     | $30, m = 0.75$ and $\alpha = 0.9$ .                                      | 66 |

| 5.1 | Memory bandwidths with various values of K, with $\lambda = \mu = 1$ ,   |    |

|     | using probabilistic model                                                | 71 |

# LIST OF FIGURES

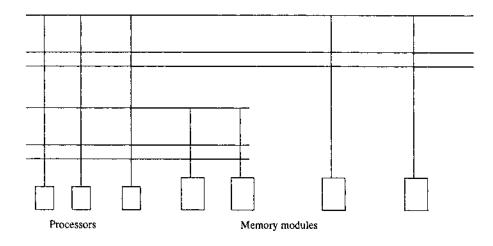

| 1.1         | Logical diagram of Processor Memory Interconnection                                    | 1  |

|-------------|----------------------------------------------------------------------------------------|----|

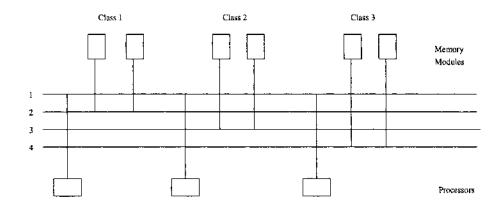

| 2.1         | Examples of MIN and MBINs                                                              | 7  |

| 2.2         | Examples of Multiple Bus Interconnection Networks                                      | 21 |

| 2.3         | Example of Partial Bus Network with three classes                                      | 28 |

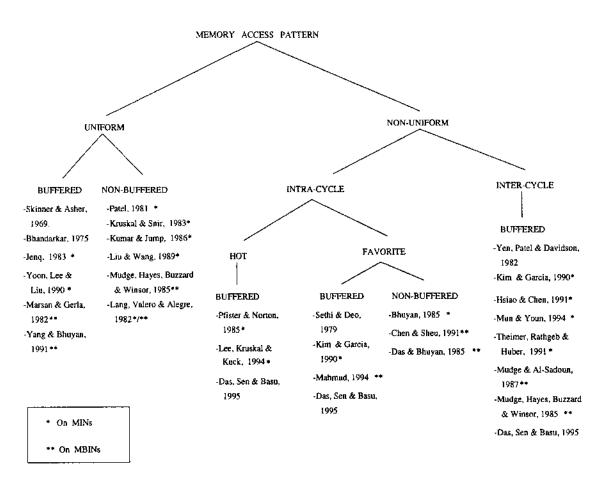

| 2.4         | A taxonomy of related work on memory references                                        | 31 |

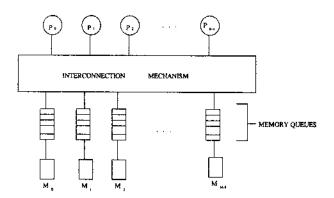

| 3.1         | A Buffered memory system                                                               | 32 |

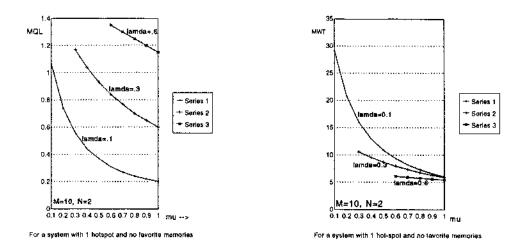

| 3.2         | Variation of mean queue length and mean waiting time with request                      |    |

|             | service rate                                                                           | 41 |

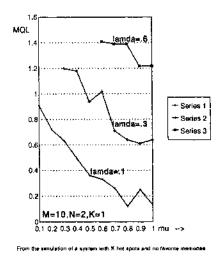

| 3.3         | Variation of mean memory-queue length with request service rate $\$ .                  | 46 |

| <b>3</b> .4 | Variation of mean mean waiting time with request service rate                          | 50 |

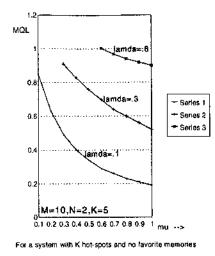

| 3.5         | Markov chain model for $N \times 2$ system $\ldots \ldots \ldots \ldots \ldots \ldots$ | 52 |

| 3.6         | Mean queue length with probabilty of requesting hot modules                            | 55 |

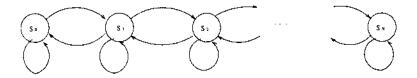

| 4.l         | Variation of mean memory-queue length with request service rate $~$                    | 60 |

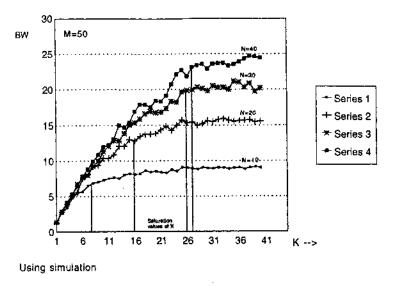

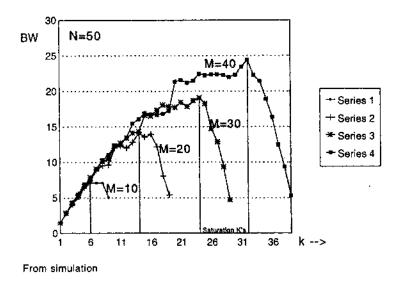

| 4.2         | Variation of memory bandwidth with number of hot modules                               | 63 |

| 4.3         | Variation of memory bandwidth with number of hot modules                               | 63 |

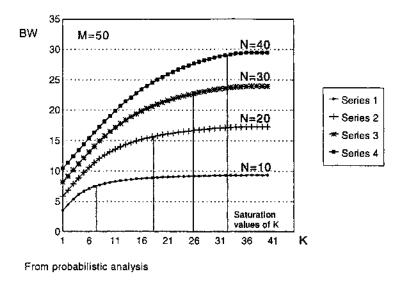

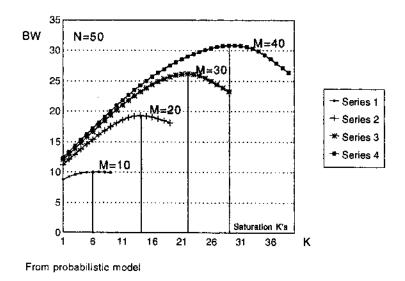

| 5.1         | Variation of memory bandwidth with number of hot modules                               | 72 |

| 5.2         | Variation of memory bandwidth with number of hot modules                               | 72 |

## CHAPTER 1

#### INTRODUCTION

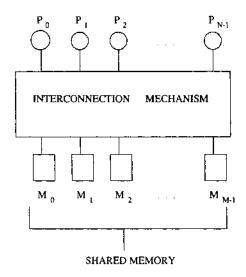

Processor memory interconnection in shared memory multiprocessor systems plays a vital role in characterizing the system performance. A shared memory multiprocessor consists of a set of processors  $\{P_0, P_1, \dots P_{N-1}\}$  and a set of memory modules  $\{M_0, M_1, \dots M_{M-1}\}$ . The processor- memory communications are established either through a set of switches (e.g. crossbar or multistage interconnection network) or through global shared (multi) bus. In this work, both types of connections between the processors and memories will be called under the generic name interconnection network. A logical diagram of such a shared memory system is shown in Figure 1.1.

Figure 1.1: Logical diagram of Processor Memory Interconnection

The interconnection mechanism should allow efficient resource sharing among the processors. Conflict arises when more than one processor attempt to access memory modules using the same path or switching module in the network. The primary goal of any interconnection network is to minimize this conflict, leading to higher acceptance rate of memory requests by the processors. The effective memory *bandwidth*, BW,

is defined as the average number of busy memory modules in each memory cycle. Of course, the BW is also dependent on the request rate of the processors. Other performance indices of such a network include processor and memory utilization, expected queue length, fault tolerence, cost etc.

At one end of the bandwidth spectrum are the single *shared bus* systems. Although they provide extremely low transfer rates and minimal fault tolerence, they are very cost effective. However the scalability of such a system is poor in the sense that the number of processors that can be supported on a single bus is rather limited without degrading the performance. At the other extreme are the *cross-bar* systems which provide complete connection among processor-memory pairs. But the total cost of the cross-bar switches increases rapidly as the number of processor and/or memory modules increase. *Multistage interconnection networks* (MINs) have been developed as a resort to trade-off between the high BW and fault-tolerence of crossbar switches and the low cost of single bus systems. MINs provide a unique path between each processor-memory pair, reducing the number of processors and memories. Also a natural extension of the single bus system, with the same goal, is the *multiple bus interconnection networks*, called MBIN. For details on MBINs, refer to [19,20,21,22].

In a processor-memory system, contention may occur either in the interconnection mechanism (e.g. bus or MIN switches) itself or while accessing an actual memory module. By some arbitration policy (usually random), one of the conflicting requests is granted, while others are either rejected (the case of a *non-buffered* system), or queued for future processing (the case of a *buffered* system).

In the past two decades, the performance of processor-memory interconnections has been studied widely using various analytical models, some of which are *exact* [1,2,4,5,7] while others are *approximate* [3,8,9]. An exact analysis assumes that a rejected memory request from a processor is not discarded but is queued up until it is serviced by the requested memory module (buffered systems). The exact models use Petri nets [25], Markov chains [1,2], queuing networks [22] and so on. An approximate analysis, on the other hand, assumes that the rejected requests are discarded (non-buffered systems). This suggests using probabilistic approach to analyze the performance of the system [3,8].

The memory reference patterns of the processors can be either uniform or nonuniform. Memory reference pattern is said to be uniform if all the processors have the same probability of accessing any memory module. This is a valid assumption if address interleaving on the low order address bits are used. Without the address interleaving, however, the memory reference pattern will be non-uniform in most cases and will depend on the locality of reference.

#### 1.1. Non-Uniform Memory Access Patterns

The non-uniform memory access patterns can be either intra-cycle or inter-cycle. In the *intra-cycle* case, the distribution of the memory requests by the processors in a particular memory cycle is not uniform. There are four types of intra-class nonuniformity. In the first type, each processor may have a *favorite* memory module(s) which it accesses more frequently than the others [8]. This is quite logical considering the spatial locality principle of memory references where address space is sequential in each memory module.

In the second type, all the processors might access a particular memory module or a class of memory modules more frequently than the others. This might capture the effect of the processors sharing a common variable or a sysnchronization primitive (e.g. barrier synchronization). The particular memory module or the class of memory modules accessed more frequently is called *hot spot(s)* [16].

The third type of non-uniformity capturing the temporal locality principle of memory reference is defined as follows [2]. If the *nth* request of a processor is for memory module  $M_i$ , then the (n + 1)th request will be for module  $M_i$  with probability  $\alpha$  and for module  $M_j$  (where  $j \neq i$ ) with probability  $\frac{(1-\alpha)}{(M-1)}$ , where M is the total number of memory modules in the system. This assumes that  $\alpha > \frac{1}{M}$ , i.e. the probability that the next memory request of a processor is to the same memory module is greater than the probability in case of uniform memory reference pattern and also greater than the probability that the next reference is to a different memory module. If  $\alpha = \frac{1}{M}$ , the model reduces to the uniform reference model as a special case.

A fourth type of non-uniformity, also called *spatial* non-uniformity, is defined when the events that a particular memory module has at least one request are not independent [20].

The *inter-cycle* non-uniformity of memory references occurs when the event that a processor requests a particular memory module is dependent on whether the same processor's memory request is satisfied in the previous cycle. If a processor's request to a particular memory module cannot be satisfied in the current memory cycle due to the fact that the particular module is already busy, then in the next cycle, the same request might be placed to the same memory module or it might be randomly distributed to any of the other available modules. In the former case we have to associate a buffer with each memory module [1,2,4], to store the rejected requests for the next cycle, or there should be some mechanism (sort of 'feedback') to remember the destinations of the rejected memory references and again place it to the same destination in the next cycle [7].

If a memory module is classified as any one of the following types, H (hot), NH (non-hot), F (favorite) and NF (non-favorite), then the various combinations of memory modules is given as  $\{H, NH\} \times \{F, NF\}$ , which when expanded gives the following set of combinations of memory modules:  $\{(H, F), (H, NF), (NH, F), (NH, NF)\}$ .

The system where the memory modules are of the type (NH, NF) is analyzed in [1,4,5,6]. The concept of hot memory modules is introduced by Pfister and Norton [16]. In the context of analyzing contention in the multistage interconnection network, they proposed a scheme to avoid tree saturation, a phenomenon occurring in systems consisting of modules of type (H, NF). The analysis of systems consisting of modules

of type (NH, F) is carried out in [2,8]. In this work, we will deal with the problem of contention in accessing the shared memory modules, after the request has successfully passed through the interconnection mechanism. See the taxonomy given at the end of Chapter 2 for a glimpse of the related work in this area.

#### 1.2. Contribution of this Thesis

We carry out an analysis of an  $N \times M$  system with memory modules of type (H, NF)and (H, F) in a unified manner. Our unified scheme gives analytic solutions for bandwidth, mean queue length and mean waiting time for a memory request by the processors, for  $2 \times M$  and  $N \times 2$  system. As our model is restricted to systems having only 2 processors in all cases excepting the  $N \times 2$  system, the number of hot memory modules is limited to 1 in the analysis of systems with memory modules of type (H, F). For  $N \times 2$  system, one (H, NF) and another (NH, NF) type memory modules are considered. The reason for not choosing favorite memory in the later case is that, we are not able to distinguish between a hot and a favorite memory in case of only one memory module. The general case of  $N \times M$  system is analyzed using simulation studies, and the results are compared to the analytic solutions in the special cases.

Since it is expected that memory requests will accumulate in the queue of a hot memory module leading to deterioration of memory bandwidth, multiple hot-spots (K many) in the multiprocessor system should lead to a definite improvement in the system performance. But it is also shown that the bandwidth (BW) of the system stops improving significantly if the number of hot memory modules is increased beyond a certain value, less than min(N, M). In this work, we also present a heuristic to find this upper bound on K. The heuristic, based on an approximate probabilistic model, actually estimates an asymptotic bandwidth of the system.

#### 1.3. Chapter summary

Chapter 2 gives the glimpses of some of the existing work in this area. Our Markov model for buffered memory multiprocessors is described in Chapter 3. A step by step approach is taken for the development of the model, and each step is precisely described in various subsections. Chapter 4 presents various simulation results for the general case of the multiprocessor architecture. An approximate probabilistic analysis for the general case of the proposed model is given in Chapter 5, which leads to a heuristic for estimating the saturation value of K beyond which the system bandwidth does not show any significant improvement. Chapter 6 finally concludes this thesis.

### CHAPTER 2

#### PREVIOUS WORK

Processor memory interconnection networks can be broadly classified into two types depending on the connection mechanism. In one type of networks commonly known as Multistage Interconnection Networks, the interconnection is through a set of switches. In the other type, the interconnection mechanism is by a single or multiple shared bus. We discuss some of the important previous works in both types of interconnection networks.

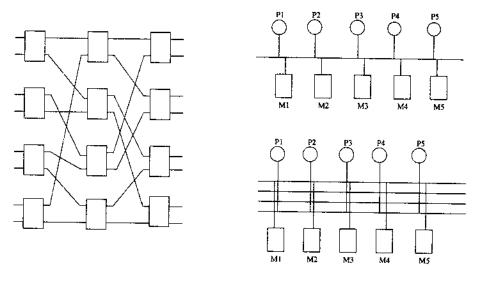

Example of MBINs : Single bus and Multiple bus

Figure 2.1: Examples of MIN and MBINs

# 2.1. Multistage Interconnection Networks

In this section we discuss multistage interconnection networks, popularly called MINs. A set of processors are logically connected to a set of memory modules through an interconnection network which is composed of high-speed switches. This is unlike general interconnection networks studied for distributed systems, which have physical processor(s) sitting in each node. Each switching module may or may not have buffers to store the memory requests rejected during the current cycle. In the former case the memory requests in one cycle is independent of the requests in the previous cycle, while it is not so in case of buffered models of MIN. This latter model is, of course, more realistic. Again, within each memory cycle, the requests made by the processors may be independent which we call *uniform reference* model, or each processor may have a locality of reference which makes the memory requests non-uniform.

### 2.1.1. Unbuffered MINs

#### Uniform Reference models

Patel [3] presented a new form of processor-memory interconnection network called Delta network. A Delta network is an  $a^n \times b^n$  switching network with n stages consisting of  $a \times b$  cross-bar modules. The link pattern between the stages is such that there is a unique path of constant length from any source to any destination. A  $2 \times 2$  crossbar switch has the capability of connecting the input I to either of the two outputs labelled 0 and 1 respectively, depending on the value of some control bit in I. Also the switch has the capability to arbitrate between two conflicting inputs. The network consists in construction of demultiplexer trees (also called fan-in trees) with every memory module as its root and the processors as leaves. Every new tree may use some of the already existing links. The path between a processor and a memory module is digit controlled such that a cross- bar module connects an input to one of its b outputs depending on a single base-b digit taken from the destination address. Patel computed the total number of cross-bar modules (of size  $a \times b$ ) required in an  $a^n \times b^n$  delta network as  $a^n - b^n/a - b$  if  $a \neq b$ , or  $nb^{n-1}$  if a = b. Patel carried out analysis of bandwidth and memory request acceptance probability of a processor, in case of a crossbar system and a delta network of the same dimension. Assuming a processor request generating probability of m and that the blocked requests are

ignored, Patel[3] came up with a closed form expression for the expected bandwidth, BW in a cross-bar of size  $M \times N$

$$BW = N \left[ 1 - N \left( 1 - \frac{m}{N} \right)^{M} \right]$$

where M = number of processors,

N = number of memory modules.

A simple explanation for the model is that  $(1 - \frac{m}{N})^M$  represents the probability that none of the M processors requests for a particular memory module in a particular memory cycle. So probability that there is at least one memory request for that memory module is obtained by subtracting this from 1. Multiplying by the number of memory modules, N, gives the expected number of busy memory modules per cycle, assuming the memory requests are uniformly distributed over all the memory modules in a cycle.

Let the probability of acceptance of a memory request  $P_A$ , be defined as the ratio of the expected bandwidth to the expected number of requests generated per cycle. Then

$$P_A = \frac{BW}{mM} = \frac{N}{mM} - \frac{N}{mM} \left(1 - \frac{m}{N}\right)^M$$

Applying the previous result for a  $M \times N$  crossbar to any  $a \times b$  crossbar module of the Delta network, the expected number of requests that it passes per cycle is obtained by setting M = a and N = b. Thus  $BW = b - b \left(1 - \frac{m}{b}\right)^a$  Dividing the above expression by the number of output lines in any of the  $a \times b$  modules yields the rate of requests on any of the *b* output lines as  $1 - \left(1 - \frac{m}{b}\right)^a$  If  $m_i$  is defined as the request rate on an output line in stage *i*, then the BW of the Delta network is given as  $BW = b^n m_n$  where  $m_i = 1 - \left(1 - \frac{m_{i-1}}{b}\right)^a$  and  $m_0 = m$ . Thus

$$P_A = \frac{b^n m_n}{a_n m}$$

Since Patel could not find a closed form solution for the BW of a Delta network, he could only graphically compare the two parameters BW and  $P_A$  of Crossbar and Delta networks for various sizes. Kruskal and Snir [27] provided asymptotic solutions for Patel's recurrence relation for the BW of delta network. Kumar and Jump [9] showed that the approximate solution obtained by Kruskal and Snir for the throughput of unbuffered delta networks is a strict upper bound. They also derived a strict lower bound on the performance of the delta network. If the output rate of the switches in stage *i* is denoted by  $x_i$  then the following upper and lower bounds for  $x_i$  is obtained.

$$\frac{2B}{\frac{2B}{x_0} + (B-1)i} \ge x_i \ge \frac{2B}{\frac{2B}{x_0} + (B-1)i + 2BE_i}$$

$$\times \log_e \left[ \frac{i \times (B-1)}{x_0} + 1 \right].$$

where,  $E_i = \frac{B^2 - B + 2}{4B^2} \times log_e \left[ \frac{i \times (B-1)}{\frac{2B}{x_0} - 2B + 2} + 1 \right].$

Streker [6] developing a set of simple approximate models for a system with N processors and M memory modules had arrived at the same formula for BW. The basic assumption remained the same - memory requests at every cycle are independent and uniformly distributed. Another way to look at it is that the rejected requests at the end of every memory cycle are discarded, and are reassigned randomly among all memory modules in the next cycle. Ravi [28] presented a very similar model for the case where the request rate is 1, and his results has been shown to be exactly the same. Briggs and Davidson [29] have extended Streker's model to incorporate cases like memory cycle times greater than unity, memory access times different from memory cycle times etc.

#### Non-uniform reference model

For non-uniform reference, the basic assumptions are changed. Now it is assumed that the rejected requests are not simply discarded but are resubmitted. Also in some cases memory requests were assumed to be non-uniform in each memory cycle. Yen, Patel and Davidson [7] proposed a new model, called the *rate adjusted probability* model, which sought to adjust the memory request rate (assumed same for all the processors) for the new assumption that the rejected requests are not simply discarded but are resubmitted as new and independent requests, thereby increasing the effective request rate. The resubmission follows a uniform distribution. One of the major drawbacks of this model is that it over-estimates BW, because multiple rejected requests to the same memory module will get evenly distributed to all the memory modules in the next cycle, thereby increasing their chance of acceptance. If  $P_A$  is the probability that a request is accepted then  $\frac{1}{P_A}$  is the expected number of rejections (blocked cycles) plus the one accept cycle. If  $\psi$  is the static request rate and  $\alpha$  is the adjusted request rate (also called *dynamic* request rate) then  $\alpha$  is given by

$$\alpha = \frac{\frac{\psi}{P_A}}{1 - \psi + \frac{\psi}{P_A}}$$

and bandwidth is given as

$$BW = M \left[ 1 - \left( 1 - \frac{\alpha}{M} \right)^N \right]$$

The probability of acceptance  $P_A$  is  $\frac{BW}{N\alpha}$ .

Bhuyan [8] introduced the concept of favorite memory modifying the uniform distribution pattern of memory requests assumed in the earlier works. Each processor  $P_i$  has a favorite memory module  $M_i$  with which it communicates more than any other memory module. A factor m which is the probability that  $P_i$  accesses  $M_i$  provided  $P_i$  generates a memory request is assumed to be known apriori. The remaining processors' requests are uniformly distributed among the (N-1) remaining modules. Obviously  $m > \frac{1}{N}$ . Bhuyan carried detailed analysis of favorite memory cases for crossbar and Delta network. If  $p_0$  is the probability that a processor generates a request, then  $p_0m$  is the rate of request to its favourite memory. Therefore, the rate of request by  $P_i$  to the non-favorite memories is  $p_0(1-m)$ , which is uniformly distributed among the (N-1) memory modules. Also probability that  $P_i$  does not request  $M_i$  is  $1 - p_0m$ . Hence for an  $N \times N$  crossbar, the probability that  $M_i$  will not be requested by the (N-1) processors (excluding  $P_i$ ) is  $\left(1 - p_0 \frac{(1-m)}{(N-1)}\right)^{N-1}$ .

$$(1 - p_0 m) \left(1 - p_0 \frac{(1-m)}{(N-1)}\right)^{N-1}$$

The probability that there will be at least one request for memory module  $M_i$  is

$$1 - (1 - p_0 m) \left( 1 - p_0 \frac{(1 - m)}{(N - 1)} \right)^{N - 1}$$

Hence the bandwidth is obtained as

$$BW = N \left[ 1 - (1 - p_0 m) \left( 1 - p_0 \frac{(1 - m)}{(N - 1)} \right)^{N - 1} \right]$$

Bhuyan extended the above analysis to favourite memory cases for  $M \times N$  crossbars with M > N and M < N: For the case M > N,  $BW = N \left\{ 1 - (1 - p_0 m) \left( 1 - p_0 \frac{1-m}{N-1} \right)^{N-1} \left( 1 - \frac{p_0}{N} \right)^{M-N} \right\}$

For the case M < N,  $BW = N - M(1 - p_0 m) \left(1 - p_0 \frac{1 - m}{N - 1}\right)^{M-1} - (N - M) \left(1 - p_0 \frac{1 - m}{N - 1}\right)^M$ For Delta networks the rate of request on an output line in the *i*th stage is

$$p_i = 1 - \left(1 - \frac{p_{i-1}}{b}\right)^a$$

where  $p_0$  is the probability of generation of a request by a processor. The analysis is restricted to only  $N \times N$  case of delta network with n stages of  $a \times a$  crossbar modules with N/a such modules per stage. A processor is connected to its favourite memory module when all switches are in a straight connection. If  $p_0$  denote the request rate of a process or and  $q_i$  denote the probability that there is a favourite request to a switch at the (i + 1)th stage, then  $p_i = 1 - (1 - p_{i-1}q_{i-1})(1 - p_{i-1}\frac{1-q_{i-1}}{a-1})^{a-1}$ . The rate of request at the final stage  $p_n$  decides the bandwidth. Hence,  $BW_f = p_n \times N$ .

## 2.1.2. Buffered MINs

With buffered MINs we now have the provision of saving rejected request-packets for resubmission to the same memory module in the next cycle. This increases the system performance considerably, especially when the traffic pattern is non-uniform. A packet is not lost when path conflict occurs with more than one processor trying to send their requests through the same port of a switching module. Also a packet can leave a buffer in one switching module only when the buffer at the succeeding stage is able to accept it. Next we consider several performance evaluation of buffered MINs with the help of various models.

Skinner and Asher [5] were the first to use Markov chain models to analyse memory interference in multiprocessor systems with memory queues. The basic assumption was that all processors and all the memory modules are identical. A multiprocessor system with n processors and m memory modules, where, at each memory cycle a set of processors are allocated a set of memory modules is similar to an occupancy problem with n balls and m urns, a common combinatorial problem. If state of the Markov chain is defined by the m-tuple  $(k_1, k_2, k_3, \ldots, k_m)$ , where  $\sum_i k_i = n$  and  $k_i$ denotes the number of processors waiting in the queue of the  $i^{th}$  memory module including the currently active processor. The number of possible states in such case is equal to the number of different ways n balls can be placed in m urns which is given by  $\binom{n+m-1}{n}$ . Since the number of states becomes prohibitively large for large values of n and m, Skinner and Asher's study was limited to a small number of processors and memory modules, and they failed to generalise it for larger number of processors and memory modules.

Bhandarkar [1] reduced the number of states noting that many of the states of the Markov chain model were identical owing to the assumption that all the processors are identical. For example in a four processor and three memory modules system, the states denoted by the following 3 tuples are identical : (1, 2, 1), (1, 1, 2), (2, 1, 1). Bhandarkar defined a *partial* state as a transition state between the current state and the next state, with the assumption that all the currently active processors will terminate their memory access at the end of the current cycle. So st the end of the current cycle the system enters a partial state where the number of processors in each memory queue decreases by one. If the current state is  $(k_1, k_2 \dots k_m)$  then the partial state at the end of the cycle is  $(j_1, j_2, \dots j_m)$  where  $j_i = k_i - 1$  if  $k_i > 0$  or = 0, otherwise. A new state  $(l_1, l_2, \dots, l_m)$  is said to be reachable from  $(k_1, k_2, \dots, k_m)$  if

$l_i \geq k_i$ . Probability of a state transition is  $\frac{x!}{d_1!d_2!...d_m!} \left(\frac{1}{m}\right)^x$  where  $d_i = l_i - j_i$  and  $\sum_i d_i = x$ . Since the number of states in this case too, became unmanageably large for m, n > 3, Bhandarkar wrote a program to compute the state transition matrix of the Markov chain.

Sethi and Deo [2] proposed a discrete Markov chain model for analysing memory interference in multiprocessor systems for non-uniform memory access pattern. They assumed that if the  $n^{th}$  request of a processor is for memory module i, then the  $(n+1)^{th}$ request will be for module i with probability  $\alpha$  and for module  $j(j \neq i)$  with probability  $\frac{(1-\alpha)}{(m-1)}$ . Thus requests to memory modules except the previous one are assumed to be uniformly distributed. If  $\alpha = \frac{1}{m}$ , where m is the number of memory modules, the model reduces to the uniform reference model. The performance measure used by Sethi and Deo for analysis of a  $p \times m$  system (p processors and m memory modules) is Average Number of Busy Memory Modules (ANBM's). This is the average number of memory modules which are busy during a memory cycle. Following Bhandarkar's approach to use the discrete Markov chain technique, the ANBM's for a  $2 \times m$  and  $p \times 2$  are computed from the state transition probabilities. The ANBM for a  $2 \times m$ system is given by

$$ANBM = \frac{m(2m+\alpha-3)}{m(m+\alpha-1)-1}$$

The ANBM for a  $p \times 2$  system having two memory modules and  $p \ge 2$  processors is given by

$$ANBM = \frac{2(p+\alpha-1)}{p+2\alpha-1}$$

Similar analysis was carried out for a  $3 \times m$  system with three processors and  $m \ge 3$  memory modules, but with  $\alpha = 1$ . The ANBM was obtained as  $3 - \frac{6}{m+2}$ .

Yen, Patel and Davidson[7] proposed a steady state flow model for multi- processor systems with memory queues. Let N and M be the number of processors and memory modules,  $\psi$  be the request rate and f be the processor utilization. Then Nf processors are active (either in accessing memory or in some internal computation) and N(1-f) processors are blocked. The Nf active processors issue  $Nf\psi$  memory requests each cycle and  $Nf(1-\psi)$  processors are blocked. Since all the  $Nf\psi$  requests are accepted, the steady state number of active processors remains fixed at Nf. To compute the number (r) of non-empty queues in the system, a successive approximation method is applied. In the first step all the N(1-f) queued requests are distributed uniformly among M queues to give

$$\frac{r'}{M} = 1 - \left(1 - \frac{1-f}{M}\right)^N$$

This model uses a better estimate assuming that each of the M queues has probability  $\frac{r'}{M}$  of making an access request. Then

$$\frac{r}{M} = 1 - \left(1 - \frac{r'}{M}\right)^M$$

is the estimated probability that there is a request for a particular memory. The probability that none of the N processors has a request for that memory is  $\left(1 - \frac{f\psi}{M}\right)^N$ . Thus the effective memory bandwidth of the system is given as

$$BW = M \left[ 1 - \left( 1 - \frac{f\psi}{M} \right)^N \left( 1 - \frac{r}{M} \right) \right] = Nf\psi$$

Pfister and Norton [16] introduced a separate class of memory-access non-uniformity called *hot spot* of higher access rate superimposed on otherwise uniform traffic. Hot spots capture the effect of all the processors continually sharing a common variable, which resides in a particular memory module called the *hot* memory. An interesting phenomenon called *tree saturation* can be observed for MINs with finite buffers. When the queue at the root of the *fan-in* tree (formed by the links connecting all the processors to a single memory module in the MIN) becomes full, the queues in the previous stage can no longer send packets to them and become full themselves leading to similar conditions to all the queues in other levels of the tree. Eventually the entire tree consists of full queues. Pfister and Norton introduced the concept of *combining* messages to similar destination at every node of the network. In particular comparisons are performed only between a pair of messages stored in the output queues

of each switching node (only blocked messages), and if the messages are combined the information is stored in a *wait buffer*. A combined message can combine again in a later node. When a reply to a combined message reaches a node where it was combined, multiplies replies are generated and the messages are routed to individual destinations based on the information stored in the *wait buffer*.

Pairwise combining shows definite improvement over non-combining in systems having hot spots. Ideally one would like to combine as many combinable messages as resided in the buffer of a switch module. But this makes the combining process complicated and also creates congestion in the wait buffer. Simulating pairwise combining in a network consisting of many stages, Lee, Kruskal and Kuck [17] observed that *tree saturation* still takes place. With infinite buffer length the congestion takes place only at the root, although the situation improved with finite buffers because messages spend more time waiting near the base of the tree thereby increasing the probability of combining. Lee and Kuck suggested a bounded combining scheme with three-way combining as the best solution noting that combinable requests coming out of the switches are slightly more than two combinables.

Jenq [10] formulated two models for analyzing single-buffered banyan network composed of  $2 \times 2$  switching elements. The basic assumption behind the first model is that the buffers in the same switching element (SE) are independent of one another and traffic pattern is uniform. He also developed another model that does not include the independence assumption, and the results from them nearly matched. So it was concluded that the independence assumption is realistic. However a major drawback of this model is that blocked states were not considered.

Yoon, Lee and Liu [12] extended Jenq's model to the more general case of networks composed of  $n \times m$  SEs. They also expanded the single-buffer model to multi-buffer model. Basically, this model has two states - one state in which there is no request in the buffer and another state in which there is a single request in. Since all the buffers are assumed to be identical and independent, these two states are sufficient to model the system behavior. But this model still did not incorporate the blocked state. Theimer, Rathgeb and Huber [14] improved upon the previous two models by discarding the assumption of independence between buffers in a SE. Instead they exhaustively enumerated the possible states in the  $2 \times 2$  SE. The model has nine states and it takes the blocked state into consideration. Although it shows significant improvement over the previous two models, the number of states become prohibitively large for arbitrary larger sizes of SE or number of buffers.

Although the performance of MINs under uniform traffic model is interesting to note, it does not represent the traffic pattern of a realistic system. Kim and Leon-Garcia [18] carried out the analysis of buffered Banyan networks, consisting of  $2 \times 2$ switching elements (SE, crossbar elements), under non-uniform traffic pattern. The two important performance metrices of any interconnection network are throughput and delay. *Throughput* is defined as the number of output packets per clock cycle that exit from each output port. *Delay* is defined as the time taken by a packet to reach the destination port starting at the input port. For non-uniform traffic pattern these parameters are going to change from module to module and hence the maximum delay and the maximum throughput at a destination port which has the worst congestion is considered. The buffered Banyan network is modeled as a Markov chain and analysed using a network decomposition technique. First, individual SE's are modelled and then the relationship among the switching elements are depicted. In fact, each SE is represented by the state of its buffers, which are as before. Buffers with single elements are considered.

State 0 : no packet in the buffer

State 1 : single packet in buffer

For our case, the throughput of the network is defined as the expected number of packets delivered from the last stage of the network per cycle. For a switching module l in stage k, let the input ports be denoted by x and the output ports by y. Let,

$B_{klx}$  Probability that there is a packet in buffer of port klx

$P_{klxy}$  Probability that a packet at klx is destined to y

$r_{klx}$  Probability that a packet at klx can advance to next stage, then

the average number of packets delivered per cycle from the port klx to kly of a SE is  $P_{klxy}B_{klx}r_{klx}$ .

To find  $B_{klx}$  the state-transition equations of the two state Markov chain is solved to get the steady state probabilities of states 0 and 1.  $B_{klx}$  is equivalent to the steady state probability of state 1. To find  $r_{klx}$  note that a packet at the buffer of the klxport is allowed to advance if the following conditions are met :

1) The packet either reaches port y without any contention or wins contention if there is any. 2) Buffer at (k + 1)l'y' is able to accept a packet. This is possible if there is no packet at that buffer, or if there is one it is going to leave the port in the current cycle.

If both 1) and 2) are satisfies then a packet reaches the next stage and contributes to the throughput of the network. Based on the above the following equation was derived

$$r_{klxy} = (1 - B_{klx} + B_{klx}P_{klxy} + .5B_{klx}P_{klxy}) \cdot (1 - B_{(k+1)l'y'} + B_{(k+1)l'y'}r_{(k+1)l'y'})$$

$r_{klx}$  can be obtained from  $r_{klxy}$  as follows

$$r_{klx} = r_{klxy}P_{klxy} + r_{klxy}P_{klxy}$$

and delay for a path is given as

$$\sum_{all stages} \frac{1}{r_{kley}}$$

Addding to this the IBC buffer delay, we get the total delay of the network. The objective is to compute the values of r and B. Since both of them are described by recurrence relations, the solutions are by iterative method, assuming a certain *load* matrix feeding certain traffic load to the first stage.

Hsiao and Chen [13] modeled single buffered MINs with SEs of arbitrary sizes using three states. 'State 0' is when the buffer is empty, 'State n' is the normal state where a buffer has a packet which arrived in the previous network cycle, and 'State b' is the blocked state where the buffer has a blocked packet which had stayed there for at least one cycle due to blocking. A blocked state occurs when a packet cannot move to the next stage because the destination stage buffer is full or it has lost the contention with other packets for a same output link. Hsiao and Chen, however based their model on certain unrealistic assumptions. For example, they assumed that a blocked request cannot go directly to the next stage even though there is an empty buffer and no other packets are destined for it. This is because a blocked packet can only contend with other blocked packets and if it wins the contention it changes state from blocked to normal state. Thus this assumption overestimates packet delay of the network. Also a blocked packet is not resubmitted to the original memory module but randomly distributed.

#### 2.2. Multiple Bus Interconnection Network

The interconnection networks discussed so far used either crossbar networks or multistage interconnection networks, which are attractive because of the high bandwidth capability and fault tolerence. But the principle disadvantage of these systems is their high cost (cost of the switching modules). Most of the commercially available systems having a single processor use a single shared bus. A logical and cost effective extension of the single bus systems are the multiple bus systems. Single bus systems are inexpensive but they lack fault tolerence and have a limited bandwidth. A multiple bus system will naturally increase the bandwidth and fault tolerence, without increasing the cost appreciatively, because we are not dealing with the expensive switching modules anyway. Another advantage of multiple bus systems over MIN's is the simple interconeection scheme and easy expansibility.

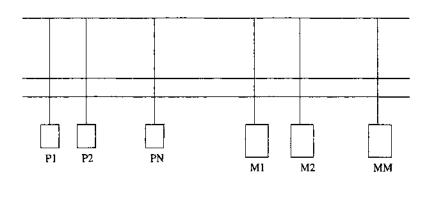

Lang [19] was the first to investigate the performance of multiple-bus systems. They divided the multiple bus systems into two categories, complete and partial, based on the interconnection scheme of the bus with the processors and memory modules. For a typical system consisting of B buses used to connect N processors to M memory modules ( $B \leq N$ ), in the *complete* case (fig 2.2a) every processor and memory module are connected to every bus; in the *partial* case (fig 2.2b), each memory module need to be connected to a subset of buses. Lang *et al.* showed that a complete multiple bus configuration with  $B \approx \frac{N}{2}$  has almost the same bandwidth as an  $N \times M$  crossbar and higher fault tolerence. Simulations were used to determine the bandwidth of both classes of system.

Figure 2.2: Examples of Multiple Bus Interconnection Networks

Mudge, Hayes, Buzzard and Winsor presented a discrete stochastic model of bandwidth for multiple bus multiprocessor systems for both the partial and complete case taking into account the various conflicts arising from memory and bus contention. Two types of assumptions are made to simplify the analysis - i) temporal independence, in which successive memory requests are assumed to be independent (i.e. blocked requests are discarded), and ii) spatial independence, in which the event that there is at least one request for a particular memory module is independent of the same event for another memory module. Later, spatial independence assumption was removed, and an iterative scheme is developed to reduce the error caused by the temporal independence.

There are two sources of conflict due to memory requests in a multiple bus system - i) memory interference, when a processor requests an already busy memory module, ii) bus interference, when a memory request cannot be completed due to non-availability of a bus. Lang *et al.* proposed a two stage arbitration scheme to resolve these conflicts. In the first step, M 1-out-of-N memory arbiters each selects one outstanding request for each memory module. In the second step, one B-out-of-M bus arbiter assigns buses to the requests selected in the first stage. Each processor is assumed to generate independent requests (Bernoulli trials) for memory modules at the beginning of each memory cycle with probability p. The memory requests are assumed to be uniformly distributed over all memory modules with probability  $\frac{1}{M}$ . Therefore, probability that a particular processor  $P_i$  requests memory module  $M_j$  is  $\frac{p}{M}$ . If  $E_j$  is the event that there is at least one request for  $M_j$ , then probability of  $E_j$  is

$$Pr[E_j] = q = 1 - (1 - \frac{p}{M})^N$$

If events  $E_j$  are assumed to be independent, then probability that exactly *i* of the M memory request arbitrs output a memory request is  $f(i) = \binom{M}{i}q^i(1-q)^{M-i}$ . The probability that B or more of the M memory request arbitrs output a memory request is  $F(B) = \sum_{i=B}^{M} f(i)$ . Now requests for at most B of these memory requests can be met as there are only B buses. Hence the BW of a *complete* multiple bus

system is

$$BW = BF(B) + \sum_{i=1}^{B-1} if(i)$$

These results are next extended to the partial bus case. Let the *B* buses be divided into *g* equal groups (assume *g* is a factor of *B*). Let  $m = \frac{M}{g}$  and  $b = \frac{B}{g}$ . Thus,  $f_g(i) = {m \choose i} q^i (1-q)^{m-i}$ , and  $F_g(B) = \sum_{i=b}^m f_g(i)$ . Hence bandwidth is given as

$$BW_g = g\left[bF_g(B) + \sum_{i=1}^{B-1} if_g(i)\right].$$

The idea is to multiply by g the bandwidth of any one of the groups of complete multiple bus systems to get the bandwidth of the whole system.

The same model is extended by the authors to the case with spatial dependence, i.e. assuming each event  $E_j$  is dependent on  $E_k$  for  $k \neq j$ . The dependence is given as follows.

$\begin{aligned} &Pr[E_j|E_k] = \sum_{i=1}^{N} Pr[E_j|E_k \text{ results from } i \text{ requests}] \times Pr[E_k \text{ results from } i \text{ requests}] \\ &= \sum_{i=1}^{N} \left[ 1 - \left(1 - \frac{p}{M-1}\right)^{N-i} \right] \binom{N}{i} \left(\frac{p}{M}\right)^i \left(1 - \frac{p}{M}\right)^{N-i}. \end{aligned}$

To consider the effects of *spatial* dependence, the authors defined a new function h(i) denoting the exact probability that *i* of the *M* memory request arbitres output a memory request. An expression for h(i) was deduced, and is given as

$$h(i) = \sum_{k=i}^{N} {\binom{N}{k}} p^{k} (1-p)^{N-k} {\binom{M}{i}} M^{-k} \theta$$

where  $\theta$  is given as,  $\theta = \sum \frac{k!}{n_1!n_2!...n_i!}$  where the summation is carried out over all  $n_1, \ldots n_i > 0$ . An alternative expression for  $\theta$  is given in [] as  $\theta = i! \binom{k}{i}$ , where  $\binom{k}{i}$  denotes a Stirling number of the second kind. It is defined as the number of ways to partition a set  $X_k$  of k elements inti i nonempty disjoint subsets. The new expression for bandwidth is given by

$$BW = BH(B) + \sum_{i=1}^{B-1} ih(i)$$

, where  $H(B) = \sum_{i=B}^{M} h(i)$ .

In order to distinguish between the two expressions of bandwidth, they are called  $BW^{f}$  and  $BW^{h}$  respectively. It is however shown that in the bus-sufficient case (i.e.

where  $B \ge M$ ) we have  $BW^h = BW^f$ .

Until now it is assumed that blocked requests are rejected, which in practise is not true. Actually they are stored in memory queue and resubmitted to the same memory module in the next cycle. The probability of acceptance of a memory request is given as  $P_a = \frac{BW}{Np}$ . Due to the resubmission of memory requests to the same memory module, teh request rate is going to increase. Let  $\alpha$  be the *adjusted* request rate. Ratio of the number of successful memory requests to teh total number of requests is the probability of acceptance,  $P_a$ , given by  $\frac{\frac{1}{a}-1}{\frac{1}{p}-1}$ . The above two equations for  $P_a$  can be used in an iterative scheme to get an improved estimate of bandwidth due to the new request rate  $\alpha$  as follows

$$\alpha_{k+1}^{-1} = 1 + \frac{BW(\alpha_k)}{Np^2}(1-p).$$

where  $BW(\alpha_k)$  is obtained by replacing p by  $\alpha$  in the expressions for f(i) and h(i), used in the expressions for BW. Finally, some asymptotic approximations to the bandwidth of multiple bus systems is considered. From our expression of bandwidth,  $BW^f$  is bounded by  $\sum_{i=0}^{M} Bf(i)$ , i.e.  $BW^f \leq B$ . Also replacing the first term on the right band side by  $\sum_{i=B}^{M} if(i)$ , we get  $BW^f \leq \sum_{i=0}^{M} if(i)$ , i.e.  $BW^f \leq Mq$ . Hence, BW = min(B, Mq). Mq is called bus-sufficient bandwidth and making B > Mqdoes not improve the bandwidth anymore.

Markov chain models for the analysis of multiple bus multiprocessors were developed by Marson and Gerla [22]. The performance index was the average number of active processors called *processing power*, *P*. The model specifies that a processor can be in any of the following three states:

1) processor is busy in internal computation using its private cache memory.

2) processor exchanges data with other cooperating processors, by accessing the global memory modules. 3) processor is waiting in the queue of any of the global memory modules.

A processor is said to be active when it is in state 1) and the processing power is

defined as:

## P = E[number of active processors].

Processors join memory queues if the requesting memory module is busy, and before proceeding to service (i.e. accessing memory) must be given a permit to access a bus. The permit is returned upon completion of service. With these assumptions a closed queueing network model is developed with the following parameters : 1) the duration of the access to the common memory is an independent exponentially distributed random variable with mean  $\frac{1}{\mu_j}$  for the  $j^{th}$  memory module. In order to simplify the model the parameter is assumed to be the same for all memory modules and simply called  $\frac{1}{\mu}$ . 2) The interval between subsequent access requests is an independent, exponentially distributed random variable with mean  $\frac{1}{\lambda_i}$  for the  $i^{th}$  processor. This was also assumed to be same for all the processors and simply called  $frac1\lambda$ . 3) A uniform reference model was assumed, that a request from a processor is directed to any of the common memory modules with probability frac1m. Marsan and Gerla carried out the exact performance analysis for a  $p \times m \times b$  system with the above assumptions. Applying Little's law to the entire memory system including queues and servers, we have the average customer delay  $D = \frac{p-P}{P\lambda}$ . The average queueing time is given as  $W = \frac{p - P(1 + \rho)}{P\lambda}$ , where  $\rho = \frac{\lambda}{\mu}$ . The average number of queued processors is  $N_q = WP\lambda = p - P(1 + \rho)$ ; and average number of processors accessing common memory is  $N_s = \frac{D-W}{P\lambda} = P\rho$ . The average cycle time (average time taken by the customers to cycle through the closed queueing network) is easily obtained as  $C = W + \frac{1}{\lambda} + \frac{1}{\mu} = \frac{p}{P\lambda}.$

Marsan and Gerla also constructed a Markov chain model using the theory of lumpable Markov chains for defining the states. The state definition is  $(n_m, q_1, q_2, \ldots, q_m)$  for the genral  $p \times m \times b$  system.  $n_m$  is the number of processors currently accessing a common memory,  $q_1 \ldots q_b$  are numbers of processors queueing for memory modules currently accessed and  $q_{b+1} \ldots q_m$  are numbers of processors queueing for free memory not accessible because no free bus is available. The general  $p \times m \times b$  case was

not easy to handle because of teh huge explosion of states as the number of processors and memory modules are increased. The state transition rates for a  $3 \times 3 \times 2$ model could be computed. Next, various approximate models were developed with reduced number of states, by reducing the amount of information about the status of the queues in each state. In the first model, the state of the system is represented by  $(n_m, n_q)$  where  $n_m$  =number of processors currently accessing a common memory module, and  $n_q$  =number of processors queued. The transition rates were computed for the most general case. Since the number of active processors is  $p - n_m - n_q$ , the processing power can be evaluated once the steady state distribution of the Markov chain is known. In the second model the state definition is the same as in the first model. The transition rates are evaluated using an "averaging" technique. Various identical states are merged into a "macro-state", the rates from the merged state to all neighbouring state are added up and the new transition rate for the merged state is defined as the ratio between the sum and the number of merged states. In the third model, a state is represented by  $(n_m, n_q, f)$ , where the definitions of  $n_m$  and  $n_q$ remains as before and f is a flag which is set to zero when no processor is queued for a bus. Transition rates for the  $p \times m \times 2$  were computed for this model. In the fourth model, the system state is simply the number of active processors. The transition rates are evaluated using the averaging technique.

A semi Markov model for the performance of multiple bus systems was proposed by Mudge and Al-Saldoun [21]. The basic assumptions are as follows: At any cycle, a processing element (PE) can be in any of the three states, thinking i.e. busy in unternal compute, accessing i.e. connected to a memory module, and waiting i.e. waiting in the queue of a memory module. A memory module can also be in any of the following two states: busy, when a PE is connected to it, and idle, when no PE is connected to it. Each PE will submit a request after its thinking time T, a discrete random variable, which is the inter-request time. Also there is a connection time between a processor and a memory module, given by the discrete independent

random variable C. Considering a  $N \times M \times B$  system, a semi-Markov process was used to describe the state of each PE. This considerably simplifies the state space reducing it to only four states as opposed to using a discrete Markov chain model for each PE, where the number of states can grow very large. Briefly, a semi-Markov process (SMP) is a stochastic process which can be in any one of the K states  $1, 2, \ldots, K$ . Each time it enters a state i it remains there for a definite amount of time called the sojourn time, having mean  $\eta_i$  and then makes a transition to state j with probability  $p_{ij}$ . The four states are as follows: The first state is the thinking state 0. The second state is the accessing state 1. The third state is the full waiting state 2. The PE enters state 2 when it requests an idle MM simultaneously with at least one other PE, and it fails to access the MM (by passing the two levels of arbitration as proposed by Lang). The fourth state is the residual waiting state 3. A PE enters state 3 when it requests a busy MM or when, due to bus contention, access is blocked to an MM even though it is idle. The underlying approximation of this model is in describing any PE behaviour independent from other PE's while compensating for the coupling between the PE's in the transition probabilities between the states of the SMP.

Detailed analysis was carried out and the following performance indices were computed for the  $N \times M \times B$  multiprocessor system. The transition probabilities between the states were computed and the steady state probabilities were determined. Let  $\alpha_i$ be the probability of the process entering state *i* and  $P_i$  be the steady state probability of the same state. The following parameters were computed:

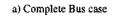

Bandwidth,  $BW = NP_1$ Processor utilization,  $PU = P_0 + P_1$ Memory utilization,  $MU = \frac{N}{M}P_1$ Bus utilization,  $BU = \frac{N}{B}P_1$ Average queue length,  $L = \frac{N}{M}(P_2 + P_3)$ Average waiting time,  $W = \frac{\eta_2 \alpha_2 + \eta_3 \alpha_3}{\alpha_1}$ . The performance of multiple bus multiprocessor systems under a non- uniform reference model called hierarchical requesting model is studied by Chen and Sheu [25]. Various types of multiple bus networks investigated involve *i*)complete(full) bus case *iii*)partial bus case *iii*)single bus case and the newly introduced *iv*)partial bus with K classes. In a single bus network, each processor is connected to all the buses, but each memory module is connected to a single bus. A new architecture of  $N \times M \times B$  multiple bus networks called partial bus networks with K classes is introduced, where there are K classes of memory modules ( $K \leq B$ ). The memory modules of class  $C_K$  are connected to all the buses 1 to B, memory modules of class  $C_{K-1}$  are connected to B-1 buses from 1 to bus B-1 etc. In general, memory modules in class  $C_j$  are connected to j + B - K buses. Fig 4 shows an example of a partial bus network with 3 classes. Memory modules which needs more fault tolerence of buses and which are more frequently referenced are connected to more number of buses in this scheme. To avoid memory and bus contention the two stage arbitration scheme proposed by Lang [19] is used. The cost and fault tolerent capability of each type of network are

A 3 X 6 X 4 Partial bus network with three classes

Figure 2.3: Example of Partial Bus Network with three classes

evaluated and compared. The cost of a multiple bus network is proportional to the number of connections in the network. For the  $N \times M \times B$  multiple bus with full bus-memory connection, cost is O(B(N + M)), and the degree of fault tolerence is B-1. Similarly cost for single bus systems is O(BN+M), and it is less fault tolerent than the complete bus case. The cost in case of the partial bus case is  $O(N + \frac{M}{g})$ , where g is the number of groups; the fault tolerence is  $\frac{B}{g} - 1$ . In case of partial bus network with K classes, cost is proportional to  $BN + \sum_{j=1}^{K} M_j(j + B - K)$ , where  $M_j$  is the number of memory modules in class  $C_j$ . The degree of fault tolerence of this network is B - K. It is seen that the cost and fault-tolerence of networks with full and single bus-memory connection.

To analyse the performance of multiple bus networks a hierarchical requesting model is proposed. For an  $N \times N \times B$  system, assume that  $N = k_1 k_2 \dots k_n$ . Each processor  $P_i$  has a memory module  $MM_i$  as its favourite memory. These processors and memories are organised into an n-level hierarchy. First, the N pairs of processors and memory modules are partitioned into  $k_1$  clusters in the first level, each cluster containing  $k_2 k_3 \ldots k_n$  pairs of processor- memory. In the second level, each of  $k_1$  clusters is partitioned into  $k_2$  subclusters of equal size, and so on. For an *n*-level hierarchy, there are n + 1 different request rates for a processor,  $m_0, m_1 \dots m_n$  depending on the hierarchy of the memory module addressed to. We assume that  $m_0 \geq m_1 \geq \ldots m_n$ . If  $N_i$  be the number of processors or memory modules belonging to the same subcluster in the (n-i)th level excluding those in the (n-i+1)thlevel, then  $N_i$  is given as  $N_i = (k_{n-i+1}-1)k_{n-i+2} \dots k_{n-1}k_n$  and  $\sum_{i=0}^n m_i N_i = 1$  where  $N_0 = 1$ . Let X be the probability that there is at least one request for a particular memory module  $MM_j$  and let  $p_0$  be the probability of connection to a favourite memory. If r be the request generation rate then the probability that at least one request is generated by those processors which request connection to  $MM_j$  with fraction  $m_i$ is  $p_i = 1 - (1 - rm_i)^{N_i}$ . Hence, probability that at least one processor requesting connection to  $MM_j$  is  $X = 1 - (1 - rm_0)(1 - rm_1)^{N_1} \dots (1 - rm_n)^{N_n}$ . Then the probability that exactly *i* of the *N* memory-request arbitrs output a memory request is given by  $P(i) = {N \choose i} X^i (1 - X)^{N-i}$ . The memory bandwidth in case of full bus-memory connection is given by

$$MBW = NX - \sum_{i=B+1}^{N} (i-B)P(i).$$

For the single bus case, if  $M_i$  be the number of memory modules connected to bus i, then the probability that there is at least one memory service bus i is  $Y_i = 1 - (1 - X)M_i$ . Then the memory bandwidth is given by

$$MBW = \sum_{i=1}^{B} Y_i$$

.

Figure 2.4: A taxonomy of related work on memory references

# 2.3. Conclusion

In this chapter, we discussed some of the important previous work in the area of processor memory interconnection. A taxonomy of all the work which has been described so far is shown on figure 2.4. All types of interconnection schemes can be broadly classified into two groups – multiple stage interconnection networks (MIN) and multiple bus interconnection networks (MBIN). Under the first scheme, we have distinguished between two types of memory access patterns, nemely, the uniform reference and the non-uniform reference models. Since no work has been done for uniform reference model under MBINs, we do not have any such classification in the second case.

# CHAPTER 3

# MARKOV MODEL FOR MULTIPROCESSORS WITH HOT SPOTS AND FAVORITE MEMORIES

In this chapter, we derive a discrete Markov model for shared memory multiprocessor systems in which each memory module has a buffer for queueing up unsatisfied memory requests. The following assumptions are made in order to develop our model, allowing two types of non-uniformity, namely, *favorite* and *hot* memories.

Figure 3.1: A Buffered memory system

- 1. There are N processors and M memory modules in the system; all processors are identical, so are all the memory modules.

- 2. When a processor requests access to a particular memory module, it is granted if the requested memory module is not busy.

- 3. There is no contention in the interconnection mechanism.

- 4. If two or more processors request access to the same memory module then only one of them is granted permission, and the rest are queued up in the queue

associated with the memory module. The process of selection is completely random.

- 5. The system is synchronous, i.e. all the requests made by the processors are at the beginning of the cycle. All the memory cycles are of equal length.

- 6. All the processors have an identical memory request rate  $\lambda$ .

- 7. The memory access of a processor may last over several memory cycles. The completion rate of a memory access by a processor is given by  $\mu$ . In almost all related works, it has been tacitly assumed that  $\mu = 1$ , to simplify the models.

- 8. If there is a 'hot' memory module in the system, then the probability of accessing the hot memory is given by m. If there are K hot memories, they are all identical and memory reference is uniform among the hot memory modules.

- 9. The memory reference pattern among the "non-hot, non-favorite" memory modules is also uniform.

- 10. Successive memory requests follow the following scheme, which models the temporal locality concept of memory references. If in the current cycle, a processor accesses memory module M<sub>j</sub>, then, given it completes its access in the current memory cycle, the probability that it will again request access from the module M<sub>j</sub> is given by α. Also, references to other memory modules are uniformly distributed, with probability given by <sup>1-α</sup>/<sub>M-1</sub>.

We follow a step by step approach in developing our model. We start with the case where there is only one hot memory in the system and the rest are all nonhot memories. The favorite memory case is not included in this analysis. Then we extend the model to K hot memories, again without any favorite memory. Next the favorite memory case is introduced along with a single hot memory. As the state space becomes enormously large for M, N > 2, we restrict our analysis to systems with two processors and M memory modules, and N processors and two memory modules. A scheme for extension to the general case of  $N \times M$  system using simulation, is discussed in Section 4. and the consequences of the experiments discussed. In Section 5, an approximate probabilistic analysis of a  $N \times M$  system is given and a heuristic is proposed to find the value of K beyond which the memory bandwidth is expected to saturate.

# 3.1. $2 \times M$ system, one hot spot without any Favorite memory

There are two processors and M memory modules in the system. Of these M memory modules, one is a hot memory. Let m be the probability of request of a hot memory by any processor. Then,  $\frac{1-m}{M-1}$  is the probability of request of any other M-1 non-hot memories. If  $\lambda$  is the request rate of a processor, then the probability that a processor requests the hot memory is given by,  $p_h = \lambda m$ . Probability that a processor requests a particular non-hot memory is,  $p = \lambda \frac{(1-m)}{(M-1)}$ . The next step is to enumerate all the possible states for this system.

The states are represented as two or three tuples, where each element gives the number of processor requests in the memory queue. Since there are only two processors in the system, at most two of the M memory modules have their memory queues filled up with processor request. We assume that the memory queue also holds the currently active processor. The first tuple always represents the number of processor requests in the queue of the hot memory. The remaining one (two) tuple(s) represents the number of requests in the queue of any one (two) (as there can be at most two memory modules holding a processor request) of the memory modules. A memory queue with no processor waiting or active is not always shown explicitly. They are usually shown as a zero tuple, when

(i) we want to distinguish between the non-existence of a processor in a hot memory module and the non-existence of a processor in a non-hot memory module. For example, the state < 0, 1 > represents the situation where there is no processor in the hot memory and only one processor in any one of the non-hot memory modules.

(ii) the state 0 represented by < 0, 0 > represents the situation when all processors are busy in their internal computation, and not accessing any memory module.

The enumeration of seven possible states of the  $2 \times M$  system is given below.

| state | state vector |

|-------|--------------|

| $S_0$ | < 0,0 >      |

| $S_1$ | < 0,1 >      |

| $S_2$ | < 0, 1, 1 >  |

| $S_3$ | < 0, 2 >     |

| $S_4$ | < 1,0 >      |

| $S_5$ | < 1,1 >      |

| $S_6$ | < 2,0 >      |

#### 3.1.1. Bandwidth Analysis

The state transition probabilities are next computed, as shown in Table 3.1. In this case,

$$\begin{split} \lambda &= 1 - \lambda; \\ b &= \binom{2}{1} \lambda (1 - \lambda); \\ c &= p(M - 1); \\ d &= p(M - 2); \\ \bar{\mu} &= 1 - \mu; \\ \bar{m} &= 1 - m; \end{split}$$

This gives a  $7 \times 7$  linear system of the form  $A^T \Pi = \Pi$  where A is the state transition matrix and  $\Pi = (\Pi_0, \Pi_1, \dots, \Pi_6)$  is a vector containing the limiting probabilities such that  $\Pi_i$  denotes the limiting probability of state  $S_i$ . This system of linear equations can be solved by replacing any one of them by  $\sum_{i=0}^{6} \Pi_i = 1$ . After some simple matrix manipulations, the following reduced form of the linear system is obtained, which is

| states | tes 0 1                 |                                            | 2                                        | 3                          | 4                                   | 5                                                             | 6                                |  |

|--------|-------------------------|--------------------------------------------|------------------------------------------|----------------------------|-------------------------------------|---------------------------------------------------------------|----------------------------------|--|

| 0      | $\bar{\lambda}^2$       | bm                                         | cd                                       | cp                         | bm                                  | 2cph                                                          | p <sub>h</sub> <sup>2</sup>      |  |

| 1      | $\mu \bar{\lambda}^2$   | $\mu b\bar{m} + \bar{\mu}\bar{\lambda}$    | $\mu cd + \bar{\mu}d$                    | $\mu cp + \bar{\mu} p$     | μbm                                 | $2\mu cp_h + \bar{\mu}p_h$                                    | $\mu p_h^2$                      |  |

| 2      | $\mu^2 \bar{\lambda}^2$ | $2\mu\bar{\mu}\bar{\lambda}+\mu^2b\bar{m}$ | $\bar{\mu}^2 + 2\mu\bar{\mu}d + \mu^2cd$ | $2\mu\bar{\mu}p+\mu^2cp$   | $\mu^2 bm$                          | $2\mu\bar{\mu}p_h + 2\mu^2 cp_h$                              | $\mu^2 p_h^2$                    |  |

| 3      | 0                       | μλ                                         | μd                                       | $\bar{\mu} + \mu p$        | 0                                   | μPh                                                           | 0                                |  |

| 4      | $\mu \bar{\lambda}^2$   | μbm                                        | μcd                                      | μср                        | $\bar{\mu}\bar{\lambda} + \mu bm$   | $\bar{\mu}c + 2\mu cp_h$                                      | $\bar{\mu}p_h + \mu p_h^2$       |  |

| 5      | $\mu^2 \bar{\lambda}^2$ | $\mu\bar{\mu}\bar{\lambda}+\mu^2b\bar{m}$  | $\mu\bar{\mu}d + \mu^2 cd$               | $\mu\bar{\mu}p + \mu^2 cp$ | $\mu\bar{\mu}\bar{\lambda}+\mu^2bm$ | $\bar{\mu}^2 + \mu\bar{\mu}c + \mu\bar{\mu}p_h + 2\mu^2 cp_h$ | $\bar{\mu}\mu p_h + \mu^2 p_f^2$ |  |

| б      | 0                       | 0                                          | 0                                        | 0                          | $\mu \tilde{\lambda}$               | μς                                                            | $\bar{\mu} + \mu p_h$            |  |

Table 3.1: State Transition Matrix A of  $2 \times M$  system

solved for the limiting probabilities. The seven equations are enumerated below.