# A 0.9-V 67-μW Analog Front-End using Adaptive-SNR Technique for Digital Hearing Aid

Sunyoung Kim, Jae-Youl Lee, Seong-Jun Song, Namjun Cho, and Hoi-Jun Yoo

Dept. of EE & CS, Korea Advanced Institute of Science and Technology (KAIST) 373-1, Guseong-dong, Yuseong-gu

Daejeon, 305-701, Republic of Korea

E-mail: sunyoung@eeinfo.kaist.ac.kr

Abstract—An analog front-end composed of a preamplifier and a  $\Sigma$ - $\Delta$  modulator is proposed and implemented for digital hearing aid chip. Combined gain control (CGC), the technique, which incorporates an automatic gain control (AGC) with an exponential gain control (EGC), is employed to enlarge dynamic range and reduce power consumption. The proposed  $\Sigma$ - $\Delta$  modulator exploits adaptive-SNR technique, which generates four different SNRs, thereby achieving low power consumption and optimizing performance. The measured power dissipation of the preamplifier is 35- $\mu$ W. In case of  $\Sigma$ - $\Delta$ modulator, the peak signal-to-noise ratio (SNR) is 86-dB, the average power consumption is 31.4-µW and the variation of SNR is 14-dB. The proposed analog front-end dissipates less than 67-µW from a single 0.9-V supply. The core area of the preamplifier and the  $\Sigma$ - $\Delta$  modulator is 0.1-mm<sup>2</sup> and 0.4-mm<sup>2</sup>, respectively, in a 0.25-µm standard CMOS technology.

# I. Introduction

Explosive growth for a biomedical electronic system market needs more low-power and low-voltage techniques than before [1]. Accordingly, an improvement in both of power dissipation and a performance of a digital hearing aid is necessary. Figure 1 shows a block diagram of a typical digital hearing aid system, consisting of five blocks: a preamplifier, a  $\Sigma$ - $\Delta$  analog-to-digital converter (ADC), a digital signal processing unit (DSP), a  $\Sigma$ - $\Delta$  digital-to-analog converter (DAC), and a receiver driver. Among these individual blocks, an analog front-end that comprises a preamplifier and a  $\Sigma$ - $\Delta$  modulator is reported to consume a major part of the total power [2], [3]. Therefore, reducing the power consumption of the analog front-end is attractive to decrease the total system power consumption.

In this paper, a new analog front-end architecture is proposed and implemented to achieve low power consumption with a 0.9-V supply voltage. Although lower supply voltage can be another effective solution, it may cause significant degradation of the system performance and make the analog circuit design difficult. In the proposed analog front-end, the preamplifier with combined gain control (CGC) and the  $\Sigma$ - $\Delta$  modulator which exploits adaptive-SNR technique are included.

The detail architecture of the proposed front-end will be explained in Section II. Section III will describe the circuits

Figure 1. Block diagram of a digital hearing aid system

of the preamplifier with measurement results. In Section IV details of the  $\Sigma$ - $\Delta$  modulator will be covered. Finally, conclusions will be made in Section V.

### II. SYSTEM DESIGN CONSIDERATIONS

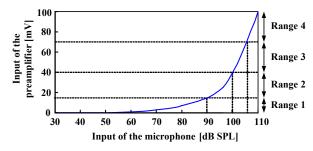

Figure 2 shows the relation between the input of the microphone and the input of the preamplifier.

Figure 2. Characteristics of a microphone for a digital hearing aid

A previous study revealed that a normal sound level common in human daily life ranges from 30 to 90-dB SPL, which corresponds to Range 1 in Figure 2 [4]. In this range, the amplitude of the sound is so small that a high performance analog front-end must be used. On the other hand, above 90-dB SPL, Ranges  $2 \sim 4$  of Figure 2, the sound level is sufficiently large that analog front-end needs not to provide high gain. Obviously, for a small sound the high performance analog front-end is indispensable. But for the large sound, the conventional analog front-end may overperform and cause unnecessary power consumption.

In this paper, a new analog front-end architecture is proposed to satisfy not only a high performance for a small sound but also a power optimization for a medium to large sound amplitude.

In the conventional design of a preamplifier, an automatic gain control (AGC) and an exponential gain

control (EGC) are designed separately because of design difficulties. In this study, however, CGC integrates AGC and EGC into a single block to reduce power consumption. In the design of the  $\Sigma$ - $\Delta$  modulator, the input sound level is divided into four parts as shown in Figure 2 to control the SNR separately at each range achieving power-optimized performance.

#### III. PREAMPLIFIER

#### A. Circuit Design

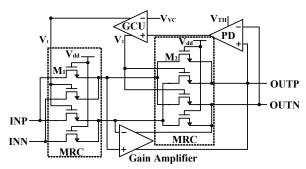

Figure 3 illustrates the suggested preamplifier. The gain of the proposed preamplifier is given as follows.

$$\frac{OUT}{IN} = gain = \frac{W_1 L_2 \left( 1 + \frac{V_x}{V_{dd} - V_{VC}} \right)}{W_2 L_1 \left( 1 - \frac{V_x}{V_{dd} - V_{VC}} \right)}, \quad V_1 = V_{VC} - V_x$$

$$V_2 = V_{VC} + V_x$$

(1)

where  $V_{VC}$  is a volume control voltage, and  $V_1$  and  $V_2$  are resistance control voltages generated by the gain control unit (GCU). GCU changes  $V_x$  according to the input signal  $V_{VC}$ . The EGC and AGC functions can be realized by controlling  $V_{VC}$  and  $V_x$ .

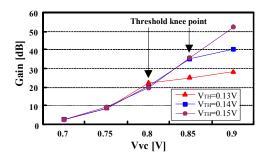

MOS resistive circuit (MRC) is implemented using four N-type transistors. It helps CGC to get the exponential gain characteristics with  $V_{VC}$  as a control signal. Moreover, a threshold knee point of the preamplifier can be changed by modifying  $V_{TH}$ . When the input sound level is high, low  $V_{TH}$  is used to reduce power dissipation and enlarge dynamic range of the preamplifier. The peak detector (PD) senses the envelope of the preamplifier output voltage and controls the GCU.

Figure 3. Proposed preamplifier with CGC technique

# B. Measurement Results

Figure 4 shows the preamplifier microphotograph in a 0.25- $\mu$ m CMOS process. In Figure 5, the measured gain and threshold knee point variations are presented as a function of  $V_{VC}$  with  $V_{TH}$  as a parameter. Because the human sense of hearing of the loudness of sound operates on a logarithmic scale and the preamplifier outputs go up linearly with the input on the same scale, it is found to operate as a volume control successfully. By reducing  $V_{TH}$ , the threshold knee

Figure 4. Chip microphotograph of the proposed preamplifier

Figure 5. Measured performance of the proposed preamplifier

point is decreased simultaneously. By preventing unnecessary high gain, it reduces power dissipation according to external conditions. Power consumption of the preamplifier is 35-µW and its core area is 0.1-mm<sup>2</sup>

# IV. $\Sigma$ - $\Delta$ modulator

# A. Circuit Design

To realize the proposed adaptive-SNR technique, the  $\Sigma$ -Δ modulator should provide four kinds of SNR for each range of Figure 2. By changing the clock frequency, the  $\Sigma$ - $\Delta$ modulator achieves different SNR characteristics, thereby obtaining power-optimized performance to specific sound range. But high clock frequency incurs a number of difficulties in design of analog circuit such as operational transconductance amplifier (OTA), because the unity-gain frequency of the OTA should be at least four times higher than the clock frequency of the  $\Sigma$ - $\Delta$  modulator [5]. The clock frequency is selected as 1.024-MHz and 2.048-MHz with the oversampling ratio (OSR) of 64 and 128, respectively. Higher order  $\Sigma$ - $\Delta$  modulator is another approach to change values of SNR. However the performance of more than  $3^{rd}$  order  $\Sigma$ - $\Delta$  modulator seriously suffers from nonidealities such as finite gain and bandwidth of the OTA and instabilities caused by saturation of the integrator [6]. In order to minimize side-effects of the higher order  $\Sigma$ - $\Delta$  modulators and change the SNR characteristics, the order of the  $\Sigma$ - $\Delta$  modulator must be limited under three.

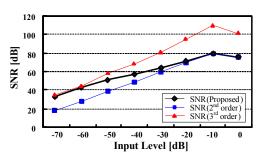

The MATLAB simulation results in Figure 6 show that the proposed  $\Sigma$ - $\Delta$  modulator accomplishes different SNR and SNDR values according to the input amplitude.

Figure.6. Simulated results of conventional vs. proposed  $\Sigma$ - $\Delta$  modulator

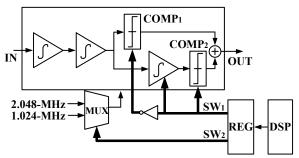

The architecture of the proposed  $\Sigma$ - $\Delta$  modulator is described in Figure 7.  $SW_1$  determines the order of the  $\Sigma$ - $\Delta$  modulator between the second and third while  $SW_2$  decides the clock frequency of the  $\Sigma$ - $\Delta$  modulator. A combination of these two switches allows the  $\Sigma$ - $\Delta$  modulator to obtain four kinds of SNRs. For easy and convenient control, these parameters of the switches are stored and applied by the control register in a DSP. By choosing the proper values according to the external sound amplitudes, the proposed  $\Sigma$ - $\Delta$  modulator obtains power-optimized SNR.

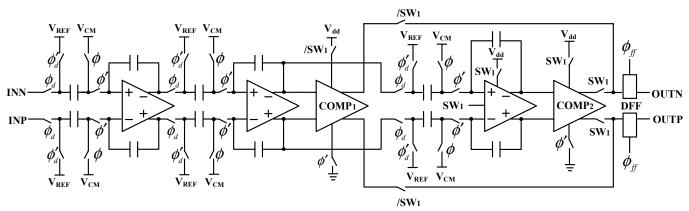

Figure 8 shows the schematic of the proposed  $\Sigma$ - $\Delta$ modulator. When the /SW<sub>1</sub> is closed, this  $\Sigma$ - $\Delta$  modulator operates in 2<sup>nd</sup> order by bypassing the output from the 2<sup>nd</sup> integrator to the OUTN or OUTP. Because the resistance value of the conventional N-type switch varies according to the drain voltage, the 2<sup>nd</sup> integrator output degrades seriously when it passes through /SW<sub>1</sub>. Hence, in order to prevent this distortion, high performance switch of which resistance is stable under all drain voltages is demanded. However, implementation of such a switch is difficult to design and consumes extra power. Therefore, this paper exploits a new method by using COMP<sub>1</sub>. It converts 2<sup>nd</sup> integrator output into a PWM signal and pass it through the /SW<sub>1</sub> without signal distortion. When the COMP<sub>1</sub> is activated, the 3<sup>rd</sup> integrator and COMP<sub>2</sub> are completely turned off to eliminate extra power consumption. On the other hand, if the /SW<sub>1</sub> is opened, the 3<sup>rd</sup> integrator accepts the output of the 2<sup>nd</sup> integrated as an input and performs the 3<sup>rd</sup> order modulation. In this phase, COMP<sub>1</sub> is turned off to avoid extra power dissipation. By turning SW<sub>2</sub> on and off, the clock frequency

Figure 7. Proposed  $\Sigma$ - $\Delta$  modulator architecture

can be selected between 2.048-MHz and 1.024-MHz, respectively. By controlling  $SW_1$  and  $SW_2$  together, four types of the  $\Sigma\text{-}\Delta$  modulators having different kinds of SNR are obtained. With  $SW_1$  open, type 1 and type 2  $2^{nd}$  order  $\Sigma\text{-}\Delta$  modulators are achieved by turning  $SW_2$  off and on, respectively. With  $SW_1$  closed, type 3 and type 4  $3^{rd}$  order  $\Sigma\text{-}\Delta$  modulators are realized by turning  $SW_2$  off and on, respectively.

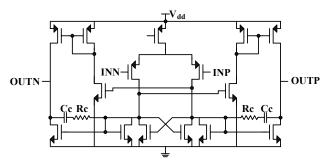

In Figure 9 a low power OTA is presented for the  $\Sigma$ - $\Delta$  modulator. It is composed of a compensated two-stage, a cross-coupled active load, and a class AB output stage [7]. It demonstrates 77.6-dB DC gain, 7.07-MHz unity gain bandwidth, and a 55° phase margin for a 3-pF load.

A 1-bit quantizer i.e., COMP1 and COMP2 with a clocked circuit minimizes the hysteresis and offset voltage [8].

Figure 9. Two-stage/class AB OTA

Figure 8.  $\Sigma$ - $\Delta$  modulator exploiting adaptive SNR technique

### B. Measurement Results

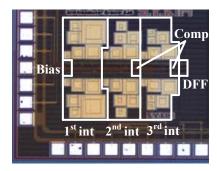

The Chip microphotograph of the proposed  $\Sigma$ - $\Delta$  modulator is shown in Figure 10. It was also fabricated in a 0.25- $\mu$ m CMOS process and its core size is 0.4-mm<sup>2</sup>

Figure 10. Chip microphotograph of the proposed  $\Sigma$ - $\Delta$  modulator

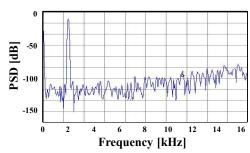

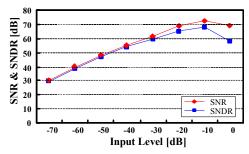

Figure 11 describes the measured output spectrum of a type 1 modulator with 2-kHz sinusoidal input signal and 1.024-MHz clock frequency. Under these conditions, the measured peak SNR is 72-dB. Figure 12 shows the measured SNR and SNDR as a function of input.

Table I summarizes the performances of the  $\Sigma$ - $\Delta$  modulator with combination of SW<sub>1</sub> and SW<sub>2</sub>. When the input sound is less than 90-dB SPL, this modulator acts as a type 4 modulator to offer high performance. But if the sound is higher than 105-dB SPL, the  $\Sigma$ - $\Delta$  modulator operates as the type 1 to reduce its power dissipation.

Figure 11. Measured spectrum of the proposed  $\Sigma$ - $\Delta$  modulator

Figure 12. Measured SNR / SNDR vs. input amplitude

The performance comparison of the proposed analog front-end with that of conventional works is described in Table II. Compared with previous works, the proposed analog front-end dissipates the lowest power consumption at 0.9-V power supply voltage.

TABLE I.  $\Sigma$ - $\Delta$  modulator performance summary

| Order of Modulator     | 2               |       | 3     |       |  |

|------------------------|-----------------|-------|-------|-------|--|

| Type                   | 1               | 2     | 3     | 4     |  |

| Clock Frequency (MHz)  | 1.024           | 2.048 | 1.024 | 2.048 |  |

| Oversampling Ratio     | 64              | 128   | 64    | 128   |  |

| Peak SNR (dB)          | 72              | 81    | 78    | 86    |  |

| Power Consumption (µW) | 26.4            | 26.8  | 35.7  | 36.7  |  |

| Signal Bandwidth (kHz) | 8               |       |       |       |  |

| Die Size (core area)   | 570-μm × 690-μm |       |       |       |  |

TABLE II. PERFORMANCE COMPARISON OF THE ANALOG FRONT-END

|                        | JSSC<br>1997 [2] | JSSC<br>2002 [3] | This<br>work |

|------------------------|------------------|------------------|--------------|

| Supply Voltage (V)     | 2.15             | 1.1              | 0.9          |

| Peak SNR (dB)          | 77               | 92               | 86           |

| Power Consumption (µW) | 323              | 190              | 67 (avg.)    |

| CMOS Technology        | 0.8-µm           | 0.6-µm           | 0.25-μm      |

# V. CONCLUSION

A new analog front-end is designed and realized in a 0.25- $\mu$ m standard CMOS process for a digital hearing aid. By exploiting CGC and adaptive-SNR technique, the proposed analog front-end reduces power consumption and obtains large dynamic range. The proposed preamplifier consumes 35- $\mu$ W and 0.1-mm² area. The peak SNR of the  $\Sigma$ - $\Delta$  modulator is 86-dB and average power consumption is 31.4- $\mu$ W with 0.4-mm² core area. The SNR varies over 14-dB range and power consumption changes 11.5- $\mu$ W from type 1 to type 4. The proposed analog front-end dissipates less than 67- $\mu$ W from a single 0.9-V supply.

# **ACKNOWLEDGEMENTS**

The authors would like to thank Youchul Jeong at KAIST for fabrication of the PCB.

# REFERENCES

- [1] Vincenzo Peluso, et al., "A 900-mV Low-Power ΣΔ A/D Converter with 77-dB Dynamic Range," *IEEE J. Solid-state Circuits*, vol. 33, No. 12, pp. 1887-1897, Dec. 1998.

- [2] Harry Neuteboom, Ben M. J. Kup, and Mark Janssens, "A DSP-Based Hearing Instrument IC," *IEEE J. Solid-state Circuits*, vol. 32, No. 11, pp. 1790-1806, Nov. 1997.

- [3] D. George Gata, et al., "A 1.1-V 270-μA Mixed-Signal Hearing Aid Chip," *IEEE J. Solid-state Circuits*, vol. 37, No. 12, pp. 1670-1678, Dec. 2002

- [4] Dave Moulton, et al., : About the Loudness of Sounds and the Risk of Hearing Damage, 1993. http://www.moultonlabs.com

- [5] Roubik Gregorian, and Gabor C. Temes, Analog MOS Integrated Circuits, John Wiley & Son, 1986, Ch.5.

- [6] Yves Geerts, and Michiel Steyaert, *Design of multi-bit delta-sigma A/D Converters*, Kluwer academic publishers, 2002, Ch.2

- [7] Shahriar Rabii, and Bruce A. Wooley, "A 1.8-V digital-audio sigmadelta modulator in 0.8-μm CMOS," *IEEE J. Solid-state Circuits*, vol. 32, No. 6, pp. 783-796, June. 1997.

- [8] Sung-Eun Kim, Seong-Jun Song, Jin Kyung Kim, Sunyoung Kim, Jae-Youl Lee, and Hoi-Jun Yoo, "A small ripple regulated charge pump with automatic pumping control schemes," in *Proc. Eur. Solid State Circuits Conf.*, Sept. 2004, pp. 383-386.