# Limits to a Correct Operation in RTD-based Ternary Inverters

Juan Núñez, José M. Quintana and María J. Avedillo

Instituto de Microelectrónica de Sevilla, Centro Nacional de Microelectrónica, Consejo Superior de Investigaciones Científicas (CSIC) and Universidad de Sevilla

Edificio CICA, Avda. Reina Mercedes s/n, 41012-Sevilla, SPAIN FAX: +34-955056686, E-mail: {jnunez, josem, avedillo}@imse.cnm.es

Abstract— Multiple-valued Logic (MVL) circuits are one of the most attractive applications of the Monostable-to-Multistable transition Logic (MML), and they are on the basis of advanced circuits for communications. However, a proper design is not inherent to the usual MML circuit topologies. This paper analyses the case of an MML ternary inverter, and determines the relations that circuit representative parameters must verify to obtain a correct behaviour.

#### I. INTRODUCTION

Resonant tunnelling devices are today considered the most mature type of quantum-effect devices, already operating at room temperature, and being promising candidates for future nanoscale integration. Resonant tunnelling diodes (RTDs) use to be implemented in III-V materials, and they exhibit a negative differential resistance (NDR) region in their current-voltage characteristics which can be exploited to significantly increase the functionality implemented by a single gate in comparison to MOS and bipolar technologies [1].

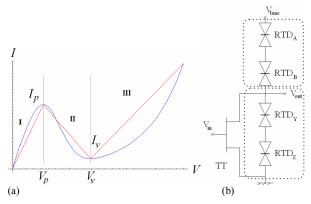

Figure 1a shows the I-V characteristic of an RTD enhancing key parameters for circuit design: peak current and voltage,  $I_p$  and  $V_{p_2}$  and valley current and voltage,  $I_{\nu}$  and  $V_{\nu}$ . Three regions are defined according to Fig. 1a: two regions of positive (I and III) and one of negative (II) differential resistance. Circuit applications of RTDs are mainly based on the MOnostable-BIstable Logic Element (MOBILE) [2-4]. The basic MOBILE is a rising edge triggered current controlled gate which consists of two RTDs (the load and driver RTDs) connected in series and driven by a switching bias voltage ( $V_{bias}$ ). When connected in series, RTDs provide multiple-peak structures in their I-V characteristics, which make it attractive for multiple-valued logic (MVL). MVL circuit applications are based on the Monostable-to-Multistable transition Logic (MML) [5], an extension of the binary MOBILE. Logic operation is based on the sequential switching of the RTDs connected in series, which is produced when the bias voltage rises to an appropriate value. Logic functionality is achieved by embedding an input stage (compound-semiconductor transistors, HEMT or HBT) which modifies, according the applied input signal, the peak current of some of the RTDs. MML circuits have been mainly applied in communication systems, where their high-speed performance is expected to be of the most importance for future commercial applications [6], [7].

Figure 1. (a) I-V characteristic for a LOCOM RTD (blue) and its linear approach (red) and (b) typical structure of a MML ternary inverter.

In this paper DC operation of a key MML circuit, the ternary-valued inverter has been studied. Our analysis shows that a correct DC operation is not an inherent property to the circuit topology, being its careful design a main concern. To analytically study the problem we have resorted to piecewise linear descriptions for the RTD driving point characteristics, which allows obtaining relations between RTD and transistor parameters that ensure a correct behaviour of the structure. The paper is organized as follows: Section II deals with the operation principle of RTD-based ternary inverters. The importance of a correct sizing of the parameters of the structure as well as the relationships between them to ensure a proper behaviour are analyzed in Section III and Section IV respectively. Simulation results are shown in Section V. Finally, some conclusions are given.

#### II. OPERATION PRINCIPLE

The piecewise linear model we have used for the RTDs has been derived from real RTDs fabricated in the LOCOM [8] fabrication process. Fig. 1a shows the piecewise linear model we are using. Peak and valley currents as well as peak and valley voltages have been selected from the LOCOM RTDs. For this RTD,  $V_p$  is 0.21V, the peak current density 21 KA/cm², and the peak current ratio is about 6.25 at room temperature. The transistor is a depletion HFET with threshold voltage -0.2V.

Thus, current through the RTD is given by

$$\begin{cases} f m_{I} V & V \leq V_{p} \\ f (m_{II} (V - V_{v}) + I_{v}) & V_{p} \leq V \leq V_{v} \\ f (m_{II} (V - V_{v}) + I_{v}) & V \geq V_{v} \end{cases}$$

(1)

where V is the voltage applied to the RTD and f the area factor<sup>1</sup>.

Figure 1b depicts a typical structure of a ternary inverter based on MML. Two negative differential resistance (NDR) devices can be identified: the driver and the load NDRs. The driver consists of a HFET (TT) and two series RTDs (RTD<sub>Y</sub> and RTD<sub>Z</sub>). The HFET provides the logic functionality as its input modulates the drain to source current of the transistor, and consequently the total current through the driver. For this structure, three feasible values of the  $V_{in}$  are considered, the high  $(V_{in}^H)$ , medium  $(V_{in}^M)$  and low  $(V_{in}^L)$  voltages, associated with the logical 2, I and 0 respectively. The load is made up of the series connection of RTD<sub>A</sub> and RTD<sub>B</sub>.

A correct evaluation of the input is determined by the relation between the peak currents of the driver and the load. If the input is at a high level,  $V_{in} = V_{in}^H$ , (ternary logic level "2"), the output must be at logic level "0". When logic level "1" ( $V_{in} = V_{in}^M$ ) the output must also be "1". Finally, for the lowest level of the input ( $V_{in}^L$ ), the output has to reach its highest value (level "2"). RTDs are supposed to have equal current densities so that peak currents are proportional to RTD areas. A proper operation is achieved if, additionally, the output node maintains its value for  $V_{bias}$  high even if the input changes. Thus, the multistability property is guaranteed.

A first approach to the operation of the structure is given by the analysis of the switching sequence of the RTDs: the first to switch is that with the smallest area factor. This approach is not efficient since it is difficult to add the effect of the transistor. This problem can be efficiently approached by considering that both NDRs (the load, NDR<sub>L</sub>, and the driver, NDR<sub>D</sub>) are composed of two RTDs each one, and thus, they present a driving point characteristic with two peaks and two valleys. Based on simple geometrical considerations it is possible to analytically obtain the joint I-V characteristic for two series-connected RTDs. Two generic piecewise linear series-connected RTDs, RTD<sub>1</sub> and RTD<sub>2</sub>, with area factors  $f_1$  and  $f_2$  respectively ( $f_1 > f_2$ ) are considered. The new joint I-V characteristic has two peak and two valley voltages (and currents) dependent on the values of  $f_1$  and  $f_2$ . The first peak and the first valley are due to the RTD which area factor is smaller, whereas the second peak and valley are caused by the other RTD [9].

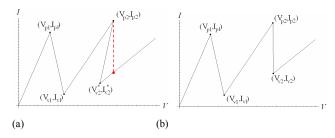

The joint *I-V* characteristic obtained is shown in Fig. 2a. It is easy to prove that for this representation, the second valley voltage is always below the second peak voltage. In order to handle well-defined functions, we have made  $V_{v2}^{f_1,f_2} = V_{p2}^{f_1,f_2}$  (thus the second valley current has been changed as the red dotted line in Fig. 2a indicates), so that the resulting characteristic is depicted in Fig. 2b.

#### III. CORRECT SIZING OF THE STRUCTURE

DC operation of the ternary inverter is obtained by applying the Kirchoff Laws to the circuit in Fig. 1b, i.e., current through NDR<sub>L</sub> must be equal to current through NDR<sub>D</sub>. Thus,

Figure 2. (a) Real *I-V* characteristic of two series connected RTDs and (b) joint *I-V* representation after changing the position of the second peak voltage.

$$g_{L}[V_{bias} - V_{out}] = g_{D}[V_{out}] + I_{DS}[V_{in}, V_{out}]$$

(2)

where g[v] and  $I_{DS}[V_{GS}, V_{DS}]$  represent the mathematical description of the driving point characteristic of two series connected linear RTDs  $(g_D[v]$  for the driver and  $g_L[v]$  for the load) and the transistor, respectively.

Two problems related to a correct sizing of the structure can be pointed out. The first one is the evaluation problem, which occurs when the modulation of the effective peak current through transistor TT is not enough for the output to invert the input  $V_{in}$ , for  $V_{bias}$  high. The second problem is the multistability lack, which occurs when a variation of the input forces a change of the output logic level. Next, both problems will be analyzed.

### A. The evaluation problem

Due to the existence of two peaks in the I-V characteristic of both NDR<sub>D</sub> and NDR<sub>L</sub>, the operation of the ternary inverter shows two "transitions". The relation between the peak currents of the driver and the load during the evaluation phase will determine the final value of the output voltage. Once we know which RTD has the stronger influence in each peak and valley of the joint I-V characteristic, it is possible to make several suppositions about the order in which RTDs commute depending on the value of the input (usually RTD areas fulfil the relation  $A_i$ - $A_B$ - $A_I$ - $A_Z$  [5]).

When  $V_{in} = V_{in}^L$  the following relationship between the peak currents  $I_{p1}^{fz,f_Y} < I_{p2}^{fz,f_Y} < I_{p1}^{f_B,f_A} < I_{p2}^{f_B,f_A}$  is verified. According to Section 3, both transitions are due to the RTDs belonging to NDR<sub>D</sub>. In a similar way, when  $V_{in} = V_{in}^H$ , the peak currents verify  $I_{p1}^{f_B,f_A} < I_{p2}^{f_B,f_A} < I_{p1}^{fz,f_Y} < I_{p2}^{fz,f_Y} < I_{p2}^{fz,f_Y}$ , that is, the first and the second transition are due to the RTDs of NDR<sub>L</sub> (RTD<sub>B</sub> and RTD<sub>A</sub>). Finally, for  $V_{in} = V_{in}^M$  two possibilities have been found to reach a 'medium' logical level of the output: if  $I_{p1}^{fz,f_Y} < I_{p1}^{f_B,f_A} < I_{p2}^{fz,f_Y} < I_{p2}^{f_B,f_A}$ , RTD<sub>Z</sub> commutes before RTD<sub>B</sub>, whereas if  $I_{p1}^{f_B,f_A} < I_{p1}^{fz,f_Y} < I_{p2}^{f_B,f_A} < I_{p2}^{fz,f_Y} < I_{p2}^{f_B,f_A} < I_{p2}^{fz,f_Y} < I_{p2}^{fz,f_Y}$ , RTD<sub>B</sub> does it firstly.

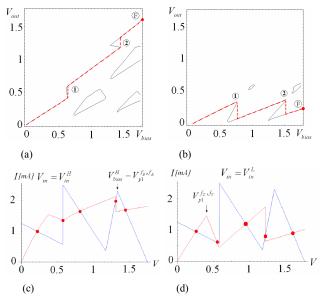

A very useful way of understanding how  $V_{out}$  evaluates when  $V_{bias}$  increases its value from 0 to  $V_{bias}^H$  for a fixed input value is a DC plot of the solutions to (2). Figures 3a and 3b depicts this plot in the  $V_{bias}$ - $V_{out}$  plane for  $V_{in}$ = $V_{in}^L$  and  $V_{in}$ = $V_{in}^H$  respectively, where the red dashed line represents the real operation of the ternary inverter. Marks "1" and "2" point out the transitions due to switching RTD<sub>Z</sub> and RTD<sub>Y</sub> respectively and "F" the final value of  $V_{out}$  when  $V_{bias}$ = $V_{bias}^H$ .

<sup>&</sup>lt;sup>1</sup> In this work all RTDs are supposed to have equal current densities, thus, peak and valley currents are proportional to f. An area factor of 1 corresponds to a RTD of area  $10\mu\text{m}^2$ .

### The multistability dissapearance problem

This problem comes from the disappearance of one (or more) of the stable states in the DC solution representation when  $V_{\it bias} = V_{\it bias}^H$  . Let us consider the disappearance of the highest output level when the input voltage increases its value to  $V_{in}=V_{in}^H$ . This malfunction appears when NDR<sub>L</sub> is biased about its first peak voltage (RTD<sub>B</sub> is in its peak and commutes, forcing a change in the output node), thus,  $V_{out}$  is approximately  $V_{bias}^H - V_{p1}^{f_B, f_A}$ . Figure 3c depicts the load curve for a properly-sized MML inverter, in which the five solutions found have been marked in red. Let us consider the case in which the input is fixed at its low value. A malfunction is found around  $V_{out} \cong V_{p1}^{f_Z,f_Y}$  when  $V_{in} = V_{in}^{L}$ , which happens when RTD<sub>Z</sub> reaches its peak voltage, increasing the value of the output node. In order to find solutions to Eq. (2) around  $V_{out} \cong V_{p1}^{f_Y,f_Z}$  it is mandatory that the first peak current of NDR<sub>D</sub> is above the current of NDR<sub>L</sub> when it is biased with a voltage equal to  $V_{bias}^H - V_{p1}^{f_Y, f_Z}$  (see Fig. 3*d*).

# IV. CRITICAL DEPENDENCIES

Once the mechanisms to analyze both malfunctions have been studied, the relationships between circuit parameters to guarantee a correct DC operation will be obtained.

## A. Evaluation constraints

Let us begin with the evaluation for  $V_{in}=V_{in}^{L}$ . In this situation, the first transition is due to RTDz, thus we must ensure that the first peak current of the driver is less than the first peak current of the load. In this way, the RTD with smallest area of the driver (RTD<sub>7</sub>) always commutes before the smallest RTD of the load (RTD<sub>B</sub>). The critical situation in which both the first peak current of NDR<sub>D</sub> and NDR<sub>L</sub> are equal is shown

Figure 3. (a)-(b)  $V_{bias}$ - $V_{out}$  plots pointing out the first ("1") and the second ("2") transition and the final value of  $V_{out}$  ("F") when  $V_{in} = V_{in}^L$ ,  $V_{in} = V_{in}^R$ respectively. Load curves marking the solutions to Eq. (2) in red, for (c)  $V_{in} = V_{in}^H$  and (d),  $V_{in} = V_{in}^L$ .

in Figures 4a. Thus, the first relation between parameters comes from:

$$f_{Z}I_{p} + FF \cdot I_{DS} \left[ V_{in}^{L}, V_{p1}(f_{Z}, f_{Y}) \right] < f_{B}I_{p}$$

(3)

According to the previous Section, RTD<sub>Y</sub> is the second RTD to commute, so that second peak current of the driver must be less than the first peak current of the load (which is originated by the smallest RTD of the load, that is, RTD<sub>B</sub>). The limit case in which the first peak current of NDR<sub>I</sub> coincides with the second peak current of NDR<sub>D</sub> is depicted in Fig. 4b. According to this, a new expression for a minimum value of FF is derived,

$$f_{Y}I_{p} + FF \cdot I_{DS} \left[ V_{in}^{L}, V_{p2}(f_{Z}, f_{Y}) \right] < f_{B}I_{p}$$

$$\tag{4}$$

When  $V_{\it in}$ = $V_{\it in}^{\it M}$ , the sequence of commutation of RTD<sub>Z</sub> and RTD<sub>B</sub> is determined by the relationship between the smallest peak currents of the driver and the load. When RTDz is the first to commute, two constraints can be derived concerning to the first and the second transition respectively,

$$\begin{aligned} f_{Z}I_{p} + FF \cdot I_{DS} \left[ V_{in}^{M}, V_{p1}(f_{Z}, f_{Y}) \right] < f_{B}I_{p} \\ f_{Y}I_{p} + FF \cdot I_{DS} \left[ V_{in}^{M}, V_{p2}(f_{Z}, f_{Y}) \right] > f_{B}I_{p} \end{aligned} \tag{5}$$

$$f_{Y}I_{p} + FF \cdot I_{DS} \left[ V_{in}^{M}, V_{p2}(f_{Z}, f_{Y}) \right] > f_{B}I_{p}$$

(6)

On the other hand, when RTD<sub>B</sub> commutes firstly,

$$f_{Z}I_{p} + FF \cdot I_{DS} \left[ V_{in}^{M}, V_{p1}(f_{Z}, f_{Y}) \right] > f_{B}I_{p}$$

$$f_{Z}I_{p} + FF \cdot I_{DS} \left[ V_{in}^{M}, V_{p1}(f_{Z}, f_{Y}) \right] < f_{A}I_{p}$$

(8)

$$f_{Z}I_{p} + FF \cdot I_{DS}[V_{in}^{M}, V_{p1}(f_{Z}, f_{Y})] < f_{A}I_{p}$$

(8)

For the highest value of the input voltage,  $V_{in} = V_{in}^H$ , the first transition happens when RTD<sub>B</sub> commutes, thus,

$$f_{Z}I_{p} + FF \cdot I_{DS} \left[ V_{in}^{H}, V_{p1}(f_{Z}, f_{Y}) \right] > f_{B}I_{p}$$

$$(9)$$

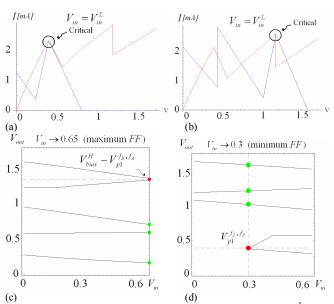

Figure 4. Critical situations for the evaluation problem when  $V_{in} = V_{in}^{L}$  for (a) first and (c) second transition.  $V_{in}$ - $V_{out}$  plots pointing out the critical (in red) solutions to Eq. (2) when (c)  $V_{in} = V_{in}^H$ , (d)  $V_{in} = V_{in}^L$ .

Finally, to ensure that the next RTD to commute is RTD<sub>A</sub>, the second peak current of the load has to be less than the first peak current of the driver,

$$f_{Z}I_{p} + FF \cdot I_{DS} [V_{in}^{H}, V_{p1}(f_{Z}, f_{Y})] > f_{A}I_{p}$$

(10)

# B. Multistability constraints

Two new restrictions to the feasible set of values of the circuit parameters can be derived through the analysis performed in Section III. Figure 4c depicts a  $V_{in}$ - $V_{out}$  plot for  $V_{in}$  increasing from  $V_{in}^L$  to  $V_{in}^H$ , where the intersections with the left ordinate axis correspond to feasible solutions to Eq. (2) for the high value of the input. Upper point (in red) corresponds to a double solution to Eq. (2) and indicates the critical situation for which higher values of FF would entail an incorrect behaviour. Thus, an expression of a maximum value of FF is obtained,

$$g_{D}[V_{bias}^{H} - (V_{p1})_{L}] + FF \cdot I_{DS}[V_{in}^{H}, V_{bias}^{H} - V_{p1}(f_{B}, f_{A})] < f_{B}I_{p}$$

(11)

When  $V_{in}$  decreases from  $V_{in}^H$  to  $V_{in}^L$ , the decision is taken around  $V_{out} \cong V_{p1}^{f_Z,f_Y}$  (the red point in Fig. 4d) and must guarantee that the peak current of the driver is under the current of the load. Thus,

$$f_{Z}I_{p} + FF \cdot I_{DS} \left[ V_{in}^{L}, V_{p1}(f_{Z}, f_{Y}) \right] > g_{L} \left[ V_{bias}^{H} - V_{p1}(f_{Z}, f_{Y}) \right]$$

(12)

### V. SIMULATION RESULTS

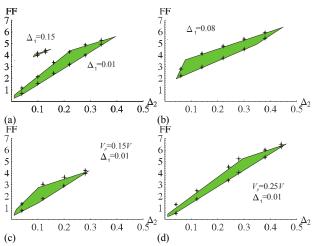

In order to check our approach we have performed a comparison between our theorical approach and HSPICE simulation. Expressions (3-12) have been employed to analyze how the DC operation of a ternary inverter is modified when some key parameters are changed. HFET and typical parameters for the RTDs from the LOCOM technology have been used. Figure 5 shows the set of feasible values of FF (those which allow a correct evaluation and multistability preserving operation) obtained by varying  $\Delta_1$  (the difference between  $f_Z$  and  $f_Y$  and  $f_B$  and  $f_A$ ), and  $\Delta_2 = f_{B} - f_Y$ , when  $f_Z = 0.6$ . The first pair of plots depict the feasible pairs  $(\Delta_2,FF)$  for different values of  $\Delta_1$  (0 and 0.15 in Fig. 5a and 0.08 in Fig. 5b). The green area corresponds to the region of feasible FF that has been derived theorically through (3-12). The black points represent the points obtained after performing HSPICE simulations. It can be observed the shrinking of the feasible region. For  $\Delta_1 > 0.15$  there are no inverters with a proper behaviour. A very close correspondence between both theoretical and simulation results can be also observed. In Figures 5c and 5d the effect of a variation of the peak voltage is analyzed. Feasible pairs ( $\Delta_2$ , FF) for  $V_p$ =0.15 (Fig. 5c) and  $V_p$ =0.25 (Fig. 5d), show that the area of the correct operation region is increased when  $V_p$  does.

# VI. CONCLUSIONS

A proper DC operation of MML circuits is not an inherent property to the circuit topology. Starting from a MML ternary inverter, two basic problems to size the inverter have been pointed: the evaluation fault and the multistability lack. To analytically study the problem, piecewise linear descriptions for the RTD driving point characteristics have been used. A procedure to calculate the relationships between circuit parameters in order to obtain correct DC operating regions has been derived.

Figure 5. Set of feasible of values of FF vs  $\Delta_2 = f_B - f_Y$  for  $\Delta_1 = f_A - f_B = f_Y - f_Z$  = {0.01 and 0.15 (a), 0.08 (b) with  $f_Z$ =0.6}, marking in green the area derived through (3-12) and with the black points, the region obtained after performing HSPICE simulations with piecewise linear RTDs. (c)-(d) Region of correct DC after changing the value of the peak voltage to (c)  $V_p$ =0.15, (d)  $V_p$ =0.25.

#### ACKNOWLEDGMENT

This work has been funded by the Spanish Government under project NDR, TEC2007-67245/MIC, and the Junta de Andalucía through the Provectos de Excelencia TIC-927 and TIC-2961.

#### REFERENCES

- P. Mazumder, S. Kulkarni, M. Bhattacharya, J.-P. Sun, and G.I. Haddad, "Digital circuit applications of resonant tunneling devices," *Proc. IEEE*, vol. 86, pp. 664-686, Apr. 1998.

- [2] T. Akeyoshi, K. Maezawa, and T. Mizutani, "Weighted sum threshold logic operation of MOBILE's (monostable-bistable transition logic element) using resonant-tunnelling transistors," *IEEE Electron Device Lett.*, vol. 14, pp. 475–477, 1993.

- [3] K.J. Chen, T. Akeyoshi, K. Maezawa, "Monolithic integration of resonant tunnelling diodes and FETs for monostable-bistable transition logic elements (MOBILEs)", *IEEE Electronic Device Letters*, vol. 16, pp. 70-73, 1995.

- [4] Christian Pacha, et al.: "Threshold Logic Circuit Design of Parallel Adders Using Resonant Tunneling Devices". IEEE Transaction on Very Large Scale Integration (VLSI) Systems, Vol 8, no. 5, October 2000, pp. 558-572.

- [5] T. Waho, Kevin J. Chen and M. Yamamoto: "Resonant-Tunneling Diode and HEMT Logic Circuits with Multiple Thresholds and Multilevel Output", *IEEE Journal of Solid-state Circuits*, Vol 33, No. 2, pp. 268 – 274, February 1998.

- [6] M. Chibashi, K. Eguchi and T. Waho: "A novel delta-sigma modulator using resonant tunnelling quantizers", IEEE Proceedings of the 2004 International Symposium on Circuits and Systems (ISCAS'04), Vol 1, No. 1, pp. 533-536, 2004.

- [7] K. Eguchi, M. Chibashi and T. Waho: "A design of 10-GHz deltasigma modulator using a 4-level differential resonant-tunneling quantizer", *IEEE Proceedings on Multiple-Value Logic (ISMVL'05)*, pp 43-47, May 2005.

- [8] W. Prost et al.: EU IST Report LOCOM no. 28 844 Dec. 2000.

- [9] K.-J. Gan, Y-K. Su: "Modeling Current-Voltage and Hysteretic Current-Voltage Characteristics with Two Resonant Tunneling Diodes Connected in Series". Solid State Electronics, Vol. 41, No. 12, pp. 1917-1922, Dec. 1997.