# On-chip Biased Voltage-Controlled Oscillator with Temperature Compensation of the Oscillation Amplitude for Robust I/Q Generation

A. J. Ginés, R. Doldán, M. J. Barragán, A. Rueda and E. Peralías Instituto de Microelectrónica de Sevilla, CNM-CSIC, University of Seville Seville, Spain

Emails: { gines, rdoldan, manuelj, rueda, peralias}@imse.cnm.es

Abstract— In this work a CMOS 1.2V 5GHz low-power voltage-controlled oscillator (VCO) is proposed. It uses an on-chip biased LC-tank topology and introduces a temperature compensation technique which stabilizes the oscillation amplitude for a robust I/Q generation using a frequency divider-by-2. Compared to a standard design with constant bias, it reduces the oscillation variation by almost two orders of magnitude between 0°C and 100°C with negligible impact on the phase noise. Worst case estimations of the VCO phase noise after layout parasitic extraction are -110.1dBc/Hz and -126.6dBc/Hz at 1MHz and 5MHz offsets from the carrier, respectively. Its nominal current consumption is 198μA (plus 22.5μA for biasing) and it occupies 370x530μm².

### I. Introduction

The requirements of the VCOs in modern radio frequency (RF) applications are usually characterized at the system level by the phase noise and power consumption. In general it is assumed that the lower the phase noise is, the higher the power consumption. Although this trade-off becomes the dominant factor for defining the VCO total power in low phase-noise communication standards (e.g. GSM which needs –125.4dBc/Hz at 1MHz from the carrier), it is not strictly true for moderate and high phase-noise standards such as Bluetooth or ZigBee [1] (–114.4dBc/Hz and –72.0dBc/Hz at 1MHz, respectively). Actually, in these last cases with relaxed noise requirements, the trade-off between power consumption and the needed VCO oscillation amplitude (A<sub>osc</sub>) becomes dominant, as the following equation shows,

$$Power \approx I_{tank} \cdot Vdd \quad ; \quad A_{osc} = I_{tank} \cdot R_{tank}$$

(1)

where for a LC-VCO topology in the limited-current regime,  $I_{\text{tank}}$  can be particularized as the current through the tank,  $R_{\text{tank}}$  is its equivalent parallel resistance and Vdd is the power supply voltage.

In a traditional implementation the amplitude  $A_{osc}$ , and therefore, according to (1), the power consumption, are usua-

lly controlled by a constant current reference  $I_{\text{bias}} = I_{\text{tank}}/M$ . The particular value of  $I_{\text{bias}}$  must be determined according to the worst process and environmental operation conditions. Hence, this approach could lead to a non-optimal design in terms of power in the typical conditions.

Among the different contributions to the VCO performance degradation, the temperature is specially critical due to its great impact on the oscillation amplitude. In this context, an on-chip biased VCO with robust temperature compensation of the oscillation amplitude Aosc is presented in this paper. We will show how the use of a non-constant bias current with proper temperature dependence allows an important reduction of power consumption (when compared to the constant bias case). In addition, the on-chip reference generation overcomes the classical drawbacks associated to the external current reference generation at the printed-circuit board (PCB) level. Some of the on-chip generation advantages are: 1) it reduces the PCB cost, 2) it eliminates an additional pin for exciting the VCO, thus also reducing the package cost, and 3) it simplifies the blocking ladder design at the bias branch.

The proposed VCO with temperature compensation of the oscillation amplitude has been integrated in a 90nm RF CMOS process. The VCO has a centre frequency of 4.9GHz with a 10% tuning range from 4.65GHz to 5.15GHz. The prototype also includes a divider-by-2 (DIV2) as active load of the VCO for a robust generation of I/Q components in the 2.4GHz unlicensed ISM band. The VCO-DIV2 system fulfills the oscillator requirements for frequency synthesizers in the ZigBee standard. The included on-chip low-power bias current generator (BCG) exhibits a proportional-to-absolute temperature (PTAT) behavior which compensates the Aosc decrement when temperature increases. Its worst case power consumption and occupied die are just 16.3µW and 25x25µm<sup>2</sup>, respectively. Compared to a standard design with constant bias, the proposed method reduces the Aosc variation up to two orders of magnitude with negligible impact on the phase noise. This

This work has been partially supported by the SR2- Short Range Ratio Catrene European Project and the Spanish TIC-927 Junta de Andalucía and TEC2007-68072 projects.

effect allows reducing the nominal power consumption a 14%, while maintaining a correct operation beyond 125°C (for the classical constant current reference approach, the operation fails above 100°C).

The paper is organized as follows. In Sect.II, the design of a CMOS 1.2V LC-VCO topology with classical constant current reference is described. This case of study illustrates the VCO problems for driving an active load, such as a frequency divider, for high temperatures. Section III presents the description of the self-biased current generator with emphasis on the PTAT behavior. It also introduces the selected implementation and its start-up circuit. Finally, the VCO with temperature compensated amplitude and the conclusions are shown in Sect.IV and Sect.V, respectively.

# II. CLASSICAL LC-VCO WITH CONSTANT BIAS

In the previous section the closed relationship between power consumption and oscillation amplitude  $A_{\rm osc}$  has been shown. In what follows, we will assume that the actual value of  $A_{\rm osc}$  is the amplitude which guarantees a correct operation of the circuit at the output of the VCO. Notice that  $A_{\rm osc}$  should be not confused with the minimum amplitude  $A_{\rm osc}^{\rm min}$  required to maintain a robust oscillation against process and environment variations, which can be estimated according to the effective transconductance and saturation voltage of the VCO active section  $(g_m, v_{\rm dsat})$ , as follows,

$$A_{osc}^{\min} \approx I_{tank}^{\min} R_{tank} \approx (g_m v_{dsat})^{\min} R_{tank} = (\alpha v_{dsat})^{\min}$$

(2)

where the parameter  $\alpha$ , usually  $\alpha \in [2,3]$ , comes from the oscillation condition [2], and defines the ratio between  $g_m$  and the tank conductance,

$$g_m = \frac{\alpha}{R_{\text{tank}}} \tag{3}$$

Actually, in most practical cases for moderate and high phase-noise standards, the actual oscillation amplitude  $A_{\rm osc}$  could be significantly greater than  $A_{\rm osc}^{\rm min}$ . In other words, the current delivered to the tank, or equivalently the power consumption is fundamentally determined by the VCO load, instead of the oscillation condition given by (3). As an example, in our particular case of the study with a VCO followed by a frequency divider-by-2 (DIV2), the VCO power is basically defined by the particular divider realization instead of other target specifications, such phase noise or  $A_{\rm osc}^{\rm min}$ .

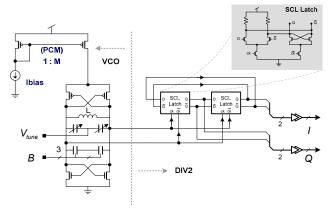

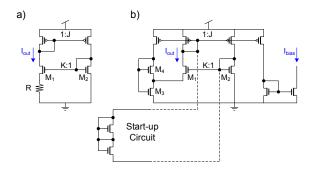

Figure 1 depicts a simplified schematic of the VCO and DIV2 system using a constant polarization current ( $I_{bias}$ ). For an easy comparison with the implementation that will be shown in Sec. IV, a common design of these blocks has been considered through the paper. Here we focus on the VCO-DIV2 characteristics when is constantly biased. The VCO uses a LC-tank with complementary cross-coupled active negative resistances and PMOS current mirror (PCM).

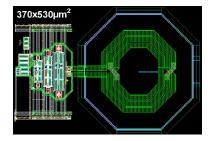

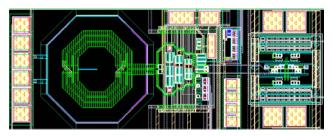

Figure 2 shows the layout of the LC-VCO (approximately  $370x530\mu m^2$ ). This block has an average current consumption of  $220\mu A$  (plus  $25\mu A$  for the  $I_{bias}$ ), a sensitivity of 250MHz/V and centre frequency of 4.9GHz. The inductor, which considers a symmetrical layout for better matching, has a

Figure 1. Simplified schematic of the LC-VCO with details of the active load in the case study (frequency divider-by-2).

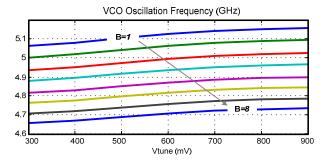

nominal value of 2.15nH with a quality factor of 22@5GHz. PMOS varactors in accumulation mode and nominal capacitance of 42fF (Q = 53 @5GHz) give a fine tuning of around 100MHz. An extra MiM (metal-metal) capacitor array controlled by a 3-bit signal **B** provides an additional coarse tuning (up to 500MHz) for dealing with process and environment changes, as the post-layout simulation results after parasitic extraction in Fig. 3 show.

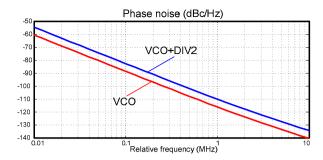

The frequency divider-by-2 (DIV2) considers two source-coupled (SCL) latches in a feedback configuration [3]. Each of the SCL latch drives in the worst case conditions  $450\mu A$  from a dedicated pad power supply to reduce noise coupling to the VCO. The contribution of the frequency divider to total phase noise of the I/Q components (-110.1dBc/Hz and -126.6dBc/Hz at 1MHz and 5MH, respectively) can be neglected as it is fundamentally dominated by the VCO. After the SCL latches, two inverters reconstruct the logical levels, control the load matching and provide isolation. With a custom optimized design and dedicated layout, this topology has proven applica-

Figure 2. VCO layout with symmetrical inductor.

Figure 3. Fine and coarse tuning of the integrated VCO after layout parasitic extraction.

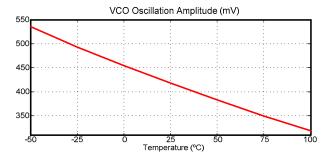

Figure 4. Temperature effect on the VCO oscillation amplitude  $A_{\rm osc}$  after layout parasitic extraction.

bility for low-power design in current deep-submicrometer technologies [4]. However, the topology could be very sensitive to the VCO oscillation amplitude variations when temperature increases.

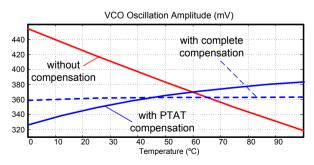

Figure 4 shows the temperature effect on the VCO oscillation amplitude  $A_{\rm osc}$  in the typical conditions with layout parasitics. Notice that  $A_{\rm osc}$  experiments a variation greater than 140mV from 0°C to 100°C, which could negatively affect to the functionality of the VCO load. Actually, in our particular case of study the operation of the DIV2 considering the worst process parameter (slow-pmos slow-nmos) fails above 100°C due to the significant reduction of  $A_{\rm osc}$ .

The theoretical justification for the  $A_{osc}$  behavior can be explained considering the temperature dependence of the tank resistance  $R_{tank} = R_{tank}(T)$ . Rewriting (1) for a fixed output bias current  $I_{bias} = I_{tank}/M$ , it is obtained,

$$A_{\text{asc}}(T) = I_{\text{tank}} \cdot R_{\text{tank}}(T) \tag{4}$$

where  $R_{tank}(T)$  can be particularized for the considered LC-VCO topology, in the form [2],

$$R_{tank}(T) = 2 \cdot \left( R_{active}(T) // R_{var} // R_{MiM} \right) // R_{ind}$$

(5)

as a function of the effective resistances of: active cross-coupled pairs ( $R_{active}$ ), varactors ( $R_{var}$ ), MiM capacitor array ( $R_{MiM}$ ) and inductor ( $R_{ind}$ ). In this expression, the dominant contribution in terms of temperature comes from the active section  $R_{active}(T)$ . This term experiments a negative PTAT (NTAT) behavior (directly translated to  $A_{osc}$ ) due to the conductance increment at high temperatures as more free charge carriers are available in a semiconductor [5].

# III. ON-CHIP PTAT CURRENT REFERENCE

The principle of the proposed temperature compensation for the oscillation amplitude  $A_{\rm osc}$  is quite simple. It considers an on-chip PTAT current reference generator (CRG) which corrects the  $R_{\rm tank}(T)$  dependence on temperature due to active section contribution,

$$A_{osc} = M \cdot I_{bias}^{NTAP}(T) \cdot R_{tank}^{PTAP}(T) \approx \text{constant}$$

(6)

The selected CRG scheme (which substitutes the  $I_{\text{bias}}$  in Fig.1) is based on the traditional self-biased current reference depicted in Fig.5a. This topology generates a nominal current which is approximately defined by the transistors aspect ratios and the resistor R. In order to achieve the wanted PTAT

response, the coupled transistors  $M_{1-2}$  can be polarized in weak-inversion [6]-[8]. Actually, taking into account that,

$$V_{GS2} = V_{GS1} + I_{out} \cdot R \tag{7}$$

and that the transistor current expression in weak inversion for a given geometric aspect (W/L) and current density I<sub>o</sub> is,

$$I_D = \frac{W}{L} \cdot I_o \cdot e^{-V_{GS}/\phi_T} \quad ; \quad \phi_T = \kappa \cdot T \tag{8}$$

the output current (Iout) is obtained,

$$I_{out} = T / R \cdot (\kappa \cdot \ln(JK))$$

(9)

where J is the current mirror factor, K is the transistor  $M_{1-2}$  aspect ratio and  $\kappa$  is a technological constant. Obviously, the final dependence of  $I_{out}$  on the temperature T should consider the particular implementation of the resistor R, specially in a full on-chip realization. Taking into account this contribution the wanted PTAT behavior can be easily achieved with a proper circuit scaling.

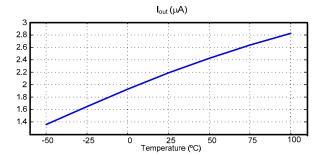

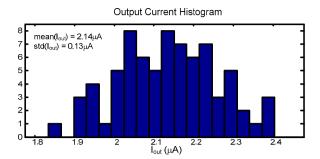

Fig.5b shows the final CRG implementation with PTAT response (see simulation of Fig.6 for details). In this architect-ture the resistor R is constructed by an active device  $M_3$ . This transistor is polarized in the ohmic region thanks to the series connection with  $M_4$  [6]. The CRG also considers: a) a simple start-up circuit to guarantee that the generator has the correct operation mode, b) an output programmable mirror which provides current selection flexibility, and c) an enable/disable circuit (omitted in the figure for simplicity) for power down the VCO. The total area and worst case power consumption of the generator core (excluding the output mirror) are  $25x25\mu m^2$

Figure 5. a) Traditional self-biased current reference; b) CRG generator with active internal resistance.

Figure 6. Simulation results of CRG showing the PTAT response of the output current  $I_{out}$ .

Figure 7. Output current histogram evaluated from a Monte-Carlo simulation with 100 runs.

and  $16.3\mu W$  (for a 1.2V voltage supply), respectively. The reference current has a nominal value of  $2.14\mu A$  with a standard deviation of  $0.13\mu A$  as the Monte-Carlo simulations of Fig.7 shows (# runs = 100).

# IV. PROPOSED VCO IMPLEMENTATION WITH TEMPERATURE COMPENSATION OF THE OSCILLATION AMPLITUDE

In this section the post-layout simulations for a temperature stabilized VCO-DIV2-CRG demonstrator are described. The prototype, which has been already fabricated in the TSMC CMOS 90nm RF process<sup>1</sup>, will be one of the main building blocks of a transceiver for domestic use compliant with the ZigBee standard. The target temperature range for this application is from 0°C to 100°C.

Figure 8 shows a comparison between the proposed and the classical constant biased VCOs. Two different designs with temperature compensation are considered. The dashed curve corresponds to an implementation with 10% power reduction and almost complete cancellation of the oscillation amplitude dependence on temperature. This design reduces the of A<sub>osc</sub> variation by almost two orders of magnitude between 0°C and 100°C (from 140mV to less than 5mV, respectively). In the second case of study, a VCO with PTAT amplitude behavior is considered to improve the DIV2 response at high temperatures. This effect allows reducing the nominal power consumption a 14%, while maintaining a correct operation beyond 120°C (for the classical constant current reference approach, the operation fails above 100°C). In both cases, the

Figure 8. Comparison between the classical constant biased VCO and the proposed temperature compensation designs.

Figure 9. Phase noise of the VCO with and without the frequency divider (DIV2) after layout parasitic extraction.

CRG has negligible impact on phase noise (see Fig.9). The final layout is depicted in Fig. 10. The total core area including decoupling capacitors and testing buffers is  $860x370\mu m^2$ .

### V. CONCLUSIONS

In this work a fully integrated 1.2V 5GHz VCO with temperature stabilization of the oscillation amplitude has been implemented in a 90nm CMOS process. The chip uses a low-power compact PTAT current cell which compensates the tank resistance temperature variations. The approach improves the oscillator robustness at high temperature allowing a significant reduction of the nominal power consumption.

### REFERENCES

- Low Rate Wireless Personal Area Networks, IEEE P802.15.4/D18, Oct. 2002.

- [2] R. Doldan et al., " A 5GHz Wide Tuning Range LC-VCO in Submicrometer CMOS Technology," *IEEE Asia Pacific Conf. on Circuits* and Systems, Dec.2008.

- [3] H. R. Rategh and T. H. Lee. Multi-GHz Frequency Synthesis & Division. Kluwer Academic Publishers (ISBN: 0-7923-7533-5), 2001.

- [4] A. J. Gines et al, "A 1.2V 5.14mW quadrature frequency synthesizer in 90nm CMOS technology for 2.4GHz ZigBee applications," *IEEE Asia Pacific Conf. on Circuits and Systems*, Dec.2008, pp.1252-1255.

- [5] Y. Tsividis. Operation and Modeling of the MOS Transistor. 2nd Edition, McGraw-Hill, New York, 1999.

- [6] F. Serra-Graells and J. L. Huertas, "Sub-1-V CMOS proportional-toabsolute temperature references," *IEEE Journal of Solid-State Circuits*, vol.38, no.1, Jan 2003, pp. 84-88.

- [7] P.H. Huang, H. Lin, Y.T. Lin, "A Simple Subthreshold CMOS Voltage Reference Circuit With Channel- Length Modulation Compensation," *IEEE Trans. on Cir. and Sys. II*, vol.53, no.9, Sept. 2006, pp.882-885.

- [8] E.M. Camacho-Galeano, C. Galup-Montoro, M.C. Schneider, "A 2-nW 1.1-V self-biased current reference in CMOS technology," *IEEE Trans. on Cir. and Sys. II*, vol.52, no.2, Feb. 2005, pp. 61-65.

Figure 10. Chip demonstrator layout.

<sup>&</sup>lt;sup>1</sup> The chip has been recently received and hopefully we will start obtaining experimental results by the end of the month.