Heidari, H., Navaraj, W., Toldi, G., and Dahiya, R. (2016) Device Modelling of Bendable MOS Transistors. In: IEEE International Symposium on Circuits and Systems (ISCAS), Montreal, Canada, 22-25 May 2016, pp. 1358-1361. ISBN 9781479953417

There may be differences between this version and the published version. You are advised to consult the publisher's version if you wish to cite from it.

http://eprints.gla.ac.uk/116636/

Deposited on: 22 August 2016

Enlighten – Research publications by members of the University of Glasgow http://eprints.gla.ac.uk

# Device Modelling of Bendable MOS Transistors

Hadi Heidari, William T. Navaraj, Gergely Toldi, and Ravinder Dahiya<sup>†</sup> Electronics and Nanoscale Engineering Division, University of Glasgow, G12 8QQ, UK <sup>†</sup>Correspondence to - Ravinder.Dahiya@glasgow.ac.uk

Abstract-This paper presents the directions for computer aided design, modelling and simulation of bendable MOSFET transistors towards futuristic bendable ICs. In order to compensate the bending stress a generalised geometry variation is discussed. Based on drain-current and threshold-voltage parameters varying under the bending stress, a Verilog-A compact model is proposed and describes I-V characteristics of a MOSFET in a standard 0.18- $\mu$ m CMOS technology. This model has been compiled into Cadence environment to predict value and orientation of the bending stress. The proposed model validates against macro-model simulation results, and agrees for both the electron and hole conduction. It has been found that there is significant performance advantage in process-induced uniaxial stressed n-MOSFET, exhibiting a smaller drain-current variation and threshold voltage shift by monitoring the bending stress and changing the supply voltage.

Index Terms—Bendable Electronics, MOS Transistor, Compact Device Modelling.

#### I. INTRODUCTION

During the last decades the microelectronics industry have witnessed aggressive scaling of CMOS transistors from micrometer to the nanometer ranges, in order to improve performance, power consumption and cost [1], [2]. Scaling has been accompanied by various techniques to boost the device's performance [3]-[5]. Among them, strain engineering [6], [7] stands significant from other techniques, by providing a large enhancement of the carriers mobility [8]. If the nanoscale integrated circuits (ICs) are additionally intended to be manufactured on ultra-thin Si-chips for bendable electronics [9], then external global stress get introduced during or due to bending and twisting of the chip. Stress applied to Si crystal changes its resistivity [10], the electronic transport properties, thus changing the MOSFETs drain current. Stress affects the transistor's performance and consequently varies the output signals of the analog and digital circuit building blocks. Moreover, in CMOS-compatible sensors such as Hall, pressure, temperature, chemical/biological, or other sensors, stress introduces offsets that affect the sensitivity and detection ability of static and low frequency environment signals [11].

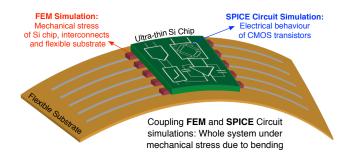

In order to fabricate ICs that function within specifications, both planar as well as during mechanical deformation, the effects of stress must be considered in the design process. Modelling of bendable devices will play a critical role in design of bendable ICs and help produce cost-effective and reliable flexible electronics, which have different simulation scenarios in both SPICE (Simulation Program with Integrated Circuit Emphasis) and FEM (Finite Element Method), as shown in Fig. 1. The conventional complementary-metal-oxide-semiconductor (CMOS) transistor compact models for

Fig. 1: Simulation scenarios of bendable ultra-thin Silicon chips.

SPICE simulations can predict the response of devices produced via various standard technologies. The local-induced stress-effects [6], [12] have been intensively studied and included in device compact models [13], [14]. On the other hand, the effects of external-induced stress are an ongoing investigation and the exist compact models are inadequate for electronics over flexible and bendable substrates [15]. This paper addresses this limitation of conventional circuits simulation tools by providing a new compact model that include the bending (both static and dynamic) related effects on device behaviour. Effects of deformation such as static and dynamic bending of the bendable substrates with electronics over them will be accounted for. The new model will allow early prediction (i.e. during the design phase itself) of the bending related effects in the electrical behaviour of devices and empower us to design circuits capable of operating reliably during arbitrary deformations. By using such models, any change of the electrical parameters of transistors induced by deformation can be predicted in the early phase of the schematic design in SPICE simulators such as Cadence environment.

The paper is organized as follows: Section II contains theoretical aspects of bending effects on transistor parameters and variation-compensation techniques. Compact device modelling of MOS transistors by using a stress-dependent MOSFET macro-model and Verilog-A are presented in Section III. The simulation results using compact models are discussed in Section IV. Finally, the conclusions are given in Section V.

# II. BENDABLE DEVICE MODELLING

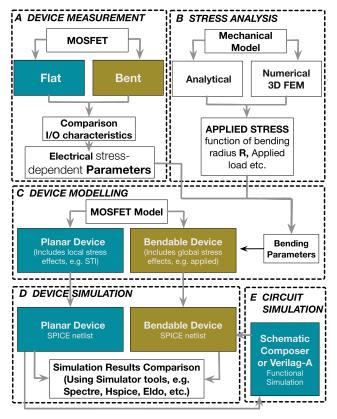

This section discusses the modelling and simulation scenarios for bendable CMOS devices and circuits. The flow involves different abstract levels, as shown in Fig. 2. The labels A, B, C etc. identify blocks in various levels of simulation.

Fig. 2: A CAD-based simulation flow to study electrical device characteristics of bendable CMOS integrated circuit.

Prior to the SPICE model, device measurement and comparison I/O characteristics of both flat and bend devices (A) will be needed. In order to identify the MOSFET parameters that are sensitive to the applied stress such as carriers mobility and threshold voltage parameters. The model includes the short channel effects such as well proximity, impact ionisation, STI stress effects, etc. The mechanical stress analysis is performed in parallel (B), in order to determine the applied stress magnitude and distribution as a function of the applied load, bending radius R. Analytical and numerical FEM models are used for this purpose. FEM simulation are used to find the strain on interconnects and their relative movement with each other to find the change in parasitic resistances and capacitance with various standard bending/flexing or movements there by affecting the interconnect delay. Their variation with stress is expressed as a function of their sensitivities to stress. These are called as stress aware device SPICE models. The stressinduced changes in MOSFET parameters are computed at the transistor level, and then propagated to the gate and circuit level in order to predict circuit-level delay, leakage current and active power consumption for strained inverters, current mirror circuits and ADCs.

Once the planar devices are measured (A) those mechanical models (B) could be used in the next abstract model of functional modelling/simulation (C). In the level of functional simulation (C) will use the original model and SPICE models

to simulate the planar devices and circuits. This simulation uses SPICE netlists (D) such as planar BSIM standard and/or locally stress aware device models such as models considering effects of strained silicon in a local scale affecting the mobility. The SPICE netlists of the planar and bendable MOSFET are provided to the simulator tool as input together with the voltage conditions. The devices are simulated in both linear and saturation regimes in order to compare their electrical parameters in each case. These models are well established and already available and used in commercial/non-commercial EDA tools such as Virtuoso Spectre, Edlo, PSpice, HSPICE, ADS etc. This will depend on the technology corresponding to the SPICE file.

From planar functional simulation, physical stress effect modelling (D) followed by physical simulation are done. In this simulation, effect of bending of interconnects could be brought in with 3D FEM of interconnect simulation (B). In this level, the output from the planar or local stress aware model of individual devices or components will be used just to model the overall parasitic effect due to bendable interconnects. The bending will cause additional strain in the wires which will affect the conductivity of the wires and the respective parasitic resistances. This level (D) covers the aspect of contacts and the lumped devices (considering planar or local stress aware model). Here a Verilog-A/system-C code could be used to synthesise the circuit; then a layout planning or optimisation stage followed by interconnects/block-powerhandling optimisation stage. This level will help to come up with proper compensation circuits for different devices/blocks for optimal operation with global bending.

The final level (E) involves behavioural composer tools such as schematic capture or Verilog-A or system-C could be used to realise the schematics/desired functionality followed by planar functional simulation. The Verilog-A describes compact models to find a stress-aware schematic with electronic compensation capabilities and layout design optimisation. This block cover analogue circuits, digital or mixed signal circuits.

#### III. BENDABLE MOS COMPACT MODEL

Several modelling teams deal with the compact modelling of bulk MOSFET and advanced technologies such as double-gate (DG) MOSFET [16], graphene FET transistors [17], MoS<sub>2</sub> FET [18], and CNTFET (Carbon NanoTube FET) [19], for use in design of analog and mixed circuits. Its major goal is to bring simple solutions, numerically efficient and close to the physics of the device. These compact modelling extensively studied the capabilities of Verilog-A and VHDL-AMS for developing compact models. However, few models work on the effect of stress in MOSFETs such as [20] and [21].

First a Verilog-A compact model is derived and describes I-V characterisations of a MOSFET in a standard 0.18- $\mu$ m CMOS technology. This model has been compiled into Cadence. The proposed model is validated against macro-model simulation results, and an agreement has been achieved for both the electron and hole conduction simultaneously.

An overview of the simulation flow that is used to link stress effects to circuit performance has been presented in Fig. 2. These step sequences enable design and fabrication of the ultra-thin Si chips to achieve the target performance objectives under mechanical stress.

### A. Generalised Geometry Variation Under Bending Stress

Several parameters are affected under bending stress and varying the transistor behaviour and performances. Therefore, it is important to properly understand bending effects on channel mobility, threshold voltage, and other electrical parameters such as saturation velocity, parasitic resistance, gate leakage, gate stack, and reliability of MOS devices.

Understanding the magnitude of the mobility variation and threshold-voltage shifting under uniaxial stress is important when determining the performance gain of bended-Si. Since performance benchmarking needs to be done to obtain highest efficiency at worst case, an adjustment to compensate for the stress-induced mobility variation and threshold-voltage shift is required. This adjustment can be accomplished by determining the difference of the stress versus crystal orientations. On the other hand, since the supply voltage of transistors are constant, therefore still the effects of geometry variation under bending stress is main challenging issues since the threshold voltage is changing proportional with stress. As it can be shown as in saturation region:

$$I_{Dstress} \propto \mu C_{ox} \frac{W}{L} (V_{GS} - V_{th})^{2}$$

$$\cong (\Delta G . \mu_{0} C_{ox0}) \left( \frac{W_{0} / \Delta G}{L_{0} / \Delta G} \right) \left[ \frac{V_{GS} - V_{th}}{\Delta G} \right]^{2} \propto \frac{I_{D_{0}}}{\Delta G} \quad (1)$$

where  $\Delta G$  is geometry variation factor of the transistor and  $I_D$  is drain-current under bending stress. Furthermore, the MOSFET geometry factor variation under bending stress directly affect the substrate doping, and reversely change oxide thickness  $(t_{ox})$  and consequently gate capacitance  $(C_{gate})$ . This can cause variance the power consumption as a factor of  $\pm \Delta G^{-2}$ :

$$P_{peak} = I_{Dstress}.V_{DDstress} = \left(\frac{I_{D0}}{\Delta G}\right) \left(\frac{V_{DD0}}{\Delta G}\right) = \frac{P_{peak0}}{\Delta G^2} \tag{2}$$

In order to adjust above mentioned issues a generalised geometry variation under bending stress approach is presented, which can control the voltage supply  $(V_{DD})$  in compare to dimension changing under stress. This can help to compensate the current drain and threshold voltage as:

$$I_{Dstress} \propto (\Delta G . \mu_0 C_{ox0}) \left(\frac{W_0/\Delta G}{L_0/\Delta G}\right) \left[\frac{V_{GS} - V_{th}}{\Delta U}\right]^2 \propto \frac{\Delta G . I_{D_0}}{\Delta U^2}$$

(3)

where  $\Delta U$  is voltage supply coefficient. If it provided by  $\Delta U^2 = \Delta G$  by monitoring the amount change of dimension change, this turns out to  $I_D = I_{D_0}$ .

#### B. Verilog-A Model

A compact model precisely predicts the performance of the simulated circuits under stress and eases the bendable large-scale integrated circuit. With the parameters extracted from a standard  $0.18-\mu m$  CMOS technology, the compact model is implemented in Verilog-A language to enable circuit simulation as in standard silicon ASIC design process [20].

Based on the state-of-the-art theoretical concepts and experimental results in literatures of the piezoresistive effect and the observed behaviour of the tested transistors, the drain-current duo to mobility variation and threshold-voltage parameters in the BSIM4 model are modified:

$$I_{D_{stress}} = I_{D_0} \times (1 - \Pi_{I_D} \cdot \sigma_{I_D}) \tag{4}$$

$$V_{th_{stress}} = V_{th_0} \times (1 - \Pi_{V_{th}} \cdot \sigma_{V_{th}}) \tag{5}$$

where  $I_{Dstress}$  and  $V_{thstress}$  are new effective drain-current and threshold-voltage parameters including bending stress.  $I_{D_0}$  and  $V_{th_0}$  are original drain-current and threshold-voltage of the transistor without stress, respectively. Piezoresistive coefficients proportional to the drain-current and threshold-voltage are shown in  $\Pi_{I_D}$  and  $\Pi_{V_{th}}$ . The  $\sigma_{I_D}$  and  $\sigma_{V_{th}}$  are known as proportional bending stress to drain-current and threshold-voltage, respectively.

Two instance parameters are defined in the compact model in order to perform simulations: bending radius (R) and stress orientation ( $\Theta$ ). The  $\sigma_{I_D}$  and  $\sigma_{V_{th}}$  are contributions of R define as:

$$\sigma_{I_D} = E \cdot \frac{h}{2R} \cdot \Delta G_{I_{D0}} \left( 1 + \frac{\Delta G_{I_D}}{G_{I_D}} \right) \tag{6}$$

$$\sigma_{V_{th}} = E \cdot \frac{h}{2R} \cdot \left(\Delta G_{V_{th0}} + \frac{\Delta G_{V_{th}}}{G_{V_{th}}}\right) \tag{7}$$

where h is the thickness of wafer and equals to 625  $\mu m$ , and the Young's modulus for silicon has been considered as  $E\cong 169$  GPa. The geometry variation factor of drain-current and threshold-voltage are shown as  $\Delta G_{I_{D0}}$  and  $\Delta G_{V_{th0}}$ , which with  $\frac{\Delta G_{I_D}}{G_{I_D}}$  and  $\frac{\Delta G_{V_{th}}}{G_{V_{th}}}$  have been considered as the geometry dependency of transistors under stress.

The  $\Pi_{I_D}$  and  $\Pi_{V_{th}}$  are contributions of the stress orientation versus the wafer crystal orientation given as:

$$\Pi_{I_D} = 1 - 2 \times \pi_{I_D} \cdot \sin(\Theta) \tag{8}$$

$$\Pi_{V_{th}} = 1 - 2 \times \pi_{V_{th}} \cdot \sin(\Theta) \tag{9}$$

where  $\Theta$  is stress orientation in  $0^{\circ}$  and  $90^{\circ}$  versus wafer crystal direction. The  $\pi_{I_D}$  and  $\pi_{V_{th}}$  are proportional coefficients of piezoresistivity which varying by drain-current and threshold-voltage, respectively.

### IV. SIMULATION RESULTS

As part of the compact model validation, a behaviour of the n-MOSFET under different bending stress are simulated. The schematic in Fig. 3 shows the simulation results. Fig. 3(a) and (b) depicts the modelled I-V characteristics. With parameters extracted from FETs, the Verilog-A model enables circuit simulation as in standard silicon ASIC design process an a negligible variation observed in the simulated threshold voltage  $(V_{th})$ , as shown in Fig. 3(c). Fig. 3(d) depicts the drain-current  $(I_D)$  variation which it increased by 5.2% under

Fig. 3: I-V curves of a bendable n-MOSFET from Verilog-A model.

bending curvature of -2.6 to 2.6 m<sup>-1</sup>. However, it can be noted that if the supply voltage reduces when the bending increases, the drain-current variation can be improved by 40%.

## V. CONCLUSION

Compact modelling is the best solution to leverage between the accuracy and design complexity. This paper described a platform to estimate the performance of conventional CMOS circuits under bending stress. It will serve to guide future experimental work by identifying which device features must be optimised as technology progresses. The simulation results show that compensation of drain-current and threshold-voltage bending stress effects is a viable approach of the design bendable circuits by using such compact models.

#### ACKNOWLEDGMENT

This work was supported by EPSRC through the Fellowship for Growth - Printable Tactile Skin (EP/M002527/1) and EPSRC First Grant - FLEXELDEMO (EP/M002519/1).

#### REFERENCES

- [1] S. Deleonibus, *Electronic Devices Architectures for the NANO-CMOS Era*. Pan Stanford Publishing, 2009.

- [2] M. Hanbücken, P. Müller, and R. B. Wehrspohn, Mechanical Stress on the Nanoscale: Simulation, Material Systems and Characterization Techniques. John Wiley & Sons, 2011.

- [3] E. P. Gusev, V. Narayanan, and M. M. Frank, "Advanced high-k dielectric stacks with polysi and metal gates: Recent progress and current challenges," *IBM j. res. and develop.*, vol. 50, no. 4/5, p. 387, 2006.

- [4] K.-J. Chui et al., "N-MOSFET with silicon–carbon source/drain for enhancement of carrier transport," ETrans. Electron Devices, vol. 54, no. 2, pp. 249–256, 2007.

- [5] T. Irisawa et al., "Electron mobility and short-channel device characteristics of soi finfets with uniaxially strained (110) channels," Trans. Electron Devices, vol. 56, no. 8, pp. 1651–1658, 2009.

- [6] J. V. Faricelli, "Layout-dependent proximity effects in deep nanoscale cmos," in CICC Conf. IEEE, 2010, pp. 1–8.

- [7] C. K. Maiti and T. Maiti, Strain-engineered MOSFETs. CRC Press, 2012.

- [8] L. Washington *et al.*, "pMOSFET with 200% mobility enhancement induced by multiple stressors," *Electron Device Letters*, vol. 27, no. 6, pp. 511–513, 2006.

- [9] R. Dahiya and S. Gennaro, "Bendable ultra-thin chips on flexible foils," IEEE Sensors J., vol. 13, no. 10, pp. 4030–4037, 2013.

- [10] C. S. Smith, "Piezoresistance effect in germanium and silicon," *Physical review*, vol. 94, no. 1, p. 42, 1954.

- [11] H. Heidari, N. Wacker, S. Roy, and R. Dahiya, "Towards bendable cmos magnetic sensors," in *PRIME Conf.*, 2015.

- [12] S. Thompson, G. Sun, K. Wu, J. Lim, and T. Nishida, "Key differences for process-induced uniaxial vs. substrate-induced biaxial stressed si and ge channel mosfets," in *IEDM Conf.* IEEE, 2004, pp. 221–224.

- [13] K.-W. Su et al., "A scaleable model for sti mechanical stress effect on layout dependence of mos electrical characteristics," in CICC Conf. IEEE, 2003, pp. 245–248.

- [14] M. V. Dunga et al., "BSIM4. 6.0 MOSFET model," U. of California, Berkeley, 2006.

- [15] H. Heidari, S. Gupta, and R. Dahiya, "Simulation Scenarios of Ultra-Thin Chips in Smart Large-Area Flexible Electronics," in *innoLAE Conference*, 2016.

- [16] J. Alvarado et al., "Implementation of the symmetric doped double-gate mosfet model in verilog-a for circuit simulation," Int. J. Numerical Modelling, vol. 23, no. 2, pp. 88–106, 2010.

- [17] S. Fregonese, M. Magallo, C. Maneux, H. Happy, and T. Zimmer, "Scalable electrical compact modeling for graphene fet transistors," *Trans. Nanotechnology*, vol. 12, no. 4, pp. 539–546, 2013.

- [18] L. Yu et al., "MoS<sub>2</sub> FET fabrication and modeling for large-scale flexible electronics," in Symp. on VLSI. IEEE, 2015, pp. T144–T145.

- [19] R. Marani, G. Gelao, and A. Gina Perri, "Comparison of ABM SPICE library with verilog-a for compact CNTFET model implementation," *Current Nanoscience*, vol. 8, no. 4, pp. 556–565, 2012.

- [20] H. Alius, H. Rempp, Z. Yu, and T. Gneiting, "A new mosfet model for the simulation of circuits under mechanical stress," in MOS-AK Workshop, London, March 2014.

- [21] N. Wacker, H. Richter, M. Hassan, H. Rempp, and J. N. Burghartz, "Compact modeling of cmos transistors under variable uniaxial stress," *Solid-State Electronics*, vol. 57, no. 1, pp. 52–60, 2011.