# Comparison Study of Integrated Potentiostats: Resistive-TIA, Capacitive-TIA, CT $\Sigma\Delta$ Modulator

Mahdi Rajabzadeh<sup>1</sup>, Denis Djekic<sup>2</sup>, Matthias Haeberle<sup>1</sup>, Joachim Becker<sup>1</sup>, Jens Anders<sup>2</sup>, Maurits Ortmanns<sup>1</sup> Email: Mahdi.rajabzadeh@uni-ulm.de

<sup>1</sup>Institute of Microelectronics, University of Ulm, D-89081 Ulm, Germany. <sup>2</sup>Institute of Smart Sensors, University of Stuttgart, D-70569 Stuttgart, Germany.

Abstract—In this paper, a comparison between three different current readouts for micro-potentiostats is presented: resistive transimpedance amplifier (R-TIA), capacitive transimpedance amplifier (C-TIA), and current-mode continuous-time sigma-delta modulator (Current-CTSDM). The comparison is carried out on the signal transfer function, the required amplifier gain-bandwidth (GBW), its input referred noise current, required area and power, and dynamic range. Each approach and its limitations are separately discussed. The three systems have been simulated using VerilogA models and the results are compared. It is shown that each system comes with its own limitations, however current-mode CTSDM are more beneficial due to their intrinsic digitization.

### I. Introduction

With the progress in integration of electrochemical impedance spectroscopy (EIS), cyclic voltammetry (CV), chronoamperometry (CA), or scanning ion-conductance microscopy (SICM), there is a continuous need for highperformance potentiostats, needing current readout circuits with high dynamic range and partially high temporal resolution. Such micropotentiostats consist of a signal generator, sample under test, a current recording system, and a subsequent processing unit, cf. Fig. 1. The potentiostats usually require very small detection limits for the input currents from pA to μA within a frequency range from DC to few MHz, depending on the application scenario. State of art current readout circuits are realized as resistive feedback transimpedance amplifiers (R-TIA) [1], capacitive feedback transimpedance amplifiers (C-TIA) [2], and current-mode continuous-time (CT) sigmadelta modulators (Current-CTSDM) [3], [4]. E.g. in [5], an R-TIA has been presented, which utilizes a highly-modified pseudo-resistor as feedback element which achieves a high robustness versus temperature and process variations. R-TIAs are very common due to their simple architecture. However, inherent trade-offs such as transimpedance versus bandwidth make them not very suitable for high frequency applications.

A C-TIA, which utilizes a small capacitance as feedback element for high sensitivity, has been presented in [2]. The presented C-TIA achieves a very high frequency range. C-TIAs overcome the trade-offs of R-TIAs by utilizing two stages, i. e., integrator and differentiator. These advantages come along with disadvantages of increased complexity of the system as well as a bandpass signal transfer function.

Another approach is to use a current input CTSDM which has been applied in [3], [4]. CTSDMs are a popular implementation for voltage mode ADCs and can obviously be used for current sensing once the input resistor of the first integrator is removed. They come with the advantage of implicit digitiza-

Fig. 1. Typical set-up of an biochemical experiment, such as EIS and SICM.

tion, but disadvantageously the concept of CTSDM relies on oversampling and noise-shaping. Thus, the operating speed is much higher than the required input bandwidth, the utilized opamps need to operate at this high frequency, and the high-frequency quantization noise from the feedback DAC might impact the sensitive input signal.

Consequently, these three architectures all come with advantages and disadvantages, but a thorough comparison study is not yet presented. This paper is organized as follows: The three different current sensing circuits are reviewed and analysed in the Sections II, III, and IV. An exemplary specification is implemented and simulated in Sections V, which are compared in Section VI, before the paper is concluded in Section VII.

### II. RESISTIVE TRANSIMPEDANCE AMPLIFIER

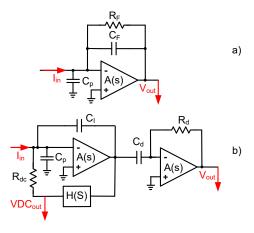

The opamp-based R-TIA is the most common sensing circuit, cf. Fig. 2a. Ideally, the R-TIA consists of an opamp and a feedback resistance  $R_{\rm F}$ , which defines the transimpedance (gain) of the system. However, due to the parasitic capacitance  $C_{\rm P}$  at the input of the amplifier, a feedback capacitor  $C_{\rm F}$  needs to be introduced to ensure the stability of the TIA. Assuming an opamp as single-pole system with DC gain  $A_0\gg 1$  and gain-bandwidth product  $GBW\gg \frac{1}{2\pi R_{\rm F}C_{\rm F}}$ , and assuming  $C_{\rm F}/C_{\rm P}\ll 1$ , the transfer function of the R-TIA becomes:

$$\frac{V_{\text{out}}}{I_{\text{in}}} = \frac{-R_{\text{F}}}{\frac{R_{\text{F}}C_{\text{P}}}{2\pi GBW}s^2 + R_{\text{F}}C_{\text{F}}s + 1}.$$

(1)

Since  $C_{\rm P}$  introduces a second pole, it is efficient to design the transfer function with a second-order Butterworth low-pass characteristic [1].  $C_{\rm F}$  can be calculated using Eq. 1 to obtain a Butterworth low-pass characteristic with corner frequency  $f_{\rm MAX}$  and quality factor  $Q=\frac{1}{\sqrt{2}}$ :

$$C_{\rm F} \approx \sqrt{\frac{2}{2\pi R_{\rm F} GBW}} \sqrt{C_{\rm P}}.$$

(2)

Naturally, R-TIA has a DC-path from input to output, which means that the achievable lower corner frequency  $f_{\rm MIN}=0$ .

©2018 IEEE. Personal use of this material is permitted. Permission from IEEE must be obtained for all other uses, in any current or future media, including reprinting/republishing this material for advertising or promotional purposes, creating new collective works, for resale or redistribution to servers or lists, or reuse of any copyrighted component of this work in other works.

Fig. 2. Schematics of a) resistive-TIA and b) capacitive-TIA.

The upper corner frequency  $f_{\text{MAX}}$  is:

$$f_{\rm MIN} = 0, f_{\rm MAX} = \sqrt{\frac{GBW}{2\pi R_{\rm F} C_{\rm P}}}.$$

(3)

As it can be seen in Eq. 3, there is a trade-off between upper corner frequency  $f_{\rm MAX}$ , TIA gain  $R_{\rm F}$ , and required gainbandwidth product GBW of the amplifier.  $f_{\rm MAX}$  decreases when the transimpedance  $R_{\rm F}$  is increased for constant GBW. Also, for constant  $f_{\rm MAX}$ , the GBW needs to be increased if  $R_{\rm F}$  is increased. Furthermore, GBW needs to be increased quadratically in order to linearly increase the operating frequency  $f_{\rm MAX}$  for a constant transimpedance  $R_{\rm F}$ . This shows the main limitation of R-TIAs: high gain and high speed are very costly to achieve, since the opamp speed needs quadratical increase.

For the R-TIA, the equivalent input noise PSD is:

$$S_{\Delta I_{n,eq}^2} = \frac{S_{\Delta V_{n,OA}^2}}{\left| R_F \| 1/jw C_P \| 1/jw C_F \right|^2} + \frac{4k_B T}{R_F} \left[ \frac{A^2}{Hz} \right], (4)$$

where  $S_{\Delta V_{n,OA}^2}$  is the equivalent input noise PSD of the opamp,  $k_{\rm B}$  the Boltzmann constant, and T the absolute temperature. The equivalent input noise can thus be reduced by increasing  $R_{\rm F}$ . The implementation of large resistors not only consumes huge area, but also introduces parasitic capacitances which degrade the speed. Alternatively, large resistances can be implemented using pseudo-resistors in order to decrease area and parasitics, which are usually very non-linear. Even though, e.g. in [1] linearization could be achieved by the seriesconnection of multiple pseudo-resistors in a highly modified form, this came at the disadvantage of needing an SOI process to reduce the parasitic capacitances and thus the associated speed degradation, and still the implementation had limited linearity [5].

# III. CAPACITIVE TRANSIMPEDANCE AMPLIFIER

Capacitive TIAs have been investigated to achieve current sensing at higher signal frequencies. A state of the art C-TIA is the integrator-differentiator structure [2], cf. Fig. 2b. It features an integrator as the first stage followed by a differentiator in order to have a flat overall gain within the desired signal bandwidth:

$$\frac{V_{\text{out}}}{I_{\text{in}}} = \frac{C_{\text{d}}}{C_{\text{I}}} R_{\text{d}},\tag{5}$$

where  $C_{\rm I}$  is the feedback capacitance of the integrator and  $C_{\rm d}$  and  $R_{\rm d}$  form the external circuitry of the differentiator. Thereby, this C-TIA provides more degrees of freedom to choose the overall gain against noise and speed.

Disadvantageously, the integrator suffers from saturation of the output voltage for low frequency and DC input signals. Therefore, an additional DC feedback path must be introduced to prevent saturation. In the DC feedback path, [2] introduced the filter H(s) which operates at low frequencies as integrator, in order to keep the DC voltage at the output at zero, and as an attenuator within the signal band. The output of H(s)generates the voltage over  $R_{\mathrm{DC}}$  to sink the DC input or low frequency current and to provide a separate DC output. Therefore, the overall characteristic of the C-TIA becomes a bandpass, where the lower corner frequency is defined by the feedback capacitance  $C_{\rm I}$ , the feedback resistor  $R_{\rm DC}$ , and the attenuation  $\gamma$  of H(s). The upper corner frequency  $f_{\text{MAX}}$  is described by the gain-bandwidth product of the amplifier that is decreased by the capacitive divider formed by parasitic input capacitance  $C_{\rm P}$  and feedback capacitance  $C_{\rm I}$ :

$$f_{\text{MIN}} = \frac{1}{2\pi R_{\text{DC}} C_{\text{I}} \gamma}, f_{\text{MAX}} = GBW \frac{C_{\text{I}}}{C_{\text{I}} + C_{\text{P}}}.$$

(6)

The trade-off between the achievable  $f_{\rm MAX}$  and GBW is decreased to a proportional dependency, which makes it less costly to realize high-speed TIAs. However, due to the loading effect of  $C_{\rm d}$ , the integrated amplifier needs to invest more power to achieve the required GBW cf. Fig. 2b. This will be discussed with an example in Sec. V.

If  $C_{\rm I} \ll C_{\rm d}$  is assumed, the noise of the differentiator gets negligible as well as a high overall current gain is achieved, cf. Eq. 5. Then, the equivalent input noise PSD is described as:

$$S_{\Delta {\rm I}_{\rm n,eq}^2} = rac{S_{\Delta {

m V}_{

m n,OA}^2}}{\left| \; R_{

m DC} \| 1/jw C_{

m P} \| 1/jw C_{

m I} \; \right|^2} + rac{4k_{

m B}T}{R_{

m DC}} \; \left[ rac{{

m A}^2}{{

m Hz}}

ight].$$

(7)

Since  $R_{\rm DC}$  has no influence on the overall gain, cf. Eq. 5, it can be increased independently to decrease the equivalent input noise. This also addresses the disadvantageous trade-off between noise and gain in R-TIAs. However, the value of  $R_{\rm DC}$  is constrained to the required  $f_{\rm MIN}$ , cf. Eq. 6, and the maximum DC input current, which needs to be compensated. Since  $R_{\rm DC}$  is not part of the signal path, it can be usually realized as pseudo-resistor whose non-linearity would not influence the SNDR of the passband [2]. However, the design of [2] suffers from shot noise generated by the realization of  $R_{\rm DC}$  with pseudo-resistors for large DC input currents.

One of the drawbacks of C-TIA is its frequency dependent dynamic range. The minimum detectable input current is defined by the integrated input referred noise in the signal band and it is not dependent on the input signal frequency. On the other hand, the maximum input current becomes limited at very low frequencies and DC by saturation of the output voltage of H(s) as:

$$I_{\text{MAX,DC}} = V_{\text{FS}}/R_{\text{DC}},$$

(8)

where  $V_{\rm FS}$  is defined to be equal to the full scale output voltage (maximum output voltage). At the lower end of the signal band, after H(s) corner frequency, the integrator output limits the achievable maximum input current due to its increasing

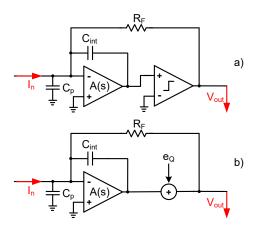

Fig. 3. Schematic of a) 1st order Current-CTSDM and b) with quantizer modeled as additive noise.

gain for decreasing frequency. Therefore, the maximum input current at  $f_{\rm in}$  is limited to [2]:

$$I_{\text{MAX,AC}} = V_{\text{FS}} \times 2\pi f_{\text{in}} C_{\text{I}}.$$

(9)

This clearly shows the trade-off between the input signal frequency  $f_{\rm in}$  and the maximum input current. Furthermore, for frequencies where the differentiator gain is greater than one, the maximum input current becomes limited by the output of the differentiator and can be calculated as:

$$I_{\text{MAX,AC}} = V_{\text{FS}} / (\frac{C_{\text{d}}}{C_{\text{r}}} R_{\text{d}}).$$

(10)

As it can be seen, the maximum input current is a function of input signal frequency and needs to be calculated separately. This leads to frequency dependent dynamic range.

## IV. Current-Mode CT $\Delta\Sigma$ Modulator

Most state of the art CTSDM are used to digitize voltages [6]. However, they can be easily adapted to a current digitization system by removing their input resistor. Fig. 3a depicts a  $1^{st}$  order current-mode CTSDM, which is used for simplicity in the following. By comparing the Current-CTSDM structure with a R-TIA (cf. Fig. 2a), only by introducing a comparator into the R-TIA feedback implicit digitization is achieved. The quantizer adds quantization noise  $e_{\rm Q}$ , cf. Fig. 3b. However,  $e_{\rm Q}$  can be designed and shaped properly in order to have negligible influence to the signal band of interest [6]. Disadvantageously, the high-frequency quantization noise requires high integrator dynamics and disturbs the virtual ground node, which is the current sensing input, making the first integrator in Current-CTSDM power hungry [3], [4].

In the signal band of interest, the signal transfer function (STF) of the Current-CTSDM with feedback resistor  $R_{\rm F}$  cf. Fig. 3a can be designed as:

$$STF_{IB} = \frac{V_{\text{out}}}{I_{\text{in}}} = -R_{\text{F}}.$$

(11)

In order to calculate the frequency requirements of a Current-CTSDM, a single-pole operational amplifier with  $C_{\rm int}$  as the integration capacitance is assumed. For an RC integrator to have an almost undisturbed transfer function, the opamp DC-gain  $A(s)\gg 1$  and the  $GBW\geq 10\times \frac{1}{R_{\rm F}C_{\rm int}}$  must be guaranteed. In CTSDM, the value of  $R_{\rm F}C_{\rm int}$  is related to the

sampling frequency  $F_{\rm S}$  and the modulator scaling coefficient  $a_1$ :

$$GBW \ge 10 \frac{1}{R_{\rm F}C_{\rm int}} = 10 a_1 F_{\rm S}.$$

(12)

Regarding the unavoidable parasitic  $C_{\rm P}$  at the input node, the GBW needs to be further increased yielding:

$$GBW \ge 10 a_1 F_{\rm S} \frac{C_{\rm int} + C_{\rm P}}{C_{\rm int}}.$$

(13)

According to [6], the required GBW can be reduced with significant loss in the inband-noise by compensating for finite GBW by loop filter scaling and phase compensation. Since the STF of a CTSDM features a low pass characteristic, the detectable frequency range spans from DC to  $f_{\rm MAX}$ , which is the inband frequency of the CTSDM given by  $F_S/2 \times OSR$  which results by reusing Eq.13:

$$f_{\text{MIN}} = 0, f_{\text{MAX}} = \frac{F_{\text{S}}}{2 \ OSR} \le \frac{GBW}{20 \ a_1 \ OSR} \frac{C_{\text{int}}}{C_{\text{int}} + C_{\text{P}}}.$$

(14)

The total input referred (thermal) noise PSD of a Current-CTSDM can be derived by assuming that  $e_{\rm Q}$  in the signal band is negligible and other stages do not contribute to the noise [6]:

$$S_{\Delta I_{n,eq}^{2}} = \frac{S_{\Delta V_{n,OA}^{2}}}{\left| R_{F} \| 1/jwC_{P} \| 1/jwC_{int} \right|^{2}} + \frac{4k_{B}T}{R_{F}} \qquad \left[ \frac{A^{2}}{Hz} \right].$$

(15)

The feedback path of Current-CTSDM can be realized using resistors  $R_{\rm F}$  or current sources (CS) since the CTSDM output is binary [6]. The realization with CS will make the implementation much more area efficient. However, the noise performance of CS is worse compared to a resistor. Alternatively, a pseudo-resistor as in [1] can be beneficially applied since for single-bit CTSDM linearity of the feedback elements are not important as single-bit DACs are inherently linear [6].

Dynamic range for CTSDM can not be analytically calculated since their stability is dependent on scaling and input signal level. Therefore, the maximum input amplitude must be found out through simulations [6].

### V. SIMULATIONS

As a case study for the comparison of the 3 current sensing architectures, all circuits have been implemented and simulated using Verilog-A models to prove the reported equations and compare the requirements and results. The three systems have been specified to have a transimpedance gain of  $20\,\mathrm{M}\Omega$ , an input frequency range of  $2\,\mathrm{MHz}$ , and a parasitic input capacitance of  $C_\mathrm{P}=2\,\mathrm{pF}$ . Tab. I shows the summary of the simulated values. The required GBW for the R-TIA with a gain of  $R_\mathrm{F}=20\,\mathrm{M}\Omega$ , using Eq. 3, is approx.  $1\,\mathrm{GHz}$ . As a consequence, with Eq. 2,  $C_\mathrm{F}$  becomes 5.6 fF, which corresponds to the assumption  $C_\mathrm{P}\gg C_\mathrm{F}$ . Note that since the feedback capacitor has a very small absolute value,  $C_\mathrm{L}=0.5\,\mathrm{pF}$  as the dominant load from subsequent stages has been added to the output of the amplifier. This has been done for all three implementations.

The C-TIA features more degrees of freedom, since the number of design parameters are more. As the first step, the value of  $C_{\rm I}$  must be chosen. Big values of  $C_{\rm I}$  lead to

TABLE I. SPECIFICATIONS OF THE THREE SYSTEMS FOR DESIRED OVERALL GAIN AND SIGNAL BANDWIDTH.

| $f_{\mathrm{MAX}} = 2 \mathrm{MHz}, \mathrm{Gain} = 20 \mathrm{M}\Omega, C_{\mathrm{P}} = 2 \mathrm{pF}, V_{\mathrm{FS}} = 1 \mathrm{V}$ |                                                                               |                                                     |                                                       |

|------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------|-----------------------------------------------------|-------------------------------------------------------|

|                                                                                                                                          | R-TIA                                                                         | C-TIA                                               | Current-CTSDM                                         |

| GBW                                                                                                                                      | $\begin{array}{c} 1\mathrm{GHz} \\ C_\mathrm{L} = 0.5\mathrm{pF} \end{array}$ | $42 \mathrm{MHz}$ $C_{\mathrm{L}} = 20 \mathrm{pF}$ | $660 \mathrm{MHz}$ $C_{\mathrm{L}} = 0.5 \mathrm{pF}$ |

| Maximum input $@V_{FS} = 1 \text{ V}$                                                                                                    | 40 nA                                                                         | 0.25 nA@ 0.5 kHz<br>40 nA@ 0.5 MHz                  | 25 nA                                                 |

| $\frac{I_{\rm n,rms}}{(0.1\mathrm{k}-2\mathrm{MHz})}$                                                                                    | $105\mathrm{pA_{rms}}$                                                        | $115\mathrm{pA_{rms}}$                              | $110\mathrm{pA_{rms}}$                                |

decreased influence of  $C_{\rm P}$ , which means that the required GBW will be smaller, cf. Eq. 6. In contrast, small values of  $C_{\rm I}$  yield higher gain and decreased input referred noise, cf. Eq. 7. Therefore, C<sub>I</sub> was fixed to 100 fF to satisfy this trade-off. In order to obtain an overall gain of  $20\,\mathrm{M}\Omega$  and by satisfying the assumption of  $C_{

m d} \gg C_{

m I}$  to decrease the influence of  $R_{\rm d}$  in thermal noise,  $R_{\rm d}$  and  $C_{\rm d}$  are chosen to be  $100 \,\mathrm{k}\Omega$  and  $20 \,\mathrm{pF}$ , respectively. To justify our choices, [2] utilized equal values in a circuit implementation. The required GBW is 42 MHz, cf. Eq. 6; however, due to the loading effect of  $C_{\rm d}=20\,{\rm pF}$ , achieving this GBW becomes more challenging in terms of power. Comparatively, R-TIA needs a  $GBW = 1 \, \text{GHz}$  cf. in Tab. I with the dominant load of  $0.5 \, \text{pF}$ (parasitic loading of subsequent stages), whereas C-TIA needs about  $GBW = 42 \,\mathrm{MHz}$  with a dominant load of  $C_\mathrm{d} = 20 \,\mathrm{pF}$ . Therefore, even though the C-TIA needs less GBW in respect to the R-TIA, due to the loading of  $C_{\rm d}$ , it needs to invest more power (transconductance  $G_{\rm m}$ ) to achieve the required GBW. For the implementation of H(s) to achieve  $f_{MIN} = 0.1 \,\mathrm{kHz}$ , it should be noted that it consists of a leaky integrator with very low corner frequency, which consumes a large area and needs an additional opamp, which are not included in the comparison.  $R_{\rm DC}$  is chosen to be  $20\,{\rm M}\Omega$  in order to have the same transimpedance gain for low input frequencies.

The design of the Current-CTSDM was done using www.sigma-delta.de. A third-order chain of integrator feedback (CIFB) CTSDM with NRZ DAC has been chosen. To achieve enough SQNR, OSR=32 is chosen, with which the inband frequency of  $2\,\mathrm{MHz}$  leads to  $F_\mathrm{S}=128\,\mathrm{MHz}$ . In order to reduce the required GBW, the CTSDM input scaling coefficient was lowered to  $a_1=0.01$  to reduce the GBW requirement according to Eq. 12. Then, the required GBW (without the effect of  $C_\mathrm{P}$ ) becomes  $a_1\cdot F_S=12.8\,\mathrm{MHz}$ . Extensive picking in the STF of CTSDM was avoided by constraining the STF to have a max. gain of  $6\,\mathrm{dB}$  [7]. Using www.sigma-delta.de and these specifications, the optimized CTSDM (using ideal models for the 2nd and 3rd filter stage) achieves maximum SQNR of  $75\,\mathrm{dbFS}$ . With  $R_\mathrm{F}=20\,\mathrm{M}\Omega$ ,  $a_1=0.01$ ,  $C_\mathrm{P}=2\,\mathrm{pF}$ ,  $F_\mathrm{S}=128\,\mathrm{MHz}$ , and using Eq. 13,  $C_{int}=39\,\mathrm{fF}$ , leading to a required GBW of  $52\times12.8\,\mathrm{MHz}$ .

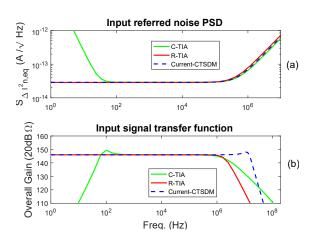

Assuming only thermal noise for resistors and amplifiers, three cases have been simulated using Pnoise analysis in Cadence. Fig. 4a shows the input referred noise PSDs of the three different systems. The input noise PSD of the amplifiers  $(S_{\Delta V_{n,OA}^2})$  are defined in respect to their  $G_{\rm m}$ , which explains the rise at high frequency spectrum behaviour of Fig. 4a, since at high frequencies (assuming  $C_{\rm P}\gg C_{\rm int}$ ), the frequency dependent term  $2\pi f C_{\rm P} S_{\Delta V_{n,OA}^2}$  dominates the noise PSD, cf. Eq. 15. At low frequencies, the C-TIA shows increase in noise PSD, cf. Fig. 4a, which is due to its bandpass signal characteristic, cf. Fig. 4b. Therefore, the integrated noise bandwidth is from  $0.1\,{\rm kHz}$  to  $2\,{\rm MHz}$ .

Fig. 4. a) Input referred noise PSD, b) input signal transfer function of R-TIA, C-TIA, and Current-CTSDM with Gain of  $20\,\mathrm{M}\Omega$  and  $C_\mathrm{P}=2\,\mathrm{pF}$ .

# VI. FURTHER DISCUSSION

For the same input bandwidth, transimpedance and parasitic input capacitance, as it was expected, the R-TIA has the highest needs in terms of GBW. On the other hand, the comparison shows that even though C-TIA needs almost a factor of 15 times less GBW than Current-CTSDM, it needs almost a factor of 1.5 more transconductance than the Current-CTSDM, due to capacitance  $C_{\rm d}$ , to achieve the required bandwidth, which means Current-CTSDM will consume less power for the realization of the first integrator than the C-TIA.

Since the three architectures need same range of  $G_{\rm M}$  for their amplifiers, respectively, it leads to a very similar values of  $S_{\Delta {

m V}_{

m n,OA}^2}$  and therefore, the three architectures show comparable integrated input referred current noise cf. Tab. I and Fig. 4.a, which validates the reported equations. Disadvantageously, the C-TIA has a frequency dependent dynamic range, since the integrator in the forward path must be compensated for low frequency signals by feedback, which leads to a bandpass characteristic cf. Fig. 4.b. In terms of complexity of the system, the R-TIA is the simplest and most straight forward architecture since it consist of only one amplifier. On the contrary, the C-TIA is more complex to design due to more components such as integrator, differentiator, and DC feedback. Current-CTSDMs basically offer the best trade-off by offering similar degrees of freedom as the C-TIA, and obtaining approx. the same noise performance of the R-TIA. Additionally, Current-CTSDM implicitly digitizes input signal, which eliminates need of a ADC present in R-TIA and C-TIA.

# VII. CONCLUSION

In this paper, we presented the Current-CTSDM and its efficiency in comparison to conventional transimpedance amplifiers using resistive and capacitive feedback. It has been proven by calculations and simulations that Current-CTSDM have the similar requirements and the same performance range as R-TIAs and C-TIAs, while their inherent trade-offs such as GBW requirements versus overall gain, bandpass signal transfer function are removed. Furthermore, Current-CTSDMs are an attractive choice since no additional ADC is required.

### ACKNOWLEDGMENT

This work was funded by the DFG under research grant GRK2203-PULMOSENS.

# REFERENCES

- [1] D. Djekic, M. Ortmanns, G. Fantner and J. Anders, "A tunable, robust pseudo-resistor with enhanced linearity for scanning ion-conductance microscopy," 2016 IEEE International Symposium on Circuits and Systems (ISCAS), Montreal, QC, 2016, pp. 842-845.

- [2] G. Ferrari, F. Gozzini, A. Molari and M. Sampietro, "Transimpedance Amplifier for High Sensitivity Current Measurements on Nanodevices," in IEEE Journal of Solid-State Circuits, vol. 44, no. 5, pp. 1609-1616, May 2009

- [3] M. Roham et al., "A Wireless IC for Time-Share Chemical and Electrical Neural Recording," in IEEE Journal of Solid-State Circuits, vol. 44, no. 12, pp. 3645-3658, Dec. 2009.

- [4] M. Stanacevic, K. Murari, A. Rege, G. Cauwenberghs and N. V. Thakor, "VLSI Potentiostat Array With Oversampling Gain Modulation for Wide-Range Neurotransmitter Sensing," in IEEE Transactions on Biomedical Circuits and Systems, vol. 1, no. 1, pp. 63-72, March 2007.

- [5] D. Djekic, G. Fantner, J. Behrends, K. Lips, M. Ortmanns and J. Anders, "A transimpedance amplifier using a widely tunable PVT-independent pseudo-resistor for high-performance current sensing applications," ES-SCIRC 2017 - 43rd IEEE European Solid State Circuits Conference, Leuven, 2017, pp. 79-82.

- [6] Gerfers, Friedel, and Maurits Ortmanns. Continuous-time sigma-delta A/D conversion: fundamentals, performance limits and robust implementations. Vol. 21. Springer Science and Business Media, 2006.

- [7] J. Wagner, R. Ritter and M. Ortmanns, "STF engineering in CT sigmadelta modulators using www.sigma-delta.de," 2016 12th Conference on Ph.D. Research in Microelectronics and Electronics (PRIME), Lisbon, 2016, pp. 1-4.