# Experimental Evaluation of Grid Support Enabled PV Inverter Response to Abnormal Grid Conditions

### **Preprint**

Austin Nelson and Gregory Martin National Renewable Energy Laboratory

James Hurtt

Florida Power and Light Company

To be presented at the Eighth Conference on Innovative Smart Grid Technologies (ISGT 2017) Washington, D.C. April 23–26, 2017

© 2017 IEEE. Personal use of this material is permitted. Permission from IEEE must be obtained for all other uses, in any current or future media, including reprinting/republishing this material for advertising or promotional purposes, creating new collective works, for resale or redistribution to servers or lists, or reuse of any copyrighted component of this work in other works.

NREL is a national laboratory of the U.S. Department of Energy Office of Energy Efficiency & Renewable Energy Operated by the Alliance for Sustainable Energy, LLC

This report is available at no cost from the National Renewable Energy Laboratory (NREL) at www.nrel.gov/publications.

Conference Paper NREL/CP-5D00-67576 April 2017

Contract No. DE-AC36-08GO28308

#### NOTICE

The submitted manuscript has been offered by an employee of the Alliance for Sustainable Energy, LLC (Alliance), a contractor of the US Government under Contract No. DE-AC36-08GO28308. Accordingly, the US Government and Alliance retain a nonexclusive royalty-free license to publish or reproduce the published form of this contribution, or allow others to do so, for US Government purposes.

This report was prepared as an account of work sponsored by an agency of the United States government. Neither the United States government nor any agency thereof, nor any of their employees, makes any warranty, express or implied, or assumes any legal liability or responsibility for the accuracy, completeness, or usefulness of any information, apparatus, product, or process disclosed, or represents that its use would not infringe privately owned rights. Reference herein to any specific commercial product, process, or service by trade name, trademark, manufacturer, or otherwise does not necessarily constitute or imply its endorsement, recommendation, or favoring by the United States government or any agency thereof. The views and opinions of authors expressed herein do not necessarily state or reflect those of the United States government or any agency thereof.

This report is available at no cost from the National Renewable Energy Laboratory (NREL) at www.nrel.gov/publications.

Available electronically at SciTech Connect http://www.osti.gov/scitech

Available for a processing fee to U.S. Department of Energy and its contractors, in paper, from:

U.S. Department of Energy

Office of Scientific and Technical Information

P.O. Box 62

Oak Ridge, TN 37831-0062

OSTI <a href="http://www.osti.gov">http://www.osti.gov</a>

Phone: 865.576.8401 Fax: 865.576.5728 Email: reports@osti.gov

Available for sale to the public, in paper, from:

U.S. Department of Commerce National Technical Information Service 5301 Shawnee Road Alexandria, VA 22312 NTIS http://www.ntis.gov

Phone: 800.553.6847 or 703.605.6000

Fax: 703.605.6900 Email: orders@ntis.gov

Cover Photos by Dennis Schroeder: (left to right) NREL 26173, NREL 18302, NREL 19758, NREL 29642, NREL 19795.

## Experimental Evaluation of Grid Support Enabled PV Inverter Response to Abnormal Grid Conditions

Austin Nelson and Gregory Martin National Renewable Energy Laboratory Golden, Colorado James Hurtt

Florida Power and Light Company

Juno Beach, Florida

Abstract—As revised interconnection standards for grid-tied photovoltaic (PV) inverters address new advanced grid support functions (GSFs), there is increasing interest in inverter performance in the case of abnormal grid conditions. The growth of GSF-enabled inverters has outpaced the industry standards that define their operation, although recently published updates to UL1741 Supplement SA define test conditions for GSFs such as volt-var control, frequency-watt control, and voltage/frequency ride-through, among others. This paper describes the results of a comparative experimental evaluation on four commercially available, three-phase PV inverters in the 24.0-39.8 kVA power range on their GSF capability and its effect on abnormal grid condition response. The evaluation examined the impact particular GSF implementations have on run-on times during islanding conditions, peak voltages in load rejection overvoltage scenarios, and peak currents during single-phase and threephase fault events for individual inverters. Testing results indicated a wide variance in the performance of GSF enabled inverters to various test cases.

Index Terms—anti-islanding, fault current, frequency-watt control, load rejection overvoltage, ride-through, volt-var control

#### I. INTRODUCTION

In an effort to positively enhance the impact of increasing amounts of distributed energy resources, grid-tied photovoltaic (PV) inverters are increasingly being designed to provide advanced grid support functions (GSF) that can provide voltage and frequency support at their local point of interconnection. Among others, these GSFs include voltage ride-through (VRT), frequency ride-through (FRT), fixed power factor (FPF), volt-var control (VVC), and frequency-watt control (FWC). The increased implementation of these functions has been complemented by the release of utility specific interconnection standards such as California Public Utilities Commission Rule 21 and Hawaii Rule 14H [1,2], as well as updates to UL1741 Supplement SA and ongoing revisions to IEEE1547-2003 [3,4].

Utilities are increasingly interested in inverter GSF capabilities addressed by new standards. This paper describes the results of laboratory testing of advanced PV inverters undertaken by the National Renewable Energy Laboratory (NREL) on behalf of the Florida Power and Light Company (FPL). FPL recently commissioned a 1.1 MW-AC PV installation on a carport near the Daytona International Speedway in Daytona Beach, Florida. In addition to providing a source of clean energy production, the site serves as a live test bed for a variety of different solar inverters—36 installed inverters from eight manufacturers.

Four test inverters were selected by FPL, herein referred to as Inverter 1-4. Each three-phase inverter model was rated between 24.0-39.8 kVA, and with different GSF capabilities. A series of GSF characterization tests were run, including VRT, FRT, FPF, VVC, and FWC. While high penetrations of GSF-capable PV inverters have the potential to provide significant voltage and frequency support on distribution feeders, grid operators face significant challenges in considering their impact on protection equipment and voltage support devices, among other considerations [5]. Other considerations are inverter response to abnormal grid conditions, such as (unintentional) islanding, transient over-voltage, and fault conditions, with GSFs enabled.

Since many GSFs have the objective of supporting the grid during voltage and frequency excursions, there is concern that such functions could adversely impact islanding detection. Modeling studies such as those in [6] suggest that certain antislanding detection methods coupled with GSFs can have adverse impacts on islanding run-on times (ROT) when multiple inverters are present on a distribution feeder. The work in [7] examines the effect of GSFs on anti-islanding ROTs, but tests single-phase inverters sized  $\leq 6$  kW. The study in [8] evaluates the effect of VVC, VRT, FRT, and fixed power factor operation on ROTs for a 12 kW inverter, leading to inconclusive results about GSF impacts on islanding detection.

LRO occurs when a portion of a distribution feeder disconnects from the grid, resulting in a high PV generation-to-load ratio. During the typically brief period before inverter controls detect the island condition, current injected by the inverter into the load can cause transient overvoltages. This phenomenon was previously studied by NREL for small residential inverters and a 12 kW commercial inverter without GSF capability [9]. The study in [10] presents improvements in LRO peak voltages due to improvements in inverter firmware for three-phase inverters, but does not focus on variations in performance due to GSFs.

Efforts have been made to improve modeling of inverter controllers under fault conditions, but the analyses are often limited to the simulation domain [11]-[13], although the study in [14] does match prototype hardware testing to inverter fault models. UL1741 requires fault current ratings for grid-tied inverters, but such listing information is not as comprehensive as the data in this study, nor does it address three-phase faults. This paper summarizes the results of hardware testing of these abnormal conditions with GSFs enabled for 24.0-39.8 kVA three-phase inverters, providing a comparative performance analysis between the four test inverters.

#### II. TEST CONFIGURATION

Four different PV inverters that are installed at the FPL solar site were selected for this study. All inverters were individually connected to a 45 kVA AC voltage source with three independently controllable phases, which served as the grid simulator for all tests. Each inverter was sourced by a pair of 1000V/30A PV simulators from the AMETEK TerraSAS family, with each connected to one of the independent MPPT trackers on each inverter. A solar current vs. voltage ("I/V") profile was selected such that the inverter would run at full power and be near the maximum power point of the I/V curve, at a DC voltage on the higher end of its stated power point tracking range. For tests below full power, the irradiance value of the curve was adjusted to attain the target AC output power.

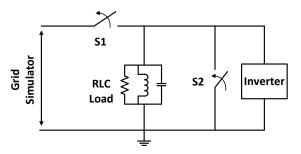

The basic one-line circuit for all tests is shown in Figure 1, with the different functions of switches S1 and S2 described in the sections that follow. Switch S1 was realized with a shunt trip circuit breaker, and was opened for anti-islanding and LRO tests. Switch S2 was a controllable contactor with very low impedance path to ground for fault tests. Individual phases or all three phases could be connected to switch S2 prior to initiating faults. The load bank was a 100 kVA RLC load bank with independent loading on each of the phases, 100 W step sizes for resistive elements, and 75 VA step sizes for reactive elements.

Figure 1. Basic one-line circuit diagram for anti-islanding, LRO, and fault tests

All inverters were 60 Hz, 277/480 VAC, three-phase models, listed for use in North America. A summary of basic inverter specifications along with their GSF capabilities are shown in Table I. Prior to completing the abnormal tests, a number of characterization tests for the VRT, FRT, FPF, VVC, and FWC functions were completed. These tests closely followed the procedures described in the updated revision of UL1741, and results were provided to FPL for comparative evaluation purposes.

For anti-islanding, LRO, and fault tests, different combinations of these GSFs were enabled in order to evaluate the effect of each function on the response to each abnormal grid condition. The VRT and FRT settings used in this study followed the guidelines given in Rule 21. Since a number of the trip times and magnitudes and times are adjustable under this standard, the example Rule 21 settings in UL1741 Table SA9.1 and SA10.1 for VRT and FRT, respectively, were programmed.

Inverter 1 was not capable of being programmed for the maximum low VRT trip times, so a modified trip time was

used that well exceeded the IEEE1547 limits; this was likewise true for the high FRT trip time. Additionally, only two low voltage trip magnitudes could be simultaneously programmed on this inverter rather than three, so all abnormal tests were run with the two lowest magnitudes programmed. Inverter 2 was much more limited in its ride through capabilities for both VRT and FRT. The widest possible ride-through limits and longest trip times were programmed for this inverter, which were in excess of the IEEE1547 limits but well within the Rule 21 limits. Details of ride-through settings and performance for each inverter were provided to FPL in a detailed technical report.

TABLE I. BASIC SPECIFICATIONS OF TEST INVERTERS

| Inverter | Nominal Real<br>Power (kW) | Nominal Reactive<br>Power (kVA) | GSF Capability                                    |

|----------|----------------------------|---------------------------------|---------------------------------------------------|

| 1        | 24.0                       | 24.0                            | VRT <sup>†</sup> , FRT <sup>†</sup> ,<br>FWC, VVC |

| 2        | 36.0                       | 39.8                            | VRT <sup>†</sup> , FRT <sup>†</sup>               |

| 3        | 36.0                       | 36.0                            | VRT, FRT,<br>FWC, VVC                             |

| 4        | 30.0                       | 33.0                            | VRT, FRT, VVC                                     |

<sup>†</sup>Settings modified from Rule 21 defaults due to ride-through capability limitations.

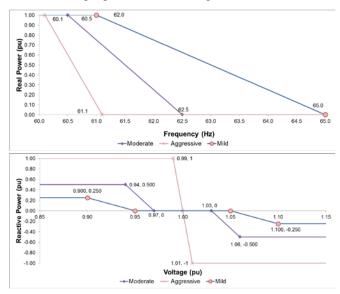

A series of three FWC and VVC characteristic curves were defined in conjunction with FPL for the characterization tests, referred to as "mild", "moderate", and "aggressive" based on their slopes, as shown in Figure 2. Each FWC curve was characterized by its start frequency and stop frequency, with a linear power curtailment region connecting the two. Similarly, VVC curves were characterized by a dead band around nominal voltage (except "aggressive"), a linear region for increasing/decreasing reactive power, and maximum reactive power limits. The peak reactive power for these curves was dependent on inverter capability, and was scaled accordingly to each test inverter. The VVC curves were all symmetrical as a function of voltage, whereas FWC curves only addressed overfrequency events. The most aggressive curve for both VWC and FWC was programmed for subsequent abnormal tests.

Figure 2. Characteristic curves tested for FWC (top) and VVC (bottom)

#### III. ANTI-ISLANDING TESTS

All anti-islanding tests were run under the test procedures in IEEE1547.1, which describes the use of a resonant RLC load to create a difficult loading scenario for islanding detection. All tests were run at 100% inverter power and the RLC load was tuned for unity quality factor, such that the fundamental component of grid current was <2% of nominal. After the circuit was operating in steady state, switch S1 was opened and the inverter ROT was measured via the current waveform. Each test was run a total of five times, with 1% changes in the inductive load for each successive test.

Three different sets of GSFs were programmed on the test inverters for each set of tests, where available. The widest FRT and VRT settings were programmed for all tests, and were the only GSFs enabled for the first set of tests. For the second set of tests, inverters capable of VVC functionality were programmed with the "aggressive" curve along with the FRT/VRT settings. Note that in some cases, some reactive power was output from the test inverter at nominal voltage due to the aggressive characteristic curve, so the reactive load was adjusted accordingly to minimize grid current. Finally, inverters capable of FWC were programmed with the "aggressive" FWC curve along with the FRT/VRT settings (VVC disabled). Each set of GSF settings was repeated at five different loading cases, creating a maximum of 15 tests per inverter.

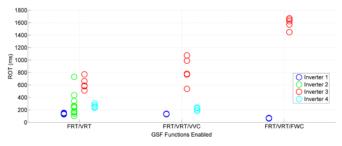

All ROTs are summarized in Figure 3 for each test case. VVC was not programmable for Inverter 2 and FWC was not programmable for Inverter 2 or Inverter 4, so these tests cases were not run. Inverter 2 had increased ROTs at both the maximum and minimum inductive loads, so several additional tests were run, creating a total of 11 test cases. A summary of the mean and maximum ROTs for each set of test cases is summarized in Table II.

As seen from the summary data, there were mixed results depending on the test inverter and the GSFs enabled. Overall, Inverter 1 had the shortest and most repeatable ROTs, including the shortest overall ROT of all test cases. Inverter 3 tended to have the longest ROTs for each of the different GSF settings. Note that longer ROT does not necessarily imply worse behavior between inverters; IEEE1547 requires that inverters cease to energize within two seconds of island formation, and the time under which such detection occurs is dependent on the manufacturer's choice of detection strategy, and may be purposely programmed to sustain longer ROTs.

Figure 3. Anti-islanding testing summary showing ROTs for every test case

The more important metric to consider is the effect of GSF combination on ROT for each inverter. For Inverter 1, the mean and maximum ROT decreased with VVC enabled, and

decreased further with FWC enabled. Regardless, the ROTs were all much faster than the required trip time and differences were on the order of several AC cycles. Similarly, the mean and maximum ROTs for Inverter 4 decreased slightly with VVC enabled, but the differences were also within several AC cycles.

TABLE II. MEAN AND MAXIMUM RUN-ON TIMES

| GSFs            | Metric | Inverter Number and ROT (ms) |                  |      |     |

|-----------------|--------|------------------------------|------------------|------|-----|

| Enabled         |        | 1                            | 2                | 3    | 4   |

| VRT/FRT         | Mean   | 142                          | 275 <sup>†</sup> | 624  | 264 |

|                 | Max    | 154                          | 731 <sup>†</sup> | 772  | 305 |

| VRT/FRT/<br>VVC | Mean   | 135                          | N/A              | 831  | 210 |

|                 | Max    | 140                          | N/A              | 1076 | 240 |

| VRT/FRT/<br>FWC | Mean   | 69                           | N/A              | 1593 | N/A |

|                 | Max    | 72                           | N/A              | 1671 | N/A |

<sup>†</sup> Statistics based on 11 tests rather than 5.

Inverter 3 demonstrated increased mean and maximum ROTs with VVC, and higher yet ROTs with FWC enabled. However, even the peak ROT for all test cases (1671 ms) was safely with the two-second trip requirement, as seen in Figure 4. Although Inverter 3 consistently had the longest ROTs with FWC enabled, it significantly reduced output power around 400-500 ms after the island event was triggered, before disconnecting ~1.0-1.5 seconds later. This behavior was consistent for all tests with FWC enabled, suggesting that the inverter still detected an island within several hundred milliseconds, but was programmed to disconnect from the grid much later when operating with FWC mode enabled.

Figure 4. Longest islanding ROT for Inverter 3

#### IV. LOAD REJECTION OVERVOLTAGE TESTS

A series of LRO tests were run for each inverter at various inverter output power to load power (P<sub>I</sub>/P<sub>L</sub>) ratios, following the same procedures are those described in [9]. Inverter power was set to 33%, 67%, and 100% of nameplate; load power consumption was set to 10%, 33%, 50%, 67%, and 100% of nameplate inverter power. Every combination of these set points where inverter output power was greater than or equal to load power was tested, creating 11 unique test cases. The first 11 tests were run with FRT and VRT settings enabled. For inverters capable of VVC, a subsequent set of four tests was run at the four highest P<sub>I</sub>/P<sub>L</sub> ratios with the aggressive VVC curve enabled. The basic test circuit is sown in Figure 1, except only purely resistive loads were used. Once the inverter was running at the target power level, switch S1 was opened, forcing all inverter output current into the resistive load. The peak voltage was measured using a sampling rate of 100 kHz at the oscilloscope with no filtering enabled.

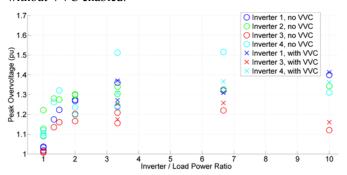

Figure 5 shows the peak overvoltage magnitude (proportional to peak nominal L-N voltage) for every test case as a function of P<sub>I</sub>/P<sub>L</sub> ratio. For higher P<sub>I</sub>/P<sub>L</sub> ratios, higher overvoltage magnitudes are expected (assuming an ideal current source model for the inverters). As shown in Figure 5, there were mixed results depending on the test inverter and P<sub>I</sub>/P<sub>L</sub> ratio, and there is no clear correlation between P<sub>I</sub>/P<sub>L</sub> ratio and the peak overvoltage magnitude, except perhaps for lower P<sub>I</sub>/P<sub>I</sub> ratios. In general, Inverter 3 had among the lowest overvoltage peaks. Almost no overvoltage was measured for Inverters 1 or 3 for unity P<sub>I</sub>/P<sub>L</sub> ratios. Inverter 4 had several of the largest overvoltages for any of the tests, but the maximum for any test case was 152% of nominal, which is well below some overvoltages measured in [9]. Finally, there was no clear evidence that enabling VVC caused any increase in peak voltage, and in several cases the peaks were lower than cases without VVC enabled.

Figure 5. Load rejection overvoltage testing summary data showing peak voltages as a function of inverter to load power ratio

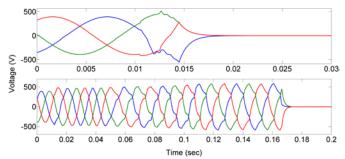

A waveform plot for the worst-case peak voltage for two of the inverters is shown in Figure 6. Note that for these figures, the grid simulator was disconnected just after 1 ms, and the time scale is not aligned between the two plots. A maximum peak of 141% of nominal occurred on Inverter 1 at 100% output power, 10% load power, and VVC enabled, which are considered the worst case test conditions. In most tests for Inverters 1-3, the peak overvoltages were a single pulse (sometimes on several phases), lasting a very brief period of time on the order of tens of microseconds. Inverter 4 had several longer overvoltage durations, such as the bottom plot, which shows a maximum peak voltage of 152% of nominal, which occurred at 67% inverter power, 10% load power, and VVC disabled, and continued for several AC cycles before the inverter tripped.

#### V. FAULT TESTS

The third abnormal condition of interest was the effect of GSFs on fault current contribution. Each inverter was run at full power, and several single-phase to ground and three-phase to ground fault tests were executed. Each of the four fault types was tested at unity power factor and at both  $\pm 0.80$  power factor. Each test was repeated three times to randomize the phase angle on the AC cycle at which the fault occurred, leading to a total of 36 tests per inverter. Fixed power factor operation was tested because it was programmable for every inverter, and it also served as a proxy for inverter behavior when operating in VVC mode away from nominal voltage.

Figure 6. Worst case LRO test runs showing 141% peak overvoltage for Inverter 1 (top) and 152% peak overvoltage for Inverter 4 (bottom).

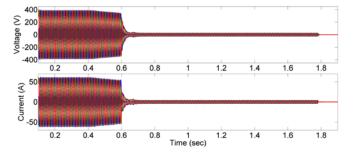

For each test, the inverter was run at full power, and the load was set to approximately match the inverter output in order to minimize grid current. The load was resistive for unity power factor, and a combination of resistive and inductive or capacitive for tests at  $\pm 0.80$  power factor (negative power factor is leading current, using generator convention). The test was started with switch S1 closed and switch S2 opened in Figure 1. Once running at steady state, a timing circuit was used to open S1 approximately 8-10 ms before switch S2 was closed, in order to protect the grid simulator. A balanced load was added to the circuit so the inverter would continue to operate at nominal conditions for the small period of time after S1 was opened, creating an island for a brief time window. AC current was measured at each of the three phases at the inverter terminals to determine the fault current contributions using a 10 MHz probe, and measurements were sampled at 10 MHz at the oscilloscope in order to capture high frequency content of the fault current. All tests were run with VRT and FRT enabled, and both VVC and FWC disabled.

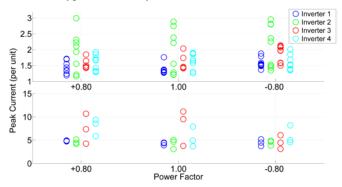

The normalized peak currents of all single-phase (top) and three-phase (bottom) fault test results are shown in Figure 7. The magnitude of the peak fault current was largely independent of which phase was faulted, so a total of nine test cases are summarized together for each power factor value in the top figure. Table III shows the mean and maximum peak fault current for each set of three-phase fault tests at different power factors (single-phase summary is not provided since peak currents were much lower).

For single-phase faults, three of the four inverters had a slightly higher mean peak current at -0.80 power factor, but the range of peak values significantly overlapped for all inverters at all power factors. Inverters 1, 3, and 4 had very similar magnitudes and ranges of fault currents; Inverter 2 had both the largest peak current values and the widest range of responses. The maximum single-phase fault current peak was 202.7 A (2.99 per unit) from Inverter 2. The reported fault maxima are the peak of any of the three phases, and in some cases occurred on a phase other than the one that was faulted.

For three-phase faults, Inverters 1 and 2 had the most consistently low and repeatable peak fault currents. Inverter 3 had the largest range and magnitude of fault currents peaks, with a maximum across all tests of 683.3 A (11.16 per unit) at unity power factor. For three-phase fault data, the reported currents are the maximum of any of the in individual phases, and are not additive across all phases. Power factor had no clear effect on peak fault currents for single-phase or three-phase faults.

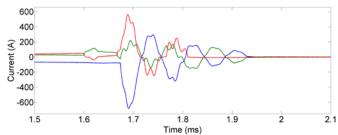

Fault current peaks were typically very short in duration, on the order of tens of microseconds. The 683.3 A fault peak was the largest for all test cases but only had duration of  $\sim$ 39  $\mu$ s, as seen in Figure 8. However, inverters sometimes continued operation for several hundred milliseconds after the peak current event occurred. In no test cases did the fault current open the 60 A, Type J time delay fuses.

Figure 7. Normalized peak phase fault current for single phase to ground tests (top) and three phase to ground tests (bottom)

TABLE III. MEAN AND MAXIMUM PEAK CURRENTS FOR THREE PHASE TO GROUND FAULT TESTS

| Power              | Metric | Inverter Number and Peak Current (A) |       |       |       |

|--------------------|--------|--------------------------------------|-------|-------|-------|

| Factor             |        | 1                                    | 2     | 3     | 4     |

| +0.80<br>(lagging) | Mean   | 198.2                                | 310.5 | 455.3 | 446.5 |

|                    | Max    | 202.0                                | 347.3 | 654.0 | 528.0 |

| 1.00               | Mean   | 173.8                                | 290.0 | 499.1 | 309.3 |

|                    | Max    | 183.3                                | 343.3 | 683.3 | 443.3 |

| -0.80<br>(leading) | Mean   | 182.7                                | 302.5 | 278.9 | 333.1 |

|                    | Max    | 212.0                                | 330.0 | 372.0 | 460.0 |

Figure 8. Phase currents from Inverter 3 during fault testing, showing maximum peak fault current of 683.3 A

#### CONCLUSIONS

The tests described in this paper examined the response of several PV inverters with advanced GSFs to abnormal grid conditions. Four commercially available inverters rated 24-36 kW were characterized for their ride-through, FPF, VVC, and FWC capability and were subjected to anti-islanding, LRO, and fault conditions with different combinations of these GSFs enabled. Islanding tests showed that neither FWC nor VVC had a clear effect on ROT. All inverters were shown to meet the two second ROT maximum required by existing standards. LRO tests yielded no clear dependence on VVC or inverter to load power ratio on the peak voltages observed, which typically had very short duration and never exceeded 152% of nominal. Single- and three-phase to ground fault tests showed no

clear dependence on power factor for peak fault current contribution. The results indicate a significant variation in how GSF-enabled inverters respond to various grid conditions. Future work will examine the effects of varying output power levels, choosing different GSF settings, further investigation into the effect of FWC on islanding ROT, and interactions among multiple inverters.

#### ACKNOWLEDGMENT

The authors express their thanks to the Florida Power and Light Company for providing funding for this project and contributing the PV inverters. The authors also thank Anderson Hoke, Sudipta Chakraborty, Mariko Shirazi, and Colin Tombari (all of NREL) for their technical inputs and contributions to this project.

#### REFERENCES

- "Rule 21 Generating Facility Interconnections," California Public Utility Code, 2000.

- [2] "Rule No. 14: Service Connections and Facilities on Customer's Premises," Hawaiian Electric Company, Inc., Oct. 2015.

- [3] "UL 1741 Supplement SA: Grid Support Utility Interactive Inverters and Converters," Underwriters Laboratories, 2016.

- [4] "IEEE Standard for Interconnecting Distributed Resources with Electric Power Systems," IEEE Std. 1547, 2003.

- [5] R. J. Bravo, R. Salas, T. Bialek and C. Sun, "Distributed energy resources challenges for utilities," 2015 IEEE 42nd Photovoltaic Specialist Conference (PVSC), New Orleans, LA, 2015, pp. 1-5.

- [6] Accelerating Development of Advanced Inverters: Evaluation of Anti-Islanding Schemes with Grid Support Functions and Preliminary Laboratory Demonstration Sandia Report No. SAND2013-10231, November 2013.

- [7] A. Hoke, A. Nelson, B. Miller, S. Chakraborty, F. Bell and M. McCarty, "Experimental evaluation of PV inverter anti-islanding with grid support functions in multi-inverter island scenarios", National Renewable Energy Laboratory, Golden, CO, Tech. Rep., NREL/TP-5D00-66732, Jul. 2016.

- [8] C. Hicks, W. Peng, Y. Baghzouz and S. Haddad, "Experimental test on the islanding of an advanced PV inverter," 2016 International Symposium on Power Electronics, Electrical Drives, Automation and Motion (SPEEDAM), Anacapri, 2016, pp. 1342-1347.

- [9] A. Nelson, A. Hoke, S. Chakraborty, J. Chebahtah, T. Wang and B. Zimmerly, "Inverter load rejection over-voltage testing", National Renewable Energy Laboratory, Golden, CO, Tech. Rep., NREL/TP-5D00-63510, Feb. 2015.

- [10] R. J. Bravo, R. Salas, R. Yinger and S. Robles, "Solar photovoltaic inverters transient over-voltages," 2013 IEEE Power & Energy Society General Meeting, Vancouver, BC, 2013, pp. 1-5.

- [11] G. Dötter, F. Ackermann, N. Bihler, R. Grab, S. Rogalla and R. Singer, "Stable operation of PV plants to achieve fault ride through capability -Evaluation in field and laboratory tests," 2014 IEEE 5th International Symposium on Power Electronics for Distributed Generation Systems (PEDG), Galway, 2014, pp. 1-8.

- [12] X. Kong, Y. Yuan, P. Li and Y. Wang, "Study on the fault current transient features of the PV inverter," *International Conference on Re*newable Power Generation (RPG 2015), Beijing, 2015, pp. 1-7.

- [13] Z. Chang, G. Song, X. Wang, S. Guo, W. Zhang and X. Jin, "Analysis on asymmetric fault current of inverter interfaced distributed generator," 2016 China International Conference on Electricity Distribution (CICED), Xi'an, 2016, pp. 1-6.

- [14] C. A. Plet, M. Brucoli, J. D. F. McDonald and T. C. Green, "Fault models of inverter-interfaced distributed generators: Experimental verification and application to fault analysis," 2011 IEEE Power and Energy Society General Meeting, San Diego, CA, 2011, pp. 1-8.