## UC Irvine UC Irvine Electronic Theses and Dissertations

**Title** Incremental Parallelization with Migration

Permalink https://escholarship.org/uc/item/82w6f2w0

**Author** Zhang, Wenhui

Publication Date 2014

Peer reviewed|Thesis/dissertation

# UNIVERSITY OF CALIFORNIA, IRVINE

Incremental Parallelization with Migration

#### DISSERTATION

submitted in partial satisfaction of the requirements for the degree of

#### DOCTOR OF PHILOSOPHY

in Information and Computer Science

by

Wenhui Zhang

Dissertation Committee: Professor Lubomir F. Bic, Co-Chair Professor Michael B. Dillencourt, Co-Chair Professor Amelia C. Regan

Portion of Chapter 2 © 2011 IEEE Computer Society Portion of Chapter 3 © 2012 IEEE Computer Society 2005 IEEE Computer Society Portion of Chapter 4 © 2012 IEEE Computer Society 2005 IEEE Computer Society Portion of Chapter 5 © 2011 IEEE Computer Society All other materials © 2014 Wenhui Zhang

## DEDICATION

This dissertation is dedicated to my husband, Chuanwen, who has persistently supported me and understood the challenges and sacrifices; our lovely son, who is a smart and handsome boy and who wished his mom could have spent more time with him; my father who has been always encouraged me to pursue higher and higher and my mother who has offered her love without expecting anything back.

## TABLE OF CONTENTS

|               |                                           |                | ]                                                                       | Page            |

|---------------|-------------------------------------------|----------------|-------------------------------------------------------------------------|-----------------|

| LI            | ST C                                      | )F FIG         | GURES                                                                   | v               |

| $\mathbf{LI}$ | ST C                                      | OF TA          | BLES                                                                    | vii             |

| A             | CKN                                       | OWLE           | EDGMENTS                                                                | viii            |

| C             | URR                                       | ICULU          | UM VITAE                                                                | ix              |

| $\mathbf{A}$  | BSTI                                      | RACT           | OF THE DISSERTATION                                                     | xi              |

| 1             | $\operatorname{Intr}$                     | oducti         | on                                                                      | 1               |

|               | $\begin{array}{c} 1.1 \\ 1.2 \end{array}$ |                | ch Motivation and Target Problem                                        | $\frac{1}{4}$   |

| <b>2</b>      | Nav                                       | 0              | nal Programming                                                         | <b>5</b>        |

|               | $2.1 \\ 2.2$                              |                | ew                                                                      | 59              |

| 3             | Incr                                      | ement          | al Parallelization                                                      | 15              |

| U             | 3.1                                       |                | dology Overview                                                         | 15              |

|               | 3.2                                       |                |                                                                         | $\frac{10}{21}$ |

|               | 0.2                                       | 3.2.1          | An Example of Matrix Multiplication                                     | $\frac{21}{21}$ |

|               |                                           | 3.2.1<br>3.2.2 | An Example of ADI                                                       | $\frac{21}{22}$ |

|               | 3.3                                       | -              | Transformation and Placement                                            | $\frac{22}{27}$ |

|               | 0.0                                       | 3.3.1          | Partitioning phase 1: Adapt to the data distribution                    | $\frac{21}{27}$ |

|               |                                           | 3.3.2          | Partitioning phase 1: Example of ADI                                    | $\frac{21}{28}$ |

|               |                                           | 3.3.3          | Partitioning phase 1: Example of Matrix Multiplication in one dimension |                 |

|               |                                           | 3.3.4          | Partitioning phase 1: Example of Matrix Multiplication in second di-    | 1 00            |

|               |                                           | 0.011          | mension                                                                 | 32              |

|               |                                           | 3.3.5          | Partitioning phase 2: Increase opportunities for parallelism            | 35              |

|               |                                           | 3.3.6          | Partitioning phase 2: Example of ADI                                    | 35              |

|               |                                           | 3.3.7          | Partitioning phase 2: Example of Matrix Multiplication in second di-    |                 |

|               |                                           |                | mension                                                                 | 36              |

|               |                                           | 3.3.8          | Assigning a location to each tile                                       | 38              |

|               | 3.4                                       | Paralle        | elization Generation                                                    | 38              |

|          |                    | 3.4.1          | Building the Weighted Dependence Graph                              | 39 |

|----------|--------------------|----------------|---------------------------------------------------------------------|----|

|          |                    | 3.4.2          | Building the Weighted Dependence Graph: Example of ADI              | 40 |

|          |                    | 3.4.3          | Building the Weighted Dependence Graph: Example of Matrix Multi-    |    |

|          |                    |                | plication                                                           | 42 |

|          |                    | 3.4.4          | Combining tiles into threads                                        | 42 |

|          |                    | 3.4.5          | Generating threads for ADI                                          | 42 |

|          |                    | 3.4.6          | Generating threads for Matrix Multiplication in one dimension       | 44 |

|          |                    | 3.4.7          | Generating threads for Matrix Multiplication in second dimension    | 44 |

|          |                    | 3.4.8          | Generating the Code                                                 | 49 |

|          |                    | 3.4.9          | Generating the Code: Example of ADI                                 | 49 |

|          |                    | 3.4.10         | Generating the Code: Example of Matrix Multiplication in one dimen- |    |

|          |                    |                | sion                                                                | 51 |

|          |                    | 3.4.11         | Generating the Code: Example of Matrix Multiplication in second     |    |

|          |                    |                | dimension                                                           | 53 |

|          | 3.5                | Feedba         | ack Mechanism                                                       | 56 |

|          |                    | 3.5.1          | Case 1: Feedback to Code Transformer                                | 57 |

|          |                    | 3.5.2          | Case 2: Feedback to Data distributor                                | 58 |

| 4        | <b>F</b>           | ~~ <b>.</b>    |                                                                     | 62 |

| 4        | <b>ь</b> хр<br>4.1 | erimer         | iment of ADI                                                        | 62 |

|          | $4.1 \\ 4.2$       | -              | iment of Matrix Multiplication                                      | 66 |

|          | 4.2                | 4.2.1          | Gentlemans Algorithm of Matrix Multiplication                       | 66 |

|          |                    | 4.2.1<br>4.2.2 | Performance data                                                    | 67 |

|          |                    | 4.2.2          |                                                                     | 07 |

| <b>5</b> | Pre                | liminar        | ry Extension                                                        | 73 |

|          | 5.1                | Naviga         | ational Programming on Cloud                                        | 73 |

|          | 5.2                | Investi        | gation and Future Improvement                                       | 76 |

|          |                    |                |                                                                     |    |

| 6        |                    |                | Vork/Literature Review                                              | 79 |

|          | 6.1                |                | outed Parallel Programming                                          | 79 |

|          | 6.2                |                | elizing Compilers                                                   | 82 |

|          | 6.3                | Cloud          | Computing                                                           | 83 |

| 7        | Cor                | clusior        | n                                                                   | 86 |

| •        | 7.1                |                | -<br>bution                                                         | 86 |

|          | 7.2                |                | e Works                                                             | 88 |

|          |                    | _              |                                                                     | _  |

| Bi       | bliog              | graphy         |                                                                     | 89 |

## LIST OF FIGURES

### Page

| $2.1 \\ 2.2$ | Four Traveler's Traces                                                         | 7<br>7 |

|--------------|--------------------------------------------------------------------------------|--------|

| 2.3          | NavP View:Itineraries of trains                                                | 8      |

| 2.4          | Example: Three lines of code computing on distributed data (a) Sequential .    | 8      |

| 2.5          | Example: Three lines of code computing on distributed data (b) MP              | 9      |

| 2.6          | Example: Three lines of code computing on distributed data (c) NavP            | 9      |

| 2.7          | Dependency Graph                                                               | 10     |

| 2.8          | SPMD MPI View                                                                  | 11     |

| 2.9          | NavP View                                                                      | 12     |

| 3.1          | The code transformations in NavP. (a) Sequential. (b) DSC                      | 17     |

| 3.2          | The code transformations in NavP. (c) Pipelining (d)Phase shifting             | 18     |

| 3.3          | Methodology                                                                    | 20     |

| 3.4          | Matrix Multiplication Sequential Pseudocode                                    | 21     |

| 3.5          | Matrix multiplication                                                          | 22     |

| 3.6          | ADI pseudocode                                                                 | 24     |

| 3.7          | Two data distribution patterns. (a) unstructured data distribution (b) twisted |        |

|              | data distribution                                                              | 25     |

| 3.8          | ADI Code and Execution Sequence                                                | 26     |

| 3.9          | Computing sequences of different number of tiles                               | 29     |

| 3.10         | Computing sequences of different number of tiles. (a) Original computation     |        |

|              | sequence of loop4 (b) Computing sequence of loop4 after tiling                 | 29     |

| 3.11         | Computing sequences of different number of tiles. (c) Computing sequence of    |        |

|              | loop4 with sub-tiles                                                           | 29     |

| 3.12         | DSC                                                                            | 31     |

| 3.13         | Pseudocode for DSC                                                             | 31     |

|              | Pseudocode for DSC in the 2nd dimension                                        | 33     |

|              | DSC in the second dimension                                                    | 34     |

| 3.16         | Loop4 pseudocode after assigning locations for tiles                           | 36     |

|              | Sub DSC in the second dimension                                                | 37     |

|              | Weighted Dependence Graph                                                      | 41     |

|              | Simplified Weighted Dependence Graph                                           | 43     |

|              | Pipelining in one dimensions                                                   | 45     |

| 3.21         | Phase shifting in one dimension                                                | 46     |

| 3.22 | Pipelining in both dimensions                                                                                                                                     |

|------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 3.23 | Phase shifting in both dimensions                                                                                                                                 |

| 3.24 | DPC Code                                                                                                                                                          |

|      | DPC Code Loop8                                                                                                                                                    |

| 3.26 | Pseudocode for pipelined DSC                                                                                                                                      |

| 3.27 | Pseudocode for DPC in one dimension                                                                                                                               |

| 3.28 | Pseudocode for pipelining in second dimensions                                                                                                                    |

| 3.29 | Pseudocode for full DPC in second dimensions                                                                                                                      |

| 3.30 | Different options of tiles for the same data distribution                                                                                                         |

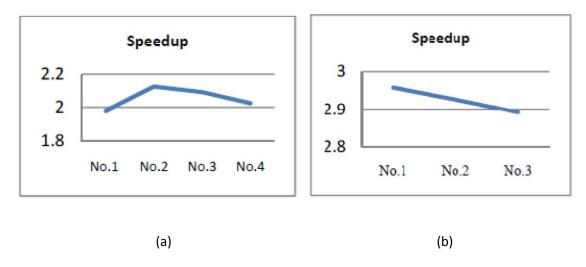

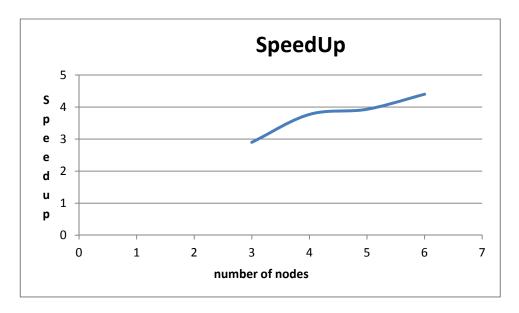

| 3.31 | (a) Speedup for different tile options for the unstructured data distribution                                                                                     |

|      | (b) Speedup for different tile options for the twisted data distribution                                                                                          |

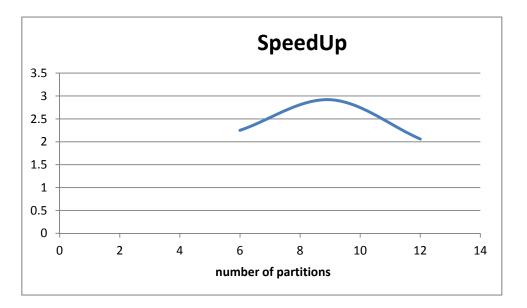

|      | Speedup achieved for the three cases of Fig.10                                                                                                                    |

| 3.33 | 6 partitions (2 partitions per node)                                                                                                                              |

| 3.34 | 9 partitions (3 per node) $\ldots \ldots \ldots$  |

| 3.35 | 12 partitions (4 per node) $\ldots \ldots \ldots$ |

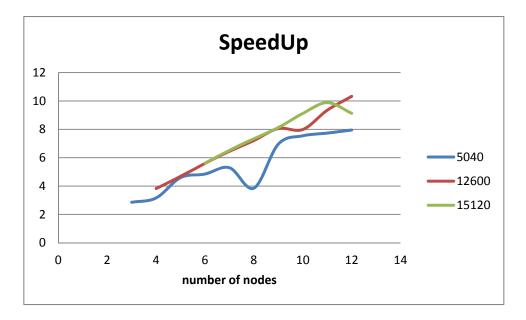

| 4.1  | Speedup with unstructured data distribution                                                                                                                       |

| 4.2  | Speedup with twisted data distribution                                                                                                                            |

| 4.3  | Pseudocode for Gentlemans Alg                                                                                                                                     |

| 4.4  | Performance on 3 PEs 69                                                                                                                                           |

| 4.5  | Performance on 8 PEs 69                                                                                                                                           |

| 4.6  | Performance on $2^*2$ PEs $\ldots \ldots \ldots$  |

| 4.7  | Performance on 3*3 PEs                                                                                                                                            |

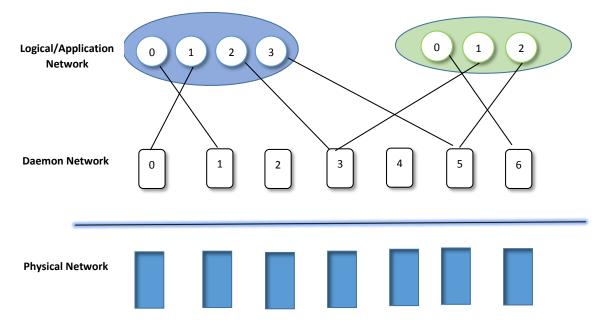

| 5.1  | Navigational Programming Architecture                                                                                                                             |

## LIST OF TABLES

### Page

| 4.1 | Speedup given unstructured data distribution. | 62 |

|-----|-----------------------------------------------|----|

| 4.2 | Speedup given twisted data distribution A     | 63 |

| 4.3 | Speedup given twisted data distribution B     | 63 |

| 4.4 | Speedup given twisted data distribution C     | 64 |

| 4.5 | Speedup given twisted data distribution D     | 64 |

| 5.1 | ADI Performance on Cloud                      | 77 |

## ACKNOWLEDGMENTS

I would like to express the deepest appreciation to Professors Lubomir F. Bic and Michael B. Dillencourt for their encouragement, advices, supports along the way of my pursuing Ph.D research. They create an inspiring, exciting, creative and free research environment in MESSENGERS group. They have been always there to have constructive discussion whenever I have had new ideas or questions. They have been encouraged me to overcome all of the challenges and steadily achieve my goals. And, I feel privileged and honored to have Professor Amelia C. Regan on my dissertation committee. Without them, the dissertation could not been finished, without them, I could not reach this point. I would like to thanks for their supports from bottom of my hearts.

Many thanks to Professor Isaac D. Scherson, Tony Givargis and Michael Dessen who also in my advancement and topic defense committees. I thank each of them for their time and helpful comments.

During my studies at University of California, I have privilege to work with members' MES-SENGERS. Specifically thanks to Lei Pan, who discussed, encouraged and gave suggestions and comments, worked with me on few papers. Really enjoyed the time we spent together with MESSENGERS, during weekday and weekend. Appreciate helps from Koji Noguchi and Ming Kin Lai for their discussion regarding running MESSENGERS system and their support of implementation. Also, I feel pleasure to work with Qinghong Shang on implementation and many thanks for her to cooperate together on papers.

## CURRICULUM VITAE

### Wenhui Zhang

#### **EDUCATION**

| Doctor of Philosophy in Computer Science                      | 2014                                     |

|---------------------------------------------------------------|------------------------------------------|

| University of California, Irvine                              | Irvine, CA                               |

| Master of Computer Science<br>University of California        | <b>2006</b><br><i>Irvine</i> , <i>CA</i> |

| Master of Computer Engineering                                | 1999                                     |

| Chinese Academy of Sciences Institute of Computing Technology | Beijing, China                           |

#### **EXPERIENCE**

| Senior Staff Software Engineer | 2012 – 2014        |

|--------------------------------|--------------------|

| Broadcom Corporation           | Irvine, California |

Software/Firmware Engineer Newport Electronics Inc.(Omega Engineering Inc.)

#### Software Engineer

China Internet Network and Information Center

2008 - 2012Santa Ana, California

1998 - 2002

Beijing, P.R.China

#### PUBLICATIONS

#### Incremental Parallelization with Migration

Zhang, Wenhui, Lei Pan, Qinghong Shang, Lubomir F. Bic, and Michael B. Dillencourt, In Parallel and Distributed Processing with Applications (ISPA), 2012 IEEE 10th International Symposium on

#### Incremental parallelization using Navigational Pro- 2005 gramming: A case study

Pan, Lei, Wenhui Zhang, Arthur Asuncion, Ming Kin Lai, Michael B. Dillencourt, and Lubomir F. Bic. , In Parallel Processing, 2005. ICPP 2005. International Conference on

# JaMes: A Java-based System for Navigational Pro- 2011 gramming.

Qinghong Shang, Munehiro Fukuda, Wendy Zhang, Lubomir Bic, and Michael B. Dillencourt., In Computational Problem-Solving (ICCP), 2011 International Conference on, pp. 444-449. IEEE, 2011

#### JOURNAL PUBLICATION

#### Toward incremental parallelization using navigational 2006 programming

Lei Pan , Wenhui Zhang , Arthur Asuncion , Ming Kin Lai , Michael B. Dillencourt , Lubomir F. Bic, IEICE Trans. Inf. and Syst., Vol. E89-D, No. 2, pp. 390-398,

#### TECHNICAL REPORTS

### Incremental Parallelization Using Navigational Pro- 2005 gramming: A Case Study

Lei Pan , Wenhui Zhang, Arthur Asuncion, Ming Kin Lai, Michael B. Dillencourt, Lubomir F. Bic, UCI Technical Report: TR-05-04, 2005

2012

### ABSTRACT OF THE DISSERTATION

Incremental Parallelization with Migration

By

Wenhui Zhang

Doctor of Philosophy in Information and Computer Science

University of California, Irvine, 2014

Professor Lubomir F. Bic, Co-Chair Professor Michael B. Dillencourt, Co-Chair

This dissertation presents a new methodology for developing parallel distributed programs in a series of incremental steps to achieve incremental parallelism and incremental performance improvement. The methodology takes advantage of threads that are able to migrate through the network and thus are able to follow distributed data. This allows the data to be partitioned and distributed first, which guarantees that elements that are used together in a computation are collocated on the same node. Next, the loops in the code are tiled to minimize migration among nodes. After deciding on the location at which each loop is to execute, the necessary migration and remote access statements are inserted to make the code executable. This process is repeated based on feedback obtained from the execution, which may improve the overall performance by suggesting a different data distribution or a different coarseness of tiling. We show each steps and the performance data for two wellknown application. Also, we illustrate the trade-offs using a well-known application with two different data distributions.

## Chapter 1

## Introduction

## 1.1 Research Motivation and Target Problem

Generating a parallel program from a sequential one for a distributed-memory environment is an important and difficult problem. A common approach is to decompose the original program into smaller computations and then to construct a distributed schedule for the computations [5, 15, 20, 21, 28, 53, 60, 64, 69]. The distributed scheduling task consists of several subtasks: assigning each computation to a processor, chronologically ordering the computations on each processor, and scheduling the data movement so that each computation has the necessary data when it executes. This is difficult under the classical message-passing approach, in which processes are stationary and any remote data required by a process is communicated through send/receive primitives.

The Navigational Programming (NavP) [34] [39] approach to generating a distributed parallel program can be summarized as follows. (1) the data are distributed; (2) the program is divided into computations (tiles) based on the data distribution, and each computation is assigned to a processor (again based on the data distribution); (3) the computations are

scheduled in those tiles and combined into parallel threads that migrate through the network based on their data dependencies.

NavP [40] is still considered SPMD (Single Program Multiple Data) in that different processes execute the same code with different data, and differs from the traditional SPMD view [40, 41] in that processes are able to access remote data by migrating to the target node. Hence the locus of any given computation is not stationary but follows the distribution of data as appropriate for best performance.

All three steps are extensions of existing techniques and tools. Data distribution (step 1) uses an affinity graph [43] produced by instrumenting the program and then partitioning the graph using Metis [26]. To break the program into subcomputations (step 2) we rely on the well-known techniques of tiling [23, 24, 52, 67, 68]. The main difference is that the execution provides feedback that guides the choice of the tile size. Scheduling (step 3) is performed only after each computation has been assigned a processor. It is straight forward because it follows the existing data dependencies; it is a form of dataflow scheduling [2, 56].

The NavP-based methodology provides two major advantages for distributed parallel programming:

- 1. Incremental parallelism. The sequential program evolves into the distributed program in a series of incremental steps: the data is distributed, the program follows the data, the program is divided into smaller computational units, the computational units are scheduled. At any point during this evolution there is a viable (executable) program that has the same semantics as the original sequential program. One consequence of this is that it is possible to return to any decision made during the generation of the parallel program, change the decision, and continue the generation process from that point forward.

- 2. Incremental performance improvement. The feedback mechanism provides per-

formance evaluations, including speedup and load balance, that can be used to adjust the output of the preceding steps. In this way, the methodology is a closed-loop system that incrementally improves the performance of the parallel and distributed program.

What enables the incremental parallelization and performance improvement is computation mobility. Our approach uses the principle of *pivot-computes*, which is different from the commonly used *owner computes* [16]. Pivot computes performs the computation on the node that contains the largest portion of the data, regardless of whether it owns it (writes it) or only reads it and then writes it on some other node. This is only possible if computations can migrate to the data. Consequently, the data layout can be decided first, the computations then follow the data distribution. This simplifies the programming task because it decouples the two main problems: data distribution/placement and code parallelization.

Another consequence of distributing data first is better performance, since migrating computation to data is frequently more efficient (only the state moves, not the code) than moving the data to computation.

This thesis presents a new methodology for developing parallel distributed programs in a series of incremental steps to achieve incremental parallelism and incremental performance improvement. The methodology takes advantage of threads that are able to migrate through the network and thus are able to follow distributed data. This allows the data to be partitioned and distributed first, which guarantees that elements that are used together in a computation are collocated on the same node. Next, the loops in the code are tiled to minimize migration among nodes. After deciding on the location at which each loop is to execute, the necessary migration and remote access statements are inserted to make the code executable. This process is repeated based on feedback obtained from the execution, which may improve the overall performance by suggesting a different data distribution or a different coarseness of tiling.

## **1.2** Dissertation Overview and Organization

Navigational Programming (NavP) offers a different approach to generating a distributed parallel program from a sequential one, in that the transformation occurs incrementally and produces an executable program at each stage. Under NavP, computations migrate using hop() statements inserted explicitly by the programmer. The cost of a hop() is essentially the cost of moving the data stored in its thread variables plus a small amount of state data. Although the state of the computation is moved on each hop, the code is not moved. The computations carry small amounts of data, such as intermediate results, as they migrate to large data structures that are stationary. The synchronization among different migrating computations is achieved by waiting on and posting of events.

In this dissertation, we describe the methodology of Incremental Parallelization with Migration. In Chapter 2, We introduce the navigational programming. Chapter 3 presents the methodology of Incremental Parallelization with Migration, and describes its steps using two examples [71] [44]. Chapter 4 shows the performance data for two examples, also compares the performance of NavP and MPI implementations [71] [44]. Chapter 5 gives a proof-of-concept extension of NavP on cloud with preliminary results and future improvement. Chapter 6 discusses related works. Finally, we conclude in Chapter 7 with a summary of the contributions of this dissertation and suggestions for further research.

## Chapter 2

## **Navigational Programming**

### 2.1 Overview

Navigational Programming (NavP) [34] [39] [30] is a methodology for distributed parallel programming based on the use of self-migrating computations. In NavP code, a programmer inserts navigational commands, i.e., hop() statements, to migrate the computation locus in order to access remotely distributed data and spread out computations. Small data is carried by the moving computation in agent variables, which are private to a computation thread and available to the thread wherever it migrates. Large data that stays on a computer is held in node variables that are resident on a particular PE (processing element) and are shared by all computation threads currently on that PE. The cost of a hop() is essentially the cost of moving the data stored in agent variables plus a small amount of state data. Although the state of the computation is moved on each hop, the code is not moved. The synchronization among different migrating computations is done through events (signalEvent() and waitEvent()). A programmer can inject, or spawn, a migrating thread at command line. The injection of a thread can also be done by another thread, called a spawner. All injections happen locally (i.e., a thread can spawn another thread only on the node on which it currently resides).There are two kinds of variables in NavP programming, one is called node variable, which is usually for large amount of data and stay in one node. It could be used for synchronizing between different threads/processes in the same node. The other is thread-carried variable which is useful for migrating with the threads.

NavP provides a different view of distributed computation from the classical SPMD (Single Program Multiple Data) view [40, 41]. The SPMD view describes distributed computations at stationary locations, while the NavP view describes a computation following the movement of its locus. The NavP view changes the way distributed parallel programs are composed and provides some new benefits.

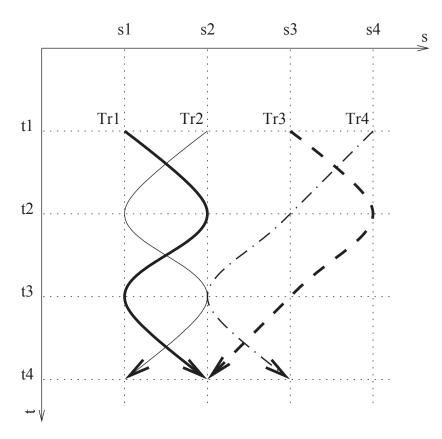

The good example to show the differences of those two views is the train example [39]. A train goes across the cities and arrives and departures at certain stations at certain time. The train schedulers and the taxi drivers are interested in when a train arrives at what time at what station, whereas, the travelers are interested in ternary which shows the sequences of time and station that my train will arrive in order. Fig. 2.1 shows the traces of four travelers. So Fig. 2.2 [39] shows the view of schedulers and taxi drivers, which is SPMD MPI view, and Fig. 2.3 shows the view of travelers, which is NavP view. Those two views are all useful and for different purposes. NavP view is for programmers to navigate computation across distributed systems.

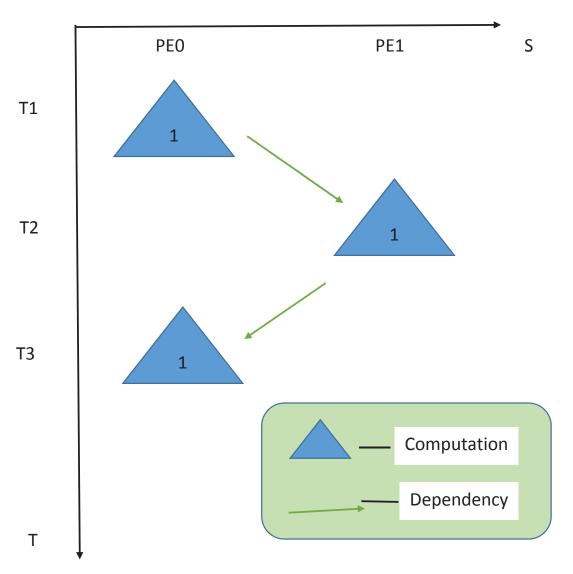

We use a code example [39] which only has three lines of sequence code to show the differences of the two different views (SPMD via NavP). The sequential algorithm is listed in Fig. 2.4. A and B are blocks with order n, and v1, v2 and v3 are vectors with size n. Line (1) gets the diagonal entries of matrix A and assigns them to the intermediate vector v1. Line (2) multiplies the matrix B by the intermediate vector v1, and assigns the intermediate result to the vector v2. At the end, ine (3) computes the matrix A by the intermediate vector v2 and assigns the result to the final vector v3.

We assume A and B are too large and cannot be hold in one physical node. Fig. 2.5 list the

Figure 2.1: Four Traveler's Traces

|    | s1  | s2      | s3  | s4  |

|----|-----|---------|-----|-----|

| t1 | Tr1 | Tr2     | Tr3 | Tr4 |

| t2 | Tr2 | Tr1     | Tr4 | Tr3 |

| t3 | Tr1 | Tr2,Tr4 | Tr3 |     |

| t4 | Tr2 | Tr1,Tr3 | Tr4 |     |

Figure 2.2: SPMD MPI View: Arrivals Departures at stations

|    | Tr1 | Tr2 | Tr3 | Tr4 |

|----|-----|-----|-----|-----|

| t1 | s1  | s2  | s3  | s4  |

| t2 | s2  | s1  | s4  | s3  |

| t3 | s1  | s2  | s3  | s2  |

| t4 | s2  | s1  | s2  | s3  |

Figure 2.3: NavP View: Itineraries of trains

(1) v1 = diag (A)

(2) v2 = Bv1

(3) v3 = Av2

Figure 2.4: Example: Three lines of code computing on distributed data (a) Sequential

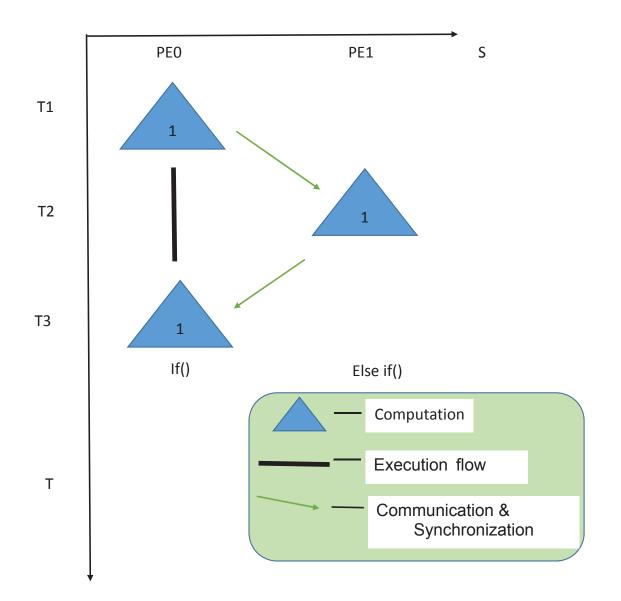

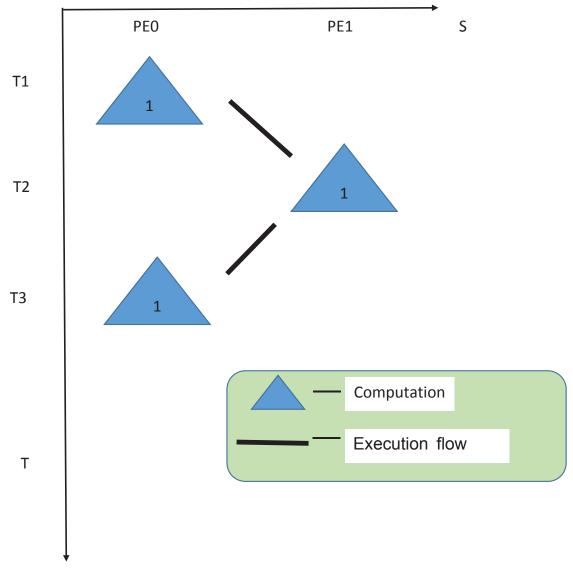

pseudocode for MPI, which needs to distinguish whether the node is PE 0 or PE1. If in PE0, it needs first getting A and sending to PE0, then, waiting for B from PE1, finally computing the final resultl; if in PE1, first it needs waiting from A from PE0, computing and sending intermediate result to PE0. Fig. 2.6 list the pseudocode for NavP, which is computational view, just needs to follow the execution flow going across the nodes.

Fig. 2.7 [39] shows the dependency graph in distributed system. Fig. 2.8 [39] shows the SPMD MPI view to distinguish different nodes and Fig. 2.9 [39] shows NavP view which just follow the execution flows going across distributed nodes.

A NavP application consists of a dynamically created, set of autonomous threads which can migrate through the network and communicated with each other in various ways.

```

(0.1) if (rank == PE0)

(1) v1 = diag (A)

(1.1) Send(v1, PE1)

(1.2) Recv(v2, PE1)

(3) v3 = Av2

(3.1) else if (rank == PE1)

(3.2) Recv(v1, PE0)

(2) v2 = Bv1

(2.1) Send(v2, PE0)

(2.2) end if

```

Figure 2.5: Example: Three lines of code computing on distributed data (b) MP

(1) mv1 = diag (A) (1.1) hop(PE1) (2) mv2 = B mv1 (2.1) hop(PE0) (3) v3 = A mv2

Figure 2.6: Example: Three lines of code computing on distributed data (c) NavP

## 2.2 Characteristics

A preliminary version of the NavP model was presented in [29, 58], and NavP is keeping improved since then [34] and extends with Java version [57]. The following list the key characteristics of NavP:

- Self-migration: A process is able to pack up its state, recreate itself on another node within the logical network, and to continue executing at the remote site. If the original process then dies after recreating itself, this operation is called a hop operation. If the caller continues, this is called a clone operation.

- Priority-based migration: Certain applications require that processes arriving at a particular node from different locations are processed in a certain predefined order. To make this more efficient, we allow processes to specify a priority as part of their migration statement. The receiving node maintains all arriving processes in a priority

Figure 2.7: Dependency Graph

Figure 2.8: SPMD MPI View

Figure 2.9: NavP View

queue ordered by process priority. When the currently-running process gives up the CPU, it is placed appropriately in the ready queue according to its priority, and the highest-priority process is selected to run next.

- Stationary and mobile data: There are two kinds of variables in NavP programs. Mobile data is private to each process and its carried with it as the process migrates among the machines. Stationary data is bound to a specific logical node and is accessible to processes currently residing on that logical node.

- Process interaction: Processes can interact with each other only when they reside on the same logical node. Data communicating is achieved through shared node variables. Process synchronization is achieved through events and wait/signal operations.

- Non-preemptive scheduling: NavP assumes a nonpreemptive scheduling discipline, which simplifies issues of synchronization. On each node, there is only one execution thread running at any time. An execution thread cannot be preempted. The only way it can be blocked is when it blocks itself by issuing specific commands such as wait(), yield(), or a blocking receive request. Nonpreemptive scheduling eliminates the need for explicit critical sections when accessing shared variables and reduces contextswitching overhead.

- Synchronization: The extended NavP model provides events and the standard primitives of wait and signal for synchronizing threads on the same logical node. Applications can create any number of distinct events. If an event has not been signaled, a wait operation on that event causes the thread to become blocked. When the event is signaled, the process becomes unblocked and becomes eligible for scheduling. An event can only be signaled once. Any process that waits on an event that has already been signaled is not blocked. A process can wait on multiple events, specified as an array of events, all of which must be signaled before the process can continue. A process can also wait on a disjunction of events, in which case it will be awakened when at least

one of the events has occurred and a return value will tell it one of the events that has occurred.

• Remote process interaction: In the basic NavP model, the only mechanism for interprocess communication is the shared node variable area. This means that for two processes to communicate, they must reside on the same logical node. This has the advantage of simplicity, but it may also introducing unnecessary migrations to access remote data. The extended NavP model solves this problem by introducing a form of remote communication between threads on different machines. This can take two different forms, both of which allow a process to deposit data into a named mailbox without migrating to the target. The difference is on the receiving side. In the first form, which corresponds to a conventional send/receive, there is a corresponding receive command in which the receiver specifies how data sent to that mailbox is to be handled. In the second form, which is a remote write operation, the receiver specifies once how data sent to this mailbox is to be handled. Each time data is sent to the mailbox, the specified handler is automatically invoked.

## Chapter 3

## **Incremental Parallelization**

### 3.1 Methodology Overview

Navigational Programming (NavP) [34] [39] offers a different approach to generating a distributed parallel program from a sequential one, in that the transformation occurs incrementally and produces an executable program at each stage. Under NavP, computations migrate u[34] [39] sing hop() statements inserted explicitly by the programmer. The cost of a hop() is essentially the cost of moving the data stored in its thread variables plus a small amount of state data. Although the state of the computation is moved on each hop, the code is not moved. The computations carry small amounts of data, such as intermediate results, as they migrate to large data structures that are stationary. The synchronization among different migrating computations is achieved by waiting on and posting of events.

The NavP approach to generating a distributed parallel program can be summarized as follows. (1) the data is distributed; (2) the program is divided into computations (tiles) based on the data distribution, and each computation is assigned to a processor (again based on the data distribution); (3) the computations are scheduled in those tiles and combined into parallel threads that migrate through the network based on their data dependencies. The NavP methodology consists of the following steps.

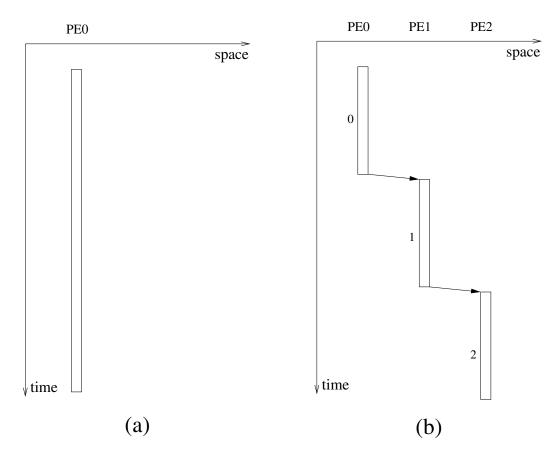

The transformations under the NavP view are depicted in Fig. 3.1 and Fig. 3.2. The arrows indicate hop() operations. The basic idea behind the transformations is to spread out computations using self-migrating computation threads as soon as possible without violating any dependency conditions.

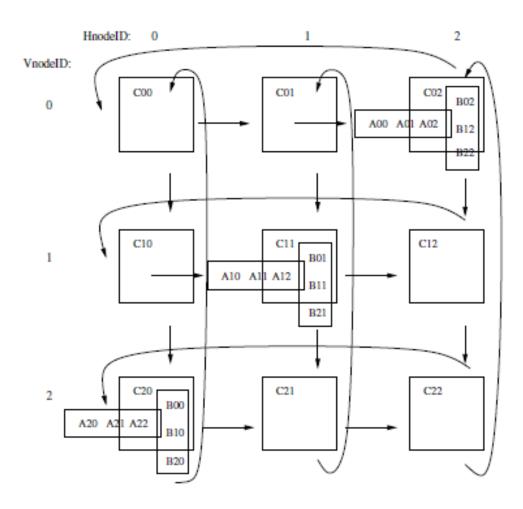

The basic idea of distributed sequential computing(DSC)[42] Transformation is that Large data is distributed among the PEs, and hop() statements are inserted into the sequential code in order for the computation to chase large data while carrying small data. The DSC Transformation is schematically depicted by Fig. 3.1(a) and (b). The resulting program performs distributed sequential computing. The immediate benefit of DSC is that, with a small amount of work, a sequential program can efficiently solve large problems that cannot fit in the main memory of one computer. By using a network of workstations, the DSC program removes paging overhead by trading it against a modest amount of network communication [29]. DSC also serves as the starting point of parallel program development in NavP.

Distributed and parallel computing (DPC) could have more than one forms. for example: Pipelining form: This transformation is depicted by (b) and (c). The basic idea is to overlap the execution of multiple DSC threads by staggering their starting times. Synchronization may be necessary to ensure that the data dependencies among the DSC threads are not violated. Or DPC could be Phase-shifting form: Sometimes the dependency among different computations allows different DSC threads to enter the pipeline from different PEs. In these situations, we can phase shift the DSC threads to achieve full parallelism, as depicted in (c) and (d).

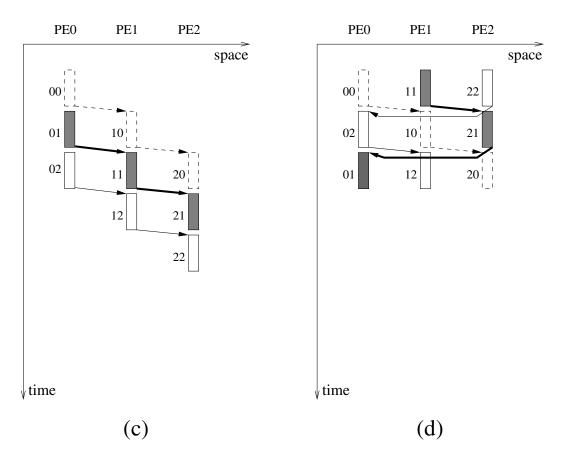

In summary, the NavP methodology consists of the following steps, illustrated in Fig. 3.3 with an example.

Figure 3.1: The code transformations in NavP. (a) Sequential. (b) DSC

Figure 3.2: The code transformations in NavP. (c) Pipelining (d)Phase shifting

- 1. Data distribution: This step runs the sequential program using a small data sample and generates the initial data partitioning and distribution.

- 2. Code Transformation: This step distributes the computation. It partitions the original sequential program into smaller units, based on the given data distribution, it assigns each unit to execute on one of the nodes, and it inserts appropriate navigational statements into the code. The resulting code is still sequential but it runs in a distributed manner using migration. This is referred to as distributed sequential computing (DSC).

- 3. Parallelization: This converts the single-threaded DSC into multiple threads. Each thread combines a number of units created in the previous step and adds signals to synchronize between different threads. Each of the threads is scheduled to run as early as possible, subject to the constraint that all dependencies must be respected. The result of this step is to generate distributed and parallel computing (DPC).

- 4. Feedback: This evaluates the performance of the DPC program in terms of speedup and load balance, by taking into account parallelism, communication cost, computation cost, and other overhead such as context switch. The purpose of this step is to provide information for the previous steps to improve performance.

After Data distribution, the data is distributed into different nodes represented by different shapes. After the Code Transformation, distributed sequential computing (DSC) is generated, it is still a single and sequential DSC thread but runs in a distributed manner using migration.after Parallelization, distributed and parallel code (DPC) is generated, it splits the single DSC thread into three threads and schedules those three threads as early as possible, which means that the resulting code is multi-threaded code and each of the threads is scheduled to run as early as possible, subject to the constraint that all dependencies must be respected. So, in this example, these three threads starts at the same time at different nodes consistent with the constrains of data dependencies.

Figure 3.3: Methodology

```

(1) do i=0,N-1

do j=0,N-1

(2)

(3)

t = 0.0

(4)

do k=0, N-1

(5)

t += A(i,k) * B(k,j)

(6)

end do

(7)

C(i,j) = t

(8)

end do

(9) end do

```

Figure 3.4: Matrix Multiplication Sequential Pseudocode

## 3.2 Two Examples

### 3.2.1 An Example of Matrix Multiplication

Matrix multiplication is a fundamental operation of many numerical algorithms. Pseudocode for sequential matrix multiplication is listed in Fig. 3.4. Throughout the paper, we assume N is the order of the square matrices.

Matrix A is divided by row blocks and matrix B is divided by column blocks (as shown in Fig. 3.5 ).

Figure 3.5: Matrix multiplication

#### 3.2.2 An Example of ADI

We will describe our methodology using the code shown in Fig. 3.4 as an example [31], which is an abstraction of a method for solving a 2-dimensional heat equation originally presented in [31]. The example is very good application which shows extensive both data communication and data computation, also strong data dependencies.

It solves a 2D heat equation using the alternating direction implicit (ADI) method, which is a finite difference method for solving parabolic, hyperbolic and elliptic partial differential equations in numerical analysis [1]. It used the PeacemanRachford algorithm to formulate the numerical solution of the partial differential equation as a second-order approximation by solving two sets of tridiagonal systems of linear equations. The variables of the first set of tridiagonal systems correspond to elements from each column of an intermediate matrix, and the variables of the second set of traditional systems correspond to elements from each row of a target matrix [62]. Using the Thomas algorithm, It reduce a traditional system of linear equations to three sets of first-order recurrence equations .

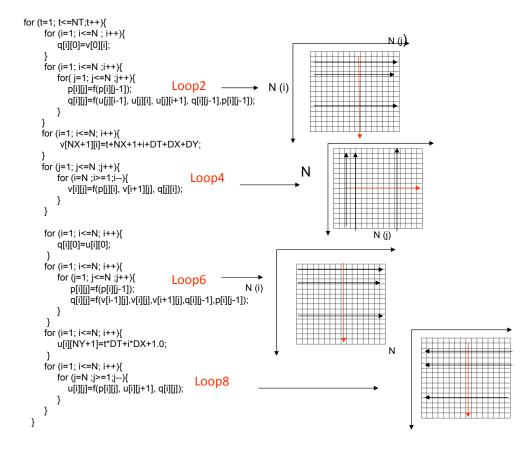

The example is a variant of the alternating direction implicit (ADI) method, which makes multiple sweeps in different directions across an array representing the discrete domain. The example shows four 2D arrays involved in the computation (u, v, p, and q). It also shows the computation kernel which consists of an outer loop (line 1) that repeatedly performs a column sweep phase (lines (2)-(18)) followed by a row sweep phase (lines (19)-(35)). The row sweep phase and the column sweep phase consist of four loops each, for a total of 8 inner loops performed for each iteration of the outer loop. In Fig. 3.8, it shows the execution sequences of the major four loops along with the pseudocode. In loop2, the inner loop computes from left to right and outer loop sweep from top to bottom. In loop4, the inner loop computes from bottom to up and outer loop sweep from left to right. In loop6, the inner loop computes from left to right and outer loop sweep from top to bottom. In loop8, the inner loop computes from left to right and outer loop sweep from top to bottom. In loop8, the inner loop computes from left to right to left and outer loop sweep from top to bottom.

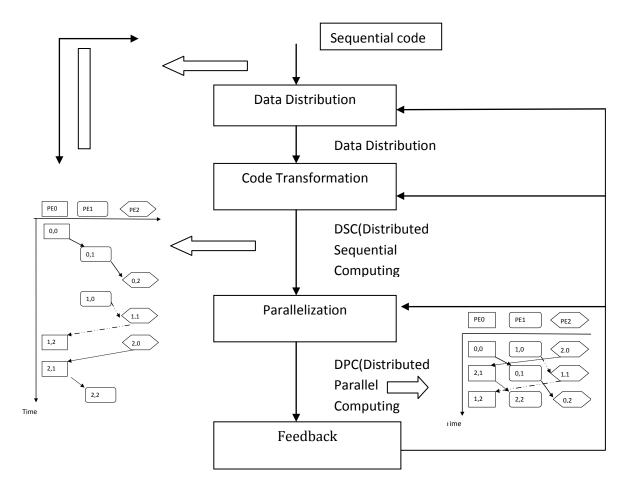

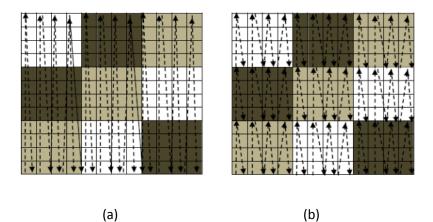

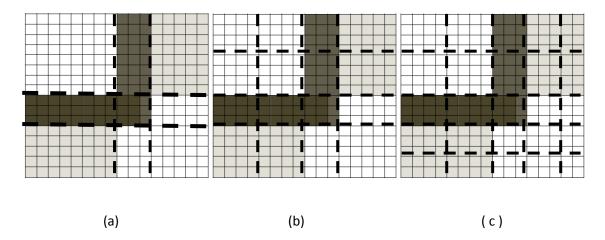

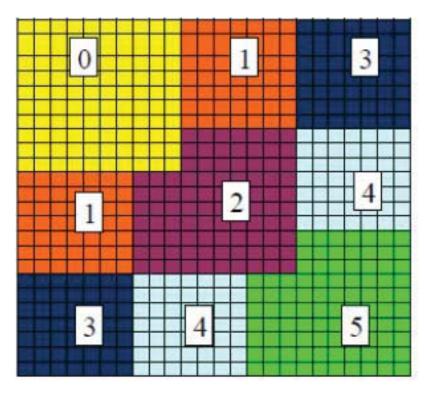

The methodology discussed in this paper takes a specified data distribution as a starting point. We use the two data distributions illustrated in Fig. 3.7 to show the methodology and compare the respective performance. The data distributions are shown for 3 nodes, each represented by a different shade. The first was generated by our Data Distributor [43]; while the second is the well-known twisted data layout [59]. In each distribution, all four 2D arrays (u, v, p, and q) are distributed as shown in the corresponding figure.

```

Perform NT iterations

(1) for (t=1; t<= ITERATIONS;t++){</pre>

//Column sweep

(2)

for (i=1; i<=N ; i++){</pre>

(3)

q[i][0]=v[0][i];

}

(4)

(5)

for (i=1; i<=N ;i++){</pre>

(6)

for( j=1; j<=N ; j++){</pre>

(7)

p[i][j]=F1(p[i][j-1]);

(8)

q[i][j]=F2(u[j][i-1],u[j][i],

u[j][i+1],q[i][j-1],

p[i][j-1]);

(9)

}

(10)

}

(11)

for (i=1; i<=N; i++){</pre>

(12)

v[NX+1][i] = t+NX+1+i+DT+DX+DY;

(13)

}

(14)

for (j=1; j<=N ;j++){</pre>

(15)

for (i=N ;i>=1;i--){

(16)

v[i][j]=F3(p[j][i],v[i+1][j],

q[j][i]);

(17)

}

(18)

}

// Row sweep

for (i=1; i<=N; i++){</pre>

(19)

(20)

q[i][0]=u[i][0];

}

(21)

for (i=1; i<=N; i++){</pre>

(22)

(23)

for (j=1; j<=N ;j++){</pre>

(24)

p[i][j]= F4(p[i][j-1]);

(25)

q[i][j]=F5(v[i-1][j],v[i][j],

v[i+1][j],q[i][j-1],

p[i][j-1]);

(26)

}

(27)

}

(28)

for (i=1; i<=N; i++){</pre>

u[i][NY+1]= t*DT+i*DX+1.0;

(29)

}

(30)

(31)

for (i=1; i<=N; i++){</pre>

(32)

for (j=N ;j>=1;j--){

u[i][j]=F6(p[i][j], u[i][j+1],

(33)

q[i][j]);

}

(34)

(35)

}

(36)}

```

Figure 3.6: ADI pseudocode

Figure 3.7: Two data distribution patterns. (a) unstructured data distribution (b) twisted data distribution

Figure 3.8: ADI Code and Execution Sequence

### 3.3 Code Transformation and Placement

Starting from the sequential code and an initial data distribution, we first build the DSC that navigates through the network and accesses the distributed data sequentially. The simplest way of constructing a working DSC program would be to insert conditional hop statements in the sequential program before each data access. The program resulting from this simple strategy would be correct, but it could be quite inefficient due to the large number of hops. To reduce the number of hops we first partition the iteration space into smaller tiles, which will be executed locally. As discussed below, we use tiling to reduce communication and increase the opportunity for parallelism. After the tiling operation is complete, we assign a location to each tile.

#### 3.3.1 Partitioning phase 1: Adapt to the data distribution

Tiling proceeds in two phases. The goal of the first phase, which is performed once, is to minimize communication overhead. The second phase, discussed in the next subsection, may be repeated multiple times and is intended to increase opportunities for parallelism.

We define the **write set** and **read set** of a tile to be, respectively, the set of all data written by and read by the tile. The partitioning in this first phase is then based on the following principles:

- 1. **Homogenous write sets**: All the writes to memory from any given tile are to data on a single machine.

- 2. Isothetic cuts: The write sets of the tiles are all rectangles and the boundaries between write sets of tiles all fall on a common set of vertical and horizontal lines.

- 3. Minimized communication: The tiles should be as large as possible, consistent with

the first two conditions.

The read sets are not necessarily homogenous. Condition 2 implies that all write sets are rectangles, but the rectangles do not necessarily have the same size. This can be seen in Fig. 3.30(a), which shows the result of applying phase 1 partitioning to the data distribution of Fig. 3.7(a).

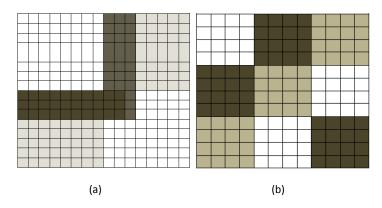

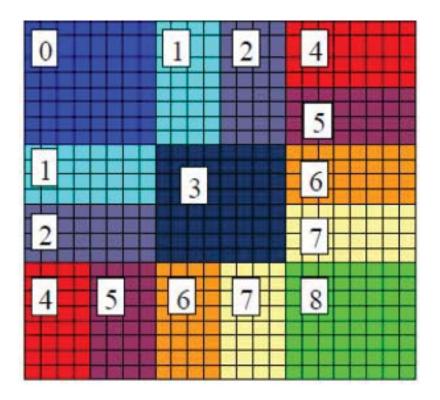

#### 3.3.2 Partitioning phase 1: Example of ADI

The tile size can be changed without changing the codes. Fig. 3.10 Fig. 3.11 illustrates the first phase of tiling for a  $3 \times 3$  twisted layout. Considering loop 4 (lines 14-18 of Fig. 3.6), if this loop is transformed to DSC simply by inserting hop statements, three hops would be required per column for a total of 3N hops (Fig. 3.10(a)). However, if the code is transformed as shown in Fig. 3.9, then only 9 hops are necessary for the entire loop as can be seen in Fig. 3.10(b).

Figure 3.9: Computing sequences of different number of tiles

Figure 3.10: Computing sequences of different number of tiles. (a) Original computation sequence of loop4 (b) Computing sequence of loop4 after tiling

(C )

Figure 3.11: Computing sequences of different number of tiles. (c) Computing sequence of loop4 with sub-tiles

### 3.3.3 Partitioning phase 1: Example of Matrix Multiplication in one dimension

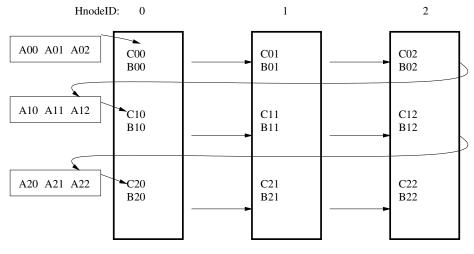

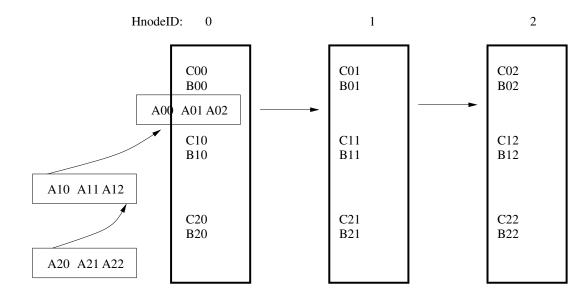

We first apply transformation to sequential matrix multiplication, as depicted in Fig. 3.12 where we assume N = 3. This DSC transformation essentially distributes the computation in the j dimension. The PE network is 1D in which each PE has a unique identifier HnodeID = 0, 1, ..., N - 1 from west to east. Again, the arrows represent hop() operations. Thick boxes contain node variables on different machines, and thin boxes carry agent variables. All PEs are assumed to be fully connected via a collision-free switch, rather than being connected as a ring. This assumption is true for most modern hardware environments, and it makes the initial staggering (i.e., moving the entries of the three matrices to the right places before any computation begins) faster, because each matrix entry can be shipped to any destination directly instead of having to go stepwise through a number of intermediate PEs.

Pseudocode for DSC matrix multiplication is listed in Fig. 3.12. In the pseudocode hereafter, A and B indicate node variables, whereas mA and mB represent agent variables. 1 Matrix A is loaded into agent variable mA and carried by the migrating thread.

In Fig. 3.13, matrix A is initially put on the PE with HnodeID = 0, and the columns of matrices B and C are distributed such that B(., j) and C(., j) are on the PE with HnodeID = j. In Fig. 3.13, node(j) maps to the PE that hosts column j of matrices B and C. Every time the computation thread hops back to node(0), it will pick up a different row of matrix A for the computation of the loop over j.

(1) hop(node(0))(2) inject(RowCarrier) (1) RowCarrier (2) do mi=0,N-1 do mj=0,N-1 (3) hop(node(mj)) (4) if(mj=0) mA(\*) = A(mi,\*) (5) t = 0.0(6) (7) do k=0,N-1 (8) t += mA(k) \* B(k)(9) end do (10) C(mi) = t(11)end do (12) end do (13) end

Figure 3.13: Pseudocode for DSC

# 3.3.4 Partitioning phase 1: Example of Matrix Multiplication in second dimension

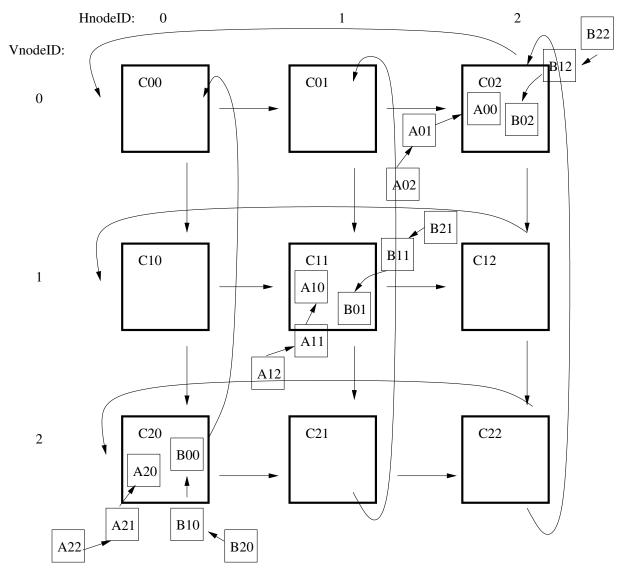

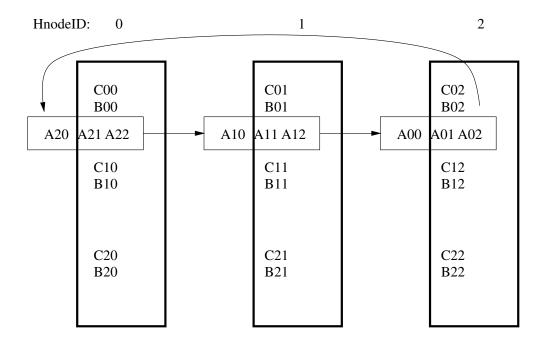

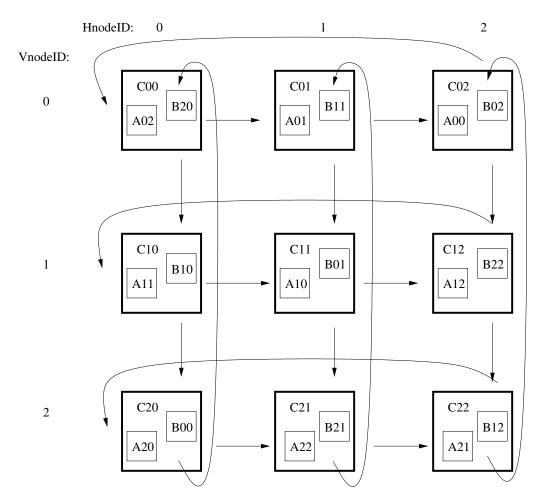

In second dimension, the first step is to introduce a 2D network in which each PE has a unique 2D identifier (HnodeID, VnodeID), where HnodeID = 0, 1, ..., N - 1 from west to east, and VnodeID = 0, 1, ..., N - 1 from north to south. Then the DSC Transformation is applied in the second dimension, as depicted in Fig. 3.15. Essentially, this DSC transformation further distributes the computations in the i dimension. Pseudocode for DSC in the second dimension is listed in Fig. 3.14. The rows of matrix A and columns of matrix B are carried in their corresponding agent variables mA and mB, respectively. The ColCarriers ship the B columns, and the RowCarriers use these B columns to compute with the A rows that they carry. The events are necessary because the consumers, i.e., the RowCarriers, need to hold on their computations until the producers, i.e., the ColCarriers, finish putting the columns of B in place. The matrices are initially distributed, as shown in Fig. 3.15 , such that A(N . 1 . l, .) and B(., l) are on node(N . 1 . l, 1), and C(i, j) (initialized to 0) is on node(i, j), where node(i, j) maps to the PE that hosts entry (i, j) of matrix C.

```

(1) do ml=0,N-1

(2)

hop(node(N-1-ml,ml))

inject(RowCarrier(N-1-ml))

(3)

inject(ColCarrier(ml))

(4)

(5) end do

(1) RowCarrier(int mi)

(2) mA(*) = A(*)

(3) do mj=0,N-1

hop(node(mi,(N-1-mi+mj)%N)

(4)

(5)

waitEvent(EP(mi,(N-1-mi+mj)%N))

do k=0, N-1

(6)

(7)

C += mA(k) * B(k)

end do

(8)

(9) end do

(10) end

(1) ColCarrier(int mj)

(2) mB(*) = B(*)

(3) do mi=0,N-1

hop(node((N-1-mj+mi)%N,mj))

(4)

(5)

B(*) = mB(*)

(6)

signalEvent(EP((N-1-mj+mi)%N,mj))

(7) end do

(8) end

```

Figure 3.14: Pseudocode for DSC in the 2nd dimension

Figure 3.15: DSC in the second dimension  $% \left( {{{\rm{DSC}}}} \right)$

#### 3.3.5 Partitioning phase 2: Increase opportunities for parallelism

The result of the first partitioning phase is a tiling with low communication cost. Splitting the tiles further will have two conflicting effects: it will increase the number of hops, but it will increase the potential for parallelism. The first effect will result in increased communication cost and hence decreased speedup, while the second effect will increase speedup.

#### 3.3.6 Partitioning phase 2: Example of ADI

As an example, Fig. 3.10(c) shows the result of splitting each tile into 4 subtiles. This transformation increases the number of hops from 9 to 36. It increases the opportunity for parallelism because, for example, the tile with write set c can begin executing as soon as the tiles with write sets a and b have completed. The tradeoffs between the increased communication cost and the increased opportunity for parallelism, and the optimal level of tile splitting that should occur, are difficult to evaluate a priori, as they depend on the tile size and on the order in which tiles are evaluated. These considerations suggest the following strategy: start with the largest possible tile; split the tiles; estimate the resulting speedup; and repeat these steps for as long as the estimated speedup continues to increase. The resulting feedback loop is discussed in Section VII. The result of this further partitioning is code that is identical to the code in Fig. 3.9. The only difference is that the parameters describing the number and extent of the blocks have changed.

```

for (J=0; J < num_blk_J; J++){</pre>

for (I = (num_blk_I-1); I >= 0; I--) {

if (I < num_blk_I)</pre>

x = load(v[i_end(I,J)+1])

[j_start(I,J)..

j_end (I,J)];

hop(comp_loc(I,J));

if (I < num_blk_I) unload(x);</pre>

for (j = j_start(I,J);

j <= j_end(I,J); j++)</pre>

for (i = i_end(I,J);

i >= i_start(I,J); i--)

v[i][j] = F3(p[j][i])

v[i+1][j],q[j][i]);

}

}

```

Figure 3.16: Loop4 pseudocode after assigning locations for tiles

# 3.3.7 Partitioning phase 2: Example of Matrix Multiplication in second dimension

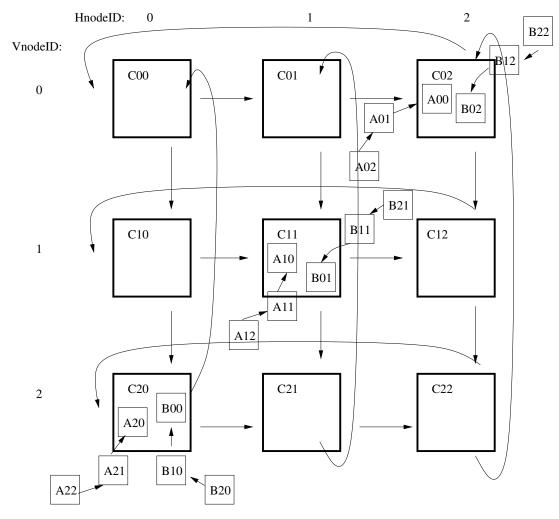

We apply the Phase 2 Transformation in both dimensions, as depicted in Fig. 3.17. Basically, a pair of A and B entries can move on along their pipelines respectively as soon as they finish computing and contributing the corresponding C entry. A producer BCarrier needs to make sure that the B entry produced by its predecessor in the pipeline is consumed before it puts the B entry it carries in place. This is the reason for a second event EC(., .). Pseudocode for DSC with pipelining in both dimensions is listed in Fig. ??. The entries of matrices A and B are carried in their corresponding agent variables mA and mB, respectively. The matrices are initially distributed, as shown in Fig. 3.17, such that A(N . 1 . 1, .) and B(., .) are on node(N . 1 . 1, 1), and C(i, j) (initialized to 0) is on node(i, j). An event EC(i, j) is signaled on node(i, j) for all values of i, j initially.

Figure 3.17: Sub DSC in the second dimension

#### 3.3.8 Assigning a location to each tile

Once the size of the tiles has been chosen, each tile needs to be assigned to one of the nodes. In most cases this is a straightforward procedure: all writes from each tile are to variables on the same node, and often the best strategy is to assign the tile to that node. This is consistent with the well-known owner-computes strategy [16].

The strategy that we actually use is to assign each tile to the node that holds the most data accessed by the tile (either as part of the read set or the write set). We call this node the pivot node, and we call the resulting strategy pivot-computes [42]. The pivot-computes strategy can result in significantly less data movement in certain situations, such as a REDUCE-type operation where a large amount of data stored on one node is summarized in a few variables stored on a second node. In this case, performing the computation on the node that holds the read set is more efficient than the node that writes the final value. For a specific example see [41]. The two strategies frequently produce the same result, as they do with the examples of this paper.

Once a tile has been assigned to a node, additional code is inserted to ensure that the execution is performed on the chosen node and all necessary data is carried there. Fig. 5 shows the result of inserting this code in the code of Fig. 3.9. The additional partial row of v necessary for the tile computation is loaded into the local variable x. After the hop to the node where the computation will occur, the data carried in x is unloaded.

### 3.4 Parallelization Generation

The result of the previous steps is a set of code tiles, each of which has been assigned to a node. The next step is to turn these into a parallel program. The fact that each tile has already been assigned a node makes this step relatively straightforward: all that is needed is to group the tiles into threads and insert appropriate commands for synchronization and transfer of data among threads. This step proceeds in three stages. First we build a Weighted Dependence Graph which captures the essential dependency relations among the tiles. Next we combine the tiles into threads. At this point, we can pass the Weighted Dependence Graph and thread information to the Feedback Mechanism. Based on the feedback, we may decide to go back and change some decisions made during the earlier code transformation and placement phase or to change the data distribution. If we are satisfied with the results of the feedback, we proceed to the third state, which is the generation of the parallel code.

#### 3.4.1 Building the Weighted Dependence Graph

The Weighted Dependence Graph is a precedence graph that captures the relationships among the tiles derived using the code transformation. Each node represents a tile. All edges are directed and indicate that the tile corresponding to the origin node must be computed before the tile corresponding to the destination node.

Each node is assigned a cost, which is the relative amount of computation required by the corresponding tile. Associated with each edge is the communication cost and context switching cost associated with that edge. The context-switching cost is taken to be constant. The communication cost is zero if the two endpoints of the edge are tiles assigned to the same node. Otherwise, the cost is a function of the amount of data that needs to be moved, using a piecewise-linear communication cost model that takes into consideration packet size, latency per packet of the given size, and bandwidth [65].

To estimate the communication cost, we use a piecewise linear communication cost model. Instead of applying fixed latency, we use different latencies in different packet size ranges. The latency for a packet is fixed if the packet size is within a certain range of size. The latency changes if the packet size increases to reach another range of size due to the presence of Maximum Transmission Unit (MTU). MTU is the packet size that a network can transmit and measured in bytes. The communication cost for a packet is per packet latency plus a per Byte bandwidth cost. A node may communicate with a number of other nodes at the same time, and many nodes may communicate with each other at the same time. So, given the limited network resources, the congestion and contention may happen and they have random costs. Our piecewise linear model assume congestion and contention free network which is the reality in most modern network for the purpose of high performance computing.

In mathematics, a transitive reduction of a binary relation R on a set X is a minimal relation R' on X such that the transitive closure of R' is the same as the transitive closure of R. The transitive reduction of a finite acyclic graph is unique. We apply transitive reduction to the Weighted Dependence graph. During the reduction, only the edges with the property of Zero cost can be reduced, because if an edge not only represents synchronization, but also carries data, the edge cannot be removed. If the edge only represents synchronization, the edge can be reduced if other edges guarantee the data dependence relation of this edge.

Once the graph has been constructed, we simplify it using a restricted form of transitive reduction: If an edge in the Weighted Dependence Graph only represents synchronization (i.e., carries no data) and if other edges guarantee the precedence relation represented by the edge, the edge can be removed.

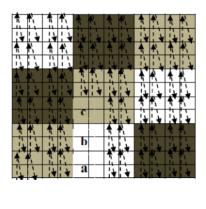

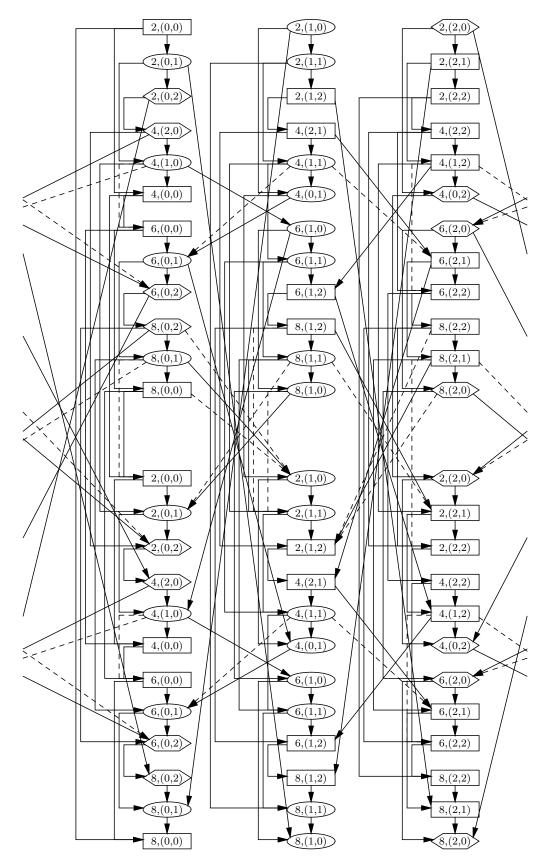

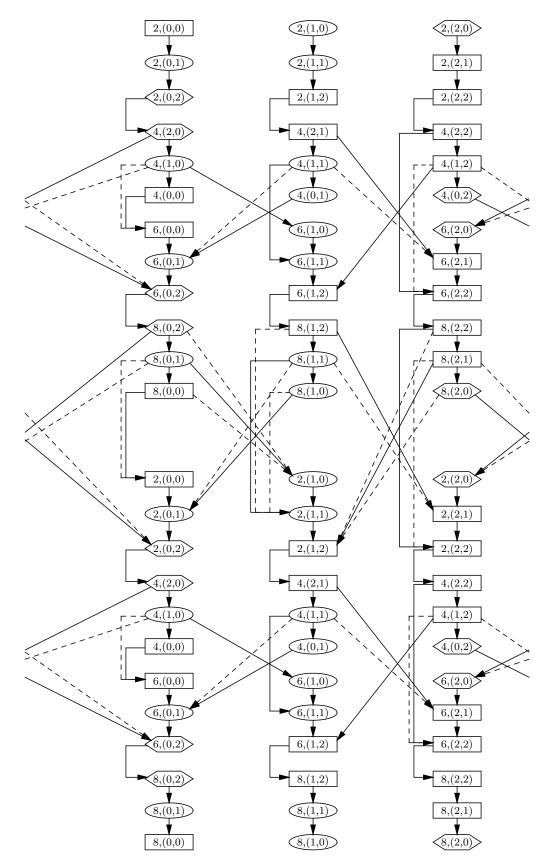

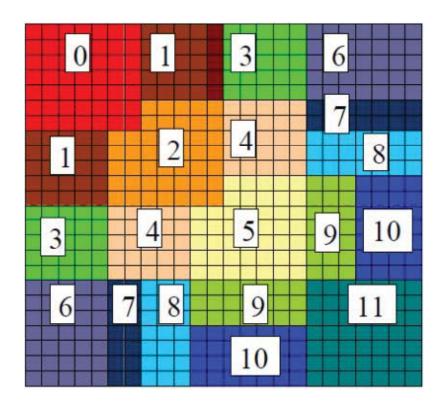

#### 3.4.2 Building the Weighted Dependence Graph: Example of ADI

Fig. 3.18 shows original Weighted Dependence Graph corresponding to loops 2, 4, 6, and 8(Loops 1, 3, 5, and 7 are used only for initialization and are omitted to simplify the presentation). Fig. 3.19 shows the reduced or simplified Weighted Dependence Graph. The shapes of the graph nodes represent the processing node where the computation is executed. There are three different shapes because the data are distributed over three processing nodes. Each

Figure 3.18: Weighted Dependence Graph

graph node is annotated L(I,J), where L is the loop number and the pair (I,J) is the write set of the tile. For example, 4(0,1) means loop4 and (0, 1) is its write set, where I=0 and J=1. A solid edge means that a whole data block has to be transferred, while a dashed edge means that the data dependence consists only of boundary data.

### 3.4.3 Building the Weighted Dependence Graph: Example of Matrix Multiplication

Since the matrix multiplication has no data dependencies, so, it could perform multiple element calculations concurrently as long as each core only compute one element at the same time. Therefore, there is no need to build dependence graph. However, since matrix A and B are not duplicated in each node and only have one copy, the carries of certain row of matrix A and certain column of matrix B needs to be at the same node at the right timing, so still needs synchronization to fully paralleled.

#### 3.4.4 Combining tiles into threads

To create execution threads from the reduced graph, we use a bottom up approach. Initially each tile is considered a separate thread. These are then combined into longer threads.

#### 3.4.5 Generating threads for ADI

There are many ways to combine the tiles into a thread. We apply a heuristic strategy, which combines threads inside a single loop within the same global iteration. Our heuristic threads together tiles that cannot be executed in parallel. In particular, it combines tiles connected by edges because the data dependencies require such tiles to be executed sequentially. For

Figure 3.19: Simplified Weighted Dependence Graph

example, in Fig. 3.18, for loop2, tile (0,0), (0,1), (0,2) are grouped into a thread, tile (1,0), (1,1), (1,2) are grouped into a thread, and tile (2,0), (2,1), (2,2) are grouped into a thread.

# 3.4.6 Generating threads for Matrix Multiplication in one dimension

Since there is no data dependencies among the DSC threads, but still need synchronization to ensure the elements need to be computed are in the local node. According to the pipelining idea which is to overlap the execution of multiple DSC threads by staggering their starting times. The result of this pipelining is depicted in Fig. 3.20. Each row of matrix A is assigned to a different computation thread. Injected into the PE pipeline in order, these threads follow each other in the network to compute the corresponding C entries.

Sometimes the dependency among different computations allows different DSC threads to enter the pipeline from different PEs. In these situations, we can phase shift the DSC threads to achieve full parallelism, We apply our Phase-shifting Transformation to achieve a full DPC, as depicted in Fig. 3.21. This is possible because each row of A, though needed on all three PEs, can start its computation from any PE.

### 3.4.7 Generating threads for Matrix Multiplication in second dimension

Same as in one dimension, in two dimension, we apply our Pipelining and Phase-shifting in both dimensions, as depicted in Fig. 3.22 and Fig. 3.23. Basically, a pair of A and B entries can move on along their pipelines respectively as soon as they finish computing and contributing the corresponding C entry. A producer BCarrier needs to make sure that the B entry produced by its predecessor in the pipeline is consumed before it puts the B entry

it carries in place. This is the reason for a second event EC(., .).

Figure 3.20: Pipelining in one dimensions

Figure 3.21: Phase shifting in one dimension

Figure 3.22: Pipelining in both dimensions

Figure 3.23: Phase shifting in both dimensions

#### 3.4.8 Generating the Code

Generating the code requires inserting code so that the multiple threads synchronize with each other.

#### 3.4.9 Generating the Code: Example of ADI

For instance, loop4 is responsible for computing v[i][j]. It must wait until p[j][i] and q[j][i] are ready, which are computed by other threads. Synchronization code must be added to wait for data computed by other threads and to signal that data is ready to be accessed. The basic principle is to insert signal/wait primitives at each end of a solid edge and add code to transfer data for any edge that carries data (edges with non-zero weight.) Fig. 3.24 shows the portion of the DPC code that represents the transformed Loop 4. Builder.msgr injects a spawner. loop4\_spawner.msgr creates the multiple threads for loop4 (Loop4\_sweeper) and injects them at the node where the computing starts for loop 4. Fig. 3.25 shows the portion of the DPC code that represents the transformed Loop 8.

Each of these threads processes a column of tiles. It executes as a doubly indexed loop (lines 9-10), where the outer loop runs through all iterations of the main loop in the original sequential program and the inner loop runs through all the tiles in the column. For each tile, it hops to the pivot node (line 11) synchronizes with other threads (line 12), computes the tile (line 13-17), and synchronizes with other threads (lines 18-21). Since each hop is carrying data, we do not explicitly show load and unload data in this pseudo code.

In this example, no data transmission code is needed for solid edges because their weights are all zero. This is true in most cases because any two tiles that access the same data will, due to the pivot-computes principle, be assigned to the same node.

```

(1) Builder.msgr(ITERATIONS)

(2)

inject(Loop4_spawner,ITERATIONS);

(3) loop4_spawner.msgr

(4) for (J = 0; J < num_blks_J J++) {

(5)

hop(comp_loc[0,J]);

(6)

inject(Loop4_sweeper, J);

(7) }

(8) Loop4_sweeper(J):

(9)for(iter=0; iter< ITERATIONS;iter--){</pre>

(10) for (I=(num_blk_I-1);I>=0;I--){

(11)

hop(comp_loc[I,J]);

if(I==(num_blk_I-1))

(12)

wait(E(iter,loop4,J,I,p/q)) ;

for(j=j_start(I,J); j<=j_end(I,J); j++){</pre>

(13)

(14)

for(i=i_end(I,J); i>=i_start(I,J);i--){

(15)

v[i][j]= F3(p[j][i],v[i+1][j],q[j][i];

}

(16)

}

(17)

(18)

if(I==0)signal(E(iter,loop6,I,J,v) ;

(19)

if(I!=(n_num_blks_I-1) && I!=0){

Push with Signal E(iter,I,J,v_plus);

(20)

(21)

Push with Signal E(iter,I,J,v_minus);}

(22)

}

(23) }

(24)}

```

Figure 3.24: DPC Code

```

loop8_sweeper.msgr

(1) for (J= n_num_blks_per_row-1; J >=0; J--) {

n_curr_node = n_node_map[I,J];

(2)

(3)

if ( n_curr_node != myID )

(4)

hop(link=n_links[n_curr_node]);

(5)

if(J == n_num_blks_per_row-1){

(6)

wait_element(m_iter,loop8,I,n_num_blks_per_row-1,u);}

(7)

wait_element(m_iter,loop8,I,J,p/q);

(8)

loop8_sweep(I,J);

if(m_iter+1 <= ITERATIONS){</pre>

(9)

(10)

set_element(m_iter+1,loop2,I,J,u);

(11)

set_space(m_iter+1,loop2,I,J,p/q);

if(n_reverse_fetch_minus[I,J]!=-1){

(12)

(13)

inject(PUSH_U_MINUS,m_iter+1,I,J);

(14)

}

if(n_reverse_fetch_plus[I,J]!=-1){

(15)

inject(PUSH_U_PLUS,m_iter+1,I,J);

(16)

}

(17)

}

(18)

(19)

```

## 3.4.10 Generating the Code: Example of Matrix Multiplication in one dimension

Pseudocode for pipelined DSC matrix multiplication is listed in Fig. 3.26. The matrix A is initially put on the PE with HnodeID = 0, and the columns of matrices B and C are distributed such that B(., j) and C(., j) are on the PE with HnodeID = j.

Pseudocode for Phase-shifting in one dimension is listed in Fig. 3.27. Rows of matrix A are carried by the corresponding agent variables mA. In this implementation, matrix A is initially distributed such that A(i, .) is on the PE with HnodeID = i, and the columns of matrices B and C are distributed such that B(., j) and C(., j) are on the PE with HnodeID = j.

```

(1) hop(node(0))

(2) do i=0,N-1

(3)

inject(RowCarrier(i))

(4) end do

(1) RowCarrier(int mi)

(2) mA(*) = A(mi,*)

(3) do mj=0,N-1

(4)

hop(node(mj))

(5)

t = 0.0

(6)

do k=0,N-1

t += mA(k) * B(k)

(7)

(8)

end do

(9)

C(mi) = t

(10) end do

(11) end

```

Figure 3.26: Pseudocode for pipelined DSC

```

(1) do mi=0,N-1

(2)

hop(node(mi))

(3)

inject(RowCarrier(mi))

(4) end do

(1) RowCarrier(int mi)

(2) mA(*) = A(*)

(3) do mj=0,N-1

(4)

hop(node((N-1-mi+mj)%N))

(5)

t = 0.0

(6)

do k=0,N-1

(7)

t += mA(k) * B(k)

(8)

end do

(9)

C(mi) = t

(10) end do

(11) end

```

Figure 3.27: Pseudocode for DPC in one dimension

# 3.4.11 Generating the Code: Example of Matrix Multiplication in second dimension

Pseudocode for DSC with pipelining in both dimensions is listed in Fig. 3.28. The entries of matrices A and B are carried in their corresponding agent variables mA and mB, respectively. The matrices are initially distributed, as shown in Fig. 3.28, such that  $A(N \cdot 1 \cdot 1, .)$  and B(., 1) are on node $(N \cdot 1 \cdot 1, .)$ , and C(i, j) (initialized to 0) is on node(i, j). An event EC(i, j) is signaled on node(i, j) for all values of i, j initially.

```

(1) do ml=0,N-1

(2)

hop(node(N-1-ml,ml))

inject(spawner(ml))

(3)

(4) end do

(1) spawner(int ml)

(2)

do mk=0,N-1

(3)

inject(ACarrier(N-1-ml,mk))

(4)

inject(BCarrier(mk,ml))

(5)

end do

(6) end

(1) ACarrier(int mi, int mk)

(2)

mA=A(mk)

do mj=0,N-1

(3)

(4)

hop(node(mi,(N-1-mi+mj)%N))

(5)

waitEvent(EP(mi,(N-1-mi+mj)%N))

C += mA * B

(6)

(7)

signalEvent(EC(mi,(N-1-mi+mj)%N))

(8)

end do

(9) end

(1) BCarrier(int mk, int mj)

(2)

mB=B(mk)

(3)

do mi=0,N-1

(4)

hop(node((N-1-mj+mi)%N,mj))

waitEvent(EC((N-1-mj+mi)%N,mj))

(5)

(6)

B = mB

signalEvent(EP((N-1-mj+mi)%N,mj))

(7)

(8)

end do

(9) end

```

Figure 3.28: Pseudocode for pipelining in second dimensions.

Pseudocode for DPC in both dimensions is listed in Fig. 3.29. The entries of matrices A