## SINGLE-CHIP REDUCED-WIRE ACTIVE CATHETER SYSTEM WITH PROGRAMMABLE TRANSMIT BEAMFORMING AND RECEIVE TIME-DIVISION MULTIPLEXING FOR INTRACARDIAC ECHOCARDIOGRAPHY

A Dissertation Presented to The Academic Faculty

by

Gwangrok Jung

In Partial Fulfillment of the Requirements for the Degree Doctor of Philosophy in the School of Electrical and Computer Engineering

> Georgia Institute of Technology December 2019

## **COPYRIGHT © 2019 BY GWANGROK JUNG**

## SINGLE-CHIP REDUCED-WIRE ACTIVE CATHETER SYSTEM WITH PROGRAMMABLE TRANSMIT BEAMFORMING AND RECEIVE TIME-DIVISION MULTIPLEXING FOR INTRACARDIAC ECHOCARDIOGRAPHY

Approved by:

Dr. F. Levent Degertekin School of Electrical and Computer Engineering *Georgia Institute of Technology*

Dr. Stanislav Emelianov School of Electrical and Computer Engineering *Georgia Institute of Technology*

Dr. Omer Inan School of Electrical and Computer Engineering *Georgia Institute of Technology*  Dr. Farrokh Ayazi School of Electrical and Computer Engineering *Georgia Institute of Technology*

Dr. Coskun Tekes Department of Computer Engineering *Kennesaw State University*

Date Approved: August, 15, 2019

#### ACKNOWLEDGEMENTS

I would like to express my gratitude to my advisor, Dr. F. Levent Degertekin for sincere support of scholastic guidance. During 5 years of PhD research, I was able to seek for creative and logical solutions since his door opened always and he was willing to discuss. It is pleasant and precious memory.

I would like thank Dr. Coskun Tekes for his invaluable time and help. He was always with me during acoustic measurements, supporting and teaching me with deep knowledge. I am grateful to Dr. Stanislav Emelianov, Dr. Farrokh Ayazi, and Dr. Omer Inan for their time and advice in reviewing my PhD dissertation and serving as committee members.

My research work is a system level combination of multiple projects, requiring various background and knowledge. I am thankful to Dr. Maysam Ghovanloo for his guidance and support, and previous GT-bionics members. I would like to acknowledge the support during my PhD from Muhammad, Thomas, Ahmad, Evren, Amir, Sush, and Yusuf.

I am grateful to my family, my mother, father and Gwangha. I could not finish my PhD without their help. They support me every time even they are not with me.

Last, but the most important, I would like to express my sincere gratitude to my dear wife Unji. She sacrifices and supports me with her love. I feel myself lucky for having her in my life. This work would not be finished without her support.

## TABLE OF CONTENTS

| ACKNOWLEDGEMENTS                                                            |     |

|-----------------------------------------------------------------------------|-----|

| LIST OF FIGURES                                                             | vii |

| SUMMARY                                                                     | xii |

| CHAPTER 1. INTRODUCTION                                                     | 1   |

| 1.1 Medical Ultrasound Imaging for ICE                                      | 1   |

| 1.2 Basic Principles of Ultrasound Imaging                                  | 4   |

| 1.3 Receiver Array Cable Reduction Technique                                | 9   |

| 1.3.1 µ-Beamformer                                                          | 9   |

| 1.3.2 Integrated ADCs                                                       | 9   |

| 1.3.3 PWM and FDM                                                           | 10  |

| 1.3.4 TDM                                                                   | 10  |

| 1.4 Transmitter Array Cable Reduction                                       | 11  |

| 1.5 Transmitter Technique for Increasing the Acoustic Pressure              | 12  |

| CHAPTER 2. Supply- Doubled Pulser Design FOR CMUTS                          | 15  |

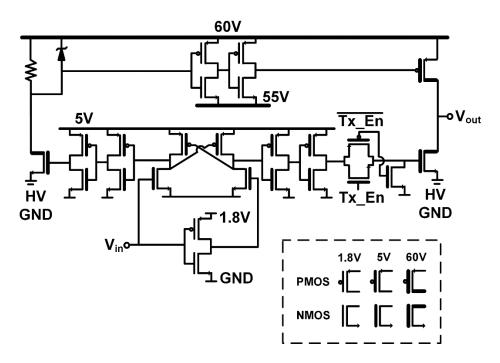

| 2.1 Three Level Supply-Doubled Pulser                                       | 15  |

| 2.2 Two Level Supply-Doubled Pulser                                         | 26  |

| 2.3 Supply-Inverted Pulser                                                  | 36  |

| CHAPTER 3. Single-chip reduced wire catheter system                         | 58  |

| 3.1 System Architecture                                                     | 58  |

| 3.4.1 Electrical Characterization for Tx Circuitry                          | 72  |

| 3.4.2 Electrical Characterization for Rx TDM                                | 73  |

| 3.4.3 Acoustic Measurement with Full System                                 | 77  |

| CHAPTER 4. Single-chip reduced wire CMUT-on-CMOS ICE system                 | 82  |

| 4.1 System Architecture                                                     | 84  |

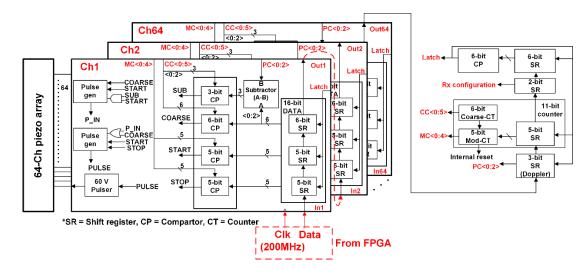

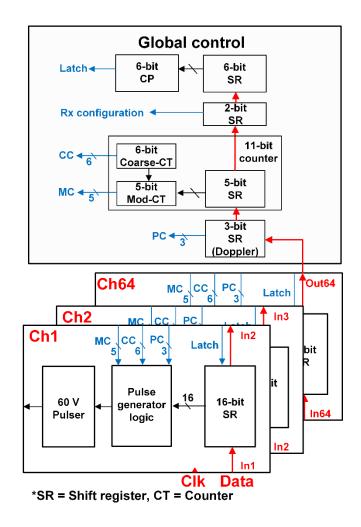

| 4.1.1 Tx Beamformer Operation                                               | 86  |

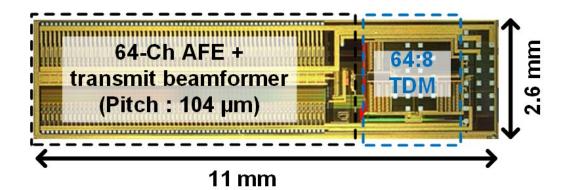

| 4.1.2 Rx Circuitry                                                          | 87  |

| 4.2 CMUT Design and Fabrication                                             | 90  |

| 4.3 Experimental Results                                                    | 93  |

| CHAPTER 5. <i>µ</i> -beamformer with TDM system for massive cable reduction | 96  |

| 5.1 $\mu$ -Beamformer Design                                                | 98  |

| 5.2 System Architecture                                                     | 100 |

| 5.3 Circuit Implementation                                                  | 103 |

| CHAPTER 6. Conclusion and future work                                       | 108 |

| 6.1 Conclusion of Supply-Doubled/Inverted Pulser Design                     | 108 |

| 6.2 Future Work of Supply-Doubled/Inverted Pulser Design                    | 109 |

| 6.3 Conclusion of Single-Chip Reduced Wire Catheter System                  | 110 |

| 6.4 Conclusion of Single-Chip Reduced Wire CMUT-on-CMOS ICE System          | 110 |

- 6.5 Future Work of Single-Chip Reduced Wire CMUT-on-CMOS ICE System 111

- Conclusion of  $\mu$ -beamformer with TDM system for massive cable reduction 111 Future Work of  $\mu$ -beamformer with TDM system for massive cable reduction 112 6.6

- 6.7

### REFERENCES

113

## LIST OF TABLES

| Table 1 | Benchmarking of the proposed pulser performance.               | 25 |

|---------|----------------------------------------------------------------|----|

| Table 2 | Benchmarking of the proposed two level pulser performance.     | 35 |

| Table 3 | Benchmarking of the proposed Tx/Rx switch performance.         | 51 |

| Table 4 | Benchmarking of the proposed pulser performance.               | 55 |

| Table 5 | Benchmarking table of state-of-the-art ultrasound array ASICs. | 80 |

## LIST OF FIGURES

| Figure 1  | ICE probe insertion diagram                                                                                                                                                                                                         | 2  |

|-----------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

| Figure 2  | Illustration of pulse-echo operation for A-scan.                                                                                                                                                                                    | 4  |

| Figure 3  | (a) Block diagram of standard Time-division multiplexing scheme and (b) reduced number of ADC scheme.                                                                                                                               | 11 |

| Figure 4  | (a) A simplified schematic diagram of the supply-doubled (inverted) high voltage pulser, and (b) the operation of voltage doubling stage.                                                                                           | 16 |

| Figure 5  | (a) Schematic of the proposed voltage doubled pulser. (b) Schematic of the input driving buffers and level shifters for high voltage PMOS input signals.                                                                            | 17 |

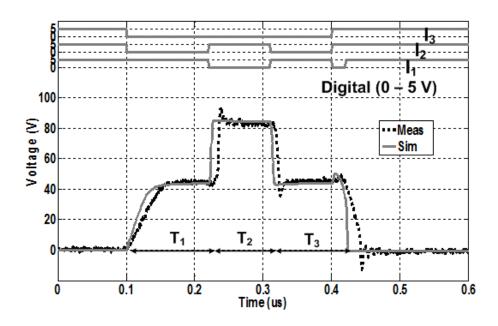

| Figure 7  | Simulated and measured three-level output pulse along with three input control signals. $C = 100 \text{ pF}$ , $CCMUT = 8 \text{ pF}$ .                                                                                             | 21 |

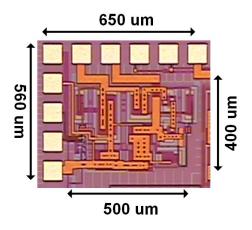

| Figure 8  | Microphotograph of the proposed pulser chip.                                                                                                                                                                                        | 22 |

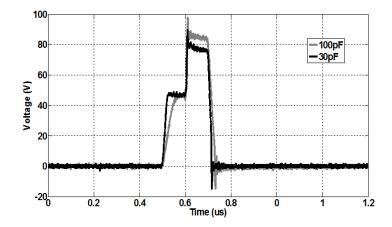

| Figure 9  | Measured output pulse with $C = 30$ pF and 100 pF when CMUT loading is 8 pF.                                                                                                                                                        | 22 |

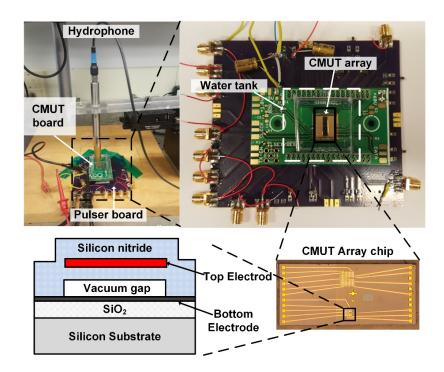

| Figure 10 | Acoustic pressure experimental setup with CMUT array board and pulser board.                                                                                                                                                        | 23 |

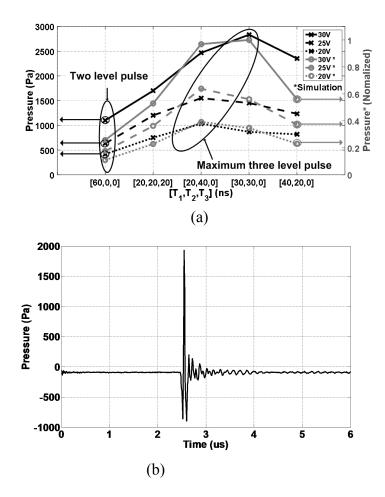

| Figure 11 | (a) Transmitted peak-to-peak acoustic pressure measurement<br>and simulation with different pulse shapes and supply voltages.<br>(b) Measured transmitted pressure with $TI = 30$ ns, $T2 = 30$ ns,<br>T3 = 0 ns, and $VDD = 30$ V. | 24 |

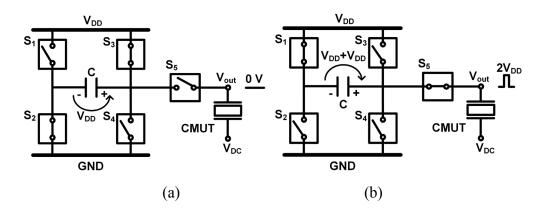

| Figure 12 | Simplified schematic diagram of the proposed pulser during (a) charging and (b) voltage doubling phases.                                                                                                                            | 26 |

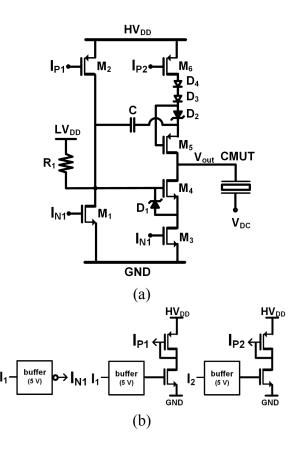

| Figure 13 | Schematic diagram of (a) the proposed pulser and (b) input driving buffers and level shifters.                                                                                                                                      | 28 |

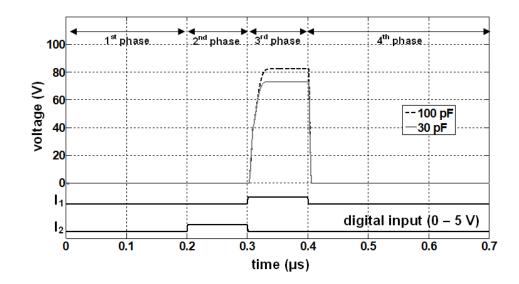

| Figure 14 | Simulation of the control inputs and output pulse with different $C$ values, when CMUT loading is considered 8 pF, and $HVDD = 45$ V.                                                                                               | 29 |

| Figure 15 | Microphotograph of the proposed pulser.                                                                                                                                                                                             | 32 |

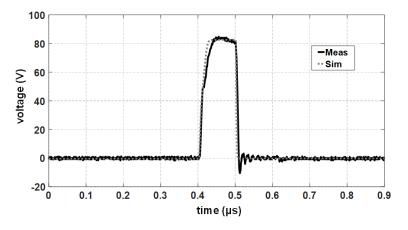

| Figure 16 | Measured and simulated supply-doubled pulse, when C and CMUT loading are considered 100 pF and 8 pF ( $HVDD = 45$ V).                                                                                           | 32 |

|-----------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

| Figure 17 | Layout of the CMUT array, and cross-section view of CMUT layers.                                                                                                                                                | 33 |

| Figure 18 | Acoustic measurement setup for testing the proposed pulser with a CMUT array.                                                                                                                                   | 33 |

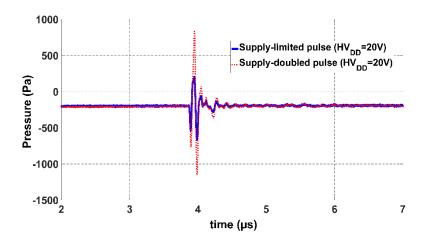

| Figure 19 | Measured transmitted pressure with CMUT. Blue line shows the pressure of conventional supply-limited pulser, red dot-line shows the pressure of supply-doubled proposed pulser.                                 | 34 |

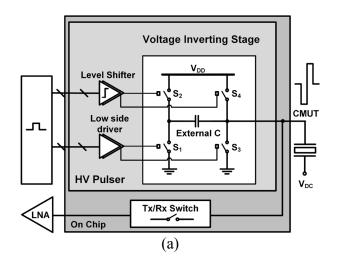

| Figure 20 | (a) Simplified schematic diagram of the proposed pulser and high voltage Tx/Rx switch, (b) the operation of voltage inverting stage.                                                                            | 38 |

| Figure 21 | Schematic diagrams of (a) proposed supply-inverted pulser, (b) level shifters for high voltage NMOS/PMOS input signals of supply-inverted pulser                                                                | 39 |

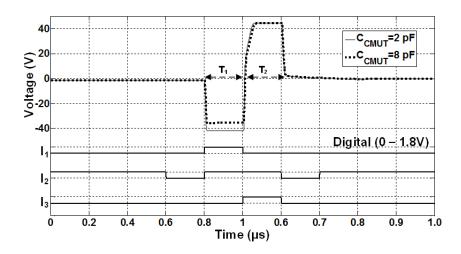

| Figure 22 | Simulation of the output pulse with different <i>CCMUT</i> values with 30 pF of $C$ .                                                                                                                           | 42 |

| Figure 23 | Schematics of proposed protection Tx/Rx switch for voltage-inverted pulser.                                                                                                                                     | 45 |

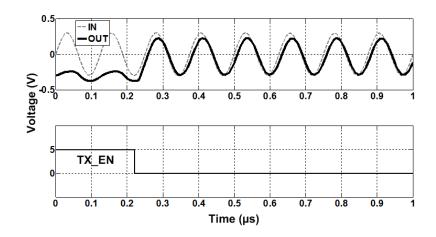

| Figure 24 | Simulation result of the Tx/Rx switch, IN is connected to the output of supply-inverted pulser during Tx period.                                                                                                | 45 |

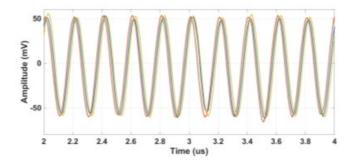

| Figure 25 | Simulation results of the Tx/Rx switch with 8 MHz of sinusoidal input. The load condition of the output node is 5 pF.                                                                                           | 47 |

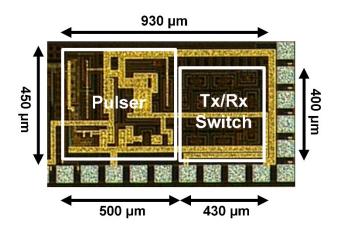

| Figure 26 | Microphotograph of the proposed supply-inverted pulser and $Tx/Rx$ switch.                                                                                                                                      | 47 |

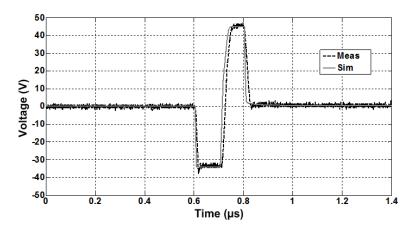

| Figure 27 | Measured and simulated supply-inverted output pulse along with three input control signals. $C = 30$ pF, equivalent $CCMUT = 8$ pF.                                                                             | 48 |

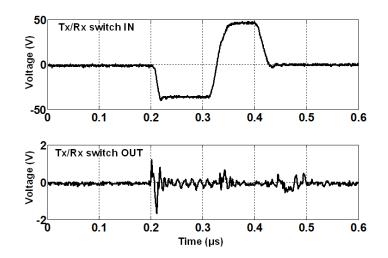

| Figure 28 | Measured Tx/Rx switch input and output during supply-inverted pulse firing period. $C = 30$ pF and equivalent $CCMUT = 8$ pF.                                                                                   | 49 |

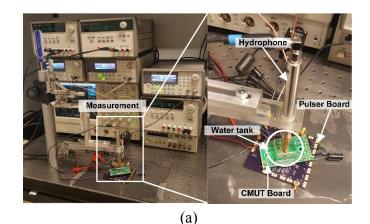

| Figure 29 | (a) Experimental setup with CMUT array board and pulser board<br>for acoustic measurements. (b) Cross section view of CMUT<br>layers and layout of the CMUT array which one element consists<br>of 4 membranes. | 50 |

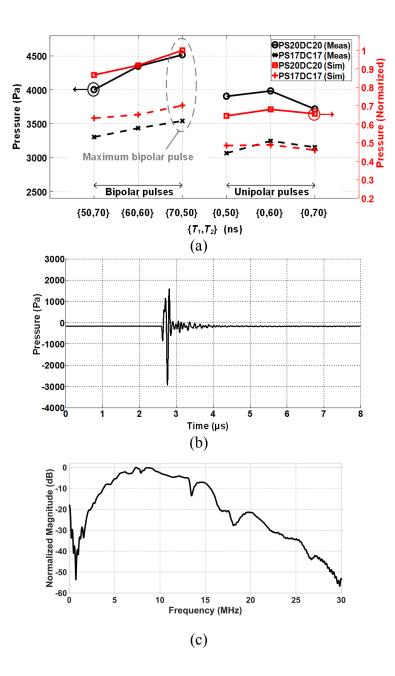

| Figure 30 | (a) Transmitted peak-to-peak acoustic pressure measurement<br>and simulation with different CMUT bias, pulse shape and<br>supply voltages. (b) Measured transmitted pressure with $T1 = 70$<br>ns, $T2 = 50$ ns, $HVDD = 20$ V, and CMUT bias = 20 V. (c)<br>Frequency spectrum of the transmitted pressure signal shown in<br>(b).   | 53 |

|-----------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

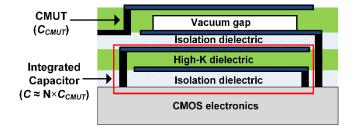

| Figure 31 | Schematic cross section view of a CMUT-on-CMOS device with integrated co-microfabricated capacitance, C. Lower relative permittivity dielectric layers (SiNi, SiO2) are used for isolation, and the high K-dielectric has a relative permittivity of $\varepsilon r = N$ . Black lines are metal connections to the CMOS electronics. | 56 |

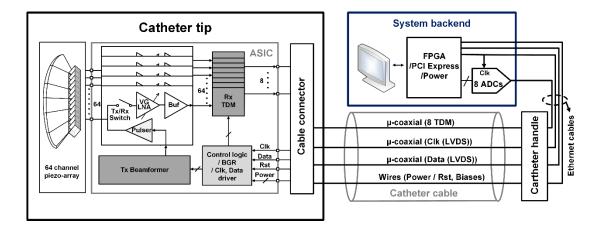

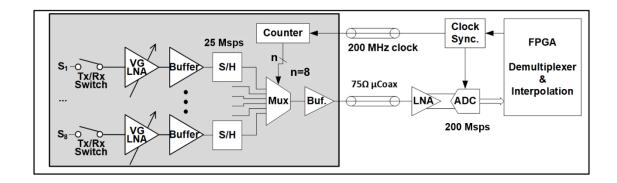

| Figure 32 | Simplified block diagram of the proposed ICE catheter system which includes backend system.                                                                                                                                                                                                                                           | 59 |

| Figure 33 | Detailed block diagram of the Tx-beamformer.                                                                                                                                                                                                                                                                                          | 61 |

| Figure 34 | Schematics of proposed 60 V pulser.                                                                                                                                                                                                                                                                                                   | 62 |

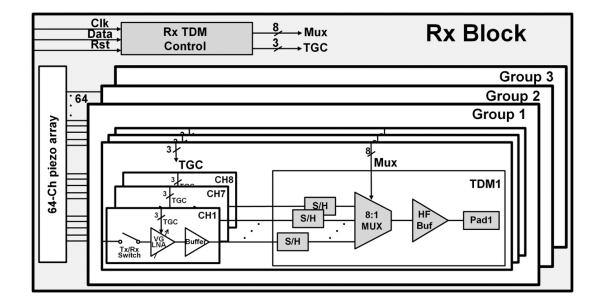

| Figure 35 | Simplified receiver TDM circuitry.                                                                                                                                                                                                                                                                                                    | 63 |

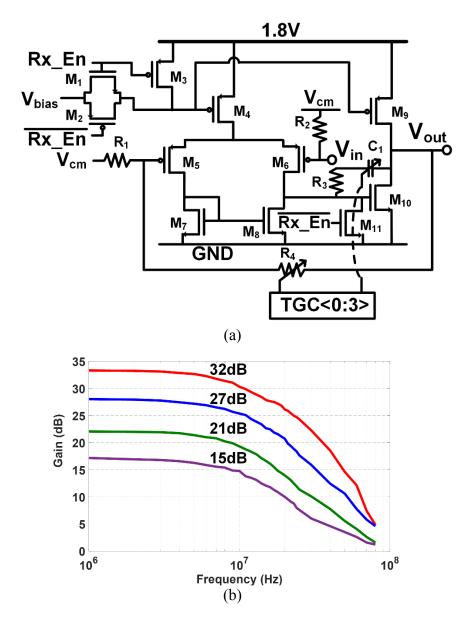

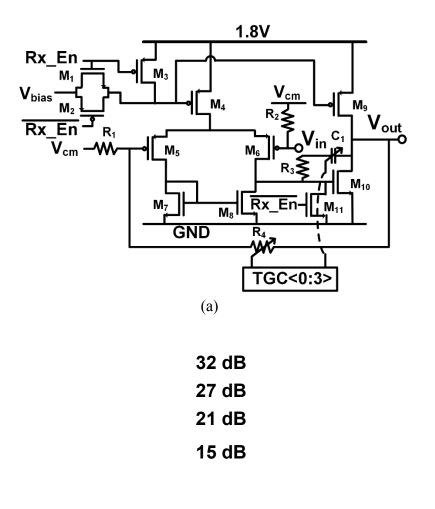

| Figure 36 | (a) Schematics of variable gain LNA, and (b) measured frequency response of variable gain LNA with different 4 gains.                                                                                                                                                                                                                 | 65 |

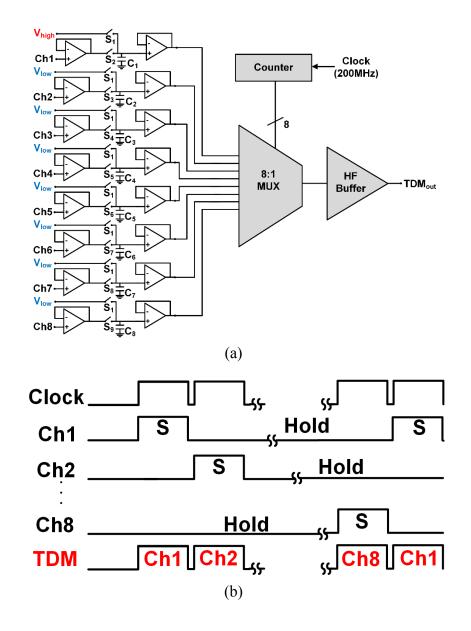

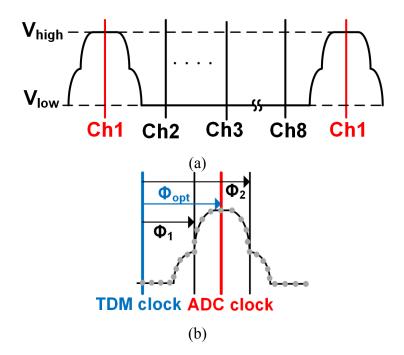

| Figure 37 | <ul><li>(a) Simplified block diagram of TDM block for 8 channels, and</li><li>(b) TDM sampling clock diagram.</li></ul>                                                                                                                                                                                                               | 67 |

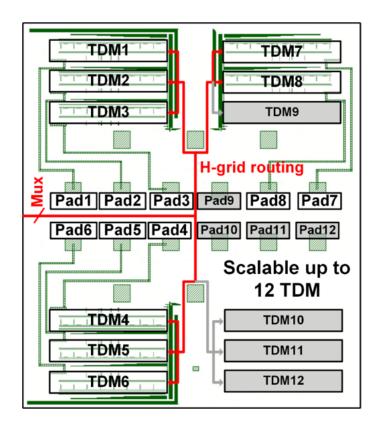

| Figure 38 | The symmetrical layout of the TDM block.                                                                                                                                                                                                                                                                                              | 68 |

| Figure 39 | (a) Link training waveform of channel number synchronization, and (b) phase synchronization.                                                                                                                                                                                                                                          | 68 |

| Figure 40 | Simplified block diagram of TDM with DDD system.                                                                                                                                                                                                                                                                                      | 70 |

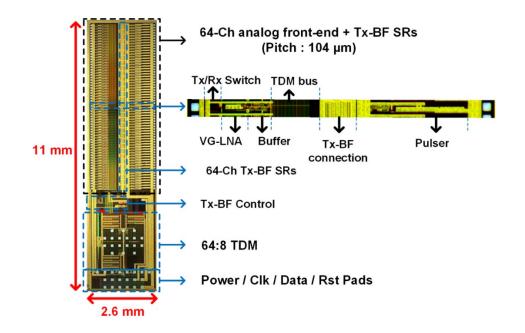

| Figure 41 | Microphotograph of 64 channel ICE ASIC.                                                                                                                                                                                                                                                                                               | 71 |

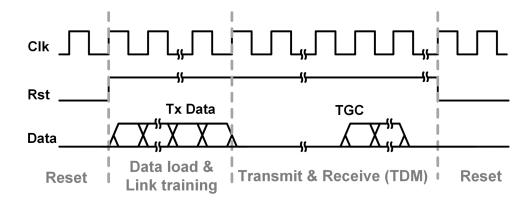

| Figure 42 | Timing diagram of the proposed system.                                                                                                                                                                                                                                                                                                | 71 |

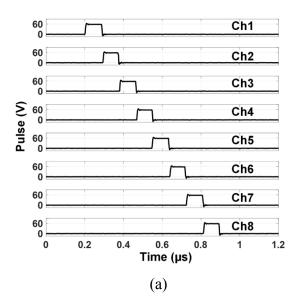

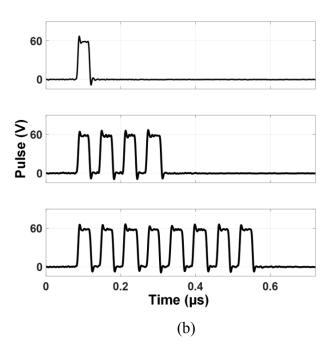

| Figure 43 | (a) Measured pulser output from adjacent 8 channels, and (b) multiple consecutive pulse generation for Doppler imaging.                                                                                                                                                                                                               | 73 |

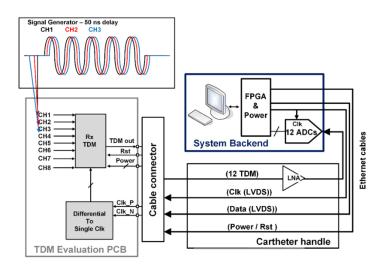

| Figure 44 | Simplified block diagram for testing TDM block with back-end system.                                                                                                                                                                                                                                                                  | 73 |

| Figure 45 | Simplified block diagram for testing TDM block with back-end system.                                                                                                                                                                                                                                                                  | 74 |

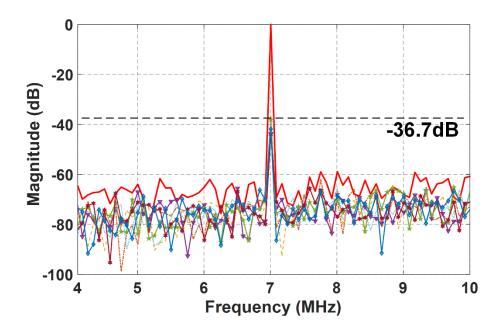

| Figure 46 | Crosstalk measurement of 8 channels of TDM circuitry.                                                                                                      | 75  |

|-----------|------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|

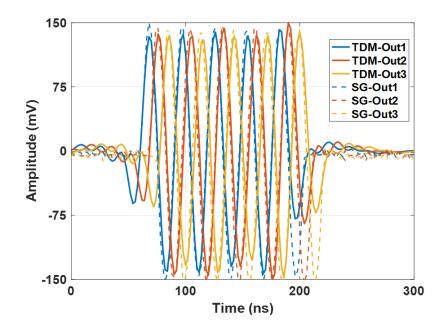

| Figure 47 | The measurement of three ideal Gaussian pulses from signal generator.                                                                                      | 76  |

| Figure 48 | Ultrasound imaging measurement setup with piezo-array immersed in the water facing standard phantom.                                                       | 76  |

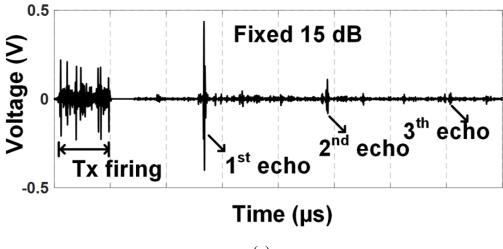

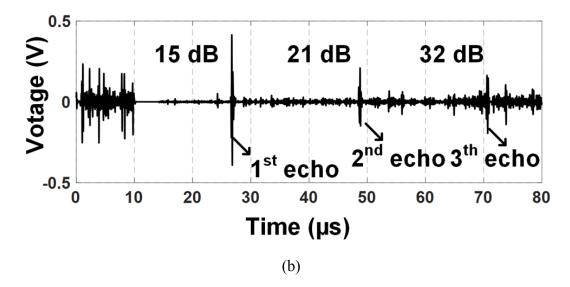

| Figure 49 | (a) Measured echoes reflected from a metal reflector at 1.6cm without TGC after TDM and DDD, and (b) with TGC control.                                     | 78  |

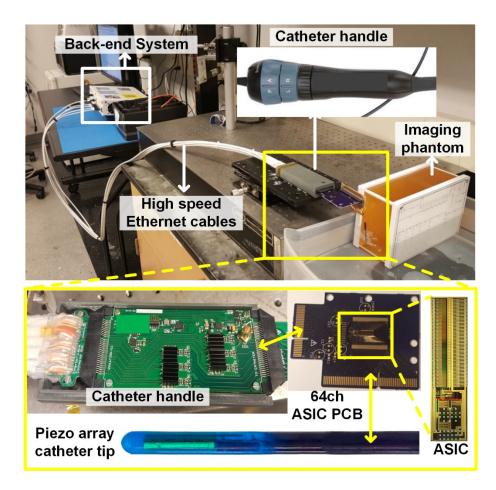

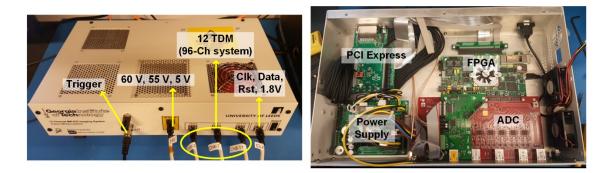

| Figure 50 | ICE System back-end setup.                                                                                                                                 | 78  |

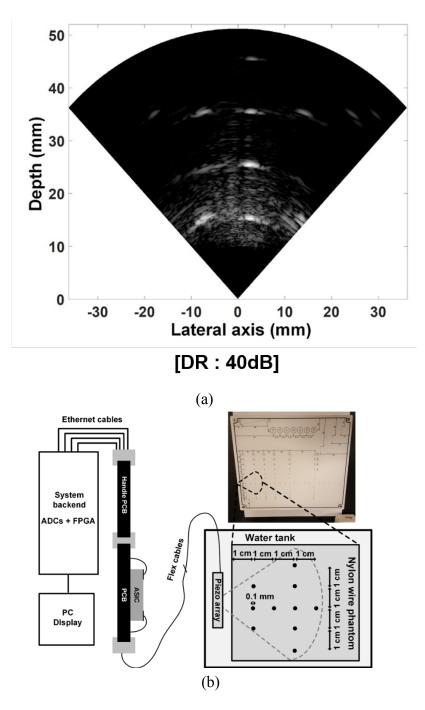

| Figure 51 | (a) Measured B-mode image of 10 nylon wires in a standard phantom and (b) imaging setup diagram with phatom.                                               | 79  |

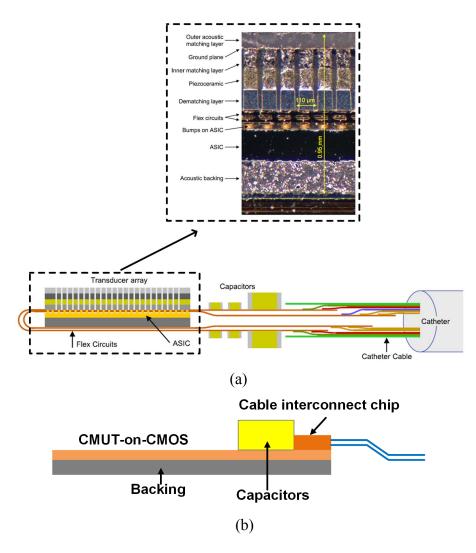

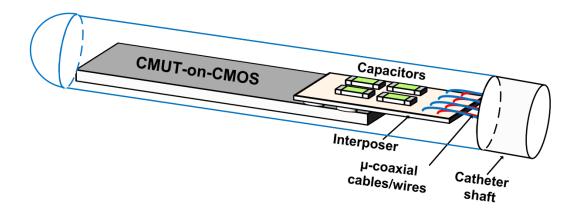

| Figure 53 | Schematic drawing of the ICE catheter tip using a single chip CMUT-on-CMOS system. The chip would be connected to the catheter cables using an interposer. | 84  |

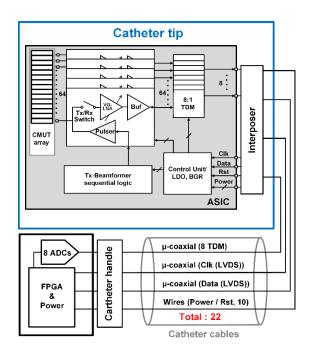

| Figure 54 | Simplified block diagram of the proposed CMUT-on-CMOS system.                                                                                              | 85  |

| Figure 55 | Simplified block diagram of the Tx beamformer with Pulser.                                                                                                 | 86  |

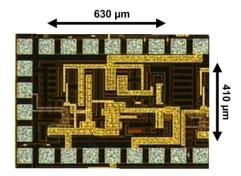

| Figure 56 | Microphotograph of the ASIC.                                                                                                                               | 89  |

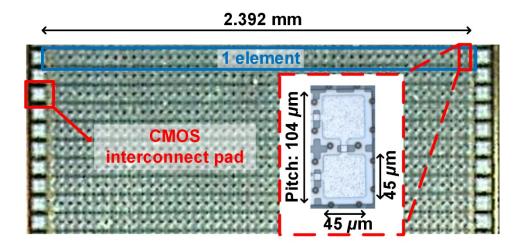

| Figure 57 | Microphotograph of the membranes of 1D CMUT-on CMOS element.                                                                                               | 92  |

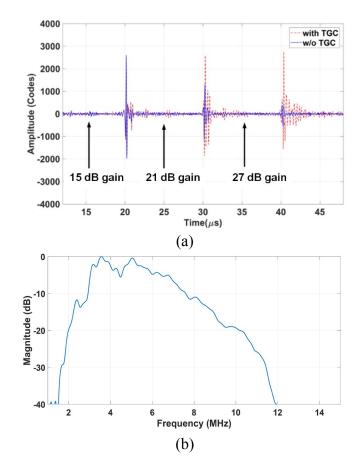

| Figure 58 | (a) Received pulse-echo signals with or without TGC, and (b) frequency spectrum of the echo signals from plain reflector.                                  | 92  |

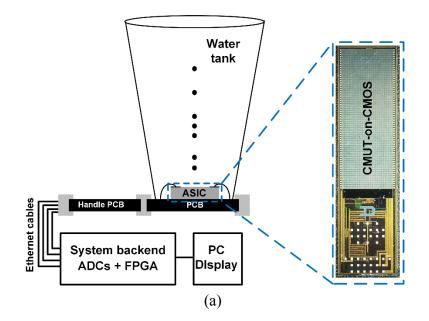

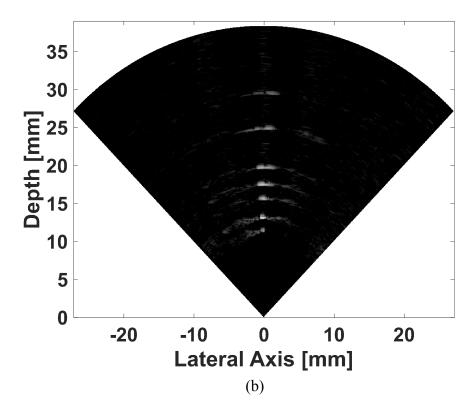

| Figure 59 | (a) Imaging experiment setup diagram with micrograph of CMUT-on-CMOS, and (b) B-mode image of 7 metal wires in the water.                                  | 94  |

| Figure 60 | $\mu$ -beamformer architecture for ICE application.                                                                                                        | 96  |

| Figure 61 | Analog delay circuit implementation using switched capacitor.                                                                                              | 97  |

| Figure 62 | Simplified block diagram of proposed $\mu$ -beamformer with TDM system.                                                                                    | 98  |

| Figure 63 | Proof-of-concept of $\mu$ -beamformer with TDM system.                                                                                                     | 100 |

| Figure 64 | Circuit implementation of AFE, $\mu$ -beamformer with TDM system.                                                                                          | 101 |

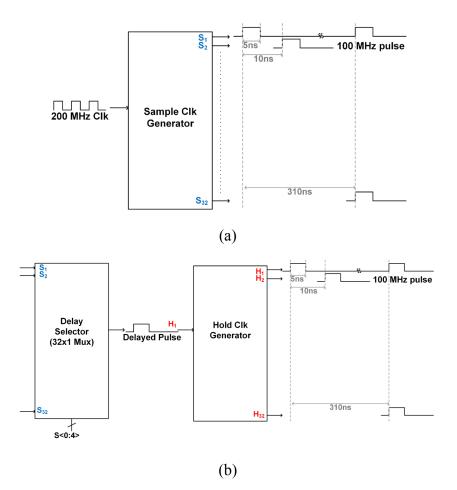

| Figure 65 | (a) Simplified block diagram of global sample clock generation,<br>and (b) local hold clock generation for switched capacitor delay<br>cell. | 101 |

|-----------|----------------------------------------------------------------------------------------------------------------------------------------------|-----|

| Figure 66 | (a) Schematics of variable gain LNA, and (b) measured frequency response of variable gain LNA with different 4 gains.                        | 104 |

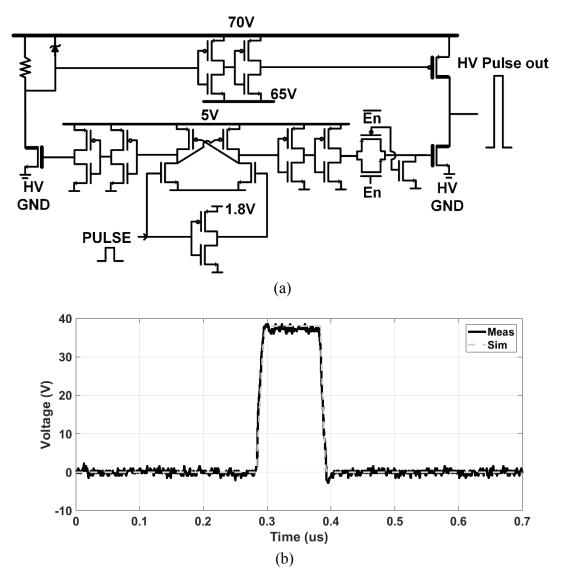

| Figure 67 | (a) Schematics of proposed 70 V pulser, and (b) the simulated and measured result of pulser with 38 V supply.                                | 105 |

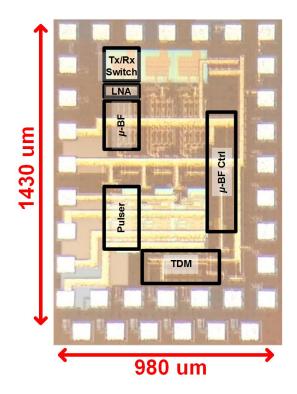

| Figure 68 | Micrograph of $\mu$ -beamformer combined with TDM system.                                                                                    | 106 |

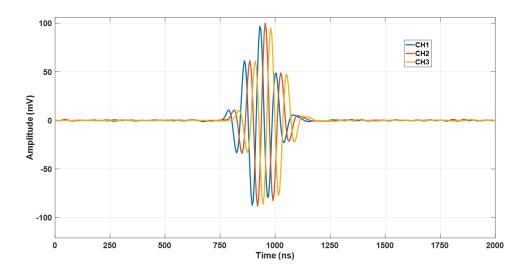

| Figure 69 | Measurement results of delayed 3 received signals with step size of 10 ns.                                                                   | 107 |

#### SUMMARY

The main objective of proposed thesis research is to develop a single chip reducedwire active catheter system, which adopts programmable transmit beamforming and receive time-division multiplexing (TDM). The proposed front-end application-specific integrated circuit (ASIC) is designed for driving a 64-channel 1-D piezo-transducer array or capacitive micromachined ultrasound transducer (CMUT) array in intracardiac echocardiography (ICE) catheters.

ICE has become more important clinical modality in interventional ultrasound imaging. It requires a minimal invasive procedure during which a small catheter is placed into a femoral vein to image the heart anatomy from inside. It provides real-time ultrasound imaging, guiding interventions like valve repair, placement of stents, closure of atrial septal defects (ASD) and catheter-based ablation to treat atrial fibrillation. ICE needs local anesthesia and the sedation and it is becoming the preferred imaging tool with better image quality over transesophageal echography (TEE) which requires general anesthesia delivered by an anesthesiologist.

Current ICE catheters offer a limited 2-D or 3-D field of view in spite of large number electrical interconnections to the main imaging system, which are mainly determined by the number of array elements and ground connections. Each element in the ICE array is connected to corresponding analog-front-end (AFE) system with a separate long wire, which is a significant limitation for improving image quality and increasing the number of elements. Also, in order to use ICE catheters under MRI instead of the ionizing X-ray radiation-based angiography, the number of interconnect wires in the catheter should be minimized to reduce RF-induced heating from metal connection. Furthermore, reducing the number of wires would improve the flexibility, reach, and even lower the cost of the single-use ICE catheters. Therefore, an interconnection reduction method which integrates electronics in the catheter tip would have a significant impact in the catheter-based ultrasound imaging applications.

#### CHAPTER 1. INTRODUCTION

#### **1.1 Medical Ultrasound Imaging for ICE**

Medical ultrasound imaging has had a significant impact on clinical practice by providing real time images of different organs with high spatiotemporal resolution noninvasively at low cost [1]. The discovery of piezoelectric effect by Pierre and Jacques Curie in 1880 [2], which enabled generation and perceiving of acoustic waves, was a critical moment in developing ultrasound technology. Furthermore, invention of the submarine detection by Paul Langevin during World War I ignited research on ultrasonics [3], [4]. In 1918, Langevin filed a patent [5] which led to the discovery of SONAR (Sound Navigation and Ranging) system to detect submarines. In 1940s, Neurologist Karl Dussik published theoretical analysis of how ultrasound can be used to image the human body [6]. He was the first to use ultrasound to diagnose a brain tumor. The first real time ultrasound Bscanner, named Vidoson, was developed by Siemens Medical Systems of Germany in 1965. In the last sixty years, medical ultrasound continued to grow and mature becoming one of the popular medical imaging modalities.

In a typical ultrasound imaging system, a one-dimensional (1-D) piezoelectric array probe is used. Piezoelectric materials are simply diced and bonded to a backing layer in the transducer probe. The system further consists of an interface, display, back-end and beamformer unit. Operator can provide instructions to the machine using the user interface. All the receiver electronics, including low noise amplifier (LNA), time gain compensation (TGC) circuits, analog to digital converters (ADCs), receiver beamformer, high voltage transmitter and transmit beamformers are placed in the beamformer unit. Electrical connection to the array is provided through long cables from the beamformer unit. Data from the scanner unit is processed by the back-end unit for display. Different ultrasound transducer probes are required to diagnose dedicated applications such as ob/gyn, abdomen, and cardiac.

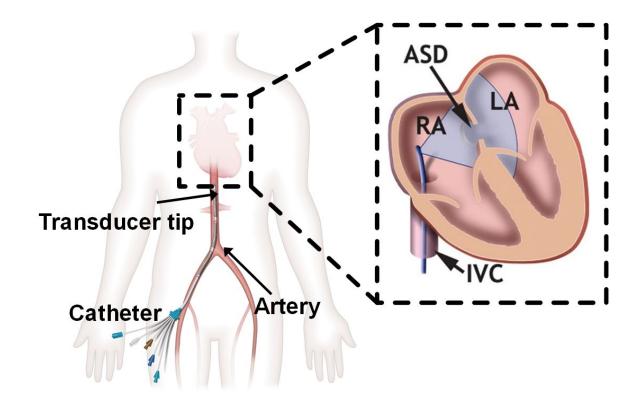

Figure 1. ICE probe insertion diagram

Heart disease is the leading cause of death in the World. About 610,000 people die of heart disease in the United States every year [7]. In addition to that, more than five million Americans are diagnosed with heart disease each year. Heart valve disease can occur in any single valve or a combination of the four valves, but diseases of the aortic and mitral valves are the most common. While up to 1.5 million people in the United States suffer from aortic stenosis, approximately 500,000 within this group of patients suffer from severe aortic stenosis. An estimated 250,000 patients with severe aortic stenosis are symptomatic [8]. So any advances in diagnosis and treatment for heart disease would have an impact. Two leading ultrasound techniques used in interventional cardiac imaging are Intracardiac echocardiography (ICE) [9], [10] and transesophageal echocardiography (TEE) [11]-[14]. These two modalities guide electrophysiology (EP) to treat arrhythmias and for structural heart procedures to treat defects in heart valves, closure of atrial septal defects (ASD) which the Centers for Disease Control and Prevention (CDC) estimated that 13 of every 10,000 babies born had an ASD [15], and catheter-based ablation which singleprocedure success rates for curing atrial fibrillation with radio frequency catheter ablation are as high as 80 % for atrial fibrillation [16]. The ICE catheter has a small ultrasound imaging probe at the tip [17]-[19]. To place the ICE catheter inside the human heart, physicians make a small incision near the upper part of the leg to insert the probe inside the femoral vein as shown in Figure 1. The catheter tip is then navigated through the femoral artery to the Inferior Vena Cava (IVC) and positioned into the right atrium of the heart. With its better image quality and ease of use, ICE is becoming the preferred imaging modality over TEE for structural heart interventions. The main advantages of ICE over TEE are it can be performed without the need of general anesthesia and procedure time can be shorter. ICE uses 8 F to 10 F (~ 3mm) catheters, the ultrasound transmitting frequency of the ICE is 5 MHz to 8 MHz, and has a penetration depth of 15 cm with lateral resolution of 1 to 2 mm, axial resolution of ~150 µm. The existing commercial ICE catheters, however, offer a limited 2- D or 3-D field of view despite utilizing large number of wires.

In these catheters, each element in the ICE array is connected to the backend data acquisition channel with a separate wire, which is a critical barrier for improving image quality and widening the field of view. In order to use ICE catheters under MRI instead of the ionizing X-ray radiation-based angiography, the number of interconnect wires in the catheter should be minimized to reduce RF-induced heating. Furthermore, reducing the number of wires improves the flexibility and lowers the cost of the single-use ICE catheters. This is the main motivation of this PhD thesis.

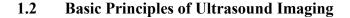

Figure 2. Illustration of pulse-echo operation for A-scan.

A typical ultrasound imaging system performs transmit and receive cycles for each of a single transducer element [20]. This combination of transmitting and receiving is referred as a pulse-echo operation. During the transmit mode, the transmitter circuitry excites the transducer with a high-amplitude and short-duration electrical pulse. The transducer converts the electrical pulses into acoustic pressure and generates ultrasound waves propagating at the speed of sound in the medium. After this transmit operation, the transducer element is switched to a receive mode and the receive cycle begins. The receive cycle shows the A (Amplitude)-scans generated by the transducer in response to the received echoes. The transmit/receive cycle is repeated until all the image lines are obtained to create the cross-sectional image as shown in Figure 2.

The medium consists of layers of materials with different acoustic impedances. The acoustic wave gets partially reflected back when it meets these layers with different acoustic impedances along the propagation path in the medium. The amount of the reflected acoustic wave is proportional to the difference of the acoustic impedances. In other words, if the difference in the acoustic impedances is large, most of the incident ultrasound wave gets reflected. Similarly, if the difference of the acoustic impedances is small, which typically is the case at boundaries of soft tissues, a small percentage of the acoustic wave gets reflected, and most of the acoustic power continues propagating in the medium. The reflected wave, which is referred as an echo, travels back towards the face of the transducer. When the echoes reach and hit to the transducer element, the transducer converts the received acoustic pressure into electrical signals. The distance of the reflector from the transducer can be found using the time difference between the initial transmitted

pulse and the received echo. Assuming a constant speed for the acoustic wave propagation in the medium, the distance from the transducer to the reflector is calculated by

$$\boldsymbol{D} = \frac{\boldsymbol{c} \times \boldsymbol{t}}{2} \tag{1}$$

Where D is the distance, t is the time of arrival, and c is the speed of sound in the particular medium (~1540 m/s for soft tissue [20]).

The process to create images from the received pulse-echo responses is as follows. First, envelope (amplitude) detection is done on the received echo signals. Each transmit pulse and its echoes form an amplitude mode (A-mode) scan line in the particular direction. After each transmit/receive cycle, the scan line is rotated either mechanically or electrically and the transmit/receive cycle is repeated to acquire a new image line. This process is repeated until the complete scan of the two-dimensional cross-sectional image area is completed one scan line at a time. Thus, each cross-sectional image may contain information of hundreds of separate A-scans. To generate the greyscale cross-sectional ICE images from the acquired A-scans, the amplitudes of the received signals in each scan line are mapped to a brightness level where higher amplitude echoes are mapped as brighter in the image. Hence, these generated images are called brightness-mode (B-mode) images.

The duration of each transmit/receive cycle depends on the desired imaging depth because the system needs to wait until the echoes from the deepest tissue come back. For instance, to construct an image with a depth of 15 cm, each receive period must be at least 200  $\mu$ s. The pulse-repetition frequency along with the total number of the required scan lines determines the image frame rate. This indicates a trade-off between the image frame

rate and the imaging depth. A volumetric imaging is another ultrasonic imaging mode. In 3D imaging, the received A-scans are rendered and presented on a volumetric image. Usually the same transducer is used both as a transmitter and a receiver. However, it is also possible to use separate transducers dedicated for receiving and transmitting operations. This enables independent optimization of the transducers for their respective operation mode and it also removes the need of switching circuitry between transmit and receive modes. On the other hand, the trade-off is that this also requires two transducers for each pulse-echo operation which requires more area.

The spatial resolution of an ultrasound system refers to the minimum separation between structures within the image that the ultrasound beam can distinguish. Spatial resolution is commonly categorized into axial resolution and lateral resolution. Axial resolution is the resolution in the direction along the axis parallel to the acoustic wave propagation, which is following

$$R_{AX} = \frac{N \times \lambda}{2} \tag{2}$$

where N is the number of cycles in the pulse and  $\lambda$  is the wavelength of the ultrasound signal corresponding to the frequency of the transmitted signal. Note that the transducer impulse response looks like a bandpass filter with a center frequency and a bandwidth. A higher bandwidth improves the axial resolution as it reduces the duration (N) of the transmitted ultrasound pulse and a higher bandwidth reduces the wavelength which also improves the axial resolution. It should be noted that the axial resolution does not depend on the distance from the transducer (unlike the lateral resolution) and is the same at any point in the scan line.

The lateral resolution is the resolution in a plane perpendicular to the direction of the ultrasound beam. The lateral resolution varies with the width (diameter) of the beam, and hence depends on the distance from the transducer. Along the beam axis there is an optimum point that is referred as the focal zone where the ultrasound beam has the smallest beam diameter providing the best lateral resolution. Away from the focal point (in the far field), ultrasound beams typically diverge which decrease the lateral resolution. Similarly, at locations very close to the array, the beam is not focused which also results in a decreased lateral resolution. The axial length over which the beam remains relatively focused is referred as the depth of field. A typical measure of the depth of field is the distance over which the lateral resolution stays within the 3 dB of the resolution at the focal point. The lateral resolution at the focal point is given with the below expression

$$R_{LA} = \frac{\lambda \times F}{D} \tag{3}$$

where F is the distance of the focal point from the transducer and D is the transducer diameter (aperture size). The ratio of the focal distance to the spatial dimension of the transducer is referred as the f-number. From (3), it becomes apparent that the lateral resolution at the focal point is directly proportional to the f-number and the wavelength. It should also be noted that the lateral resolution is generally few times poorer than the axial resolution.

#### 1.3 Receiver Array Cable Reduction Technique

#### 1.3.1 μ-Beamformer

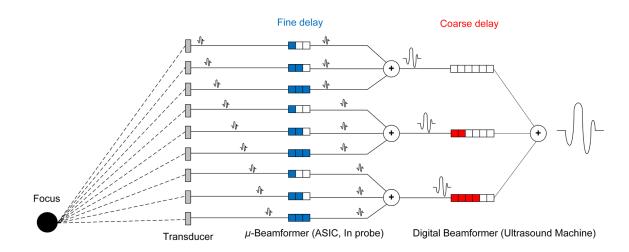

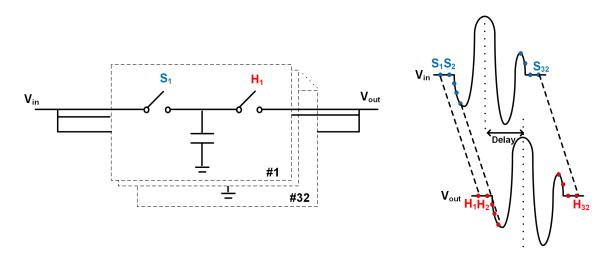

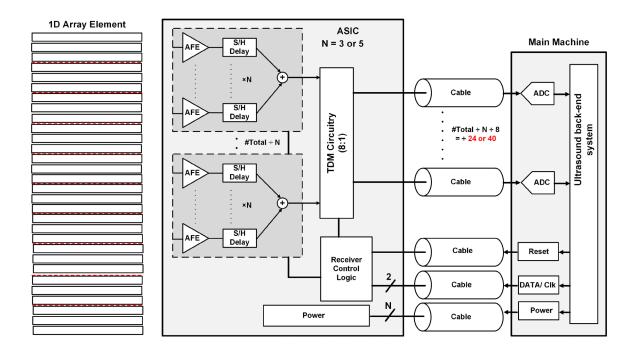

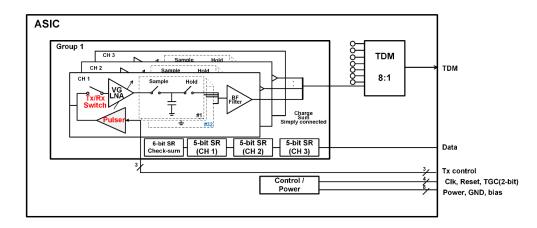

To reduce the number of wires in ultrasound systems, recent research shows several approaches in receiver (Rx) side. Sub-array beamforming ( $\mu$ -beamforming) with analog delay chains which adopts a switched-capacitor-based delay has been demonstrated [21]-[29]. This technique is performed by delaying the signals relative to each other in such a way that waves from a certain focal point, arrive simultaneously and can be coherently summed in a sub-array block. This approach requires a large number of capacitors and switches for each channel for achieving enough delays, induces mismatch between channels, and could not satisfy back-end system which make use of the advanced imaging technique requiring the raw echo data from all channels. The digital subarray beamforming with  $\Delta\Sigma$  modulator has shown compact integration [30]. However, this system requires high frequency operation (960 MHz), which is difficult to feed into long interconnection in catheter-based application, limiting the integration of high voltage (HV) transmit circuits with thick oxide gate on a single chip.

#### 1.3.2 Integrated ADCs

One of the popular techniques which is adopted in 2-D array type systems is onchip integrated ADC. The integration of ADCs will allow digital signal processing for reducing the number of interconnects between the transducer array and the signal processing unit. This technique is usually used in combination with  $\mu$ -beamforming [23], however, in a size and power constrained system, such as an ICE catheter, this would be simply be not feasible or very challenging to implement [31].

#### 1.3.3 PWM and FDM

To reduce the cable count for ultrasound catheter probes, pulse width modulation (PWM) technique was reported in [32]. PWM employs a train of pulses where the signal is sampled and each sample value is encoded in the width of a pulse. Once converted to duty cycle, the information becomes more immune to channel noise and attenuation. Furthermore, PWM requires less area and power than ADCs [33]. One major disadvantage of PWM technique is that it requires very high channel bandwidth to transfer data from PWM source to signal processor. Frequency division multiplexing (FDM) has been shown to be feasible for ICE application [34]. However, this approach requires multiple number of analog filters and mixers that are vulnerable to process variations, which will increase the mismatch and the complexity of the system.

#### 1.3.4 TDM

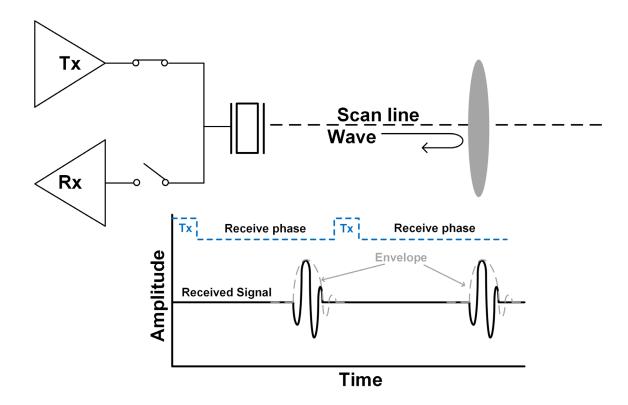

Time-division multiplexing (TDM) has been used in communications systems to reduce the number of channels. This method allows multiple channels to share the same wire by assigning each channel in a proper time slot while sampling at the receiver with the same channel number of ADCs as shown in Figure 3(a) [35], [36]. One of the advantages of Analog TDM is that it needs relatively small amount of circuitry and lower power consumption, since it requires multiplexer and digital counting logic to sample the data. This compact structure makes it suitable for catheter-based applications. Another

approach shows to reduce the number of ADC that de-multiplexer samples with high clock frequency which is at least the number of channel times of the Nyquist rate as shown in Figure 3 [37].

**Figure 3.** (a) Block diagram of standard Time-division multiplexing scheme and (b) reduced number of ADC scheme.

#### 1.4 Transmitter Array Cable Reduction

Recent research shows that the transmit beamformer can be integrated in the application-specific integrated circuit (ASIC) to reduce the cable in transmitter (Tx) side. A column-row-parallel on-chip transmit beamformer was reported, however, it requires the number of cables proportional to the number of elements [38]. Another approach uses an external counter and the beamformer has limited operation ability which can only fire one pulse for each channel [39], [40]. On-chip beamformer with integrated counter was

presented in [41], however, it still requires multiple number of control signals to generate pulse for each channel.

#### **1.5** Transmitter Technique for Increasing the Acoustic Pressure

In recent years, the capacitive micromachined ultrasound transducers (CMUT) have shown several advantages over the conventional bulk piezoelectric transducers, due to smaller size, wider bandwidth, and ease of integration with interfacing circuitry [42]. Compared to piezo-electric transducers, CMUTs typically have larger electrical impedances for the same transducer area. Although integration with reduced parasitics lead to low noise CMUT receivers [43], larger voltages are required to generate the required pressure output by CMUT transmitters as compared to piezoelectric transducers. Therefore, CMUT based ultrasound systems would benefit from high voltage (HV) ultrasound pulse generators that utilize the maximum available voltage level given the integrated circuit process constraints.

HV digital pulsers are commonly used in current commercial systems for their simplicity [44], while recent publications shows that linear amplifiers are also becoming attractive in driving piezoelectric transducers, capable of generating low harmonic content signals by adopting apodization profiles [45]. For a CMUT load, however, nonlinear distortion of the transducer can refute good linearity performance of the linear amplifier's output signal. Moreover, amplifiers have higher power consumption and considerable power loss when charging and discharging the CMUT parasitic capacitance, which reduce the pulser power efficiency [46]. A three-level pulser with pulse shaping and charge

recycling capabilities has been reported in [47], saving power in the pulser at the cost of requiring multiple supply voltages, which need HV DC-DC converters and extra capacitors, increasing overall system complexity and power consumption. Furthermore, there is demand for pulsers capable of generating versatile HV output waveforms efficiently within a compact chip area especially for applications such as intracardiac echocardiography (ICE) and intravascular ultrasound (IVUS) imaging, which are implemented on catheters that are only 1 mm to 3.3 mm in diameter (3–10 F) [48]-[55].

The main challenges in designing interface electronics in catheter based applications are limited space, temperature rise, supply voltage drop across long interconnects, and number of control lines in the catheter. These applications clearly benefit from interface electronics integration, such as CMUT-on-CMOS or flip-chip bonding [56], [57]. To further reduce the catheter electrical interconnect complexity, the ultrasonic transmitter (US-Tx) beam-forming, driver electronics and HV pulser can be integrated directly under the CMUT array. In addition, the CMUT fabrication processes allow for fabricating HV capacitors within its MEMS structure, which can be used in the pulser bootstrap circuit to further reduce the size and voltage drop across the long catheter wires by using a lower external supply voltage [58].

This thesis describes development and implementation of several integrated electronic techniques for high performance ICE catheters with cable reduction. In Chapter 2, high voltage pulser designs are introduced that are suitable for use with CMUTs and provide voltage levels exceeding the CMOS process limits by adopting dedicated protection technique. Chapter 3 focuses on design and verification of ASIC for 64 channel

single-chip reduced wire catheter system. Chapter 4 demonstrates the single-chip CMUTon-CMOS system, showing compact and feasible package solution for ICE application. Chapter 5 describes the hybrid cable reduction system, which combines TDM system with sub-array beamformer ( $\mu$ -beamformer). The proposed system shows massive cable reduction in Rx circuitry, paving the way to design reduced wire 2D array system. Finally, Chapter 6 concludes the thesis and describe future works.

# CHAPTER 2. SUPPLY- DOUBLED PULSER DESIGN FOR CMUTS

#### 2.1 Three Level Supply-Doubled Pulser

Capacitive micromachined ultrasound transducers (CMUT) have been shown to have many advantages for medical ultrasound imaging systems, such as compact size, integration with analog front-end circuits, and wide bandwidth. However, CMUTs are prone to having low transmit sensitivity, and one way to overcome this limitation is using higher pulse voltages. Moreover, advanced 3-D ultrasound applications, such as Intracardiac echocardiography (ICE) and intravascular ultrasound (IVUS) imaging, require integration of the interface electronics with the CMUT arrays in a very limited space, in which low supply voltages are preferred for safety reasons.

15

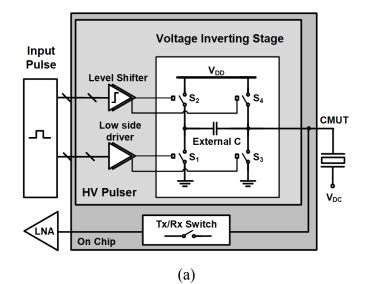

**Figure 4.** (a) A simplified schematic diagram of the supply-doubled (inverted) high voltage pulser, and (b) the operation of voltage doubling stage.

Capacitive micromachined ultrasound transducer (CMUT) has shown many advantages in ultrasound medical imaging, such as compact size, integration with analog front-end circuits, and wide bandwidth. However, CMUTs are prone to having low transmit sensitivity, and one way to overcome this limitation is using higher pulse voltages. Moreover, advanced 3-D ultrasound applications, such as Intracardiac echocardiography (ICE) and intravascular ultrasound (IVUS) imaging, require integration of the interface electronics with the 2-D CMUT arrays in a very limited space, in which low supply voltages are preferred for safety reasons.

The primary objective of voltage-doubling circuit is to generate sharp pulses with amplitudes close to twice the supply voltage without violating safe operating range of its circuit elements [58]. A simplified schematic diagram of the proposed pulser is depicted in Figure 4(a).

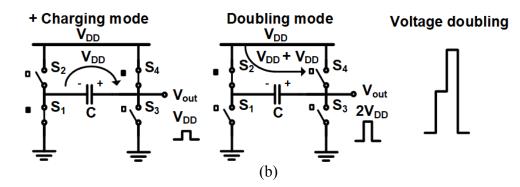

**Figure 5.** (a) Schematic of the proposed voltage doubled pulser. (b) Schematic of the input driving buffers and level shifters for high voltage PMOS input signals.

The external control logic generates low voltage control signals and level shifters convert the dc voltage levels to drive double-diffused metal oxide semi-conductor (DMOS) transistors of the pulser. Figure 4(b) shows operation of the voltage doubling stage. A capacitor, C, which can be on-chip or integrated with the CMUT array, is charged to  $V_{DD}$ during charging mode through S<sub>1</sub> and S<sub>4</sub>. Then, a HV switch, S<sub>2</sub>, drives the negative terminal of C to  $V_{DD}$  during doubling mode, while all other switches are open for  $V_{out}$  to reach  $2V_{DD}$ . S<sub>3</sub> is used to discharge C by connecting it to ground. The CMUT can be modeled mainly as a capacitive load, resulting in a capacitive voltage divider between C and CMUT, which indicates the actual output pulse voltage. The voltage doubling stage requires careful design because it goes beyond the process operating voltage. To ensure safe operation, we employed dynamically gate-biased transistor stack and Schottky diodes to protect all the transistors from out of range operating conditions. Figure 5 shows detailed schematic of the proposed pulser, which is driven by three input control signals (I<sub>1</sub>, I<sub>2</sub>, and I<sub>3</sub>). Two N-type DMOS transistors, M<sub>1</sub> and M<sub>3</sub>, are driven by 0 - 5 V control signals. Two P-type DMOS transistors, M<sub>2</sub> and M<sub>5</sub>, are driven by 40 - 45 V level-shifted control signals. Note that in this case,  $V_{DD} = 45$  V. To achieve a compact design, simple level shifters are used in Figure 5(b), while ensuring that IN<sub>P1</sub> and IN<sub>P2</sub> generate 40 – 45 V sharp pulses with low current consumption, compared to the CMUT driving stage [59].

The circuit operation is similar to the bootstrapping circuits in [60]-[64]. During charging mode, the external capacitor, C, is charged up to  $V_{DD}$  -  $(V_{D2} + V_{D3})$  by turning on  $M_1$  and  $M_5$  transistors, where  $(V_{D2} + V_{D3})$  is the forward voltage drop across  $D_2$  and  $D_3$ . When C is charged, we turn on  $M_2$  and turn off all the other transistors so that  $V_{out}$  is bootstrapped to  $2V_{DD}$  -  $(V_{D2} + V_{D3})$ . During this doubling mode, it is crucial to ensure that all devices in the circuit are operated in their safe operating conditions, considering the fact that in this process, the drain-source junction breakdown and gate-oxide breakdown voltages are 60 V and 5 V, respectively. To prevent excessive  $V_{DS}$  on  $M_5$  and its parasitic N-well substrate diodes from turning on, two HV Schottky diodes are added in series with  $M_5$ . Each diode has a maximum reverse voltage of 36 V, and when the output is doubled, the two diodes should handle 45 V of total reverse voltage between them, resulting in each diode having reverse voltage well below its limit. Between  $V_{out}$  terminal and GND, stacked N-type DMOS transistors,  $M_3$  and  $M_4$ , are used to ensure safe operation when  $V_{out}$  is doubled. The gate of  $M_4$  is dynamically biased to  $V_{DD}$  during doubling mode, while  $M_3$  is

turned off. The Zener diode,  $D_1$ , keeps  $V_{GS}$  of  $M_4$  below 5 V, so that  $M_3$  and  $M_4$  can divide the doubled output voltage across their designated drain-source voltage limit.

The value of external capacitor, C, is key to determine the pulser Vout and slew rate according to,

$$V_{out1} = V_{DD} - (V_{D2} + V_{D3})$$

(4)

$$V_{out} = V_{DD} + V_{out1} \times \frac{C}{C + C_{CMUT}}$$

(5)

where  $C_{CMUT}$  is the equivalent capacitance of the CMUT. Therefore, C should be large to obtain higher V<sub>out</sub>. However, larger C would increase the output RC time constant, limiting the operating frequency range and slew rate of output pulses,

$$SR = \max(\frac{dV}{dt}) = \frac{I_{\max}}{C + C_{CMUT}}$$

(6)

where  $I_{max}$  is the maximum current sourced to capacitance. By decreasing slew rate, Vout will suffer from slow charging problem. Moreover, if C is integrated in the CMUT, its value may be limited by the size of the CMUT. Thus deciding the optimal value of C is critical in the pulser design. In this study, we consider a particular application of 2-D CMUT array for intracardiac echography (ICE), where the center frequency is about 8.3 MHz and CMUT array element size is limited to approximately 100 × 100  $\mu$ m<sup>2</sup>, resulting in *C*<sub>CMUT</sub> = 2 pF. We also investigated the case for an 8 pF device capacitance, the capacitance of the CMUT when probed by an oscilloscope probe (P6139A, Tektronix) for electrical characterization.

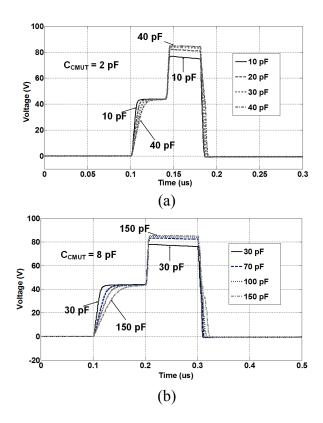

**Figure 6.** Simulation of the output pulse with different *C* values, (a) when CMUT loading is considered 2 pF, (b)  $C_{CMUT} = 8$  pF.

A realistic design target for the pulser would be to achieve peak HV level of at least  $1.8 \times \text{VDD}$  while having a rise time less than a quarter period of the CMUT center frequency, i.e. 30 ns for the 8.3 MHz CMUT. (1) and (2) suggest that the minimum required C would be > 4 × C<sub>CMUT</sub>. Considering the forward voltage drop across the diodes and parasitic capacitances of the large DMOS transistors, we chose C = 30 pF for 2 pF of CCMUT. Also to obtain SR > 3 V/ns during the charging mode, we designed M<sub>5</sub> to have I<sub>max</sub> > 100 mA, based on (3). Since the size of large DMOS transistors mainly define the layout size, we chose Imax for driving a 2 pF CMUT load at 8.3 MHz center operating frequency. Figure 7 shows the comparison between simulation and measurement results with three control signals, I<sub>1</sub>, I<sub>2</sub>, and I<sub>3</sub>.

**Figure 7.** Simulated and measured three-level output pulse along with three input control signals. C = 100 pF,  $C_{CMUT} = 8 \text{ pF}$ .

To verify the pulser design and compare with measurements we simulated the voltage-doubled output pulse for 2 pF of CMUT load and 8 pF of passive probe loading, for which C was changed within 10 - 40 pF and 30 - 150 pF, respectively. For ensuring the initial condition of Vout = 0 V, a 100 k $\Omega$  resistor was added in parallel with C, which adds a slight slope on doubled output pulse with minimal effect on output voltage division. With 2 pF load, C = 30 pF shows 85 Vpp of output pulse, rise time of 11.5 ns, and SR = 3.2 V/ns in the charging mode, which is suitable for driving a CMUT array with 8.3 MHz center frequency. With 8 pF load, C = 100 pF shows 85 Vpp of output pulse, rise time of 34.8 ns, and SR = 1.0 V/ns during charging mode. The slew rate of the doubling stage does not depend on the value of C, as evident in Figure 6, because the charged C is simply connected in series with *V*<sub>DD</sub>.

Figure 8. Microphotograph of the proposed pulser chip.

Figure 9. Measured output pulse with C = 30 pF and 100 pF when CMUT loading is 8 pF.

The proposed pulser was designed and fabricated in a 0.18-µm 60 V power management 4M1P HV-CMOS process, and occupied a core area of 0.2 mm<sup>2</sup>, as shown in Figure 8. The chip was mounted on a PCB inside a QFN package along with an off-chip surface mount capacitor, *C*. Figure 9 shows the measured output voltage with two different *C* and more than 8 pF loading, including the input capacitance of a passive probe and parasitic capacitance of wire-bonding and PCB routing in parallel with 100 k $\Omega$  resistor. The measured waveform with *C* = 100 pF, shows peak *V*<sub>out</sub> = 85 V and slew rates of 0.88 V/ns, 3.2 V/ns, and 2.44 V/ns during charging, doubling, and falling modes, respectively. Similarly, with C = 30 pF, peak  $V_{out} = 78.6$  V was achieved with slew rates of 2.1 V/ns, 2.9 V/ns, and 4.7 V/ns, respectively. Figure 7 shows a sample measurement with non-zero  $T_1$ ,  $T_2$ , and  $T_3$  values overlapped for comparison with the simulations.

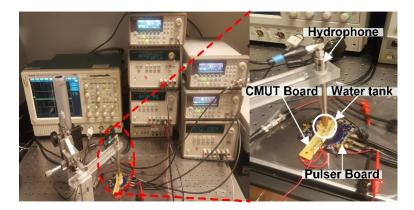

Figure 10. Acoustic pressure experimental setup with CMUT array board and pulser board.

An acoustic pressure measurement setup was used to measure the US-Tx pressure with an actual CMUT load, as shown in Figure 10. The CMUT used in this experiment occupied  $100 \times 100 \ \mu m^2$  area on silicon and consisted of a 2 × 2 array of four 45  $\mu m$  wide square membranes. It created a 2 pF element, ~1.8 pF of which was due to bond pads parasitic capacitance, with 8.33 MHz center frequency and -3 dB bandwidth of 5 MHz. It was part of a larger 2-D ICE imaging array, which was fabricated using a low temperature CMOS-compatible process.

Figure 11. (a) Transmitted peak-to-peak acoustic pressure measurement and simulation with different pulse shapes and supply voltages. (b) Measured transmitted pressure with  $T_1$  = 30 ns,  $T_2$  = 30 ns,  $T_3$  = 0 ns, and  $V_{DD}$  = 30 V.

The CMUT array, mounted on a separate PCB, was connected to the larger pulser board via header pins. The off-chip capacitor, C = 30 pF, was selected to obtain maximum output swing and fast slew rate as discussed. The CMUT array was submerged in a water tank, while a hydrophone (HGL-0085, Onda Corp) was placed above the CMUT array, 4.5 mm from its surface, to measure the US-Tx acoustic pressure. The measured peak-to-peak US-Tx pressure results are summarized in Figure 11. V<sub>DD</sub> in these experiments was reduced to 30 V because the CMUT breakdown voltage was 60 V. The maximum peak-to-peak pressure of 2467 Pa was recorded with [30, 30, 0], as shown in Figure 11(b). Table 1 summarizes the pulser specs for the [30, 30, 0] pulse shape and benchmarks its performance against prior work.

| Parameter                    | This     | [47] | [59] | [65]    |

|------------------------------|----------|------|------|---------|

|                              | work     |      |      |         |

| Input voltage (V)            | 5        | 3.3  | 3.3  | 1.8     |

| Output voltage (V)           | 85       | 30   | 60   | 12.8    |

| VDD (V)                      | 45       | 30   | 60   | 12.8    |

| Frequency (MHz)              | 8.33     | 2.5  | 1.38 | 1.25    |

|                              |          | to 5 |      |         |

| Rise/fall time (ns)          | 26,16/18 | 30   | 68/6 | 40/50   |

|                              |          |      | 8    |         |

| Power (mW)                   | 48.6     | 52.4 | 98.1 |         |

| Power (mA)                   | 150      | -    | -    | 19.9    |

|                              | Dynamic  |      |      | Dynamic |

|                              | *        |      |      | *       |

| Chip area (mm <sup>2</sup> ) | 0.2      | -    | 0.08 | 0.022   |

| Output load (pF)             | 2        | 40   | 18   | 15      |

| Pulse shaping                | Y        | Y    | N    | Ν       |

| Technology (µm)              | 0.18     | 0.18 | 0.35 | 0.18    |

Table 1. Benchmarking of the proposed pulser performance.

This chpater presents an integrated voltage-doubling and pulse-shaping HV pulser circuit to interface CMUT ultrasound systems in a 0.18-µm 60 V 4M1P CMOS/DMOS process. The presented circuit overcomes process limitation by adopting HV protection techniques that generate 85 Vpp of output pulse with 45 V supply voltage. A three level pulsing scheme is successfully applied to a CMUT array element and optimized for maximum acoustic pressure, as predicted by a large signal CMUT model, paving the way for simulation-based CMUT pulser optimization. The prototype pulser ASIC measurements were conducted with an off-chip capacitor, which can be integrated with the

CMUT using high-K dielectric layers during CMUT fabrication. Ongoing research involves co-optimization of the pulser and CMUT arrays using CMUT-on-CMOS technology for very compact catheter-based ultrasound imaging systems.

## 2.2 Two Level Supply-Doubled Pulser

Unipolar digital pulsers have often been used in integrated ultrasound systems, but recently linear amplifiers and three-level pulser topologies have also shown good performance in terms of low harmonic content and power efficiency, respectively. However, these new circuits require additional auxiliary blocks, such as digital-to-analog converters (DAC) and DC-DC converters with extra capacitors, which would increase the overall system complexity. In the previous section, a 3-level supply-doubled pulser using boot-strapping circuit to overcome the HV supply limitation was described and used for pulse-shape optimization. However, that circuit requires three different input control signals, and unavoidably has to deal with middle level transitions.

**Figure 12.** Simplified schematic diagram of the proposed pulser during (a) charging and (b) voltage doubling phases.

The proposed pulser is designed to generate two-level sharp pulses with supplydoubled voltage [66]. A simplified schematic diagram of the proposed pulser is shown in Figure 12. The operation of pulser is similar to a bootstrap switch. A capacitor, C, is charged to V<sub>DD</sub> during charging phase through HV switches, S<sub>2</sub> and S<sub>3</sub>, while all the other HV switches are open, and V<sub>out</sub> stays 0 V. When C is fully charged, S<sub>1</sub> drives the negative terminal of V<sub>DD</sub> and S<sub>5</sub> connects the charged C to V<sub>out</sub> that theoretically reaches 2V<sub>DD</sub> during the voltage doubling phase. Subsequently, S<sub>4</sub> and S<sub>5</sub> are closed to return V<sub>out</sub> back to 0 V, and the same sequence repeats after S<sub>5</sub> opens to detach Vout from the charging C. The CMUT is often modeled as a mainly capacitive load, which is connected to Vout. The actual output pulse voltage can be found from the capacitive voltage division between C and CMUT. Hence, deciding the optimal value of C, depending on the CMUT specs is quite important in design of this pulser. The proposed pulser also requires careful design because it can go beyond the process limitations. Therefore, the pulser features stacked dynamically gate-biased transistors, Schottky diodes, and Zener diodes to protect all the transistors from consequences of "out of range" operation. Figure 13 shows the detailed schematic diagram of two level suppy-doubled pulser.

**Figure 13.** Schematic diagram of (a) the proposed pulser and (b) input driving buffers and level shifters.

The proposed pulser utilizes double-diffused metal oxide semiconductor (DMOS) transistors, Schottky diodes, and Zener diodes, as shown in Figure 13. The digital control logic from an external pulse generator control two 5 V input signals ( $I_1$  and  $I_2$ ), needed to control the pulser. Two N-type DMOS transistors, M<sub>1</sub> and M<sub>3</sub>, are driven by 0 - 5 V control signals. Two P-type DMOS transistors, M<sub>2</sub> and M<sub>6</sub>, are driven by level-shifted high voltage control signals. Level shifters are designed compactly to generate 40~45 V sharp signals ( $I_{P1}$  and  $I_{P2}$ ), when  $HV_{DD} = 45$  V, with little current consumption compared to the CMUT driving phase to drive high side of supply-doubled stage of pulser, as shown in Figure 13(b). M<sub>4</sub> and M<sub>5</sub> are dynamically gate biased during the voltage doubling phase.

Figure 14. Simulation of the control inputs and output pulse with different *C* values, when CMUT loading is considered 8 pF, and  $HV_{DD} = 45$  V.

In a closer look, the circuit operation can be divided into four phases, as shown in Figure 14. During the first phase, M<sub>3</sub> is turned on to connect  $V_{out}$  to 0 V. Note that the gate of M<sub>4</sub> is connected with pull-up resistor to  $LV_{DD} = 5$  V as its initial phase. In phase 2, the off-chip capacitor, C, is charged up to  $HV_{DD} - (V_{D2} + V_{D3} + V_{D4})$  by turning on M<sub>1</sub> and M<sub>6</sub> transistors, where  $(V_{D2} + V_{D3} + V_{D4})$  is the forward voltage drop of two Schottky and a Zener diode of the same names in series. The forward voltage drop of D<sub>2</sub> also ensures that M<sub>5</sub> remains off during this phase, such that  $V_{out}$  continues to stay at 0 V. Once C is fully charged, in the third phase, M<sub>2</sub> is turned on, while all other controllable transistors are turned off. This operation employs bootstrapping technique with the charged C connected in series with  $HV_{DD}$  through M<sub>2</sub>, resulting in  $V_{out}$  to be boot-strapped to nearly 2  $HV_{DD}$ . During this phase, Zener diode, D<sub>2</sub>, is reverse biased with 5 V across it, turning on M<sub>5</sub>, which is a P-type DMOS, to connect the charged C to  $V_{out}$ . It is necessary to make sure that all devices in the circuit are operated in their safe operating conditions, considering the fact that in this 0.18  $\mu$ m Bipolar-CMOS-DMOS (BCD) process, the maximum permissible drain to source and gate to source voltages are 60 V and 5 V, respectively. To ensure M<sub>6</sub>, which is a P-type DMOS transistor, operates in the safe region, D<sub>3</sub> and D<sub>4</sub>, which are HV Schottky diodes, are added in series to D<sub>2</sub>. Each Schottky diode has a reverse break down voltage of 36 V, and together, they can protect against 45 V of reverse voltage during the voltage doubling phase by dividing the reverse voltage within their limits. Also M<sub>3</sub> and M<sub>4</sub>, which are N-type DMOS transistors, are stacked to handle supply-doubled output signal while the gate of M<sub>4</sub> is dynamically biased to  $HV_{DD}$ . The Zener diode, D<sub>1</sub>, keeps V<sub>gs</sub> of M<sub>4</sub> below 5 V, so that M<sub>3</sub> and M<sub>4</sub> can divide the supply-doubled voltage, which is above the process limit, among them.

The value of C is an important parameter that determines  $V_{out}$  according to,

$$V_{cap} = HV_{DD} - (V_{D2} + V_{D3} + V_{D4})$$

(7)

$$V_{out} = HV_{DD} + V_{cap} \times \frac{C}{C + C_{CMUT}}$$

(8)

where  $C_{CMUT}$  is the equivalent capacitance of the CMUT. Larger *C* would increase  $V_{out}$ , resulting in higher voltage swing. However, it also increases the charging time in the second phase. Hence, *C* should be selected carefully. Moreover, if in the future, *C* is integrated with the CMUT by adding more layers with high-K dielectric in the MEMS process, the maximum available size would be limited by the area of the CMUT. Figure 14 shows the simulation results, while connecting the output node to equivalent CMUT

loading of 8 pF, which is the same as the input capacitance of the oscilloscope probe, P6139A (Tektronix, Beaverton, OR). The design target for the pulser would be to achieve maximum peak-to-peak voltage level of  $1.8 \times HV_{DD}$ , while having rise- and fall-times less than a quarter period of the center frequency of the CMUT, which is 30 ns for 8.33 MHz. (1) and (2) suggest that the minimum required C would be larger than  $4 \times C_{CMUT}$ . However, considering the forward voltage drop across diodes, parasitic capacitances of the large DMOS transistors, and PCB parasitic capacitance, C was chosen  $\sim 12 \times C_{CMUT}$ . As simulation shows in Fig. 3, of C = 30 pF was not sufficient to drive the 8 pF capacitive load up to 1.8 $HV_{DD}$ , while C = 100 pF resulted in  $V_{out} > 1.8HV_{DD}$ . The rise-time and falltime are fast enough because during rise-time, charged C is simply connected in series with  $HV_{DD}$ , while during fall-time, one node of C is floating, and the load capacitance is only  $C_{CMUT}$  and parasitic capacitance. The size of M<sub>6</sub> is selected such that it can deliver more than 100 mA to fully charge C = 100 pF within the second phase, which is about 100 ns. During the 4th phase, M<sub>3</sub> pulls down Vout to 0 V to complete generation of the sharp twolevel pulse.

The proposed pulser is designed and fabricated in a 60 V 0.18- $\mu$ m power management BCD process. The core of the pulser occupies 0.258 mm<sup>2</sup> of silicon area, as shown in Figure 15. The chip was mounted on a PCB within a QFN package with a 100 pF off-chip surface mount (SMD) capacitor. Figure 16 compares the measured output voltage with simulation results, which shows very good agreement. During measurement,  $C_{CMUT}$  was replaced with an oscilloscope probe that has 8 pF parasitic capacitance (P6139A, Tektronix) and  $HV_{DD} = 45$  V. The measured waveform shows  $V_{out} = 84.2$  V, and peak rise and fall slew rates of 2.52 V/ns and 7.5 V/ns, respectively, which are suitable for driving an 8 pF CMUT load with 8 MHz center frequency. Measurements from over 10 chips have shown consistent results with  $V_{out}$  (mean±std) = 84.03 ± 1.28 V, indicating reliability of this HV pulser circuit.

Figure 15. Microphotograph of the proposed pulser.

Figure 16. Measured and simulated supply-doubled pulse, when C and CMUT loading are considered 100 pF and 8 pF ( $HV_{DD} = 45$  V).

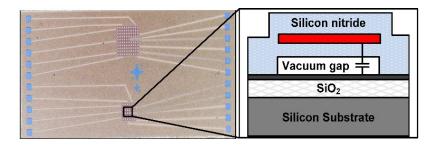

An acoustic pressure measurement setup was used to measure the transmitted ultrasonic pressure with a CMUT, fabricated in our in-house process. Figure 17 shows the layout and cross-sectional view of the CMUT. The CMUT used to test the pulser in this measurement occupies  $100 \times 100 \ \mu m^2$  on silicon substrate and consists of a 2 × 2 array of

four 45  $\mu$ m wide square membranes, fabricated using a low temperature CMOScompatible process. The CMUT characterization shows 2 pF capacitance and 8.33 MHz of center frequency, with 5MHz of -3dB bandwidth. The CMUT array was mounted on a separate PCB and connected to the pulser PCB via vertical connection line, as shown in Figure 18.

Figure 17. Layout of the CMUT array, and cross-section view of CMUT layers.

Figure 18. Acoustic measurement setup for testing the proposed pulser with a CMUT array.

By selecting C = 100 pF, the pulse can drive up to 8 pF of capacitive loading with fast-enough output swings, considering large parasitic capacitance added to the CMUT setup by the interconnects and the PCB. The CMUT array was submerged in water in a small container, while a hydrophone (HGL-0085, Onda Corp, Japan) was aligned above

the CMUT array, 5.9 mm from its surface, to measure the transmitted ultrasonic acoustic pressure.  $HV_{DD}$  in this measurement was lowered to 20 V, because the collapse voltage of the CMUT is ~40 V. The proposed supply-doubled pulser generates ~2 kPa<sub>p-p</sub> with  $V_{out} \approx$  36 V, which is more than twice the pressure pulse generated when the same CMUT was driven by a conventional supply-limited pulser (~0.92 kPa<sub>p-p</sub>,  $V_{out} \approx$  20 V). This is because of the nonlinear CMUT characteristic in large signal operation, resulting in the proposed pulser being able to generate larger pressure in a limited-supply voltage environment.

**Figure 19.** Measured transmitted pressure with CMUT. Blue line shows the pressure of conventional supply-limited pulser, red dot-line shows the pressure of supply-doubled proposed pulser.

The new pulser performance is summarized in Table 1, and compared with the prior work in the literature. Power consumption is calculated by assuming that the proposed pulser would be used in an imaging system up to a depth of 7.5 cm with 1 to 10 ratio of Tx and Rx periods with one pulse firing. The proposed pulser shows successful operation

beyond process voltage limits, while maintaining fast slew rates to drive CMUTs operating in 8.33 MHz range.

| Parameter      | [47] | [58]         | [65]      | This     |  |

|----------------|------|--------------|-----------|----------|--|

|                |      |              |           | work     |  |

| Input voltage  | 3.3  | 5            | 1.8       | 5        |  |

| (V)            |      |              |           |          |  |

| Output         | 30   | 85           | 12.8      | 84.2     |  |

| voltage (V)    |      |              |           |          |  |

| $V_{DD}(V)$    | 30   | 45           | 12.8      | 45       |  |

| Frequency      | 2.5  | 8.33         | 1.25      | 8.33     |  |

| (MHz)          | - 5  |              |           |          |  |

| Rise/fall slew | 1/1  | 1.73,2.5/4.7 | 0.32/0.25 | 2.52/7.5 |  |

| rate (V/ns)    |      |              |           |          |  |

| Power (mW)     | 52.4 | 48.6         | -         | 51.8     |  |

| Peak current   | -    | 150          | 19.9      | 160      |  |

| (mA)           |      | Dynamic*     | Dynamic*  | Dynamic* |  |

| Chip area      | -    | 0.2          | 0.022     | 0.258    |  |

| $(mm^2)$       |      |              |           |          |  |

| Output load    | 40   | 8            | 15        | 8        |  |

| (pF)           |      |              |           |          |  |

| Technology     | 0.18 | 0.18         | 0.18      | 0.18     |  |

| (µm)           |      |              |           |          |  |

**Table 2.** Benchmarking of the proposed two level pulser performance.

\* Simulation results

In conclusion, this section presented a HV pulser with the ability to drive CMUT arrays beyond the supply voltage. The new pulser has been implemented in a  $0.18_{\mu}m$  60 V Bipolar-CMOS-DMOS (BCD) process. The proposed circuit overcomes process limitation, adopting HV protection techniques and combining them with a bootstrap topology. In our measurements, the pulser generated 84.2 V<sub>pp</sub> of output swing with a 45 V supply voltage. The close to doubled supply voltage can be generated with only two control signals at low voltage logic levels, simplifying the system design by eliminating the need for auxiliary blocks, such as DAC or DC-DC converter. The required capacitor, *C*, is too

large to be integrated on-chip, but it can be integrated with the CMUT fabrication process using high-K dielectric layers. Therefore, the proposed beyond supply voltage pulser is expected to be an attractive candidate for highly-integrated CMUT-on-CMOS 2-D and 3-D ultrasound imaging architectures that are often supply voltage limited, and high drive pulses to improve CMUT output pressure and ultrasound image quality.

## 2.3 Supply-Inverted Pulser

Two level high voltage (HV) digital pulsers are commonly used in CMUT ultrasound imaging systems for their simplicity. A three-level pulser with pulse shaping and charge recycling capabilities has also been reported in [47], saving power in the pulser at the cost of requiring multiple supply voltages, requiring HV DC-DC converters and extra capacitors and increasing the overall system complexity. Additionally, it is shown in [67] a differential three level pulser that achieves lower power consumption and area reduction compared to commonly used single ended pulsers. This differential pulser took advantage of the fact that each of the CMUT terminals can be connected to a different pulser obtaining a differential driving voltage. However, it still requires multiple HV supplies.

The integration of electronics with ultrasound transducer array would improve performance by reducing parasitic effect and removing long cable loading effect. A motivation for this pulser design is especially for compact catheter-based imaging applications, such as ICE and IVUS. This application can get advantages using this design by improving safety at lower cost by using lower voltages on the catheter without compromising the pulser voltage levels. One feasible solution is adopting bootstrapping circuit in the pulser design, which is used in various applications such as improving accuracy for sample-and-hold circuits in analog-to-digital converters (ADC), and voltage level shifters of DC-DC converters. These circuits are widely used for generating twice the supply voltage to maximize the efficiency of circuit or to reduce ON-resistance of the switches. In cases where the CMUT fabrication processes allow HV capacitors to be built within their MEMS structure, these capacitors can be used in the pulser bootstrap circuit to further reduce the size and voltage drop across the long catheter wires by using a lower external supply voltage. Although this approach could also be applied to piezoelectric transducers, bootstrapping circuits requiring an extra HV capacitors would be more suitable for CMUT based catheters that utilize CMUT-on-CMOS or flip chip bonded CMOS electronics. A supply-doubled pulser using bootstrapping circuit for driving CMUT was proposed in previous sections, which showed pulse-shaping capability with a single HV supply. However, in that example it was limited to a positive unipolar pulse, and lacked a protection HV switch, prohibiting the use of the same CMUT element both for transmission and for reception.

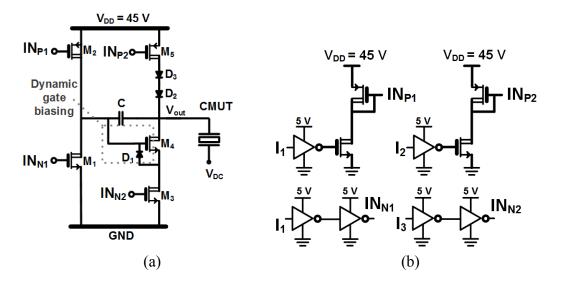

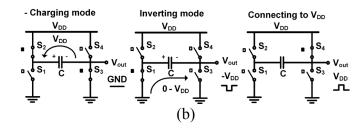

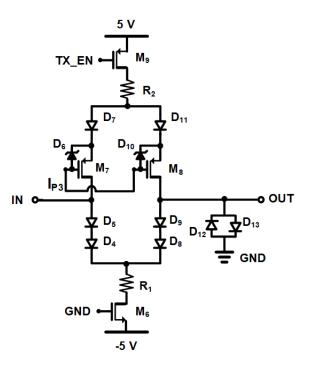

**Figure 20.** (a) Simplified schematic diagram of the proposed pulser and high voltage Tx/Rx switch, (b) the operation of voltage inverting stage.

In this chapter, a HV supply-inverted bipolar pulser combined with a Tx/Rx switch is presented. The pulser provides a HV output swing close to twice its supply voltage, and above the device breakdown, which is often limited by the CMOS process. The design goal of the supply-inverted pulser is to generate a bipolar pulse with peak-to-peak amplitude close to twice the supply voltage without requiring a negative HV supply. It is important to keep every circuit element operating in safe range, including receiver's low voltage (LV) devices during the supply-inverting operation. Figure 20(a) illustrates a simplified schematic diagram of the proposed pulser and Tx/Rx switch. The digital control logic from external pulse generators trigger low voltage control signals to drive N-type doublediffused metal oxide semi-conductor (DMOS) transistors to turn on/off low side switches. The level shifters convert the DC voltage levels of control signals to drive P-type DMOS transistors of the pulser to control high side switches. The Tx/Rx switch protects the low voltage receiver from HV signals including the negative part of the HV pulse. Blocking this negative HV pulse requires careful design as the output drops lower than the substrate voltage, which can cause parasitic diodes to switch on unexpectedly.

**Figure 21.** Schematic diagrams of (a) proposed supply-inverted pulser, (b) level shifters for high voltage NMOS/PMOS input signals of supply-inverted pulser