## **HKUST SPD - INSTITUTIONAL REPOSITORY**

| Title   | A 27W D2D Wireless Power Transfer System with Compact Single-Stage Regulated<br>Class-E Architecture and Adaptive ZVS Control |

|---------|-------------------------------------------------------------------------------------------------------------------------------|

| Authors | Ma, Xiaofei; Lu, Yan; Ki, Wing Hung                                                                                           |

- Source Digest of Technical Papers IEEE International Solid-State Circuits Conference, v. 2022-February, February 2022, p. 238-240

- Version Accepted Version

- DOI 10.1109/ISSCC42614.2022.9731724

- Publisher IEEE

- Copyright © 2022 IEEE. Personal use of this material is permitted. Permission from IEEE must be obtained for all other uses, in any current or future media, including reprinting/republishing this material for advertising or promotional purposes, creating new collective works, for resale or redistribution to servers or lists, or reuse of any copyrighted component of this work in other works.

This version is available at HKUST SPD - Institutional Repository (https://repository.ust.hk/ir)

If it is the author's pre-published version, changes introduced as a result of publishing processes such as copy-editing and formatting may not be reflected in this document. For a definitive version of this work, please refer to the published version.

## 14.6 A 27W D2D Wireless Power Transfer System with Compact Single-Stage Regulated Class-E Architecture and Adaptive ZVS Control

Xiaofei Ma1.2, Yan Lu2, Wing-Hung Ki1

<sup>1</sup>Hong Kong University of Science and Technology, Hong Kong, China <sup>2</sup>University of Macau, Macau, China

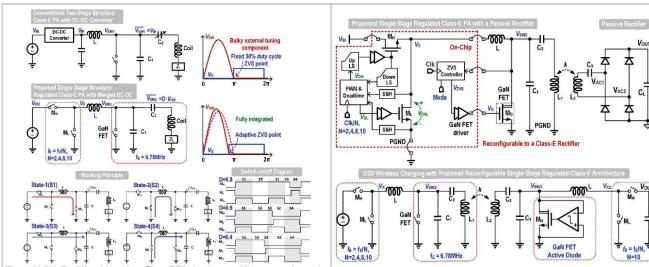

Compact and high-power bidirectional wireless power transfer (WPT) systems are desirable for mobile device-to-device (D2D) wireless fast charging. Prior WPT solutions [1-3] with integrated Class-D power amplifier (PA) provide relatively low output power (<10W). A Class-E PA has higher output power capability than a Class-D PA with the same input voltage. The 70W single-ended Class-E PA in [4] uses one additional bulky discrete MOSFET working as a tunable capacitor for impedance matching, achieving zero-voltage-switching (ZVS) and zero-voltage-derivative-switching (ZVDS) with 50% switching duty cycle across wide load and distance ranges. The 100W differential Class-E PA in [5] provides higher output power but requires a discrete impedance tuning network with 2  $G_{\rm BLOCK}$ 's, 3  $R_{\rm DC}$ 's, and 2 MOSFETs. These two solutions are well suited for pad-to-device wireless charging, but are hard to be embedded in a mobile phone. In addition, to regulate the PA output power, the supply voltage of the PA is tuned by a DC-DC converter in a conventional two-stage solution. In this work, we design a compact single-stage regulated Class-E architecture with adaptive ZVS control for D2D wireless fast charging.

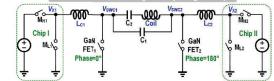

Fig. 14.6.1 shows the highly-integrated single-stage regulated WPT transmitter (TX) structure that merges a DC-DC buck converter with a Class-E PA, saving one power inductor and one filtering capacitor. The off-chip Gallium-Nitride (GaN) switch M<sub>G</sub> works at the LC tank resonant frequency f<sub>o</sub> of 6.78MHz, while the integrated NMOS switches M<sub>H</sub> and M<sub>L</sub> work at 847.5KHz (1/8 of f<sub>o</sub>) for improving the efficiency. To remove the bulky resonant tuning components, we set the ZVS point of M<sub>G</sub> adaptively off the 50% duty cycle (D<sub>E</sub>) point of the Class-E PA, to accommodate load and distance variations. Although off the D<sub>E</sub>=50% operation point will result in higher voltage stress on M<sub>G</sub>, it is designed to be lower than the drain-source breakdown voltage. Besides, M<sub>c</sub> will be turned on right after the ZVS point, to reduce the reverse conduction time, thus improving the efficiency.

There are four working states for output regulation, as shown in Fig. 14.6.1 (Bottom). The switches  $M_H$  and  $M_L$  together with the inductor L form the core of a buck converter. In the steady-state, volt-second balance of L mandates the average value of  $V_{SW2}$  to be equal to  $D \cdot V_{IN2}$ , with D being the duty ratio. The inductor also serves as the choke of the Class-E PA and has large value. The inductor current has small ripple and is proximated as a constant. In State-1, L is energized through the path of  $M_{H}$ -L- $M_{G}$ . In State-2, the inductor current is in the freewheeling mode. In State-3 and State-4, the resonant tank is charged by the inductor current. Taking duty ratio D=0.8 as an example, the one-step regulated Class-E PA works in states  $1 \rightarrow 3 \rightarrow 1 \rightarrow 3 \rightarrow 4$  periodically.

Fig. 14.6.2(top) shows the overall design. The high-side driver of  $M_{H}$  is powered by a traditional bootstrap circuit, using one external diode and one external capacitor. The deadtime controller is a low-power digital circuit with good noise immunity and issues a firm initial deadtime after power-up reset. The bidirectional D2D wireless charging mode with the regulated Class-E architecture is configured in Fig. 14.6.2(bottom). In the rectifier mode, the multiplexer directly connects the comparator output to the GaN driver forming an active diode. When  $V_{SW3}$  is high, the GaN FET  $M_{G}$  is turned off, and the choke inductor L is energized.  $M_{G}$  will be turned on when  $V_{SW3}$  is lower than the ground.

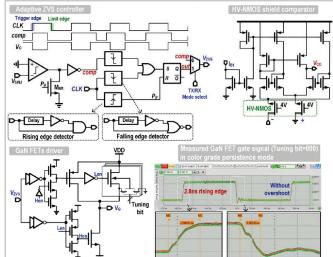

Fig. 14.6.3 presents the adaptive ZVS controller and the GaN driver. The adaptive ZVS controller tracks the ZVS point, which changes with coil distance and load impedance. This ZVS tracking feature can reconfigure the Class-E PA into a Class-E rectifier. A pushpull comparator with HV-NMOS shielding is designed to detect the ZVS point of the V<sub>SW</sub> node. As V<sub>SW</sub> can reach as high as 70V, two 100V NMOS FETs are used to protect the 5V FETs in the comparator. Therefore, this HV comparator can directly sense the V<sub>SW</sub> point without area-consuming resistor divider.

The M<sub>G</sub> turn-off point is triggered by the rising edge of the external input 6.78MHz CLK signal. Also, a short positive pulse P<sub>R</sub> is applied to M<sub>NR</sub> to prevent the comparator from toggling incorrectly due to the induced ringing caused by the high di/dt of the parasitic inductance at the source of M<sub>G</sub>. At the rising edge of the comparator output, which is the detected ZVS point of V<sub>SW2</sub>, M<sub>G</sub> is turned on. At the falling edge of the CLK signal, M<sub>G</sub> will be turned on firmly to prevent it from being damaged when the resonant tuning circuit loses its ZVS state.

Driving the off-chip GaN FET must address the ringing issue caused by the bonding wire and PCB trace parasitic inductors. A conventional solution either uses gate resistance to damp the ringing, which will increase the rising and falling edge time and causes more power loss, or uses active gate driving, which needs complex circuits to generate the driving patterns. [6] uses an NMOS as the high-side switch in the GaN driver, as only NMOS is available in an enhancement-mode GaN process. Fig. 14.6.3(bottom) shows our GaN driver using a CMOS process, to reduce the parasitic inductance-induced ringing of the off-chip GaN FET. In this GaN driver, the NMOS high-side switch works as a current chock when the driver output voltage exceeds the NMOS threshold voltage, and a smaller size PMOS is used to pull up the voltage when the high-side NMOS is turned off. The current chock allows the driver to turn the GaN FET on fast within 2.8ns, while no overshoot or ringing occurs at the V<sub>G</sub> rising edge. The parasitic inductance is different for different packages and PCB layouts. Therefore, the high-side NMOS has three tuning bits, which connects the body of the high-side NMOS to the source or to ground, to control the threshold of the high-side choke NMOS. For larger parasitic inductance, we can increase the threshold voltage of the high-side choke NMOS and vice versa.

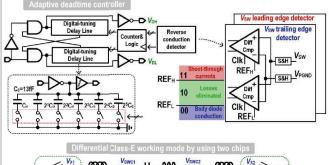

Fig. 14.6.4 shows the digital deadtime controller for the switching regulation part. The digital control loop controls two complementary 6-bit capacitor delay lines for the  $V_X$  leading and trailing edges. The unit capacitance is 13fF. The total capacitance of one capacitor array is 0.8pF. It occupies a small chip area and consumes very low power. The initial delay at the system power-up is set to half of the full delay range. The sample and hold circuits (SH) sample the  $V_x$  and  $V_{PGND}$  signals. Here,  $V_x$  and  $V_{PGND}$  can assume negative values. However, a conventional SH has difficulty in storing a negative voltage. Thus, the SH uses a local charge pump that generates a negative voltage to turn off the sampling switch. Subsequently, the differential dynamic comparator compares  $V_{DSL}=V_{PGND}$  with the reference voltage to detect the body diode working condition of the low-side NMOS M<sub>L</sub>. If the comparator output is '00', M<sub>L</sub> is working in body diode conduction mode, and the control loop will reduce the delay. If the comparator output is '11', shoot-through current occurs between the high- and low-side witches, and the control loop will hold the counter.

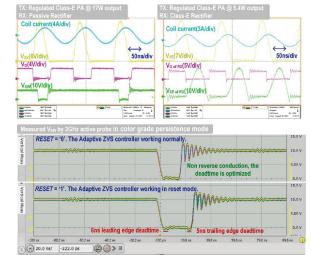

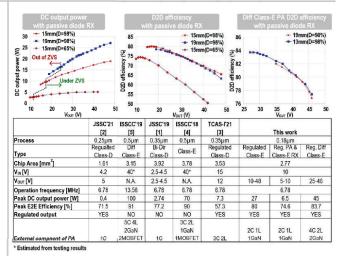

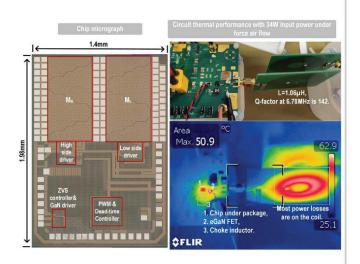

A prototype of our design was fabricated in a 0.18µm BCD-on-SOI process.  $M_{G}$  is an eGaN FET EPC2007C and the choke inductor is 5.6µH. The regulated PA delivers a maximum 27W output power at  $V_{IN}$ =10V and  $V_{OUT}$ =48V, with 63.3% end-to-end (E2E) efficiency over a coil distance of 19mm. The maximum E2E efficiency of 80% is achieved at 15mm coil distance with  $V_{OUT}$ =17V. Fig. 14.6.5 shows the measured current waveform acquired by a de-skewed current probe. Fig. 14.6.5(bottom) shows the measured  $V_X$  of which the leading and trailing edge dead time is controlled adaptively. As shown in Fig. 14.6.4(bottom), the regulated differential PA by using two chips can deliver 45W output power over a coil distance of 19mm. Fig. 14.6.6 is a table that compares the output power and system E2E efficiency of our design with state-of-the-art designs under different conditions. Our one-step regulated PA has the highest efficiency and output power among all single-stage regulated PAs. Fig. 14.6.7 shows the chip micrograph and the die area is 2.77mm<sup>2</sup>.

## Acknowledgment:

This work is supported in part by the Science and Technology Development Fund, Macau SAR under Grants 0093/2019/A2 and SKL-AMSV(UM)-2020-2022.

## References.

[1] F. Mao, Y. Lu, and R. P. Martins, "A Reconfigurable Cross-Connected Wireless-Power Transceiver for Bidirectional Device-to-Device Wireless Charging," *IEEE J. Solid-State Circuits*, vol. 54, no. 9, pp. 2579–2589, Sept. 2019.

[2] F.-B. Yang, J. Fuh, Y.-H. Li, M. Takamiya, and P.-H. Chen, "Structure-Reconfigurable Power Amplifier (SR-PA) and 0X/1X Regulating Rectifier for Adaptive Power Control in Wireless Power Transfer System," *IEEE J. Solid-State Circuits*, vol. 56, no. 7, pp. 2054– 2064. July 2021.

[3] X. Ge, L. Cheng, Y. Yao, and W.-H. Ki, "A 6.78 MHz Single-Stage Wireless Power Transmitter Using a 3-Mode Zero-Voltage Switching Class-D PA," *IEEE Trans. Circuits Syst. Regul. Pap.*, pp. 1–13, 2021.

[4] C. Yeh et al., "A 70W and 90% GaN-Based Class-E Wireless-Power-Transfer System with Automatic-Matching-Point-Search Control for Zero-Voltage Switching and Zero-Voltage-Derivative Switching," in *IEEE International Solid - State Circuits Conference* (ISSCC), Feb. 2018, pp. 138–140.

[5] C.-Y. Xie et al., "15.3 A 100W and 91% GaN-Based Class-E Wireless-Power-Transfer Transmitter with Differential-Impedance-Matching Control for Charging Multiple Devices," in *IEEE International Solid- State Circuits Conference (ISSCC)*, Feb. 2019, pp. 242–244.

[6] M. Kaufmann and B. Wicht, "A Monolithic GaN-IC With Integrated Control Loop for 400-V Offline Buck Operation Achieving 95.6% Peak Efficiency," in *IEEE* Journal of Solid-State Circuits, vol. 55, no. 12, pp. 3169-3178, Dec. 2020.

Figure 14.6.1: Traditional two-stage Class-E PA structure, and the proposed one-step regulated Class-E PA structure and its working principle.

driver; and the measured GaN FET gate signal under 15W output power.

Figure 14.6.5: Measured waveforms of PA with passive diode rectifier and PA with Class-E rectifier; and measured V<sub>sw</sub> waveform under 0.9A input current.

Figure 14.6.2: Block diagram and the diagram of D2D working mode.

Figure 14.6.6: Comparison with the state-of-the-art; measured D2D efficiency and DC output power under different output voltages and coil distances.

Figure 14.6.7: Chip micrograph (left), circuit thermal performance (right).