# UCLA

UCLA Electronic Theses and Dissertations

Title

A 300-GHz 52-mW CMOS Receiver with On-Chip LO Generation

Permalink https://escholarship.org/uc/item/29d423cp

Author

Memioglu, Onur

Publication Date

2021

$Peer\ reviewed | Thesis/dissertation$

### UNIVERSITY OF CALIFORNIA

Los Angeles

A 300-GHz 52-mW CMOS Receiver with On-Chip LO Generation

A dissertation submitted in partial satisfaction of the requirements for the degree Doctor of Philosophy in Electrical and Computer Engineering

by

Onur Memioglu

2021

© Copyright by Onur Memioglu 2021

### ABSTRACT OF THE DISSERTATION

# A 300-GHz 52-mW CMOS Receiver with On-Chip LO Generation

by

Onur Memioglu Doctor of Philosophy in Electrical and Computer Engineering University of California, Los Angeles, 2021 Professor Behzad Razavi, Chair

A 300-GHz heterodyne receiver downconverts the input to an IF of 27 GHz and performs quadrature separation, thereby avoiding the need for power-hungry couplers and phase splitters. The LO generation consists of a 270-GHz fundamental-mode subsampling PLL with offset mixing driven by a 108-GHz PLL and a 54-GHz PLL. Fabricated in 28-nm CMOS technology, the receiver provides a voltage gain of 18 dB with a noise figure of 20 dB with I/Q gain mismatch of 1.2 dB and phase mismatch of 5.4 degrees. The dissertation of Onur Memioglu is approved.

Gregory J. Pottie

Aydin Babakhani

Yuanxun Wang

Behzad Razavi, Committee Chair

University of California, Los Angeles

2021

To my family

## TABLE OF CONTENTS

| 1 | Intro | oductio  | n                                    | 1  |

|---|-------|----------|--------------------------------------|----|

| 2 | Ove   | rall PLI | L Architecture                       | 4  |

| 3 | Prop  | posed Sy | ystem Design                         | 10 |

|   | 3.1   | 300-G    | Hz PLL Design                        | 11 |

|   |       | 3.1.1    | Subsampling Phase Detector           | 13 |

|   |       | 3.1.2    | 300-GHz VCO Design                   | 14 |

|   |       | 3.1.3    | Offset Mixer Design                  | 18 |

|   |       | 3.1.4    | Gain Stage                           | 19 |

|   | 3.2   | Phase    | Noise Analysis for 300-GHz PLL       | 20 |

|   | 3.3   | 120-G    | Hz PLL Design                        | 23 |

|   | 3.4   | 60-GH    | z PLL Design                         | 25 |

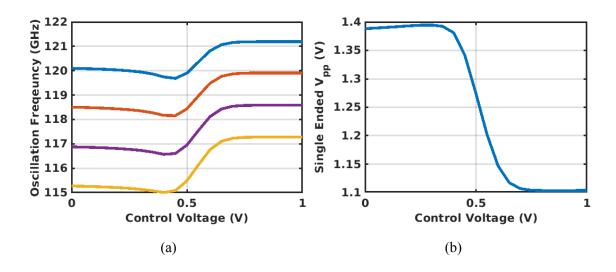

|   |       | 3.4.1    | 60-GHz VCO Design                    | 26 |

|   |       | 3.4.2    | Divide-by-8 Circuit                  | 27 |

|   |       | 3.4.3    | Divide-by-15 Circuit                 | 32 |

|   |       | 3.4.4    | Master Slave Sampling Phase Detector | 34 |

|   | 3.5   | Loop F   | Performance for 60 GHz PLL           | 37 |

| 4 | Layo  | out and  | Floorplanning                        | 40 |

| 5 | Circ  | uit Sim  | ulations and Results                 | 49 |

|   | 5.1   | On-Ch    | ip Downconversion Mixer              | 50 |

|    | 5.2   | Measurement Setups and Results               | 56 |

|----|-------|----------------------------------------------|----|

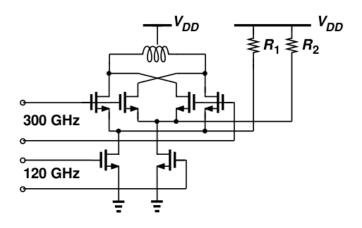

| 6  | Over  | rall Receiver Architecture                   | 64 |

|    | 6.1   | RF Mixer Design                              | 67 |

|    | 6.2   | IF Amplifier                                 | 74 |

|    | 6.3   | Quadrature Clock Generation                  | 77 |

|    | 6.4   | IF Mixer                                     | 79 |

|    | 6.5   | Baseband Amplifier                           | 80 |

|    | 6.6   | Measurement Setup and Results                | 82 |

| 7  | Com   | parison with state-of-the-art and Conclusion | 89 |

| Re | feren | ces                                          | 91 |

### LIST OF FIGURES

| 2.1  | A 300-GHz LO generator with 100-GHz VCO at the PLL (a), A 320-GHz LO generator              |    |

|------|---------------------------------------------------------------------------------------------|----|

|      | with integrated x16 frequency multiplier (b)                                                | 4  |

| 2.2  | A standard PLL design with 300 GHz VCO, a phase detector, charge pump, loop fil-            |    |

|      | ter and a divide-by-600 circuit (a), Subsampling PLL with 500 MHz reference (b),            |    |

|      | Subsampling PLL with 10 GHz reference (c)                                                   | 5  |

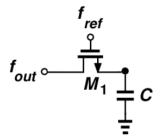

| 2.3  | Subsampling phase detector with an NMOS and a capacitor (a) an ideal sampler with           |    |

|      | square wave reference waveform (b), sampling transistor with square-wave reference          |    |

|      | (c), sampling with finite rise-fall time signal (d)                                         | 7  |

| 2.4  | 300-GHz PLL employing a mixer to reduce frequency input to SSPD and uses a 60-              |    |

|      | GHz reference                                                                               | 8  |

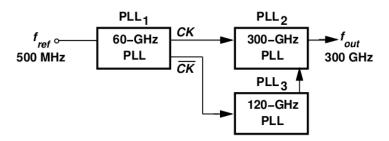

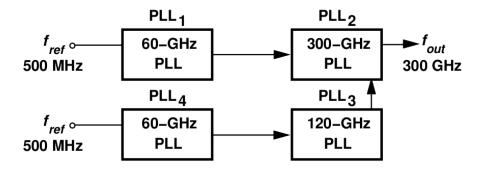

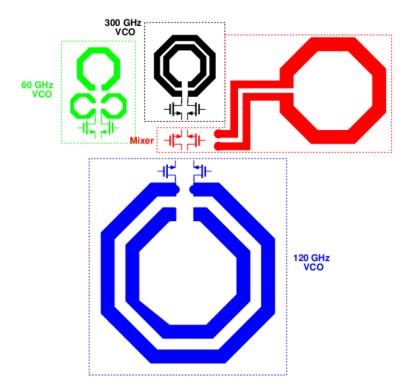

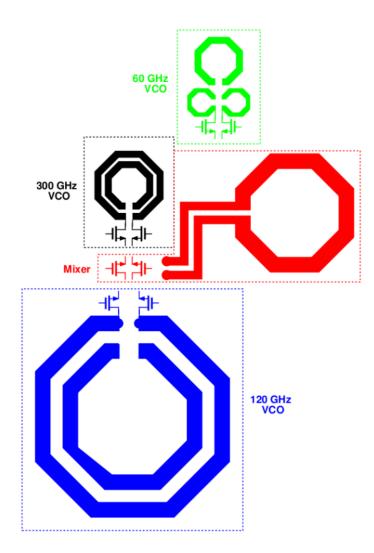

| 3.1  | Proposed system architecture including a PLL at 60 GHz, 120 GHz and 300 GHz $\ldots$        | 10 |

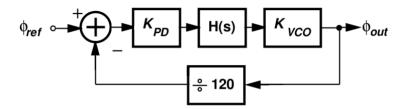

| 3.2  | Proposed 300-GHz PLL architecture                                                           | 12 |

| 3.3  | Small signal phase equivalent of 300-GHz PLL                                                | 12 |

| 3.4  | Approximate x5 subsampling phase model for 300-GHz PLL                                      | 13 |

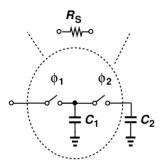

| 3.5  | Subsampling stage in 300-GHz PLL                                                            | 14 |

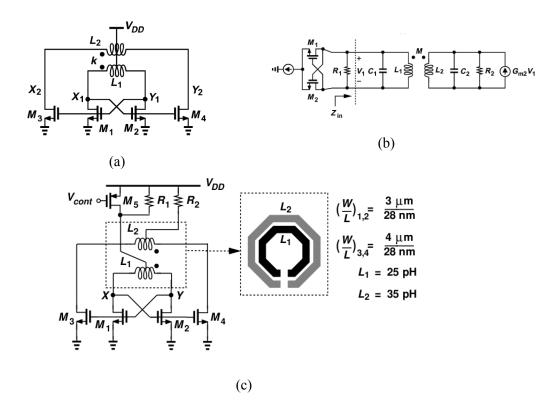

| 3.6  | Buffer feedback oscillator (a), simplified small-signal analysis (b), BFO converted into    |    |

|      | a VCO with the help of $M_5$ and physical implementation of transformer (c) $\ldots \ldots$ | 16 |

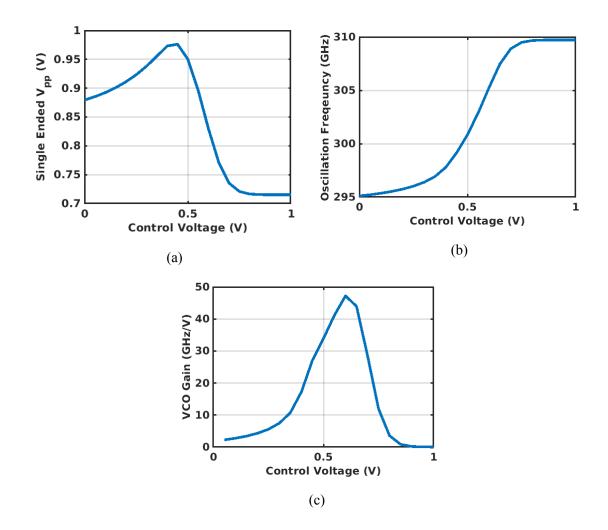

| 3.7  | Single ended peak to peak swing with respect to control voltage (a), VCO frequency          |    |

|      | with respect to control voltage (b), VCO gain with respect to control voltage (c) $\ldots$  | 17 |

| 3.8  | 300-GHz offset mixer                                                                        | 18 |

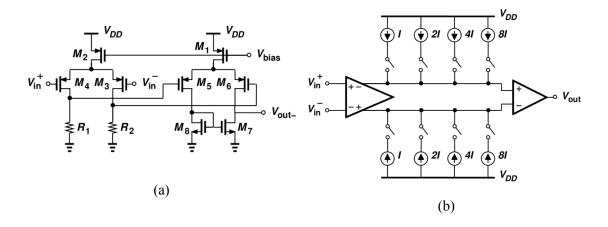

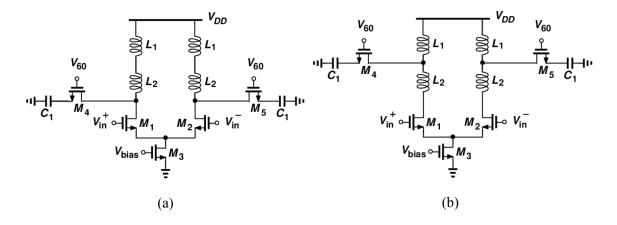

| 3.9  | Gain stage design (a), programmable currents added to control output DC level (b)           | 20 |

| 3.10 | Small signal model for phase noise analysis                                                 | 21 |

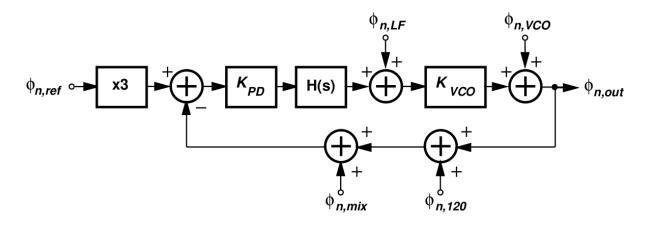

| 3.11 | A system proposition for uncorrelating phase noise                                       | 22 |

|------|------------------------------------------------------------------------------------------|----|

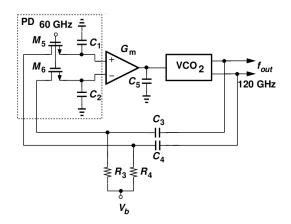

| 3.12 | 120-GHz PLL                                                                              | 23 |

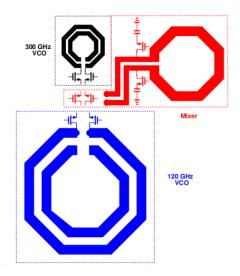

| 3.13 | 120-GHz VCO schematic                                                                    | 24 |

| 3.14 | Modulation of 120-GHz VCO with 60-GHz VCO                                                | 25 |

| 3.15 | 120 GHz VCO oscillation frequency with respect to control voltage and capacitor banks    |    |

|      | (a), single ended peak-to-peak swing (b)                                                 | 25 |

| 3.16 | 60GHz PLL schematic                                                                      | 26 |

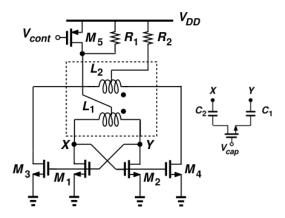

| 3.17 | 60 GHz VCO schematic                                                                     | 27 |

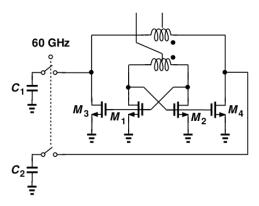

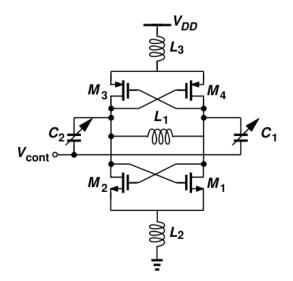

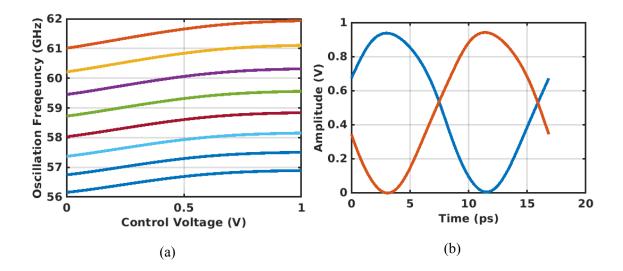

| 3.18 | 60 GHz VCO oscillation frequency with respect to control voltage and capacitor banks     |    |

|      | (a), output swings in time domain (b)                                                    | 28 |

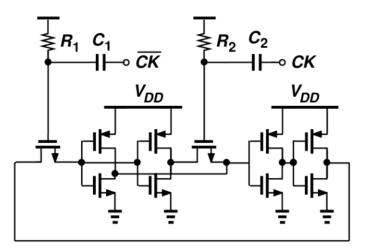

| 3.19 | Simple divide-by-2                                                                       | 29 |

| 3.20 | D-flip-flop divide-by-2 circuit                                                          | 29 |

| 3.21 | Modified divide-by-2 circuit for 60 GHz input                                            | 30 |

| 3.22 | 60-GHz divider with a strong feedforward path                                            | 30 |

| 3.23 | 60-GHz divide-by-8 outputs at each step                                                  | 31 |

| 3.24 | Maximum divider frequency at SS corner (a), minimum divider frequency at FF corner       |    |

|      | (a(b)                                                                                    | 32 |

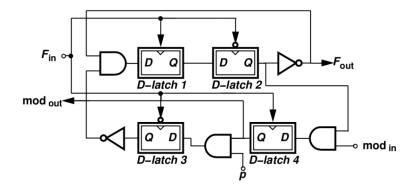

| 3.25 | Modular programmable divider architecture                                                | 33 |

| 3.26 | 2/3 divider cell logic diagram                                                           | 33 |

| 3.27 | 2/3 divider cell circuit diagram implemented with TSPC logic                             | 34 |

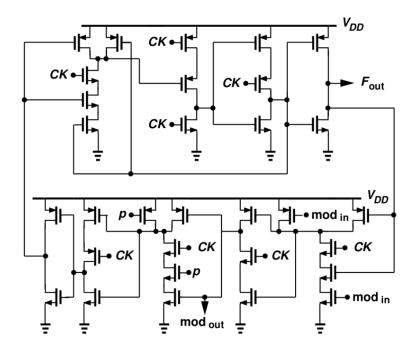

| 3.28 | Simulation result for the divide-by-15 circuit with all 2/3 divider cell and mod outputs | 35 |

| 3.29 |                                                                                          |    |

|      | (a(b)                                                                                    | 36 |

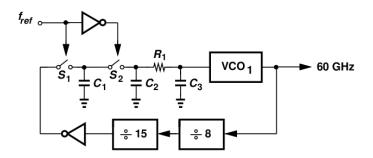

| 3.30 | 60 GHz PLL system diagram                                                                | 37 |

| 3.31 | Equivalent circuit for an MSSPD                                                          | 38 |

|------|------------------------------------------------------------------------------------------|----|

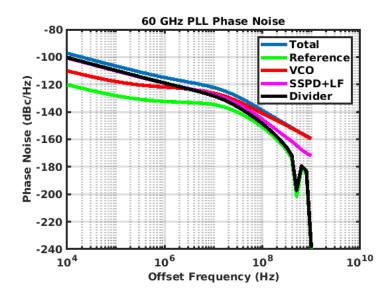

| 3.32 | 60 GHz PLL noise contributors                                                            | 39 |

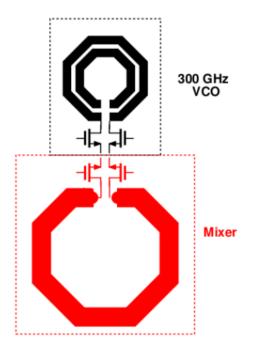

| 4.1  | An idealized placement for VCO inductor and mixer inductor in 300 GHz PLL loop . $\ .$   | 41 |

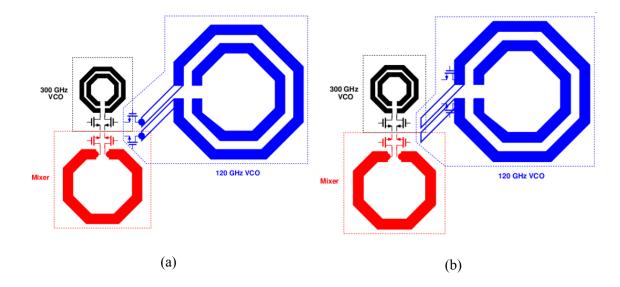

| 4.2  | 120 GHz VCO inductor on the right side of 300 GHz VCO inductor and mixer induc-          |    |

|      | tor. 120 GHz VCO transistors are close to the other transistors (a), 120 GHz VCO         |    |

|      | transistors are at the VCO inductor (b)                                                  | 42 |

| 4.3  | Layout placement for VCO inductors and transistors                                       | 43 |

| 4.4  | Layout placement for inductors and transistors                                           | 44 |

| 4.5  | Different placements for the sub-sampler, right at the transistors (a), after travelling |    |

|      | through some path (b)                                                                    | 45 |

| 4.6  | Layout placement for VCO inductors in 60 GHz VCO                                         | 46 |

| 4.7  | Layout placement for 60 GHz VCO inductors in the whole floorplan                         | 47 |

| 4.8  | Final layout placement for 60 GHz VCO inductors in the whole floorplan                   | 48 |

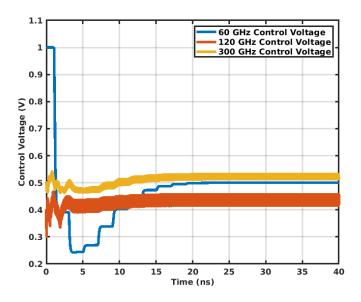

| 5.1  | Control Voltages for different PLL's when locking                                        | 49 |

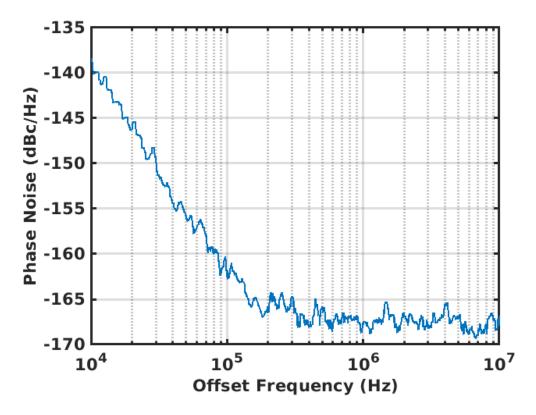

| 5.2  | 60-GHz PLL's output phase noise and its noise contributors                               | 50 |

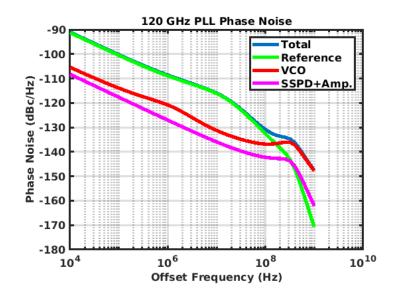

| 5.3  | 120-GHz PLL's output phase noise and its noise contributors                              | 51 |

| 5.4  | 300-GHz PLL's output phase noise and its noise contributors                              | 51 |

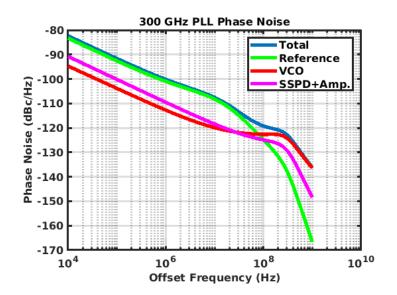

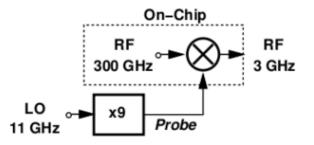

| 5.5  | Fundamental mixer with 297-GHz LO input to generate 3 GHz IF output (a), harmonic        |    |

|      | mixer which uses 27th harmonic with 11-GHz LO input to generate 3 GHz IF output          |    |

|      | (b), harmonic mixer which uses 3rd harmonic and x9 frequency multiplier to move          |    |

|      | input frequency from 11 GHz to 99 GHz to generate 3 GHz IF (c)                           | 52 |

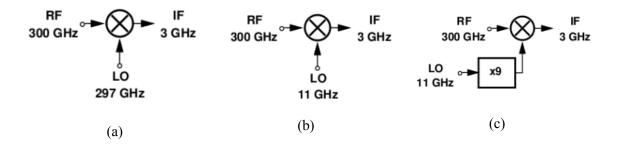

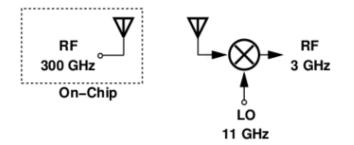

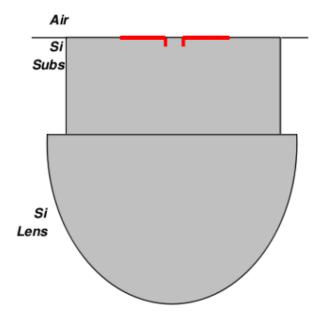

| 5.6  | Measurement setup with an on-chip antenna                                                | 53 |

| 5.7  | On-chip antenna with silicon lens to enhance gain                                        | 54 |

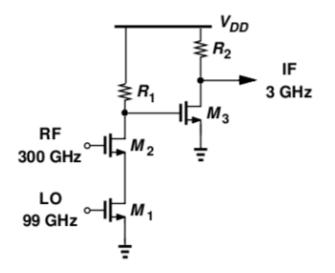

| 5.8  | On-Chip harmonic mixer and external frequency multiplier for the test setup                | 55 |

|------|--------------------------------------------------------------------------------------------|----|

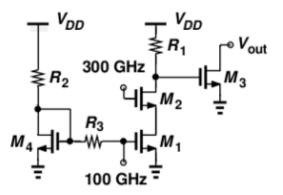

| 5.9  | Harmonic mixer and output buffer                                                           | 55 |

| 5.10 | Harmonic mixer and output buffer and the current mirror                                    | 56 |

| 5.11 | Downconverted output at 3 GHz with -55 dBm output power                                    | 57 |

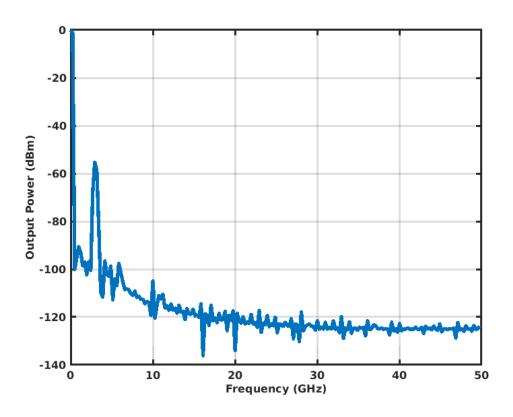

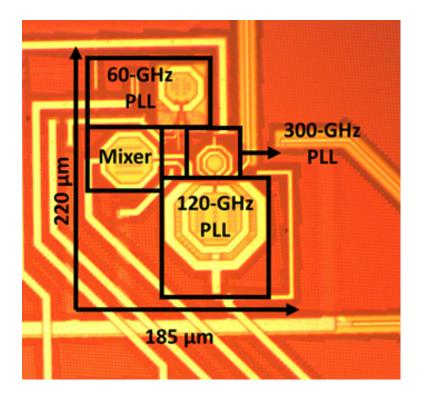

| 5.12 | 300 GHz PLL chip micrograph. The active area is 180 $\mu m$ x 220 $\mu m$                  | 58 |

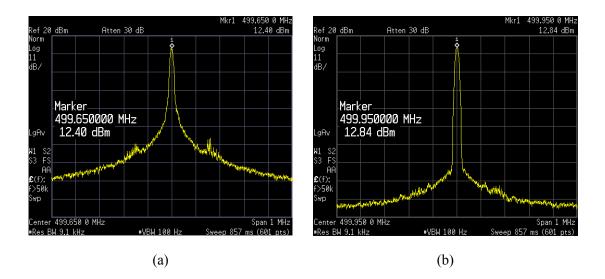

| 5.13 | 500-MHz divider output measurement setup                                                   | 58 |

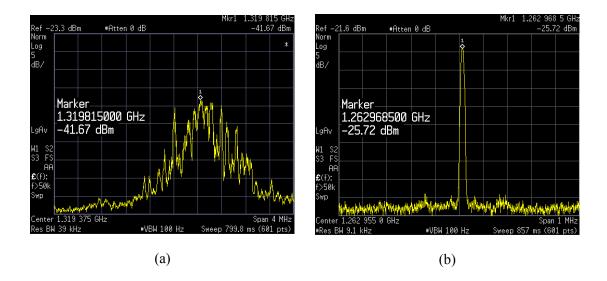

| 5.14 | Spectrum of unlocked (a) and locked (b) 500-MHz divider outputs (b)                        | 59 |

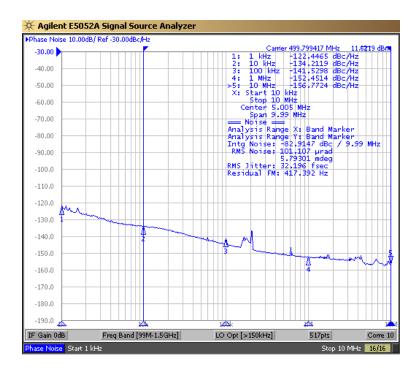

| 5.15 | 500 MHz locked signal phase noise                                                          | 59 |

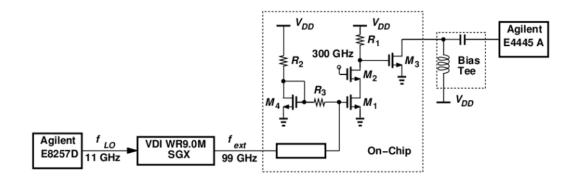

| 5.16 | 300 GHz PLL output measurement setup for spectrum analysis                                 | 60 |

| 5.17 | Spectrum of unlocked (a) and locked (b) 300-GHz PLL outputs (b) For both cases $f_{ext}$ = |    |

|      | 99.54 GHz                                                                                  | 61 |

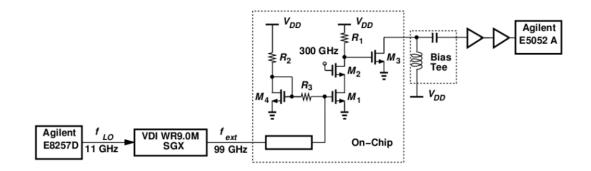

| 5.18 | 300 GHz PLL output measurement setup for phase noise analysis                              | 61 |

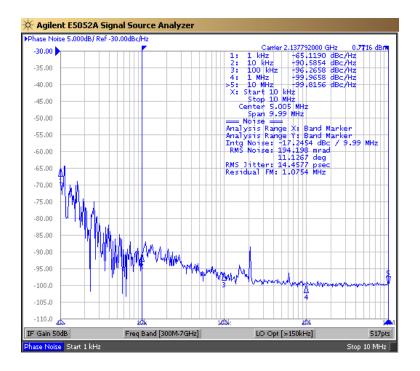

| 5.19 | 300 GHz PLL downconverted phase noise. $f_{ext}$ = 99.288 GHz                              | 62 |

| 5.20 | Phase noise of the crystal oscillator                                                      | 63 |

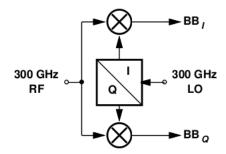

| 6.1  | Homodyne receiver with IQ seperated clocks                                                 | 64 |

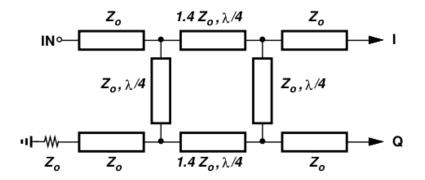

| 6.2  | Quadrature coupler with quarter wavelength transmission lines                              | 64 |

| 6.3  | Homodyne receiver with IQ seperated input                                                  | 65 |

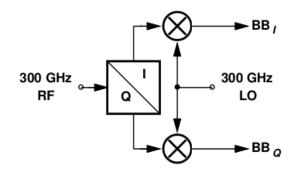

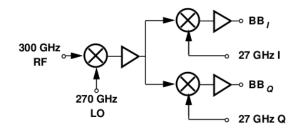

| 6.4  | Heterodyne quadrature receiver                                                             | 66 |

| 6.5  | Clock generator for the heterodyne receiver                                                | 67 |

| 6.6  | RF mixer simplified (a), approximate structure to model gain (b)                           | 67 |

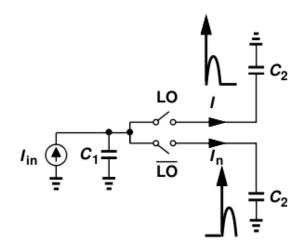

| 6.7  | Mixer current waveforms going into the load capacitors                                     | 68 |

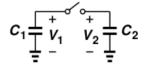

| 6.8  | Charge sharing between transistors                                                         | 69 |

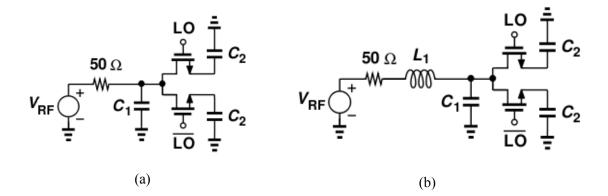

| 6.9  | Mixer directly connected to 50 $\Omega$ input (a), mixer connected to input with a resonating |    |

|------|-----------------------------------------------------------------------------------------------|----|

|      | inductor (b)                                                                                  | 72 |

| 6.10 | RF mixer schematic with component values                                                      | 74 |

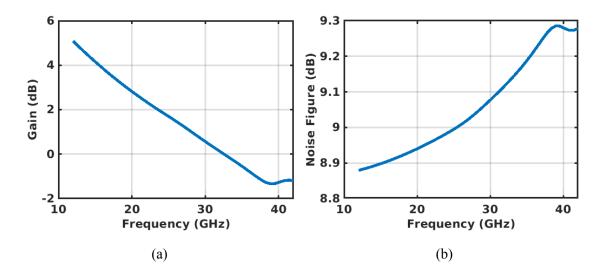

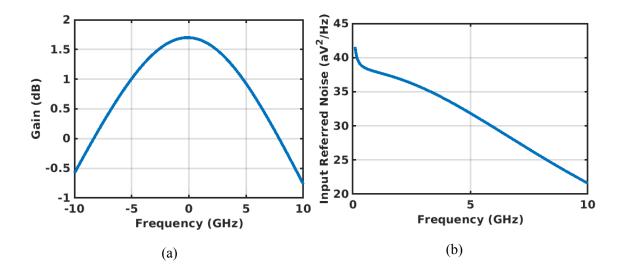

| 6.11 | RF mixer gain(a) and noise figure for downconverted signal (b)                                | 74 |

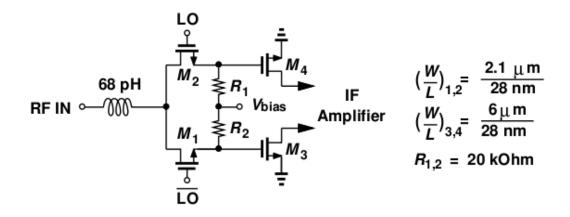

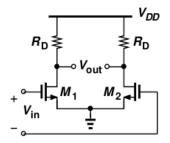

| 6.12 | Basic differential as IF amplifier                                                            | 75 |

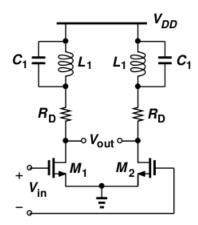

| 6.13 | IF amplifier with shunt peaking                                                               | 76 |

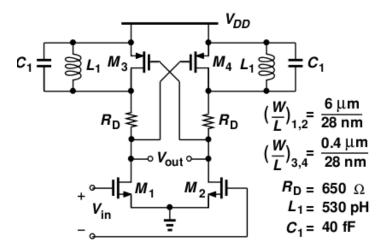

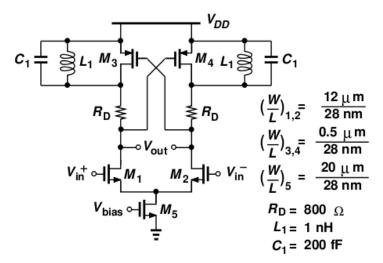

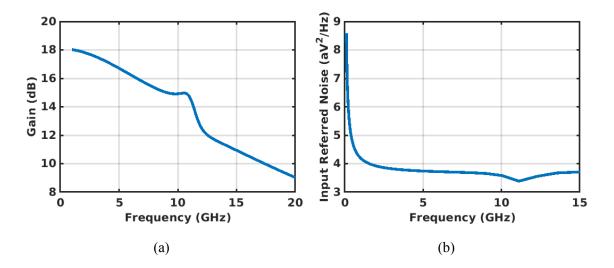

| 6.14 | IF amplifier with shunt peaking and PMOS cross-coupled pair                                   | 77 |

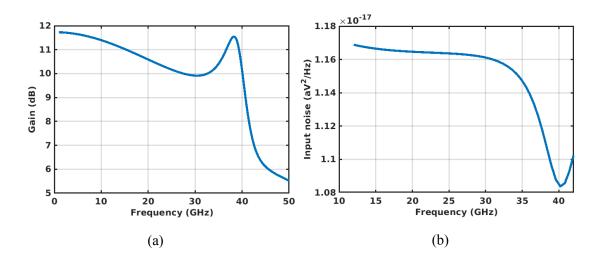

| 6.15 | IF amplifier gain(a) and input referred noise (b)                                             | 77 |

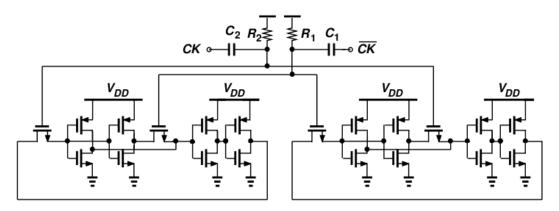

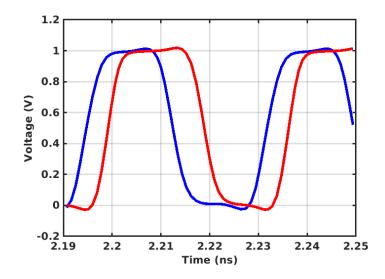

| 6.16 | Complete divider schematic for quadrature separation                                          | 78 |

| 6.17 | Transient waveforms for quadrature divider                                                    | 78 |

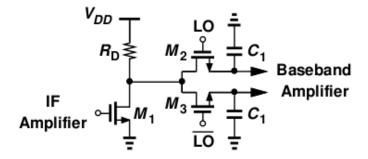

| 6.18 | IF mixer schematic                                                                            | 79 |

| 6.19 | IF mixer gain(a) and output noise (b)                                                         | 80 |

| 6.20 | Baseband amplifier schematic                                                                  | 81 |

| 6.21 | Baseband amplifier gain(a) and input referred noise (b)                                       | 81 |

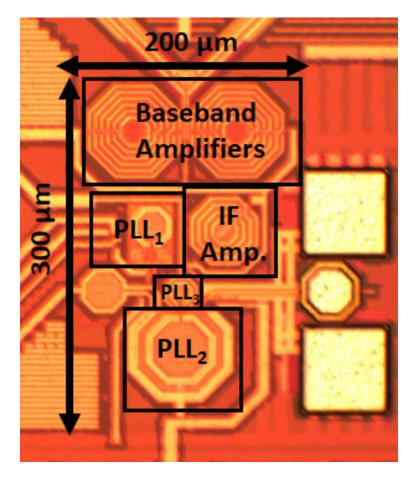

| 6.22 | Chip photo for 300-GHz receiver                                                               | 82 |

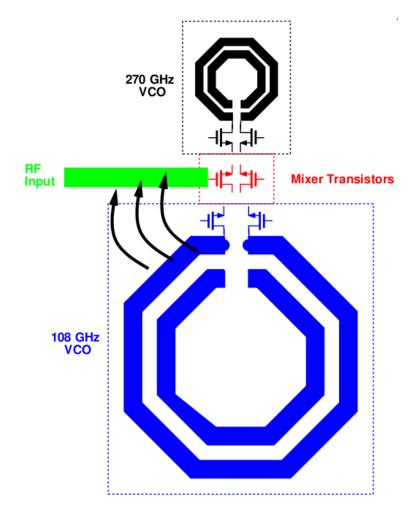

| 6.23 | Coupling path for 108-VCO                                                                     | 83 |

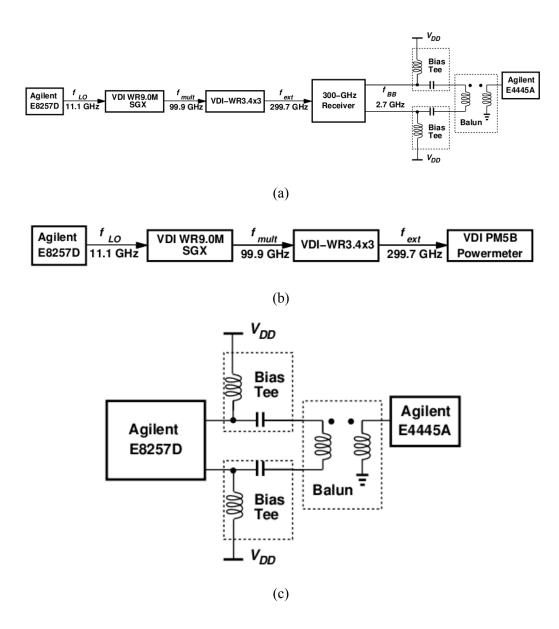

| 6.24 | Measurement setups for gain measurement (a) and input power measurement (b) and               |    |

|      | loss calibration (c)                                                                          | 85 |

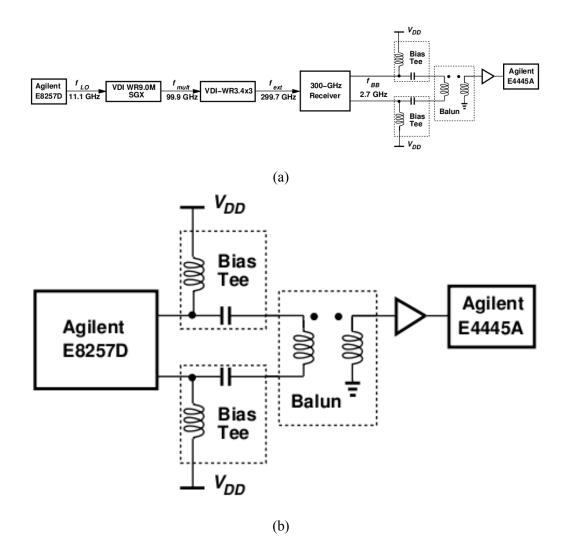

| 6.25 | Measurement setups for noise figure measurement, gain measurement (a) and loss cal-           |    |

|      | ibration (b)                                                                                  | 87 |

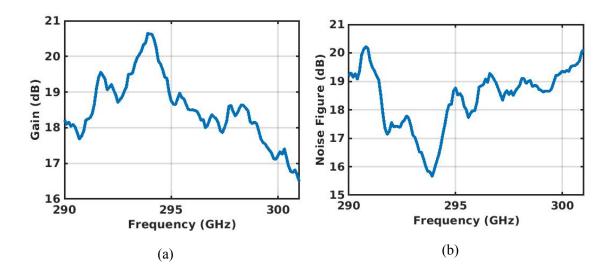

| 6.26 | Gain (a) and noise figure (b) measurement results                                             | 88 |

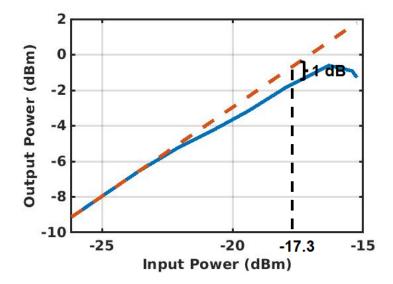

| 6.27 | $P_{1dB}$ measurement at 1 GHz                                                                | 88 |

## LIST OF TABLES

| 5.1 | Comparison for state-of-the-art PLL's at 300 GHz         | 63 |

|-----|----------------------------------------------------------|----|

| 7.1 | Comparison with other state-of-the-art 300-GHz receivers | 89 |

### ACKNOWLEDGMENTS

I am using this opportunity to express my gratitude to everyone who supported me throughout the course of this thesis. Firstly, I would like to thank Prof. Behzad Razavi for his invaluable support and guidance. I am fortunate to have an advisor like him who gave me the freedom to explore my own approach and supportive throughout all the phases of thesis accomplishment from ideas to chip design and measurements.

I would also like to thank all of the members CCL group members for their friendship and supports namely, Atharav, Mehrdad, Hossein, Matias and Yu whose friendship and support always were the greatest motivation throughout my work.

I would like to thank Adnan Gündel for his life-long support and advices both in this Ph.D. work and other topics.

Lastly, I would like to express my heart-felt gratitude to my family whose love, support and encouragement always helped me to find the right path. None of these would have been possible without love and patience of my family.

# VITA

| 2011-2015 | B.Sc. in Electrical and Electronics Engineering, Middle East Technical Univer-                    |

|-----------|---------------------------------------------------------------------------------------------------|

|           | sity, Ankara, Turkey                                                                              |

| 2015-2018 | M.Sc. in Electrical and Electronics Engineering, Middle East Technical University, Ankara, Turkey |

| 2019      | Ph.D. Candidate in Electrical and Computer Engineering, University of Califor-                    |

|           | nia, Los Angeles                                                                                  |

# **CHAPTER 1**

## Introduction

Development of integrated millimeter-wave (mm-Wave) and THz systems in the recent years have found many applications in various areas like wireless communication at 60-GHz, automotive radars at 77-GHz [1–3], THz high speed communication links [4–8], gas spectroscopy [9–13] and biomedical imaging [14–21]. Ongoing demand for higher data rates greater than 20 Gb/s requires highly stable low phase noise local oscillators to improve bit error rate (BER) of these communication systems. These phase locked oscillators were previously developed with BiCMOS [22–24] or III-V semiconductor technologies like InP [25–27]. With the continuous scaling of CMOS technology, CMOS transistors can reach a unit gain frequency ( $f_t$ ) of 350 GHz and more. Therefore, it is more attractive to build a compact system in the CMOS technology with reduced area, cost and power consumption. However, near ft operation, low quality factor value for inductors creates a very low phase noise performance for the VCO's around sub-THz frequency which requires the use of very high PLL bandwidth to reduce the VCO phase noise.

Data communication in the 300-GHz band has also found renewed interest in the past few years. Rising demands for high data rate wireless communication, still pushes the boundaries for the available frequencies. The idea of getting a high bandwidth communication and the unallocated frequency band from 252 GHz to 322 GHz makes a suitable candidate for next generation communications. The IEEE 802.15.3d standard, which was established in 2017 for radios in the 300 GHz frequency band, is currently trying to determine feasible standards for high bandwidth communication in 300 GHz [28]. In addition to the IEEE task force, a number of researchers have demonstrated the viability of such radios in a range of semiconductor technologies like SiGe BiC-

### MOS, InP HEMT and with CMOS [4-8, 26, 29-36].

For 300-GHz transceivers to serve as an attractive complement to WiFi and WiGig, they should perform extensive beam forming so as to overcome the path loss. This point underscores the importance of low power consumption per element. Moreover, high order modulation schemes require a local oscillator (LO) signal with very low phase noise. Unfortunately, the generation and distribution of LO phases proves extremely power hungry.

A receiver architecture in these frequencies started with simple modulations like OOK/ASK modulations. These modulations allows much simpler designs for both transmitters and receivers [37–39]. First of all, these types of receivers do not require a locked local oscillator for up/down-conversion. With the limited speed of the transistors, these type of transmitters/receivers are the most common ones. Unfortunately, these systems do not offer much advantage in terms of data bandwidth. The inefficient modulation schemes lead to lower data rates and high bit error rates.

With further advances in the semiconductor technologies and  $f_{max}$  values reaching frequencies of 500 GHz and more, the quadrature transmitters and receivers became feasible for 300 GHz. These systems offer robust performance and better data rates when compared to OOK/ASK however they have some challenges in terms of design. First of all, these systems require a local oscillator that is phase locked to a reference to generate stable clocks. Without phase locked LOs, the quadrature modulations would be highly inefficient due to high phase noises and low frequency stability of oscillators. Traditionally, these PLLs are designed at lower frequencies and the harmonic of the VCO is extracted to be the local oscillator [23, 26, 40, 41]. This method offers better power consumption but suffers from the low power of the desired signal at the output. Another approach is to use frequency multipliers to go to the desired frequencies [30, 42–44]. By using different numbers of frequency multipliers, these types of circuits consume too much power to get a modest swing at the desired frequency. Use of injection locked multipliers can also cause the output signal to be at a different frequency than the desired signal. Therefore, additional tracking loops are needed to be used for correct operation [24]. Again, these multipliers have very low efficiency in terms of power output. In [22], a frequency stabilization technique is proposed for frequencies between 302-330 GHz. This proposed system doesn't use a reference frequency and hence cannot be reliable to be used in a transceiver chain.

Second problem is to obtain a quadrature clocks to drive mixers in the chip. Some design examples typically include a lossy on chip quadrature hybrid [4, 30, 35, 43]. These hybrids, since passive, introduce a direct 3-dB reduction in the LO power due to the nature of the hybrid. In addition, on chip lossy metals introduce additional losses since these designs must be at quarter wavelength.

The problem of LO generation at frequencies of several hundred gigahertz has generally entailed two facets: (1) it has been considered difficult to design VCOs that achieve such speeds, especially in view of the low varactor Q's, and (2) it is also difficult to develop dividers for these frequencies.

A third issue related to terahertz generation is the reference phase noise. Even a reference frequency of hundreds of MHz with a phase noise of -160 dBc/Hz places an upper bound of about -100 dBc/Hz at 300 GHz if all other noise are neglected. Indeed, typical PFDs and charge pumps also suffer from these levels of noise. To reduce these contributions, one can reduce the PLL bandwidth, but the VCO noise then dominates. Thus, a single PLL is not an attractive choice for our purpose.

In this paper, we will propose an efficient clock generation scheme with a quadrature receiver at 300-GHz for low power and high performance downconversion of the 300-GHz signal to lower bands. In the first parts of the paper, we will go into the details of the 300-GHz LO generation circuit. In the next parts we will explain the quadrature receiver in detail and combine both of these architectures to achieve a 300-GHz receiver with excellent performance and low power consumption.

# **CHAPTER 2**

# **Overall PLL Architecture**

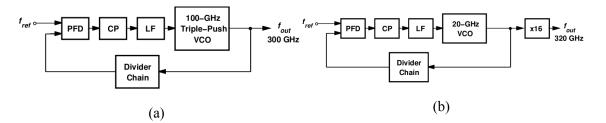

A fundamental generator at THz frequencies is still a difficult challenge although the transistors  $f_T$  reaches greater than 300-GHz. Most commonly used technique is to extract the harmonic of the VCO to reach THz frequencies. An example is to use a 100-GHz PLL and use a triple push VCO at 100 GHz to obtain 300 GHz output as shown in Fig. 2.1(a). As we are extracting the harmonic of the VCO, the output power of the extracted signal will be inherently low. Another common approach is to synthesize a low frequency and use frequency multipliers to go to THz frequencies. A sample approach is given in Fig. 2.1(b) where we have a x16 frequency multiplier which uses four x2 multipliers. This approach is also very power inefficient as the output swing of the multipliers are low. Each multiplication stage needs a driver in between to fully drive the preceding stage to achieve maximum output power.

Figure 2.1: A 300-GHz LO generator with 100-GHz VCO at the PLL (a), A 320-GHz LO generator with integrated x16 frequency multiplier (b)

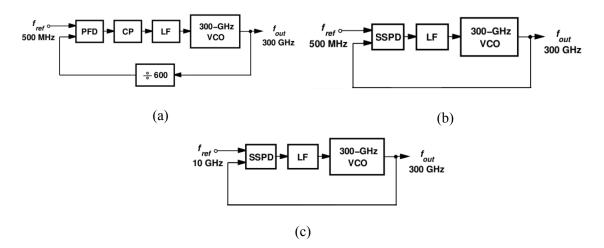

As seen from the Fig. 2.1, all the generators use a PLL loop at a much lower frequency than the output frequency. We would like to retain the amplitude and power benefits of a fundamental oscillator as they would yield higher output swings and consume less power when compared to the frequency multiplication techniques. Let's set up the PLL circuit in Fig. 2.2(a) with a fundamental oscillator at 300-GHz. Assuming that we have a VCO at this frequency and a reference frequency of 500-MHz, we would need a divide-by-600 circuit.

Figure 2.2: A standard PLL design with 300 GHz VCO, a phase detector, charge pump, loop filter and a divide-by-600 circuit (a), Subsampling PLL with 500 MHz reference (b), Subsampling PLL with 10 GHz reference (c)

Most critical part in this design is the first divider in the chain. Only an injection locked frequency divider would be able to divide this input as conventional dividers would lack the necessary speed to overcome such high frequencies. For an ILFD, we must make sure that the output swing at the VCO is able to lock to the divider. Eq. 2.1 describes the injection locking range of the divider. In order to maximize the injection locking range, the injection current must be maximized which means that we need to push a large current from 300-GHz VCO to create a viable locking range.

$$\omega_L = \frac{\omega_0}{2Q} \cdot \frac{I_{inj}}{I_{osc}} \tag{2.1}$$

A VCO at 300 GHz may not sufficiently carry a large current due to limited transistor sizes. Moreover, pulling too much current out of the oscillator can reduce the Q factor of the tank eventually damping the oscillation. Even though if we manage to divide 300-GHz into some reasonable frequency like 100-GHz we may still need to employ another ILFD to go into the ranges for standard divider circuits like D-flipflop dividers. Additionally, these ILFDs need to tuned by external means as in [24] to check whether the ILFD locked to the correct frequency. Otherwise, the PLL wouldn't lock.

Another option is to remove the divider chain completely from the loop and use a subsampling phase detector to directly sample the VCO signal at the input with 500-MHz reference signal as shown in Fig2.2(b). Apart from sampling problems, which will be discussed later, the lack of divider in the subsampling PLL may lead to false lock conditions. Since the reference frequency is 500-MHz, this PLL may lock to 299.5-GHz or 300.5-GHz or any other integer multiple of 500-MHz. In order to achieve proper lock, we need to monitor the output frequency with a frequency locked loop or with a secondary coarse PLL to correct the output frequency. It would be again difficult to build a PLL with a divider to detect the correct frequency so this idea is also not feasible.

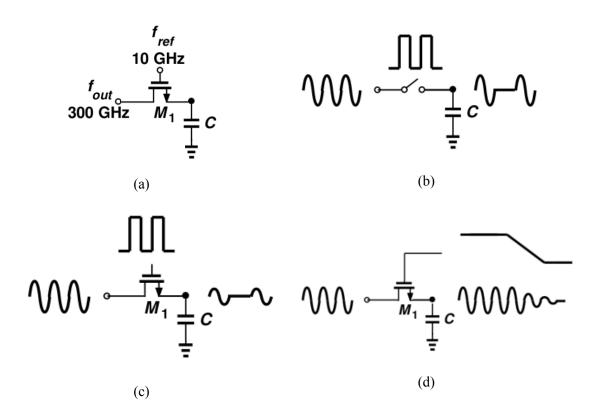

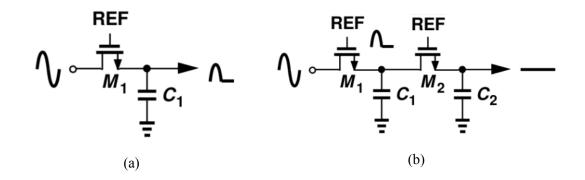

In order to lock to the correct frequency, we can use a higher reference frequency than 500-MHz as in Fig 2.2(c). Let us assume that we have a reference of 10-GHz and the VCO at 300 GHz can oscillate between 295-GHz and 305-GHz. In this case, even with subsampling, the oscillator can only lock to 300-GHz because VCO cannot oscillate at any integer multiple of 10 GHz. For the subsampling phase detector, we can use a capacitor and a single MOSFET as a switch to sample 300-GHz with 10-GHz reference as in Fig. 2.3(a).

Now with the simple sampling circuit, let's see what happens when we try to sample 300-GHz signal with 10-GHz. For the sake of simplicity let us start the analysis of SSPD with an ideal switch instead of transistor and perfect square waveform for 10-GHz as in Fig. 2.3(b). When the switch turns on, 300-GHz signal will be on the capacitor and when the switch turns off, the capacitor will maintain its charge and hence the current phase information. With ideal switch and sampling waveform, we can extract phase information from the 300-GHz signal without any loss.

For the next part of analysis, we keep the waveform same but change the ideal switch to a MOSFET as in Fig. 2.3(c). A transistor has finite on and off resistance when compared to an ideal switch. When the transistor turns on, we will be forming an RC low pass filter at the SSPD. Since

Figure 2.3: Subsampling phase detector with an NMOS and a capacitor (a) an ideal sampler with square wave reference waveform (b), sampling transistor with square-wave reference (c), sampling with finite rise-fall time signal (d)

we have  $f_{ref} \ll f_{VCO}$ , input will reach steady state until switch turns off. As a result, we can say that 300-GHz sees an RC low pass filter at the input. In this case, we will lose some of the signal amplitude during sampling due to filtering effect formed by the RC circuit. The effective phase detector gain, when compared with the previous case will be reduced by the factor in Eq. 2.2.

$$V_{out} = \frac{1}{\sqrt{1 + \omega^2 R_{om}^2 C^2}}$$

(2.2)

The bandwidth of the sampler needs to be adjusted to accommodate higher input frequencies so that  $K_{PD}$  remains intact. One can increase the size of the switch transistors to reduce the on resistance but this will also increase the load capacitance on the 300-GHz VCO due to the transistor parasitics.

What would happen if the reference signal is not a perfect square wave but has some rise and fall time? Now we know that during on time, the signal will experience filtering effect and during off time, the phase information will be preserved. Now if the on resistance increases slowly due to finite fall time, the filter's bandwidth will start to reduce slowly. Fig. 2.3(d) shows the output signal during a transition period. Slow decrease in bandwidth would result in the reduction of the amplitude of sampled signal, in this case phase information. When the rise/fall time becomes comparable with the period of the sampled signal, SSPD gain reduces drastically, leading to lock failure in an actual PLL.

As a result, in order for the SSPD to operate correctly, we need very short rise and fall times. In other words, we need a high frequency reference signal so that we would maintain a substantially high phase detector gain and the loop operates correctly. By simulations, we can show that for a 60-GHz sinusoidal reference signal, we can show that for 300-GHz input, we have a gain 1.2-mV/rad, for 180-GHz input, we have a gain of 32-mV/rad.

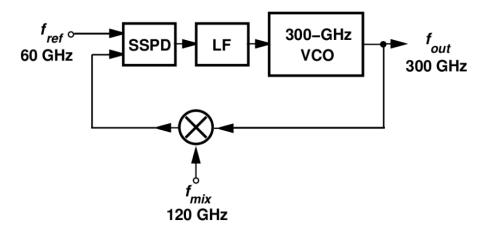

Figure 2.4: 300-GHz PLL employing a mixer to reduce frequency input to SSPD and uses a 60-GHz reference

We can improve the gain of the phase detector by reducing the frequency coming from the VCO. As discussed earlier, a frequency divider wouldn't be easy to design at 300 GHz due to the very high frequency. Fig. 2.4 shows a simple structure which can solve our needs and achieve phase locking for 300 GHz input. Rather than using a divider, we employ a mixer at the feedback

path with 120 GHz LO signal. By this way 300 GHz signal is reduced to 180 GHz which has sufficiently higher phase detector gain.

# **CHAPTER 3**

## **Proposed System Design**

Fig. 2.4 shows that we need to have two signals, one at 60-GHz and the other at 120-GHz to drive such a PLL. As we need a very low phase noise reference for 300 GHz generation, we must generate 60 GHz signal from a crystal reference at a much lower frequency, and we can have another PLL that can generate 120-GHz from the existing 60 GHz.

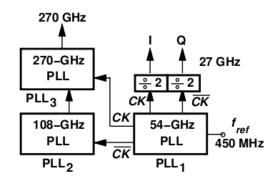

Fig. 3.1 shows the proposed LO generator architecture. It consists of a 60-GHz PLL, a 120-GHz PLL, and a 300-GHz PLL that receives the former PLLs' outputs. A 60-GHz PLL (PLL<sub>1</sub>) is used to generate a 60-GHz output by using a 500-MHz crystal oscillator reference. This output is shared by the 300-GHz PLL (PLL<sub>3</sub>)and 120-GHz PLL (PLL<sub>2</sub>). PLL<sub>2</sub> generates 120-GHz output which is used by the offset mixer in the PLL<sub>3</sub> to downconvert 300-GHz output to 180-GHz. From 180-GHz, PLL<sub>3</sub> locks to 60 GHz reference and generates an output of 300-GHz.

Figure 3.1: Proposed system architecture including a PLL at 60 GHz, 120 GHz and 300 GHz

The architecture of Fig. 3.1 merits five remarks. First, to lower the reference phase noise contribution, we select a relatively narrow bandwidth, about 50-MHz, for PLL<sub>1</sub>, but design the 60-GHz VCO for very low phase noise, about -117 dBc/Hz at 1 MHz offset. On the other hand, we choose wide bandwidths for PLL<sub>2</sub> and PLL<sub>3</sub>, 400 MHz and 700 MHz, respectively, so as to attenuate the

phase noise of their VCOs.

Second, to minimize power consumption and simplify the routing of signals, we avoid highfrequency inductor-hungry buffers: the output of PLL<sub>1</sub> directly drives its own feedback divider and the phase detectors (PDs) in PLL<sub>2</sub> and PLL<sub>3</sub>, the 120-GHz signal generated by PLL<sub>2</sub> is directly applied to PLL<sub>3</sub>, and the output of PLL<sub>3</sub> directly switches the input transistors of the mixer. The cost is extensive iteration between design and layout. Third, another benefit of avoiding buffers is the small area of the overall generator, about 185  $\mu$ m x 220  $\mu$ m, which proves useful if multiple beam-forming transceivers are to be integrated on the same chip. Fourth, we exploit the line inductances associated with the distribution of the waveforms to create series peaking and slightly enlarge the voltage swings. Fifth, the generator's frequency planning affords great flexibility in direct-conversion or heterodyne transceiver design and coverage of numerous bands from 60 GHz to 420 GHz.

### 3.1 300-GHz PLL Design

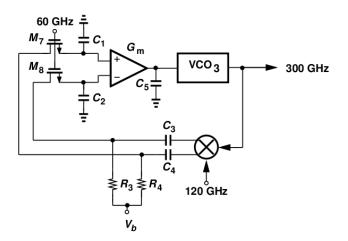

300-GHz PLL consists of a subsampling phase detector, an amplification denoted as  $G_m$ , a VCO at 300-GHz and a mixer shown in Fig. 3.2. Rather than employing a power hungry injection locked divider, we simply use a double balanced active mixer to downconvert 300-GHz output to 180-GHz, with the help of 120-GHz signal generated from an additional PLL.

One of the important question that needs to be answered is that whether this PLL locks to 300-GHz with the given configuration. Let us consider the simplified phase equivalent diagram of the 300-GHz PLL in Fig. 3.3.

A mixer in time domain can be considered as a multiplier circuit. If we multiply two cosines of different frequency and phases, we would obtain:

$$\cos(\omega_1 + \theta_1).\cos(\omega_2 + \theta_2) = \frac{\cos[(\omega_1 + \omega_2)t + (\theta_1 + \theta_2)] + \cos[(\omega_1 - \omega_2)t + (\theta_1 - \theta_2)]}{2} \quad (3.1)$$

Figure 3.2: Proposed 300-GHz PLL architecture

Figure 3.3: Small signal phase equivalent of 300-GHz PLL

In phase domain, the mixer adds phases for the upconversion, and subtracts phases for the downconversion. Since we are using the downconverted output, this mixer can be approximated as a subtractor in phase domain.

Secondly, now the frequency at the input of the SSPD is reduced to 180-GHz, we have x3 subsampling at the input, therefore the reference phase at the input is multiplied by 3. At 120-GHz input side, we assume that the input is  $2\Phi_{ref}$  because this signal is generated using another PLL from 60-GHz.

Let us start analyzing the PLL. If we write the phase error:

$$\phi_e = 3\phi_{ref} - (\phi_{out} - 2\phi_{ref}) \tag{3.2}$$

$$\phi_e = 5\phi_{ref} - \phi_{out} \tag{3.3}$$

$$\phi_{out} = K_{PD} \cdot H(s) \frac{K_{VCO}}{s} \phi_e \tag{3.4}$$

$$\phi_{out} = K_{PD} * H(s) \frac{K_{VCO}}{s} . (5\phi_{ref} - \phi_{out})$$

(3.5)

$$\frac{\phi_{out}}{\phi_{ref}} = A_{\phi}(s) = \frac{5K_{PD}H(s)\frac{K_{VCO}}{s}}{1 + K_{PD}H(s)\frac{K_{VCO}}{s}}$$

(3.6)

$$\frac{\phi_{out,open}}{\phi_{ref,open}} = T(s) = 5K_{PD}H(s)\frac{K_{VCO}}{s}$$

(3.7)

where  $A_{\Phi}(s)$  is the closed loop response and T(s) is the open loop response.

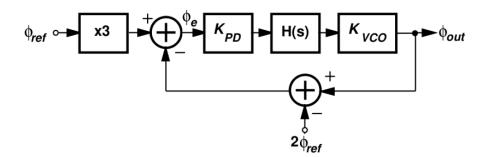

When we analyze the open loop gain, which is given in Eq. 3.7 we find an interesting resulting. Although it is a x3 subsampling stage, the overall system can be approximated as a x5 subsampling stage without mixer and 120-GHz input as in Fig. 3.4. This gives us a clear image why this is a viable structure for a PLL to lock.

Figure 3.4: Approximate x5 subsampling phase model for 300-GHz PLL

#### 3.1.1 Subsampling Phase Detector

The SSPD in 300-GHz PLL is a differential sampling stage which has 180-GHz input coming from the mixer. As discussed in the previous chapter, we need to reduce the input frequency to maximize the phase detector gain. From simulation results, direct sampling of 300 GHz signal by 60 GHz has a phase detector gain of 1.2-mV/degree whereas, direct sampling of 180-GHz signal by 60-GHz reference has a phase detector gain of 32-mV/deg.

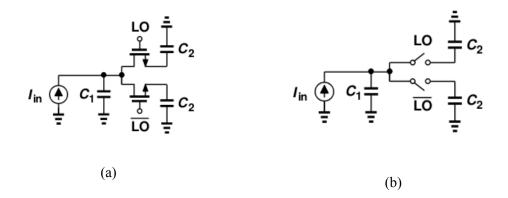

A phase detector which consists of only a single NMOS as a switch and a capacitor C as in Fig. 3.5 is chosen as a simple structure to perform phase detection. The switch size is chosen as 2  $\mu$ m and capacitor is chosen as 5 fF. These values give a bandwidth of 360 GHz including the parasitics, which is 2 times the input signal frequency.

Figure 3.5: Subsampling stage in 300-GHz PLL

Reference signal in this case is a sinusoidal signal at 60-GHz. One way to improve the phase detector gain is to improve rise and fall time of the reference. By making a square wave, we would be able to sample more effectively thus increasing our  $K_{PD}$ . Given that the signal's high frequency we would need power hungry buffers in order to decrease signal transition times by around 1 ps according to the simulations, which is not feasible to do. With reduced input frequency and 60-GHz reference frequency, we can get substantially high gain and as a result achieve phase lock.

#### 3.1.2 300-GHz VCO Design

For an oscillator at 300-GHz, typical approach is to extract harmonic from an existing oscillator. However, these approaches prove to be very power inefficient and the output doesn't have sufficient swing at the output in most of the cases. In this design we propose a fundamental oscillator that can oscillate at 300-GHz and that has a sufficient swing at its output to drive a mixer in the receive path.

As a fundamental oscillator, a simple cross-coupled oscillator can be used as a THz oscillator as long as we can have a tank with high enough Q-factor. However, this approach falls short for 2 reasons. Firstly, in order to get the oscillation frequency, we need to select very low transistor sizes to reduce parasitic capacitances and also to keep the inductance as high as possible. The output swing of a cross coupled pair is:

$$V_{out} = \frac{4}{\pi} I_b R_p \tag{3.8}$$

Choosing low inductances, will eventually reduce the output swing of the transistor because as illustrated in (3.8), the output swing heavily depends on the  $R_p$  formed by the inductor and its quality factor. Secondly, this oscillator will be susceptible to any load connected to its output, reducing oscillation frequency drastically.

As illustrated in [45], the addition of transformer and buffer to the XCO, which is referred as buffer feedback oscillator (BFO) entails some advantages over the XCO alone. The schematic is given in Fig. 3.6(a) which shows a cross coupled pair is connected to common source stages  $M_3$ and  $M_4$ . Through the coupling action, some of the power couples back into the XCO, enabling special properties.

Fig. 3.6(b) shows a simplified small signal analysis of the structure. The frequency of oscillation can be calculated using the small signal analysis. If we assume  $L_1=L_2=L$  and  $C_1=C_2=C$ , this oscillator would yield two modes of oscillation:

$$\omega_1^2 = \frac{1}{(L+M)C}$$

(3.9)

$$\omega_2^2 = \frac{1}{(L-M)C}$$

(3.10)

Equation (3.10) is obtained when the transformer currents are out of phase and yields a much higher oscillation frequency. However this mode of oscillation is not observed in this configuration. Equation (3.9) is observed when the transformer currents are in phase and can be obtained if used in the current configuration.

This structure uses 3  $\mu$ m transistors in the cross-coupled pair with 25-pH inductance in the L<sub>1</sub> to create oscillation in the BFO structure. According to simulation results, we would need a

Figure 3.6: Buffer feedback oscillator (a), simplified small-signal analysis (b), BFO converted into a VCO with the help of  $M_5$  and physical implementation of transformer (c)

transistor size around 2.2  $\mu$ m transistors to get the same oscillation frequency with only a simple cross-coupled pair.

Creating a VCO is another challenge at these frequencies. Lack of varactor models at these frequencies, we propose a tuning technique that adjusts the CM level at X and Y by  $M_5$  in Fig. 3.6(c). At lower CM levels,  $M_1$ - $M_4$  spend more time in the off region, exhibiting a smaller average gate capacitance and hence providing a greater oscillation frequency.  $R_1$  ensures oscillator startup even if  $V_{cont}$  is near  $V_{DD}$  at the beginning of operation.  $R_2$  establishes an output CM level around 0.75\* $V_{DD}$  and suited to the offset mixer. Change in VDD voltage also results in the change of the amplitude swing, where swing is maximized when  $V_{ctrl}$  is around 0.45 V whereas the VCO gain is maximized when  $V_{ctrl}$  is at 0.6 V. Fig. 3.7(a) shows how the amplitude varies with the  $V_{ctrl}$ . This oscillator consumes 2.5 mA from a 1 V source when it oscillates at 300-GHz.

Figure 3.7: Single ended peak to peak swing with respect to control voltage (a), VCO frequency with respect to control voltage (b), VCO gain with respect to control voltage (c)

This tuning approach doesn't load the oscillator directly so that we can choose the size of  $M_5$  very large without affecting oscillation frequency. However one major drawback of this approach is that the flicker noise of  $M_5$  directly modulates the oscillator leading to phase noise. Due to large bandwidth of 300-GHz PLL, this additional noise is suppressed by the PLL bandwidth. In addition, large size of PMOS transistor also effectively reduces the noise contribution coming from this transistor. This method allows the transistor to be tuned between 295 GHz to 310 GHz leading to a  $K_{VCO}$  of 47 GHz/V when  $V_{cont}$  is 0.6 V. Fig. 3.7(b) shows the oscillation frequency and Fig. 3.7(c)

shows the VCO gain with respect to V<sub>ctrl</sub>.

### 3.1.3 Offset Mixer Design

The offset mixer is used to simply reduce 300 GHz to 180 GHz with the help of 120-GHz LO signal coming from 120-GHz PLL.

Figure 3.8: 300-GHz offset mixer

The schematic of this offset mixer is given in Fig. 3.8. This mixer uses a double balanced active mixer topology. LO transistors have a width of 4  $\mu$ m and 300-GHz transistors have a size of 1  $\mu$ m. Low transistor size for 300-GHz is chosen to minimize the effect on the oscillation frequency and amplitude of the VCO. The gain of this mixer is given in Eq. 3.11 assuming that the RF transistors can fully switch the current from one transistor to the other.

$$V_{out} = \frac{4}{\pi} g_m . V_{LO} . \omega LQ \tag{3.11}$$

In order to maximize the gain of the mixer, we need to ensure that transconductance, LO swing and Q-factor of the inductor in Fig. 3.8 is maximized. 120-GHz LO swing comes directly from a VCO which has a swing around 1  $V_{pp}$ . The inductor at the load allows the structure to resonate at 180-GHz, maximizing the voltage swing at the output. The swing value depends on the R<sub>p</sub> value of the inductor at 180-GHz. The designed inductor has 200 pH with a Q-factor of 18. In order to maximize  $g_m$ , we need to push current through the LO transistors. Current passing through the RF transistors are limited hence in order to get more current to those transistor additional resistors are employed as in Fig. 3.8. Resistors  $R_1$  and  $R_2$  are used to provide 40% of the bias current to the 120-GHz LO transistors boosting the overall gain of the structure.

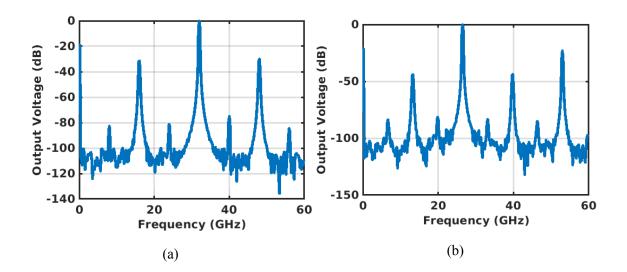

There are two benefits associated with this mixer. Firstly, offset mixer seperates 300-GHz VCO from the subsampling phase detector. Due to the capacitances being switched on and off for some time in the SSPD, it is possible that direct connection to the subsampling phase detector would create a modulation in the oscillation frequency at the VCO. However, by inserting the mixer, we ensure that the VCO sees a fixed capacitance and hence do not change its oscillation frequency. Secondly, this mixer does not generate spurs because its output components can be expressed as  $120n \pm 300m$  GHz, where n and m are integers, which are harmonics of the 60-GHz reference and map to dc after the PD.

#### 3.1.4 Gain Stage

In order to compensate some of the loss in the phase detector, an additional  $g_m$  stage is added to the PLL loop as depicted in Fig. 3.2. This amplifier consists of two stages of amplification. First stage is a fully differential PMOS pair with resistive loads and the second stage is consists of 5 transistor OTA as in Fig. 3.9(a).

Due to the finite loop gain and first order loop characteristics, the loop may be unable to lock to the reference frequency. The oscillation frequency must be close enough to be able to lock to the reference frequency. The DC bias at the output of the gain stage determines the control voltage of the VCO and hence determines the VCO's output frequency. By manipulating the output DC level, we can establish a close enough VCO frequency so that the PLL locks.

The DC bias of the output stage is modified by inserting a DC current at the positive and negative output of the fully differential amplifier. By adding small DC offset at the input of second stage,

Figure 3.9: Gain stage design (a), programmable currents added to control output DC level (b)

the output voltage can be controlled. Fig. 3.9 (b) shows the amplifier with the programmable DC bias controller. The current sources are switched externally and has a step of  $10\mu$ A with a total of 160 $\mu$ A. This gives the output DC range from 150 mV to 650 mV which is the desired range for the VCO. This amplifier generates a maximum of 16 dB gain with a bandwidth of 1 GHz. The output This large DC bias adjustment covers all of the VCO range where K<sub>VCO</sub> is greater than 5 GHz/V. At maximum K<sub>VCO</sub> point, the loop may become unstable due to the excessive gain as simulations show. As a result, a gain switch is added to the fully differential amplifier to reduce overall gain to 10 dB, such that the loop remains stable.

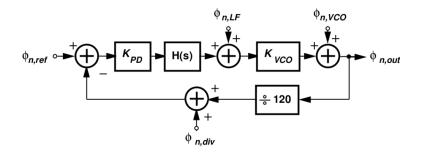

# 3.2 Phase Noise Analysis for 300-GHz PLL

In the previous sections, we showed that this PLL acts as an equivalent of x5 subsampling PLL. By using this approximation, we could still get a fairly good approximation of the exact phase noise for 300-GHz signal. For the full analysis, let us use diagram in Fig. 3.10 for phase noise analysis.

Firstly, let's start by analyzing VCO noise and calculate its contribution at the output.

$$\phi_{n,out} = (\frac{1}{1+T(s)})^2 \phi_{n,VCO}$$

(3.12)

Figure 3.10: Small signal model for phase noise analysis

Secondly, let's calculate SSPD and gain stage noise contribution at the output.

$$\phi_{n,out} = \left(\frac{A_{\phi}(s)}{K_{PD}H(s)}\right)^2 \phi_{n,K_{PD}}$$

(3.13)

Both of these contributions can be approximated like we have a x5 subsampling PLL.

Let's calculate the effect of reference and 120-GHz PLL at the same time.

$$\phi_{n,out} = 9\phi_{n,ref} \frac{A_{\phi}(s)^2}{25} + \phi_{n,120} \frac{A_{\phi}(s)^2}{25} + H^2_{n,refn,120}(\phi n, ref\phi_{n,120})$$

(3.14)

We know that VCO, SSPD and gain stage noises are uncorrelated with each other so we can utilize superposition to simplify our analysis. However, 60-GHz reference noise and 120-GHz noise are correlated to each other. In fact, in this case we can approximate that they are fully correlated within the loop bandwidth of 120-GHz PLL. We will analyze 120 GHz PLL phase noise in the following sections and we will see that the major noise contribution is coming from the 60-GHz reference for 120-GHz signal. Now assuming full correlation, the correlation term in Eq. 3.14 becomes:

$$\phi_{n,out} = 9\phi_{n,ref} \frac{A_{\phi}(s)^2}{25} + \phi_{n,120} \frac{A_{\phi}(s)^2}{25} + 6\frac{A_{\phi}(s)^2}{25}\phi_{n,ref}\phi_{n,120}$$

(3.15)

From 120 GHz PLL, we can relate output noise to the reference as:

$$\phi_{n,120} = 2\phi_{n,ref} \tag{3.16}$$

When we substitute this in Eq. 3.15, this will yield:

$$\phi_{n,out} = 9\phi_{n,ref} \frac{A_{\phi}(s)^2}{25} + 4\phi_{n,ref} \frac{A_{\phi}(s)^2}{25} + 12\phi_{n,ref} \frac{A_{\phi}(s)^2}{25}$$

(3.17)

$$\phi_{n,out} = A_{\phi}(s)^2 \phi_{n,ref} \tag{3.18}$$

in which we can assume that this PLL acts like a x5 subsampling PLL.

An interesting question in here is that what would happen if the noises are uncorrelated? If we can generate 60-GHz using two different PLL's and one of them is used as a reference for 300-GHz PLL and the other is used as a reference for 120-GHz PLL as denoted in Fig. 3.11.

Figure 3.11: A system proposition for uncorrelating phase noise

Since the noises are uncorrelated, we can neglect the correlation term in Eq. 3.14. The overall phase noise becomes:

$$\phi_{n,out} = 9\phi_{n,ref} \frac{A_{\phi}(s)^2}{25} + \phi_{n,120} \frac{A_{\phi}(s)^2}{25}$$

(3.19)

$$\phi_{n,out} = 9\phi_{n,ref} \frac{A_{\phi}(s)^2}{25} + 4\phi_{n,ref} \frac{A_{\phi}(s)^2}{25}$$

(3.20)

$$\phi_{n,out} = \frac{13}{25} A_{\phi}(s)^2 \phi_{n,ref}$$

(3.21)

which is approximately half of the phase noise that we get when we use single 60-GHz PLL.

Utilizing 2 60-GHz PLLs would significantly increase the power budget and complexity of the entire system and the gain would be only 3 dB given that both 60-GHz PLLs and crystals are at the

same phase noise level with each other. Any noise mismatch in these components would reduce the noise benefit from additional circuitry, therefore it is not implemented in this design.

## 3.3 120-GHz PLL Design

120-GHz PLL design is very similar to the 300-GHz PLL with a few changes. The most notable change for this PLL is the direct connection of the VCO to the SSPD stage. Since the VCO is frequency is 2 times the reference frequency, SSPD would have sufficient gain to lock the loop. The schematic of this PLL is given in Fig. 3.12.

Figure 3.12: 120-GHz PLL

VCO in this loop has some small modifications. First of all, although, it uses the same architecture with 300-GHz VCO as seen in Fig. 3.12(b). The values of the inductors and transistors are modified to better accommodate the lower frequency.

For the PLL system to work, all of the frequencies, 60-GHz, 120-GHz, 300-GHz PLLs must be aligned so that we can achieve a locking at 300-GHz PLL. 300-GHz VCO has a frequency change from 295 GHz to 310 GHz. This means that if we want to lock the PLL system for this entire range, 120-GHz VCO must oscillate between 118 GHz to 124 GHz. Unfortunately the frequency change of 120-GHz VCO in this case is eventually limited to 1.5 GHz as shown from simulations in Fig. 3.15(a). Recalling Eq. 3.10, the oscillation frequency depends on the inductance, mutual

Figure 3.13: 120-GHz VCO schematic

inductance and the parasitic capacitance. Rather than changing transistor sizes to match oscillation frequency, the inductances are increased to get the maximum output swing from the VCO, limiting capacitance change from VDD variation. Combined with increased capacitance from large inductor size, CM level change leads to a very narrow change in oscillation frequency.

In order to boost the frequency range of this PLL to cover more than the 300-GHz VCO, 3 capacitor banks with a load of 4 fF in Fig. 3.13 are added. The resulting oscillation frequency coverage with capacitor banks is given in Fig. 3.15(a) where it covers a range from 115 GHz to 121.2 GHz. Although, this VCO exhibits a smaller  $K_{VCO}$ , this PLL can lock much better than the 300-GHz. With high VCO swing and lower frequency, SSPD has a higher phase detector gain and eventually compensating the low gain from the VCO.

Due to the absence of the mixer, the output of this VCO is directly connected to the subsampling phase detector. As seen in the Fig. 3.14, this capacitor switching operation would create a modulation in the VCO frequency, causing spurs at 120 GHz  $\pm$  60 GHz at a level as high as -30 dBc according to simulation results. Fortunately, upon driving the offset mixer in Fig. 3.8, these components translate to integer multiples of 60 GHz, producing no additional spurs in the 300-GHz output.

Figure 3.14: Modulation of 120-GHz VCO with 60-GHz VCO

Figure 3.15: 120 GHz VCO oscillation frequency with respect to control voltage and capacitor banks (a), single ended peak-to-peak swing (b)

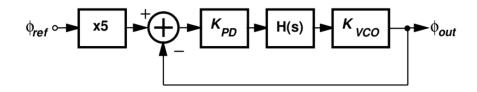

## 3.4 60-GHz PLL Design

The purpose of this PLL is divided in 2 parts. First of all, it should be able to have a rail to rail swing at 60 GHz such that it can drive the subsampling switches at both high frequency PLLs and secondly, to generate a 60-GHz signal from 500-MHz crystal reference with lowest noise as possible. The loop bandwidth is chosen as 50-MHz to limit the reference noise and VCO noise contributions.

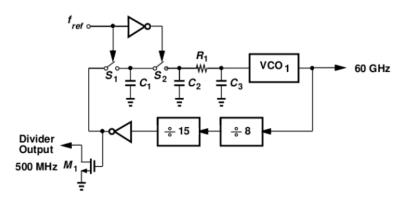

Figure 3.16: 60GHz PLL schematic

The PLL architecture is given in the Fig. 3.16. In this PLL rather than using a subsampling architecture, we employ dividers to go down all the way down to 500 MHz. As discussed in previous sections, it would be still hard not to use dividers in this case because, without dividers, this PLL can lock to any integer multiple of 500 MHz. To avoid using extra complex circuitry for a second loop, we have dividers at this circuit to divide 60 GHz down to 500 MHz.

After the division, the signal is sampled using master slave sampling phase detector. Previous sections extensively used a single stage sampling compared to this one. These switches are driven by complimentary inputs from the 500 MHz crystal.

After sampling the signal, it is only filtered with the low pass filter formed by the  $C_3$  and  $R_1$ , forming the control voltage. No amplifiers are necessary at this loop because the divided signal is more like a square wave such that the sampler acts like a bang-bang phase detector. This generates enough loop gain to achieve phase locking. This was not the case in the previous PLLs because the SSPD gain was sufficiently low so we need some boost at the loop itself.

#### 3.4.1 60-GHz VCO Design

Being at a lower frequency than both 120-GHz and 300-GHz, we don't use the buffer feedback oscillator as an oscillator for 60-GHz. This VCO is formed by complimentary cross coupled pair as seen in Fig. 3.17. This oscillator uses 15  $\mu$ m width both NMOS and PMOS transistors and 60 pH inductance as L<sub>1</sub>. Low frequency enables us to use the varactor models existing in the process

library with enough confidence. Fine tuning of this VCO is established with the varactors. In order to get a large tuning range for this VCO, 7 capacitor banks each consisting of 8 fF are added to increase the coarse tuning range of the frequency.

Figure 3.17: 60 GHz VCO schematic

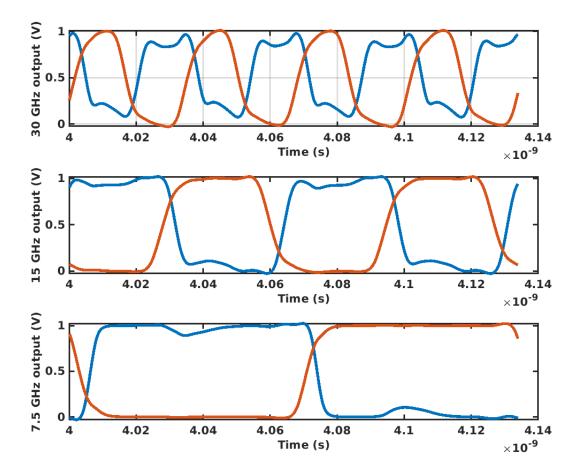

Varactors in this oscillator provide a frequency change of 900 MHz. With the additional capacitor banks, this oscillator oscillates from 56 GHz to 62 GHz as in Fig. 3.18(a). With this range, this PLL covers 280 GHz to 310 GHz in the higher frequency regime, overlapping with the 300 GHz VCO frequency.

The amplitude of the oscillation is provided in Fig. 3.18 (b), swinging from 0 to 950 mV.

#### 3.4.2 Divide-by-8 Circuit

A critical difference in 60-GHz PLL is the use of frequency dividers in the feedback path. As discussed earlier, with a very low reference frequency at 500 MHz, it is possible that this loop might lock to any integer multiplier of 500 MHz. In order to prevent this, either an additional frequency tracking loop or a frequency divider must be used.

For 60-GHz divider, it is possible to design a divider as transistors have enough gain. However

Figure 3.18: 60 GHz VCO oscillation frequency with respect to control voltage and capacitor banks (a), output swings in time domain (b)

it is still a tedious task to design a divider that can operate at 60 GHz. That is why in order to achieve a divide-by-120 in total, we employ two different divider stuructures in the loop. The first divide-by-8 structure is responsible for bringing the frequency down to 7.5 GHz and the divide-by-15 brings the frequency down to 500 MHz.

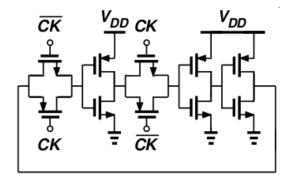

The first divide-by-8 structure consists of 3 cascaded divide-by-2 circuits. A sample divide-by-2 circuit is given in Fig. 3.19. In this structure, we have 3 inverters connected back to back with two switches inserted in between two inverters. These switches are driven with complimentary inputs such that only one of the switches remains on at the same time. This maintains the loop to be open at all times with non-overlapping clocks.

An inverter and a switch structure can be viewed as a single latch. When the switch turns on, the inverted input is at the output and when the switch turns off, the output doesn't change relative to the input. This divider uses two latches in series which acts as a D-flipflop. The extra inverter at the output is used to generate complementary output for the divider operation. Equivalently it is a D-flip flop based divide-by-2 structure as in Fig. 3.20.

Circuit in Fig. 3.19 still lacks the speed to successfully divide 60 GHz into 30 GHz. Although

Figure 3.19: Simple divide-by-2

Figure 3.20: D-flip-flop divide-by-2 circuit

it is the simplest form of a latch, it still cannot keep up to speeds like 60 GHz. The inverters need to drive a switch and an additional inverter. As a result, inverters cannot fully pull up and down their outputs with the 60 GHz clock inputs. In order to boost the speed of the divider, a few modifications are made to that circuit. Firstly, The PMOS side of the switch is removed to reduce the inverter load. Since PMOS pair is removed, in order to pull up the voltage at the output of the switch, the input clock DC level is boosted to 1 V. The output of 60-GHz VCO is AC coupled to the divider and 1 V DC level is supplied from a 4 k $\Omega$  resistor. Secondly an additional feedforward path is added to boost the speed of the circuit. The feedforward path helps the latch to prepare the output for the second stage. As the input is ready for the next latch, the circuit can operate at faster speeds. The complete circuit diagram for 60 GHz divider is given in the Fig. 3.21.

Two feedforward paths can be used to achieve more symmetrical response from the loop and an increased speed for the divider. The extra feedforward path, however, can complete a loop with three inverters, resulting in an oscillation like a ring oscillator.

Figure 3.21: Modified divide-by-2 circuit for 60 GHz input

For a single feedforward path, the size of the feedforward inverter must be chosen such that, it wouldn't disrupt the operation on the main path. If the feedforward path gets too strong, then one of the latches will operate like a buffer and as a result, this structure wouldn't divide the input frequency. Fig. 3.22 shows the divide-by-2 structure with a dominant feedforward path. We can see that the output of latch is buffered and connected to the input of itself. This can be problematic with the fast-fast corner in the chip when the feedforward path gets stronger. The structure might even start oscillating when the switch turns on. Extensive corner simulations are required to verify that the divider can successfully cover the frequency range of our 60-GHz VCO without any possible oscillations.

Figure 3.22: 60-GHz divider with a strong feedforward path

Fig. 3.23 shows the response of the divider cells outputs with 60-GHz input driven by the VCO at nominal conditions. At the first divider successfully divides 60-GHz into 30-GHz, second divider takes 30-GHz input and produces 15-GHz output and finally last divider takes 15-GHz input and returns 7.5 GHz output.

Figure 3.23: 60-GHz divide-by-8 outputs at each step

Fig. 3.24 shows the DFT results of the divider in slow-slow and fast-fast corners. From the SS corner in Fig. 3.24(a), we can divide a maximum of 64 GHz without any problems. From the FF corner in Fig. 3.24(b), we can divide a minimum of 53 GHz without any problems.

Figure 3.24: Maximum divider frequency at SS corner (a), minimum divider frequency at FF corner (a(b)

### 3.4.3 Divide-by-15 Circuit

This divide-by-15 stage is used to divide 7.5 GHz input from the previous divide-by-8 to 500 MHz. The output of this circuit will drive the phase detector of the 60-GHz PLL. Unlike the previous divider, it has relaxed requirements in terms of speed.

As the divider architecture, the modular programmable divider from [46] is chosen. Fig. 3.25 shows the overall structure which is composed of 2/3 divider cells cascaded together with a modulus feedback. The operation is as follows. When the divider cell in 2/3 divider is in a division period, the previous cell generates the  $mod_{n-1}$  signal. This signal moves to the left side of the chain and throughout this movement it is clocked again in each cell along its way. With the  $p_n$  inputs, 2/3 divider cells decide the division ratio of each cell. If  $p_n$  is zero, the divided signal propagates through the chain from left to right without an additional period. If  $p_n$  is one, then the divider cell adds an extra period to the signal. With this operation, the output period can be calculated as:

$$T_{out} = 2^{n} . T_{in} + 2^{n-1} . T_{in} . p_{n-1} + 2^{n-2} . T_{in} . p_{n-2} + \dots + 2^{1} . T_{in} . p_{1} + 2^{0} . T_{in} . p_{0}$$

(3.22)

Alternatively, the division ratio "N" can be expressed as:

$$N = 2^{n} + 2^{n-1} \cdot p_{n-1} + 2^{n-2} \cdot p_{n-2} + \dots + 2^{1} \cdot p_{1} + 2^{0} \cdot p_{0}$$

(3.23)

$$F_{\text{in}} \underbrace{-2/3 \text{ Cell}}_{p_{0}} \underbrace{F_{\text{out}}}_{p_{1}} \underbrace{F_{\text{o2}}}_{p_{1}} \bullet \bullet \bullet \underbrace{F_{\text{on-2}}}_{p_{n-2}} \underbrace{2/3 \text{ Cell}}_{p_{n-1}} \underbrace{F_{\text{on-1}}}_{p_{n-1}} \underbrace{F_{\text{on-1}}}_{p_{n-1$$

Figure 3.25: Modular programmable divider architecture

Since we need a divide-by-15 design in our PLL configuration, we would need 3 stages of dividers. By using the equation in 3.23, we can see that all  $p_n$  values must be equal to 1. In other words, each 2/3 divider cell must add an extra period to the divided signal.

A 2/3 divider cell consists of two blocks. The first block, where the signal propagates, is a divide-by-2 circuit which consists of 2 latches to form a d-flipflop divider as in Fig. 3.20. Second part of the circuit is called as "end-of-cycle" logic which takes in the mod input from the preceding stage and with p input decides the division ratio of the cell. If the p value is 0, then end-of-cycle logic doesn't affect the division ratio and 2/3 cell divides the input frequency by 2. If p=1, then end-of-cycle logic forces the top divider to absorb an extra period. Logic circuit for 2/3 divider is shown in Fig. 3.26.

Figure 3.26: 2/3 divider cell logic diagram

All of the 2/3 divider cells consists of TSPC stages. It is an ideal choice for reduced clock loading and power consumption for the logic cells. Due to the reduced clock loading, it also benefits the circuit in terms of speed. A circuit diagram for 2/3 divider cell implemented with TSPC logic is given in the Fig. 3.27. The overall circuit divides the input clock from 7.5 GHz to 500 MHz with a total power consumption of 1 mW.

Figure 3.27: 2/3 divider cell circuit diagram implemented with TSPC logic

The timing diagram is given in the Fig. 3.28. When we look at the timing diagram for all of the outputs,  $F_{o1}$ ,  $F_{o2}$  and  $F_{o3}$ , when the signals are high, there is an additional period where the signal remains high in all 2/3 divider cell outputs.

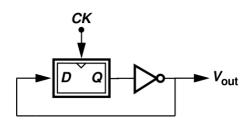

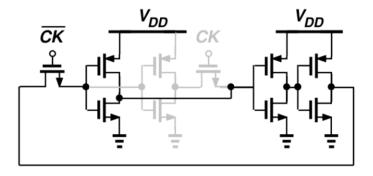

#### 3.4.4 Master Slave Sampling Phase Detector

60-GHz PLL also uses a sampling phase detector to determine the phase difference between input and the reference. Unlike its higher frequency counterparts, this PLL uses a master-slave sampling stage as depicted in Fig. 3.16.

Figure 3.28: Simulation result for the divide-by-15 circuit with all 2/3 divider cell and mod outputs

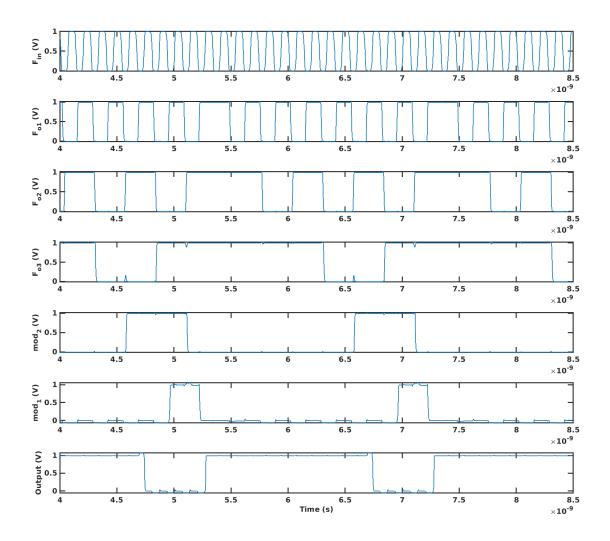

A master slave sampling is more advantageous than a single stage sampling. Simply by sampling the signal at 2 different stages, we get a pure DC signal at the output. Fig. 3.29 shows a comparison of output signals when there is single stage sampling and when there is master slave sampling. With a single stage sampling, when the switch is on, we have a sinusoidal signal on the sampling capacitor. When the switch turns off, we sample the phase of the signal on the capacitor resulting in a pure DC as seen in Fig. 3.29(a).

For MSSPD sampling in Fig. 3.29(b), the DC part of the initial signal is sampled on the capacitor. This results in an output with a pure DC and a higher phase detector gain.

Figure 3.29: Single stage sampling for phase detector (a), master slave sampling for phase detector (a(b)

In order to prove the increase in phase detector gain, let's start by analyzing single stage sampling. We would like to calculate the first fourier coefficient of the resulting signal in order to find the DC power, which is our phase detector gain, we can write the following equation:

$$a_0 = \frac{1}{T} \left[ \int_0^{T/2} A . \cos(\omega t + \theta) \, dt + \int_{T/2}^T A . \cos(\theta + \pi) \, dt \right]$$

(3.24)

$$a_0 = \frac{1}{T} \left[ \frac{A.sin(\omega t + \theta)}{\omega} \Big|_0^{T/2} - A.cos(\theta) \Big|_{T/2}^T \right]$$

(3.25)

$$a_0 = \frac{-Asin(\theta)}{\pi} - \frac{cos(\theta)}{2}$$

(3.26)

For small phase difference,  $\theta = 0$ , we can further calculate the phase detector gain as:

$$K_{PD} = \frac{-Asin(\theta)}{\pi} \tag{3.27}$$

$$K_{PD} = \frac{-A\theta}{\pi} \tag{3.28}$$

where the phase detector gain is scaled by  $1/\pi$ .

If we sample the phase using a MSSPD, we would directly sample the phase without any loss in voltage, assuming ideal sampling. Fig. 3.29(b) illustrates MSSPD sampling and the output signal. In this case, phase detector gain will be:

$$a_0 = K_{PD} = Asin(\theta) \tag{3.29}$$

For small phase difference,  $\theta = 0$ , we can further calculate the phase detector gain as:

$$K_{PD} = A\theta \tag{3.30}$$

which is  $\pi$  times higher than the single sampling stage.

The major reason why this is not used in the higher frequency PLLs is that MSSPD needs complementary clocks to operate and for those PLLs, the clock frequency is at 60 GHz. These switches are driven by the same 60-GHz VCO. In order to reduce the loading on the 60-GHZ VCO, we only use single stage sampling at those PLLs.

With a rail to rail swing coming from the divider and reference buffers, this phase detector is very ideal as it has high phase detector gain, pretty low power consumption and excellent phase noise performance. Due to its high phase detector gain, 60 GHz PLL doesn't have an additional amplifier at the output of this circuit.

### 3.5 Loop Performance for 60 GHz PLL

60-GHz PLL is a type 1 PLL like the previous PLLs as it contains only a single integrator at the loop. To analyze it more closely, let's take a look at the system diagram of the 60-GHz PLL in Fig. 3.30.

Figure 3.30: 60 GHz PLL system diagram

MSSPD acts as both a phase detector and a low pass filter in the loop due to its sampling nature. A sampling circuit in Fig. 3.31 can be approximated as an RC circuit at frequencies much lower than the sampling frequency with an equivalent  $R_s$  of  $1/Cf_{ref}$ . With a gain of  $K_{PD}$ , we can write

Figure 3.31: Equivalent circuit for an MSSPD

the transfer function of MSSPD as:

$$H_{PD}(s) = \frac{K_{PD}}{1 + sRC} \tag{3.31}$$

Equivalently,

$$H(s)_{PD} = \frac{K_{PD}}{1 + \frac{s}{f_{ref}}}$$

(3.32)

The open loop transfer function would be

$$\frac{\phi_{out,open}}{\phi_{ref,open}} = T(s) = 120H(s)\frac{K_{VCO}}{s}$$

(3.33)

The closed loop transfer function can be calculated as

$$\frac{\phi_{out}}{\phi_{ref}} = A_{\phi}(s) = \frac{120H(s)\frac{K_{VCO}}{s}}{1+H(s)\frac{K_{VCO}}{s}}$$

(3.34)

For the phase noise analysis, we need to take a look at the phase noise contributions. Fig. 3.32 shows the phase noise contributions for this PLL. For each contribution, we can write the following equations to determine the total phase noise contribution of this PLL using superposition.

$$\phi_{n,out,VCO} = (\frac{1}{1+T(s)})^2 \phi_{n,VCO}$$

(3.35)

$$\phi_{n,out,lf} = \left(\frac{A_{\phi}(s)}{K_{PD}H(s)}\right)^2 \phi_{n,K_{PD}}$$

(3.36)

Figure 3.32: 60 GHz PLL noise contributors

Unlike high frequency PLLs, the noise contributions in this PLL contributes the most of the phase noise in the overall system. Once the reference is multiplied by 120, 120-GHz PLL and 300-GHz PLL components' noise contribution is negligible compared to the reference noise as we will prove later throughout simulations.

## **CHAPTER 4**

## Layout and Floorplanning

A crucial part of the design is the layout of the PLLs. Without correct layout and placement, it would be hard to correctly operate the system in harmony especially at 300 GHz. Since the frequency is very high, we need to be very careful about the placement as it may lead to a shift in frequencies or create high losses in the oscillation amplitudes, which would result in the loop not to lock.

First major concern is the design of the 300 GHz loop. From Fig. 3.2, we can see that 300 GHz VCO is driving the 180-GHz mixer from the output of the VCO. As the most vulnerable part of circuit in terms of oscillation frequency and amplitude, the mixer must be placed very close to the 300-GHz VCO to load the VCO with the least amount of parasitic capacitance. In terms of inductor radius, 300-GHz VCO radius is 16.75  $\mu$ m and the mixer inductor radius is 27.5  $\mu$ m. According to these dimensions, 300-GHz VCO and mixer inductors can be placed as in Fig. 4.1.

Fig. 4.1 reflects a very idealized picture in terms of the placement. 300-GHz VCO inductor is placed on the top side with mixer inductor is placed on the bottom side. As the transistors are placed very closely, this type of arrangement would provide the best swing from the 300-GHz VCO and at the output of the mixer. Another concern for a placement like this is the coupling between inductors.

Here we see another advantage of using a BFO. We have two inductors in the VCO that is coupled to each other. These inductors due to their strong coupling wouldn't couple with the neighboring inductors. Simulation results for a placement like in Fig. 4.1 would only result in a change of 300-GHz VCO frequency by 3.3 GHz and its amplitude by 62 mV even though when the bottom edges of the inductors are placed 10 µm apart.

Figure 4.1: An idealized placement for VCO inductor and mixer inductor in 300 GHz PLL loop

For the remaining part of the 300-GHz loop, we can place the sub-sampler and the amplifier very close to the mixer, reducing the routing losses. The only long path is from the output of the amplifier driving the PMOS control transistor to adjust VCO frequency. However, due to the low frequency nature of that specific line, we can afford to a very long line as it wouldn't create much loss terms of the control voltage.

When we go to the next critical loop in our PLL design, we have 120-GHz PLL. In this PLL, we have a 120-GHz VCO again driving the mixer and differently from the other PLL, this VCO is driving its own subsampling stage. Building on top of our previous floorplan in Fig. 4.1, we can add the 120-GHz VCO inductors, which have an outer radius of 45.8 µm, right next to the small 300-GHz VCO inductors as in the Fig. 4.2 VCO transistors are directly connected to the sub-sampler without any extra routing. This type of arrangement brings some different challenges to the layout design. First of all, although not as vulnerable as 300-GHz VCO, 120-GHz oscillator is still prone to parasitic capacitances which can largely impact its oscillation frequency and amplitude.

Figure 4.2: 120 GHz VCO inductor on the right side of 300 GHz VCO inductor and mixer inductor. 120 GHz VCO transistors are close to the other transistors (a), 120 GHz VCO transistors are at the VCO inductor (b)

A possible floorplan is to place the transistors away from the VCO inductor and closer to the mixer transistors as in Fig. 4.2(a). In this case, VCO transistors will be able to drive the mixer transistors however, due to significant distance from the inductor and the use of low level metals for routing from inductors to the transistors results in a high inductor resistance. This effectively reduces the Q factor of the VCO inductors and reduces the output swing of the VCO. When compared with ideal conditions (when the routing is minimum) from simulation results, it leads to a loss of 200 mV (1.6 dB loss).

Second option is to place the transistors close to the inductor have some routing from the transistors to the input of the mixer. This type of arrangement as in Fig. 4.2(b) would eventually lead to better VCO characteristics in terms of amplitude. Now since the inductor is directly connected to the transistors, this wouldn't reduce the Q value of the inductor. However extra routing using the lower metal layers from the output would lead to some resistive loading from the mixer combined with the gate resistance of mixer transistors. From the simulation results, although it is a better alternative from the previous routing, it still has a loss around 150 mV (1.16 dB loss). This amount of loss might seem pretty small and manageable but unfortunately it has a large impact on the loop performance. The mixer, in order to operate properly, the transistors must be switched from on to off fully in a 8.33 ps. A switching like this requires a very large 120-GHz swing as the transistors suffer from speed degradation at such large frequencies. A reduction of 1.2 dB in amplitude results in a loss of 3.6 dB in the overall mixer gain at 180 GHz. A reduction of 1.6 dB in amplitude results in a loss of 4.8 dB in the overall mixer gain at 180 GHz.

Figure 4.3: Layout placement for VCO inductors and transistors

We cannot afford to such a high loss at the mixer output. This may eventually lead to very small lock ranges or may prohibit the loop to lock. As a result, we propose the floorplan in the Fig. 4.3 where on the top side, we have 300 GHz VCO inductors directly connected to the 300-GHz VCO transistors, on the bottom side we have 120-GHz VCO inductors that is directly connected to 120-GHz VCO transistors. In order to minimize the routing to mixer transistors, we place those transistors right in the middle of two VCOs. With a routing like this, we would minimize the loading on both of the VCOs and get the best performance out of the them. There is still one question remains. Where should we place the mixer inductors?

Figure 4.4: Layout placement for inductors and transistors

Since the center area is occupied by the VCO inductors, we need to place the mixer inductor to the side as in the Fig. 4.4. In order to reach to the inductor, we now need to travel some distance from the mixer to its inductor. One might say that this arrangement would again result to a lower mixer gain. In order to prevent the loss, we would offer some modifications to the layout.

First of all, we need to use thick metal layers to route the output of the mixer to its inductors. This would minimize the loss by the line resistances. It is true that these lines would add some inductance and slightly lower the Q-factor of the overall inductor. Second modification is the placement of the sub-sampler in the loop. Where is the correct location for the the sub-sampler? In order to answer this question, let's take a look at the Fig. 4.5.