# Device-Circuit Interactions and Impact on TFT Circuit-System Design

Xiang Cheng, Student Member, IEEE, Sungsik Lee, Member, IEEE, Reza Chaji, Member, IEEE, and Arokia Nathan, Fellow, IEEE

Abstract—This paper reviews the importance of device-circuit interactions (DCI) and its consideration when designing thin film transistor circuits and systems. We examine temperature- and process-induced variations and propose a way to evaluate the maximum achievable intrinsic performance of the TFT. This is aimed at determining when DCI becomes crucial for a specific application. Compensation methods are then reviewed to show examples of how DCI is considered in the design of AMOLED displays. Other designs such as analog front-end and image sensors are also discussed, where alternate circuits should be designed to overcome the limitations of the intrinsic device properties.

Index Terms—Small signal model, s parameter, TFT, cutoff frequency,  $V_{\rm T}$  shift

#### I. INTRODUCTION

lthough the ever-evolving TFT technology continues to produce devices with improved performance, such as higher mobility, steeper subthreshold slop and lower  $V_T$  [1]–[9], circuit implementation is still somewhat constrained. This applies for most of the material families including metal-oxides, organics, and amorphous silicon (a-Si:H) although much less so with low temperature (LTPS). poly-silicon Here, a key design consideration is the device-circuit interaction (DCI), which has to be accounted for when circuits are designed with devices of poor performance and high degree of non-ideality [10]-[19] as compared to the CMOS counterpart. This is particularly true when the intrinsic performance of TFTs does not the meet the requirements of a desired application. As shown

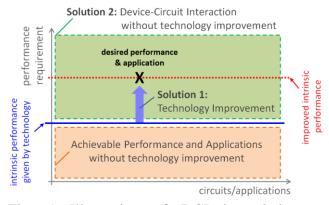

Fig. 1 Illustration of DCI in relation to performance requirements of a desired application

in Fig. 1, if the performance of the desired application is much lower than the maximum achievable intrinsic performance of the TFT, it is then possible to design the circuit independently without considering device non-idealities. For example, when the error in the TFT's output current created by  $V_T$  shift is much lower than the required accuracy, the  $V_T$  shift problem is not of concern. However, when the performance requirement needs to be higher than the intrinsic performance, the designer should seek a compensation solution based on DCI or wait for improvements in the technology. We will discuss the intrinsic performance of TFTs in Section II along with compensation methods in Section III.

Another aspect of DCI stems from the material and processing attributes of the TFT which usually come with specific, and often self-limiting, properties. For example, in analog front-end and digital designs, alternative circuit architectures are needed to match the properties of the CMOS counterpart [20]–[24]. This will be discussed in Section IV along with

Manuscript received, xxx.2016

X. Cheng, S. Lee, and A. Nathan are with the Electrical Engineering Division, Department of Engineering, University of Cambridge, Cambridge CB3 0FA, U.K. (e-mail: xc260@cam.ac.uk; sl684@cam.ac.uk; an299@eng.cam.ac.uk).

R. Chaji is with IGNIS Innovation Inc., Waterloo, ON, N2V 2C5 Canada(e-mail: rzchaji@gmail.com)

solutions to deal with, for example, light-induced non-ideality in oxide TFTs.

#### II. IMPACT OF TFT PROPERTIES

The TFT is the major building blocks of active thin film circuits and its properties determine circuit performance. In applications such as displays and analog front-end circuits, the accuracy of the output signal strongly affects the quality of the displayed image without mura (luminance non-uniformity) or in processing analog signal without significant error. The critical parameters for TFTs (e.g. mobility, C<sub>OX</sub>, V<sub>T</sub>, etc.) determine the performance of the circuit and are more often discussed when comparing TFT behavior or modelling a single transistor's terminal characteristics [12], [25]-[31]. However, other issues such as stability, temperature sensitivity and process variations can also limit the overall performance and may even affect the functionality of the circuit. There has been significant effort devoted to the study and modeling of bias induced V<sub>T</sub>-shift [11], [15], [16] and V<sub>T</sub>-shift compensation in AMOLED pixel circuits [32]–[35]. We will analyze the sensitivity of drain current on V<sub>T</sub>-stability and temperature and process variations with the aim of establishing guidelines on the level of accuracy that can be achieved without applying compensation methods (i.e. the intrinsic performance) as well as identify the parameters that contribute most to error and how this can be improved with processing.

#### 1) Temperature dependence

The parameters of the TFT are affected by material properties and on temperature, which in turn impacts the terminal current-voltage (I-V) behavior. According to the I-V model of the TFT:

$$I_{DS} \approx \frac{1}{2 + \alpha_p} \frac{\mu_0^*}{Q_{ref}} \frac{W}{L} C_{ox}^{\alpha_p} (V_{GS} - V_T)^{(\alpha_p + 1)}, \quad (1)$$

=  $K \times (V_{GS} - V_T)^{(\alpha_p + 1)}$

where,

$$K \equiv \frac{1}{2 + \alpha_p} \frac{\mu_0^*}{Q_{ref}} \frac{W}{L} C_{ox}^{\alpha_p}$$

(2)

The variations can be specified as three key

2

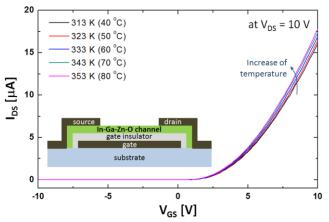

Fig. 2 I-V characteristics of the examined TFT under different temperatures.

parameters: K,  $V_T$  and  $\alpha_p$ . By considering these parameters as functions of temperature, the derivative of  $I_{DS}$  as a function of temperature can be expressed as follows:

$$dI_{DS}(T) = (V_{GS} - V_T)^{(\alpha_p + 1)} \frac{\partial K}{\partial T} dT$$

-  $K(\alpha_p + 1) (V_{GS} - V_T)^{\alpha_p} \frac{\partial V_T}{\partial T} dT$  (3)

+  $K \ln (V_{GS} - V_T) (V_{GS} - V_T)^{(\alpha_p + 1)} \frac{\partial \alpha_p}{\partial T} dT$

Therefore the temperature sensitivity of the overall current can be separated into three parts, in which each part of the function is determined by the temperature sensitivity of K,  $V_T$  or  $\alpha_p$ . The contribution of each parameter can then be calculated through extraction of the temperature sensitivity of the three parameters.

Consider the transfer characteristic for an indium-gallium-zinc-oxide (IGZO) TFT, measured every 10°C from 40°C to 80°C, shown in Fig. 2. The results show that the overall current would increase when temperature increases. To further investigate the degree of influence of the three parameters, their values have been extracted from the measured transfer characteristics according to Eq. (1). Here, we extract the threshold voltage  $(V_T)$  independently from a multi-derivative method [36], and then use it to calibrate the gate voltage as  $V_{GS} - V_T$ . With this, I-V data is plotted in log-log plot. In this plot, all the data turns into a linear behavior, where the intercept on the y-axis,  $\log(I_{DS})$ , is  $\log(K)$ , with slope  $\alpha_{p}$ . From

3

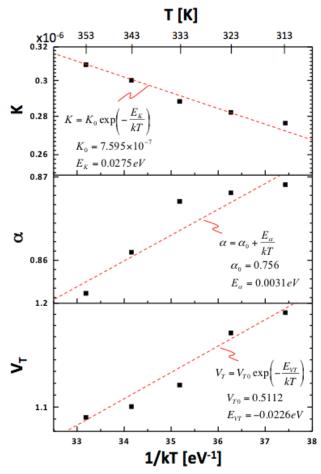

Fig. 3 Extracted values of K,  $\alpha_p$  and V<sub>T</sub> at the different temperatures.

this, we will get K and  $\alpha_p$  independently. The results are shown in Fig. 3. As can be seen, all three parameters are approximately linearly related to 1/kT in the temperature range considered.

Therefore, through a linear fitting of the parameters, we get the empirical models of the parameters with the following relations:

$$\alpha_P(T) = \alpha_0 + \frac{E_\alpha}{kT} \tag{4}$$

$$K(T) = K_0 \exp(-\frac{E_K}{kT})$$

(5)

$$V_T(T) = V_{T_0} \exp\left(-\frac{E_{VT}}{kT}\right) \tag{6}$$

Combining Eq. (4), (5), (6) and Eq. (3), the current sensitivity can be derived as:

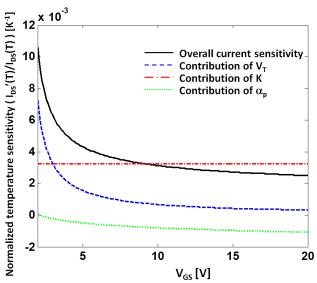

Fig. 4 Normalized temperature sensitivity of current and the contribution of different parameters at 313K.

$$\frac{dI_{DS}(T)}{dT} = \left(V_{GS} - V_T\right)^{(\alpha_p + 1)} K_0 \frac{E_K}{kT^2} \exp\left(-E_K / kT\right) - K(\alpha_p + 1) \left(V_{GS} - V_T\right)^{\alpha_p} V_{T_0} \frac{E_{VT}}{kT^2} \exp\left(-E_{VT} / kT\right)$$

(7)

$$- K \ln\left(V_{GS} - V_T\right) \left(V_{GS} - V_T\right)^{\alpha_p + 1} \frac{E_\alpha}{kT^2}$$

Note that the three terms at the RHS of Eq. (7) define the contribution of K,  $V_T$  and  $\alpha_p$ , respectively.

To understand how much the overall current is affected by ambient temperature and the associated contribution of the different parameters, the normalized temperature sensitivity is shown in Fig. 4. As can be seen, the overall temperature sensitivity drops with increase in  $V_{GS}$  due to the fact that the contribution of V<sub>T</sub> drops while V<sub>GS</sub> increases. This tendency starts to saturate when V<sub>GS</sub> increases to 4V, when the contribution of K becomes dominant. This analysis suggests that TFTs can be very unstable when biased at a voltage near V<sub>T</sub>. Although higher stability can be achieved through intentionally biasing the transistor at higher voltage levels, the maximum achievable level will be determined by the temperature sensitivity of K. As the temperature dependence of  $\alpha_p$  has a negative contribution to current with respect to temperature and its contribution increases at higher bias, the temperature dependence of K can be compensated by  $\alpha_p$  resulting in decreased sensitivity. However, a higher bias level

implies increased power consumption of the circuit. Therefore, an appropriate bias point should be chosen for enough stability with acceptable power consumption.

# 2) Geometric dependence

Apart from time- or temperature-dependent variations in device parameters, processing-induced spatial variations should be considered especially in pixelated arrays or analog circuit applications. These variations would cause pixel non-uniformity in displays or imagers and create error or undesired behavior in analog circuit design. Note that the non-uniformity can be global (i.e. between panels) or local (i.e. between transistors). The latter is harder to deal with especially when transistor matching is of concern (such as in differential pairs or current mirrors). This paper will focus on local non-uniformity and discuss the contribution of the different parameters in creating current mismatch.

Analysis of geometric dependence can follow a similar route as with temperature dependence. As different parameters would follow a certain probability distribution, the overall current will be determined by the randomness of all three parameters according to Eq. (1). As variations are usually smaller than the respective mean values, the mismatch in  $I_{DS}$  can be expressed as a first order approximation:

$$\Delta I_{DS} = (V_{GS} - V_{T0})^{(\alpha_{p0}+1)} \Delta K$$

-  $K_0 (\alpha_{p0} + 1) (V_{GS} - V_{T0})^{\alpha_{p0}} \Delta V_T$

+  $K_0 \ln(V_{GS} - V_{T0}) (V_{GS} - V_{T0})^{(\alpha_{p0}+1)} \Delta \alpha_p$  (8)

Here,  $K_0$ ,  $V_{T0}$  and  $\alpha_{p0}$  are the mean values of the parameters, and  $\Delta K$ ,  $\Delta V_T$  and  $\Delta \alpha_p$  their respective variations. Assuming K,  $\alpha_p$  and  $V_T$  are independent variables and that all follow a normal distribution, the variance of  $I_{DS}$  can be expressed as:

$$\sigma^{2}_{I_{DS}} = (V_{GS} - V_{T0})^{2(\alpha_{p0}+1)} \sigma^{2}_{K} + K_{0}^{2} (\alpha_{p0}+1)^{2} (V_{GS} - V_{T0})^{2\alpha_{p0}} \sigma^{2}_{V_{T}} + K_{0}^{2} [\ln(V_{GS} - V_{T0})]^{2} (V_{GS} - V_{T0})^{2(\alpha_{p0}+1)} \sigma^{2}_{\alpha_{p}}$$

(9)

where  $\sigma_{K}$ ,  $\sigma_{\alpha_n}$  and  $\sigma_{V_T}$  are the standard deviation

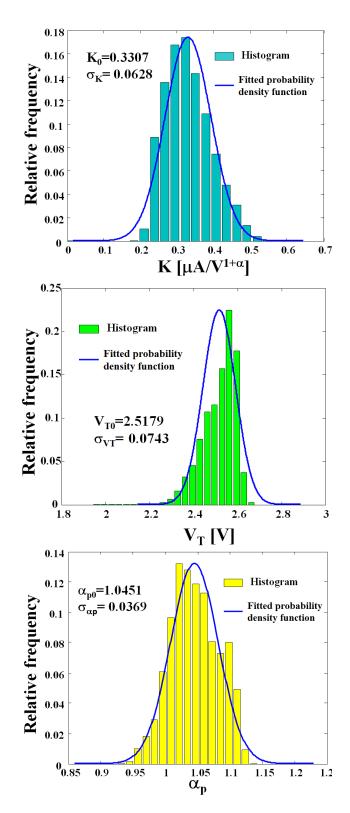

Fig. 5 Probability distribution and histogram of (a) K, (b)  $V_T$  and (c)  $\alpha_p$ . The data was extracted at room temperature from a 1080\*1920 RGBW AMOLED panel with pixel circuits as described in Fig. 7.

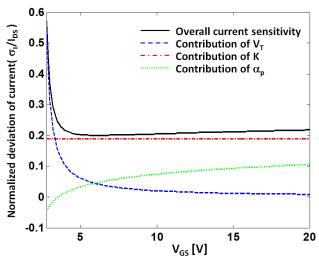

Fig. 6 Normalized standard deviation of current and the contribution of different parameters.

of K,  $\alpha_p$  and V<sub>T</sub>, respectively. As expected, the standard deviation of the overall current is determined by the deviation of all three parameters.

To analyze the variation sensitivity of the overall current, we need statistical data for all three parameters. Here, we acquired statistical data of the transfer characteristics by measuring a 1080\*1920 RGBW OLED display panel. By using the pixel circuit described in [32], which will be reviewed in the next section, we could extract the I-V characteristics of the driver TFTs within the panel and extract statistical data for the three parameters. Here, the TFTs for driving the green OLED pixels are used as shown in Fig. 5. The probability density functions are fitted to a normal distribution using MATLAB. With the fitted mean values and standard deviations, we calculate the relative contributions of each parameter to the current variance using Eq. (9).

The standard deviation of  $I_{DS}$  and the contribution of each parameter are shown in Fig. 6. We see a similar overall curve in the sense that the sensitivity is higher when biased near V<sub>T</sub>. However, unlike the temperature dependence where sensitivity drops with increasing bias, the dependence on geometric shows a minimum at around V<sub>GS</sub>=6V. This is due to the decreasing contribution of V<sub>T</sub> and the increasing contribution of  $\alpha_p$ . Therefore, analog designers can intentionally choose a bias point close to the minimum point for the output transistor, when designing circuits to reduce the output current sensitivity to process variations.

The analysis of temperature and geometric dependence here is done using a generic approach since the current-voltage behavior is estimated by three key parameters, namely K,  $V_T$  and  $\alpha_p$ . This is adaptable to most TFT types because of the similar working principle albeit with different parameter values. Therefore, the methodologies and derivations presented here are generic and empirically approached for applicability to other material families including OTFTs and related material families.

5

# III. COMPENSATION METHODS IN CIRCUITS & APPLICATIONS

The intrinsic performance of TFTs does not specific meet the requirements always of applications. For example, the threshold voltage shift in TFTs creates visible shadows or ghosting in displays or imagers after extended operation. The resulting non-uniformity creates mismatch in output characteristics especially in matrix architectures (displays or sensors). These kinds of defects have proven difficult to improve by processing, and thus need to be compensated through circuit solutions. Here, we will discuss V<sub>T</sub> shift and non-uniformity compensation methods such on-pixel as programming and by off-pixel feedback. The compensation methods can also be extended to other circuit applications.

#### 1) On pixel programming

The most common way of compensating TFT defects in active matrix arrays is through on-pixel compensation. The methods were first developed for a-Si:H TFTs in AMOLEDs as this family of TFTs have severe  $V_T$  shift under positive bias, which leads to big errors when supplying current to the OLED [37].

$V_T$  compensation techniques can be categorized into two kinds: current programming [34], [38]–[44] and voltage programming [45]–[52]. The basic working principles of these have been reviewed in [37], [53]. Recent progress in voltage programming

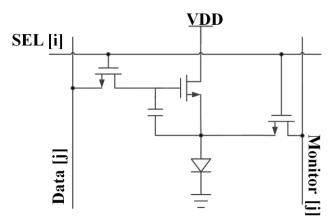

Fig. 7 AMOLED pixel structure for off-pixel defect extraction and feedback

has been reported in [35], [54]. Here, the working principle is slightly different from the original idea in that the technique does not capture the cut-off point of a diode-connected transistor. Instead, it uses a TFT to discharge a pre-charged capacitor with fixed gate bias in a fixed time period to capture the TFT's property (i.e.  $V_T$ ). This technique can provide faster  $V_T$  extraction and is good particularly when the speed of the circuit is of concern.

#### 2) Off pixel feedback

Another way of defect compensation is based on off pixel feedback. Since in display applications the driving period of each pixel can be separated into several phases, it is possible to use part of the driving sequence to extract all of the defect and aging data present in the pixel and then drive with revised extracted parameters as feedback [32], [55]–[60].

A pixel structure for defect extraction reported in [32] is shown in Fig. 7. The pixel circuit shows a similar structure as the simple 2T1C structure – the only difference being addition of a monitor line to monitor the TFT and OLED characteristics and extract their defect and aging status. The driving sequence for this pixel circuit is similar to the 2T1C except for the addition of a defect extraction phase. Defect extraction starts after the SEL signal selects the pixel and before writing data to it. The extraction phase consists of two parts – the driver TFT and the OLED, respectively (shown in Fig. 8).

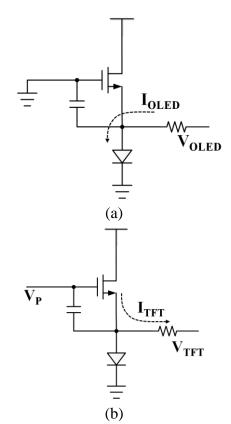

Fig. 8 Equivalent circuit for the defect extraction phase when extracting (a) OLED and (b) TFT status.

Fig. 8(a) shows an equivalent circuit of the extraction phase for the OLED. In this phase the gate voltage of the driver TFT is set to ground level to turn it off and the monitor line is set to a higher voltage of  $V_{OLED}$ . The current flowing through the OLED can then be captured by measuring the current flowing into the monitor line. As the I-V characteristic of the OLED can be a signature of its efficiency, the aging of OLED can then be captured from pre-acquired data for this type of OLED.

In Fig. 8(b), the gate voltage of the driver TFT is set to a higher level of  $V_P$ . The TFT is then turned on and part of the drain current flows to the monitor line. Combining the extracted I-V characteristic data of the OLED and the voltage and current measurements in this phase, the I-V characteristic of the driver TFT can be extracted.

After capturing the defect and aging data for both the driver TFT and OLED, the data voltage for the desired luminance can be calculated and applied to the pixel by external circuitry.

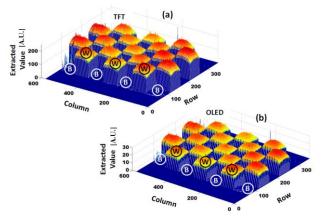

Fig. 9 Extracted aging parameters for (a) TFTs and (b) OLEDs after continuously displaying a checker board (W: displayed with white squares, B: displayed with black squares)

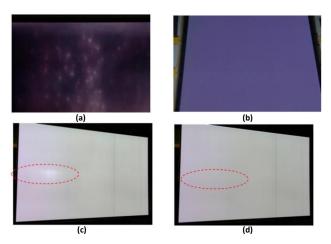

Fig. 10 Defect compensation in display panels (a) display panel as fabricated without compensation (b) display panel after defect compensation (c) hot spot induced by TFT back plane (d) hot spot

The aging and defect status of TFTs and OLEDs extracted through the monitor lines are shown in Fig. 9(a) and Fig. 9(b), respectively. The sharp hazards that happen randomly among the panel show the fabrication defects of the pixels. And the patterns in red, yellow and green color express the aging of each device. As the center of the displayed white square has higher temperature due to self-heating of the surrounding pixels, the aging of these pixels will be faster compared to other pixels.

The display panel using this method has the ability of compensating all kinds of defects that can be extracted through the monitor line. The compensation results are shown in Fig. 10 depicting the defect status in Fig. 10(a)&(b) and temperature compensation in Fig. 10(c)&(d).

This method provides a generic solution for TFT compensation and will be particularly useful in compensation of mechanically-induced (reversible) defects or aging in flexible displays. As measurement of the TFTs can be done in a monitoring phase, the obtained parameters can then be used to bias the TFTs to have an ideal overall performance. The geometric dependence of transistors can also be extracted from this pixel, as during the sequence described in Fig. 8(a) & (b) one can also apply voltage sweep to obtain the measured I-V characteristics for both TFT and OLED devices.

In summary, defects of TFTs can be compensated through separating the working sequence into several phases and by adding a compensation phase to extract and compensate non-idealities. To apply this method to other analog circuits, it is possible to intentionally separate the working sequence and apply similar methods. Here, switch-capacitor circuits can be a promising candidate. An example of this applied to analog building blocks was reported in [61].

# IV. SPECIFIC DEVICE PROPERTIES AND ALTERNATE CIRCUIT ARCHITECTURES

Devices processed using different thin film technologies usually have a specific property, which can sometimes be self-limiting. This requires the use of alternate circuit architectures. For example, most TFT technologies lack complementarity, thus the circuits have to be designed using mono-type devices, which means the designs cannot benefit from the well-established CMOS architectures. Specifically, the load of an analog amplifier needs to be redesigned to achieve high gain as the complementary load is not applicable. Another example is persistence photoconductivity in oxide TFTs, which, while ideal for image capture, requires a sharp gate a pulse to reset for high frame rates. We will discuss these examples in the following.

# 1) Analog gain stage with mono-type TFTs

CMOS gain stages benefit from the complementary structure [62]–[64]. For example, in

7

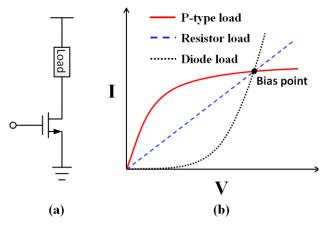

Fig. 11 (a) Common-source gain stage of an amplifier (b) sketch of different type of loads passing through the same bias point

the case of NMOS as the input stage and PMOS as the load, the gain of the stage can be boost up to the order of magnitude of  $g_m r_o$ . The use of PMOS load provides large enough bias current with small voltage and, at the same time, big small signal resistance. These requirements are hard to be achieved with only one type of transistors.

To simplify the problem, we consider a single common source amplifier stage as shown in Fig. 11(a). Here, the load is considered as a two terminal device. Assuming the bias conditions of the driver TFT is fixed (to maintain  $g_m$  for fair comparison between different loads), the load of this gain stage would have fixed bias current. Here, we consider a fixed bias point of the load for comparison, i.e. the I-V characteristic of the load should pass a fixed point in the I-V plot (Fig. 11(b)). As the gain stage needs a higher small signal resistance of the load to produce high gain (i.e. derivative at the bias point should be close to zero), the current is better a concave function of voltage which means p-type load is more beneficial. Note that for other type of loads, the same small signal resistance can only be achieved by moving the bias point to the right hand side, i.e. increase the voltage bias of the load. However, a higher voltage bias would yield higher power consumption. From this standpoint, we conclude that for high gain, a p-type load with fixed gate bias (concave function) is more beneficial than a resistive load (linear function) and, subsequently, a diode or diode-connected TFT load (convex function) as it yields higher gain at the same power

Fig. 12 Gain stage of an amplifier with (a) feedback load [22], [24] (b) boost strap load [20]

consumption.

The most familiar concave function in TFT behaviors is the output characteristic  $(I_D-V_{DS})$  characteristic with fixed  $V_{GS}$ ). However, the design is limited by the connection of n-type devices as the source terminal of the load TFT is connected to the output node of the gain stage. Thus, the gate terminal of the TFT cannot be chosen as a fixed level but should follow the change of the source terminal.

One straight forward solution is to use a depletion mode load and short circuit the load transistor's source and gate terminals. (Depletion mode transistor can work in saturation regime with zero  $V_{GS.}$ ) Amplifiers have been designed around 1980s to achieve high gain with depletion and enhancement NMOS transistors [64]–[66]. However, in TFT circuit area, this approach is limited by process complexity. By far, only digital circuits have been fabricated out of depletion load [67]–[69].

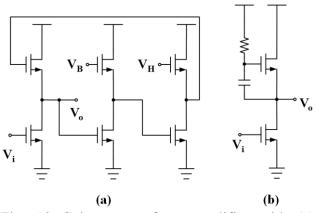

In order to use only enhancement mode TFTs while still obtaining high enough gain, it is also possible to use feedback loop to maintain a fixed  $V_{GS}$  for high small signal resistance of the load. One approach is reported in [22], [24]. The circuit reported is shown in Fig. 12(a). Here, an analog adder is designed for the DC bias of the load transistor. The feedback circuit, in effect, adds a bias voltage to the source terminal of the load transistor and applies the resulting voltage to the gate terminal. Here, the feedback voltage at the gate terminal of the load TFT can be calculated as:

$$V_F = V_H - V_B + V_o \tag{10}$$

8

Here,  $V_H$  and  $V_B$  are external bias voltages and Vo is the output of the gain stage (which is also the source terminal voltage of load). As the feedback voltage contains the output, this topology has a positive feedback.

Another approach using positive feedback has been reported by H.Marien et al [20]. The load of their gain stage is designed with boost strap structure. Other than maintaining the  $V_{GS}$  level of the load TFT, the structure successfully separates the DC bias and the small signal resistance and as a result obtains a higher gain for small signals at a higher frequency. The circuit needs a large capacitor for the load (a high pass filter) to reduce its lower 3dB frequency close to DC range. This also makes the circuit hard to work at very low frequencies, especially when the original signal is close to DC. An NMOS version of the circuit has been shown in Fig. 12(b). Other approaches regarding positive feedback are also reported in [23].

To summarize, positive feedback is used for gain-enhancement in single type TFT amplifiers. The major problem of this kind of approach is that positive feedback sacrifices the phase margin (PM) of the amplifier and would potentially cause instability. Although a cascode technique can be chosen to enhance the gain without sacrificing PM, it is not preferred in TFTs since a much higher supply voltage is needed because of the high threshold voltage of TFTs.

## 2) Persistent Photoconductivity

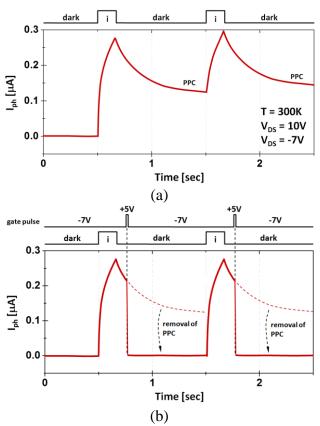

This can arise depending on the channel composition in oxide transistors when the transistor is under exposure to ambient light or when subject to negative bias illumination stress (NBIS) [21]. As the drain current of the TFT increases after exposure to ambient light, it is possible to use this characteristic for photo-sensing applications. In this application, the variation of current is not a defect that needs to be compensated. However, to use this property, the slow recovery process makes it hard to capture the changing image at high frame rate or to restore the TFT's initial state. Fig. 13(a) depicts the drain current of an IGZO TFT under periodic luminance

Fig. 13 (a) Observation of persistent photoconductivity (PPC) as a slow recovery and (b) removal of PPC with a positive gate pulse to get fast recovery.

and darkness. The results show the drain current recovering only slowly even in a completely dark environment..

In order to remove the persistent photoconductivity and recover the TFT to its original state, it has been found that by applying a positive pulse to the gate of the TFT, the PPC can be eliminated very quickly. The results in Fig. 13(b) show that fast PPC removal is possible after the gate pulse technique.

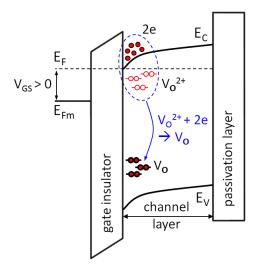

The phenomenon of PPC is explained by the band diagram shown in Fig. 14. As the ambient light excites the electrons in defect states to the conduction band, ionized oxygen defects are created. The excited electrons effectively increase the conductivity of the device as the electron concentration is increased. In order to accelerate the recovery process, the recombination of photo-induced electrons and ionized oxygen defects  $V_0^{2+}$  needs to be accelerated. By applying a positive

Fig. 14 Band diagram to explain the effect of positive gate pulse on recovery.

voltage pulse to the gate of the transistor, the electrons are swept away from the conduction band to recombine with the ionized oxygen defects thus removing the PPC.

PPC removal is a great example of device circuit interaction as the defect (i.e. light induced instability) of a TFT can actually be utilized to sense luminance signal, i.e. as a photo sensor. Indeed DCI should be considered not only to enhance circuit performance and/or overcome difficulties in the design but also to utilize specific properties stemming from the operating environment.

## V. CONCLUSION

This paper reviewed and analyzed the intrinsic parameters of TFTs and proposed ways of analyzing the maximum achievable current accuracy of TFTs and to help determine when compensation becomes mandatory to enhance reliability and combat ageing. We presented techniques for extraction of defects and aging in devices using closed-loop feedback techniques and discussed their extension to other applications.

In summary, device circuit interactions are crucial when designing high performance circuits and systems to either utilize or minimize the impact of intrinsic adversaties associated with low temperature thin film technology. Consideration of device circuit interactions in design of TFT systems is even more compelling than the case of CMOS technology because of the wide range of materials imperfections, which give rise to device instability and large area processing-induced non-uniformity. Of specific importance to mechanically flexible systems is the impact of bending-induced (reversible) defects and associated aging, which makes compensation even more compelling. The techniques presented here can extend the current application of TFTs from active matrix pixelated arrays to newly-emerging application area that require TFT operation in analog operation mode.

## REFERENCES

- K. Nomura, H. Ohta, A. Takagi, T. Kamiya, M. Hirano, and H. Hosono,

"Room-temperature fabrication of transparent flexible thin-film transistors using amorphous oxide semiconductors.," *Nature*, vol. 432, pp. 488–492, 2004.

- [2] D. J. Gundlach, Y. Y. Lin, T. N. Jackson, S. F. Nelson, and D. G. Schlom, "Pentacene organic thin-film transistors-molecular ordering andmobility," *IEEE Electron Device Lett.*, vol. 18, 1997.

- [3] H. Klauk, "Organic thin-film transistors," *Chem. Soc. Rev.*, vol. 39, no. 7, p. 2643, 2010.

- [4] L. Feng, W. Tang, X. Xu, Q. Cui, and X. Guo, "Ultralow-Voltage Solution-Processed Organic Transistors With Small Gate Dielectric Capacitance," *IEEE Electron Device Lett.*, vol. 34, no. 1, pp. 129–131, Jan. 2013.

- [5] Jae Sang Lee, Seongpil Chang, Sang-Mo Koo, and Sang Yeol Lee, "High-Performance a-IGZO TFT With ZrO2 Gate Dielectric Fabricated at Room Temperature," *IEEE Electron Device Lett.*, vol. 31, no. 3, pp. 225– 227, Mar. 2010.

- [6] J.-S. Park, J. K. Jeong, Y.-G. Mo, H. D. Kim, and S.-I. Kim, "Improvements in the device characteristics of amorphous indium gallium zinc oxide thin-film transistors by Ar plasma treatment," *Appl. Phys. Lett.*, vol. 90, no. 26, p. 262106, 2007.

- [7] D. Braga and G. Horowitz,

"High-Performance organic field-effect transistors," *Advanced Materials*, vol. 21, no. 14–15. pp. 1473–1486, 2009.

- [8] X. Guo and S. R. P. Silva, "ENGINEERING: High-Performance Transistors by Design," *Science (80-. ).*, vol. 320, no. 5876, pp. 618– 619, May 2008.

- [9] C. Dimitrakopoulos and P. Malenfant,

"Organic thin film transistors for large area electronics," *Adv. Mater.*, vol. 14, no. 2, pp. 99–117, 2002.

- [10] S.-J. Kim, S.-Y. Lee, Y. W. Lee, S.-H. Kuk, J.-Y. Kwon, and M.-K. Han, "Effect of Charge Trapping/Detrapping on Threshold Voltage Shift of IGZO TFTs under AC Bias Stress," *Electrochem. Solid-State Lett.*, vol. 15, no. 4, p. H108, 2012.

- [11] A. a. Fomani and A. Nathan, "Metastability mechanisms in thin film transistors quantitatively resolved using post-stress relaxation of threshold voltage," *J. Appl. Phys.*, vol. 109, no. 8, p. 084521, 2011.

- M. J. Powell, "The physics of amorphous-silicon thin-film transistors," *IEEE Trans. Electron Devices*, vol. 36, no. 12, pp. 2753–2763, 1989.

- [13] H. Klauk, G. Schmid, W. Radlik, W. Weber, L. S. Zhou, C. D. Sheraw, J. A. Nichols, and T. N. Jackson, "Contact resistance in organic thin film transistors," *Solid-State Electron.*, vol. 47, pp. 297–301, 2003.

- [14] P. V Necliudov, M. S. Shur, D. J. Gundlach, and T. N. Jackson, "Contact resistance extraction in pentacene thin film transistors," *Solid. State. Electron.*, vol. 47, no. 2, pp. 259– 262, Feb. 2003.

- [15] R. B. M. Cross and M. M. De Souza,

"Investigating the stability of zinc oxide thin film transistors," *Appl. Phys. Lett.*, vol. 89, no. 26, p. 263513, 2006.

- [16] A. Suresh and J. F. Muth, "Bias stress stability of indium gallium zinc oxide channel based transparent thin film transistors," *Appl. Phys. Lett.*, vol. 92, no. 3, p. 033502, 2008.

- [17] Y. Qiu, Y. Hu, G. Dong, L. Wang, J. Xie, and Y. Ma, "H[sub 2]O effect on the stability of organic thin-film field-effect transistors," *Appl. Phys. Lett.*, vol. 83, no. 8, p. 1644, 2003.

- [18] M. J. Powell, C. van Berkel, and J. R. Hughes, "Time and temperature dependence of instability mechanisms in amorphous silicon

thin-film transistors," *Appl. Phys. Lett.*, vol. 54, no. 14, p. 1323, 1989.

- [19] K. H. Ji, J.-I. Kim, Y.-G. Mo, J. H. Jeong, S. Yang, C.-S. Hwang, S.-H. K. Park, M.-K. Ryu, S.-Y. Lee, and J. K. Jeong, "Comparative Study on Light-Induced Bias Stress Instability of IGZO Transistors With SiNx and SiO2," *IEEE Electron Device Lett.*, vol. 31, no. 12, pp. 1404–1406, Dec. 2010.

- [20] H. Marien, M. Steyaert, E. van Veenendaal, and P. Heremans, "Analog techniques for reliable organic circuit design on foil applied to an 18dB single-stage differential amplifier," *Org. Electron.*, vol. 11, no. 8, pp. 1357–1362, Aug. 2010.

- [21] S. Jeon, S.-E. Ahn, I. Song, C. J. Kim, U.-I. Chung, E. Lee, I. Yoo, A. Nathan, S. Lee, J. Robertson, and K. Kim, "Gated three-terminal device architecture to eliminate persistent photoconductivity in oxide semiconductor photosensor arrays," *Nat. Mater.*, vol. 11, no. 4, pp. 301–305, 2012.

- [22] S. Sambandan, "High-gain amplifiers with amorphous-silicon thin-film transistors," *IEEE Electron Device Lett.*, vol. 29, pp. 882– 884, 2008.

- [23] P. Bahubalindruni, V. G. Tavares, P. G. De Oliveira, P. Barquinha, R. Martins, and E. Fortunato, "High-gain amplifier with n-type transistors," 2013 IEEE Int. Conf. Electron Devices Solid-State Circuits, EDSSC 2013, vol. 2, no. 2, 2013.

- Y.-C. Tarn, P.-C. Ku, H.-H. Hsieh, and L.-H. Lu, "An Amorphous-Silicon Operational Amplifier and Its Application to a 4-Bit Digital-to-Analog Converter," *IEEE J. Solid-State Circuits*, vol. 45, no. 5, pp. 1028–1035, May 2010.

- [25] L. L. Li, H. Marien, J. Genoe, M. Steyaert, and P. Heremans, "Compact Model for Organic Thin-Film Transistor," *IEEE Electron Device Lett.*, vol. 31, no. 3, pp. 210– 212, 2010.

- [26] S. Lee, S. Jeon, R. Chaji, and A. Nathan, "Transparent semiconducting oxide technology for touch free interactive flexible displays," *Proc. IEEE*, vol. 103, no. 4, pp. 644–664, 2015.

- [27] X. Cheng, S. Lee, G. Yao, and A. Nathan, "TFT Compact Modelling," J. Disp. Technol., pp. 1–1, 2016.

- [28] A. Valletta, A. S. Demirkol, G. Maira, M. Frasca, V. Vinciguerra, L. G. Occhipinti, L. Fortuna, L. Mariucci, and G. Fortunato, "A compact Spice model for organic TFTs and applications to logic circuit design," in 2015 IEEE 15th International Conference on Nanotechnology (IEEE-NANO), 2015, pp. 1434–1437.

- [29] O. Marinov, M. J. Deen, U. Zschieschang, and H. Klauk, "Organic thin-film transistors: Part I-compact DC modeling," *IEEE Trans. Electron Devices*, vol. 56, no. 12, pp. 2952– 2961, 2009.

- [30] M. Shur, M. Hack, and J. G. Shaw, "A new analytic model for amorphous silicon thin-film transistors," *J. Appl. Phys.*, vol. 66, no. 7, p. 3371, 1989.

- [31] P. V. Necliudov, M. S. Shur, D. J. Gundlach, and T. N. Jackson, "Modeling of organic thin film transistors of different designs," *J. Appl. Phys.*, vol. 88, no. 11, p. 6594, 2000.

- [32] G. R. Chaji, S. Alexander, J. Marcel Dionne, Y. Azizi, C. Church, J. Hamer, J. Spindler, and A. Nathan, "Stable RGBW AMOLED display with OLED degradation compensation using electrical feedback," *Dig. Tech. Pap. - IEEE Int. Solid-State Circuits Conf.*, vol. 53, no. 3, pp. 118–119, 2010.

- [33] J. K. Jeong, J. H. Jeong, J. H. Choi, J. S. Im, S. H. Kim, H. W. Yang, K. N. Kang, K. S. Kim, T. K. Ahn, H.-J. Chung, M. Kim, B. S. Gu, J.-S. Park, Y.-G. Mo, H. D. Kim, and H. K. Chung, "3.1: Distinguished Paper: 12.1-Inch WXGA AMOLED Display Driven by Indium-Gallium-Zinc Oxide TFTs Array," *SID Symp. Dig. Tech. Pap.*, vol. 39, no. 1, p. 1, 2008.

- [34] J.-H. Lee, W.-J. Nam, S.-H. Jung, and M.-K. Han, "A New Current Scaling Pixel Circuit for AMOLED," *IEEE Electron Device Lett.*, vol. 25, no. 5, pp. 280–282, May 2004.

- [35] M. Bagheri, X. Cheng, J. Zhang, S. Lee, S. Ashtiani, and A. Nathan, "Threshold Voltage Compensation Error in Voltage Programmed AMOLED Displays," *J. Disp. Technol.*, no. 2, pp. 1–1, 2016.

- [36] S. Lee and A. Nathan, "Conduction Threshold in Accumulation-Mode InGaZnO Thin Film Transistors," *Sci. Rep.*, vol. 6, no. October 2015, p. 22567, 2016.

- [37] A. Nathan, G. R. Chaji, and S. J. Ashtiani,

"Driving schemes for a-Si and LTPS AMOLED displays," *IEEE/OSA J. Disp. Technol.*, vol. 1, no. 2, pp. 267–277, 2005.

- [38] Y. C. Lin, H.-P. D. Shieh, and J. Kanicki, "A Novel Current-Scaling a-Si:H TFTs Pixel Electrode Circuit for AM-OLEDs," *IEEE Trans. Electron Devices*, vol. 52, no. 6, pp. 1123–1131, Jun. 2005.

- [39] Y.-C. Lin and H.-P. D. Shieh, "A Novel Current Memory Circuit for AMOLEDs," *IEEE Trans. Electron Devices*, vol. 51, no. 6, pp. 1037–1040, Jun. 2004.

- [40] M. Ohta, H. Tsutsu, H. Takahara, I.

Kobayashi, T. Uemura, and Y. Takubo, "9.4: A Novel Current Programmed Pixel for Active Matrix OLED Displays," *SID Symp. Dig. Tech. Pap.*, vol. 34, no. 1, p. 108, 2003.

- [41] T. Sasaoka, M. Sekiya, A. Yumoto, J. Yamada, T. Hirano, Y. Iwase, T. Yamada, T. Ishibashi, T. Mori, M. Asano, S. Tamura, and T. Urabe, "24.4L: Late-News Paper: A 13.0-inch AM-OLED Display with Top Emitting Structure and Adaptive Current Mode Programmed Pixel Circuit (TAC)," *SID Symp. Dig. Tech. Pap.*, vol. 32, no. 1, p. 384, 2001.

- [42] S. J. Ashtiani, P. Servati, D. Striakhilev, and A. Nathan, "A 3-TFT Current-Programmed Pixel Circuit for AMOLEDs," *IEEE Trans. Electron Devices*, vol. 52, no. 7, pp. 1514– 1518, Jul. 2005.

- [43] K. Sakariya, P. Servati, and A. Nathan,

"Stability Analysis of Current Programmed a-Si:H AMOLED Pixel Circuits," *IEEE Trans. Electron Devices*, vol. 51, no. 12, pp. 2019–2025, Dec. 2004.

- [44] J. Yamashita, K. Uchino, T. Yamamoto, T. Sasaoka, and T. Urabe, "44.2: New Driving Method with Current Subtraction Pixel Circuit for AM-OLED Displays," *SID Symp. Dig. Tech. Pap.*, vol. 36, no. 1, p. 1452, 2005.

- [45] G. R. Chaji and A. Nathan, "Low-Power Low-Cost Voltage-Programmed a-Si:H AMOLED Display for Portable Devices," *J*.

*Disp. Technol.*, vol. 4, no. 2, pp. 233–237, Jun. 2008.

- [46] S.-H. Jung, W.-J. Nam, and M. Han, "P-104: A New Voltage Modulated AMOLED Pixel Design Compensating Threshold Voltage Variation of Poly-Si TFTs," *SID Symp. Dig. Tech. Pap.*, vol. 33, no. 1, p. 622, 2002.

- [47] Joon-Chul Goh, Hoon-Ju Chung, Jin Jang, and Chul-Hi Han, "A new pixel circuit for active matrix organic light emitting diodes," *IEEE Electron Device Lett.*, vol. 23, no. 9, pp. 544–546, Sep. 2002.

- [48] S.-M. Choi, O.-K. Kwon, and H.-K. Chung, "P-11: An Improved Voltage Programmed Pixel Structure for Large Size and High Resolution AM-OLED Displays," *SID Symp. Dig. Tech. Pap.*, vol. 35, no. 1, p. 260, 2004.

- [49] Jae-Hoon Lee, Ji-Hoon Kim, and Min-Koo Han, "A new a-Si:H TFT pixel circuit compensating the threshold voltage shift of a-Si:H TFT and OLED for active matrix OLED," *IEEE Electron Device Lett.*, vol. 26, no. 12, pp. 897–899, Dec. 2005.

- [50] Y.-H. Tai, B.-T. Chen, Y.-J. Kuo, C.-C. Tsai, K.-Y. Chiang, Y.-J. Wei, and H.-C. Cheng, "A New Pixel Circuit for Driving Organic Light-Emitting Diode With Low Temperature Polycrystalline Silicon Thin-Film Transistors," *J. Disp. Technol.*, vol. 1, no. 1, pp. 100–104, Sep. 2005.

- [51] Y. Matsueda, R. Kakkad, Y. S. Park, H. H. Yoon, W. P. Lee, J. B. Koo, and H. K. Chung, "35.1: 2.5-in. AMOLED with Integrated 6-Bit Gamma Compensated Digital Data Driver," *SID Symp. Dig. Tech. Pap.*, vol. 35, no. 1, p. 1116, 2004.

- [52] C.-L. Lin and T.-T. Tsai, "A Novel Voltage Driving Method Using 3-TFT Pixel Circuit for AMOLED," *IEEE Electron Device Lett.*, vol. 28, no. 6, pp. 489–491, Jun. 2007.

- [53] J. L. Sanford and F. R. Libsch, "4.2: TFT AMOLED Pixel Circuits and Driving Methods," *SID Symp. Dig. Tech. Pap.*, vol. 34, no. 1, p. 10, 2003.

- [54] M. Bagheri, S. Ashtiani, and A. Nathan, "Fast voltage-programmed pixel architecture for AMOLED displays," *J. Disp. Technol.*, vol. 6, no. 5, pp. 191–195, 2010.

- [55] H. J. In and O. K. Kwon, "External compensation of non-uniform electrical characteristics of thin-film transistors and degradation of OLED devices in AMOLED displays," *IEEE Electron Device Lett.*, vol. 30, no. 4, pp. 377–379, 2009.

- [56] S. Jafarabadiashtiani, G. Chaji, S. Sambandan, D. Striakhilev, A. Nathan, and P. Servati, "P-25: A New Driving Method for a-Si AMOLED Displays Based on Voltage Feedback," *SID Symp. Dig. Tech. Pap.*, vol. 36, no. 1, p. 316, 2005.

- [57] J. H. Baek, M. Lee, J. H. Lee, H. S. Pae, C. J. Lee, J. T. Kim, C. S. Choi, H. K. Kim, T. J. Kim, and H. K. Chung, "A Current-Mode Display Driver IC Using Sample-and-Hold Scheme for QVGA Full-Color AMOLED Displays," *IEEE J. Solid-State Circuits*, vol. 41, no. 12, pp. 2974–2982, Dec. 2006.

- [58] S. J. Ashtiani and A. Nathan, "A Driving Scheme for Active-Matrix Organic Light-Emitting Diode Displays Based on Current Feedback," J. Disp. Technol., vol. 5, no. 7, pp. 257–264, Jul. 2009.

- [59] H.-J. In, P.-S. Kwag, J.-S. Kang, O.-K. Kwon, and H.-K. Chung, "Voltage-programming method with transimpedance-feedback technique for threshold voltage and mobility compensations in large-area high-resolution AMOLED displays," *J. Soc. Inf. Disp.*, vol. 14, no. 8, p. 665, 2006.

- [60] H.-J. In, B.-D. Choi, H.-K. Chung, and O.-K. Kwon, "Current-Sensing and Voltage-Feedback Driving Method for Large-Area High-Resolution Active Matrix Organic Light Emitting Diodes," *Jpn. J. Appl. Phys.*, vol. 45, no. 5B, pp. 4396–4401, May 2006.

- [61] R. Itou, M. Kayama, and T. Shima, "Some analog building blocks for TFT circuits," in Proceedings of the 44th IEEE 2001 Midwest Symposium on Circuits and Systems. MWSCAS 2001 (Cat. No.01CH37257), 2001, vol. 1, pp. 417–420.

- [62] A. S. Sedra and K. C. Smith, *Microelectronic circuits*, 6th ed. New York Oxford University Press, 2011.

# > REPLACE THIS LINE WITH YOUR PAPER IDENTIFICATION NUMBER (DOUBLE-CLICK 14 HERE TO EDIT) <

- [63] P. R. Gray, P. Hurst, R. G. Meyer, and S. Lewis, *Analysis and design of analog integrated circuits*. Wiley, 2001.

- [64] R. Gregorian and G. C. Temes, Analog MOS Integrated Circuits for Signal Processing, 1st ed. New York: Wiley-Interscience, 1986.

- [65] Y. P. Tsividis, D. L. Fraser, and J. E. Dziak,

"A process-insensitive high-performance NMOS operational amplifier," *IEEE J. Solid-State Circuits*, vol. 15, no. 6, pp. 921– 928, Dec. 1980.

- [66] D. Senderowicz, D. A. Hodges, and P. R. Gray, "High-performance NMOS operational amplifier," *IEEE J. Solid-State Circuits*, vol. 13, no. 6, pp. 760–766, Dec. 1978.

- [67] M. J. Seok, M. H. Choi, M. Mativenga, D. Geng, D. Y. Kim, and J. Jang, "A Full-Swing a-IGZO TFT-Based Inverter With a Top-Gate-Bias-Induced Depletion Load," *IEEE Electron Device Lett.*, vol. 32, no. 8, pp. 1089–1091, Aug. 2011.

- [68] B. Kim, C.-I. Ryoo, S.-J. Kim, J.-U. Bae, H.-S. Seo, C.-D. Kim, and M.-K. Han, "New Depletion-Mode IGZO TFT Shift Register," *IEEE Electron Device Lett.*, vol. 32, no. 2, pp. 158–160, Feb. 2011.

- [69] D. P. Heineck, B. R. McFarlane, and J. F. Wager, "Zinc Tin Oxide Thin-Film-Transistor Enhancement/Depletion Inverter," *IEEE Electron Device Lett.*, vol. 30, no. 5, pp. 514– 516, May 2009.