# Formal Verification of Timed Systems: A Survey and Perspective

# FARN WANG

# Invited Paper

An overview of the current state of the art of formal verification of real-time systems is presented. We discuss commonly accepted models, specification languages, verification frameworks, state-space representation schemes, state-space construction procedures, reduction techniques, pioneering tools, and finally some new related issues. We also make a few comments according to our experience with verification tool design and implementation.

**Keywords**—Embedded systems, formal methods, formal verification, models, real-time systems, specification, temporal logics, theory, tools.

#### I. INTRODUCTION

Real-time systems differ from untimed systems in that their behavioral correctness relies not only on the results of their computations, but also on the clock times when the results are produced. Formal verification means to rigorously explore the correctness of system designs expressed as mathematical models, most likely with the assistance of modern computers. From our viewpoint, there have been the following three motivations for the heated research on the formal verification of real-time systems in the last two decades.

With the success of formal verification in the very large scale integration (VLSI) industry [53], it is natural to expect that similar success can be repeated in the formal verification of real-time systems. In particular, the achievement of binary decision diagram (BDD) technology [52] has raised the hopes and confidence of the industry for the verification of real-time systems.

Manuscript received November 15, 2003; revised April 19, 2004. This work was supported in part by the National Science Council (NSC) of Taiwan, R.O.C., under Grants NSC 92-2213-E-002-103 and NSC 92-2213-E-002-104, and in part by the System Verification Technology Project of the Industrial Technology Research Institute, Taiwan, R.O.C.

The author is with the Department of Electrical Engineering, National Taiwan University, Taipei 106, Taiwan, R.O.C. (e-mail: farn@cc.ee.ntu.edu.tw).

Digital Object Identifier 10.1109/JPROC.2004.831197

- With the readiness of concrete theoretical frameworks for the verification of real-time systems [5], [11], [113], [127]–[129], [133], [197], both programmers and theoreticians are eager to see how the theory adapts to real-world projects.

- With the increasing scope and complexity of embedded systems and resulting state-space explosion, it is becoming less and less likely that we can run a sufficient number of simulation traces to gain both enough coverage of the state spaces and enough confidence in the systems with a project schedule. Further, even if it were feasible to have extensive coverage of the system, the potential of a single untested sequence of events that no one thought of to cause system failure is also of concern.

In the last two decades, many achievements in the formal verification of real-time systems have been reported, from various solid theory foundations to complex implementation techniques and formal verification of many real-world projects [37], [189], [203], [206]. Still the intrinsic complexity of various framework for real-time system verification is forbiddingly high. The verification problems of timed systems are usually exponentially more complex than their untimed counterparts. For example, the model-checking problem of computation tree logic (CTL) is in PTIME<sup>1</sup> [60], [61], while that of timed CTL (TCTL) is in PSPACE<sup>2</sup> [5]. Thus, in the foreseeable future, it will be difficult to use formal techniques alone for decisive answers to complex verification tasks.

But this does not mean that we are pessimistic about the future of formal verification. On the contrary, with most major projects currently spending over 50% of their development costs in verification and integration, there are tremendous opportunities for using formal verification to sizably reduce the

<sup>1</sup>PTIME problems can be solved with time complexity polynomials to the input sizes in bit counts.

<sup>2</sup>PSPACE problems may incur memory consumption polynomials to the input sizes in bit counts.

0018-9219/04\$20.00 © 2004 IEEE

explosive growth of verification and integration costs and to enhance the quality of system designs in industry. On the one hand, for complex real-time systems, formal verification will likely be used to enhance the intelligence and performance of simulation and testing. For example, coverage metrics can be more precisely mapped to the functions to be verified. On the other hand, for targets with clean modularity and interface, formal verification can be used to rigorously check the components and the interfaces and gradually could be accepted as standard methods in the automation of industrial quality control. Actually it is claimed that this latter approach has already had a dramatic effect on the SLAM project of Microsoft, which plans to incorporate model-checking capability in its Windows driver development kit (DDK) [34].

In this paper, we give a review of these many achievements so that readers can use the paper as an index to the literature. We organize the paper according to the various research topics in formal verification, including models in Section II, description and specification languages in Section III, verification frameworks in Section IV, representation of state space in Section V, constructions of state-space representations in Section VII, some tools in Section VIII, and some other issues in Section IX, including symbolic simulation, parametric analysis, controller synthesis, probabilistic analysis, and worst case execution time (WCET) analysis.

There are many frameworks to choose from to complete a verification task. Each framework has its unique advantage and may incur an intrinsic challenge. We feel it is better to let the readers be informed of the challenges in the verification frameworks of his/her choice. Thus we have cited many complexity results of various verification problems in the paper. Complexity of a verification problem means the order of growth of required resources to solve the problem with respect to the input sizes in bit counts. The resources can be CPU times, memory space, message counts, power consumption, etc. But in this paper, we are mainly concerned with CPU times and memory space. Some jargon of the complexity classes includes *PTIME*, *NP-complete*, *PSPACE*, *EXPTIME*, *4 EXPSPACE*, *5 nonelementary complexities*, <sup>6</sup> and *undecidability*.

Heitmeyer and Mandrioli have also written a handbook on formal verification techniques for real-time computing [106]. Regarding techniques for untimed systems, a classic book is one by Clarke *et al.* [65]. A previous survey paper in this regard is by Ostroff [179].

<sup>3</sup>NP problems means that we can guess a solution in time complexity polynomials to the input sizes. NP-complete problems are the hardest ones in NP and are in general considered untamable problems in computer sciences.

<sup>4</sup>EXPTIME problems consume CPU times exponential to the sizes of inputs in bit counts.

<sup>5</sup>EXPSPACE is the set of problems that at most consume memory capacity exponential to the input sizes in bit counts. EXPSPACE-complete problems are harder than EXPTIME problems.

$^6$ Nonelementary complexities are like  $2^{2^*}$  with the heights of the exponent stacks at least proportional to the input sizes in bit counts.

<sup>7</sup>Undecidable problems do not guarantee termination. In general, it is not possible to design algorithms (procedures that guarantee termination) for undecidable problems.

Before you go on, we remind you that the paper may show the author's intentional or unconscious bias toward each approach in formal verification. After all, the amount of space needed to explain the details of each subfield is a subjective decision.

## II. Models

Formal verification grows from formal or mathematical logics [41], in which we discuss the grammar (syntax) and meaning (semantics) of logic formulas. It is possible to associate the same grammar with different styles of meaning. The meaning of a logic formula is defined as a set of *models*. A *model* in mathematical logic is a domain of values and some functions on the domain. Without such formal definitions, rigorous and mechanical verification of real-time systems will be impossible.

Intuitively, in the forum of specification and verification, a model is a behavior of a system description (or specification). According to the various frameworks we use, a model for a real-time system can be a state set, a state sequence, an event sequence, a state tree, or an infinite domain with relations. Some other possibilities can also be found in [80].

# A. Linear Time Versus Branching Time

We can view a computation either as a linear sequence with only one future or as a tree with many possible futures. The former is called *linear-time semantics* [185], while the latter is called *branching-time semantics* [60], [61].

Linear-Time Temporal Logics: The research on automatic verification of computer programs was initiated when Pnueli proposed using linear-time propositional temporal logic (LPTL) [185] to specify and compute the behaviors of computer systems. LPTL is a subclass of modal logic [41] with possible-world semantics and modal operators: □ (for all possible worlds) and ◊ (there exists a possible world). In LPTL, □ is interpreted as "from now on, at all states" (or henceforth, always), while ◊ is interpreted as "from now on, there exists a state" (or eventually). For example, we may have the model of a railroad crossing system. approaching and down are two atomic propositions, and we want to specify that whenever an approaching train is detected, from that state on, eventually the gate is down. In LPTL, this can be expressed as

$\square$ (approaching  $\rightarrow \lozenge$ down).

Two other commonly used modal operators are  $\bigcirc$  (next) and  $\mathcal{U}$  (until).  $\bigcirc p$  means that p is true in the next state.  $p\mathcal{U}q$  means that p is true until q is true.

In defining logics, people usually try to use minimal syntax structures. Usually  $\Diamond p$  and  $\Box p$  can be defined as the shorthands for true  $\mathcal{U}p$  and  $\neg \Diamond \neg p$ , respectively. On the other hand, Kamp showed that  $p\mathcal{U}q$  cannot be modeled with modal operators  $\Box$ ,  $\Diamond$ , and  $\bigcirc$  [131].

In the late 1980s, people added the concept of "clock time" to LPTL. That is, a global clock is assumed in the model such that the global clock does not have to increment its reading

at every state. Initially, Ostroff [178] discussed issues in expressiveness and complexity with quantification and linear constraints of clock readings in LPTL. For example, we may write

$$\forall x \exists y \Box \bigg( (T = x \land \text{approaching}) \\ \rightarrow \Diamond (T = y \land y - x \le 300 \land \text{down}) \bigg). \tag{1}$$

Here T is the special variable for the reading of the global clock at the current state.

Alur and Henzinger proposed *timed propositional temporal logic (TPTL)* [15]. TPTL has a clock-reading freezing modal operator and uses binary difference constraints between frozen clock readings. The intuition is that quantifications on clock readings following  $\square$  are universal, while the ones following  $\lozenge$  are existential. For example, we may write

$$\Box x. (approaching \rightarrow \Diamond y. (y - x \le 300 \land down))$$

(2)

which means that the gate will be down in 300 s from any state in mode approaching. Note that this formula specifies something different from (1). In (1), time y is independent of the states quantified by the modal operator  $\square$ , while in (2), it is not.

Alur and Henzinger also defined *metric temporal logic* (MTL), which allows the specification of timing distances between states quantified by adjacent modal operators [16]. For example, we may write

$$\square(\text{approaching} \rightarrow \lozenge_{\leq 300} \text{down})$$

to specify the same property as (2). A nice exploration of various discrete-time extensions of LPTL is [16].

In 1992, Wang *et al.* extended TPTL to *Asynchronous PTL (APTL)* for distributed systems with clock jitters [228]. Specifically, they redefine the semantics of clock differences in distributed systems with a timing precedence relation. The idea is that instead of comparing the values of clock readings, we now compare the temporal precedence of clock readings. For example, we may write  $\Box[x,y]x+2 \lhd y+1$ , which means that we have two distributed clocks such that at every state, if the reading of the two clocks are x and y, respectively, then every second tick of the first clock must precede the next tick of the second clock. Putting it another way, for every tick of clock 2, clock 1 will tick at least twice.

Branching-Time Temporal Logics: The intuition behind linear-time logics is that there is only one future. With branching-time logics, the possibility of many futures is assumed, and modal operators  $\exists$ ,  $\forall$  are provided to specify the relation among different futures. Path quantifier  $\exists$  means "there exists a run from now on" and  $\forall$  means that "for all runs from now on." For example, in CTL [60], [61]

$$\forall \Box (approaching \rightarrow \forall \Diamond down)$$

means that whenever the monitor is in mode approaching, along all runs henceforth, the gate will eventually be closed. Note that in CTL and its extensions, linear-time modal operators  $(\Box, \Diamond, \mathcal{U}, \bigcirc)$  must immediately follow a path quantifier

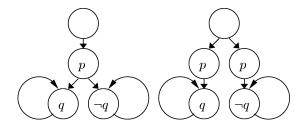

Fig. 1. Two behaviors that CTL can differentiate.

$(\exists, \forall)$ . In the literature of CTL, modal operators  $\exists, \forall, \Box, \Diamond$ ,  $\mathcal{U}$ , and  $\bigcirc$  are written as E, A, G, F, U, and X, respectively.

In semantics, an LPTL formula defines a set of linear state sequences, while a CTL formula defines a set of computation trees. CTL and LPTL are not comparable in expressiveness. For example, the LPTL formula  $\Box \Diamond p$  says p states happen infinitely many times. Also, the *nonZeno* requirement [113] in TPTL is  $\Box x. \Diamond x > 1$ . These properties are known to be inexpressible in the timed extensions of CTL. On the other hand, CTL allows for the reasoning of properties between possible future behaviors. For example, the CTL formula

$$\forall \Box \left( p \to ((\exists \bigcirc q) \land (\exists \bigcirc \neg q)) \right)$$

can differentiate the two behaviors in Fig. 1, while no LPTL formula can.

Emerson *et al.* proposed *real-time CTL (RTCTL)* [83], which uses formulas like  $\exists \neg p \mathcal{U}^{\leq k} p$  to specify the existence of a state sequence along which p becomes true within the next k states. This type of property is suitable for cycle-based systems like VLSI, in which the discrete global clock ticks at every discrete state change [83].

Harel *et al.* [104] discussed the expressiveness and complexity of the CTL extension with universally quantified clock variables and arbitrary linear clock constraints.

The most used branching-time temporal logic for real-time systems is TCTL [5], which supports modal operators like  $\exists \Box_{\sim c}, \exists \Diamond_{\sim c}, \exists \mathcal{U}_{\sim c}, \forall \Box_{\sim c}, \forall \Diamond_{\sim c}$ , and  $\forall \mathcal{U}_{\sim c}$ . Here c is a natural number and  $\sim$  is one of  $\leq$ , <, =, >, or  $\geq$ . For example

$$\forall \Box (approaching \rightarrow \forall \Diamond <_{300} down)$$

means that whenever the monitor is in mode approaching, along all runs henceforth, the gate will be closed in 300 s.

Beside its modality, TCTL also differs from TPTL and the like in that TCTL is defined with dense-time clock models. Thus, there is no modal operator involving ().

Integration of Linear Time and Branching Time: Emerson and Halpern defined a unified specification language, called  $CTL^*$ , for both LPTL and CTL [81]. Remember that in CTL, we require that linear-time modal operators must immediately follow path quantifiers. If this restriction is lifted in CTL, then we get CTL\*. Regarding LPTL, each LPTL formula specifies the set of linear sequences satisfying it. Thus, intuitively, LPTL is a subclass of CTL\* because every LPTL formula implicitly carries a universal quantifier on all computation sequences. That is, an LPTL formula  $\phi$  characterizes the same set of state sequences as the CTL\* formula  $\forall \phi$ .

It is also natural to extend CTL\* to TCTL\*. Möller discussed how to model check a subclass of TCTL\* [167]. Wang carried out experiments using model-checking algorithms on the subclass of TCTL\* which contains fairness assumptions [220].

# B. Discrete Time Versus Dense Time

In the definition of real-time system models, we can require that all time readings are integers and all clocks increment their readings at the same time. This is discrete-time semantics [15], [127]. The other choice is dense-time semantics [11], [78], which means that time readings can be rationals or reals and all clocks increment their readings at a uniform rate.

Discrete-time models are suitable for synchronous systems where all concurrent processes share the same global clock. Example languages are TPTL and MTL [16]. Densetime models are better for distributed systems with multiple clocks and timers, which can be tested, set, and reset independently. Examples include TCTL [5].

Note that in our explanation of discrete-time models, we require that there is a single global clock. It may seem that such a requirement is inappropriate for distributed systems with digital clocks. In fact, after the sampling or detection of an event in an embedded system, the occurrence time of the event is still stored in a digital format. Thus, philosophically, discrete-time semantics with distributed clocks seems a plausible choice. But in general, if the clocks are distributed and do not increment their readings at the same time, then we still have to implicitly record the ticking order of the clocks so that the clocks still increment their readings at the same rate. The information pieces of ticking orders are of factorial complexity, which is the same as that of region graph construction for dense-time models [5], and do not save any computation resources. Henzinger et al. discussed the relation between systems with distributed digital clocks and those with distributed dense clocks [112].

Clock-reading models can also affect the verification complexity. For example, the satisfiability problem of TPTL is in EXPSPACE, while its dense-time version is undecidable. Intuitively, discrete-time models may lead to lower complexity in verification and analysis, since there are many fewer states. But in practice, the impact on complexity is tricky. Specifically, with the symbolic techniques for timed and hybrid systems [18], [113], state spaces are represented as Boolean combinations of linear constraints of state variables. An important operation is checking the emptiness of state-space representations. However, the emptiness problem of linear constraints is in PTIME for reals (in dense-time models) and NP-complete for integers (in discrete-time models).

## C. State Based Versus Event Driven

A state is a snapshot of a system at a moment in time. In the sense of control, it is everything that we need to know about the system at that moment in order to determine the future for all future input sequences. Mathematically, it consists of the recording of the values of all variables and control locations. For instance, at a railroad crossing, the variable gate can be used for the gate position of the present state. State-based real-time temporal logics are usually derived from their untimed counterparts [60], [61], [185]. Examples include TCTL [5], RTCTL [83], TPTL, MTL [16], and APTL [228].

An event represents an instantaneous change of states and may trigger a series of responses in a system. For example, the detection of an approaching train at a railroad crossing is an event that will hopefully cause the gate to close. Event-driven system descriptions are very natural in the world of embedded system engineering. One pioneering work that incorporates timed events into the linear-time model is *real-time logic (RTL)* by Jahanian and Mok [127]. RTL is a linear-time event-driven logic with event occurrence-time functions. For example, we may write

$$\forall i \, (\text{approaching}(i) + 300 \ge \text{down}(i))$$

which means that after the ith train approaching event has occurred, the ith gate down event must happen in 300 s. RTL is a subclass of first-order integer arithmetic with monadic functions. Yang  $et\ al.\ [233]$  have also designed a temporal logic, synchronous real-time event logic (SREL), based on event countings along state sequences in a discrete-time domain.

One thing to note is that in synchronous cycle-based systems, e.g., VLSI circuits, people usually treat state and event as the same thing, since variables change values only at the beginning of each clock cycle and then remain steady in the cycle. But for distributed real-time systems, this treatment may lead to imprecise modeling, since there is no common clock among the many distributed sites.

It also has long been argued that neither pure state-based nor pure event-based languages quite support the natural expressiveness desirable for the specification of real-world systems [57], [122], [134], [137], [174]. Recently, Wang has proposed an extension to TCTL for the specification and model checking of behaviors involving both states and events with fairness assumptions [220]. For example, in the railroad crossing system, we may want to say that when the monitor signals the controller to lower the gate, then the gate must be down in 300 s. This can be specified as  $\forall \Box^{\log \text{er}} \geq 1 \forall \lozenge_{\leq 300} \text{down}$ . Here  $\Box^{\epsilon \geq c} p$  means that whenever c events of type  $\epsilon$  happen, p must immediately be true.

## III. DESCRIPTION AND SPECIFICATION LANGUAGES

#### A. Timed Automata

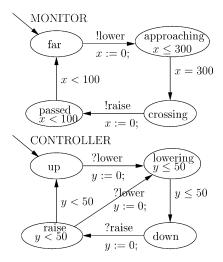

The model of *timed automata* was first proposed by Alur and Dill [11]. A timed automaton is a finite-state automaton equipped with a finite set of clocks which can hold nonnegative real values. It is structured as a directed graph whose nodes are *modes* (*control locations*) and whose arcs are *transitions*. The example of a monitor process for trains approaching a railroad crossing is in Fig. 2. The monitor is in mode *far* when all trains are far from the crossing, or in mode *approaching* when a train will arrive at the crossing within 300 s, or in mode *crossing* when a train is at the crossing, or in mode *passed* when trains have just left the crossing within

Fig. 2. The model of gate-monitor.

the last 100 s. The ovals represent modes, while the arcs represent transitions. The modes are labeled inside the ovals with *invariance conditions* which are Boolean conjunctions. All states in a mode must satisfy the corresponding invariance condition. At any moment, the timed automaton can reside in only one mode. The transitions are labeled with triggering conditions and a set of clocks to be reset during the transitions. A timed automaton can make a transition only if it satisfies the corresponding triggering condition. The invariance conditions and triggering conditions are Boolean combinations of clock (difference) inequalities. In a timed automaton's operation, one of the transitions can be triggered when the corresponding triggering condition is satisfied. Upon being triggered, the automaton instantaneously transits from one mode to another and resets some clocks to zero. In between transitions, all clocks increase their readings at a uniform rate.

A state of a timed automaton is a recording of its present mode and the readings of all clocks. With discrete-time models, all clocks will have integer readings and increment their readings at the same instant. With dense-time models, clock readings are reals (or rationals). A computation of a timed automaton can be defined as an infinite sequence of time-state pairs such that the time components form a nondecreasing and divergent real number sequence.

A timed automaton is a nondeterministic machine and does not have to make transitions as long as the invariance condition is satisfied. One usual way to force transitions is by using an invariance condition. For example, in Fig. 2, in the "approaching" mode, we require that  $x \leq 300$  to force the transition out of the mode in 300 time units.

In practice, a real-time system is usually described as a set of process timed automata, each representing the behavior of an autonomous process. Such a decomposition is natural in the description and construction of concurrent and distributed systems. By decomposing a timed automaton to a set of process automata, engineers can greatly simplify their tasks in the modeling of complex, concurrent behaviors. The timed automaton can be constructed as the product automaton of the process timed automata. The mode set of the product automaton is now the Cartesian product of the mode sets of the process timed automata. The invariance condition is defined by the conjunction of the invariance conditions of the modes of the process timed automata. The behavior of the product timed automaton is an interleaving of transitions of the process timed automata.

What makes timed automata interesting is that their model-checking problem is in PSPACE [5]. Moreover,

Fig. 3. The model of gate-monitor-controller.

under certain conditions, symbolic manipulation techniques for timed automata have performed well enough to verify many industrial systems [113].

## B. Communicating Timed Automata

Complex state transitions may require cooperation among processes to construct. For example, in the railroad crossing example, at the time when an approaching train is detected, the monitor sends a "signal" to the gate controller to move the gate down. Conceptually we can decompose the system into two processes: the train monitor and the gate controller. The sending and receiving of the signal can best naturally be modeled by the interaction between the monitor and the controller. There are also two process transitions involved in the behavior, i.e., the detection of the approaching train and the starting of the gate's moving down.

The first language device designed to "glue" process transitions into a (global) transition is the channel concept for binary synchronization in Hoare's Communicating Sequential Processes (CSP) [115]. Such a device can greatly help to improve the modularity of model descriptions. For example, in the embedded control system for a railroad crossing, we may have a channel called lower for the communication of the command to move the gate down. The language device !lower represents the sending (or output) event through the channel, while ?lower represents the receiving (or input) event through the same channel. Two process transitions labeled, respectively, with the sending event and receiving event through the same channel must happen at the same instant to make a legitimate global transition. The interactive synchronization between a train monitor and a gate controller can be modeled with the communicating timed automaton in Fig. 3. When the monitor detects that a train is approaching the railroad crossing, it sends out a signal through channel lower to the controller to move the gate down. A process transition with an input event that cannot find a peer process transition with matching output event simply cannot be executed.

CSP-style synchronization channels were incorporated in communicating real-time state machines (CRSM) [198] in

1992. Such devices are now supported in real-time system model-checkers like I/O automata [90], [133], [157], UP-PAAL [39], [183], SGM [120], [222], [223], and the region-encoding diagram (RED) [213], [216], [217], [219].

A similar synchronization device is used in HyTech [18] and Kronos [75], [237] with no distinction between senders and receivers. Each process is declared with the set of synchronizers to respond to. Then when a synchronizer happens, all processes declared to respond to it will have to make a process transition. Such a device is handy in modeling broadcasting, multicasting, and other multiparty synchronizations. For example, to model the bus collision behavior in carrier sense multiple access with collision detection (CSMA/CD) protocol [175], the bus process may execute a transition labeled with the event Collision Detected, which will force every sender process to respond to a transition with the same event. It is also possible to combine basic CSP-style binary synchronizations to construct such complex multiparty synchronizations. For example, in RED [219], to model the bus collision event in CSMA with n senders, the bus needs to execute a transition with n !Collision\_Detected labels, and, thus, forces each of the n senders to respectively respond with a transition with one ?Collision\_Detected label.

# C. Hybrid Automata

Hybrid automata [18], [108] are used to model embedded systems with continuous variables, whose values may increment/decrement at various rates. Arbitrary linear constraints are allowed for invariance conditions and triggering conditions. Timed automata [11] are a special subclass of hybrid automata in which all continuous variables increment their values at a uniform rate and only upper-bound and lower-bound inequalities of clocks are allowed. A hybrid automaton shares the same structure as timed automata, except that in each mode, the increment rate of each continuous variable is independently specified.

In general, hybrid automata are not subject to algorithmic verification, but there are subclasses which are [109].

## D. Logics

Logic formulas can also be used to describe system behavior. In such frameworks, the system descriptions (including the models for systems and environments) and the specifications are all put down in the same language. In its operation, a logic theory is defined by a set of axioms and inference rules. Every formula that can be constructed through repetitive applications of the inference rules is called a theorem. Two key issues are soundness and completeness. Soundness means that the theorems in the theory are consistent, i.e., do not contradict one another. Completeness means that every theorem can be proved in a finite number of steps of inference rule applications. When we use logics for verification, we usually put down the system description as axioms and inference rules and the specification formulas as a theorem. A proof plan may also involve several lemmas and corollaries as intermediate steps to the establishment of the goal theorem.

To know when to stop inferencing in case the specification formula is actually not a theorem, we need to prove a *small model theorem* to establish the maximum number of inference steps for the proof of the specification formula. The complexity of the verification procedure depends on the complexity of the small models.

Propositional temporal logics, linear time and branching time, have been discussed in Section II-A. The advantage of such frameworks is that they usually come with small model theorems and algorithms to check whether a formula is a theorem or not. The disadvantage is that they are usually not expressive enough to model complex behaviors with, for instance, queues, stacks, counters, range-unbounded variables, polynomial constraints, etc.

First-order and higher order logics have also been used [127], [197] for specification and verification. The advantage is that such logics are very expressive for modeling complex behaviors. The disadvantage is that in general, it is not possible to design algorithms to check whether a formula is a theorem or not.8 First-order logics seem a good compromise between expressiveness and computability, since they are complete in general. That is, we still have *semidecision* procedures that are guaranteed to construct proofs if the specification formulas are indeed theorems.

On the other hand, higher order logics [96], [181] are in general incomplete. Interested readers are referred to [176] for a tutorial on Isabelle/HOL. Mattolini and Nesi presented *temporal-interval logic with compositional operators (TILCO)* [161] with formal proof support from Isabelle/HOL.

## E. Timed Process Algebras

*Timed CSP* was first designed by Reed and Roscoe [188] and later modified by Davies and Schneider [74]. It supports the following three grammar rules with timing constraints:

Wait

$$t|P_1 \stackrel{t}{\triangleright} P_2|P_1 \stackrel{\downarrow}{t} P_2$$

.

"Wait t" means to wait for t time units.

$P_1 \stackrel{\iota}{\triangleright} P_2$  models the timeout in communication. It behaves as  $P_1$  until, at time t, when no synchronization has happened yet, the control is transferred to  $P_2$ .

$P_1 \stackrel{t}{t} P_2$  models the interrupt in embedded systems. It behaves as  $P_1$  until at time t, regardless of synchronizations, when control is transferred to  $P_2$ .

The time value domain in timed CSP is dense. A variety of semantics has been defined. The simplest one associates a program with a set of timed traces. Schneider wrote a book in this regard [194]. In the book, manual proofs are illustrated and a refinement relation from untimed CSP programs to timed CSP programs is presented. With the introduction of the event *tock*, which advances time by one unit, Schneider also showed how to translate timed CSP programs to untimed CSP programs with tock events.

Baeten et al. have done substantial work in extending the process algebra known as the algebra of communicating

<sup>8</sup>In the jargon of computer science, the *decision problems* of such logics are said to be *undecidable* or *incomputable*.

processes (ACP) to the real-time domain [30]–[32]. The time models can be dense or discrete. Both absolute time and relative times can be specified. Time-stamped actions can be used to combine actions with the passage of time. The integration operator  $\int_{v \in V} P$  allows composition over a continuum of alternatives. The initial abstraction operator  $\sqrt{v \cdot F(v)}$  defines a mapping from a parametric initial setting of real variable v to a set of processes, whose behaviors depend on the value of v.

Work on the *calculus of communicating systems (CCS)* with timing can be found in [59], [170], and [234].

Another timed extension of process algebra is PACSR [152], [184], which supports resource-awareness and probability reasoning in embedded system design.

LOTOS is an ISO standard specification language based on process algebra [43], [123]. Its real-time extension is called *Enhanced Timed-LOTOS (ET-LOTOS)* [124], [150], [151].

#### F. Timed Petri Nets

Petri nets [87], [130] are convenient for modeling concurrent systems. In a Petri net, we have places, which may hold tokens, and transitions, which may consume some tokens from the places and produce some other tokens in other places. A state of a Petri net is called a *marking*, which assigns a number of tokens to each place. Since each place can hold an unbounded number of tokens, Petri nets are infinite-state systems. One special thing about Petri nets is that they lack the capability to test the nonexistence of tokens. Specifically, a transition may happen if all its input places have tokens. But no action can be taken when there is no token in some input place. Theoretically, Petri nets are equivalent to *counter machines without zero-test capability* [97] and *vector addition systems* (VAS) [118], [132].

Several classes of timed extensions of Petri nets have been proposed [3], [42], [47], [93], [163], [187]. For example, Merlin and Faber defined time Petri nets, in which each transition is associated with a clock that records the time lapse since it was last enabled [163]. Clock readings can be natural numbers in discrete-time models or dense numbers in continuous-time models. State may change due to transitions and time passage. Each transition also has two attributes: earliest firing time (Eft) and latest firing time (Lft). An enabled transition can only fire when its clock reading is no less than its Eft, and if continuously enabled, it must be fired before its Lft. Thus, time may not increment beyond the minimum deadlines set by the Lft of all enabled transitions. This semantics that "some enabled transition must fire" is different from the nondeterministic semantics of timed automata, in which a continuously enabled transition does not have to be fired before the Lft.

Ghezzi *et al.* proposed another Petri net extension, called *Time Environment/Relation (ER) nets*, for timed systems [93]. Each token, instead of each transition, is associated with a time stamp. Transitions can be triggered only when the earliest time and latest time requirements are met with respect to the token time stamps. They also presented three

axioms which must be satisfied in each action to maintain the natural concepts of time stamps.

Adbulla and Nylen defined *timed Petri nets* [3], in which each token is associated with a clock which can be reset at the time of transition. This resembles the clock reset operations of timed automata. There is also no obligation to fire an enabled transition before the Lft expires.

Serugendo *et al.* extended Merlin and Faber's time Petri net to *real-time synchronized Petri nets* with synchronizations between a set of objects, modeled with real-time Petri nets [195].

Girault and Valk editted a handbook on formal methods based on Petri nets [94]. Cerone and Maggiolo-Schettini wrote a survey paper on various approaches to extending Petri nets to specification and verification of timed systems [56].

# G. Graphical Languages

Statecharts [103] were introduced to help users describe behavioral hierarchies of untimed concurrent systems in a graphical style. System operations can be hierarchically decomposed to parallel and serial modes. Such behavioral hierarchy has inspired various compositional frameworks for verification and analysis, e.g., assume–guarantee reasoning [1], [17], [99], [162], [205], and state refinement verification [9], [232].

*Modecharts* [128] were the first timed extension of statecharts. Their semantics was defined with RTL [127] in discrete time-domain. Timing intervals and discrete events can be used as triggering conditions for transitions.

Statecharts support many powerful primitives, like exceptions, group transitions, and history. As a result, their semantics is complex. Hierarchic reactive module (HRM) is a model description language for timed systems with restrictions on transitions to simplify the semantics [14]. Syntactically, transitions in HRM can only connect to entry/exit points of structural modules. Transitions are forbidden from jumping directly to inner modules.

Timed unified modeling language (UML) is the real-time extension of UML [72], which is in turn a variation of state-charts. Translation schemes from timed UML to various verification tool languages have been studied and implemented [73], [88], [136], [146], [172].

#### IV. VERIFICATION FRAMEWORK

There are the following four major approaches to computationally verifying timed systems.

# A. Satisfiability Checking

In this framework, we write both the system behavior description B and specification S as logic formulas and try to prove that  $B \to S$  is a theorem (i.e., tautology) of the underlying axioms. In reality, we usually check if  $B \land \neg S$  is a contradiction, or equivalently  $B \land \neg S$  is unsatisfiable. In the implementation, we can use the tableau method to construct an untimed Kripke structure and check if  $B \land \neg S$  is satisfied at the initial nodes in the structure. A tableau is a small

model that can be used to check the existence of a model for  $B \land \neg S$ . Conceptually it is a directed graph  $\langle V, E \rangle$  such that V is the set of possible worlds (or states) and E is the set of transitions from world to world.

In the following, we illustrate the tableau construction for TPTL satisfiability checking [15]. Assume that we are given a TPTL formula  $\phi$  such that negations only appear in front of atomic constraints like p and  $x+c\sim y+d$ . This is possible because of deMorgan's law and  $\neg\Box\phi_1\equiv\Diamond\neg\phi_1$ ,  $\neg\Diamond\phi_1\equiv\Box\neg\phi_1$ , and  $\neg(\phi_1\mathcal{U}\phi_2)\equiv(\Box\neg\phi_2)\vee((\neg\phi_2)\mathcal{U}\neg(\phi_1\wedge\phi_2))$ . Given a TPTL formula  $\phi$ ,  $\mathtt{closure}(\phi)$  is a set of TPTL formulas constructed with the following induction rules.

- $\phi \in \text{closure}(\phi)$  and true  $\in \text{closure}(\phi)$ .

- If  $\phi_1 \lor \phi_2 \in \text{closure}(\phi)$  or  $\phi_1 \land \phi_2 \in \text{closure}(\phi)$ , then  $\phi_1 \in \text{closure}(\phi)$  and  $\phi_2 \in \text{closure}(\phi)$ .

- If  $\phi_1 \mathcal{U} \phi_2 \in \text{closure}(\phi)$ , then  $\phi_1, \phi_2, \bigcirc \phi_1 \mathcal{U} \phi_2 \in \text{closure}(\phi)$ .

- If  $\Box \phi_1 \in \operatorname{closure}(\phi)$ , then  $\phi_1$ ,  $\bigcirc \Box \phi_1 \in \operatorname{closure}(\phi)$ .

- If  $\Diamond \phi_1 \in \text{closure}(\phi)$ , then  $\phi_1$ ,  $\Diamond \Diamond \phi_1 \in \text{closure}(\phi)$ .

- If  $\bigcirc \phi_1 \in \text{closure}(\phi)$ , then  $\phi_1 \in \text{closure}(\phi)$ .

- If  $x.\phi_1 \in \text{closure}(\phi)$ , then  $\phi_1[x := T] \in \text{closure}(\phi)$  where T is the symbol for current time and  $\phi_1[x := \epsilon]$  is identical to  $\phi_1$  except that every occurrence x is replaced by  $\epsilon$ .

- If  $x+c \sim T+d \in \operatorname{closure}(\phi)$  where  $c, d \in N$  and  $\sim \in \{<, \leq, =, \geq, >\}$ , then  $x+c \sim T+d-1 \in \operatorname{closure}(\phi)$ . The case for  $T+d \sim x+c$  is symmetric.

Here, for convenience, we assume only inequalities like  $x+c\sim y+d$ , where x and y are clock variables and c and  $d\in N$  are used.

A node v in V for  $\phi$  is a subset of closure( $\phi$ ) that satisfies the following *node consistency conditions*.

- true  $\in v$ .

- If  $T + c \sim T + d \in v$ , the truth value of  $c \sim d$  is in v.

- If  $\neg \phi_1 \in v$ , then  $\phi_1 \not\in v$ .

- If  $\phi_1 \lor \phi_2 \in v$ , then  $\phi_1 \in v$  or  $\phi_2 \in v$ .

- If  $\phi_1 \wedge \phi_2 \in v$ , then  $\phi_1 \in v$  and  $\phi_2 \in v$ .

- If  $\phi_1 \mathcal{U} \phi_2 \in v$ , then either  $\phi_2 \in v$  or both  $\phi_1 \in v$  and  $\bigcap \phi_1 \mathcal{U} \phi_2 \in v$ .

- If  $\Box \phi_1 \in v$ , then both  $\phi_1 \in v$  and  $\bigcirc \Box \phi_1 \in v$ .

- If  $\Diamond \phi_1 \in v$ , then either  $\phi_1 \in v$  or  $\bigcap \Diamond \phi_1 \in v$ .

- If  $x.\phi_1 \in v$ , then  $\phi_1[x := T] \in v$ .

If  $(v, v') \in E$ , then the following transition consistency conditions must also be maintained in E, i.e., exactly one of the following two is true.

- 1) For all  $\bigcirc \phi_1 \in v$ , then  $\phi_1 \in v'$ .

- 2) For all  $\bigcirc \phi_1 \in v$ , then  $\phi_1^T \in v'$ , where  $\phi_1^T$  is identical to  $\phi_1$  except that every constraint like  $x+c \sim T+d$  with  $c,d \in N$  is respectively replaced with  $x+c \sim T+d-1$ . (The case for  $T+d \sim x+c$  is symmetric.)

Case 1 models the passage of zero time units, while case 2 models the passage of one time unit. Also note that when a constraint like  $x+c \sim T-1$  is generated, we will no longer ask for the decrements from T-1. Thus, T-1 serves as a

flag, since no matter when we freeze T to x, the truth value of  $x+c\sim T-1$  is already determined at the moment when T-1 is generated.

The small model theorem of TPTL says that if there is a model for  $\phi$ , then there is such a model:

- whose nodes are in the powerset of  $closure(\phi)$  and satisfy the node consistency condition; and

- whose transitions satisfy the transition consistency condition; and

- that contains a cycle such that

- the cycle is reachable from an initial state node; and

- if  $\Diamond \phi_1$  is labeled in some node in the cycle, there is another node labeled with  $\phi_1$  in the cycle; and

- if  $\phi_1 \mathcal{U} \phi_2$  is labeled in some node in the cycle, there is another node labeled with  $\phi_2$  in the cycle.

The satisfiability problem of linear-time temporal logics TPTL [15], TETL, MTL [16], and APTL [228] are EX-PSPACE-complete.

It is also possible to use temporal logics with dense-time semantics to do satisfiability checking. However, the satisfiability problems of TPTL with dense-time semantics and TCTL are all undecidable [5], [16]

# B. Model Checking

The framework of *model checking* [60], [61] means that the system descriptions are given as automata, the specification formulas are given as temporal logic formulas, and we want to check if all models of a given system description satisfy a given specification formula. One popular framework in this category is the TCTL model-checking problem [5] in which the system descriptions are timed automata, while the specifications are TCTL formulas. The TCTL model-checking problem is PSPACE-complete. Note that the framework in [5] only permits atomic constraints like  $x \sim c$  with  $\sim \in \{\leq, <, =, >, \geq\}$ . For about one decade, people have straightforwardly extended the framework with constraints like  $x - y \sim c$  [113]. Recently, Bouyer [46] showed that the model-checking algorithms in [5], [113] is not correct for such an extension.

An important subclass in the model-checking framework is *safety checking*, i.e., the model checking of formulas like  $\forall \Box \eta$  where  $\eta$  is a propositional formula for the safety property of a system. In implementation, the safety analysis problem is usually translated to the negation of the *reachability problem*, i.e., whether  $\exists \Diamond \neg \eta$  is true or not. Most of the implementations in model checking have focused on the efficiency enhancement of safety checking. The major reason for this may be that fully model checking complex timed systems is indeed too difficult.

It is also possible to model check linear-time temporal logics like TPTL [15] or MTL [16]. In this framework, we want to verify that every computation of the timed automata is also a state sequence of the linear-time property.

Model checking has also been applied to frameworks other than automata. FDR is a commercial model-checker for CSP but does not quite support real-time system modeling [89]. The idea is to check whether, by hiding some internal variables, a behavior description in CSP can be identified as a refinement of another specification in CSP.

There is also model-checking research for Petri nets. One common approach is to put in restrictions to reduce Petri nets to finite-state systems, which are then subject to algorithmic model checking. In general, the reachability (of a specification marking) problem of Petri nets is decidable but without known elementary complexity. Another commonly accepted framework for verification with Petri nets is called the *coverability* problem, in which we are given a specification marking v and want to see if there is a reachable marking v such that v is no less than v place by place.

## C. Simulation

It is also possible to use state-transition systems (automata) for both system behavior descriptions and specifications. This framework can be useful when a specification is too complex to put down in temporal logics. After all, a picture is worth a thousand words. Given a behavior model description A and a specification B, intuitively, we want to check whether A simulates B, i.e., every behavior of A is also a behavior of B with respect to the input and output events (i.e., observable events) and the times at which those events occur. However, we need to define behavior more clearly.

In linear time, a behavior is an (infinite or finite) sequence of events and the occurrence times of those events. Such a sequence together with the event occurrence times is called a *timed trace*. The framework of *trace inclusion* verifies whether A *implements* B, i.e., the timed traces of A are also timed traces of B. This framework may not have the power to discern certain behaviors. For example, in Fig. 1, although the two systems have the same set of traces, the choices at p states are not the same. In addition, Alur and Dill showed that the inclusion problem of timed traces is undecidable [12].

An alternative framework is *simulation* [158], [159], [209], which, in formal verification literature, does not mean that we build a mathematical model in the programming language C, execute the model with an inference engine, and then observe the trace [66], [224]. Instead, *simulation* is a relation between states of two model descriptions at an abstraction level (regarding the same set of observable inputs and outputs). Given a behavior model description A and a specification B, intuitively, we want to check if there is a simulation relation from A to B (i.e., A simulates B). For convenience, we write  $\nu \xrightarrow{\delta,e}_A \nu'$  iff in A, we can transit from  $\nu$  to  $\nu'$  by first letting time progress by  $\delta$  (a nonnegative real) and then executing a transition labeled with event e. A relation  $\gamma$  between the state sets of A and B is a simulation iff for every  $(\nu_1, \nu_2) \in \gamma$ :

- ν<sub>1</sub> and ν<sub>2</sub> are the same, predicate by predicate, at the abstraction level;

- if  $\nu_1 \xrightarrow{\delta,e}_A \nu_1'$  for some  $\nu_1'$ , then  $\nu_2 \xrightarrow{\delta,e}_B \nu_2'$  for some  $\nu_2'$  of B such that  $(\nu_1',\nu_2') \in \gamma$ ; and

for every initial state ν<sub>1</sub> of A, there is an initial state ν<sub>2</sub>

of B such that (ν<sub>1</sub>, ν<sub>2</sub>) ∈ γ.

Timed simulation has been used extensively for systems modeled with various extensions of I/O automata [44], [105], [141], [154]–[156], [160]. Since I/O automata [133] have first-in-first-out (FIFO) queues and their verification problem is in general undecidable, a lot of the work was carried out using theorem provers (see Section IV-D). TaşIran *et al.* showed that the simulation checking problem for timed automata is EXPTIME [209].

The third alternative is *timed bisimulation*, which is also a relation between states of two (timed) automata at an abstraction level. For convenience, given a relation  $\gamma$ , we let  $\check{\gamma} = \{(b,a)|(a,b) \in \gamma\}$ . Given two model descriptions A and B, a relation  $\gamma$  is a timed bisimulation between A and B iff  $\gamma$  is a timed simulation from A to B and  $\check{\gamma}$  is a timed simulation checking is decidable [55]. Lasota showed that timed bisimulation checking is also decidable for timed basic parallel processes (BPPs)<sup>9</sup> [145]. Bisimulation-based verification of timed automata can be found in [71], [153]. Work on discrete-time models can be found in [147]–[149].

#### D. Theorem Proving

This approach stems from very early research in artificial intelligence [58]. In this framework, verification engineers manually design a verification plan (proof sketch) and then use theorem provers to mechanically check the correctness of the reasoning steps in the plan. Since many of the theorem provers accept undecidable classes of logic formulas, the approach usually does not guarantee the termination of individual mechanical verification tasks. If a user feels that a prover cannot finish a task, he/she may have to either intervene with expertise (formalized as axioms or proof strategies) or change the verification plan. Fulfillment of a verification plan depends heavily on the users' profound knowledge of the underlying logics and proficiency in using the tools.

Various algorithms were developed to check subclasses of first-order logics. Shostak [202] and Nelson and Oppen [173] presented algorithms to decide unquantified combinations of some fragments of first-order logics. Shostak also presented algorithms (congruence closure) to decide equality with uninterpreted functions [200] and methods, like loop residue [201] and SUP-INF [199], to decide linear arithmetic. Oppen presented algorithms for checking *Presburger arithmetic* formulas<sup>10</sup> [177]. Techniques from propositional calculus [52], [98] can also be employed to check propositional fragments of first-order or high-order logics.

There is also an extensive library of term rewriting techniques for first-order and higher order logics [77], [135]. Research has shown that controlled heuristics on term-rewriting rules are important.

<sup>9</sup>BPPs are systems constructed with rules  $P := p|P_1||P_2|1 \triangleright P_1$ , where p is an atomic process and  $1 \triangleright P_1$  is the process of the passage of one time unit followed by process  $P_1$ .

<sup>10</sup>Presburger arithmetic is the theory of linear constraints like  $c_1x_1+\ldots+c_nx_n \sim d$ , Boolean operators, and quantification on variables  $x_1,\ldots,x_n$ .

Shankar designed an operator |P| (read "since" P) in a state-based model in the well-documented theorem prover Prototype Verification System (PVS) [197]. The operator measures the time that has elapsed since P last held. It is implemented with three axioms in PVS. The first specifies the initial value of each |P|. The second and third respectively define when |P| should remain the same and when it should increment in an action. Users can also define their own axioms in PVS for convenience. Work along this line can be found in [24], [25], [117], and [193].

#### V. REPRESENTATIONS OF STATE SPACES

Many verification frameworks rely on the analysis of reachable state spaces. The efficient manipulation of representations of reachable state spaces is fundamental to efficient verification of real-time systems. One important work in this regard is [5], in which Alur et al. presented a finite representation, called the region graph, for the dense-time state space of timed automata, and then proved the PSPACE-completeness of the TCTL model-checking problem. A region graph is a directed graph whose nodes are called regions and whose arcs represent either time progress or discrete transitions between regions. A region is a state subspace with three characteristics. The first is the control location of the states, the second is the integer parts of clock readings in the states up to the biggest timing constants used in the automata and the TCTL formula, and the third is the ordering among the fractional parts of clock readings in the states.

Region graphs are important in establishing complexity. For practical verification, symbolic data structures can usually yield more compact representations. In the following sections, we discuss some work in this regard.

## A. Difference-Bounded Matrices

Since Dill proposed to use the difference-bounded matrix (DBM) to record the time space of real-time systems [78], the DBM has been adopted by two major model checkers: Kronos [75], [237] and UPPAAL [39] and has become the most popular data structure for such a purpose.

A DBM is a two-dimensional array. Each entry in a DBM records the difference between two clocks' readings of a state in the space characterized by the DBM. Zero is also treated as a special clock. Conceptually, given a set X of clocks, a DBM D is a mapping from  $(\{0\} \cup X)^2$  to a set of elements like  $(\sim,c)$  such that:

- $\sim$  is either < or <;

- $c \in \{-C, \ldots, -1, 0, 1, \ldots, C, C^+\}$  where C is the biggest timing constant used in the real-time systems or in the specification and  $C^+$  means any constant greater than C; and

- $c = C^+ \Rightarrow \sim = <$ .

For each two  $x, x' \in \{0\} \cup X$ ,  $D(x, x') = (\sim, c)$  means that  $x - x' \sim c$ . A time space characterizable by a DBM is called a *zone*.

A DBM can represent a convex state space in the time space. Efficient operations like intersection and normalization to all-pair shortest-path form, can be performed. But a DBM cannot represent a concave state space.

Annichini *et al.* [21] have extended DBM with parameters for the semialgorithmic analysis of counter and clock systems.

## B. BDD-Like Data Structures

BDD [52] is a minimum canonical form for propositional logic and has become an indispensible technology in hardware verification. Topologically, a BDD is an acyclic directed graph with a single source and two sinks (for FALSE and TRUE, respectively). It can represent both disjunctions and conjunctions. Each node is labeled with a decision atom, and the outgoing arcs are labeled with the values of the corresponding decision atom. It is minimum because BDD has the least representation size for any state space with respect to a given variable ordering. It is canonical because there is exactly one BDD for any given state space. This canonicality feature also implies that equality checking between state spaces and emptiness checking of a state space can be done efficiently.

The first paper to discuss how to use BDD to encode zones (actually for asynchronous systems with clock jitters) was by Wang et al. in 1993 [227]. They discussed how to use BDD with decision atoms like  $x_i + c \le x_j + d$  to model check timed automata. Here, c and d are timing constants with magnitude no greater than the biggest constant used in the behavior model and specification. Each decision atom can assume a Boolean truth value. The approach may suffer from bad performance, since the size of the decision atom domain is already proportional to the timing constants and, thus, exponential to the input size. However, they did not report implementation or experiments. In 1996, Balarin implemented the same scheme and reported experiments with approximation techniques [33]. In 1999, Møller et al. used the same idea to devise a data structure called a difference decision diagram (DDD) and discussed many manipulation techniques [168], [169].

The *numerical decision diagram (NDD)* [26] uses binary encoding for clock readings, and its performance is very sensitive to timing-constant magnitude.

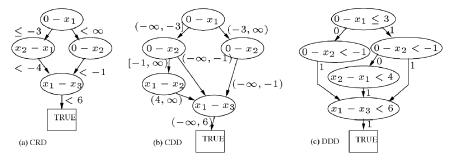

The clock-difference diagram (CDD) [36] uses decision atoms like x-y and labels arcs with disjoint intervals. For example, a node label x-y together with an arc label (3,5] constitute the constraint  $3 < x - y \le 5$ . CDDs were only used in UPPAAL [36] as recording devices of zones constructed with DBMs. No model-checking and reachability algorithms were implemented with CDDs in [36].

RED [213], [214] encodes the ordering of fractional parts of clock readings in the variable ordering and has achieved very high space efficiency for symmetric systems with large numbers of clocks and small timing constants. RED is a canonical representation of timed automata state subspaces. But for large timing constants, REDs performance degrades rapidly.

Then in 2001, Wang proposed the *clock-restriction diagram (CRD)* [216]–[218], which has a structure similar

Fig. 4. Comparison among CRD, CDD, and DDD.

to CDD. The major difference between CRDs and CDDs is that the arcs from a node in CDDs are labeled with "DISJOINT" intervals, while those from a node in CRDs are labeled with upperbounds, which are structurally overlapping. Due to this minor difference, CRDs may avoid the representation fragmentation problem which are observed in CDDs with respect to some benchmarks. A complete set of symbolic manipulation algorithms with CRDs, including weakest precondition constructions, strongest postcondition constructions, and normalizations, has been developed and reported in [219]. According to the experience reported in [219], CRDs lead to clearer algorithm structures in the manipulation of dense-time state-space representations than CDDs. It was also reported that with careful programming, CRD technology outperforms DBM [216], [217], [219]. Similar experiments can be found in [196].

The size of a BDD can be reduced by only recording those paths to sink TRUE. The CRD, CDD, and DDD for the state space  $(0-x_1 \le -3 \land x_2 - x_1 < -4 \land x_1 - x_3 < 6) \lor (0-x_2 < -1 \land x_1 - x_3 < 6)$  is in Fig. 4.

# C. Sets of Constraints

For linear hybrid systems, whose timing constraints may not be pairwise differences of clock readings, the state spaces can then be represented as unions of convex polyhedra [8], [102], each of which is bounded by a set of linear constraints. Early work in this regard is the linear relation analysis [69], [101] in the forum of *abstract interpretation* [67], [68].

Wang proposed a BDD-like data structure, called the *hybrid-restriction diagram (HRD)*, for the representation and manipulation of hybrid automata state spaces and reported experiments [221].

## VI. CONSTRUCTION OF TIME-SPACE REPRESENTATIONS

Since verification problems are highly complex for real-time systems, only with tight integration between data structures and algorithms can we effectly verify real-world system designs. The computation of real-time systems can be viewed as the interleaving of time progresses and discrete transitions [111]. Technically, given a state-space representation, we need to implement two procedures:  $\mathtt{time}(\eta)$  and  $\mathtt{xtion}(\eta,e)$  that construct the state-space representations of time progress and state transition e, respectively, from states in  $\eta$ . Then we apply these two procedures to iteratively construct the state-space representations reachable from the

initial states. Specifically, given the set of transition E and the representations for the initial condition I and the invariance constraint  $\Phi$  of a system, we execute the following loop, until  $\eta = \eta'$ :

for

$$(\eta = I \land \Phi$$

,  $\eta' = \text{false}; \ \eta \neq \eta';)$  {  $\eta' = \eta; \ \eta = \eta \lor \Phi \land \ \text{time}(\Phi \land \bigvee_{e \in E} \text{xtion}(\eta, e))$  }

After the loop,  $\eta$  is the representation for the state space reachable from the initial condition.

The transitions in timed systems are usually presented as rules (or guarded commands) in the form " $\tau \longrightarrow x := \epsilon;$ ," which means that when the *triggering condition*  $\tau$  is satisfied, the *assignment* of  $\epsilon$  (an expression) to x can be executed. Computationally

$$\mathtt{xtion}(\eta, ``\tau \longrightarrow x := \epsilon; ") \equiv x = \epsilon \wedge \exists x (\eta \wedge \tau).$$

The existentially quantified  $\boldsymbol{x}$  can be removed with a Fourier–Motzkin elimination.

On the other hand, the basic symbolic manipulation to derive constraints after time progress from a zone, i.e., procedure time() in Section IV-B, is in [113]. For simplicity, we assume that we are given a zone with only operator  $\leq$  as follows:

$$\bigwedge_{i} x_{i} \leq c_{i} \wedge \bigwedge_{j} -y_{j} \leq d_{j} \wedge \bigwedge_{k} x_{k} - y_{k} \leq e_{k}.$$

Here,  $x_i, y_j, x_k$ , and  $y_k$  are clock variables, and  $c_i, d_j$ , and  $e_k$  are integer constants in  $\{-C, -C+1, \ldots, 0, \ldots, C\}$  with C as the biggest timing constant used in the behavior description and specification. In practice, both  $\leq$  and < can be used. We want to determine the *postcondition* of time progress, i.e., what the zone becomes after the progress of time  $\delta \geq 0$ , with  $\delta \in \mathcal{R}$ . If we use the symbol x to represent the reading of clock x after time progress of  $\delta$ , then the reading of clock x before the time progress can be symbolically represented as  $x - \delta$ . Prior to the time progress, the above zone constraint must be satisfied; we have

$$\exists \delta \begin{pmatrix} \delta \geq 0 \land \bigwedge_{i} x_{i} - \delta \leq c_{i} \land \bigwedge_{j} - (y_{j} - \delta) \leq d_{j} \\ \land \bigwedge_{k} (x_{k} - \delta) - (y_{k} - \delta) \leq e_{k} \end{pmatrix}$$

$$= \exists \delta \begin{pmatrix} -\delta \leq 0 \land \bigwedge_{i} x_{i} - \delta \leq c_{i} \land \bigwedge_{j} - y_{j} + \delta \leq d_{j} \\ \land \bigwedge_{k} x_{k} - y_{k} \leq e_{k} \end{pmatrix}$$

The new existentially quantified variable  $\delta$  can be eliminated by deriving inequalities like

$$x_i - \delta - y_j + \delta \le c_i + d_j \equiv x_i - y_j \le c_i + d_j$$

for each pair of  $x_i - \delta \le c_i$  and  $-y_j + \delta \le d_j$  (including  $-\delta < 0$ ). Thus, we have

$$\exists \delta \begin{pmatrix} -\delta \leq 0 \land \bigwedge_{i} x_{i} - \delta \leq c_{i} \land \bigwedge_{j} -y_{j} + \delta \leq d_{j} \\ \land \bigwedge_{k} x_{k} - y_{k} \leq e_{k} \\ \land \bigwedge_{i,j} x_{i} - y_{j} \leq c_{i} + d_{j} \land \bigwedge_{j} -y_{j} \leq d_{j} \end{pmatrix}$$

$$= \begin{pmatrix} \bigwedge_{k} x_{k} - y_{k} \leq e_{k} \\ \land \bigwedge_{i,j} x_{i} - y_{j} \leq c_{i} + d_{j} \land \bigwedge_{j} -y_{j} \leq d_{j} \end{pmatrix}$$

again with a Fourier–Motzkin elimination of  $\delta$ . Since new constraints like  $x_i-y_j \leq c_i+d_j$  can be generated iteratively, it seems that we may not be able to converge to a fixpoint in the process of symbolic state-space representation construction. Fortunately, according to [78], when  $c_i+d_j$  is bigger than the biggest timing constant (i.e., C) used in the model description and the specification formula, then we can discard the corresponding inequality. And when  $c_i+d_j$  is smaller than -C, we can replace the inequality with  $x_i-y_j<-C$ . The replacements do not change the results of verification, since they are region equivalent.

A more efficient formulation for calculating the time progress postcondition is used in [196] and [219] and does not need to introduce the variable  $\delta$ . This is done in two steps by first deducing transitivity constraints  $x_i - y_j \leq c + d$  through each pair of constraints like  $x_i \leq c$  and  $-y_j \leq d$ , and then removing all upperbound constraints like  $x_i \leq c$ .

With the capability to derive zones after discrete transitions and time progresses, we can (explicitly or implicitly) construct a zone graph whose nodes are zones and whose arcs represent time progresses and discrete transitions. However, such a framework can still be enhanced in efficiency. In the following, we survey various techniques used in the construction of state-space representations for real-time systems.

## A. Backward Versus Forward Analysis

The time progress operation in the previous section reasons into the future. *Forward reachability analysis* uses such a basic step (together with operations for forward discrete transitions) to iteratively construct the representation for the state spaces forwardly reachable from the initial state.

We can also define a basic manipulation step for backward time progress. This can be achieved by substituting each x for  $x + \delta$  instead of  $x - \delta$ . Backward reachability analysis uses such a basic step (together with operations for backward discrete transitions) to iteratively construct the representation for the state spaces backwardly reachable from the goal state.

For the widely used framework of safety checking, backward and forward analyses can both perform well. But backward analysis is almost mandatory for model checking because the modalities of strong "until"  $(\mathcal{U}, \exists \mathcal{U}, U, \text{ or EU})$  and strong "eventually"  $(\lozenge, \exists \lozenge, F, \text{ or EF})$  can only be efficiently handled with backward fixpoint computation.

## B. Compositional Approach

Engineers usually describe their systems as a set of concurrent modules and design each module to work correctly with respect to uncertainty in the environment. Thus, it is natural to expect that such defensive designs can significantly reduce verification complexity. Various compositional verification strategies have been proposed to implement such expectations. Laroussinie et al. [142], [144] proposed a procedure to iteratively refine the specification formulas in a timed modal logic which accepts formulas like  $\langle e \rangle \eta$  (eventually, after event e,  $\eta$  is satisfied),  $[\delta]\eta$  (for every time passage by  $\delta \geq 0$ ,  $\eta$  is always true), and  $\langle \delta \rangle \eta$  (eventually, there is a time passage by  $\delta \geq 0$  such that  $\eta$  is true). Given concurrent timed automata  $A_1, \ldots, A_m$  and such a formula  $\phi$ , the model-checking task is to prove  $A_1 | \dots | A_n \models \phi$ , where  $A_1 | \dots | A_n$  is the composition of the concurrent modules. Then we can refine the specification as  $\phi/A_n$  and inductively prove  $A_1 | \dots | A_{n-1} \models \phi / A_n$ . Here  $\phi / A_n$  is a refinement of  $\phi$  with respect to  $A_n$ . Intuitively,  $\phi/A_n$  is obtained by restricting  $\phi$  with transition relations of  $A_n$  encoded in the timed modal logic. This process is then repeated until we can prove or disprove true  $\models (\dots (\phi/A_n) \dots)/A_1$ .

In [223], Wang and Hsiung proposed a compositional framework, called *state-graph manipulators* (*SGM*), to construct the global state graphs. SGM takes advantage of compositional verification to support a user-friendly interface. They use state graphs of concurrent modules as high-level data objects and package various verification techniques into SGMs to help users manipulate state graphs without the prerequisite deep knowledge of verification technology. They have also shown that by applying various reduction SGMs to the intermediate state graphs produced after each binary composition, significant enhancement can be obtained in verification performance.

In [114], compositionality is utilized in the framework of refinement of reactive modules [17]. Intuitively, module P is a refinement of Q, in symbols  $P \preceq Q$ , if each observable behavior of P is also a behavior of Q. We want to prove  $P_1 || P_2 \preceq Q$  by proving  $P_1 \preceq Q$  and  $P_2 \preceq Q$ . However, this is usually impossible. The techique in [114] relies on the derivation of assumptions  $A_1$  and  $A_2$  from  $P_1$  and  $P_2$ , respectively. Then in the framework of assumption—guarantee, we can prove the guarantee by instead proving  $P_1 || A_2 \preceq A_1$ ,  $A_1 || P_2 \preceq A_2$ , and  $A_1 || A_2 \preceq Q$ .

# C. On-the-Fly Approach

In some early verification tools [53], the global state-space representations are constructed without regard to whether the states are reachable or not. In reality, if we have better knowledge which allows us to not represent unreachable states, then significant representation and manipulation complexity can be reduced. This is the basic idea of on-the-fly construction of state-space representations [45], [110]. Global state-space representations are constructed in a minimal way. Intuitively, we do not generate anything that is not used to answer the verification problem.

## D. Normalizations

One challenge in real-time system verification arises in the fact that there is not an efficient and canonical (unique) representation of state spaces. Regions [5] and RED [213] are canonical but are also of high complexity. Zones, convex polyhedra [69], [101], DBM [78], CDD [36], DDD [168], [169], and CRD [216], [217] are not canonical and incur complexity both in the need to check equality/containment between representations and in the possibility of representing/manipulating the same state spaces many times.

The purpose of normalization is to reduce the number of possible representations for the same state space. A normal form has to be defined first. The most popular one is *closure form* (or tight form) of zones, which means all constraints are tight [78]. Closure form zones can be obtained with an all-pair shortest-path algorithm in the style of Kleene's closure. In [143], reduced form is defined to have the minimum number of constraints for each zone and it also exhibits space efficiency. In [216], [217], [219], the performance of various normal form possibilities of CRDs are investigated.

Recently, people have also researched using a satisfiability-checking procedure (SAT procedure) to efficiently decide the emptiness of real-time state space [207]. In this way, normalization is traded for the efficiency of many off-the-shelf SAT solvers [171], [238], [239].

# VII. REDUCTION TECHNIQUES

Reduction techniques are used to simplify state-space representations and promote verification efficiency. The theoretical foundation is bisimulation equivalence [165], which characterizes states that can be distinguished by TCTL models. If we find that two state-space representations  $\phi_1$  and  $\phi_2$  describe bisimilarly equivalent states and  $\phi_2$  has lower space complexity than  $\phi_1$ , then we can replace  $\phi_1$  with  $\phi_2$ .

Approximation is another reduction approach, which may not preserve bisimulation equivalence.

In the following, we briefly discuss several reduction techniques for timed systems.

# A. Inactive Variable Elimination

A variable is *inactive* in a state if along all computations from the state, the variable will not be read again before being written to. Two states are bisimilarly equivalent iff all variables other than those inactive ones have the same contents in the two states. In [76], Daws and Yovine presented a technique to detect inactive clocks in timed concurrent systems with synchronizations. They also presented techniques to detect clocks with equal readings and only represent one of them in the state-space representation.

Wang and Hsiung presented techniques to detect the inactiveness of variables in local state graphs considering the read—write behaviors in concurrent systems [223].

## B. Partial-Order Reduction

A major cause for state-space explosion in verification is that we have to enumerate all the sequences (i.e., total ordering) of events in concurrent systems, like the ordering among the clock readings, clock resets, etc. But in reality, engineers rarely rely on the exact ordering of such sequences to assure the correctness of their system designs. Partial-order reduction has been realized in various strategies for untimed systems [92], [95], [116], [138], [182] and has been proven to be a valuable technique for untimed system verification.

For timed systems, Pagani presented a notion of independence between transitions based on global-time semantics of timed automata [180]. Yoneda *et al.* proposed a partial-order technique for model checking timed linear-time temporal logic on time Petri nets [38], [235], [236]. Bengtsson *et al.* used a definition of independence similar to [235], [236] and let clocks run without synchronization until communication time in a partial-order semantics. Minea [166] extended further the work of Bengtsson *et al.* [38].

## C. Internal Transition Bypassing

A transition is *internal* if it is not observable from the outside. By eliminating state information related to internal transitions, significant reduction in the complexity of state graphs can usually be achieved. Similar concepts date back to the *internal actions* of process algebrae [115], [165]. A recent similar concept is the *invisible transition* by Miller and Katz [164]. Wang and Hsiung extended the technique to timed systems with concurrent read/write operations [223]. In [148] and [149], related work by Lawford *et al.* on discrete-time systems can be found.

## D. Symmetry Reduction

In a concurrent system with symmetric processes running different copies of the same program, we can permute the roles of processes to transform state-space representations to normalized representations [84]. Symmetry reduction can be viewed as a special case of static partial-order reduction [138]. Wang presented a BDD-like data structure and a symmetry reduction technique [213]. The technique is quite efficient for fully symmetric systems with small timing constants. Wang also presented a symmetry reduction method for general timed systems based on an analysis of zone constraints and reported his experiments [218].

# E. Approximation

The most general theory of *abstract interpretation* for the analysis of computer systems was invented by Cousot *et al.* [67], [68]. There are two strategies for approximation: underapproximations and overapproximations. With underapproximations (or overapproximations) of state-space representations, we approximate a reachable state space with a representation for its subset (or superset respectively) in the hopes of reducing representation and manipulation complexity. In [231], Wong-Toi presented a powerful overapproximation technique called *convex-hull approximation*. The idea is to represent a union of convex hulls with a minimal convex hull encompassing all convex hulls in the union. The technique has been proven very useful in checking

safety properties and has been used in many tools [39], [48], [75], [183], [237].

However, for BDD-like data structures, convex-hull approximation is difficult to implement if we consider variable-ordering interleaving between discrete variables and clock constraint variables. Special approximation techniques in this regard can be found in [33], [224].

In [210], Tripakis and Yovine developed various methods to approximate timed systems with untimed automata. The expectation was to exploit the existing rich infrastructure in algorithms and tools for the verification of untimed systems.