# An Auto-I/Q Calibrated CMOS Transceiver for 802.11g

Yong-Hsiang Hsieh, *Student Member, IEEE*, Wei-Yi Hu, Shin-Ming Lin, Chao-Liang Chen, Wen-Kai Li, Sao-Jie Chen, *Senior Member, IEEE*, and David J. Chen, *Member, IEEE*

Abstract—The CMOS transceiver IC exploits the superheterodyne architecture to implement a low-cost RF front-end with an auto-I/Q calibration function for IEEE 802.11g. The transceiver supports I/Q gain and phase mismatch auto tuning mechanisms at both the transmitting and receiving ends, which are able to reduce the phase mismatch to within  $1^{\circ}$  and gain mismatch to 0.1 dB. Implemented in a 0.25  $\mu$ m CMOS process with 2.7 V supply voltage, the transceiver delivers a 5.1 dB receiver cascade noise figure, 7 dBm transmit, and a 1 dB compression point.

*Index Terms*—Auto calibration, DC offset cancellation, gain mismatch, phase mismatch, RF transceiver, 802.11g.

### I. INTRODUCTION

N THE MARKET of wireless local area networks (WLANs), high data-rate transmission has been the trend. IEEE 802.11g standard works at 2.4 GHz ISM band and supports data rates up to 54 Mb/s using OFDM modulation [1]. To achieve the desired performance upper bound, it is crucial to deliver a close match of I and Q signals in both the modulator and the demodulator. Solutions on in-phase and quadrature (I/Q) gain and phase mismatch compensation can be classified into three types. The first type uses a fully digital compensation technique. For example, Eberle et al. [2] presented a digital compensation architecture for the I/Q mismatch problem that occurred in a digital receiver. The second type uses baseband plus RF front-end to calibrate the gain and phase mismatch. For example, baseband signal processing techniques have been used to generate a test signal to the RF front-end [3], [4]. Since the output of the RF front-end running this test signal will give information on the I/Q mismatch, the baseband can sense this output to determine a control code for the front-end circuits to compensate the I/Q mismatch. But the RF front-end and baseband circuits are often developed independently, and thus, implementing the second type of calibration is not possible. The third type does not require any baseband support. For example, the 802.11a/b/g transceiver presented by Ahola et al. [5] achieved an accuracy quadrature phase through careful analysis and design of the I/Q generation parts of the local oscillator. Another approach of this type has been presented by Hsieh et al. [6]; an auto-I/Q calibrated transceiver with no more than 5% additional chip area for the calibration circuitry.

Manuscript received February 26, 2005; revised June 23, 2005.

Y.-H. Hsieh and S.-J. Chen are with the Graduate Institute of Electronics Engineering and Department of Electrical Engineering, National Taiwan University, Taipei 106, Taiwan, R.O.C. (e-mail: alex.hsiehyh@msa.himet.net).

W.-Y. Hu, S.-M. Lin, C.-L. Chen, W.-K. Li, and D. J. Chen are with MuChip, Hsin-Chu 300, Taiwan, R.O.C.

Digital Object Identifier 10.1109/JSSC.2005.857348

This paper gives a more detailed description of [6], especially on the auto-calibration mechanism and calibration circuits design.

#### II. SYSTEM ARCHITECTURE

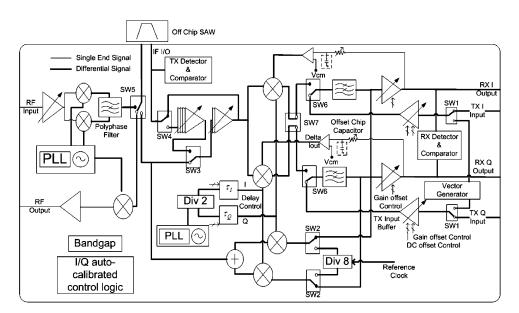

Fig. 1 illustrates the overall transceiver architecture. At the receiver front-end, a single-ended input, two-stage low-noise amplifier (LNA) is followed by an image-reject mixer and a polyphase filter. A CMOS analog switch (SW5) is used to drive the off-chip SAW filter. From IF to baseband, the IF signal flows through a CMOS analog switch (SW4) to a two-mode (RX/TX) variable gain amplifier (VGA), followed by an in-phase and quadrature (I/Q) down-conversion mixer and a fifth-order Bessel filter. The VGA and the Bessel filter are reused in both the receiving and transmitting paths through SW3, SW4, and SW6 to reduce the total transceiver die area. To remove the demodulator DC offset, a continuous feedback DC offset cancellation loop is designed as shown in Fig. 1: One of the differential RX I output (RX Q output) DC signal is extracted by the RC low pass filter. This extracted DC voltage will be compared with the common mode voltage V cm of RX I output (RX Q output). The resulted DC offset voltage will create an offset current on buffer output; this offset current flows through the resistors' load of mixer and generates a compensated offset

As shown in Fig. 1, the transmitting path begins with an input buffer, followed by a Bessel low-pass filter (LPF). A traditional Gilbert-cell double-balance mixer, succeeding LPF through SW2, is used to up-convert the baseband signal to IF frequency. The transmitter (TX) output power range is determined by the dual-mode VGA gain that varies from -23~dBm to 2~dBm. The TX shares the same SAW filter with the receiver using on-chip CMOS analog switches SW4 and SW5, which are designed to have a differential output impedance of  $200~\Omega$ . A differential-to-single Gilbert-cell mixer drives a single-ended, two-stage preamplifier that was designed to have 15 dB gain and 7 dBm output  $P_{1dB}$ .

An integer-N phase-locked loop (PLL) operates with a 1 MHz reference frequency, which is derived from the system reference frequency generated by an external 40 MHz crystal oscillator. Three additional capacitor arrays in parallel with the tank circuits are used to tune the RF VCO frequency from about 1930 to 2210 MHz. The calibration of the center frequency is performed when the channel changes. The quadrature local signals for the image-reject RF mixer are generated by the two-stage polyphase filter. The IF PLL is implemented with an integer-N structure using the same reference frequency as

Fig. 1. Transceiver diagram.

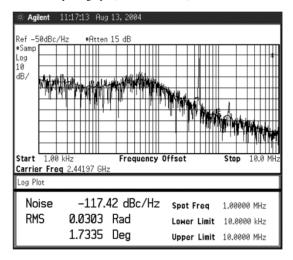

the RF PLL. Since the IF VCO oscillation frequency is 748 MHz, it is divided by two to create the 374 MHz quadrature IF local signals. The RF and IF VCO's have phase noises of -116 dBc/Hz and -120 dBc/Hz, respectively, at a 1 MHz offset.

## III. AUTO-I/Q CALIBRATION ALGORITHMS

The auto-I/Q calibration is performed when powered up to correct the process-related imperfections on I/Q mismatch; when temperature conditions change, the baseband processor can trigger the radio auto-I/Q calibration through the three wire series interface. But the measured results, which are the circuits without recalibrations, show that the degradation of EVM is less than 1.5% on the different temperatures. To reduce the overall current consumption, all the calibration circuits will be turned off after the calibration. The overall calibration flow starts from TX DC-offset cancellation, then to TX I/Q gain, and finally to TX I/Q phase. The RX I/Q gain and RX I/Q phase calibrations will be performed after all the TX calibrations, because the RX calibrations need to use a test tone from the calibrated TX.

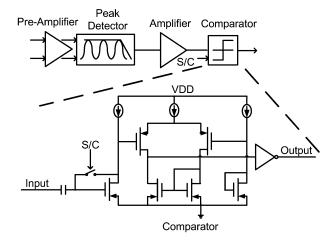

The DC-offset cancellation process needs to be executed first. As shown in Fig. 1, a switch SW1 on both the I and Q paths switches the input of TX input buffer from the baseband to the vector generator, and a DC test vector (0, 0) is applied to the modulator. A peak detector on the IF output converts the local leakage power level into a DC voltage, which is then amplified by a gain cell and applied to a sampling-and-compare (S/C) comparator, as shown in Fig. 2. The auto I/Q-calibration control logic changes 1 bit in the TX input buffer digital-to-analog converter (DAC) to create an extra DC signal on the I path. If the extra DC signal on the DAC output has the same polarity with the DC offset, the local leakage power on the peak detector input becomes bigger; otherwise, it becomes smaller. The S/C comparator gives information on the polarity of the DC offset that occurred on the I path. Based on the output of the comparator, a binary search algorithm is performed to find the proper control code for the DAC to create a compensated DC offset. The

Fig. 2. Architecture of TX detector and comparator.

I/Q path DC-offset cancellation is performed in the following sequence: I path  $\to Q$  path  $\to I$  path. A -40 dBc TX local leakage can be achieved using this algorithm.

The basic idea of TX I/Q gain mismatch calibrations is from [7]. The proposed transmitter architecture implements this idea with only 2.5% additional chip area. A DC test vector  $(0,V_T)$  or  $(V_T,0)$  is applied to the TX I/Q input in different time slots, and different signal power levels caused by the I/Q-path gain mismatch will appear on the modulator output. The peak detector then is used to sense which test vector will give a higher output power on the modulator. And the comparator output gives information on which path of the modulator has less gain. A 4-bit gain-controlled TX input buffer is designed to compensate for the gain mismatch. The gain of the TX input buffer is then increased step by step on the smaller gain path. When the S/C comparator changes its output polarity, the I/Q path gain becomes balanced and the gain calibration process stops.

The ideal input DC test vectors  $(0, V_T)$  and  $(V_T, 0)$  become invalid under the existence of DC offset and vector mismatch, and thus we use equivalent test vectors  $(0, V_T)$  and

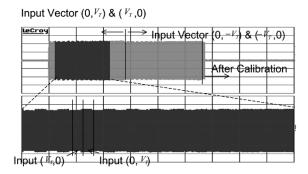

Fig. 3. Measured TX gain calibration.

$(V_T + \Delta V_T, 0 + \Delta DC)$  instead. But error can be eliminated by averaging the 4-bit TX buffer DAC values between input vectors  $(0, V_T)$  and  $(V_T, 0)$ ; and  $(0, -V_T)$  and  $(-V_T, 0)$ .

The TX gain calibration result is shown in Fig. 3. To track the IF output signal response when the circuits are auto-calibrating, the IF signal is down converted into a 5 MHz signal as shown in Fig. 3. The calibration process is divided into two segments. The first segment of calibration is performed with input vectors  $(0, V_T)$  and  $(V_T, 0)$ , then the second segment of calibration is performed with input vectors  $(0, -V_T)$  and  $(-V_T, 0)$ . The difference voltage swings are caused by the difference of gains obtained from the I and Q signal paths. During the calibration, voltage swings become smaller and smaller; finally when the voltage swings obtained at consecutive time slots are close to each other, the calibration will stop. After the calibration, the gain mismatch is reduced from about 0.4 dB to less than 0.1 dB.

After the gain mismatch calibration, a phase calibration is performed; the algorithm for phase calibration is similar to the TX gain calibration algorithm. The test vector is changed to  $(V_T,V_T)$  and  $(V_T,-V_T)$  instead of  $(0,V_T)$  and  $(V_T,0)$  in different time slots. Local quadrature mismatch causes different output power levels on the modulator output in different time slots. An extra delay is added on the local (delay-cell) buffer [8] to balance the delay. When the comparator output changes its polarity, the calibration loop stops. The existing DC offset and gain mismatch on I/Q paths will generate an error in the phase calibration result, which is about  $0.54^{\circ}$  under a DC offset of -40 dBc and a gain mismatch resolution of 0.1 dB. The resolution of phase delay in local buffer [8] is  $0.5^{\circ}$ , and thus the equivalent resolution of the quadrature mismatch is about  $1.04^{\circ}$ .

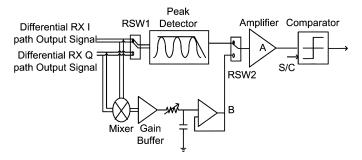

For the receiver I/Q mismatch calibration, a single tone is generated from the transmitter and is applied to the receiver demodulator. After down-conversion, a 5 MHz signal appears on the demodulator I/Q output. Fig. 4 shows both the gain and phase imbalance detection-and-comparison mechanisms. During the RX gain mismatch calibration, RSW1 changes the input from I path to Q path in different time slots. The comparator samples the I path signal and holds it to compare with the Q path signal. A compensated gain is added to the related path after the I/Q-auto calibration control logic senses the comparator output. A sequential search algorithm is used here and calibration will stop when the comparator changes its output polarity.

As shown in Fig. 1, a single-tone signal is generated as follows. A 5 MHz Q signal, obtained by dividing the 40 MHz ref-

Fig. 4. Architecture of RX detector and comparator.

erence clock by 8, is applied to the up-conversion mixer through SW2. A 379 MHz signal is created after up-conversion with a single-sideband (SSB) suppression of higher than -40 dBc. Finally, this single tone will loop back to the receiver through SW5.

The nonideal SSB generator in the transmitter will cause error during the RX gain mismatch calibration. Assume that the ratio of the image signal to the test tone signal is SSB, the peak detector output as shown in Fig. 4 is

$$V_{Ip} \approx \frac{1}{2} \times A - \frac{1}{2} \times A \times SSB,$$

when RSW1 switches to the I path input (1)

$V_{Qp} \approx \frac{1}{2} + \frac{1}{2} \times SSB,$

when RSW1 switches to the Q path input (2)

and

compensated gain:

$$\Delta G_1 = V_{Qp} - V_{Ip}$$

=  $\frac{1-A}{2} + \frac{1+A}{2} \times SSB \approx \frac{1-A}{2} + SSB$  (3

where A is the I/Q path gain ratio (A=1 in a balanced gain case).

The purpose of RX gain calibration is to compensate the gain imbalance caused by the term (1-A), but in this case the image signal in SSB will affect the calibration result. To eliminate this effect, the gain calibration has to be performed once again with swapped I/Q path signals by setting the RSW7 switch that follows the second I/Q down-conversion mixers: these two mixers are placed physically very close to each other, thus the gain mismatch here can be ignored. The peak detector output then becomes

$$V_{Ip} \approx \frac{1}{2} - \frac{1}{2} \times \text{SSB},$$

when RSW1 switches to the I path input (4)

$V_{Qp} \approx \frac{1}{2}A + \frac{1}{2} \times A \times \text{SSB},$

when RSW1 switches to the Q path input (5)

and

compensated gain:

$$\Delta G_2 = V_{Ip} - V_{Qp}$$

=  $\frac{1-A}{2} - \frac{1+A}{2} \times SSB \approx \frac{1-A}{2} - SSB$ . (6)

Combining (3) and (6), the obtained result contains only the (1 - A) term, the effect of SSB is thus eliminated.

For the RX phase mismatch calibration, the I/Q signals are mixed together through the mixer circuit as shown in Fig. 4.

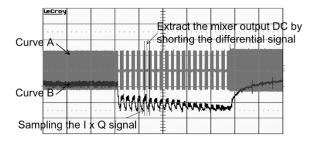

Fig. 5. Measured RX quadrature phase calibration.

When there is I/Q mismatch, a DC signal appears on the output of this mixer. The S/C comparator compares the DC operating point at the output of the gain buffer with the DC level obtained after the mixing of I/Q signals. The logic output of the comparator gives information on which quadrature local signal needs to add an extra delay to compensate the quadrature mismatch. The algorithm is similar to the TX phase calibration one, and an extra delay is implemented by a local delay-cell buffer [8] after the quadrature generator.

In this RX phase mismatch calibration case, the nonideal gain mismatch and SSB test tone will not affect the calibration result. The mixer output as shown in Fig. 4 is as follows:

Signal on mixer output  $V_{\theta}$  $\approx G \times \left(\frac{1}{4} \times A \times SSB^{2} + \frac{1}{4} \times A + \frac{1}{4} \times A \times SSB\right) \times \sin(\theta)$

where G is the gain of the mixer and  $\theta$  is the quadrature mismatch vector. From (7), since both A and SSB are coefficients

of  $\sin(\theta)$  only, they do not affect the calibration target, and it is

thus easy to push  $V_{\theta}$  to 0.

Fig. 5 shows the RX phase mismatch calibration result. Curve A shows the RX I path signal output and curve B shows the voltage of node B in Fig. 4. Values of the DC voltages on curve B are caused by the quadrature phase mismatches in different time slots. During the calibration, after a compensated phase delay is added to the quadrature local signal through the delay cell [8], the difference on two consecutive DC voltages becomes smaller and smaller, until the S/C comparator output changes its output polarity and thus the calibration process stops. After quadrature phase mismatch calibration, the quadrature phase error is reduced from about  $3^{\circ}$  to less than  $1^{\circ}$ .

## IV. IMPLEMENTATION OF I/Q AUTO-CALIBRATION CIRCUITRY

The detector and comparator circuits used in TX I/Q calibration are shown in Fig. 2, where a comparator is used to sense the DC offset on the peak detector output under different input test vectors. To relax the resolution requirement of this comparator, a fixed-gain amplifier is placed before the peak detector, and a DC-gain amplifier is added between the peak detector and the comparator. The resolution of the comparator designed for I/Q gain calibration is

$$0.64 \,\mathrm{mV}_{(1)} \times 10_{(2)} \times 0.85_{(3)} \times 4_{(4)} = 12.8 \,\mathrm{mV}$$

(8)

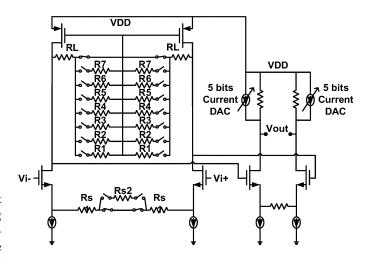

Fig. 6. Simplified circuit of TX input buffer with gain and dc offset tuning.

where

(7)

- (1) is the swing of 0.1 dB difference given an IF output power of −15 dBm. A close loop is implemented here through the TX gain control VGA to lock the IF output power when TX is under gain and phase calibrating;

- (2) is the gain of the fixed-gain amplifier between the IF output and the peak detector;

- (3) is the gain of the peak detector given an IF frequency input;

- (4) is the gain of the DC-gain amplifier between the peak detector and the comparator.

From (8), without considering the factors of fixed-gain and DC-gain amplifiers, resolution of the comparator becomes 0.544 mV. With the same architecture, the calculated resolution of the comparator used in phase calibration under 0.5° resolution is 3 mV. That is, our designed comparator meets the sensitivity requirement of 3 mV. The comparator used for RX calibration is the same as this TX comparator and under the same relaxed resolution requirement.

The circuit of a TX input buffer for gain and DC-offset tuning is shown in Fig. 6, where switch resistors are used for gain tuning with 0.05 dB resolution, and a current DAC is used to create offset current with its resistor load and to generate the compensated DC voltage.

The circuit of a delay cell buffer is from Der  $\it et al.$  [8]. To obtain a signal delay, a current DAC is used to control the bias current on the delay path and the forward path, and different bias current conditions on these two paths will generate different signal delays. A disadvantage of this circuit is its output swing will change under different current bias conditions. Since different output swings on the  $\it I$  and  $\it Q$  local signals will cause different mixer conversion gains in both the TX/RX chains, a limiter is placed after the delay cell to solve this problem.

### V. MEASURED RESULTS

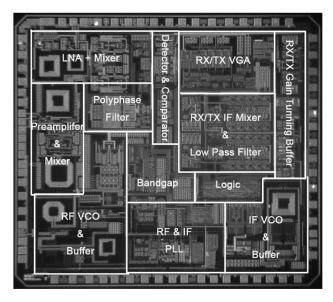

A fully integrated 802.11g transceiver die microphotograph is shown in Fig. 7. The PLL performance is shown in Fig. 8 with an integrated phase noise measured on TX output from 10 kHz to 10 MHz is  $1.7^{\circ}$ . Calibrations for I/Q mismatch and DC offset were performed in an on-chip auto-tuning loop. After

| TABLE I                         |

|---------------------------------|

| PERFORMANCE SUMMARY OF THE CHIP |

| Parameter                                        | Measured result  |

|--------------------------------------------------|------------------|

| Supply Voltage                                   | 2.7V ~ 3.3V      |

| Supply Current<br>RX mode<br>TX mode             | 150mA<br>120mA   |

| RX chain noise figure                            | 5.1dB            |

| RX chain max gain/min gain                       | 109dB/20dB       |

| RX Chain IIP3 (min gain)                         | 0dBm             |

| I/Q amplitude error on TX/RX (after calibration) | 0.1dB            |

| I/Q phase error on TX/RX (after calibration)     | 1°               |

| TX OP1dB                                         | 7dBm             |

| TX EVM (-4dBm output power)                      | 3.2%             |

| LO integration noise (10KHz to 10MHz)            | 1.7°             |

| Technology                                       | 0.25um 1P5M CMOS |

| Die size                                         | 10.2mm^2         |

Fig. 7. Die microphotograph  $(3.4 \text{ mm} \times 3 \text{ mm})$ .

Fig. 8. Measured integrated phase noise on TX output.

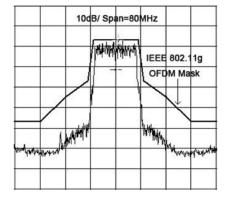

the TX DC offset, I/Q gain, and I/Q phase calibrations, the transmitter EVM, as shown in Fig. 9, is about 3.2% at -4 dBm

| Data Rate | 54Mbps |

|-----------|--------|

| EVM       | 3.2%   |

| Power     | -4dBm  |

Fig. 9. Measured constellation diagram and spectra.

output. The receiver features a noise figure NF = 5.1 dB. The receive IIP3 at minimum gain is 0 dBm. The maximum and minimum gains of receiver are 109 dB and 20 dB, respectively. The receiver EVM for the 54-Mb/s mode is about 4% after the RX I/Q gain and phase calibrations. The typical measurement results are summarized in Table I.

# VI. CONCLUSION

The presented transceiver supports a self-calibration mechanism for tuning both the receiver and the transmitter I/Q mismatches. Using the proposed innovative architecture, CMOS process-related imperfections on I/Q mismatch can be corrected such that the designed transceiver exceeds the standard specifications by a wide margin. The overhead of all the additional circuits needed for auto-calibration is just 5% of the total die area. The transceiver also features a good performance on both the receiving and the transmitting ends. Furthermore, the techniques presented in this paper can be extended to calibrate I/Q mismatch and DC offset in a zero-IF transceiver.

# REFERENCES

[1] IEEE Wireless LAN Standards [Online]. Available: http://standard-s.ieee.org/getieee802/802.11.html

- [2] W. Eberle et al., "OFDM-WLAN receiver performance improvement using digital compensation techniques," in Proc. IEEE Radio and Wireless Conf. (RAWCON), Aug. 2002, pp. 111–114.

- [3] K. Vavelidis et al., "A dual-band 5.15-5.35 GHz, 2.4-2.5 GHz 0.18 um CMOS transceiver for 802.11a/b/g wireless LAN," IEEE J. Solid-State Circuits, vol. 39, no. 7, pp. 1180-1184, Jul. 2004.

- [4] M. Zannoth et al., "A highly integrated dual-band multimode wireless LAN transceiver," *IEEE J. Solid-State Circuits*, vol. 39, no. 7, pp. 1191–1195, Jul. 2004.

- [5] R. Ahola et al., "A single-chip CMOS transceiver for 802.11a/b/g wireless LANs," *IEEE J. Solid-State Circuits*, vol. 39, no. 7, pp. 1191–1195, Jul. 2004

- [6] Y. H. Hsieh et al., "An auto I/Q-calibrated CMOS transceiver for 802.11g," in Proc. ISSCC, Feb. 2005, pp. 92–93.

- [7] M. Faulkner et al., "Automatic adjustment of quadrature modulators," Electron. Lett., vol. 27, no. 3, pp. 214–216, Jan. 1991.

- [8] L. Der et al., "A 2 GHz CMOS image-reject receiver with LMS calibration," *IEEE J. Solid-State Circuits*, vol. 38, no. 2, pp. 167–175, Feb. 2003

Yong-Hsiang Hsieh (S'00) received the M.S. and Ph.D. degrees in electrical engineering from the National Taiwan University (NTU), Taipei, Taiwan, R.O.C., in 1999 and 2005, respectively.

In 2000, he joined the MuChip Company, Ltd., Hsin-Chu, Taiwan, to work in RF circuits, WLAN systems including 802.11a/b/g, and RF audio systems using CMOS technology.

**Wei-Yi Hu** received the M.S. degrees in electrical engineering from the National Taiwan University (NTU), Taipei, Taiwan, R.O.C., in 2002.

In 2002, he joined the MuChip Company, Ltd., Hsin-Chu, Taiwan, to work in RF circuits including power amplifiers, mixers using CMOS technology, and CMOS analog circuits.

**Shin-Ming Lin** received the M.S. degrees in electrical engineering from the National Taiwan University, Taipei, Taiwan, R.O.C., in 2002.

In 2002, he joined the MuChip Company, Ltd., Hsin-Chu, Taiwan, to work in RF circuits including voltage-controlled oscillators, phase-lock loops using CMOS technology, and CMOS analog circuits.

**Chao-Liang Chen** received the M.S. degrees in electrical engineering from the Tamkang University, Taipei, Taiwan, R.O.C., in 1999.

In 2002, he joined the MuChip Company, Ltd., Hsin-Chu, Taiwan, to work in IF circuits including variable gain amplifiers, filters using CMOS technology, and CMOS analog circuits.

**Wen-Kai Li** received the M.S. degree in electrical engineering from the National Taiwan University, Taipei, Taiwan, R.O.C., in 2002.

In 2002, he joined the MuChip Company, Ltd., Hsin-Chu, Taiwan, to work in RF circuits including low noise amplifiers, mixers using CMOS technology, and CMOS analog circuits.

**Sao-Jie Chen** (M'88–SM'03) received the B.S. and M.S. degrees in electrical engineering from the National Taiwan University, Taipei, Taiwan, R.O.C., in 1977 and 1982, respectively, and the Ph.D. degree in electrical engineering from the Southern Methodist University, Dallas, TX, in 1988.

Since 1982, he has been a member of the faculty in the Department of Electrical Engineering, National Taiwan University, where he is currently a Professor. From 1985 to 1988, he was on leave from National Taiwan University and working toward the Ph.D. de-

gree at Southern Methodist University. During the fall of 1987, he held a visiting appointment at the Department of Electrical and Computer Engineering, University of Wisconsin, Madison. His current research interests include VLSI physical design automation, fault-tolerant computing, object-oriented software engineering, and supercomputer architecture design and simulation.

Dr. Chen is a member of the Chinese Institute of Engineers, the Association for Computing Machinery, and the IEEE Computer Society.

**David J. Chen** (M'81) received the Ph.D. degree in electrical engineering from the University of Southern California, Los Angeles, in 1991. He received the EMBA degree from the Anderson School at the University of California, Los Angeles, in 1995.

Since 1981, he has been engaging in the area of analog and RF CMOS IC design and product development for telecommunications and wireless consumer devices. He worked in the U.S. from 1981 to 1998, primarily as a Senior Design Engineer at Rockwell Semiconductor, Newport Beach, CA, and

then as an Engineering Manager at Sharp Corporation (USA), Irvine, CA. In 1999, he joined Mixam Microelectronics, an IC startup company in Taiwan, as VP of Engineering. In 2000, he founded MuChip Company, Ltd. in Hsin-Chu, Taiwan, with focus on CMOS RF IC and SOC design and development for consumer wireless applications, where he currently serves as Chairman of the Board. He has received two IC patents, with others pending.