# An Infinite Phase Shift Delay-Locked Loop With Voltage-Controlled Sawtooth Delay Line

Chao-Chyun Chen, Student Member, IEEE, and Shen-Iuan Liu, Senior Member, IEEE

Abstract—A wide-range delay-locked loop (DLL) with infinite phase shift and digital-controlled duty cycle is presented. By changing the polarity of the input clock of the voltage-controlled sawtooth delay, this proposed DLL achieves infinite phase shift by only a single loop. The proposed DLL has been fabricated in a 0.18  $\mu$ m CMOS process and the core area is 0.45  $\times$  0.3 mm<sup>2</sup>. The measurement results show the proposed DLL operates from 50 to 500 MHz. The duty cycle of the output clock can be adjusted from 30% to 60% in the step of 5%. At 500 MHz, the measured rms jitter and peak-to-peak jitter is 1.43 and 11.1 ps, respectively. Its power consumption is 6 mW for a supply of 1.5 V.

*Index Terms*—Clock synchronization, delay-locked loop (DLL), dual-loop DLL, duty cycle, infinite phase shift, jitter.

# I. INTRODUCTION

**OR** the high performance microprocessors and memory ICs, the phase-locked loops (PLLs) and delay-locked loops (DLLs) are usually adopted to reduce the skews and jitters of the clock signals. If the multiplied clock is not required, the DLL [1] is usually chosen for its unconditional stability and better jitter performance. To make the DLL immune to harmonic or false locking, the conventional voltage-controlled delay line (VCDL) must have the initial delay between  $0.5T_{\text{REF}}$ and  $1.5T_{\text{REF}}$  [2], where  $T_{\text{REF}}$  is the reference clock period. Therefore, there are several disadvantages in a conventional DLL. First, due to the process, voltage, and temperature (PVT) variations, the initial delay constraint of the VCDL may limit the operation range of a DLL. Second, it is difficult to guarantee the initial delay constrain if a wide operation frequency range is needed. Third, the VCDL may distort the duty cycle of the clock, owing to the unbalanced rising and falling times. It is unsuitable for the applications, which require the precise duty cycle of the clock.

To overcome the above problems, several solutions have been proposed, such as the replica delay line [2], a start-up control circuit [3], the dual-loop approach [4]–[8], and the phase mixing technique [9]. In [2], an additional replica delay line is needed. Once the mismatch exists between the replica and the main delay lines, the operation range will be limited. In [3], a start-up control circuit and a stage selector are used. However, many DFFs are needed in a stage selector, which occupy large chip area. The dual-loop DLL [4]–[8] can generate the fine phase

The authors are with the Graduate Institute of Electronics Engineering and Department of Electrical Engineering, National Taiwan University, Taipei 10617, Taiwan (e-mail: lsi@cc.ee.ntu.edu.tw).

Digital Object Identifier 10.1109/JSSC.2008.2004532

shift by the phase interpolator [4]. However, the dual-loop DLL may have the large output jitter and active area. To extend the operation range, the quadrature phase mixing technique is adopted in [9]. The wide phase shift is achieved, but the phase discontinuity may occur at the quadrant boundaries. To correct the duty cycle distortion of the clock caused by the VCDL and PVT variations, the pulsewidth control loop (PWCL) [10], [11] or the duty-cycle corrector [2], [12], [13] are usually used in the DLL.

In this paper, a wide range DLL with infinite phase shift by using the voltage-controlled sawtooth delay line (VCSDL) is presented. Compared with the dual-loop DLLs [4]–[8], the proposed DLL achieves infinite phase shift by using only a single loop. Therefore, the output jitter and chip area are reduced. Meanwhile, the duty cycle of the output signal is controlled to overcome the distortion, which is affected by the VCDL and PVT variations.

This paper is organized as follows. In Section II, the circuit description is given. Section III shows the experimental results. Section IV gives the conclusions.

# II. CIRCUIT DESCRIPTION

## A. Voltage-Controlled Sawtooth Delay Line (VCSDL)

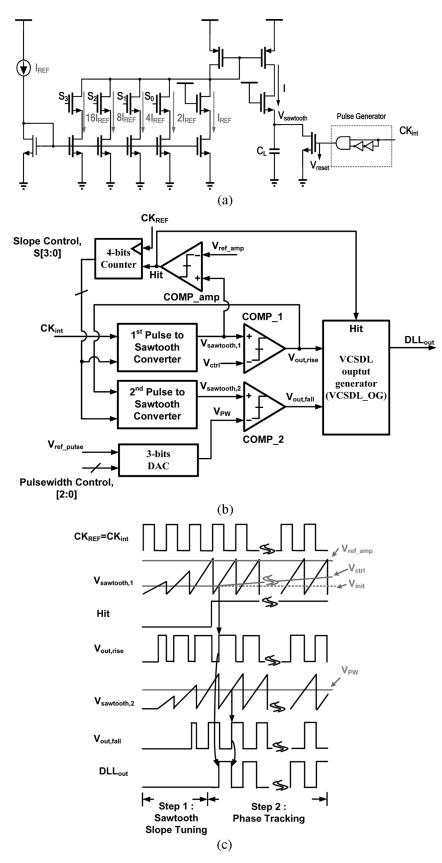

The pulse-to-sawtooth converter is shown in Fig. 1(a). A digitally controlled current, I, will charge the capacitor  $C_L$  to generate a ramp signal. To realize a sawtooth signal, the internal clock CK<sub>int</sub> is converted to a pulse  $V_{\text{reset}}$  by the pulse generator.  $V_{\text{sawtooth}}$  will be reset by  $V_{\text{reset}}$  if the rising edge of the internal clock CK<sub>int</sub> arrives. Four output bits (S<sub>3</sub>, S<sub>2</sub>, S<sub>1</sub>, and S<sub>0</sub>) of the 4-bits counter determine the slope of this sawtooth signal.

Fig. 1(b) shows the proposed VCSDL. It is composed of three comparators, two pulse-to-sawtooth converters, a 3-bits digital-to-analog converter (DAC), a 4-bits counter, and a VCSDL output generator (VCSDL OG). For simplicity, the latency for the pulse-to-sawtooth converter, the comparators, and the VCSDL output generator is neglected. The timing diagram of the VCSDL is shown in Fig. 1(c) and it is realized by two steps: sawtooth slope tuning and phase tracking. These two steps are also summarized by the flow chart as shown in Fig. 1(d). In the first step (i.e., sawtooth slope tuning), the output "Hit" of the third comparator (COMP\_amp) is low and the slope of the sawtooth signals will be adjusted. In Fig. 1(b),  $V_{\rm ctrl}$  is set to its initial value  $V_{\rm init}$ , and the 4-bits counter counts up. Therefore, the slope of the sawtooth signals at the outputs of the pulse-to-sawtooth converters will be increased. The output,  $V_{out,rise}$ , of the first comparator (COMP\_1) is realized by comparing  $V_{\rm sawtooth,1}$  with  $V_{\rm ctrl}$ . This comparator's output,  $V_{\rm out,rise}$ , enters into the VCSDL output generator and the

Manuscript received February 29, 2008; revised June 21, 2008. Current version published November 19, 2008.

Fig. 1. (a) Pulse-to-sawtooth converter. (b) Proposed voltage-controlled sawtooth delay line (VCSDL). (c) Timing diagram of the proposed VCSDL.

second pulse-to-sawtooth converter. The second comparator (COMP\_2) generates  $V_{\rm out,fall}$  by comparing  $V_{\rm sawtooth,2}$  and the pulsewidth control voltage  $V_{\rm pw}$ . When the amplitude of

$V_{\text{sawtooth},1}$  is larger than the reference voltage  $V_{\text{ref}\_\text{amp}}$ , the output "Hit" of the third comparator (COMP\_amp) goes high and it is latched in the 4-bits counter. Then, the 4-bits counter

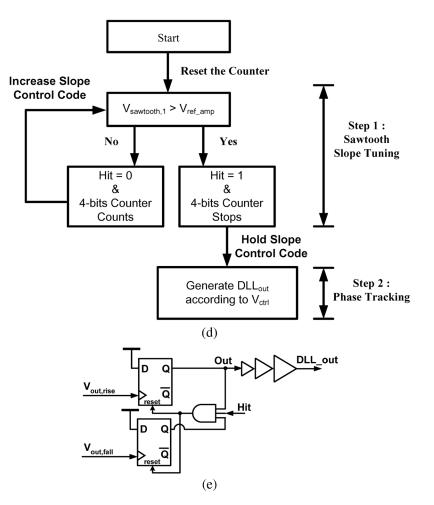

Fig. 1. (continued) (d) Flow chart of the VCSDL. (e) VCSDL output generator.

stops, and the slope of the sawtooth signals is fixed. The control voltage  $V_{\text{crtl}}$  is disconnected from  $V_{\text{init}}$  and the CG is enabled.

In the second step, the VCSDL output generator generates the output clock DLLout of this DLL and the DLL is under phase tracking. The VCSDL output generator is shown in Fig. 1(e). The VCSDL output generator is composed of two D-flip-flops, an AND gate and a clock buffer. The rising edge of  $V_{\text{out,rise}}$  becomes the rising edge of  $DLL_{out}$ , and the rising edge of  $V_{out,fall}$ becomes the falling edge of DLL<sub>out</sub>. To increase the control voltage,  $V_{ctrl}$ , the rising edge of  $V_{out,rise}$  will be delayed and the delay of the VCSDL is increased. Thus, the output clock DLL<sub>out</sub> of the DLL is also delayed. Supposed that  $V_{\rm DW}$  is fixed and  $V_{\text{ctrl}}$  is increased, the delay of VCSDL is increased as shown in Fig. 1(c). In the steady state, the rising edges between reference clock and output of the DLL are in-phase and the corresponding phase difference is eliminated. Note that the delay range of the VCSDL is proportional to the low-level pulsewidth of  $V_{\text{out,rise}}$ . So, it is proportional to the control voltage  $V_{\text{ctrl}}$  and the ratio of  $C_L/I$  in the pulse-to-sawtooth converter, respectively. It means a wide range delay is achieved if the low-level pulsewidth of  $V_{\text{out,rise}}$  is large. Theoretically, the delay range can be close to one period of the input clock.

The duty cycle of the output clock is controlled by  $V_{pw}$ . When  $V_{pw}$  increases, the rising edge of  $V_{out, fall}$  is delayed and the duty cycle of the output clock, DLL<sub>out</sub>, will be increased. In fact, the

3-bits pulsewidth control code will determine  $V_{pw}$  by the 3-bit DAC [14]. Thus, the duty cycle of the output clock is adjustable.

## B. Proposed DLL

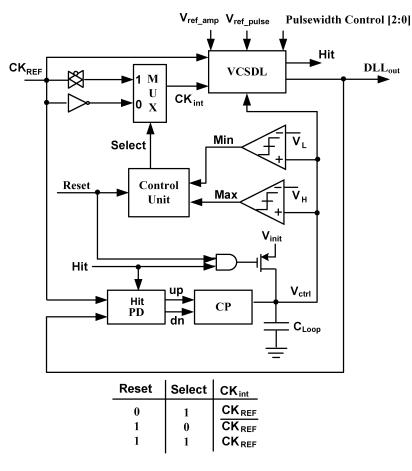

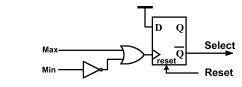

Fig. 2 shows the proposed DLL. It consists of a phase detector (PD), a charge pump, a loop filter, a VCSDL, the comparators, the multiplexer, an AND gate, a PMOS transistor and a control unit. Depending on the "Select" of the control unit, CK<sub>init</sub> changes its polarity. When the system starts, the signal "Reset" goes high and the signal "Hit" is low to turn on the PMOS transistor. Initially,  $V_{\text{ctrl}}$  is set to an initial voltage  $V_{\text{init}}$ , which is lower than the high threshold voltage,  $V_{\rm H}$ , and higher than the low threshold voltage,  $V_L$ , and the output "Select" of the control unit is set to high. When the slope of the sawtooth signals is determined, the signal "Hit" in the VCSDL goes high to enable the PD and disconnect  $V_{\text{ctrl}}$  from its initial voltage. The PD converts the phase error between  $\mathrm{CK}_\mathrm{REF}$  and  $\mathrm{DLL}_\mathrm{out}$  to control the charge pump. The charge pump and the loop filter generate the control voltage  $V_{\text{ctrl}}$  to reduce this phase error. The control unit is shown in Fig. 3. When  $V_{\rm ctrl}$  is lower than the high threshold voltage  $V_{\rm H}$ , "Select" is high and the input clock CK<sub>REF</sub> is chosen as  $CK_{int}$ . Once  $V_{ctrl}$  is larger than the high threshold voltage  $V_{\rm H}$ , the control signal, MAX, goes high and the inverse  $CK_{REF}$  is adopted. Due to the finite input offset voltage in a

Fig. 2. Proposed DLL and the truth table of its control unit.

comparator, the reference voltage,  $V_L$ , is higher than the comparator's offset voltage. The reference voltage,  $V_{\rm H}$ , is lower than the supply voltage by the same amount. From simulations, the input offset voltage of the comparator is smaller than 80 mV in this work. Assume the propagation delays of the inverter and the transmission gate in Fig. 2 are matched. When the multiplexer switches from CK<sub>REF</sub> to its inverse one for the VCSDL, it is equivalent to increase the delay by  $0.5T_{\text{REF}}$  where  $T_{\text{REF}}$  is the period of  $CK_{REF}$ . The proposed DLL can have the infinite phase shift, since the DLL generates the phase shift from  $0^{\circ}$  to 360°. Note that the latency of the VCSDL is neglected and the input clock for the VCSDL is CK<sub>REF</sub> in Fig. 1(c). Once the latency of the VCSDL is considered, the inverted CK<sub>REF</sub> may be selected as the input clock of the VCSDL. Finally, the VCSDL is adjusted to align the input clock  $CK_{REF}$  and the output of the DLL, DLL<sub>out</sub>. By changing the polarity of the input clock of the VCSDL, it increases the delay by  $0.5T_{\text{REF}}$  where  $T_{\text{REF}}$  is the period of CK<sub>REF</sub>. The phase switching scheme yields larger transients in this DLL. The transients can be decreased by using a large charge pump current.

This proposed DLL has two advantages. First, the infinite phase shift capability is achieved in a single-loop DLL. Therefore, the chip area and power can be reduced. Second, the jitter performance of the proposed DLL is improved, compared to the dual-loop DLLs. It is because the delay line of the peripheral DLL contributes an extra jitter to the core DLL in the dual

Fig. 3. Control unit.

loop DLL. Although the proposed VCSDL achieves a very wide range, its highest operation frequency is limited and it can not be used for multi-phase clock generation.

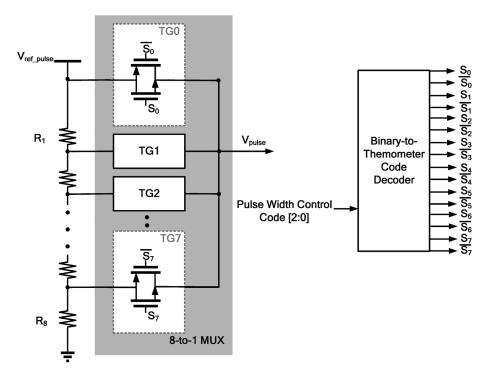

## C. 3-bit DAC

The pulsewidth of the output clock is controlled by  $V_{\rm PW}$ , which is the output voltage of the 3-bit DAC. This 3-bit DAC shown in Fig. 4 is similar to [14]. It consists of a resistor ladder, a binary-to-thermometer code decoder and an 8-to-1 multiplexer. This 8-to-1 multiplexer, which is realized by the CMOS transmission gates, selects  $V_{\rm PW}$  from the resistor ladder. The variable output duty cycle of the DLL is given as

$$\Delta_{\text{duty\_cycle}} = \frac{K_{\text{VCSDL}}}{T_{\text{REF}}} \cdot V_{\text{PW}}$$

$$= \frac{K_{\text{VCSDL}}}{T_{\text{REF}}} \cdot V_{\text{ref\_pulse}} \cdot \frac{N}{2^3} \cdot 100\%,$$

$$0 \le N \le 7 \qquad (1)$$

Fig. 4. The 3-bit DAC.

Fig. 5. Phase detector.

where  $K_{\text{VCSDL}}$  (sec/V) is the gain of the VCSDL,  $V_{\text{ref-pulse}}$  is the reference voltage of this 3-bit DAC, and N is the equivalent pulsewidth control code of the 3-bit DAC [14].

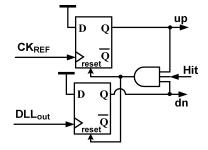

# D. Other Circuits

In this work, to mitigate the static phase error, when both the control signals, the charge pump in [12] is used here. A dynamic PD [15] is shown in Fig. 5 to achieve a higher operation frequency. The comparator in the DLL is realized by a differential amplifier with cascaded inverters.

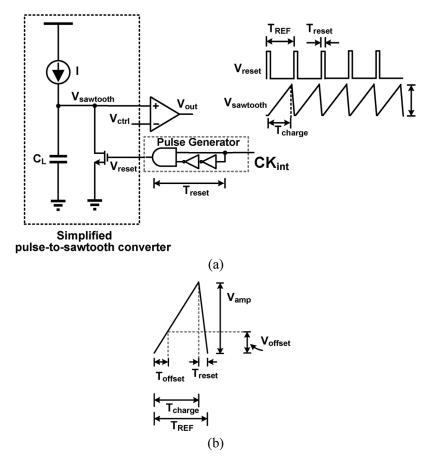

# III. THE ANALYSIS OF THE PROPOSED VCSDL

The pulse-to-sawtooth converter in Fig. 1(b) converts the internal clock to generate the sawtooth signal. The sawtooth signal and the control voltage  $V_{\rm ctrl}$  are compared by the comparator to determine the delay range of the VCSDL. Thus, the delay range of the VCSDL is subject to the non-ideal effects, such as the offset voltage of the comparator, the propagation delay of the pulse generator, mismatch between current sources and mismatch between the capacitors in the pulse-to-sawtooth converter. Fig. 6(a) shows a simplified pulse-to-sawtooth converter where a constant current source I and a capacitor  $C_L$  are

used. Since the comparator may have the finite offset voltage, the amplitude of the sawtooth signal is not exactly equal to  $V_{\text{ref\_amp}}$ . Here the amplitude of the sawtooth signal is assumed to be  $V_{\text{amp}}$ . Fig. 6(b) shows the expanded sawtooth signal. The charging time  $T_{\text{charge}}$  is approximated as

$$T_{\text{charge}} \approx V_{\text{amp}} \cdot \frac{C_L}{I}.$$

(2)

Moreover,  $T_{\text{charge}} = T_{\text{REF}} - T_{\text{reset}}$  where  $T_{\text{reset}}$  is the reset time to discharge the capacitor in the pulse-to-sawtooth converter. When  $V_{\text{ctrl}}$  is equal to  $V_{\text{amp}}$ , the maximum delay range  $T_{\text{VCSDL,max}}$  of this VCSDL is given as

$$T_{\text{VCSDL,max}} = \frac{C_L}{I} (V_{\text{amp}} - V_{\text{offset}})$$

(3)

where  $V_{\text{offset}}$  is the equivalent offset voltage of the comparator. By changing the polarity of the input clock of the VCSDL, it increases the delay by  $0.5T_{\text{REF}}$  where  $T_{\text{REF}}$  is the period of CK<sub>REF</sub>. Therefore, to have the infinite phase shift for the proposed DLL,  $T_{\text{VCSDL,max}}$  should meet the following constraint

$$T_{\text{VCSDL,max}} > 0.5T_{\text{REF}}$$

. (4)

From (3) and (4), the maximum current in the pulse-to-sawtooth converter can be given as

$$I < \frac{(V_{\rm amp} - V_{\rm offset}) \cdot C_L}{0.5T_{\rm REF}}.$$

(5)

To generate the signals,  $V_{\text{out,rise}}$  and  $V_{\text{out,fall}}$ , the amplitude of the sawtooth signal should be larger than the equivalent offset voltage,  $V_{\text{offset}}$ , of the comparator. Therefore,  $V_{\text{amp}}$  is expressed as

$$V_{\rm amp} = \frac{I}{C} (T_{\rm REF} - T_{\rm reset}) > V_{\rm offset}.$$

(6)

Fig. 6. (a) Simplified pulse-to-sawtooth converter and its timing diagram. (b) Expanded sawtooth signal.

The minimum current source in the pulse-to-sawtooth converter can be rewritten as

$$I > \frac{V_{\text{offset}} \cdot C_L}{(T_{\text{REF}} - T_{\text{reset}})}.$$

(7)

To achieve the infinite phase shift for the proposed DLL, the current source in the pulse-to-sawtooth converter should meet the constraints in (5) and (7). It can be expressed as

$$\frac{V_{\text{offset}} \cdot C_L}{(T_{\text{REF}} - T_{\text{reset}})} < I < \frac{(V_{\text{amp}} - V_{\text{offset}}) \cdot C_L}{0.5T_{\text{REF}}}.$$

(8)

In this work,  $T_{\text{reset}}$  is equal to the propagation delay of the pulse generator which is composed of two inverters and one AND gate.  $T_{\text{reset}}$  is around 170 ps in our process. The reference voltage,  $V_{\text{ref\_amp}}$ , is chosen as 0.6 V. In the pulse-to-sawtooth converter, the current source is adjustable within  $I_{\text{REF}}$  and  $31I_{\text{REF}}$ , which is controlled by 4 bits. The offset voltage,  $V_{\text{offset}}$ , of the comparator is sensitive to the PVT variations. To have the operation frequency range of this DLL from 50 to 500 MHz,  $I_{\text{REF}}$  and  $C_L$  in the pulse-to-sawtooth converter is chosen as 30  $\mu$ A and 0.3 pF, respectively, to overcome the variation of  $V_{\text{offset}}$  and fulfill the constraint of (8).

### **IV. EXPERIMENTAL RESULTS**

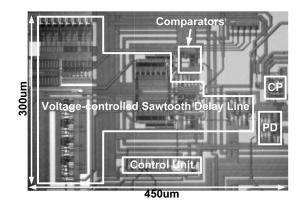

The proposed DLL has been fabricated in a 0.18  $\mu$ m CMOS process. Fig. 7 shows the die photo and its core area is 0.14 mm<sup>2</sup>.

Fig. 7. Die photo.

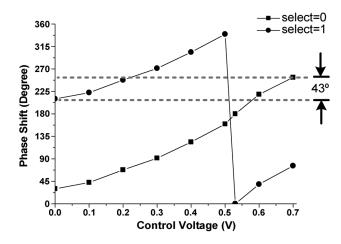

The DLL operates from 50 to 500 MHz for a 1.5 V supply and it dissipates 6 mW at 500 MHz. The control signal of the multiplexer, "Select", in Fig. 2 can be externally controlled to demonstrate the variable phase range of the proposed DLL. Fig. 8 shows the measured transfer curve of the VCSDL at 500 MHz. The measured phase shift of the VCSDL is from 30° to 253°, when "Select" in the multiplexer in Fig. 2 is high. The variable phase range of 223° is around  $0.62T_{\text{REF}}$ . When "Select" is low, the variable phase shift of the VCSDL is from 210° to 436°. For (4), it demonstrates that  $T_{\text{VCSDL,max}} > 0.5T_{\text{REF}}$ . By changing the polarity of the reference clock, the proposed DLL can generate the phase shift from 0° to 360°. In Fig. 8, the overlapped

Fig. 8. Measured transfer curve of the voltage-controlled sawtooth delay line.

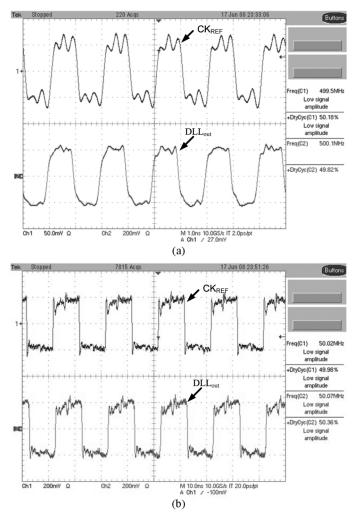

Fig. 9. (a) Output clock with 50% duty cycle at 500 MHz. (b) Output clock with 50% duty cycle at 50 MHz.

phase range is 43°. When the proposed DLL is used to eliminate the phase error between  $CK_{REF}$  and  $DLL_{out}$ , the control signal of the multiplexer, "Select", is controlled internally by the control unit in Fig. 2. Fig. 9(a) and (b) show the output clocks with duty cycle of 50% when the proposed DLL is locked at

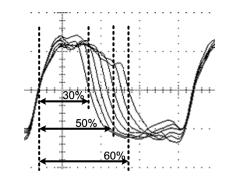

Fig. 10. Measured output clocks with different duty cycles at 500 MHz.

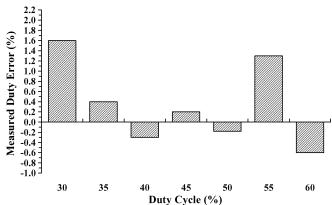

Fig. 11. Measured duty cycle errors for the output clock at 500 MHz.

500 MHz and 50 MHz, respectively. The excessive amount of reflections for the output clock waveforms in Fig. 9 and Fig. 10 are due to inadequate termination and cross coupling between signals. Fig. 10 shows the measured output clocks with different duty cycles at 500 MHz. The measured duty cycles of the output clocks at 500 MHz can range from 30% to 60% in a step of 5%. The measured duty cycle errors at 500 MHz are also shown in Fig. 11.

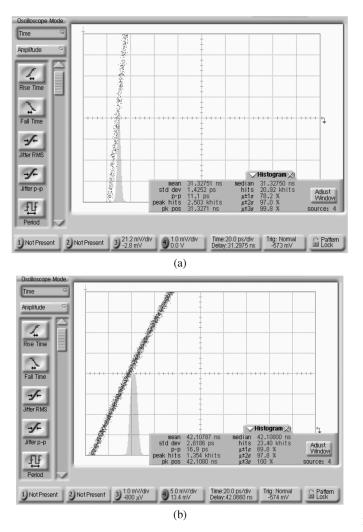

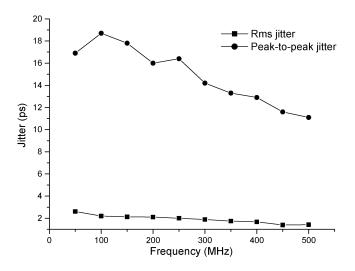

Fig. 12(a) and (b) show the measured period jitter histogram of the output clock at 500 MHz and 50 MHz, respectively. Fig. 13 shows the measured period jitters for different input frequencies. At 50 MHz, the measured rms and peak-to-peak period jitters are 2.62 ps and 16.9 ps, respectively. As the operation frequency goes up to 500 MHz, the measured rms and peak-to-peak period jitters go down to 1.43 ps and 11.1 ps, respectively.

The figures-of-merit (FOMs) for both power consumption and chip area are shown in Fig. 14(a). FOM<sub>power</sub> [13] is defined as

$$FOM_{POWER} = \frac{Power \ consumption(mW)}{Maximum \ operation \ frequency(MHz)}_{(9)}$$

where the power consumption is represented in mW and the maximum operation frequency is represented in MHz.

where the power consumption is represented in mW and the maximum operation frequency is represented in MHz.  $FOM_{AREA}$  [13] is defined as

$$FOM_{AREA} = \frac{Active area(mm^2)}{Channel \ length^2 \cdot Maximum \ delay(\mu m^2 \cdot ns)}$$

(10)

Fig. 12. Measured period jitter histogram for the output clock at (a) 500 MHz and (b) 50 MHz.

Fig. 13. Measured peak-to-peak and rms period jitters for different input frequencies.

where the occupied area is in square millimeters, the minimum channel length is in micrometers, and the maximum delay is the

Fig. 14. (a) Figures-of-merit for power and area. (b) Overall figures-of-merit for DLL and jitter performance.

delay time for the lowest operation frequency in nanoseconds. Fig. 14(b) shows the overall FOM and the jitter performance. The overall FOM is defined as the product of the  $FOM_{POWER}$  and the  $FOM_{AREA}$ . The proposed DLL achieves the smallest FOM among the works in Fig. 14(b). Table I gives the performance summary and comparison with the previous works.

# V. CONCLUSION

A wide range DLL with infinite phase shift and digital-controlled duty cycle is presented. By changing the polarity of the input clock of the voltage-controlled sawtooth delay line, this proposed DLL achieves infinite phase shift by only a single loop. Moreover, the analysis for the proposed VCSDL is also given. The experimental results show that the measured rms jitter and peak-to-peak jitter is 1.43 ps and 11.1 ps, respectively, at 500 MHz. Its power consumption is 6 mW for a supply of 1.5 V.

### ACKNOWLEDGMENT

The authors would like to thank National Chip Implementation Center (CIC), Taiwan, for fabricating the chips.

|                                       | [2]                 | [6]                 | [7]                 | [10]                | [11]                | [13]               | This work           |

|---------------------------------------|---------------------|---------------------|---------------------|---------------------|---------------------|--------------------|---------------------|

| Process                               | 0.35um              | 0.25um              | 0.18um              | 0.25um              | 0.35um              | 0.18um             | 0.18um              |

| Supply<br>Voltage                     | 3.3V                | 2.5V                | 1.8V                | 2.5V                | 3.3V                | 1.8V               | 1.5V                |

| Max.<br>Operation<br>Frequency        | 250MHz              | 600MHz              | 760MHz              | 1400MHz             | 1.27GHz             | 550MHz             | 500MHz              |

| Min.<br>Operation<br>Frequency        | 62.5MHz             | 150MHz              | 60MHz               | 770MHz              | 1GHz                | 40MHz              | 50MHz               |

| Output Duty<br>Cycle Control<br>Range | No                  | 50%                 | No                  | 25%~75%             | 35%~70%             | 50%                | 30%~60%             |

| Synchronous                           | Yes                 | Yes                 | Yes                 | No                  | Yes                 | Yes                | Yes                 |

| Infinite Phase<br>Shift               | No                  | Yes                 | Yes                 | No                  | No                  | No                 | Yes                 |

| Architecture                          | Single Loop         | Dual Loop           | Dual Loop           | No                  | Single Loop         | Single Loop        | Single Loop         |

| Peak-to-Peak<br>Jitter                | 29ps<br>@250MHz     | 54ps<br>@400MHz     | 39ps<br>@700MHz     | 10ps<br>@1GHz       | 19.6ps<br>@1.25GHz  | 12ps<br>@550MHz    | 11.1ps<br>@500MHz   |

| Power                                 | 41.6mW              | 60mW                | 63mW                | 18mW                | 150mW               | 12.6mW             | 6mW                 |

| Core Area                             | 0.08mm <sup>2</sup> | 0.13mm <sup>2</sup> | 0.19mm <sup>2</sup> | $0.05 \text{ mm}^2$ | 0.14mm <sup>2</sup> | 0.2mm <sup>2</sup> | 0.14mm <sup>2</sup> |

TABLE I PERFORMANCE SUMMARY AND COMPARISON

## REFERENCES

- M. Johnson and E. Hudson, "A variable delay line PLL for CPU-coprocessor synchronization," *IEEE J. Solid-State Circuits*, vol. 23, no. 10, pp. 1218–1223, Oct. 1988.

- [2] Y. Moon, J. Choi, K. Lee, D. K. Jeong, and M. K. Kim, "An all-analog multiphase delay-locked loop using a replica delay line for wide-range operation and low-jitter performance," *IEEE J. Solid-State Circuits*, vol. 35, no. 3, pp. 377–384, Mar. 2000.

- [3] H. H. Chang, J. W. Lin, C. Y. Yang, and S. I. Liu, "A wide-range delaylocked loop with a fixed latency of one clock cycle," *IEEE J. Solid-State Circuits*, vol. 37, no. 8, pp. 1021–1027, Aug. 2002.

- [4] S. Sidiropoulos and M. A. Horowitz, "A semidigital dual delay-locked loop," *IEEE J. Solid-State Circuits*, vol. 32, no. 11, pp. 1683–1692, Nov. 1997.

- [5] B. W. Garlepp, K. S. Donnelly, J. Kim, P. S. Chau, J. L. Zerbe, C. Huang, C. V. Tran, C. L. Portmann, D. Stark, Y.-F. Chan, T. H. Lee, and M. A. Horowitz, "A portable digital DLL for high-speed CMOS interface circuits," *IEEE J. Solid-State Circuits*, vol. 34, no. 5, pp. 632–644, May 1999.

- [6] Y. J. Jung, S. W. Lee, D. Shim, W. Kim, C. Kim, and S. I. Cho, "A dual-loop delay-locked loop using multiple voltage-controlled delay lines," *IEEE J. Solid-State Circuits*, vol. 36, no. 5, pp. 784–791, May 2001.

- [7] S. J. Bae, H. J. Chi, Y. S. Sohn, and H. J. Park, "A VCDL-based 60–760 MHz dual-loop DLL with infinite phase-shift capability and adaptivebandwidth scheme," *IEEE J. Solid-State Circuits*, vol. 40, no. 5, pp. 1119–1129, May 2005.

- [8] F. Yang, J. H. O'Neill, D. Inglis, and J. Othmer, "A CMOS low-power multiple 2.5–3.125-Gb/s serial link macrocell for high IO bandwidth network ICs," *IEEE J. Solid-State Circuits*, vol. 37, no. 12, pp. 1813–1821, Dec. 2002.

- [9] T. H. Lee, K. S. Donnelly, J. T. C. Ho, J. Zerbe, M. G. Johnson, and T. Ishikawa, "A 2.5 V CMOS delay-locked loop for an 18 Mbit, 500 Megabyte/s DRAM," *IEEE J. Solid-State Circuits*, vol. 29, no. 12, pp. 1491–1496, Dec. 1994.

- [10] F. Mu and C. Svensson, "Pulsewidth control loop in high-speed CMOS clock buffers," *IEEE J. Solid-State Circuits*, vol. 35, no. 2, pp. 134–141, Feb. 2000.

- [11] S. R. Han and S. I. Liu, "A 500-MHz-1.25 GHz fast-locking pulsewidth control loop with presettable duty cycle," *IEEE J. Solid-State Circuits*, vol. 39, no. 3, pp. 463–468, Mar. 2004.

- [12] J. G. Maneatis, "Low-jitter process-independent DLL and PLL based on self-biased techniques," *IEEE J. Solid-State Circuits*, vol. 31, no. 11, pp. 1723–1732, Nov. 1996.

- [13] R. J. Yang and S. I. Liu, "A 40–550 MHz harmonic-free all-digital delay-locked loop using a variable SAR algorithm," *IEEE J. Solid-State Circuits*, vol. 42, no. 2, pp. 361–373, Feb. 2007.

- [14] D. A. Johns and K. Martin, Analog Integrated Circuit Design. New York: Wiley, 1997.

[15] S. Kim, K. Lee, Y. Moon, D. K. Jeong, Y. Choi, and H. K. Lim, "A 960 Mb/s/pin interface for skew-tolerant bus using low jitter PLL," *IEEE J. Solid-State Circuits*, vol. 32, no. 5, pp. 691–700, May 1997.

**Chao-Chyun Chen** (S'03–M'08) was born in Taipei, Taiwan, on April 14, 1978. He received the B.S. degree in electrical engineering from the National Central University, Chugng-Li, Taiwan, in 2000, and the M.S. degree in electrical engineering from Yuan-Ze University, Chugng-Li, Taiwan, in 2002. He is currently pursuing the Ph.D. degree in electrical engineering at the National Taiwan University, Taipei.

His research interests are PLL, DLL, and high-speed interfaces for gigabit transceivers.

**Shen-Iuan Liu** (S'88–M'93–SM'03) was born in Keelung, Taiwan, in 1965. He received the B.S. and Ph.D. degrees in electrical engineering from National Taiwan University (NTU), Taipei, Taiwan, in 1987 and 1991, respectively.

During 1991–1993, he served as a Second Lieutenant in the Chinese Air Force. During 1991–1994, he was an Associate Professor in the Department of Electronic Engineering, National Taiwan Institute of Technology. He joined the Department of Electrical Engineering, NTU, in 1994, where he has been a Pro-

fessor since 1998. His research interests are in analog and digital integrated circuits and systems.

Dr. Liu has served as chair of the IEEE SSCS Taipei Chapter in 2004-2008. He has served as general chair of the 15th VLSI Design/CAD Symposium, Taiwan (2004) and as Program Co-chair of the Fourth IEEE Asia-Pacific Conference on Advanced System Integrated Circuits, Fukuoka, Japan (2004). He was the recipient of the Engineering Paper Award from the Chinese Institute of Engineers in 2003, the Young Professor Teaching Award from MXIC Inc., the Research Achievement Award from NTU, and the Outstanding Research Award from the National Science Council in 2004. He has served as a technical program committee member for ISSCC in 2006-2008 and A-SSCC since 2005. He was an Associate Editor for IEEE TRANSACTIONS ON CIRCUITS AND SYSTEMS-II: EXPRESS BRIEFS in 2006-2007. Now, he is an Associate Editor for IEEE JOURNAL OF SOLID-STATE CIRCUITS since 2006 and an Associate Editor for IEEE TRANSACTIONS ON CIRCUITS AND SYSTEMS-I: REGULAR PAPERS since 2008. He is also an Associate Editor for IEICE (The Institute of Electronics, Information and Communication Engineers) Transactions on Electronics since 2008. He joined the Editorial Board of Research Letters in Electronics in 2008. He is a senior member of IEEE and a member of IEICE.