| Title            | A 300 nW, 15 ppm/ , 20 ppm/V CMOS Voltage Reference Circuit Consisting of Subthreshold MOSFETs                                                                                                                                                                                                                                                   |  |  |  |  |  |

|------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|

| Author(s)        | Ueno, Ken; Hirose, Tetsuya; Asai, Tetsuya; Amemiya, Yoshihito                                                                                                                                                                                                                                                                                    |  |  |  |  |  |

| Citation         | IEEE Journal of Solid-State Circuits, 44(7), 2047-2054<br>https://doi.org/10.1109/JSSC.2009.2021922                                                                                                                                                                                                                                              |  |  |  |  |  |

| Issue Date       | 2009-07                                                                                                                                                                                                                                                                                                                                          |  |  |  |  |  |

| Doc URL          | http://hdl.handle.net/2115/39949                                                                                                                                                                                                                                                                                                                 |  |  |  |  |  |

| Rights           | © 2009 IEEE. Personal use of this material is permitted. However, permission to reprint/republish this material for advertising or promotional purposes or for creating new collective works for resale or redistribution to servers or lists, or to reuse any copyrighted component of this work in other works must be obtained from the IEEE. |  |  |  |  |  |

| Туре             | article                                                                                                                                                                                                                                                                                                                                          |  |  |  |  |  |

| File Information | jssc_ueno2009.pdf                                                                                                                                                                                                                                                                                                                                |  |  |  |  |  |

# A 300 nW, 15 ppm/°C, 20 ppm/V CMOS Voltage Reference Circuit Consisting of Subthreshold MOSFETs

Ken Ueno, Student Member, IEEE, Tetsuya Hirose, Member, IEEE, Tetsuya Asai, Member, IEEE, and Yoshihito Amemiya

Abstract—A low-power CMOS voltage reference was developed using a 0.35  $\mu$ m standard CMOS process technology. The device consists of MOSFET circuits operated in the subthreshold region and uses no resistors. It generates two voltages having opposite temperature coefficients and adds them to produce an output voltage with a near-zero temperature coefficient. The resulting voltage is equal to the extrapolated threshold voltage of a MOSFET at absolute zero temperature, which was about 745 mV for the MOSFETs we used. The temperature coefficient of the voltage was 7 ppm/°C at best and 15 ppm/°C on average, in a range from -20 to  $80^{\circ}$ C. The line sensitivity was 20 ppm/V in a supply voltage range of 1.4–3 V, and the power supply rejection ratio (PSRR) was -45 dB at 100 Hz. The power dissipation was 0.3  $\mu$ W at  $80^{\circ}$ C. The chip area was 0.05 mm². Our device would be suitable for use in subthreshold-operated, power-aware LSIs.

*Index Terms*—CMOS, voltage reference, ultra-low power, subthreshold, weak inversion, process variation, die-to-die variation, power-aware LSIs.

### I. INTRODUCTION

NE of the promising areas of research in microelectronics is the development of ultra-low power LSIs that operate in the subthreshold region of MOSFETs, i.e., a region at which the gate-source voltage of MOSFETs is lower than the threshold voltage [1], [2]. Such LSIs would be suitable for use in poweraware LSI applications such as portable mobile devices, implantable medical devices, and smart sensor networks [3]. These devices have to operate with ultra-low power, e.g., a few microwatts or less [3]-[5] because they will probably be placed under conditions where they have to get the necessary energy from poor energy sources such as microbatteries and environmental energy sources [6]. As a step toward such LSIs, we first need to develop a voltage reference circuit that can operate with an ultra-low current, several tens of nanoamperes or less. To achieve such low power operation, the circuit has to be operated in the subthreshold region of MOSFET.

A voltage reference is one of the important building blocks for analog, digital, and mixed-signal circuit systems in micro-

Manuscript received November 07, 2008; revised March 09, 2009. Current version published June 24, 2009. This work was supported by VLSI Design and Education Center (VDEC), the University of Tokyo in collaboration with Cadence Design Systems, Inc.

K. Ueno, T. Asai, and Y. Amemiya are the Department of Electrical Engineering, Hokkaido University, Sapporo 060-0814, Japan (e-mail: k\_ueno@sapiens-ei.eng.hokudai.ac.jp).

T. Hirose is the Department of Electrical and Electronics Engineering, Kobe University, Kobe 657-8501, Japan (e-mail: hirose@eedept.kobe-u.ac.jp).

Digital Object Identifier 10.1109/JSSC.2009.2021922

electronics. It generates a constant reference voltage for other various components such as operational amplifiers, comparators, and AD/DA converters. For this purpose, bandgap reference circuits with CMOS-based vertical bipolar transistors are conventionally used in CMOS LSIs [7], [8]. However, they need resistors with a high resistance of several hundred megaohms to achieve low-current, subthreshold operation. Such a high resistance needs a large area to be implemented, and this makes conventional bandgap references unsuitable for use in ultra-low power LSIs. Therefore, modified voltage reference circuits for low-power LSIs have been reported (see [9]-[13]). However, these circuits have various problems. For example, their power dissipations are still large, and their outputs voltages are sensitive to supply voltage and temperature variations; these are quite inconvenient for practical use in ultra-low power LSIs. Moreover, the effect of the process variations on the reference voltage was not discussed in detail.

To solve these problems, we developed a new voltage reference that can operate with sub-microwatt power dissipation and has less temperature sensitivity and a smaller line sensitivity [14] than the reported works [9]-[13]. Our device consists of subthreshold MOSFET circuits and uses no resistors. It generates two voltages having opposite temperature coefficients (TCs), i.e., a MOSFET threshold voltage with a negative TC and a multiple of the thermal voltage with a positive TC, and adds them to produce an output voltage with a zero TC. The output voltage is equal to the threshold voltage of a MOSFET at 0 K and is about 745 mV for MOSFETs we used. The voltage is quite insensitive to temperature and the supply voltage variations, although its value fluctuates with process variation. By utilizing the nature of the reference voltage, which changes with the process conditions of threshold voltage in each LSI chip, the circuit can be used as an elementary circuit block for on-chip process compensation systems. The following sections provide the details on our device. Section II describes the principle of our voltage reference and discusses the effect of process variations. Section III explains the method of designing the circuit with a SPICE simulator. Section IV shows the characteristics of a prototype device we made using a 0.35  $\mu$ m standard CMOS process technology. A small TC of 7 ppm/°C and a line sensitivity of 20 ppm/V were achieved.

# II. CIRCUIT CONFIGURATION

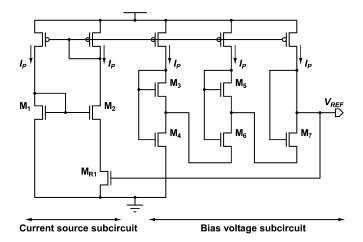

The principle of our voltage reference circuit is illustrated in Fig. 1. The circuit consists of a current source subcircuit

Fig. 1. Schematic of our voltage reference circuit.

and a bias-voltage subcircuit. The current source subcircuit is a modified  $\beta$  multiplier self-biasing circuit that uses a MOS resistor M<sub>R1</sub> instead of ordinary resistors. It generates a current,  $I_P$ . The bias-voltage subcircuit accepts current  $I_P$  through pMOS current mirrors and produces an output voltage (i.e., reference voltage),  $V_{\text{REF}}$ . The bias-voltage subcircuit consists of a transistor  $(M_4)$  and two source-coupled pairs  $(M_3-M_6)$ and  $M_5$ – $M_7$ ). The gate-source voltages of  $M_3$ – $M_7$  in the bias-voltage subcircuit and M<sub>R1</sub> in the current source subcircuit form a closed loop [15], [16]. All the MOSFETs except for  $m M_{R1}$  are operated in the subthreshold region. The MOS resistor  $M_{R1}$  is operated in a strong-inversion, deep-triode region. The circuit generates two voltages with a negative TC and a positive TC and combines them to produce a constant voltage with a zero TC. The following sections describe the operation in detail.

# A. Operation Principle

The subthreshold drain current  $I_D$  of a MOSFET is an exponential function of the gate-source voltage  $V_{\rm GS}$  and the drain-source voltage  $V_{\rm DS}$ , and given by

$$I_D = KI_0 \exp\left(\frac{V_{\text{GS}} - V_{\text{TH}}}{\eta V_T}\right)$$

$$\times \left(1 - \exp\left(-\frac{V_{\text{DS}}}{V_T}\right)\right),$$

$$I_0 = \mu C_{\text{OX}}(\eta - 1)V_T^2,$$

(1)

where K is the aspect ratio (=W/L) of the transistor,  $\mu$  is the carrier mobility,  $C_{\rm OX}$  is the gate-oxide capacitance,  $V_T(=k_BT/q)$  is the thermal voltage,  $k_B$  is the Boltzmann constant, T is the absolute temperature, and q is the elementary charge,  $V_{\rm TH}$  is the threshold voltage of a MOSFET, and  $\eta$  is the subthreshold slope factor [1], [17]. For  $V_{\rm DS}>0.1$  V, current  $I_D$  is almost independent of  $V_{\rm DS}$  and given by

$$I_D = KI_0 \exp\left(\frac{V_{\rm GS} - V_{\rm TH}}{\eta V_T}\right). \tag{2}$$

In the current-source subcircuit, gate-source voltage  $V_{\rm GS1}$  in  $\rm M_1$  is equal to the sum of gate-source voltage  $V_{\rm GS2}$  in  $\rm M_2$  and drain-source voltage  $V_{\rm DSR1}$  in  $\rm M_{R1}$ , i.e.,

$$V_{\text{GS1}} = V_{\text{GS2}} + V_{\text{DSR1}}.$$

(3)

Because currents  $I_P$  in  $M_1$  and in  $M_2$  are equal to each other, (3) can be rewritten as

$$V_{\text{DSR1}} = \eta V_T \ln(K_2/K_1).$$

(4)

MOS resistor  $M_{R1}$  is operated in a strong-inversion, deep-triode region, so its resistance  $R_{M_{R1}}$  is given by

$$R_{M_{R1}} = \frac{1}{K_{R1}\mu C_{\text{OX}}(V_{\text{REF}} - V_{\text{TH}})}.$$

(5)

From (3), (4), and (5), we arrive at the expression

$$I_{P} = \frac{V_{\text{DSR1}}}{R_{M_{R1}}} = K_{R1} \mu C_{\text{OX}} (V_{\text{REF}} - V_{\text{TH}}) \eta V_{T} \ln(K_{2}/K_{1})$$

(6)

for current  $I_P$ . In the bias-voltage subcircuit, the gate-source voltages ( $V_{\rm GS3}$  through  $V_{\rm GS7}$ ) of the transistors form a closed loop, and the currents in  $M_4$  and  $M_6$  are  $3I_P$  and  $2I_P$ . Therefore, we find that output voltage  $V_{\rm REF}$  of the circuit is given by

$$V_{\text{REF}} = V_{\text{GS4}} - V_{\text{GS3}} + V_{\text{GS6}} - V_{\text{GS5}} + V_{\text{GS7}}$$

$$= V_{\text{GS4}} + \eta V_T \ln \left( \frac{2K_3K_5}{K_6K_7} \right)$$

$$= V_{\text{TH}} + \eta V_T \ln \left( \frac{3I_P}{K_4I_0} \right) + \eta V_T \ln \left( \frac{2K_3K_5}{K_6K_7} \right)$$

(7)

where we assumed that the mismatch between the threshold voltages of the transistors can be ignored. Equation (7) shows that  $V_{\rm REF}$  can be expressed as a sum of the gate-source voltage  $V_{\rm GS4}$  and thermal voltage  $V_T$  scaled by the transistor sizes. Because  $V_{\rm TH}$  has a negative TC and  $V_T$  has a positive TC, output voltage  $V_{\rm REF}$  with a zero TC can be obtained by adjusting the size of the transistors.

The temperature dependence of the threshold voltage can be given by

$$V_{\rm TH} = V_{\rm TH0} - \kappa T \tag{8}$$

where  $V_{\rm TH0}$  is the threshold voltage at 0 K, and  $\kappa$  is the TC of  $V_{\rm TH}$  [18]. Equations (6) and (8) show that output voltage  $V_{\rm REF}$  can be rewritten as

$$V_{\text{REF}} = V_{\text{TH0}} - \kappa T + \eta V_T \ln \left\{ \frac{6\eta K_{R1} K_3 K_5 (V_{\text{REF}} - V_{\text{TH}})}{K_4 K_6 K_7 (\eta - 1) V_T} \ln \left( \frac{K_2}{K_1} \right) \right\}. \quad (9)$$

The TC of  $V_{\rm REF}$  is given by

$$\frac{dV_{\text{REF}}}{dT} = -\kappa + \frac{\eta k_B}{q} \times \ln \left\{ \frac{6\eta K_{R1} K_3 K_5 (V_{\text{REF}} - V_{\text{TH}})}{K_4 K_6 K_7 (\eta - 1) V_T} \ln \left(\frac{K_2}{K_1}\right) \right\} + \eta V_T \left\{ \frac{1}{V_{\text{REF}} - V_{\text{TH}}} \left(\frac{dV_{\text{REF}}}{dT} + \kappa\right) - \frac{1}{T} \right\}.$$

(10)

On condition that  $V_{\rm REF}-V_{\rm TH0}\ll \kappa T$  and  $\eta V_T\ll \kappa T$ , the TC of  $V_{\rm REF}$  can be rewritten as

$$\frac{dV_{\text{REF}}}{dT} = -\kappa + \frac{\eta k_B}{q} \ln \left\{ \frac{6q\eta\kappa}{k_B(\eta - 1)} \frac{K_{R1}K_3K_5}{K_4K_6K_7} \ln \left(\frac{K_2}{K_1}\right) \right\}$$

(11)

(see the Appendix for the derivation of (11)). Therefore, a zero TC can be achieved on condition that

$$-\kappa + \frac{\eta k_B}{q} \ln \left\{ \frac{6q\eta\kappa}{k_B(\eta - 1)} \frac{K_{R1}K_3K_5}{K_4K_6K_7} \ln \left( \frac{K_2}{K_1} \right) \right\} = 0. (12)$$

A zero TC voltage can be obtained by setting the aspect ratios  $K_i$  in accordance with (12). From (9) and (12), we find that

$$V_{\text{REF}} = V_{\text{TH0}}.\tag{13}$$

This shows that the circuit generates a voltage equal to the threshold voltage of MOSFETs at 0 K.

Using (6), (8), and (9), we can express current  $I_P$  as

$$I_P = K_{R1} \mu C_{\text{OX}} \kappa T \eta V_T \ln \left( \frac{K_2}{K_1} \right). \tag{14}$$

The current is determined only by the aspect ratios  $(K_1, K_2,$  and  $K_{R1})$  and the temperature coefficient  $(\kappa)$  of the threshold voltage of MOSFETs, and it is independent of  $V_{\rm TH0}$ . The dependence of  $\kappa$  on process variation is far smaller than that of  $V_{\rm TH0}$  as shown in the next section, so current  $I_P$  is less dependent on process variations.

The TC of  $I_P$  is given by

$$\frac{1}{I_P}\frac{\partial I_P}{\partial T} = \frac{1}{u}\frac{\partial \mu}{\partial T} + \frac{1}{T}\frac{\partial T}{\partial T} + \frac{1}{V_T}\frac{\partial V_T}{\partial T}.$$

(15)

The temperature dependence of the mobility can be expressed as

$$\mu = \mu_0 \left(\frac{T}{T_0}\right)^{-m} \tag{16}$$

where  $\mu_0$  is the mobility at temperature  $T_0$ , and m is the mobility temperature exponent [18]. Equations (15) and (16) show that the TC of the current can be given by

$$\frac{1}{I_P}\frac{\partial I_P}{\partial T} = \frac{2-m}{T}. (17)$$

The value of m is about 1.5 in standard CMOS process technologies, so current  $I_P$  has a positive TC and increases with temperature.

# B. Dependence of Output Voltage on Temperature and Process Variation

The output voltage  $V_{\rm REF}$  of our circuit is equal to the threshold voltage of MOSFETs at 0 K, so its value depends on process variation. However, its TC is quite insensitive to process variation and is very small in a wide temperature range. These are discussed in the following.

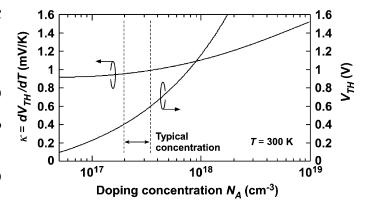

Fig. 2. Threshold voltage  $(V_{\rm TH})$  and its TC  $(\kappa = dV_{\rm TH}/dT)$  as a function of channel doping concentration  $(N_A)$ , calculated using 0.35  $\mu$ m standard CMOS parameters at room temperature.

Process variations can be classified into two categories: i.e., within-die (WID) (intra-die) variation and die-to-die (D2D) (inter-die) variation [19]-[21]. The WID variation causes mismatches between transistor parameters within a chip and affects the relative accuracy of the parameters. It can be reduced by using large-sized transistors and various analog layout techniques [21], [22]. In our circuit design, we used a large WLvalues and a common centroid technique. In contrast, the D2D variation affects the absolute accuracy of transistor parameters and is difficult to reduce with existing techniques. Our circuit generates voltage  $V_{\rm REF}$  equal to the threshold voltage of a MOSFET at 0 K, so the D2D variation will directly affect  $V_{\rm REF}$ . On the other hand, the TC of  $V_{\rm REF}$  is quite insensitive to process variations and is very small in a wide temperature range. We show these characteristics with the aid of computer simulation.

The TC of the reference voltage is expressed by (11) and can be set to 0 if (12) is satisfied. Therefore  $\kappa$  (TC of the threshold voltage of MOSFETs) is the key parameter to achieving zero TC operation. The threshold voltage in (8) is theoretically given by

$$V_{\rm TH} = -\frac{E_g}{2q} + \psi_B + \frac{\sqrt{4\varepsilon_{\rm si}qN_A\psi_B}}{C_{\rm OX}},$$

$$\psi_B = V_T \ln\left(\frac{N_A}{n_i}\right), \tag{18}$$

where  $\psi_B$  is the difference between Fermi-level potential and intrinsic-level potential,  $\varepsilon_{\rm si}$  is the silicon permittivity,  $N_A$  is the channel doping concentration,  $n_i$  is the intrinsic carrier density, and  $E_g$  is the bandgap energy of silicon [17]. Equation (18) shows that the TC,  $(\kappa = dV_{\rm TH}/dT)$ , of the threshold voltage is given by

$$\kappa = -(2\eta - 1)\frac{k_B}{q} \left\{ \ln\left(\frac{\sqrt{N_c N_v}}{N_A}\right) + \frac{3}{2} \right\} + \frac{\eta - 1}{q} \frac{dE_g}{dT}$$

(19)

where  $N_c$  and  $N_v$  are the effective densities of states in the conduction and valence bands [17]. From (18) and (19), we find that both  $V_{\rm TH}$  and its temperature coefficient  $\kappa$  depend on channel

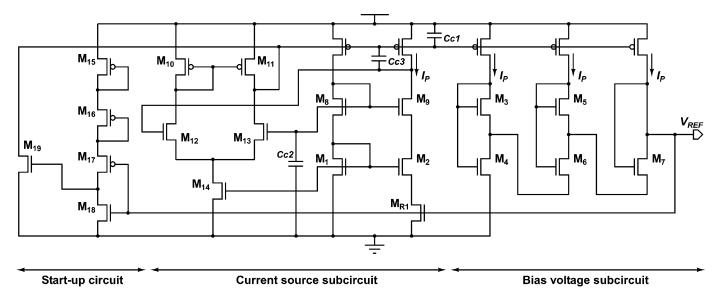

Fig. 3. Entire circuit of our voltage reference. All MOSFETs are operated in subthreshold region, except for MOS resistor  $M_{\rm R1}$ , which is operated in strong-inversion, triode region.

doping concentration  $N_A$ . This concentration is a process-dependent quantity, so  $\kappa$  can change with process variation. The change is very small, however, because  $\kappa$  is a logarithmic function of  $N_A$ . Therefore, the TC of  $V_{\rm TH}$  has little dependence on process variation.

To study the effect of process variation on the threshold voltage and its TC, we calculated (18) and (19) numerically using a set of 0.35  $\mu$ m CMOS parameters at room temperature. Fig. 2 shows the result, a plot of the calculated  $V_{\rm TH}$  and  $\kappa$  as a function of  $N_A$ . The dashed lines (2.0–3.3  $\times$  10<sup>17</sup> cm<sup>-3</sup>) represent the range of  $N_A$  for the CMOS process we used. In this concentration range, threshold voltage  $V_{\rm TH}$  changes by  $\pm$ 20% with  $N_A$ , while its temperature coefficient  $\kappa$  changes by only  $\pm$ 2%. Therefore, the TC of the output voltage hardly depends on process variation.

# C. Entire Configuration for Actual Circuit

The entire circuit we designed is illustrated in Fig. 3. Capacitors  $C_{C1}$ ,  $C_{C2}$ , and  $C_{C3}$  are used to prevent parasitic oscillation and noise disturbances. A differential amplifier  $M_{10}$ – $M_{14}$  and a current mirror  $M_8$ – $M_9$  are used to increase the power supply rejection ratio (PSRR) to reduce the line sensitivity of the circuit. A start-up circuit  $M_{15}$ – $M_{19}$  is used to avoid the stable state in the zero bias condition. Table I shows the size of transistors  $M_1$ – $M_7$  and  $M_{R1}$ .

#### III. SIMULATION RESULTS

We confirmed the operation of our circuit with the aid of a SPICE simulation using a set of 0.35  $\mu$ m standard CMOS parameters and assuming a 1.5 V power supply. To study the dependence of the output voltage on process variations, we performed Monte Carlo simulations assuming both D2D variation (e.g.,  $\Delta V_{\rm TH}, \Delta \mu, \Delta T_{\rm OX}, \Delta L, \Delta W$ ) and WID variation (e.g.,  $\sigma_{V_{\rm TH}}, \sigma_{\mu}, \sigma_{T_{\rm OX}}, \sigma_{L}, \sigma_{W}$ ) in transistor parameters. For WID variation, we assumed that every parameter shows a Gaussian distribution that depends on device area (e.g.,

TABLE I TRANSISTOR SIZES OF OUR CIRCUIT

| Transistor        | Value (W/L)                                                                                        |

|-------------------|----------------------------------------------------------------------------------------------------|

| $M_1$             | $60 \ \mu\text{m} \ / \ 3 \ \mu\text{m} = (3 \ \mu\text{m} \ / \ 3 \ \mu\text{m}) \times 20$       |

| $M_2$             | $300 \ \mu\text{m} \ / \ 3 \ \mu\text{m} = (3 \ \mu\text{m} \ / \ 3 \ \mu\text{m}) \times 100$     |

| $M_3$             | $252 \ \mu \text{m} \ / \ 3 \ \mu \text{m} = (3 \ \mu \text{m} \ / \ 3 \ \mu \text{m}) \times 84$  |

| $M_4$             | $6 \ \mu \text{m} / 3 \ \mu \text{m} = (3 \ \mu \text{m} / 3 \ \mu \text{m}) \times 2$             |

| $M_5$             | $252 \ \mu \text{m} \ / \ 3 \ \mu \text{m} = (3 \ \mu \text{m} \ / \ 3 \ \mu \text{m}) \times 84$  |

| $M_6$             | $6 \ \mu \text{m} / 3 \ \mu \text{m} = (3 \ \mu \text{m} / 3 \ \mu \text{m}) \times 2$             |

| $M_7$             | $6 \ \mu \text{m} / 3 \ \mu \text{m} = (3 \ \mu \text{m} / 3 \ \mu \text{m}) \times 2$             |

| $M_{\mathrm{R1}}$ | $4 \ \mu \text{m} \ / \ 150 \ \mu \text{m} = (2 \ \mu \text{m} \ / \ 150 \ \mu \text{m}) \times 2$ |

$\sigma_{V_{\rm TH}}=A_{V_{\rm TH}}/\sqrt{LW}$ ) [19]–[21]. For D2D variation, we assumed a uniform distribution (e.g.,  $-0.1~{\rm V}<\Delta V_{\rm TH}<0.1~{\rm V}$ ), which shows worst case corners independent of device area [19]–[21]. Let us call a Monte Carlo simulation for a set of parameters a "run".

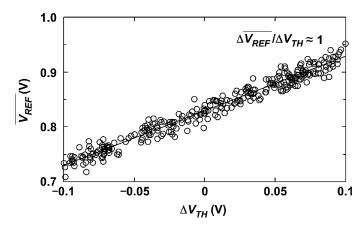

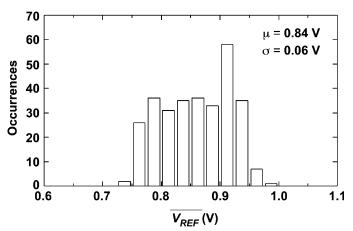

The results for 300 runs are depicted in Figs. 4 and 5. Fig. 4 shows the dispersion of  $V_{\rm REF}$  from the average value ( $\overline{V_{\rm REF}}$ ) of  $V_{\rm REF}$  in the temperature range from -20 to  $80^{\circ}{\rm C}$  as a function of D2D threshold-voltage variation  $\Delta V_{\rm TH}$ . Each open circle shows  $\overline{V_{\rm REF}}$  for a run. As discussed in Section II,  $V_{\rm REF}$  varies significantly with each run in a range from 0.7 V to 0.9 V; this reflects the variation in transistor parameters for each run. The value of  $\overline{V_{\rm REF}}$  depends linearly on  $\Delta V_{\rm TH}$  because the circuit produces the voltage equal to the 0-K threshold voltage of MOS-FETs. Fig. 5 shows the distribution of  $\overline{V_{\rm REF}}$ . The average of  $\overline{V_{\rm REF}}$  was 840 mV, and the standard deviation was 60 mV. The coefficient of variation  $\sigma/\mu$  was 7%, including D2D and WID variations.

#### IV. EXPERIMENTAL RESULTS

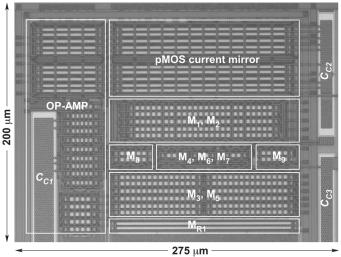

We fabricated a prototype chip, using a 0.35  $\mu$ m, 2-poly, 4-metal standard CMOS process. Fig. 6 shows a micrograph of

Fig. 4. Average output voltage as a function of D2D variation  $\Delta V_{\rm TH}$  of threshold voltage, as obtained from Monte Carlo simulation of 300 runs. Output voltage shows a linear dependence on threshold voltage  $(\Delta \overline{V}_{\rm REF}/\Delta V_{\rm TH}\approx 1)$ .

Fig. 5. Distribution of output voltage, as obtained from Monte Carlo simulation of 300 runs.

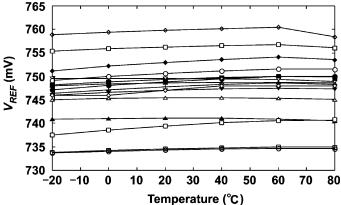

our chip. The chip area was  $0.055~\mathrm{mm^2}$  (=200  $\mu\mathrm{m} \times 275~\mu\mathrm{m}$ ). Fig. 7 shows measured output voltage  $V_{\mathrm{REF}}$  as a function of temperature, with supply voltage  $V_{\mathrm{DD}}$  as a parameter. Almost constant voltage was able to be achieved. The average of output voltage was 745 mV. The temperature variation was 0.48 mV in a temperature range from -20 to  $80^{\circ}\mathrm{C}$ , so the temperature coefficient was 7 ppm/°C.

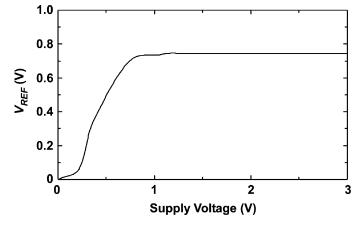

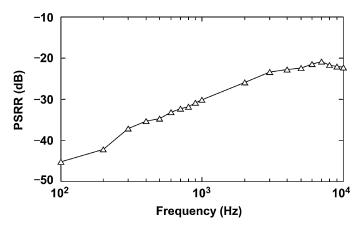

Fig. 8 shows output voltage  $V_{\rm REF}$  at room temperature as a function of supply voltage. The circuit operated correctly when supply voltage was higher than 1.4 V. The line sensitivity was 20 ppm/V in the power range of 1.4 to 3 V. Fig. 9 shows the power supply rejection ratio (PSRR) at room temperature with a 1 pF filtering capacitor and a 2 V power supply. The PSRR was  $-45~{\rm dB}$  at 100 Hz. Thus, we were able to achieve the voltage reference circuit that was almost independent of temperature and supply voltage.

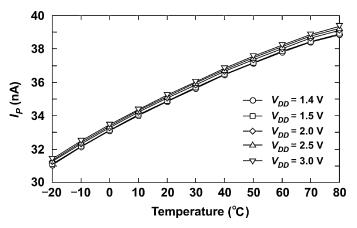

Fig. 10 shows measured current  $I_P$  as a function of temperature, with power supply voltage as a parameter. The current  $I_P$  was about 36 nA at room temperature and reached the maximum of 39 nA at 80°C. The power dissipation of the circuit with a 1.5 V power supply was 0.32  $\mu$ W at room temperature and varied from 0.28 to 0.35  $\mu$ W at temperatures from -20 to

Fig. 6. Micrograph of chip. Chip area is 0.055 mm<sup>2</sup>.

Fig. 7. Measured output voltage  $V_{\rm REF}$  as a function of temperature, with various supply voltages. Temperature coefficient was 7 ppm/ $^{\circ}$ C.

Fig. 8. Measured output voltage  $V_{\rm REF}$  at room temperature as a function of power supply. Line sensitivity was 20 ppm/V for supply voltages 1.4–3.0 V.

$80^{\circ}$ C. The temperature variation of the power dissipation was  $0.2\%/^{\circ}$ C.

To study the D2D variation of our device, we measured 17 samples, each on a different chip, and confirmed their constant-voltage operation. Fig. 11 shows measured output voltage  $V_{\rm REF}$  as a function of temperature for a 1.5 V supply voltage. The D2D

Fig. 9. Measured PSRR at room temperature with 1 pF filtering capacitor and a 2 V supply voltage.

Fig. 10. Measured current  $I_P$  as a function of temperature for different supply voltages.

variation in  $V_{\rm REF}$  was 25 mV. This value was far smaller than expected from the Monte Carlo simulation. This is so because the sample chips were fabricated from the same wafer, the variation of the reference voltage became smaller, and in our simulations, we assumed a uniform distribution for the D2D variation. This seems, however, to be an overestimation on the D2D variation, and in practice, a broad Gaussian distribution would be more suitable to represent the D2D variation.

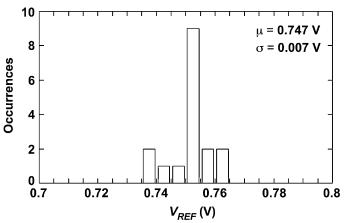

Temperature coefficients from 7 to 45 ppm/°C were observed in the 17 samples. The average TC of  $V_{\rm REF}$  was 15 ppm/°C. Fig. 12 shows the distribution of output voltage  $V_{\rm REF}$  at room temperature. The coefficient of variation  $\sigma/\mu$  was 0.87%.

Table II summarizes the characteristics of our device in comparison with other low-power CMOS voltage references reported in [9]–[13]. Our device is comparable to other circuits in power dissipation, PSRR, and chip area, and it is superior to others in TC and line sensitivity. Our circuit is therefore useful as a voltage reference for power-aware LSIs.

#### V. DISCUSSION

Regarding other applications, the output voltage of our circuit can be used as a monitor signal for the D2D process variation in MOSFET threshold voltage because the output voltage is equal to the 0-K threshold voltage of MOSFETs in an LSI chip.

Fig. 11. Measured output voltage  $V_{\rm REF}$  as a function of temperature for 17 samples on different chips from same wafer. Supply voltage was set to 1.5 V. Temperature coefficients from 7 to 45 ppm/ $^{\circ}$ C were observed. Average TC was 15 ppm/ $^{\circ}$ C.

Fig. 12. Distribution of output voltage for 17 samples measured at room temperature.

This output voltage can be used to compensate for the threshold voltage variation in LSI chips. For example, consider the application to a reference current source. The process variation of the current  $I_P$  flowing in our circuit [see (14)] can be expressed as

$$\frac{\Delta I_P}{I_P} = \frac{\Delta \mu}{\mu} + \frac{\Delta C_{\rm OX}}{C_{\rm OX}} + \frac{\Delta \kappa}{\kappa}.$$

(20)

The current is independent of the threshold voltage variation. Although the current depends on the variation of the mobility  $\Delta\mu/\mu$ , gate-oxide capacitance  $\Delta C_{\rm OX}/C_{\rm OX}$ , and the temperature coefficient of the threshold voltage  $\Delta\kappa/\kappa$ , these variations are far smaller than the threshold voltage variation.

This way, the circuit can be used as an elementary circuit block for on-chip D2D process compensation systems, such as process and temperature compensated current [23].

# VI. CONCLUSION

We developed an ultra-low power CMOS voltage reference consisting of subthreshold MOSFET circuits. The device generates two voltages having opposite TCs, i.e., a MOSFET threshold voltage and a multiple of the thermal voltage, and adds them to produce an output voltage with a zero TC. We

|                      | This work             | [9]                      | [10]                     | [11]                     | [12]                  | [13]                   |

|----------------------|-----------------------|--------------------------|--------------------------|--------------------------|-----------------------|------------------------|

| Process              | 0.35-μm, CMOS         | 0.35-μm, CMOS            | 0.6-μm, CMOS             | 0.35-μm, CMOS            | 1.2-μm, CMOS          | 0.18-μm, CMOS          |

| Temperature range    | −20 - 80°C            | 0 - 80℃                  | 0 - 100℃                 | 0 - 70℃                  | –25 - 125℃            | 20 - 120℃              |

| $V_{DD}$             | 1.4 - 3 V             | 0.9 - 4 V                | 1.4 - 3 V                | 1.4 - 3 V                | 1.2 V                 | 0.85 - 2.5 V           |

| $\overline{V_{REF}}$ | 745 mV                | 670 mV                   | 309.3 mV                 | 579 mV                   | 295 mV                | 221 mV                 |

| Power                | 0.3 μW(@1.4 V)        | 0.036 μW(@0.9 V)         | 29.1 μW(@3 V)            | 4.6 μW(@2 V)             | 4.3 μW (@1.2 V)       | 3.3 µW (@0.85 V)       |

|                      | Room temp.            | Room temp.               | Max. temp.               | N.A.                     | N.A.                  | Average                |

| TC                   | 7 ppm/°C              | 10 ppm/°C                | 36.9 ppm/℃               | 62 ppm/℃                 | 119 ppm/℃             | 271 ppm/℃              |

| Line sensitivity     | 20 ppm/V              | 2700 ppm/V               | 800 ppm/V                | 6700 ppm/V               | N.A.                  | 9000 ppm/V             |

| PSRR                 | -45 dB(@100 Hz)       | -47 dB(@100 Hz)          | -47 dB(@100 Hz)          | -84 dB(@1 kHz)           | N.A.                  | N.A.                   |

| Chip area            | 0.055 mm <sup>2</sup> | $0.045 \; \mathrm{mm}^2$ | $0.055 \; \mathrm{mm}^2$ | $0.126 \; \mathrm{mm}^2$ | $0.23 \; \text{mm}^2$ | 0.0238 mm <sup>2</sup> |

TABLE II

COMPARISON OF REPORTED LOW-POWER CMOS VOLTAGE REFERENCE CIRCUITS

made a prototype chip, using a 0.35  $\mu$ m standard CMOS process, and demonstrated its operation by measurements. The TC and line sensitivity of the output voltage were 7 ppm/°C and 20 ppm/V. The power dissipation was about 0.3  $\mu$ W. The circuit will be useful as a voltage reference circuit for a power-aware LSIs such as mobile devices, implantable medical devices, and smart sensor networks.

As other applications, because the reference voltage changes with the process conditions of threshold voltage in each LSI chip, the circuit can be used as an elementary circuit block for on-chip process compensation systems. The reference voltage of the proposed circuit enables us to monitor the D2D process variations in each LSI chip.

#### APPENDIX

On condition that  $V_{\rm REF}-V_{\rm TH0}\ll\kappa T$  and  $\eta V_T\ll\kappa T$ , the TC of  $V_{\rm REF}$  in (10) can be rewritten as

$$\frac{dV_{\text{REF}}}{dT}$$

$$= -\kappa + \frac{\eta k_B}{q} \ln \left\{ \frac{6\eta K_{R1} K_3 K_5 (V_{\text{REF}} - V_{\text{TH0}} + \kappa T)}{K_4 K_6 K_7 (\eta - 1) V_T} \right.$$

$$\times \ln \left( \frac{K_2}{K_1} \right) \right\}$$

$$+ \eta V_T \left\{ \frac{1}{V_{\text{REF}} - V_{\text{TH0}} + \kappa T} \left( \frac{dV_{\text{REF}}}{dT} + \kappa \right) - \frac{1}{T} \right\}$$

$$= -\kappa + \frac{\eta k_B}{q} \ln \left\{ \frac{6\eta K_{R1} K_3 K_5 \kappa T}{K_4 K_6 K_7 (\eta - 1) V_T} \ln \left( \frac{K_2}{K_1} \right) \right\}$$

$$+ \frac{\eta V_T}{\kappa T} \left( \frac{dV_{\text{REF}}}{dT} + \kappa \right) - \frac{\eta V_T}{T}$$

$$= -\kappa + \frac{\eta k_B}{q} \ln \left\{ \frac{6\eta K_{R1} K_3 K_5 \kappa T}{K_4 K_6 K_7 (\eta - 1) V_T} \ln \left( \frac{K_2}{K_1} \right) \right\}$$

$$+ \frac{\eta V_T}{\kappa T} \frac{dV_{\text{REF}}}{dT}$$

$$= -\kappa + \frac{\eta k_B}{q} \ln \left\{ \frac{6\eta \eta \kappa}{k_B (\eta - 1)} \frac{K_{R1} K_3 K_5}{K_4 K_6 K_7} \ln \left( \frac{K_2}{K_1} \right) \right\}.$$

Therefore, (11) can be obtained.

# REFERENCES

- [1] A. Wang, B. H. Clhoun, and A. P. Chandracasan, *Sub-Threshold Design for Ultra Low-Power Systems*. New York: Springer, 2006.

- [2] A. P. Chandrakasan, D. C. Daly, J. Kwong, and Y. K. Ramadass, "Next generation micro-power systems," in *Proc. IEEE Symp. VLSI Circuits*, 2008, pp. 2–5.

- [3] K. Ueno, T. Hirose, T. Asai, and Y. Amemiya, "CMOS smart sensor for monitoring the quality of perishables," *IEEE J. Solid-State Circuits*, vol. 42, no. 4, pp. 798–803, Apr. 2007.

- [4] N. M. Pletcher, S. Gambini, and J. M. Rabaey, "A 2 GHz 52 µW wake-up receiver with -72 dBm sensitivity using uncertain-IF architecture," in *IEEE Int. Solid-State Circuits Conf. (ISSCC) Dig. Tech. Papers*, 2008, pp. 524–525, 633.

- [5] T. Umeda, H. Yoshida, S. Sekine, Y. Fujita, T. Suzuki, and S. Otaka, "A 950-MHz rectifier circuit for sensor network tags with 10-m distance," *IEEE J. Solid-State Circuits*, vol. 41, no. 1, pp. 35–41, Jan. 2006.

- [6] P. Fiorini, I. Doms, C. Van Hoof, and R. Vullers, "Micropower energy scavenging," in *Proc. 34th European Solid-State Circuits Conf. (ESS-CIRC)*, 2008, pp. 4–9.

- [7] H. Neuteboom, B. M. J. Kup, and M. Janssens, "A DSP-based hearing instrument IC," *IEEE J. Solid-State Circuits*, vol. 32, no. 11, pp. 1790–1806, Nov. 1997.

- [8] H. Banba, H. Shiga, A. Umezawa, T. Miyaba, T. Tanzawa, S. Atsumi, and K. Sakui, "A CMOS bandgap reference circuit with sub-1-V operation," *IEEE J. Solid-State Circuits*, vol. 34, no. 5, pp. 670–674, May 1999

- [9] G. De Vita and G. Iannaccone, "A sub-1-V, 10 ppm/°C, nanopower voltage reference generator," *IEEE J. Solid-State Circuits*, vol. 42, no. 7, pp. 1536–1542, Jul. 2007.

- [10] K. N. Leung and P. K. T. Mok, "A CMOS voltage reference based on weighted  $\Delta V_{\rm GS}$  for CMOS low-dropout linear regulators," *IEEE J. Solid-State Circuits*, vol. 38, no. 1, pp. 146–150, Jan. 2003.

- [11] M.-H. Cheng and Z.-W. Wu, "Low-power low-voltage reference using peaking current mirror circuit," *Electron. Lett.*, vol. 41, no. 10, pp. 572–573, 2005.

- [12] G. Giustolisi, G. Palumbo, M. Criscione, and F. Cutri, "A low-voltage low-power voltage reference based on subthreshold MOSFETs," *IEEE J. Solid-State Circuits*, vol. 38, no. 1, pp. 151–154, Jan. 2003.

- [13] P.-H. Huang, H. Lin, and Y.-T. Lin, "A simple subthreshold CMOS voltage reference circuit with channel-length modulation compensation," *IEEE Trans. Circuits Syst. II, Expr. Briefs*, pp. 882–885, 2006.

- [14] K. Ueno, T. Hirose, T. Asai, and Y. Amemiya, "A 0.3-µW, 7 ppm/° C CMOS voltage reference circuit for on-chip process monitoring in analog circuits," in *Proc. 34th European Solid-State Circuits Conf.*, 2008, pp. 398–401.

- [15] B. Gilbert, "Translinear circuits: A proposed classification," *Electron. Lett.*, vol. 11, no. 1, pp. 15–16, 1975.

- [16] S.-C. Liu, J. Kramer, G. Indiveri, T. Delbruck, and R. Douglas, Analog VLSI: Circuits and Principles. Cambridge, MA: MIT Press, 2002.

- [17] Y. Taur and T. H. Ning, Fundamentals of Modern VLSI Devices. Cambridge, U.K.: Cambridge Univ. Press, 2002.

- [18] I. M. Filanovsky and A. Allam, "Mutual compensation of mobility and threshold voltage temperature effects with applications in CMOS circuits," *IEEE Trans. Circuits Syst. I, Fundam. Theory Appl.*, pp. 876–884, 2001.

- [19] K. A. Bowman, S. G. Duvall, and J. D. Meindl, "Impact of die-to-die and within-die parameter fluctuations on the maximum clock frequency distribution for gigascale integration," *IEEE J. Solid-State Circuits*, vol. 37, no. 2, pp. 183–190, Feb. 2002.

- [20] H. Onodera, "Variability: Modeling and its impact on design," *IEICE Trans. Electron.*, vol. E89-C, pp. 342–348, 2006.

[21] M. J. M. Pelgrom, A. C. J. Duinmaijer, and A. P. G. Welbers,

- [21] M. J. M. Pelgrom, A. C. J. Duinmaijer, and A. P. G. Welbers, "Matching properties of MOS transistors," *IEEE J. Solid-State Circuits*, vol. 24, no. 5, pp. 1433–1439, Oct. 1989.

- [22] A. Hastings, The Art of Analog Layout. Englewood Cliffs, NJ: Prentice-Hall, 2001.

- [23] K. Ueno, T. Hirose, T. Asai, and Y. Amemiya, "A 46 ppm/° C temperature and process compensated current reference with on-chip threshold voltage monitoring circuit," in *Proc. IEEE Asian Solid-State Circuits Conf. (A-SSCC)*, 2008, pp. 161–164.

**Tetsuya Hirose** (M'05) received the B.S., M.S., and Ph.D. degrees from Osaka University, Osaka, Japan, in 2000, 2002, and 2005, respectively.

From 2005 to 2008, he was a Research Associate at the Department of Electrical Engineering, Hokkaido University, Sapporo, Japan. Since April 2008, he has been a Lecturer at the Department of Electrical and Electronics Engineering, Kobe University, Kobe, Japan. His current research interests are in the field of low-power analog/digital integrated circuits design and subthreshold MOSFET

functional LSIs for intelligent sensors.

Dr. Hirose is a member of the Institute of Electronics, Information and Communication Engineers of Japan and the IEEE.

**Tetsuya Asai** (M'01) received the B.S. and M.S. degrees in electrical engineering from Tokai University, Kanagawa, Japan, in 1993 and 1996, respectively, and the Ph.D. degree in electrical and electronic engineering from Toyohashi University of Technology, Aichi, Japan, in 1999.

He is now an Associate Professor in the Department of Electrical Engineering, Hokkaido University, Sapporo, Japan. His current research interests include nonlinear analog processing in neural networks and reaction-diffusion systems as well as design and ap-

plications of neuromorphic VLSIs.

of Japan and the IEEE.

**Ken Ueno** (S'05) received the B.S. degree in the Department of Electronics and Information Engineering, Hokkai-Gakuen University, Sapporo, Japan, in 2002, and the M.S. degree in the Department of Electrical Engineering, Hokkaido University, Sapporo, Japan, in 2007, where he is currently working toward the Ph.D. degree.

His current research interests are in PVT-tolerant ultra-low-power analog CMOS circuits.

Mr. Ueno is a member of the Institute of Electronics, Information and Communication Engineers

**Yoshihito Amemiya** received the B.E., M.E., and Ph.D. degrees from the Tokyo Institute of Technology, Tokyo, Japan, in 1970, 1972, and 1975, respectively.

He joined NTT Musashino Laboratories in 1975, where he worked on the development of silicon process technologies for high-speed logic LSIs. From 1983 to 1993, he was with NTT Atsugi Laboratories and developed bipolar and CMOS circuits for Boolean logic LSIs, neural network LSIs, and cellular automaton LSIs. Since 1993, he has been a

Professor with the Department of Electrical Engineering, Hokkaido University, Sapporo. His research interests are in the fields of silicon LSI circuits, signal processing devices based on nonlinear analog computation, logic systems consisting of single-electron circuits, and information-processing devices making use of quantum nanostructures.