# Cancellation of OpAmp Virtual Ground Imperfections by a Negative Conductance Applied to Improve RF **Receiver Linearity**

Dlovan H. Mahrof, Student Member, IEEE, Eric A. M. Klumperink, Senior Member, IEEE, Zhiyu Ru, Member, IEEE, Mark S. Oude Alink, Member, IEEE, and Bram Nauta, Fellow, IEEE

Abstract—High linearity CMOS radio receivers often exploit linear V-I conversion at RF, followed by passive down-mixing and an OpAmp-based Transimpedance Amplifier at baseband. Due to nonlinearity and finite gain in the OpAmp, virtual ground is imperfect, inducing distortion currents. This paper proposes a negative conductance concept to cancel such distortion currents. Through a simple intuitive analysis, the basic operation of the technique is explained. By mathematical analysis the optimum negative conductance value is derived and related to feedback theory. In- and out-of-band linearity, stability and Noise Figure are also analyzed. The technique is applied to linearize an RF receiver, and a prototype is implemented in 65 nm technology. Measurement results show an increase of in-band IIP<sub>3</sub> from 9 dBm to >20 dBm, and IIP2 from 51 to 61 dBm, at the cost of increasing the noise figure from 6 to 7.5 dB and <10% power penalty. In 1 MHz bandwidth, a Spurious-Free Dynamic Range of 85 dB is achieved at <27 mA up to 2 GHz for 1.2 V supply voltage.

Index Terms-Receiver linearity, interference robustness, compression, blocking, in-band and out-band IIP<sub>3</sub>, IIP<sub>2</sub>, mixer-first receiver architecture, transimpedance amplifier (TIA), negative conductance technique, CMOS, wideband base station receiver, software radio, software defined radio, cognitive radio.

# I. INTRODUCTION

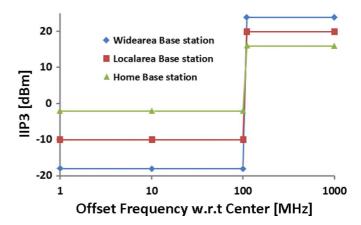

INEARITY requirements on radio receivers become increasingly challenging, as the radio spectrum becomes more crowded. Moreover, there is a trend towards more wideband and more flexible radio hardware with less dedicated RF filtering ("Software Defined Radio"). As an example, Fig. 1 plots IIP<sub>3</sub> requirements calculated for E-UTRA for a wideband base station receiver in three scenarios: wide area, local area and home [1]. Apart from the high 100 MHz bandwidth, note the sudden step in IIP<sub>3</sub> requirements at the band-edge. Also

Manuscript received August 15, 2013; revised October 24, 2013; accepted November 22, 2013. Date of publication January 09, 2014; date of current version April 21, 2014. This paper was approved by Guest Editor Waleed Khalil. This work was supported by the Dutch Technology Foundation STW (the Applied Science Division of the NWO, and the Ministry of Economic Affairs Technology Program).

D. H. Mahrof and M. S. Oude Alink were with the University of Twente, Enschede, The Netherlands, and are now with Bruco IC Company, 7623 CS Borne, The Netherlands (e-mail: d.h.mahrof@alumnus.utwente.nl).

E. A. M. Klumperink and B. Nauta are with the University of Twente, IC Design group, 7500 AE Enschede, The Netherlands.

Z. Ru was with the University of Twente, IC Design group, Enschede, The Netherlands, and is now with MediaTek, Woburn, MA 01801 USA.

Color versions of one or more of the figures in this paper are available online at http://ieeexplore.ieee.org.

Digital Object Identifier 10.1109/JSSC.2013.2294637

Fig. 1. Example IIP<sub>3</sub> requirement for E-UTRA [1].

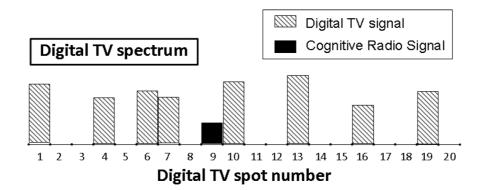

note that less coverage area (home versus wide area), corresponds to higher in-band IIP<sub>3</sub> but a smaller step to out-of-band IIP<sub>3</sub> (i.e., around 16 dB for home area versus 40 dB for wide area). As a consequence of the lack of a reasonable transition band, on-chip analog filtering is ineffective to relax the IIP<sub>3</sub> requirement, and off-chip filters are expensive. Depending on the blocker scenario, compression point requirements may or may not be affected. In this paper, we propose a circuit technique that can increase IIP<sub>3</sub> simultaneously for in- and out-of-band, at roughly constant compression point. Receivers with high  $IIP_3$ are also very important for opportunistic dynamic spectrum access via a cognitive radio, as is exemplified in Fig. 2 for a Digital TV band. Strong interferers (incumbent TV signals) may be present in directly adjacent channels, again making on-chip RF filtering ineffective. Again, high linearity is required also to prevent cross-modulation effects [2] from desensitizing the receiver. A part from the RF receivers, the spectrum sensing front-end also requires high in-band IIP<sub>3</sub> in order to minimize the errors in detecting the empty channels in the spectrum.

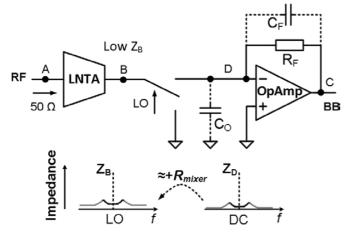

Strong RF interference can easily clip baseband amplifiers, while higher required bandwidths limit the amount of available loop-gain for negative feedback. When pushing linearity, avoiding voltage gain at RF (See Fig. 3) is instrumental [3]–[8]. Exploiting RF V-I conversion followed by passive down-mixing and then simultaneous I-V conversion and filtering at IF/baseband with OpAmps, an out-of-band IIP<sub>3</sub> of up to +18 dBm has been shown [3], [4]. Passive mixer-first architectures can even achieve up to +25 dBm out-of-band

See http://www.ieee.org/publications standards/publications/rights/index.html for more information.

Fig. 2. Digital TV spectrum [2] in which a cognitive radio operates in an adjacent channel.

Fig. 3. High blocker tolerant linear receiver.

$IIP_3$  [7]. However in-band  $IIP_3$  is much worse, certainly at high gain. The best in-band IIP<sub>3</sub> results that we found for receivers were +3.5 dBm for [3] at 34 dB gain and +11 dBm for [6] at 19 dB gain. Analysis shows that finite OpAmp gain can be a bottleneck, as a non-zero virtual ground node voltage can result in distortion currents. In [9], we recently proposed to exploit a negative conductance technique to cancel distortion currents. In this way, the design of the OpAmp is relaxed and its performance no longer needs to be a bottleneck. The use of a negative conductance has been proposed in [10] to realize TIA flicker noise shaping. Paper [10] also briefly mentions linearity improvement, but linearity benefits were not the focus there. In this paper we will analyze the benefits of a negative conductance, compare analysis to measurements and report some extra experimental results in addition to [9]. Section II presents an intuitive model to understand the basic distortion cancellation concept. Additionally, the optimum negative conductance value is derived by mathematical analysis and related to negative feedback theory. Section III analyses stability issues related to this negative conductance technique. A receiver design, in which the concept is exploited, is discussed in Section IV. The receiver noise figure analysis including the negative conductance contribution is discussed in Section V. The analysis is verified by measurements in Section VI, while results are also benchmarked to other high linearity receivers. Finally, Section VII presents conclusions.

# II. LINEARIZATION CONCEPT

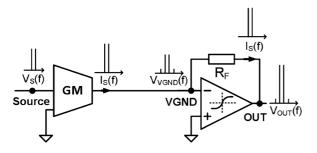

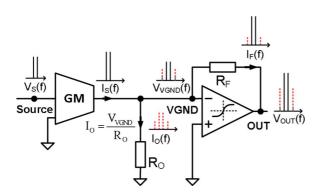

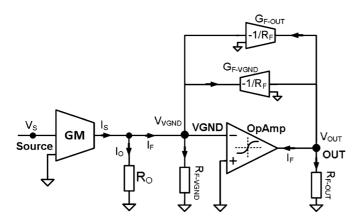

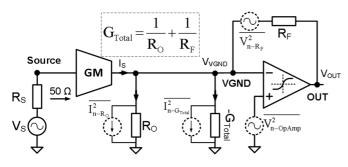

To understand the OpAmp linearity limitation and the distortion cancellation technique intuitively, it is instructive to follow a 4-step approach to analyze what happens at the virtual ground node "VGND", as illustrated in Figs. 4 to 8:

- Step 1: Assume the RF V-I conversion and mixing are perfectly ideal (i.e., linear and infinite current source resistance for GM), we can use the equivalent baseband model in Fig. 4 (omitting the downconversion for simplicity). Assuming a 2-tone input signal  $V_{S}(f)$ , the injected current  $I_{S}(f)$  to the VGND node is linear, so without IM<sub>3</sub> tones. Now, if the OpAmp handles large signals at a high but finite gain, its output stage will produce IM<sub>3</sub> products at the OUT node, i.e.,  $V_{OUT}(f)$ . However, as  $I_S(f)$  has no  $IM_3$ and the feedback resistor  $R_{\rm F}$  is linear, the voltage over R<sub>F</sub> does not contain IM<sub>3</sub> (assuming negligible OPAMP input current). Consequently, the  $IM_3$  products of  $V_{VGND}(f)$  are in absolute sense equal to those of  $V_{OUT}(f)$  both in magnitude and phase. Let us denote this "IM<sub>3</sub> copy" effect in Fig. 4 as "problem A". Note that the two main tones of  $V_{VGND}(f)$  are much smaller than that of  $V_{OUT}(f)$ , as the ratio  $V_{OUT}(f)/V_{VGND}(f)$  for linear terms is equal to the loop gain. As a consequence the ratio between the linear terms and the  $IM_3$  products at VGND node is *much worse* than at the OUT node, causing a more serious problem discussed next.

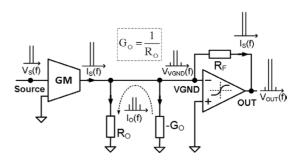

- Step 2: Assume we add a finite output resistance  $R_O$  as shown in Fig. 5. The nonlinear voltage  $V_{VGND}(f)$ over  $R_O$  now generates a nonlinear current  $I_O(f)$ , and hence  $I_F(f)$  becomes nonlinear. This current is absorbed by the OpAmp output stage and increases  $IM_3$  at both  $V_{OUT}(f)$  and  $V_{VGND}(f)$ . We will denote this " $R_O$  loading" effect on the VGND node in Fig. 5 as "problem B".

- Step 3: Once one realizes the main cause for distortion current is  $V_{VGND}(f)/R_O$ , it is easy to verify that adding a negative conductance with value  $G_O = 1/R_O$  between VGND and ground can be a solution (see Fig. 6). The negative conductance senses  $V_{VGND}$  and generates a copy of the distorted current  $I_O(f)$ , which now flows in a "local circle"

Fig. 4. OpAmp nonlinearity problem A:  $\mathrm{IM}_3$  is copied from the OUT node to the VGND node.

Fig. 5. OpAmp nonlinearity problem B:  $R_{O}$  loads the VGND node.

via the ground. Consequently, the current injected to the VGND node becomes linear again and we are back at the circuit of problem A, having solved problem B.

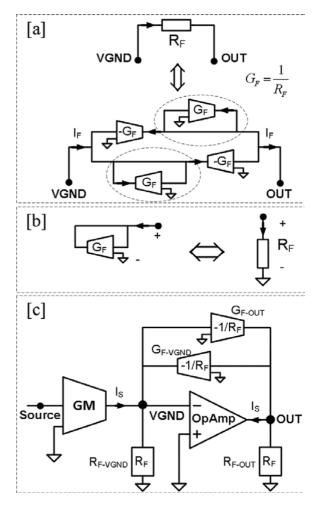

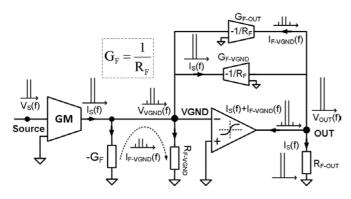

Step 4: Still, the OpAmp output voltage contains some  $IM_3$ , equal to that on the VGND node. By slight overcompensation this IM<sub>3</sub> contribution can also be cancelled. To show this, it is useful to model the floating resistor  $R_F$  with an equivalent network consisting of four single-ended linear transconductor blocks  $G_F$  ( $G_F = 1/R_F$ ), all referred to ground as shown in Fig. 7(a). The two shorted  $G_F$  blocks, indicated with a dashed ellipse, can be replaced by a simple  $R_F$  resistor to the ground (see Fig. 7(b)). Thus Fig. 7(c) results with  $R_{F-VGND}$  and  $R_{F-OUT}$ , (loading resistances at the VGND node and the OUT node, respectively), G<sub>F-VGND</sub> (the transconductance sensing V<sub>OUT</sub> and injecting current to the VGND node), and  $G_{F-OUT}$  (the transconductance sensing  $V_{\rm VGND}$  and injecting current to the OUT node). We assigned different names to  $G_F$  and  $R_F$ blocks in order to distinguish between their effects on nonlinearity at the VGND node and the OUT node separately. Fig. 7(c) clearly shows the loading effect of  $R_F$  (i.e.,  $R_{F-VGND}$ ) at the VGND node. Now, when the negative conductance cancels this loading effect (see Fig. 8), the injecting current of  $G_{\rm F-VGND}$  becomes equal to the linear current  $I_{S.}$  As  $V_{OUT} = I_{S}/G_{F-VGND} = -I_{S} \cdot R_{F}$ , the OpAmp output voltage V<sub>OUT</sub> becomes linear. This way problem A is solved as well.

Fig. 6. Solving problem B via negative conductance with  $G_0 = 1/R_0$ .

Fig. 7. Equivalent model of the effect that  $R_{\rm F}$  has on the OUT node and the VGND node.

Overall, combining the solutions for problem A and B, the optimal total negative conductance is:  $G_{TOTAL} = 1/R_O + 1/R_F$ . To mathematically prove this optimum cancellation condition, the OpAmp (see Fig. 9) is modeled as an OTA with nonlinear transconductance and also a nonlinear output resistance because we aim for high output swing:

$$I_{\rm F} = gm_1 V_{\rm IN} + gm_3 V_{\rm IN}^3 + go_1 V_{\rm O} + go_3 V_{\rm O}^3$$

(1)

In the model, we assume that the third order nonlinearities are more pronounced than the second order nonlinear terms, which is reasonable considering the OpAmp will be implemented in fully differential form. In the Appendix A, the nonlinear relation

Fig. 8. Solving problem A via negative conductance with  $G_F = 1/R_F$ .

Fig. 9. Baseband model with  $R_{\rm O}$  and the extended  $R_{\rm F}$  for nonlinearity derivations.

between  $V_{OUT}$  and signal current  $I_S$  is derived using the model in Fig. 9. It can be expressed in terms of a linear  $(\Omega_1)$  and thirdorder nonlinear  $(\Omega_3)$  coefficient:

$$V_{OUT} = \Omega_1 I_S + \Omega_3 I_S^3 \tag{2}$$

The linear coefficient  $\Omega_1$  is the I/V conversion gain:

$$\Omega_{1} = \frac{1}{\left[\frac{1}{a}\left(\frac{1}{R_{O}} + \frac{1}{R_{F-VGND}}\right) + G_{F-VGND}\right]}$$

(3)

Where (a) is a function of the linear terms of the OpAmp model (i.e.,  $gm_1, go_1$ ) and the  $R_F$  effects at the OUT node (i.e.,  $R_{F-OUT}$  and  $G_{F-OUT}$ ). For very high  $gm_1$ , (a) reaches  $-\infty$ . Consequently, the I/V conversion gain of (3) becomes  $1/G_{F-VGND} = -R_F$ .

The third-order distortion coefficient  $(\Omega_3)$  is:

$$\Omega_3 = \frac{\mathrm{NL}_3 \left(\frac{1}{\mathrm{R}_{\mathrm{O}}} + \frac{1}{\mathrm{R}_{\mathrm{F-VGND}}}\right)}{\left[\frac{1}{\mathrm{a}} \left(\frac{1}{\mathrm{R}_{\mathrm{O}}} + \frac{1}{\mathrm{R}_{\mathrm{F-VGND}}}\right) + \mathrm{G}_{\mathrm{F-VGND}}\right]^4} \qquad (4)$$

where (NL<sub>3</sub>: see Appendix A) is related to the nonlinear terms of the OpAmp model and is a function of (i.e.,  $gm_1, gm_3, go_1$ and  $go_3$ ) and the effect of  $R_F$  on the OUT node (i.e.,  $R_{F-OUT}$ and  $G_{F-OUT}$ ). Now, if the *negative conductance technique cancels*  $1/R_O + 1/R_{F-VGND}$  from (3) and (4) we see that  $\Omega_1$ reaches  $1/G_{F-VGND} = -R_F$  and  $\Omega_3$  becomes zero (distortion is cancelled) Note that since the voltage swing at the VGND

Fig. 10. Applying feedback theory to Fig. 9, excluding GM.

node is small, the effect of negative conductance nonlinearity can be very small.

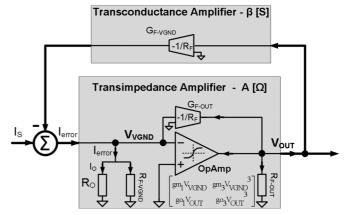

The linearity benefit can also be verified by applying feedback theory to Fig. 9 as shown in Fig. 10, excluding GM. The feedback topology of the circuit is Voltage-Current Feedback [11]. The output voltage (i.e., V<sub>OUT</sub>) is sensed and converted to a proportional feedback current  $\beta V_{OUT}$ , where  $\beta = G_{F-VGND}$ (in Siemens). This feedback current is subtracted from the input current  $I_{\rm S}$  resulting in an error current  $I_{\rm error} = I_{\rm S}\beta V_{\rm OUT}$  to be amplified by the block A. Here,  $A = V_{OUT}/I_{error}$ , where A has the dimension of a transimpedance  $[\Omega]$ . It consists of all the blocks of Fig. 9, excluding GM and  $\mathrm{G}_{\mathrm{F-VGND}}.$  Actually for finite A, there will be a non-zero Ierror due to the loading effect of  $R_O$  and  $R_{F-VGND}$  on the VGND node. Now the negative conductance increases the input impedance of the A block to infinity by cancelling  $R_O$  and  $R_{F-VGND}$ , so that  $I_{error}$  becomes zero and  $A = V_{OUT}/I_{error} = infinity$ . Consequently, loopgain  $A\beta$  goes to infinity and  $V_{OUT}/I_S$  achieves its ideal value  $1/\beta = R_F$ , i.e., perfect linearity. We conclude that the negative conductance technique increases the loop gain by increasing the value of A. Also note that only a finite value for  $G_O$  is needed to make the loopgain theoretically approach infinity, which is not possible by increasing  $gm_1$  in the gain block. Although the feedback theory puts the application of a negative conductance technique in the right context, however the problem with control theory is that it assumes blocks with unilateral operation, which are sometimes not easy to identify (e.g., see Fig. 10: feedback resistor  $R_F$  which is supposed to realize the  $\beta$  block also becomes part of the A block). In compare to the feedback analysis, our analysis explains in a simple way how  $IM_3$  is affected by  $R_0$ and  $R_{F}$ .

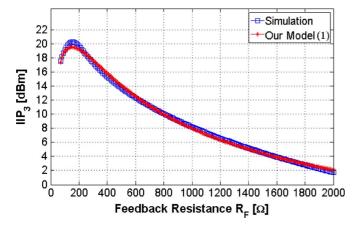

To verify the OpAmp model, we fitted the model derived above to simulations done for the OpAmp that will be introduced later in this paper. Fig. 11 shows a close agreement.

Now, before we proceed with detailed circuits design, we will first deal with a potential caveat of negative conductance: the risk of instability.

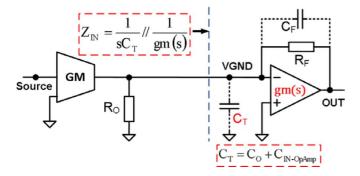

## **III. STABILITY ANALYSIS**

We will consider two stability aspects: 1) the risk of oscillation, based on a small signal model, and 2) the risk of latch-up.

Fig. 11. OpAmp model (1) verification.

Fig. 12. Circuit diagram for small signal stability analysis.

Let us first look at the small signal behavior, referring to Fig. 12. As the low-pass filtering is desired,  $C_F$  is added as feedback capacitor. Capacitor  $C_T$  models the total input capacitance to ground of the OpAmp  $C_{IN-OpAmp}$  and other capacitance  $C_O$  at the VGND node (see Fig. 3). For simplicity, the OTA is modeled as a frequency dependent transconductance with a dominant pole at  $\omega_O$  and infinite output impedance:

$$gm(s) = \frac{gm_O}{1 + \frac{s}{\omega_O}}$$

(5)

Assuming no further loading at the OUT node, looking into the VGND node (see Fig. 12), the impedance  $(Z_{IN})$  consists of the reactance of  $C_T$  in parallel to 1/gm(s):

$$Z_{IN} = \frac{1}{s C_{T}} / / \frac{1}{gm(s)}$$

$$= \frac{1}{s C_{T}} / / \left[ \frac{1}{\underbrace{gm_{O}}_{Resistance}} + \underbrace{\frac{s}{gm_{O}\omega_{O}}}_{Inductance (L)} \right]$$

(6)

Therefore, a parallel RLC tank is seen looking into the VGND node. If the negative conductance would both cancel  $1/R_O$  and  $gm_O$ , then oscillation would happen at a resonance frequency that depends on the value of  $C_T$  and L (i.e.,  $f_{\rm res} = 1/(2\pi\sqrt{C_TL})$ ). However, note that the typical virtual ground impedance  $1/gm_O$  will normally be much lower than  $R_O$  and  $R_F$ . Thus, as the negative conductance  $G_{\rm Total}$  is

Fig. 13. Latch-up problem at the OUT node.

Fig. 14. Replacing the LNTA (GM) of Fig. 3 by a linear resistance  $R_{RF}$ .

designed to cancel  $1/R_{O}$  and  $1/R_{F}$ , the point of small signal instability can be designed to be safely far away.

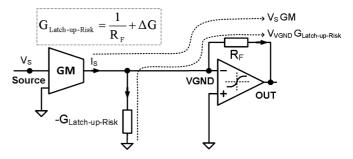

Let us now look at the potential of latch-up of the OpAmp for a case that the negative conductance is too strong, i.e., it produces more current than needed after compensating the current in  $R_O$ . As shown in Fig. 13, the negative conductance injects current via  $R_F$  (i.e.,  $V_{VGND}G_{Latch-up-Risk}$ ) that needs to be handled by the OpAmp output stage in addition to the main current coming from GM (i.e.,  $I_S$ ):

$$\begin{split} ^{IOpAmp-Latch-up-Risk} &= I_{S} + V_{VGND}G_{Latch-up-Risk} \\ &= I_{S} + \frac{1}{\left[ \left( \frac{1}{R_{F-VGND}} - G_{Latch-up-Risk} \right) + a \, G_{F-VGND} \right]} \\ &\times I_{S}G_{Latch-up-Risk} \end{split}$$

(7)

Where the relation between  $V_{\rm VGND}$  and  $I_{\rm S}$  is derived in Appendix B. Referring to Fig. 13 and substituting  $G_{\rm Latch-up-Risk}=(1/R_{\rm F})+\Delta G$ , in (7) gives the following relation:

$$I_{OpAmp-Latch-up-Risk} = I_{S} \left[ 1 - \frac{\Delta G + \frac{1}{R_{F}}}{\left( \Delta G + \frac{a}{R_{F}} \right)} \right]$$

(8)

The OpAmp output stage current flows throw  $R_{\rm F}$  and make a voltage drop. The peak of this voltage drop is around VDD/2 -  $V_{\rm OpAmpOutputStage-OV}$ , where  $V_{\rm OpAmpOutputStage-OV}$  is the over drive voltages of the OpAmp output stage transistors. Hence, if very strong negative conductance has been used (i.e., high  $\Delta G$  in (8)), then the current of (8) becomes higher than the OpAmp output stage current capability and the latch-up occur.

Fig. 15. Complete receiver with distortion compensation by -Go.

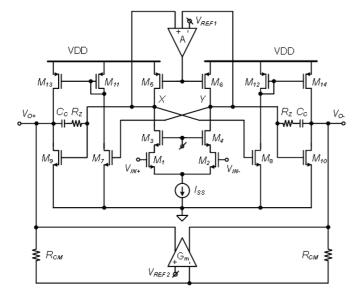

# IV. RECEIVER DESIGN

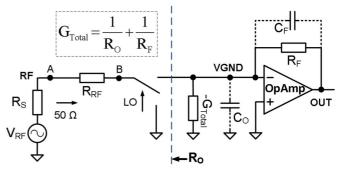

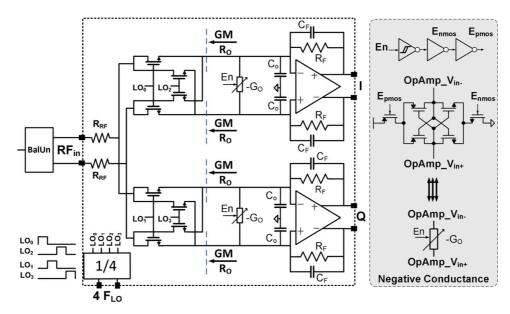

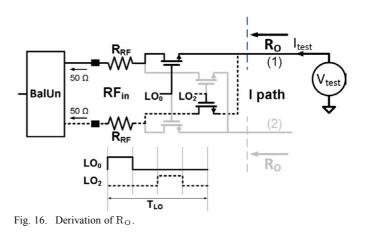

We will now apply the negative conductance idea to a high linearity zero-IF radio receiver architecture of Fig. 3. To demonstrate the linearity potential of this technique, we will replace the active V-I conversion by a more linear fully passive mixer with resistors in series [4], as shown in Fig. 14. Fig. 15 shows the complete front-end IC schemati including the negative conductance. Using the equivalent model in Fig. 5, we can model the RF part of each branch in I and Q as a grounded resistor R<sub>O</sub> and a transconductor GM referred to ground as denoted in Fig. 15. However, as resistor R<sub>RF</sub> is in series with the mixer on-resistance  $R_{\rm ON-MIXER}$  and the virtual ground impedance R<sub>VGND</sub> of the OpAmp, the equivalent GM now equals  $1/(R_{RF} + R_{ON-MIXER} + R_{VGND})$ . This is chosen to be 20 mS to realize RF input impedance matching f 50  $\Omega$ , assuming perfect non overlapping 25% duty-cycle clocks, so the RF-input continuously sees a conduction path to ground. The equivalent output impedance of the mixer at baseband now is  $R_{O} = 2 (R_{BalUn} + R_{RF} + R_{ON-MIXER})$ , where the factor 2 is due to the quadrature mixer with 25% duty cycle, connecting each I and Q baseband part to RF two times per LO cycle. To understand this point, let us derive R<sub>O</sub> from the power that is delivered by a test voltage source (i.e.,  $V_{test} = V_a \cos(\omega_{LO} t)$ ) "looking back" in  $R_O$  as shown in Fig. 16. This source is connected to the first branch of the I-path. The current  $I_{\rm test}$ will flow through  $R_{ON-MIXER} + R_{RF} + R_{BalUn}$  two times LO-cycle, hence we get:

$$P = \frac{1}{T_{LO}} \begin{bmatrix} \frac{T_{LO}}{\int} & \frac{3T_{LO}}{V_{test}} I_{test} dt + \int_{\frac{T_{LO}}{2}}^{\frac{3T_{LO}}{4}} V_{test} I_{test} dt \\ & = \frac{V_a^2}{4 \left( R_{ON-MIXER} + R_{BalUn} + R_{RF} \right)}$$

(9)

This power must be equal to the power dissipation in  $R_{\Omega}$ :

$$P = \frac{1}{T_{LO}} T_{LO} \int_{0}^{T_{LO}} \frac{V_{test}^2}{R_O} dt = \frac{V_a^2}{2R_O}$$

(10)

By equating (9) and (10), the following  $R_O$  is derived:

$$R_{O} = 2(R_{ON-MIXER} + R_{BalUn} + R_{RF})$$

(11)

In the derivation of  $R_O$ , the power is only balanced with the fundamental, while the effect of the 3rd and higher harmonics are neglected due to the existence of  $C_O$  (see Fig. 15).

Now, the 50  $\Omega$  input impedance matching is implemented as a combination of series resistances  $R_{RF} \approx 12 \Omega$ , the up-converted impedances of the passive mixer switches  $R_{ON-MIXER} \approx 28 \Omega$  plus the VGND impedance  $R_{VGND} \approx$ 7  $\Omega$ . The passive mixer consists of simple NMOS switches.  $C_O = 8$  pF effectively shorts the LO leakage and high IF frequency components to ground. The TIA consists of a class-A input stage and a class-AB output stage, to maximize output swing (see Fig. 17, [12] and [3]). Common mode feedback ensures biasing at VDD/2. The feedback impedance is

Fig. 17. Circuit diagram of the fully differential OpAmp design [12].

Fig. 18. Equivalent baseband model for noise figure analysis.

$R_F = 1.5 \ k\Omega$  and  $C_F = 8 \ pF$ , to obtain 26 dB voltage gain and a  $-3 \ dB$ -bandwidth of 12 MHz. The differential topology allows for a simple differential implementation of the negative conductance (right part of Fig. 15) and high IIP<sub>2</sub>. To be able to measure what is the effect of different negative conductance values,  $-G_O$  is implemented as a parallel array of identical "unit-transconductors", digitally controllable via multiplier M, with transconductance steps of 0.2 mS. Thus M = 28 renders  $G_O = 5.6 \ mS$  to compensate the nominal value of  $R_O = 180 \ \Omega \ (R_O = 2 \ (R_{BalUn} + R_{RF} + R_{ON-MIXER}) = 2(50 + 12 + 28) = 180 \ \Omega)$ .

We will now consider the noise degradation resulting from the introduction of the negative conductance. Actually this noise can be cancelled by a noise cancellation path [4], [13], however this is expected to result in a linearity bottleneck in the auxiliary noise cancellation path. Hence we will analyze the noise figure degradation and aim for minimizing the noise penalty.

# V. NOISE FIGURE ANALYSIS (NF)

Receiver topologies with a passive mixer and transimpedance amplifier (TIA), can suffer from amplification of OpAmp noise [14]. The output referred OpAmp noise contribution can be written as:

$$\overline{V_{n-OUT}^2} = \left(1 + \frac{R_F}{R_O}\right)^2 \overline{V_{n-OpAmp}^2}$$

(12)

Fig. 19. Die photograph (65 nm CMOS,  $1.45 \text{ mm} \times 1.45 \text{ mm}$ ).

Where  $V_{n-OpAmp}$  refers to the (equivalent) input noise voltages of the OpAmp,  $R_O$  and  $R_F$  are as used in Fig. 5. For our design  $R_F = 1.5 \text{ k}\Omega$  and  $R_O = 180 \Omega$ , then the amplification factor is equal to  $(1 + R_F/R_O)^2 = 87$ . Often a high RF V/I conversion (GM-value) is used to achieve an overall noise figure around or below 3 dB. Here we will use 20 mS, the value desired for input impedance matching. Fig. 18 shows a baseband model of Fig. 14 with noise sources added. The noise of GM is represented by the current noise source  $(I_{n-Ro})$  of  $R_O$ . The noise of  $R_F$  is modeled via voltage noise source  $V_{n-RF}$ , while  $I_{n-GTotal}$  represents the current noise source of the negative conductance. For simplicity, the OpAmp is modeled as a simple Transconductance (gm). To analyze the noise contributions of  $I_{n-Ro}$  and  $I_{n-GTotal}$  to the output voltage,  $\Omega_1$  (i.e., the I/V conversion of the TIA (3)) is useful. The straightforward NF analysis shows:

$$NF = 1 + \frac{1}{\left(\frac{1}{2}\Omega_{1}GM\right)^{2}R_{S}} \left[\underbrace{\Omega_{1}^{2}\left(\frac{1}{R_{O}} + \gamma G_{Total}\right)}_{\text{First Term}} + \underbrace{\frac{\overline{V_{n-OpAmp}^{2}}}{\overline{I_{n-R_{O}}^{2}}} \frac{1}{R_{O}}\left(1 + R_{F}\left(\frac{1}{R_{O}} - G_{Total}\right)\right)^{2}}_{\text{Second Term}} + \underbrace{R_{F}\left(\frac{1}{gmR_{F}} - 1\right)^{2}}_{\text{Third Term}}\right]$$

(13)

The first term between the square brackets in (13) shows that the negative conductance  $G_{Total}$  has a direct noise contribution to the output. Its noise contribution is scaled by  $\gamma/(((1/2) \text{ GM})^2 R_S)$ . The "noise excess factor"  $\gamma$  can be minimized to around 2/3 (i.e., theoretically) by choosing a non-minimum channel length for the negative conductance transistors. Long-channel transistors are preferred for 1/f noise. We used 1  $\mu$ m channel length in this design. The second term is the mentioned amplification factor (12) of OpAmp noise including the negative conductance effect (G<sub>Total</sub>). It is interesting to observe that this term reaches zero when the negative conductance reaches G<sub>Total</sub>. However, the direct

Fig. 20. Measurements: (a) In-band  $IIP_3$  vs. the number of parallel Negative Conductance Unit-Cells M (b)  $IM_3$  versus input power for three M settings, with LO = 1 GHz.

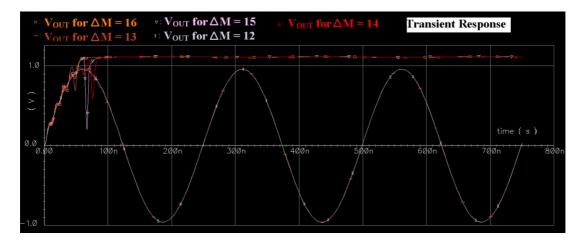

Fig. 21. Latch-up simulation of  $V_{OUT}$ , input power of -16 dBm.

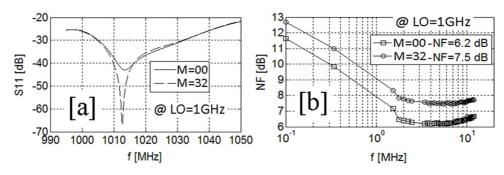

noise contribution of the negative conductance is much higher than the canceled OpAmp noise contribution, hence the total noise figure of the circuit increases. We verified (13) by noise simulations using the OpAmp circuit of Fig. 17. The NF is increased from 6 to 7.5 dB given that GM is equal to 20 mS. Note that it is also possible to apply the negative conductance in combination with an LNTA with higher GM and hence lower NF. In that case, the negative conductance can be lower, as  $R_O > 1/GM$ . However, then IIP<sub>3</sub> of the LNTA becomes a bottleneck.

#### VI. MEASUREMENT RESULTS AND BENCHMARKING

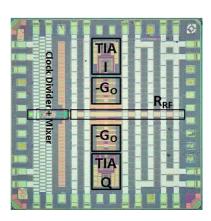

Fig. 19 shows a photo of the implemented 65 nm IC. The active area is  $<0.2 \text{ mm}^2$  including the clock circuit. Thick metal was used for  $R_{RF}$  for high linearity and low spread.

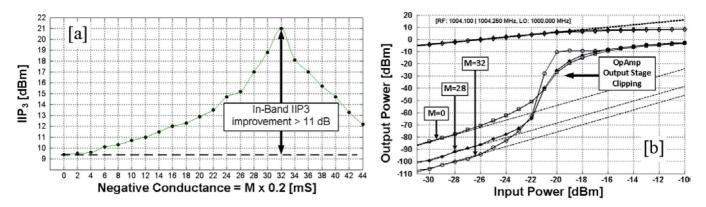

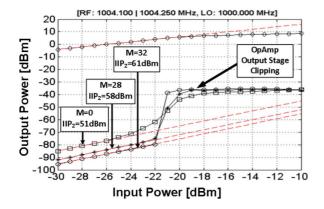

The front-end achieves 26 dB gain (BalUn losses are de-embedded) at 1 GHz LO, over 24 MHz bandwidth (BW), 12 MHz on either side of LO. To demonstrate distortion cancelling, Fig. 20(a) shows the measured in-band IIP<sub>3</sub> at 150 kHz tone spacing ( $f_1 = 1004.1$  MHz and  $f_2 = 1004.25$  MHz) vs. M. IIP<sub>3</sub> clearly improves from around +9 dBm to +21 dBm!

The optimum IIP<sub>3</sub> of +21 dBm is located at M = 32, which fits to our theory  $G_{Total} = 1/R_O + 1/R_F = 1/1500 + 1/180 =$ 6.22 mS so M = 6.22 mS/0.2 mS = 31 very well. Fig. 20(b) shows the IM<sub>3</sub> curves versus power for three cases: M = 0 (off), M = 28 (cancelling of I<sub>O</sub>, Fig. 6) and M = 32 (overall optimum IIP<sub>3</sub>). Up to -22 dBm input power (note: this power is high for an in-band signal), IM<sub>3</sub> improves. The rise of distortion for high input powers > -23 dBm is due to the clipping of the OpAmp output stage to its 1.2 V supply. The negative conductance was pushed to instability (i.e., latch-up of OpAmp output stage). This occurs at M = 45 (see (8)  $\Delta G = \Delta M \times 0.2 \text{ mS}$ ), safely away from the optimum point by  $\Delta M = 45 - 32 = 13$ . This shows a close agreement with our explanation in Section III and with the simulations in Fig. 21, which is done for the circuit of Fig. 13. One tone input signal with power of -16 dBm is used. Around this input power, the OpAmp output stage begins to clip. According to our simulation, the latch-up occurs for  $\Delta M \ge 14$ . The same mechanism, discussed in Section II, of this technique also improves  $IIP_2$  by more than 10 dB as shown in Fig. 22 Table I compares/summarizes the IIP<sub>2</sub> and IIP<sub>3</sub> improvement for three M settings 0, 28 en 32. Note that the optimum linearity point will vary somewhat with Process, Voltage and Temperature (i.e., PVT). The analysis in this paper gives the relation between the required negative conductance and the resistance values  $R_{O}$  and  $R_{F}$ , which can be a basis for designing an automatic PVT correction circuit.

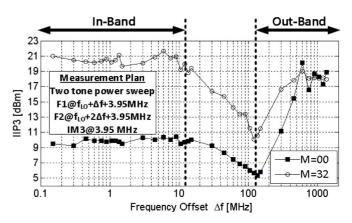

Fig. 23 provides  $IIP_3$  curves versus the frequency offset  $\Delta f$ , with fixed 3.95 MHz in-band  $IM_3$  position. The negative conductance clearly increases the  $IIP_3$  both in- and out-of-band

Fig. 22. Measurements:  $\rm IM_2$  versus input power for three M settings, with  $\rm LO=1$  GHz.

TABLE I  $IIP_2$  and  $IIP_3$  Improvement

| М  | IIP2 [dBm] | IIP3 [dBm] |  |

|----|------------|------------|--|

| 0  | 51         | 9.4        |  |

| 28 | 58.4       | 17         |  |

| 32 | 61.2       | 21         |  |

(all-Band) with a worst case  $IIP_3 > +10$  dBm. The reason behind less linearity improvement in the transition band can be understood considering the equivalent circuit earlier derived for stability analysis in Fig. 12. The negative conductance cancels only the loading of  $R_O$  and  $R_F$ . However, gm(s),  $C_F$  and  $C_T$ introduce frequency dependences. Consequently, the "loading effect" on the VGND node (see Fig. 5) becomes frequency dependent and will introduce a phase shift compared with the (frequency independent) current generated by the negative conductance. This results in imperfect cancellation, i.e., less linearity improvement at high frequencies. This may be improved in the future by designing the negative conductance to be frequency dependent as well. Up to 10 MHz, in-band IIP<sub>3</sub> is > +20 dBm, i.e., >10 dB improvement thanks to the negative conductance. Then the IIP<sub>3</sub> declines from 12 MHz to 135 MHz, on the one hand because the OTA gain and hence its linearity degrades, but on the other hand also because the benefit from cancellation drops (the top line in Fig. 23 drops faster, versus  $\Delta f$ , than the bottom line). Note that the out-of-band IIP<sub>3</sub> at  $\Delta f > 450$  MHz is again high, +18 dBm. This is because at high  $\Delta f$  (i.e., spacing between the carriers) the carriers are filtered due to the low pass filtering by  $C_F$ ,  $R_F$  and  $C_O$ , hence less  $IM_3$  products. In this region the negative conductance doesn't result in any benefit anymore.

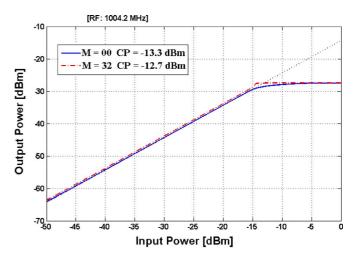

The compression point (CP) is around -13 dBm (hardly affected by M as shown in Fig. 24). Due to the virtual ground, S<sub>11</sub> is hardly affected by the negative conductance and Fig. 25(a) shows that S<sub>11</sub> < -25 dB. Noise is more worrisome, but depending on the application some degradation may be acceptable, provided that the overall SFDR still improves (i.e., IIP<sub>3</sub> in dBm should improve more than NF in dB degrades). Fig. 25(b) shows that NF increases from 6.2 dB at M = 0 to 7.5 dB at M = 32.

Fig. 23. 2-tone IIP  $_3$  measured at  $\rm IM_3=3.95~MHz$  versus tone spacing  $\Delta f,$  with LO = 1 GHz.

Fig. 24. Compression point.

This result is close to the NF prediction in the previous section. The 1/f corner was around 2 MHz.

The current consumption without the negative conductance at 1 GHz LO is 18 mA (including 8 mA of clock circuitry (i.e., on-chip drivers and divider)), and 1.6 mA more for M = 32. The clock divider frequency range (i.e., also the receiving RF frequency) is 0.2–2.6 GHz, where it consumes 2.8–19 mA. The maximum gate-source voltage of the mixer switches is equal to the 1.2 V supply. The LO leakage to the RF port is less than -75 dBm. The optimum IIP<sub>3</sub> has been measured for 5 samples. The optimum in-band IIP<sub>3</sub> varies ±1 dB around +21 dBm and the corresponding M varies ±2 around M = 32.

Table II benchmarks this work to other state-of-the-art receivers with high linearity and/or SFDR. Our front-end is more linear than [3] and [5], where active RF blocks are present. Even compared to the mixer-first designs [6], [7], we achieve better in-band IIP<sub>3</sub> while our SFDR in 1 MHz of 85 dB is the highest.

#### VII. CONCLUSION

Due to the strong relationship between linearity and voltage swing, it is challenging to improve linearity in advanced CMOS technologies with low supply voltages. Architectures with RF V-I conversion followed by a passive mixers and an OTA-RC

Fig. 25. Measurements (a)  $S_{11}$  (b) Noise Figure, with LO = 1 GHz.

TABLE II

Summary of Measurement Results and Comparison to Other State-of-the-Art Receivers

|                            | This work     | Ru [3]                             | Murphy [4]   | Youssef [5]                         | Soer [6]                    | Andrews [7]                 | units |

|----------------------------|---------------|------------------------------------|--------------|-------------------------------------|-----------------------------|-----------------------------|-------|

| Linearization<br>Technique | Negative GO   | Partial cancel<br>Noise/Distortion | Cancel Noise | Freq. Translated<br>Active feedback | Feedback +<br>N-path filter | Feedback +<br>N-path filter |       |

| Matching                   | Switch-R      | Common-gate                        | Switch-R     | R                                   | -                           | via TIA                     |       |

| Mixer type                 | Switch-R      | Switch-I                           | Switch-R&I   | Gm + Switched-I                     | Switch-RC                   | Switch-RC                   |       |

| Baseband-stage             | TIA + RC      | TIA+RC                             | TIA + RC     | Inverter-RC                         | Voltage Amp                 | TIA+RC                      |       |

| CMOS Techn.                | 65nm          | 65nm                               | 40nm         | 65nm                                | 65nm                        | 65nm                        |       |

| Active Area                | < 0.2         | < 1                                | 1.2          | < 0.06                              | < 0.13                      | 0.75                        | mm2   |

| RF Frequency               | 0.2-2.6       | 0.4-0.9                            | 0.08-2.7     | 1.0-2.5                             | 0.2-2.0                     | 0.1-2.4                     | GHz   |

| Gain                       | 26.5          | 34                                 | 70           | 30                                  | 19                          | 40-70                       | dB    |

| In-band BW[1]              | 24            | 24                                 | 4            | 5                                   | 50                          | 1.6                         | MHz   |

| NF                         | 7.5           | 4                                  | 2            | 7.25-8.9                            | 6.5                         | 4                           | dB    |

| In-band $IIP_3$            | > +20         | +3.5                               | -22          | -20                                 | +11                         | -67                         | dBm   |

| SFDR @ 1MHz<br>bandwidth   | 85            | 75                                 | 60           | 57                                  | 79                          | 29                          | dB    |

| Wide-Band IIP <sub>3</sub> | ≥+18 @ >450   | +18 @ Δf>800                       | +13.5        | > +12                               | Not                         | +25                         | dBm   |

| @2-tone ∆f                 | >+10 @ All ∆f |                                    | @∆f>40       | @ ∆f>60                             | measured                    | @ ∆f>50                     | @ MHz |

| Supply Voltage             | 1.2           | 1.2                                | 1.3          | 1.2                                 | 1.2                         | 1.2 / 2.5                   | V     |

| Power<br>Consumption       | 13.9          | 39.6                               | 15.6         | 62                                  | 60                          | < 70[2]                     | mW    |

[1] In-band BW is twice the zero-IF bandwidth around the LO frequency

Transimpedance Amplifier perform relatively well. In such architectures, the OpAmp can become the bottleneck, especially for wide channel bandwidth, where the amount of loop gain available for negative feedback is limited. Still high linearity is wanted, not only out-of-band but also in-band, as RF-filtering often is ineffective for close-in interferers. This paper shows how virtual ground imperfections due to OTA nonlinearity lead to distortion currents, which can be cancelled exploiting a negative conductance in parallel to the virtual ground node. Although the technique results in slightly degraded noise figure from 6 to 7.5 dB the in-band IIP<sub>3</sub> (and IIP<sub>2</sub>) is improved by much more (>10 dB), resulting in-band SFDR = 85 dB in 1 MHz bandwidth.

## APPENDIX A

In this section, a 3rd order Taylor approximation of  $V_{OUT}$  versus  $I_S$  (i.e.,  $V_{OUT} = V_{OUT}(I_S, I_S^3)$ ) of the transimpedance amplifier in Fig. 9 will be derived. The following procedure will be applied:

- 1.  $V_{OUT}$  is derived as a function of  $V_{VGND}, V^3_{VGND}$  and  $V^3_{OUT} \rightarrow V_{OUT} = V_{OUT}(V_{VGND}, V^3_{VGND}, V^3_{OUT})$ .

- 2. The resulting relationship is rewritten as a function of  $V_{\rm VGND}$  and  $V_{\rm VGND}^3$ , by using the definition

of the 3rd order Taylor coefficients  $\rightarrow V_{OUT} = V_{OUT}(V_{VGND}, V_{VGND}^3).$

[2] Includes the clock circuitry

- 3. The inverse function,  $V_{VGND}$  as a function of  $V_{OUT}$  and  $V_{OUT}^3$ , is written as a 3rd order Taylor function by using the procedure explained in [15]  $\rightarrow V_{VGND} = V_{VGND}$  ( $V_{OUT}, V_{OUT}^3$ ).

- 4. I<sub>S</sub> is rewritten as a function of  $V_{VGND}$  and  $V_{OUT} \rightarrow I_S = I_S(V_{VGND}, V_{OUT})$ .

- 5. Substituting  $V_{\rm VGND}$  of step 3 in  $I_{\rm S}$  of step 4 makes  $I_{\rm S}$  to be a function of  $V_{\rm OUT}$  and  $V_{\rm OUT}^3 \rightarrow I_{\rm S} = I_{\rm S}(V_{\rm OUT},V_{\rm OUT}^3).$

- 6. Finally, by repeating the procedure explained in [15], the function of step 5 is inversed to obtain  $V_O$  as a function of  $I_S$  and  $I_S^3 \rightarrow V_{OUT} = V_{OUT}(I_S, I_S^3)$ .

Step  $1 \rightarrow V_{OUT} = V_{OUT}(V_{VGND}V_{VGND}^3, V_{OUT}^3)$ : We begin the derivation by expressing the feedback current  $I_F$  at the VGND node and the OUT node (see Fig. 9) as follows:

At VGND node :

$$I_F = \frac{V_{VGND}}{R_{F-VGND}} + G_{F-VGND}V_{OUT}$$

(14)

At OUT node :

$$I_F = -\frac{V_{OUT}}{R_{F-OUT}} - G_{F-OUT}V_{VGND}$$

(15)

Referring to the OpAmp nonlinear model, we equate the  $I_F$  in (1) to  $I_F$  in (15) as follows:

$$gm_{1}V_{VGND} + gm_{3}V_{VGND}^{3} + go_{1}V_{OUT} + go_{3}V_{OUT}^{3}$$

$$= -\frac{V_{OUT}}{R_{F-OUT}} - G_{F-OUT}V_{OUT}$$

$$V_{OUT} = -\frac{(gm_{1} + G_{F-OUT})}{(go_{1} + \frac{1}{R_{F-OUT}})}V_{VGND}$$

$$-\frac{gm_{3}}{(go_{1} + \frac{1}{R_{F-OUT}})}V_{VGND}^{3} - \frac{go_{3}}{(go_{1} + \frac{1}{R_{F-OUT}})}V_{OUT}^{3}$$

(16)

Step  $2 \rightarrow V_{OUT} = V_{OUT}(V_{VGND}, V^3_{VGND})$ :  $V_{OUT}$  is defined as:  $V_{OUT} = \beta_1 V_{VGND} + \beta_2 V^2_{VGND} + \beta_3 V^3_{VGND}$ , which is a 3rd order Taylor approximation around  $V_{VGND} = 0$ , where  $\beta_1, \beta_2$  and  $\beta_3$  are the Taylor coefficients:

$$\beta_{n=1,2,3} = \frac{1}{n!} \left. \left( \frac{\partial^{n} V_{OUT}}{\partial V_{VGND}^{n}} \right) \right|_{V_{VGND}=0}$$

To derive  $\beta_1$ , we differentiate (16) with respect to V<sub>VGND</sub> as follows:

$$\begin{aligned} \frac{\partial V_{OUT}}{\partial V_{VGND}} &= a + 3bV_{VGND}^2 + 3cV_{OUT}^2 \frac{\partial V_{OUT}}{\partial V_{VGND}} \Rightarrow \frac{\partial V_{OUT}}{\partial V_{VGND}} \\ &= \frac{a + 3bV_{VGND}^2}{1 - 3cV_{OUT}^2} \\ \therefore \beta_1 &= \left(\frac{\partial V_{OUT}}{\partial V_{VGND}}\right) \Big|_{V_{VGND}=0} \\ &= a = -\frac{\left(gm_1 + G_{F-OUT}\right)}{\left(go_1 + \frac{1}{R_{F-OUT}}\right)} \end{aligned}$$

The same procedure is used to derive  $\beta_2$  and  $\beta_3$ :

$$\beta_{2} = \frac{1}{2} \left( \frac{\partial^{2} V_{OUT}}{\partial V_{VGND}^{2}} \right) \Big|_{V_{VGND}=0} = 0 \text{ and}$$

$$\beta_{3} = \frac{1}{6} \left( \frac{\partial^{3} V_{OUT}}{\partial V_{VGND}^{3}} \right) \Big|_{V_{VGND}=0} = b + a^{3}c$$

$$V_{OUT} = \underbrace{a}_{\beta_{1}} V_{VGND} + \underbrace{(b + a^{3}c)}_{\beta_{3}} V_{VGND}^{3}$$

(17)

Step 3  $\rightarrow V_{VGND} = V_{VGND}(V_{OUT}, V_{OUT}^3)$ : We write the inverse of (17) in the Taylor series form:  $V_{VGND} = \alpha_1 V_{OUT} + \alpha_2 V_{OUT}^2 + \alpha_3 V_{OUT}^3$ . Deriving  $\alpha_1, \alpha_2$  and  $\alpha_3$  can be done by the procedure below.

First, let us substitute (17) into its abovementioned inversed form as follows:

$$\begin{aligned} \mathbf{V}_{\mathrm{VGND}} &= \alpha_1 \left( \beta_1 \mathbf{V}_{\mathrm{VGND}} + \beta_3 \mathbf{V}_{\mathrm{VGND}}^3 \right) \\ &+ \alpha_2 (\beta_1 \mathbf{V}_{\mathrm{VGND}} + \beta_3 \mathbf{V}_{\mathrm{VGND}}^3)^2 + \alpha_3 (\beta_1 \mathbf{V}_{\mathrm{VGND}} + \beta_3 \mathbf{V}_{\mathrm{VGND}}^3)^3 \end{aligned}$$

By equating the right to the left side of the equation above [15], the coefficients  $\alpha_1, \alpha_2$  and  $\alpha_3$  are derived:

$$V_{\rm VGND} = \underbrace{\frac{1}{a}}_{\alpha_1} V_{\rm OUT} \underbrace{-\frac{(b+a^3c)}{a^4}}_{\alpha_3} V_{\rm OUT}^3 \qquad (18)$$

Step  $4 \rightarrow I_S = I_S(V_{VGND}, V_{OUT})$ : Referring to  $I_S$  in Fig. 9, we substitute the  $I_F$  (14) at the VGND node in the following equation:

$$I_{\rm S} = I_{\rm O} + I_{\rm F} = \left(\frac{1}{\rm R_O} + \frac{1}{\rm R_{\rm F-VGND}}\right) V_{\rm VGND} + G_{\rm F-VGND} V_{\rm OUT} \quad (19)$$

Step  $5 \rightarrow I_S = I_S(V_{OUT}, V_{OUT}^3)$ : By substituting (18) into (19), the following equation is obtained:

$$I_{S} = \left[\frac{1}{a}\left(\frac{1}{R_{O}} + \frac{1}{R_{F-VGND}}\right) + G_{F-VGND}\right] V_{OUT} - \frac{(b+a^{3}c)}{a^{4}}\left(\frac{1}{R_{O}} + \frac{1}{R_{F-VGND}}\right) V_{OUT}^{3} \quad (20)$$

Step 6  $\rightarrow V_{OUT} = V_{OUT}(I_S, I_S^3)$ : Finally, by inversing (20), we reach (21), shown at the bottom of the page, where  $NL_3 = ((b + a^3c))/(a^4)$  is related to the nonlinear terms of the OpAmp model.

#### APPENDIX B

In this section, the relation between  $V_{VGND}$  and  $I_S$  is derived to be used in the latch-up analysis section. In order to simplify this analysis, we assume a linear OpAmp (i.e.,  $gm_3 = go_3 = 0$ ). Consequently, (16) and (21) can be simplified as follows:

$$V_{\rm VGND} = \frac{1}{a} V_{\rm OUT} \tag{22}$$

$$V_{\rm OUT} = \Omega_1 I_{\rm S} \tag{23}$$

)

$$V_{OUT} = \underbrace{\frac{1}{\left[\frac{1}{a}\left(\frac{1}{R_{O}} + \frac{1}{R_{F-VGND}}\right) + G_{F-VGND}\right]}}_{\Omega_{1}} I_{S} + \underbrace{\frac{NL_{3}\left(\frac{1}{R_{O}} + \frac{1}{R_{F-VGND}}\right)}{\left[\frac{1}{a}\left(\frac{1}{R_{O}} + \frac{1}{R_{F-VGND}}\right) + G_{F-VGND}\right]^{4}}_{\Omega_{3}} I_{S}^{3}$$

(21)

Combining (22) and (23), gives the following relation:

$$V_{VGND} = \frac{\Omega_1}{a} I_S = \frac{1}{\left[ \left( \frac{1}{R_O} + \frac{1}{R_{F-VGND}} \right) + a G_{F-VGND} \right]} I_S$$

(24)

After that the negative conductance cancels the loading effect of  $R_O$  on the VGND node, it injects current via  $R_F$  that needs to be handled by the OpAmp output stage (see Figs. 13 and 17). Now if the negative conductance becomes too strong then the potential latch-up becomes a real risk. For the case of latch-up, (24) can be further elaborated to obtain the following equation:

$$V_{VGND} = \frac{I}{\left[\left(\frac{1}{R_{F-VGND}} - G_{Latch-up}\right) + a G_{F-VGND}\right]} I_{S}$$

(25)

#### ACKNOWLEDGMENT

The authors thank STMicroelectronics for silicon donation and CMP, Andreia Cathelin (STM), Michiel C.M. Soer, Gerard Wienk, and Henk de Vries for their measurement assistance. Special thanks goes to Shadi S. T. Youssef and Harish K. Subramaniyan for their discussions and remarks on this work.

#### REFERENCES

- 3GPP TS 36.104:, "Evolved universal terrestrial radio access (E-UTRA); Base station (BS) radio transmission and reception," [Online]. Available: http://www.3gpp.org

- [2] D. H. Mahrof, E. A. M. Klumperink, J. Haartsen, and B. Nauta, "On the effect of spectral location of interfererson linearity requirements for wideband cognitive radio receivers," in *IEEE Symp. New Frontiers in Dynamic Spectrum Access Networks (DySPAN)*, Apr. 2010, pp. 1–9.

- [3] Z. Ru, E. A. M. Klumperink, and B. Nauta, "A software-defined radio receiver architecture robust to out-of-band interference," in *IEEE ISSCC Dig. Tech. Papers*, 2009, pp. 230–231.

- [4] D. Murphy, A. Hafez, A. Mirzaei, M. Mikhemar, H. Darabi, M. F. Chang, and A. Abidi, "A blocker-tolerant wideband noise-cancelling receiver with a 2 dB noise figure," in *IEEE ISSCC Dig. Tech. Papers*, 2012, pp. 74–76.

- [5] S. S. T. Youssef, R. A. R. van der Zee, and B. Nauta, "Active feedback receiver with integrated tunable RF channel selectivity, distortion cancelling, 48 dB stop-band rejection and > + 12 dBm wideband IIP3, occupying < 0.06 mm<sup>2</sup> in 65 nm CMOS," in *IEEE ISSCC Dig. Tech. Papers*, 2012, pp. 166–168.

- [6] M. C. M. Soer, E. A. M. Klumperink, Z. Ru, F. E. van Vliet, and B. Nauta, "A 0.2-to-2.0 GHz 65 nm CMOS receiver without LNA achieving >11 dBm IIP3 and <6.5 dB NF," in *IEEE ISSCC Dig. Tech. Papers*, 2009, pp. 222–223.

- [7] C. Andrews and A. C. Molnar, "A passive mixer-first receiver with digitally controlled and widely tunable RF interface," *IEEE J. Solid-State Circuits*, vol. 45, no. 12, pp. 2696–2708, Dec. 2010.

- [8] S. C. Blaakmeer, E. A. M. Klumperink, D. M. W. Leenaerts, and B. Nauta, "The Blixer, a wideband balun-LNA-I/Q-mixer topology," *IEEE J. Solid-State Circuits*, vol. 43, pp. 2706, 2715, Dec. 2008.

- [9] D. H. Mahrof, E. A. M. Klumperink, M. S. Oude Alink, and B. Nauta, "A receiver with in-band IIP3 > 20 dBm, exploiting cancelling of OpAmp finite-gain-induced distortion via negative conductance," in *IEEE Radio Frequency Integrated Circuits Symp. (RFIC)*, 2013, pp. 601–604.

- [10] J. Deguchi *et al.*, "A fully integrated 2 × 1 dual-band direct-conversion mobile WiMAX transceiver with dual-mode fractional divider and noise-shaping transimpedance amplifier in 65 nm CMOS," *IEEE J. Solid-State Circuits*, vol. 45, no. 12, pp. 2774–2784, Dec. 2010.

- [11] B. Razavi, *RF Microelectronics*. Englewood Cliffs, NJ, USA: Prentice Hall, 1998.

- [12] Z. Ru, "Frequency translation techniques for interference-robust software-defined radio receivers," Ph.D. dissertation, Univ. Twente, Enschede, The Netherlands, 2009.

- [13] F. Bruccoleri, E. A. M. Klumperink, and B. Nauta, "Noise cancelling in wideband CMOS LNAs," in *IEEE ISSCC Dig. Tech. Papers*, 2002, pp. 406–407.

- [14] W. Redman-White and D. M. W. Leenaerts, "1/f noise in passive CMOS mixers for low and zero IF integrated receivers," in *Proc. ESSCIRC*, 2001, pp. 18–20.

- [15] E. A. M. Klumperink, "Transconductance based CMOS circuits" Ph.D. dissertation, Univ. Twente, Enschede, The Netherlands, 1997 [Online]. Available: http://jive.el.utwente.nl/home/erick/Klumperink-PhD-Thesis.pdf?

**Dlovan H. Mahrof** (S'13) was born on December 26, 1973, in Al-Sulaimaniya, Iraq. He received the B.Sc. degree in power engineering from Baghdad University, Iraq, in 1995. He received the B.Sc. degree and the M.Sc. degree in electrical engineering from Twente University, The Netherlands, in 2005 and 2008. From 2008 to 2012, he did his Ph.D. research on "Distortion Mitigation in Cognitive Radio Receivers" with the IC-Design group of Twente University, headed by Bram Nauta. During the RFIC 2013 Symposium, Seattle, WA, USA, he

won the Best Student Paper Award-1st place.

From 2012 until the present, he has been working at Bruco IC Company, The Netherlands, as a system and ASIC-design engineer. His research interests include circuit design, and advanced concept techniques applied to RF frontends.

Eric A. M. Klumperink (M'98–SM'06) was born on April 4, 1960, in Lichtenvoorde, The Netherlands. He received the B.Sc. degree from HTS, Enschede, The Netherlands, in 1982. After a short period in industry, he joined the University of Twente in 1984, participating in analog CMOS circuit research, resulting in several publications and his Ph.D. thesis "Transconductance Based CMOS Circuits" (1997).

In 1998, he became Assistant Professor at the IC-Design Laboratory in Twente and his research focus changed to RF CMOS circuits. In April–Au-

gust 2001, he extended his RF expertise during a sabbatical at the Ruhr Universitaet in Bochum, Germany. Since 2006, he is an Associate Professor, teaching Analog & RF IC Electronics courses. He participates in the CTIT Research Institute, guiding Ph.D. and M.Sc. projects related to RF CMOS circuit design with focus on Software Defined Radio, Cognitive Radio and Beamforming.

Dr. Klumperink served as an Associate Editor for the IEEE TRANSACTIONS ON CIRCUITS AND SYSTEMS II (2006–2007), IEEE TRANSACTIONS ON CIRCUITS AND SYSTEMS I (2008–2009), and IEEE JOURNAL OF SOLID-STATE CIRCUITS (2011–2013). He is a member of the technical program committees of the IEEE International Solid State Circuits Conference (ISSCC) and IEEE RFIC Symposium. He holds several patents, has authored and co-authored more than 180 international refereed journal and conference papers, and was a co-recipient of the ISSCC 2002 and the ISSCC 2009 Van Vessem Outstanding Paper Award.

Zhiyu Ru (M'09) received the Bachelor degree from Southeast University, Nanjing, China, in 2002, the Master degree from Lund University, Lund, Sweden, in 2004, and the Ph.D. degree from the University of Twente, Enschede, The Netherlands, in 2009, all in electrical engineering. In 2003, he was with Z-Com in Nanjing, working on WLAN products. In 2004, he did his Master thesis with Ericsson in Lund, working on the DVB-T receiver. From 2005 to 2009, he did his Ph.D. research with the IC-Design group of Twente, working on software-defined radios. From 2010 to 2012, he did postdoctoral research in the same group on clocking techniques. In 2011, he was a visiting scientist at Massachusetts Institute of Technology (MIT), Cambridge, MA, USA. In 2012, he joined MediaTek in MA.

Mark S. Oude Alink (M'13) was born in 1984, in Hengelo, The Netherlands. He received the B.Sc. degree in computer science in 2004 and the M.Sc. degrees in electrical engineering and computer science (both *cum laude*) in 2008, all from the University of Twente, Enschede, The Netherlands. He received the Ph.D. degree (*cum laude*) from the same university in May 2013.

He is currently a system engineer and IC designer at Bruco Integrated Circuits in Borne, The Netherlands.

**Bram Nauta** (M'91–SM'03–F'08) was born in Hengelo, The Netherlands. In 1987 he received the M.Sc. degree (*cum laude*) in electrical engineering from the University of Twente, Enschede, The Netherlands. In 1991 he received the Ph.D. degree from the same university on the subject of analog CMOS filters for very high frequencies.

In 1991 he joined the Mixed-Signal Circuits and Systems Department of Philips Research, Eindhoven, The Netherlands. In 1998 he returned to the University of Twente, as full Professor heading the IC Desarah interact is the speed englage CMOS airwrite.

sign group. His current research interest is high-speed analog CMOS circuits.

Dr. Nauta served as Associate Editor of IEEE TRANSACTIONS ON CIRCUITS AND SYSTEMS II (1997–1999). He was Guest Editor, Associate Editor (2001–2006) and later the Editor-in-Chief (2007–2010) of IEEE JOURNAL OF SOLID-STATE CIRCUITS. He was a member of the technical program committee of the IEEE International Solid State Circuits Conference (ISSCC), where he served in several roles including the European Regional Chair and the 2013 Program Chair. He also serves in the Technical Program Committee of the European Solid State Circuit Conference (ESSCIRC) and the Symposium on VLSI circuits. He was a co-recipient of the ISSCC 2002 and 2009 Van Vessem Outstanding Paper Award. He is a distinguished lecturer of the IEEE, a member of IEEE SSCS AdCom, and an IEEE fellow.