# An In-Band Full-Duplex Radio Receiver With a Passive Vector Modulator Downmixer for Self-Interference Cancellation

Dirk-Jan van den Broek, *Student Member, IEEE*, Eric A. M. Klumperink, *Senior Member, IEEE*, and Bram Nauta, *Fellow, IEEE*

*Abstract*—In-band full-duplex (FD) wireless, i.e., simultaneous transmission and reception at the same frequency, introduces strong self-interference (SI) that masks the signal to be received. This paper proposes a receiver in which a copy of the transmit signal is fed through a switched-resistor vector modulator (VM) that provides simultaneous downmixing, phase shift, and amplitude scaling and subtracts it in the analog baseband for up to 27 dB SI-cancellation. Cancelling before active baseband amplification avoids self-blocking, and highly linear mixers keep SI-induced distortion low, for a receiver SI-to-noise-and-distortion-ratio (SINDR) of up to 71.5 dB in 16.25 MHz BW. When combined with a two-port antenna with only 20 dB isolation, the low RX distortion theoretically allows sufficient digital cancellation for over 90 dB link budget, sufficient for short-range, low-power FD links.

*Index Terms*—Distortion, full duplex (FD), interference cancellation, receiver, self-interference (SI), vector modulator (VM).

#### I. INTRODUCTION

**I** N-BAND full-duplex (FD) wireless communication is an emerging, unconventional scheme for radio links: transmission and reception occur simultaneously at the same frequency, thus utilizing the same spectral resources in two directions at once. In the physical layer, FD obviously promises up to  $2\times$  spectral efficiency. In higher network layers, further advantages are being explored such as collision prevention, low latency, and security [1]. Additionally, FD simplifies frequency planning.

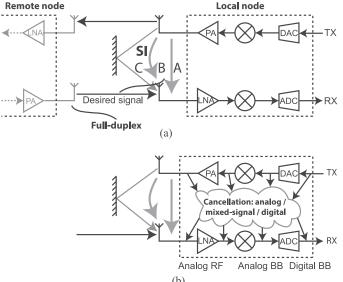

The main issue in achieving FD wireless is strong in-band (same-channel) crosstalk from transmitter to receiver, referred to as self-interference (SI), see Fig. 1(a) [2]. Recovering the (much weaker) desired signal from a remote transmitter necessitates SI isolation and cancellation. Cancellation uses knowledge of the transmit signal from various points in the TX chain to subtract SI in the RX chain [Fig. 1(b)].

From this generic view, many types of SI-cancellation can be conceived, and to some extent freely combined, ranging from

The authors are with IC Design Group, University of Twente, 7500AE Enschede, The Netherlands (e-mail: j.d.a.vandenbroek@utwente.nl).

Digital Object Identifier 10.1109/JSSC.2015.2482495

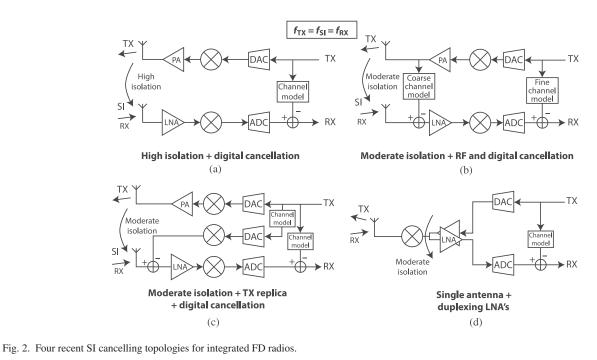

RF to analog BB, to digital BB and even cross-domain cancellation. Fig. 2 shows four recent approaches to SI-cancellation.

- High isolation can be obtained at the antenna by design, e.g., using cross-polarization [3]. However, it is difficult to achieve high isolation in compact hand-held devices with a varying antenna near-field. Such variations can be addressed using tuneable coupling between antennas [4] which recently showed integration potential and wideband cancellation at 60 GHz [5]. Another approach is electrical balance duplexing [3], which can be tuneable and frequency-agile, but has extreme linearity requirements only demonstrated in SOI CMOS [6].

- 2) Direct crosstalk as well as part of the reflected SI can be cancelled using an analog multitap filter at RF, combined with digital cancellation [7], [8]. This requires nanosecond-scale analog delays in its analog filter [7], which have only recently been integrated in the form of *N*-path filters [8]. This approach has potential to compete with high-end (802.11 style) half-duplex links [7]; however, silicon/PCB area and power consumption remain high.

- 3) A replica TX chain can be used to regenerate the SI in the digital BB and cancel it at RF, combined with digital cancellation [9]. However, its ultimate cancellation performance is limited by uncorrelated noise and distortion sources between the two TX chains, and by phase noise (PN) if separate LO signals are used for the TX chains [10].

- 4) A mixer-first transceiver with baseband noise-cancelling, duplexing LNAs can be used that intrinsically copy a transmit signal to their antenna port, while rejecting it in their output [11]. Placing the LNAs in the baseband allows complex signal processing to tune their SIrejection. Although very suitable for integration and capable of operating with a single-port antenna, the duplexing LNAs have limited capability to work with high TX powers [11] and the TX performance will be limited by the loss of the mixers.

As an alternative method, in [12], we demonstrated an SI-cancelling receiver for frequency-agile, low-power, short-range FD. This paper provides more background information, implementation details, performance analysis, and modeling of the presented design. It is structured as follows: First, we briefly review system considerations for FD and show how the

0018-9200 © 2015 IEEE. Personal use is permitted, but republication/redistribution requires IEEE permission. See http://www.ieee.org/publications\_standards/publications/rights/index.html for more information.

Manuscript received April 20, 2015; revised August 17, 2015; accepted September 11, 2015. Date of publication October 19, 2015; date of current version November 24, 2015. This paper was approved by Guest Editor Kenichi Okada. This work was supported by the European Union Seventh Framework Programme (FP7/2007-2013) under Grant 316369—Project DUPLO.

Analog RF Analog BB Digital BB (b) Fig. 1. (a) Generic view of an FD link between a local and a remote node, subject to three types of SI: (A) electrical crosstalk between TX and RX, (B) RF coupling due to limited antenna isolation and a varying antenna near-field, and (C) SI reflected by the environment. (b) Generic view of SI-cancellation in a single FD node, from various points in the TX chain to various points in the RX chain.

proposed receiver topology emerges. Next, Section III describes the implementation of the prototype SI-cancelling receiver. Section IV describes the measured performance and relates it to FD link capabilities. Section V concludes this work.

# II. SYSTEM CONSIDERATIONS AND PROPOSED ARCHITECTURE

The SI-cancelling receiver developed here aims to bring FD to low-power, short-range communication devices. For this purpose, a TX power of 0 dBm is assumed, a bandwidth of 16.25 MHz (the active bandwidth of WLAN) and a 10 dB RX noise figure (NF). This results in an RX noise floor of roughly -90 dBm. Thus, in order not to degrade the noise floor, combined isolation and cancellation mechanisms should reliably reject the SI by at least 90 dB. Furthermore, we assume that a compact antenna solution in a changing near-field can achieve a worst-case isolation of only 20 dB, requiring 90 - 20 = 70 dB from cancellation.

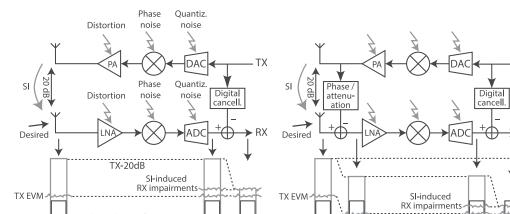

Fig. 3(a) visualizes an attempt to cancel the remaining SI after antenna isolation all in the digital domain. Assuming digital cancellation can only cancel the deterministic, linear part of the SI, TX EVM, and SI-induced RX noise and distortion may still mask the desired signal [2]. To prevent this, roughly 70 dB TX EVM and 70 dB RX DR would be required, which is not feasible in a low-power FD node.

Introducing a frequency-flat phase shift/attenuation-based canceller at RF can improve RF SI-rejection to a level limited by the frequency-selectivity of the antenna interface, environment, and the desired bandwidth [Fig. 3(b)]. To further cope with frequency-selectivity in this architecture, the canceller would need to incorporate multinanosecond time or group delay (i.e., a nonflat phase response) [8], which may become costly

in silicon area. However, in an indoor scenario, the reflections in the 2.4 GHz ISM band are reportedly present at -40to -50 dB [13]. For an antenna interface with limited additional frequency-selectivity, a frequency-flat canceller at RF may therefore reduce requirements on TX EVM, RX DR, and digital cancellation to  $90 - \{40 \text{ to } 50\} = 40$  to 50 dB, which is much more feasible than 70 dB.

As such, the useful attenuation range for the canceller in this system with respect to the TX power ranges from 20 dB (worst-case SI from the antenna) to 50 dB (best-case level of the reflections). As for the phase shift, a full  $360^{\circ}$  range is desirable since the absolute phase of the SI can assume any value depending on the antenna configuration. So the canceller may consist of 20 dB fixed attenuation, about 30 dB variable attenuation, and a full  $360^{\circ}$  phase shift.

For a frequency-flat canceller, the tolerable group delay  $\delta$  of the antenna solution can be evaluated mathematically. Assuming optimum cancellation in the center of bandwidth BW, the phase error at the band edge equals  $\phi_e = \delta \times 2\pi BW/2$ , resulting in an SI-cancellation at the band edge of SIC =  $-20 \log_{10}(2 \sin(\phi_e/2))$ . Rewriting yields the tolerable group delay

$$\delta = \frac{2}{\pi BW} \sin^{-1} \left( \frac{10^{-\frac{SIC}{20}}}{2} \right) \approx \frac{10^{-\frac{SIC}{20}}}{\pi BW}$$

(1)

using a small-angle approximation. Here, SIC is the desired *worst-case* SI-cancellation (at the band edge). Similarly, it can be shown that when *band-integrated* cancellation is considered, the tolerable group delay increases by a factor  $\sqrt{3}$ . For the aforementioned 20–30 dB SIC on top of 20 dB isolation integrated over 16.25 MHz BW, the tolerable group delay is 3.4–1.1 ns. For the following system design considerations, such values are assumed feasible.

The focus of this paper is on the receiver. An FD RX should realize a reasonable compromise between noise and SI-induced distortion. In other words, its SI-to-noise-and-distortion-ratio (SINDR) should be high for an optimum FD link budget. SINDR is depicted in Fig. 3(b).

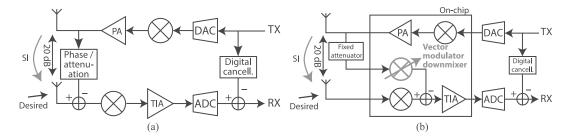

Maintaining high in-band linearity under strong SI is crucial to obtain an high SINDR, which motivates interchanging the LNA and mixer and moving to a mixer-first architecture [Fig. 4(a)]. Subsequently, the cancellation node may be moved to the analog baseband and the phase shift, attenuation and downmixing can be combined in a single component, i.e., a vector modulator (VM) downmixer [Fig. 4(b)].

This topology taps the TX signal at the TX RF output, thus including TX impairments in the cancellation, relaxing TX EVM requirements by the amount of cancellation achieved. It cancels SI before the baseband amplifiers and ADC, relaxing their DR requirements by the same amount. A fixed attenuator is added to match the VM range to the worst-case isolation of the chosen antenna solution and kept external for versatility.

The topology in Fig. 4(b) has high integration potential and as discussed, it is applicable to low-power, short-range FD nodes. Section III discusses implementation details of the receiver prototype.

Fig. 3. FD nodes assuming a moderate 20 dB antenna isolation: (a) SI is affected by transmitter and receiver imperfections, which limit cancellation in the digital domain. (b) Phase/amplitude-based canceller can enhance a moderately isolating antenna in the analog domain, relaxing TX EVM, RX dynamic range (DR), and digital cancellation requirements.

Fig. 4. (a) Generic phase shift/attenuation-based canceller preceding a mixer-first receiver. (b) Cancellation node is moved to the analog baseband and the phase shift, attenuation and downmixing are combined into a VM downmixer.

#### III. IMPLEMENTATION OF AN SI-CANCELLING RECEIVER

RX thermal noise floor

(a)

This section describes the implementation of an SIcancelling receiver in 65 nm CMOS according to the topology of Fig. 4(b). As explained in Section II, to allow cancellation of residual SI, including delayed SI-components, in digital and uncover the desired signal, the RX should have very high SINDR, and thus high in-band linearity under cancellation of strong SI. This prevents the SI from inducing distortion that raises the RX noise floor and masks the desired signal. In the proposed topology, this puts very strict in-band linearity requirements on both downmixers, as they both have to process the maximum TX leakage at their inputs. Furthermore, to

RX thermal noise

(b)

TX

RX

**RX SINDR**

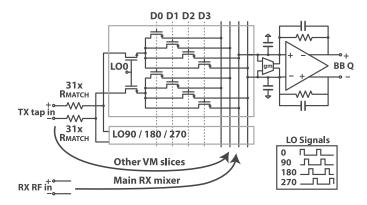

90 л \_п 180 \_п 31x TX tap in 31 RMATCH BB out Q SI-currents Main mixer RMATCH 4上  $\sim$ RX RF in **BB** out I **۸۸۸** RMATCH t t Virtual ground I Virtual ground Q

LO signals

<u>о п п</u>

Vector modulator 31 slices

Fig. 5. Implementation details of the SI-cancelling receiver. The VM (top) is a 31 slice version of the main receiver (bottom), each slice followed by static phase rotator switches. The VM diverts SI currents through linear passive networks before amplification.

prevent RX clipping under strong SI, cancellation has to take place before amplification. Contrary to traditional systems, there is no TX–RX frequency separation, so filtering cannot be used.

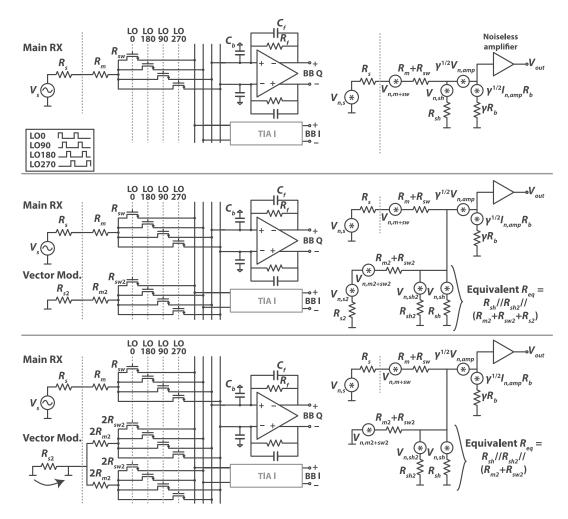

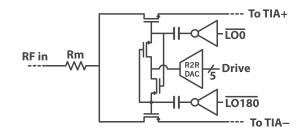

Hence, both the main RX and the VM are based on highly linear passive mixers with series resistors into virtual ground nodes provided by transimpedance amplifiers (TIAs) [14]. Fig. 5 shows an overview of the implemented receiver. The VM is a sliced version of the main RX, followed by static phase rotator switches that route the current of each slice into the four virtual grounds. This way, the SI currents are diverted through highly linear passive networks and only the residue is amplified. The number of slices and other design details are motivated next.

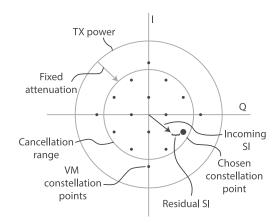

# A. Resolution

The sliced VM principle is similar to the constant- $g_m$  VM presented in [15] but implemented with resistors to a virtual ground rather than active transconductors. The amount of slices of the VM determines the number of phase/amplitude constellation points it can cover, and thus the amount of cancellation that can be achieved due to quantization effects. This is illustrated in Fig. 6. For n slices, the constellation consists of n + 1 by n + 1points. The maximum quantization error occurs when the actual SI phase and amplitude represent a point right in the center of four VM constellation points. Normalizing the constellation to a square of  $1 \times 1$ , the quantization error has a magnitude of  $q_e = \frac{\sqrt{2}}{2n}$ . Since the VM has to cover a full circle of phase shifts, the cancellation range is the largest circle that can be drawn through the constellation with maximum error  $q_e$ , which has a radius of 1/2 + 1/(2n). Thus, the worst-case cancellation given a number of slices is given by

SIC(dB) = 20 \*

$$\log_{10} \frac{\frac{1}{2} + \frac{1}{2n}}{\frac{\sqrt{2}}{2n}} = 20 * \log_{10}(n+1) - 3 \text{ dB}.$$

(2)

Fig. 6. Cancellation principle explained using a three slice VM (i.e., a  $4 \times 4$  constellation): a fixed attenuation maps the VM cancellation range on the worst-case expected SI, the VM selects the phase/amplitude point closest to the incoming SI, and some residual SI remains due to quantization effects.

As discussed in Section II, a cancellation up to 30 dB allows reducing the direct crosstalk to levels where frequency-selective components dominate the SI. Combined with practical constraints, a resolution of n = 31 slices was chosen, allowing 27.1 dB cancellation.<sup>1</sup> 31 slices can be conveniently segmented and controlled with 5 bits.

## B. Noise

Designs based on 50  $\Omega$  resistive termination and four phases, 25% duty cycle mixing have an NF that is fundamentally limited to 3.9 dB [16]. However, in the proposed design, the VM injects considerable noise current into the virtual ground nodes without contributing desired signal. Its noise contribution could be lowered by designing a weak TX coupler and scaling the VM impedance up from the 50  $\Omega$  standard (i.e., weaker coupling of the SI into the RX path [8]), but in order to use standard external equipment, 50  $\Omega$  matching was maintained also for the VM.

The VM noise depends on its setting. Analyzing this for all possible VM settings is mathematically involved, since each setting is a complex mapping of resistors and switches into each of the virtual ground nodes. However, three extremes can be analyzed to obtain upper and lower bounds for the NF.

- 1) The VM is disabled: the system acts as a conventional mixer-first receiver.

- The VM is set to an I/Q corner of the constellation, i.e., all slices are configured equally and the VM essentially behaves like a regular mixer.

- 3) The VM is set to minimum amplitude, i.e., the center of the constellation, where half of the slices is set 180° out of phase with the other half.

The latter point cannot be reached in practice, due to the odd number of slices, but given sufficient VM resolution it can be well approximated. Similarly, the second point (maximum amplitude) is not used in practice, since the VM will only use the highest amplitude it can achieve over the desired

<sup>1</sup>Slightly less than the 28.5 dB mentioned in [12] as a result of more accurate calculation.

Fig. 7. Left: Single-ended representations of the receiver in three configurations. Right: Equivalent noise models following the approach of [16]. Top: Cancellation path disabled. Center: VM set to maximum amplitude. Bottom: VM set to minimum amplitude.

TABLE I CALCULATED AND SIMULATED RX NF

|                  | Analysis | Simulation |

|------------------|----------|------------|

| VM disabled (dB) | 6.4      | 6.2        |

| VM maximum (dB)  | 9.8      | 9.9        |

| VM minimum (dB)  | 12.3     | 12.5       |

full phase circle (Section III-A). However, both points provide useful bounds for the NF. Fig. 7 depicts single-ended equivalent circuits in these three configurations, and their equivalent in-band LTI models for noise analysis according to [16]. For this analysis to be valid in-band, the time constants  $(R_s + R_m + R_{sw})(1 + A)C_f$  and  $R_fC_f$  are assumed much larger than  $1/f_{LO}$ , which is typically the case in this design. Out-of-band, the  $C_b$  shield the TIAs from high frequency IF components. For simplicity, the source impedances are considered resistive and frequency independent. Only thermal noise is considered.

In situation 1), the mixer can be represented by a resistor  $R_m + R_{sw}$ , due to the nonoverlapping nature of the LO signals. The noise and impedance folding effects of the linear time-variant circuit are represented by a shunt resistance  $R_{\rm sh} = \frac{4\gamma}{1-4\gamma}(R_m + R_{sw})$  in the LTI equivalent [16]. Here,  $\gamma = 2/\pi^2$ . The feedback amplifier is modeled by a noiseless amplifier preceded by its input impedance  $R_b = R_f/(1+A)$ and two correlated noise voltages  $v_{n,\rm amp}$  and  $i_{n,\rm amp}R_b$  where  $i_{n,\rm amp}^2 R_b^2 = \frac{4kTR_f}{(A+1)^2} + \frac{v_{n,\rm amp}^2}{(A+1)^2}$  [16]. The noise factor is then given by [16]

$$F = 1 + \frac{R_m + R_{sw}}{R_s} + \frac{R_{sh}}{R_s} \left(\frac{R_s + R_m + R_{sw}}{R_{sh}}\right)^2 + \gamma \frac{R_f}{R_s} \left(\frac{R_s + R_m + R_{sw}}{\gamma R_f}\right) + \gamma \frac{v_{n,\text{amp}}^2}{4kTR_s} \times \left(\frac{R_s + R_m + R_{sw}}{\gamma R_f} + \frac{R_s + R_m + R_{sw} + R_{sh}}{R_{sh}}\right)^2.$$

(3)

In situation 2), the VM can be represented like the main mixer by a source resistance  $R_{s2}$ , a switch and matching resistance  $R_{m2} + R_{sw2}$ , and a shunt resistance  $R_{sh2} = \frac{4\gamma}{1-4\gamma}(R_{s2} + R_{m2} + R_{sw2})$  accounting for the time-variant effects. This network is effectively in parallel with the original shunt resistance, so we can replace  $R_{sh}$  in (3) by an equivalent resistor

$$R_{\rm eq} = R_{\rm sh} / / R_{\rm sh2} / / (R_{sw2} + R_{m2} + R_{s2}). \tag{4}$$

In situation 3), the input of the VM can be considered a differential ground: the source resistance  $R_{s2}$  does not contribute any noise in this case, but the VM itself directly acts as a shunt resistor with value  $R_{m2} + R_{sw2}$ , which can be modeled in the LTI circuit as  $R_{sh2} = \frac{4\gamma}{1-4\gamma}(R_{m2} + R_{sw2})$ . The equivalent total shunt resistance now equals

$$R_{\rm eq} = R_{\rm sh} / / R_{\rm sh2} / / (R_{sw2} + R_{m2}).$$

(5)

The NF can be evaluated for the three scenarios by introducing practical values.  $R_s$  was kept at 50  $\Omega$  for both inputs.  $R_f$ is chosen 1.5 k $\Omega$  for 24 dB overall receiver gain. A two-stage, telescopic op-amp was used with  $A = 1000 \times$  open loop gain. The main noise contributors of the op-amp are the input pair  $(g_{m1} = 2 \times 23.4 \text{ mS})$  and the active loads of the input stage  $(g_{m2} = 2 \times 12.8 \text{ mS})$ . Assuming a noise excess factor of 1, the input-referred op-amp noise can be calculated as  $v_{n,\text{amp}}^2 = 4kT(g_{m1} + g_{m2})/(g_{m1}^2)$ . Taking into account a nonzero baseband impedance due to finite op-amp gain, matching is achieved by setting  $R_{sw} + R_m = 48 \Omega$  and  $R_{sw2} + R_{m2} = 48 \Omega$ . The results are listed in Table I.

Beside the analysis, simulations were performed at 2.5 GHz LO frequency, with the real baseband amplifier, but ideal mixers, resistors, and sources.  $C_f$  was chosen 8 pF for 13 MHz BW and  $C_b = 10$  pF capacitors were put on the virtual grounds to filter higher harmonics. Table I lists the simulated NF at 10 MHz offset, to minimize the influence of flicker noise. Analysis and simulation are in close agreement. In conclusion, the VM contributes the largest amount of noise at small amplitude settings, and enabling the cancellation path degrades the system NF by up to roughly 6 dB.

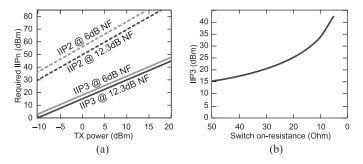

#### C. Linearity

This work considers SI-induced RX distortion as limiting for digital cancellation, since cancelling this in digital requires precise models of the TX, the channel and the RX distortion behavior, as well as added signal processing. Hence, we target minimizing the SI-induced distortion. In this FD mixer-first design, both SI-induced second-order nonlinearity (IM2) and third-order intermodulation (IM3) fall directly in the band of interest and deteriorate the system noise + distortion floor for desired signals. Thus, we aim for sufficient in-band IIP2 and IIP3 by design. Given the targeted 16.25 MHz BW, 20 dB worst-case isolation, and 12.3 dB NF, Fig. 8(a) plots the required in-band IIP2 and IIP3 to keep the SI-induced IM2 and IM3 equal to the system noise floor, as a function of transmit power. For illustrative purposes, the case for a 6 dB NF is also drawn. As motivated in Section II, this work targets at least 0 dBm TX power, resulting in in-band IIP2 and IIP3 requirements of roughly 20 and 50 dBm, respectively. Note that we aim for sufficiently low distortion to achieve analog cancellation while preserving the noise floor. We do not pursue sufficiently low distortion to further increase the TX power, as this would again put unfeasible requirements on the TX EVM and TIA/ADC DR (see Section II).

Ideally, for  $0 \Omega$  switches and a perfectly linear 50  $\Omega$  matching resistor, there is no signal swing across the switches and

Fig. 8. (a) Required IIP2 and IIP3 to keep the SI-induced IM2 and IM3 equal to the system thermal noise floor, as a function of TX power, assuming 16.25 MHz BW, 20 dB isolation, and 12.3 dB or 6 dB NF. (b) Theoretical IIP3 as a function of switch on-resistance.

therefore no IM3-currents are induced by the SI before cancellation. The only source of IM3 is the TIAs that process residual SI and the (usually weaker) desired signal. Therefore, every 1 dB of cancellation of the SI would result in a 2 dB reduction of the SI-induced IM3, boosting the effective IIP3 by 1 dB. However, low-ohmic mixer switches are powerhungry to drive, resulting in a tradeoff between power consumption and IIP3 for switched-resistor mixers. Assuming simple square-law behavior of the switch devices and ideal virtual grounds, the in-band linear and third order components can be computed to be  $a_1 = (R_s + R_m + R_{sw})^{-1}$  and  $a_3 =$  $(-R_s R_{sw}^2)/(2V_{OD}^2(R_{sw}+R_s)^5)$ , where  $V_{OD}$  is the overdrive voltage of the switches [17]. Then, IIP3 =  $\sqrt{(3/4)|a_1/a_3|}$ . Using  $V_{\rm OD} = 800 \text{ mV}$  and taking  $R_s = 50 \Omega$  and  $(R_m +$  $R_{sw}$  = 50  $\Omega$ , the IIP3 is plotted as a function of  $R_{sw}$  in Fig. 8(b). For >20 dBm IIP3, the design was implemented with 25  $\Omega$  resistors, with the remaining 25  $\Omega$  distributed over the switch resistance, virtual ground impedance, and routing parasitics. The bulk of the mixer switches was tied to the baseband side for reduced on-resistance and better linearity. The multiplexer switches of the VM were sized wide and low-ohmic, since parasitics are absorbed in the baseband capacitance and since they are driven by static control signals. This allows negligible increase of the virtual ground impedance.

For low IM2, a fully differential structure was adopted for both mixers with carefully balanced parasitics, and a common centroid layout scheme was used for the VM slices.

The TIAs were not specifically designed for linearity, and therefore will dominate the system IM3 performance when cancellation is deactivated. However, they perform such that under 27 dB cancellation, the mixers will dominate the IM3 performance by a large margin. In addition, the TIAs were further linearized by a differential negative conductance at their inputs [14]. While not strictly necessary for this application, it allows us to eliminate the TIA as a linearity bottleneck in measurements and study the raw linearity achieved by the mixers, even with cancellation disabled. Fig. 9 shows an implementation detail of one fully differential VM slice for one LO phase, and one of the negative-conductance-assisted TIAs. The TIAs are implemented as high-gain, two-stage OTAs with a telescopic input stage and a push–pull output stage [14].

Fig. 9. Implementation details of one VM slice for one LO phase, and the TIA linearized by negative conductance.

Fig. 10. 5 bit tuneable level shifting of the LO for tuneable input matching.

# D. LO Generation and Input Matching

The 25% duty cycle LO is generated by an on-chip divideby-two and logic operations on the four resulting phases. The final stages of LO drivers are ac-coupled to the mixer switches to allow level shifting the LO signals for reduced switch onresistance. Fig. 10 shows the level shifting circuit for two clock phases and two switches. The ac coupling capacitors are slowly charged by small switches during the intervals where the LO is low. The level shift voltage is set between 0 V and mid-supply by a 5 bit R-2R DAC, allowing digital control of input matching. This allows good input matching over process spread. Independent DACs are used for the VM and the main mixer, to overcome any differences in, e.g., layout parasitics. In measurements, the RX and VM were tuned for matching once and the resulting DAC values were used throughout.

#### **IV. MEASUREMENT RESULTS**

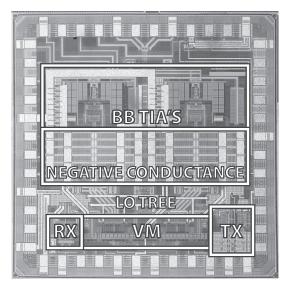

The design was implemented in 65 nm CMOS; a die photo is shown in Fig. 11. This section describes the measured performance of the prototype.

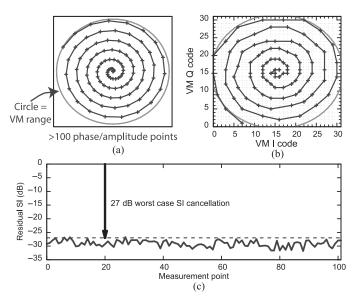

#### A. Cancellation

The cancellation performance of the circuit was evaluated using an 802.11 g-like TX signal of 52 tones with random phases in 16.25 MHz centered at 2.5 GHz. The SI channel was emulated by a commercial high-resolution VM. Over 100 arbitrarily chosen phase/amplitude points were evaluated within the cancellation range of the VM, as shown in Fig. 12(a). An iterative search algorithm based on received power minimization was used to find the VM setting for best cancellation for each

Fig. 11. Die photo with relevant blocks indicated. The 65 nm design measures  $1.4 \times 1.4$  mm.

Fig. 12. (a) Over 100 arbitrary, spiral-shaped phase/amplitude points emulate the SI channel. (b) On-chip VM finds the corresponding setting for best cancellation. (c) Residual SI is always at least 27 dB below the VM range (circle).

point, shown in Fig. 12(b). The residual SI power was measured for each point, relative to the maximum power the VM could cancel [i.e., the gray circle in Fig. 12(a) and (b)]. The results, plotted in Fig. 12(c), show better than 27 dB cancellation which is very close to the calculated 27.1 dB from Section III-A. This is expected, since despite the minimal practical sizing of the VM slices, matching was found to be much better than strictly required for the 31 slice VM.

# B. Noise

In the thermal noise limited region, an NF was measured of  $6.3 \,\mathrm{dB}$  without cancellation enabled;  $10.3 \,\mathrm{dB}$  with cancellation set for maximum SI (i.e., the VM is set to a point on the maximum circle it can cover) and  $12.3 \,\mathrm{dB}$  when set for small

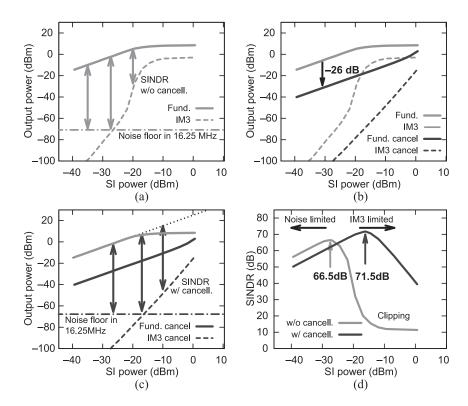

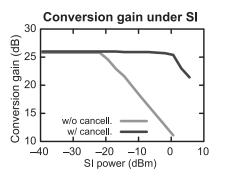

Fig. 13. Results of a two-tone linearity test. (a) Cancellation disabled, including 16.25 MHz noise floor and defining SINDR (linearity performance). (b) Cancellation enabled (linearity performance), including noise floor and SINDR. (d) SINDR with and without cancellation for various SI powers (SINDR in 16.25 MHz). Note that the performance has improved slightly with respect to [12], to reflect the most recent measurements.

SI (i.e., the VM is set to a minimum amplitude). These values correspond very well with analysis and simulation as listed in Table I. The 1/f noise corner of the RX was measured to reside at roughly 2 MHz.

### C. Linearity

For a symmetrical point-to-point link based on this design, the available link budget<sup>2</sup> will at first increase linearly with increasing transmit power (i.e., an increasing SINDR, see Section II). However, at some point, the increasing SI will induce distortion in the RX that raises the noise floor, limits digital cancellation, and thus decreases the link budget again. This also holds under cancellation, due to the finite linearity of the RX and VM mixers. In other words, there is an optimum SI power for which the system achieves the highest SINDR and thus the largest link budget. To find this optimum, a twotone self-interferer was applied and its power was swept under cancellation.

First, the IM3 products were observed. Under cancellation, an effective in-band IIP3 can be defined with respect to the SI.<sup>3</sup> The peak SINDR can then be calculated as

SINDR (dB) =

$$\frac{2}{3}$$

(Effective IIP3 (dBm)

- Noise Floor (dBm)) - 3 dB (6)

<sup>2</sup>"Link budget" in this work assumes 0 dB SNR at the receiver and does not

include any fading and AGC margins, to obtain a standard independent metric. <sup>3</sup>Effective in-band IIP3 is similar to effective out-of-band IIP3, as used in interference-cancelling FDD systems, e.g., [18].

where the 3 dB is due to the RX noise floor and SI-induced IM3 products adding as powers.

Due to the discrete nature of the VM, it is difficult to guarantee exactly 27 dB cancellation, therefore the measurement was performed under 26 dB cancellation, in order not to be optimistic. Fig. 13(a) shows the results without cancellation. Drawing a noise floor in 16.25 MHz allows deriving the SINDR. Fig. 13(b) shows how the results change under 26 dB cancellation. Again, the RX noise floor can be included to derive the SINDR [Fig. 13(c)]. Both SINDRs are shown in Fig. 13(d). Note that the performance has improved slightly with respect to [12], to reflect the most recent measurements. The peak SINDR of the system increases from 66.5 dB without cancellation, to 71.5 dB under cancellation, indicating a 5 dB increase in link budget when cancellation is enabled. The point of maximum link budget has moved from -27.6 to -16.4dBm SI at the RX input. Also, if the system operates slightly above the optimum amount of SI (e.g., the external attenuator is chosen conservatively or the TX power is slightly larger than expected), the link budget degrades smoothly, whereas the original RX would suffer from output stage clipping [Fig. 13(d)].

The measurements show that the IIP3 increases from 9 dBm to an effective 21.5 dBm when cancellation is enabled: an increase of 12.5 dB. The fact that the IIP3 does not increase by the full 27 dB indicates that the linearity bottleneck has moved from the TIA to the nonlinear RX and VM switches. Since enabling the cancellation increases the effective IIP3 by 12.5 dB but also increases the noise floor by 6 dB, (6) shows

TABLE II Summary of Cancellation, Noise, and Linearity Effects on Overall FD Link Performance, Assuming 20 dB Antenna Isolation

|                                                              | Without cancell. | With cancell. |

|--------------------------------------------------------------|------------------|---------------|

| Maximum link budget (SINDR + Isolation) (dB)                 | 86.5             | 91.5          |

| Digital cancellation requirement (SINDR - Cancellation) (dB) | 66.5             | 44.5          |

| TX power @ max. link budget (SI + Isola-<br>tion) (dBm)      | -7.6             | 3.6           |

Fig. 14. Conversion gain for desired signal with increasing SI, without and with cancellation.

why the 27 dB cancellation only yields a 5 dB link budget increase.

However, the main intention of the canceller was *not to improve link budget, but to relax TX EVM, TIA/ADC DR, and digital cancellation requirements*, and all of these are still relaxed by the full 27 dB of cancellation, minus the 5 dB link budget increase. Table II summarizes the effect of the cancellation on the link budget of the system, under the assumption of 20 dB antenna isolation. Its main merit is bringing the digital cancellation, TX EVM, and TIA/ADC DR requirements down from an unfeasible 66.5 dB to a realistic 44.5 dB.

Given the optimum TX power based on IM3, the IM2 was evaluated. Referring to Fig. 8 at 3.6 dBm TX power, 56 dBm IIP2 would be required for IM2 equal to the noise floor. Measuring the beat component of two in-band tones, +60 dBm IIP2 was measured, which is sufficient by some margin and similar to that achieved in other mixer-first designs. Note that in this mixer-first design, IM2 is dominated by the mixers and therefore is not reduced by cancellation. As such, defining an effective IIP2 is not useful. Since the design required a postproduction routing fix, a limited number of functional samples was available and the IIP2 was not characterized over multiple samples.

In Fig. 13(c), to find the SINDR, the fundamentals were extrapolated from the case without cancellation. This assumes that under cancellation, the SI does not compress the RX for the SI power range of interest. This can be validated by applying a third tone, representing the desired signal, and monitoring its conversion gain. Fig. 14 shows the result: under cancellation, the RX can handle in excess of 1.5 dBm of SI before the desired signal is compressed; at this point, the residual SI is strong enough to saturate the TIA, despite the cancellation. This is 24 dB higher SI than without cancellation and justifies the extrapolation made in Fig. 13(b) and (c).

Fig. 15. Performance of the receiver over a wide range of LO frequencies.

As mentioned in Section III-C, the TIAs can also be eliminated as linearity bottleneck by enabling the differential negative conductance present at their inputs. With the cancellation disabled, this allows us to observe the raw linearity of the main RX mixer, which results in an IIP3 of 19 dBm. The fact that the effective IIP3 under cancellation is even 2.5 dB higher, can be explained by two phenomena: 1) distortion cancellation mechanisms occurring between the RX and VM and 2) the fact that cancelled SI does not cause signal swing on the virtual grounds, whereas received signal does. Note that the measurements in Figs. 13 and 14 were performed without negative conductance.

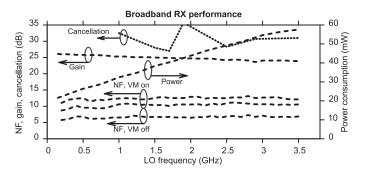

### D. Broadband Performance

Although the aforementioned results were obtained at 2.5 GHz LO frequency, the receiver employs frequency-agile operation and cancellation principles. Fig. 15 shows several performance characteristics over a broad range of LO frequencies. NF and RX gain are reasonably flat over the entire operating range from 0.15 to 3.5 GHz. Due to the discrete nature of the VM, the cancellation performance varies, as expected, but always exceeds 27 dB. Power consumption increases linearly with frequency with a static component, as expected.

### E. Transmitter

The cointegrated transmitter is discussed separately in [19]. Like the RX, it features frequency-agile operation. For a 0 dBm 802.11a output at 2.5 GHz, it achieves -40 dB EVM, which almost meets the 44.5 dB requirement at 3.6 dBm output as listed in Table II. Further improving its EVM by, e.g., predistortion is part of ongoing research.

# F. Phase Noise

PN can be troublesome for FD [2], [10]: in our design, uncorrelated PN between the RX and the VM mixer would induce a noise floor relative to the SI power before cancellation. Assuming a typical PLL with, e.g., -110 dBc/Hz PNin 10 MHz BW, its integrated in-band PN of -40 dBc would hamper digital cancellation. A shared clock for RX and VM solves this issue, but if the TX mixer remains uncorrelated, a noise floor would still appear below the SI after cancellation. Therefore, all mixers in the system share a common LO source,

|                            | [8]                                              | [11]                               | This work                             |  |

|----------------------------|--------------------------------------------------|------------------------------------|---------------------------------------|--|

|                            | Dual-port N-path filter                          | Mixer-first architecture           | Mixer-first receiver                  |  |

| Topology                   | based canceller + noise-                         | + noise-cancelling                 | + SI-cancelling VM-                   |  |

|                            | cancelling receiver                              | duplexer LNA's downmixer           |                                       |  |

| Technology                 | 65 nm CMOS                                       | 65 nm CMOS                         | 65 nm CMOS                            |  |

| Supply                     | N/R                                              | 1.2 V (LO)/2.5 V (BB)              | 1.2 V                                 |  |

| Operating freq.            | 0.8–1.4 GHz                                      | 0.1–1.5 GHz                        | 0.15–3.5 GHz                          |  |

| Max. gain                  | 42 dB                                            | 51–55 dB                           | 24 dB                                 |  |

| NF                         | 5.7-6.3 dB (4.8 in HD)                           | 5.5 dB                             | 10.3-12.3 dB (6.3 in HD)              |  |

| Power consumption          | 63–69 mW (RX) + 44 –                             | 12.56 NV (1.1.77V)                 | 22-46  mW (RX) + 1-                   |  |

|                            | 182 mW (canc.)                                   | 43-56 mW (incl. TX)                | $10 \text{ mW} (\text{canc.})^{1)}$   |  |

| Baseband BW                | >30 MHz (-15 to +15)                             | 6–192 MHz                          | 24 MHz (-12 to +12)                   |  |

| In-band IIP3               | -20 dBm                                          | -32.7 dBm                          | +9/+19 dBm (neg. con-                 |  |

|                            |                                                  |                                    | ductance OFF/ON) <sup>2)</sup>        |  |

| Effective in-band IIP3     | 2 dBm                                            | $-0.7 \text{ dBm}^{3)}$            | 21.5 dBm                              |  |

| with respect to SI         | 2 dBm                                            | -0.7 dBii                          |                                       |  |

| SINDR in 16.25 MHz         | 62.5 dB peak at -30.7                            | 60.8 dB peak at -32.6              | 71.5 dB peak at -16.4                 |  |

| BW                         | dBm SI                                           | dBm SI                             | dBm SI                                |  |

| Out-of-band IIP3           | 17 dBm                                           | 22.5 dBm                           | 22.0 dBm                              |  |

| Resolution-limited SI      | N/R                                              | N/A                                | 27 dB                                 |  |

| Cancellation               | IV/K                                             |                                    | 27 00                                 |  |

| SI power at 1dB RX         | ≫–8 dBm                                          | -17.3 dBm                          | >+1.5 dBm <sup>4)</sup>               |  |

| compression                |                                                  |                                    | · · · · · · · · · · · · · · · · · · · |  |

| In-band IIP2               | +10 dBm                                          | +7 dBm <sup>5)</sup>               | +60 dBm                               |  |

| Effective in-band IIP2     | +68 dBm                                          | +24 dBm <sup>5)</sup>              | +60 dBm                               |  |

| with respect to SI         |                                                  |                                    |                                       |  |

| 1/f Noise corner           | N/R                                              | N/A                                | 2 MHz                                 |  |

|                            | 20 dB worst-case in 25 MHz BW,                   | 33.5 dB in                         | 15.6 dB worst-case, 21 dB integrated  |  |

| Practical cancellation de- | 34 dB initial iso. from 1.4 GHz                  | $\sim 1 \text{ MHz BW}^{7}$ , with | in ~16 MHz BW, 25 dB initial          |  |

| tails                      | dipole pair, 8 ns peak group delay <sup>6)</sup> | single-port antenna                | iso. from crossed 2.5 GHz dipoles,    |  |

|                            |                                                  |                                    | 4 ns peak group delay                 |  |

| Area                       | 4.8 mm <sup>2</sup>                              | $1.5 \text{ mm}^2$                 | $2 \text{ mm}^2$                      |  |

TABLE III COMPARISON WITH OTHER INTEGRATED FD TRANSCEIVERS, ASSUMING NO ANTENNA ISOLATION

Notes: Several values of [11] and this work were updated with respect to [12] to reflect the most recent data sets.

<sup>1</sup>The transmitter adds 129 mW at 2.5 GHz, as detailed in [19].

<sup>2</sup>Negative conductance gives about 1.5 dB NF penalty [14].

<sup>3</sup>From -38.7 dBm IIP3 and 38 dB IIP3 improvement at 33.5 dB isolation.

<sup>4</sup>135 kHz spacing [11], under 27 dB cancellation.

<sup>5</sup>Estimated from [11], Fig. 31.

<sup>6</sup>Cancellation was optimized for wide bandwidth.

<sup>7</sup>From [11], Fig. 25.

resulting in PN rejection. Experiments detailed in [19] and subsequent analysis with different SI path loss models suggest sufficient PN rejection to realize the proposed 90 dB link budget with a commercially available PLL, even in very reflective environments.

# G. Image Rejection

A concern of the proposed topology is image rejection: the RX and the VM process the full SI power, but ideally, the received image of the SI should be below the noise floor. As such, about 71 dB image rejection is required from the mixers, which is not a feasible value. However, if the image rejection is over 27 dB, it does not limit analog cancellation, and the residual image can be dealt with in digital cancellation [20]. The prototype achieves 37 dB image rejection, sufficient for analog cancellation by a margin of 10 dB, but the image must be accounted for in digital to reach the full 44.5 dB digital cancellation potential.

# H. Comparison

Table III compares this work to two previously published integrated FD receivers. For fair comparison, no antenna isolation is assumed for all designs. The peak SINDR of the other works was calculated using (6). The SI power at which the peak SINDR occurs is given by

SI (dBm) = Effective IIP3 (dBm)

$$-1/3 * [Effective IIP3 (dBm) - Noise Floor (dBm)]$$

(7)

where the noise floor depends on the NF and RX BW. Although this work features the highest peak SINDR, and thus the highest link budget potential given a fixed amount of antenna isolation, it should be noted that the architecture of [8] can theoretically achieve significant cancellation over a wide bandwidth even when the initial antenna isolation is high, thanks to its ability to address delayed SI components. Although the gain of this design is relatively low due to limited range of the BB feedback network, experiments using an external  $10 \text{ k}\Omega$  feedback network resulted in 39.3 dB gain at the cost of a reduced compression level, but without compromising the peak SINDR.

#### I. Antenna Experiments

To verify the claims of 20 dB as a representative worstcase antenna isolation and -40 to  $-50 \,\mathrm{dB}$  as the level where frequency-selective components dominate the SI in 16.25 MHz BW, some experiments were performed with the transceiver, using a crossed pair of commercial WLAN dipoles as a simple FD TX/RX antenna pair. Connections were kept short to avoid introducing unnecessary propagation delay. Initial results are described in [21]. In a lab environment without special precautions, this antenna solution provides typically 25 dB isolation with 4 ns peak group delay and  $2.5 \,\mathrm{dB}$  amplitude variation. A typical measurement when combined with the proposed front-end showed 46 dB combined effect of bandintegrated isolation and cancellation (40.6 dB at the worst band edge), with the remaining SI clearly dominated by frequencyselectivity and not limited by the cancellation potential of the receiver. Given sufficient TX EVM and ADC DR as discussed, these components can be further cancelled in digital. Also, heavily influencing the antenna near-field with a hand showed that 20 dB is a reasonable worst-case isolation for this FD antenna. Further characterization of the transceiver in realworld scenarios and implementing digital cancellation is part of ongoing research.

# J. Design Improvements

Several improvements can be envisioned over this researchoriented design. First, the 50  $\Omega$ -matched VM, preceded by a fixed attenuator, injects considerable noise into the TIAs, which can be reduced by scaling the VM impedance up for similar attenuation. This also reduces the power tapped from the TX. Second, the BB feedback network can be easily modified to achieve more gain as mentioned in Section IV-H. Furthermore, the high 1/f-noise corner decreases SNR for low-offset carriers in an OFDM system but can be improved by, e.g., scaling the TIA input stages.

## V. CONCLUSION

This work presented an integrated SI cancelling receiver, aiming to bring in-band FD wireless communication to compact low-power devices. Starting from FD system considerations, we found that a phase/amplitude-based SI-canceller in the analog domain is useful to improve upon low and varying antenna isolation.

The proposed receiver takes an attenuated copy of the transmit signal, and provides simultaneous tuneable phase shift, amplitude scaling and downmixing using a VM downmixer, for SI-cancellation in the RX analog baseband. The main RX and VM are based on a highly linear switched-resistor mixerfirst architecture, to cancel SI with highly linear passive circuits, prior to amplification of the residue. This keeps SI-induced distortion low and thus maximizes the digital cancellation and link budget potentials. For the sliced VM, the cancellation performance was derived as a function of the number of slices. We also show how to analytically obtain upper and lower bounds for the settingdependent noise performance of the receiver including VM. Other design choices, such as the VM resolution, were also motivated. The SINDR of the system was defined as a crucial figure for link budget performance.

With only 20 dB isolation from the antenna, the prototype with 31 slice VM achieves up to 27 dB cancellation at 3.6 dBm TX power, without introducing distortion above the RX noise floor. Given its 12.3 dB worst-case NF with cancellation enabled, this results in up to 91.5 dB link budget in a 16.25 MHz bandwidth, enough for short-range links. Since the TX is inside the cancellation loop, and cancellation occurs before amplification, the 27 dB cancellation reduces the requirements on TX EVM, baseband amplifiers, and ADC to feasible levels. The entire system offers frequency-agile operation and cancellation from 0.15 to 3.5 GHz LO frequency.

#### REFERENCES

- A. Sabharwal, P. Schniter, D. Guo, D. Bliss, S. Rangarajan, and R. Wichman, "In-band full-duplex wireless: Challenges and opportunities," *IEEE J. Sel. Areas Commun.*, vol. 32, no. 9, pp. 1637–1652, Sep. 2014.

- [2] B. Debaillie *et al.*, "Analog/RF solutions enabling compact full-duplex radios," *IEEE J. Sel. Areas Commun.*, vol. 32, no. 9, pp. 1662–1673, Sep. 2014.

- [3] B. van Liempd et al., "RF self-interference cancellation for full-duplex," in Proc. 9th Int. Conf. Cognit. Radio Oriented Wireless Netw. Commun. (CROWNCOM), 2014, pp. 526–531.

- [4] A. Wegener, "Broadband near-field filters for simultaneous transmit and receive in a small two-dimensional array," in *Proc. IEEE MTT-S Int. Microw. Symp. (IMS)*, 2014, pp. 1–3.

- [5] T. Dinc and H. Krishnaswamy, "A T/R antenna pair with polarizationbased reconfigurable wideband self-interference cancellation for simultaneous transmit and receive," in *Proc. IEEE MTT-S Int. Microw. Symp.* (*IMS*), 2015, pp. 1–4.

- [6] B. van Liempd et al., "2.2 A +70 dBm IIP3 single-ended electricalbalance duplexer in 0.18 μm SOI CMOS," in Proc. IEEE Int. Solid-State Circuits Conf. (ISSCC), 2015, pp. 1–3.

- [7] D. Bharadia, E. McMilin, and S. Katti, "Full duplex radios," SIGCOMM Comput. Commun. Rev., vol. 43, no. 4, pp. 375–386, Aug. 2013.

- [8] J. Zhou, T.-H. Chuang, T. Dinc, and H. Krishnaswamy, "19.1 Receiver with > 20 MHz bandwidth self-interference cancellation suitable for FDD, co-existence and full-duplex applications," in *Proc. IEEE Int. Solid-State Circuits Conf. (ISSCC)*, 2015, pp. 1–3.

- [9] M. Duarte, C. Dick, and A. Sabharwal, "Experiment-driven characterization of full-duplex wireless systems," *IEEE Trans. Wireless Commun.*, vol. 11, no. 12, pp. 4296–4307, Dec. 2012.

- [10] A. Sahai, G. Patel, C. Dick, and A. Sabharwal, "On the impact of phase noise on active cancelation in wireless full-duplex," *IEEE Trans. Veh. Technol.*, vol. 62, no. 9, pp. 4494–4510, Nov. 2013.

- [11] D. Yang, H. Yuksel, and A. Molnar, "A wideband highly integrated and widely tunable transceiver for in-band full-duplex communication," *IEEE J. Solid-State Circuits*, vol. 50, no. 5, pp. 1189–1202, May 2015.

- [12] D.-J. van den Broek, E. Klumperink, and B. Nauta, "19.2 A selfinterference-cancelling receiver for in-band full-duplex wireless with low distortion under cancellation of strong TX leakage," in *Proc. IEEE Int. Solid-State Circuits Conf. (ISSCC)*, 2015, pp. 1–3.

- [13] E. Everett, A. Sahai, and A. Sabharwal, "Passive self-interference suppression for full-duplex infrastructure nodes," *IEEE Trans. Wireless Commun.*, vol. 13, no. 2, pp. 680–694, Feb. 2014.

- [14] D. Mahrof, E. Klumperink, Z. Ru, M. Oude Alink, and B. Nauta, "Cancellation of OpAmp virtual ground imperfections by a negative conductance applied to improve RF receiver linearity," *IEEE J. Solid-State Circuits*, vol. 49, no. 5, pp. 1112–1124, May 2014.

- [15] M. Soer, E. Klumperink, B. Nauta, and F. van Vliet, "3.5 A 1.0-to-2.5 GHz beamforming receiver with constant-Gm vector modulator consuming < 9 mW per antenna element in 65 nm CMOS," in *IEEE Int. Solid-State Circuits Conf. Dig. Tech. Papers (ISSCC)*, 2014, pp. 66–67.

- [16] C. Andrews and A. Molnar, "Implications of passive mixer transparency for impedance matching and noise figure in passive mixer-first receivers," *IEEE Trans. Circuits Syst. I*, vol. 57, no. 12, pp. 3092–3103, Dec. 2010.

- [17] A. Molnar and C. Andrews, "Impedance, filtering and noise in n-phase passive CMOS mixers," in *Proc. Custom Integr. Circuits Conf. (CICC)*, 2012, pp. 1–8.

- [18] J. Zhou, A. Chakrabarti, P. Kinget, and H. Krishnaswamy, "Low-noise active cancellation of transmitter leakage and transmitter noise in broadband wireless receivers for FDD/co-existence," *IEEE J. Solid-State Circuits*, vol. 49, no. 12, pp. 3046–3062, Dec. 2014.

- [19] D.-J. van den Broek, E. Klumperink, and B. Nauta, "A self-interference cancelling front-end for in-band full-duplex wireless and its phase noise performance," in *Proc. IEEE Radio Freq. Integr. Circuits Symp.*, pp. 75– 78, 2015.

- [20] D. Korpi, L. Anttila, V. Syrjala, and M. Valkama, "Widely linear digital self-interference cancellation in direct-conversion full-duplex transceiver," *IEEE J. Sel. Areas Commun.*, vol. 32, no. 9, pp. 1674–1687, Sep. 2014.

- [21] B. Debaillie *et al.*, "RF self-interference reduction techniques for compact full-duplex radios," in *Proc. IEEE Veh. Technol. Conf. (VTC)*, 2015, pp. 1–5.

**Dirk-Jan van den Broek** (S'14) was born in Roosendaal, The Netherlands, in 1986. He received the M.Sc. degree (*cum laude*) in electrical engineering from the University of Twente, Enschede, The Netherlands, in 2012. He is currently working toward the Ph.D. degree in integrated circuit design at ICD-Group, University of Twente.

**Eric A. M. Klumperink** (M'98–SM'06) was born in Lichtenvoorde, The Netherlands, in April 4, 1960. He received the B.Sc. degree in electrical engineering from HTS, Enschede, The Netherlands, in 1982.

He joined the University of Twente, Enschede, The Netherlands, in 1984, where he received the Ph.D. degree in 1997. In 1998, he was an Assistant Professor with the IC Design Laboratory, Twente, The Netherlands.

Dr. Klumperink served as an Associate Editor for the IEEE TCAS-II (2006–2007), the IEEE TCAS-I

(2008–2009), and the IEEE JSSC (2010–2014). He served as an IEEE SSC Distinguished Lecturer in 2014/2015, holds 10+ patents, authored and coauthored 150+ internationally refereed journal and conference papers, and was recognized as 20+ ISSCC paper contributor over 1954–2013. He is a member of the Technical Program Committees of the ISSCC and the IEEE RFIC Symposium. He was the corecipient of the ISSCC 2002 and the ISSCC 2009 "Van Vessem Outstanding Paper Award."

**Bram Nauta** (M'91–SM'03–F'08) was born in Hengelo, The Netherlands, in 1964. He received the M.Sc. degree (*cum laude*) in electrical engineering from the University of Twente, Enschede, The Netherlands, in 1987, and the Ph.D. degree in integrated circuit design from the University of Twente, in 1991.

In 1991, he joined the Mixed-Signal Circuits and Systems, Department of Philips Research, Eindhoven, The Netherlands. In 1998, he was a Full Professor with IC Design Group, University of

Twente. His research interests include high-speed analog CMOS circuits, software defined radio, cognitive radio, and beamforming.

Dr. Nauta served as the Editor-in-Chief (2007–2010) of the IEEE JOURNAL OF SOLID-STATE CIRCUITS (JSSC), and was the 2013 Program Chair of the International Solid State Circuits Conference (ISSCC). Also he served as an Associate Editor of the IEEE TRANSACTIONS ON CIRCUITS AND SYSTEMS II (1997–1999), and the JSSC (2001–2006). He was in the Technical Program Committee of the Symposium on VLSI Circuits (2009–2013) and is in the Steering Committee and Programme Committee of the European Solid State Circuit Conference (ESSCIRC). He is member of the ISSCC Executive Committee. He served as Distinguished Lecturer of the IEEE, and is elected member of the IEEE-SSCS ADCOM. In 2014, he was a Distinguished Professor with the University of Twente. He was the corceipient of the ISSCC 2002 and the 2009 "Van Vessem Outstanding Paper Award," and in 2014 he was the recipient of the 'Simon Stevin Meester' Award (500.000 Euro), the largest Dutch National Prize for achievements in technical sciences.