# High-Linearity Bottom-Plate Mixing Technique With Switch Sharing for *N*-path Filters/Mixers

Yuan-Ching Lien<sup>®</sup>, *Student Member, IEEE*, Eric A. M. Klumperink<sup>®</sup>, *Senior Member, IEEE*, Bernard Tenbroek, Jon Strange, *Senior Member, IEEE*, and Bram Nauta<sup>®</sup>, *Fellow, IEEE*

Abstract-A four-path filter/mixer for surface acoustic wave (SAW)-less frequency division duplex (FDD) radio receivers is proposed, targeting high linearity and compression requirements. A bottom-plate mixing technique improves linearity by reducing the gate-source voltage modulation of the MOSFET switches. Differential bottom-plate mixing allows for switch sharing which halves the effective switch resistance to reduce drain-source voltage modulation. The first four-path switch-RC filter stage with bottom-plate mixing and a shared switch renders 2nd-order voltage-domain RF-bandpass filtering around the LO frequency. Extra out-of-band rejection is implemented combined with V-I conversion and zero-IF frequency down-conversion in the second cross-coupled switch-RC four-path stage, which offers a low-ohmic high-linearity current path for out-of-band interferers. A prototype chip fabricated in a 28-nm CMOS technology achieves an out-of-band IIP3 of +44 dBm, IIP2 of +90 dBm and blocker 1-dB gain-compression point of +13 dBm for a blocker frequency offset of 80 MHz. At this offset frequency, the measured desensitization is only 0.6 dB for a 0-dBm blocker, and 3.5 dB for a 10-dBm blocker at 0.7-GHz LO (i.e., 6- and 9-dB blocker noise figure). The chip consumes 38-96 mW for LO-frequencies of  $0.1-\overline{2}$  GHz and occupies an active area of 0.49 mm<sup>2</sup>.

*Index Terms*—Bandpass, blocker rejection, CMOS, compression point, filter, frequency division duplex (FDD), high linearity, IIP2, IIP3, interference robustness, mixer-first receiver, *N*-path filter, notch, passive mixer, surface acoustic wave (SAW) less, tunable.

## I. INTRODUCTION

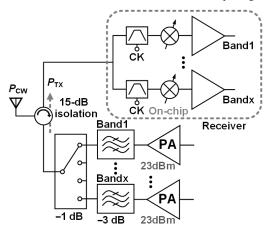

**L** TE-ADVANCED wireless receivers require high-linearity up-front filtering to prevent corruption of the in-band signals by strong out-of-band (OOB) signals and selfinterference from the transmitter in case of frequency division duplex (FDD). Surface acoustic wave (SAW)-duplexer-filters are generally used for this purpose (see Fig. 1), but supporting the plethora of existing and new bands becomes troublesome with separate filters for each band. Wideband circulators can provide about 10–15-dB isolation from TX to RX. In this paper, we explore the possibility of combining an off-chip

Manuscript received February 13, 2018; revised July 18, 2018 and October 14, 2018; accepted October 16, 2018. Date of publication November 16, 2018; date of current version January 25, 2019. This paper was approved by Associate Editor Alyosha Molnar. This work was supported by MediaTek Inc. (*Corresponding author: Yuan-Ching Lien.*)

Y.-C. Lien is with the University of Twente, 7500 AE Enschede, The Netherlands, and also with Mediatek, Kent ME19 4AD, U.K. (e-mail: y.lien@utwente.nl).

E. A. M. Klumperink and B. Nauta are with the University of Twente, 7500 AE Enschede, The Netherlands.

B. Tenbroek and J. Strange are with Mediatek, Kent ME19 4AD, U.K. Color versions of one or more of the figures in this paper are available

online at http://ieeexplore.ieee.org. Digital Object Identifier 10.1109/JSSC.2018.2878812

PA Band1 Band1

Fig. 1. Conventional LTE receiver with external SAW duplexing filters.

Fig. 2. Proposed LTE receiver with on-chip reconfigurable N-Path BPF.

circulator with high-linearity on-chip N-path filtering and mixing. As an N-path bandpass filter (BPF) has a programmable RF-center frequency, one circulator and a programmable chip can replace a set of SAW filters, as shown in Fig. 2. However, even with 15-dB isolation from the circulator, the on-chip filter needs to deal with up to +4 dBm TX leakage  $P_{TX}$ (see Fig. 2), with a 15-dBm OOB continuous-wave (CW) blocker  $P_{cw}$  also present. Intermodulation  $P_{IIM3}$  will in this case deteriorate the RX sensitivity. For LTE applications, the integrated thermal noise is 101 dBm for a 20-MHz channel BW. If we assume  $P_{\text{IIM3}}$  is roughly the same as 101 dBm, the resulting required IIP3 is about 45-50 dBm, which is an extremely tough requirement. Inductor-less tunable N-path filters [1], [2] and mixer-first receivers in [3]-[6] achieved > +10 dBm compression point and an IIP3 of 20–30 dBm, i.e., about 20 dB worse than required. Moreover, improved filtering is desired. A 2nd-order BPF is obtained with a simple switch-RC N-path filter and this high-linearity passive filtering

0018-9200 © 2018 IEEE. Personal use is permitted, but republication/redistribution requires IEEE permission. See http://www.ieee.org/publications\_standards/publications/rights/index.html for more information.

Fig. 3. (a) Conventional 4th-order BPF realization by cascading a series LC tank. (b) Proposed 4th-order BPF using V-I conversion and current subtraction.

relaxes the linearity requirement of the subsequent active amplifiers, which are much less linear. To sufficiently relax amplifier linearity, while dealing with strong blockers and TX leakage that is close to the desired RX frequency, more than 2nd-order filter roll-off may be required. Higher order N-path filtering can be realized by incorporating  $g_m$  cells [2], [7], but the active  $g_m$  circuits limit the achievable linearity. In this paper, we increase filter roll-off by cascading an N-path voltage in-voltage out (V-V) and voltage in-current out (V-I)BPF, while a bottom-plate mixing technique with switch sharing is proposed to enhance the linearity [8]. Compared to [8], this paper explains the concept in more depth, analyzes the filter transfer, noise figure and linearity, and adds simulation results and linearity benchmarks. Note that we do not target to deliver a solution ready for LTE advanced; rather, we aim for flexibility in combination with high linearity and propose a new technique that pushes flexibility and linearity. This paper is organized as follows. Section II introduces the RF BPF receiver architecture, while section III describes the receiver circuit implementation. Section IV proposes an LTI RLC model, to roughly estimate transfer function. We will propose a semi-empirical model that will be validated by measurements. Section V provides the measurement results, and the conclusion is presented in Section VI.

#### **II. RECEIVER ARCHITECTURE**

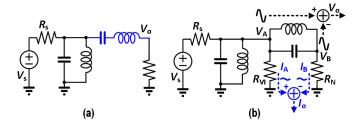

We will now describe how we conceived the RX architecture. An N-path filter can emulate a parallel LC tank, modeled by a parallel R, L, and C [1], and perform BPF. A 4th-order BPF response could be obtained by adding a series LC tank [see Fig. 3(a) in the case of ideal LC tanks]. A series LC tank can be synthesized from a parallel LC tank via gyrator circuits [2], but these circuits limit achievable linearity. A quarter-wavelength transmission line could also be exploited [9], but this limits tuning range (0.6–0.85 GHz) while the achieved IIP3 was not sufficient (18 dBm). Fig. 3(b) shows an alternative 4th-order BPF realization by using two parallel LC tanks. As the tanks become high-ohmic in-band and low-ohmic OOB, the 1st tank attenuates OOB voltage swing bypassing OOB current, while the 2nd LC bypasses OOB current to the termination resistance  $R_N$ . If we take the output voltage across the 2nd tank, i.e.,  $V_0 = V_A - V_B$  as in Fig. 3(b), the OOB signals become largely common mode and are attenuated. Nevertheless, a high-linearity differential amplifier that can handle large common-mode voltage swings

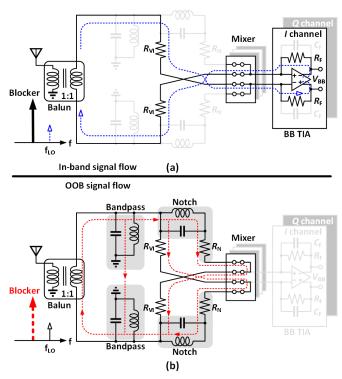

Fig. 4. (a) In-band and (b) OOB signal flow in the proposed receiver.

due to blockers is hard to implement. Instead, we propose V-I conversion by high-linearity passive resistors  $R_{VI}$  and  $R_N$  combined with current subtraction (see Fig. 3(b), output  $I_0$ ). Current subtraction will be implemented by simple wire cross-coupling in the differential implementation.

Note that the BPF in Fig. 3(b) has an extra V-I conversion resistor that degrades filter-Q compared to Fig. 3(a) (i.e., Assuming  $R_s = R_{VI}$  for matching,  $R_s = R_{VI}$  simply halves the resistance seen by the input and hence halves Q). Although not optimal for filter selectivity, this does allow for a highlinearity implementation and this is our key target here.

Fig. 4 shows the conceptual diagram of the proposed blocker rejection receiver. The parallel LC tanks are emulated by *N*-path filters. The differential structure offers the possibility of high-linearity current subtraction by wire-crossing. Input voltage signals are converted to current by resistor  $R_{\rm VI}$ , which also allows for RF-impedance matching, and this current is down-converted by the mixer switches. For in-band signals, the LC tanks are high ohmic, and the baseband (BB) current is converted to BB voltage  $V_{BB}$  by the transimpedance amplifiers (TIAs), as shown in Fig. 4(a). For OOB signals, the LC tanks become low ohmic and bypass the current as shown in Fig. 4(b). OOB signals are first attenuated by a voltage BPF and then converted to current by resistors  $R_{\rm VI}$ . The 2nd tank acts now as notch filter, blocking in-band signals [Fig. 4(a)], but passing OOB blockers [Fig. 4(b)] which are converted to current by  $R_N$ . Due to the differential symmetry and low switch resistance, OOB blocker current will mainly circulate in the RF domain [see Fig. 4(b)], ideally without entering the BB TIA. In summary, the 1st stage gives RF blocker voltage reduction and the 2nd stage V-I

Fig. 5. Switched RC mixer with (a) top-plate and (b) bottom-plate mixing.

conversion with RF blocker current bypassing to improve selectivity.

#### **III. CIRCUIT IMPLEMENTATION**

#### A. Non-Linearity Considerations

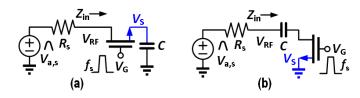

*N*-path filters and mixer-first receivers are switch-*RC* circuits that exploit the low-noise "mixer-region" [10], [11] or "passive mixer mode" [12], where the *RC* time constant is much larger than the on-time of the switch. In conventional (top-plate switched) mixers as shown in Fig. 5(a), the MOS switch suffers from largely varying  $V_{\text{GS}}$  and  $V_{\text{DS}}$ , which modulates MOSFET channel resistance and limits linearity. To obtain some intuitive insight in the non-linearity mechanism, we will qualitatively describe the variations in channel resistance assuming the gate-voltage is switched on to a constant value (e.g., = VDD).

For simplicity, suppose the RF-voltage is a sinewave at frequency  $f_{\rm RF}$  in its positive signal-half with amplitude  $V_{\rm RF}$ and average = 0 (dc value = 0), so that the RF side of the MOSFET is the drain terminal. We choose  $\rho = R_{sw}/R_s \ll 1$ (e.g.,  $\rho = 0.1$ ) to achieve high OOB linearity. For in-band signals  $Z_{in}$  is significantly higher than source resistance  $R_s$  (e.g.,  $4.3R_s$  for a four-path mixer with 25% duty-cycle clocks [13]). As the switch resistance is assumed to be much smaller than  $R_s$  (e.g.,  $\rho = 0.1$ ), the BB-voltage  $\hat{V}_S$  will almost reach  $\hat{V}_{RF} = \hat{V}_{a,s} Z_{\rm in}/(R_s + Z_{\rm in})$  where  $\hat{V}_{a,s}$  is the amplitude of the antenna signal. As a result,  $V_{GS}$  of the mixer switch is strongly modulated while the switch is closed, whereas the modulation of  $V_{\text{DS}}$  is much smaller and the non-linearity is mainly due to V<sub>GS</sub> modulation. For OOB signals, Z<sub>in</sub> decreases with offset frequency, reducing the  $V_{GS}$  modulation, while the  $V_{\rm DS}$  modulation becomes slightly higher due to the increasing current. The distortion overall reduces due to the OOB filtering at  $V_S$ . When OOB signals are very far away from the LO frequency, the BB-voltage  $\hat{V}_S$  becomes almost zero resulting in negligible  $V_{\text{GS}}$  modulation. Assuming  $\hat{V}_{\text{DS}} \approx \rho \hat{V}_{a,s}$ , OOB IIP3 can then be estimated as [14]

$$V_{\text{IIP3}} = \sqrt{\frac{4}{3} \frac{(1+\rho)^4}{\rho^3 (2g_2^2 - g_3(1+\rho))}} \tag{1}$$

where  $g_2$  and  $g_3$  are related to the 2nd and 3rd derivation of  $I_D(V_{\text{DS}})$ , which can be estimated as  $g_2$  is  $(2V_{\text{OD}})^{-1}$  and  $g_3 = -(2V_{\text{SAT}}^2)^{-1}$ , where  $V_{\text{OD}}$  is overdrive voltage  $V_{\text{GS}} - V_{\text{th}}$ and  $V_{\text{SAT}}$  is a velocity saturation parameter, respectively [14].

## B. High-Linearity Bottom-Plate Mixing Technique

We will now introduce the bottom-plate mixing technique. Instead of using a switch between the RF node and the "top

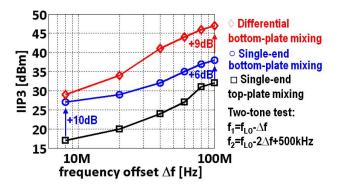

Fig. 6. Simulated IIP3 for four-path single-ended top-plate, single-ended bottom-plate, and differential bottom-plate mixing filters.

plate" of a grounded capacitor [Fig. 5(a)], we propose to connect the RF node to the top plate and instead switch the bottom-plate to ground as shown in Fig. 5(b). Although the name may suggest a relation with bottom-plate sampling, it is clearly different as it does not use two switches, while it also does not produce a sampled time-discrete output, but rather a continuous mixer output (for a further discussion of the difference between mixing and sampling, see also [15]). The main target for bottom-plate mixing is switch-resistance induced distortion improvement. In contrast, the deployment of bottom-plate sampling is for reducing the signal dependent charge injection and clock feedthrough.

For LTE applications, the duplex frequency is <200 MHz for most of the frequency bands, while a BPF with channel BW up to 10 or 20 MHz is required. Hence not only far-OOB IIP3 matters, but also the non-linearity for OOB signals that are still rather close to the LO-frequency. To reduce the  $V_{GS}$ modulation and improve linearity, we proposed a bottom-plate mixing technique [8] as shown in Fig. 5(b). When the switch is turned on, the drain terminal voltage  $V_D$  of the NMOS switch will be pulled to ground, instead of being connected to a variable voltage  $V_S$  as in Fig. 5(a). Now  $V_{GS}$  is kept constant, i.e., the in-band  $V_{GS}$  modulation problem is avoided. In-band voltage signals are down-converted and mixed to capacitor C, while the signal source still sees a high impedance, i.e., very small  $V_{\rm DS}$  modulation occurs. In conclusion, the bottom-plate mixing keeps  $V_{GS}$  constant to obtain better linearity.

Applying 1-GHz 25% duty cycle four-phase clocks with rising/falling time of 10 ps and common-mode voltage of half supply, simulations reported in Fig. 6 indeed confirm benefits. (We will discuss them in more detail below.) We tried to quantify the benefits analytically, but unfortunately accurate MOSFET models are complex. Experiments also indicate that several effects can play a role, e.g., subthreshold conduction, body effect, and charge injection. Splitting and quantifying these factors proved complicated, and hence we resort to simulations combined with qualitative reasoning and rough calculations. Bottom-plate mixing proofs to have clear linearity benefits, and reasoning supports this: apart from avoiding  $V_{\rm GS}$  modulation, source-bulk voltage modulation is also avoided in Fig. 5(b), reducing threshold voltage variation due to the body effect. Moreover, as in bottom-plate mixing

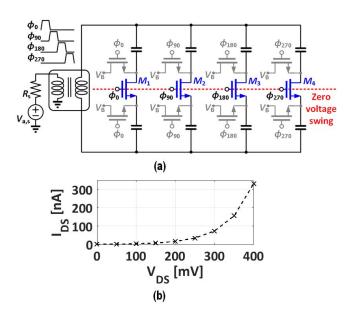

Fig. 7. (a) Circuit schematic of a four-phase differential bottom-plate mixing bandpass *N*-path filter.  $W/L = 180 \ \mu \text{m}/30 \text{ nm}$  for  $M_1-M_4$  and  $W/L = 18 \ \mu \text{m}/30 \text{ nm}$  for other NMOS transistors, (b) simulated non-linear sub-threshold current  $I_{\text{DS}}$  of  $M_1$  when it is off.

circuits, signal dependent charge injection from MOS switches is reduced as there is a low-ohmic path to ground.

Fig. 7(a) shows the circuit schematic of a four-phase differential bottom-plate mixing N-path filter.  $M_1-M_4$  are NMOS switches with large W/L ratio for the N-path filter function, while the other NMOS switches are chosen  $10 \times$  smaller to periodically reset the dc bias to the common-mode level. Larger switch size for the dc bias setting can offer faster settling (i.e., less clock cycles) to the desired common-mode level, but more LO power is required. Note that one shared NMOS switches to ground in the conventional pseudo differential architecture of Fig. 5(b). Therefore,  $\rho$  is reduced to half of its single ended value thanks to switch sharing in the differential circuit. For  $\rho \ll 1$ , (1) can approximate to

$$V_{\text{IIP3}} \approx \sqrt{\frac{4}{3}} \frac{1}{\rho^3 (2g_2^2 - g_3)}.$$

(2)

Note that (2) predicts OOB IIP3 is improved by 9 dB if  $\rho$  is halved. Fig. 6 shows the simulated IIP3 for a single-ended topplate, single-ended bottom-plate and differential bottom-plate mixing N-path filter, driven by four-phase clocks and switch size of 180  $\mu$ m/30 nm. The BPF BW  $f_{-3dB,BPF}$  is 30 MHz and  $f_{LO}$  is 1 GHz. TSMC 28-nm technology simulation with a PSP MOS-model was used. Comparing to the conventional topology, bottom-plate mixing improves IIP3 by 10 dB and 6 dB for in-band and OOB, respectively. As the blocker offset frequency  $\Delta f$  becomes very large, the  $\hat{V}_S$  of single-ended topplate mixing will almost reach zero and nearly constant  $V_{GS}$ is obtained. Therefore, the single-ended top-plate and bottomplate mixing will achieve similar IIP3 (i.e., the difference of IIP3 is less than 1 dB by simulation). Note that the switch sharing in the differential bottom-plate mixing offers an additional 9-dB OOB IIP3 improvement, as predicted by (2).

An experiment was devised to find out whether weak inversion conduction in  $M_1-M_4$  limits in-band linearity for the mixer in Fig. 7(a). Ideal switches were added in series to both sides of  $M_1-M_4$ , to block current during their off-state. This improves linearity, indicating that subthreshold current likely limits the achievable linearity. As shown in Fig. 7(a),  $Z_{in}$  is high ohmic for in-band signals, resulting in significant input signal swing which is ac-coupled via the N-path filter capacitors to the drain or source terminals of the transistors that are supposed to be off, but apparently modulate their current. Fig. 7(b) shows the simulated  $I_{DS}$  of  $M_1$  in Fig. 7(a) as a function of  $V_{DS}$  (common mode of  $V_D$  and  $V_S$  is 0.2 V) when  $M_1$  is off (gate terminal is connected to the ground). The un-constant slope indicates the sub-threshold current is non-linear.

In summary, the in-band IIP3 of conventional top-plate mixers is dominated by  $V_{GS}$  modulation, while far-OOB IIP3 is limited mainly by  $V_{DS}$  modulation. Bottom-plate mixing keeps  $V_{GS}$  constant to achieve high linearity for all frequencies. Moreover, OOB linearity is improved by 9 dB due to switch sharing. Subthreshold current likely limits the achievable in-band IIP3.

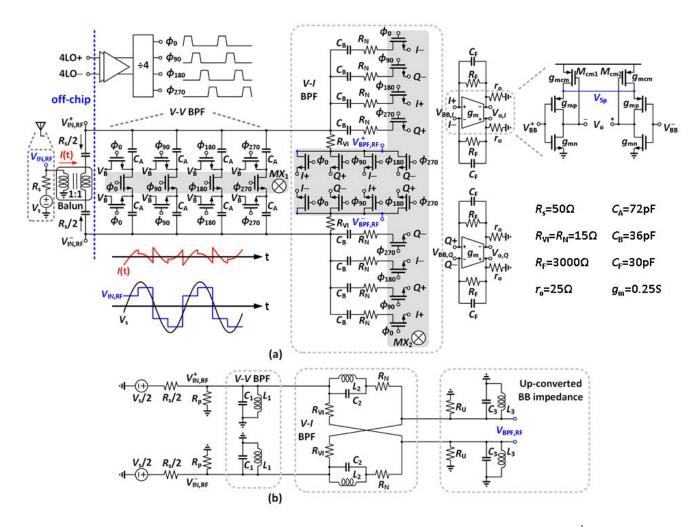

# C. Cascading Passive RF BPF Stages

The circuit schematic of the entire proposed receiver is shown in Fig. 8(a).  $C_A$  and the corresponding switches implement the bandpass in Fig. 4(b).  $C_B$ ,  $R_{VI}$ ,  $R_N$ , and the corresponding switches implement the OOB current subtraction circuit in Fig. 4(b). Because the proposed receiver is self-biased, two external RF dc blockers with low loss (<0.5 dB up to 8 GHz) are applied. A differential external clock with 4 times the LO frequency  $f_{LO}$  is applied to generate 4-phase 25% duty-cycle clocks via a divide-by-4 ring counter. By exploiting only one clock-edge, the pulse width of 25% duty-cycle clocks is determined by the period and not sensitive to the duty-cycle of the external clock. As a result, the timing error can be smaller than for a divide-by-2 flip-flop with extra logic circuits to realize 25% duty cycle. Note that most power is consumed in the output buffers that drive large mixer switches (not in divider itself), so that the power penalty of using a divide-by-4 compared to a divided-by-2 four-phase clock generator is not so significant. Both N-path filter stages are driven by the same clocks and hence have the same center frequency. Zero-IF frequency conversion is also implemented in the second V-I stage. The common-mode bias-voltage  $V_B$ for the mixer switches in the first V-V BPF is set to  $\approx 0.2$  V. There is a tradeoff regarding the choice of  $V_B$ . Lower  $V_B$ reduces on-resistance of switches, but increases subthreshold current when switches are off. The W/L of all mixer switches is 180  $\mu$ m/30 nm and the differential on-resistance is as low as  $\approx 2 \Omega$  when the bulk is connected to ground. The resistance of  $R_{\rm VI}$  and  $R_N$  for V-I conversion is 15  $\Omega$ , which is implemented in top metal with high-current density tolerance, low parasitic capacitance, and very high linearity.  $R_{\rm VI}$  and  $R_N$  also reduce the voltage swing across mixer switches to improve the linearity. Mismatch between  $R_{VI}$  and  $R_N$  causes intermodulation tones at  $f_{LO} + f_b$  and  $f_{LO} - f_b$ , where  $f_b$  is blocker frequency. These intermodulation tones will be down-

Fig. 8. (a) Circuit schematic of the proposed receiver and (b) corresponding RLC model (equivalent LTI model for the RF part)<sup>1</sup>.

converted to a BB frequency of  $f_b$ , which is not in-band, and hence not of primary importance.

Much like the BPF, a conventional top-plate switch notch N-path filter [16] also suffers from strong  $V_{GS}$  modulation that causes non-linearity. The bottom-plate mixing technique can also be applied in the notch filter that is composed of  $C_B$ ,  $R_N$ , and the corresponding mixer switches in Fig. 8(a) to gain similar benefits. The  $4 \times R_N$  are used instead of one (in Fig. 4) and the switch to ground to reduce  $V_{GS}$  modulation is possible now. Also, the down-converted BB output current signals are available for OOB blocker bypassing. Switch sharing between circuit halves seems not possible.

In this receiver, the down-converted BB signal is used as output, so that the OOB rejection limitation due to switch resistance in a bandpass *N*-path filter [1] is avoided.

The second V-I BPF stage in Fig. 8(a), composed of  $R_{VI}$ and a notch *N*-path filter, enhances the selectivity, but the OOB impedance at the V-I BPF input is  $(R_{VI} + R_{sw})||(R_N + R_{sw})$ while it is  $R_{sw}$  in a conventional V-V *N*-path filter [1]. For mixer switches in the V-I BPF that are off, still a large OOB voltage signal is directly coupled to the MOSFETswitch via capacitor  $C_B$ , again potentially resulting in non-

<sup>1</sup>One single set of mixer switches  $MX_2$  is now implementing  $L_2C_2$  and also  $L_3C_3$ .

linear subthreshold current limiting IIP3. Fortunately, the first stage V-V BPF already greatly reduces the OOB voltage signal swing, alleviating this problem.

For implementing more number of paths, a more elaborate BB I/Q re-combination circuit is required, e.g., the eight-path receiver by [13].

# D. Baseband Amplifier

A CMOS inverter is one of the best transconductors in terms of dynamic range per power [17], and it can serve to make a low-noise quite-linear BB TIA. Stability concerns for closed-loop operation are avoided in a single-stage amplifier. Because it is pseudo differential, extra circuitry is needed to reduce the common mode gain, while maximizing differential mode gain, which often leads to extra power consumption and noise [18], [19]. We avoid this by implementing a low common-mode output impedance using  $M_{cm1}$  and  $M_{cm2}$ which are put above the core  $g_{mn}$  and  $g_{mp}$  devices for current re-use, as shown in the right-top corner of Fig. 8(a). Feedback resistor  $R_F$  provides self-biasing. Each BB amplifier consumes about 15 mW from a 1-V supply. The W/L values are 1700 and 1200  $\mu$ m/40 nm for the PMOS and NMOS of the inverter, respectively, while  $g_{mn} + g_{mp} = 250 \text{ mS}$ and  $r_{\rm on}||r_{\rm op}| = 25 \ \Omega$ . By using a higher threshold voltage

328

for  $M_{cm1}$  and  $M_{cm2}$  and small overdrive voltage of about 60 mV for the PMOS of the inverter, all transistors can operate in saturation.  $M_{cm1}$  and  $M_{cm2}$  only generate common mode noise, which will be cancelled at the differential output. Operating  $M_{cm1}$  and  $M_{cm2}$  in saturation also provides isolation between the supply voltage and the outputs of the amplifier, which is good for supply noise rejection. For differential input signals, voltage  $V_{Sp}$  ideally shows very low impedance and small voltage swing due to differential symmetry and a gain of  $\approx (g_{mn} + g_{mp})(r_{on}||r_{op}) = 16 \text{ dB}$ is achieved. For a common mode input signal,  $V_{Sp}$  follows input signal and  $g_{mp}$  is degenerated. The BB amplifier output is diode-connected with output impedance of  $1/g_{mcm}$  giving a low common-mode gain of  $g_{\rm mp}/g_{\rm mcm} \approx 3$  dB. Note that a traditional CM-feedback circuit with triode devices would lead to much smaller  $g_{mcm}$ , i.e., more common-mode gain.

## IV. CIRCUIT ANALYSIS

In this section, we will analyze different properties of the mixer-first receiver, like transfer function, noise and input impedance.

The equivalent RLC circuit in Fig. 8(b) models the frequency response of the multiple-stage *N*-path filter in magnitude. The intuition behind this semi-empirical model comes from the observation that the capacitors  $C_A$  in the first capacitor bank are not directly in parallel to the capacitors  $C_B$  in the second bank, but are coupled via resistor  $R_N$ , introducing an extra filter order.

# A. RLC BPF Model

The filter shape of an *N*-path filter around its LO-frequency can be modeled by a parallel RLC circuit [1], [16]. The corresponding model parameter can be found as [16]

$$R_{\rm p} = \frac{N^2 \sin^2(\frac{\pi}{N})}{\pi^2 - N^2 \sin^2(\frac{\pi}{N})} (R_{\rm s} + R_{\rm L})$$

(3)

$$C_p = \frac{\pi^2}{mN\sin^2(\pi/N)}C\tag{4}$$

$$L_p = \frac{1}{(2\pi f_{\rm LO})^2 C_p}$$

(5)

where m = 2 for single-ended circuit and m = 8 for differential case. N is the number of clock-phases. Note that the *LC* tank modeled the *N*-path filter only in its magnitude but not in its phase as noted in [12, eq. (43)].

Assume that mixer switches in Fig. 8(a) are ideal. The RLC equivalent circuit for the RF part of the proposed receiver is shown in Fig. 8(b). The V-V BPF is modeled by the  $L_1C_1$  tank while the V-I BPF is modeled by  $R_{VI}$ ,  $R_N$ , and the  $L_2C_2$  tank. The Miller approximation is applied to the BB amplifier, resulting in capacitor  $(1 + A)C_F$ , where  $A = g_m(r_o || R_F)$  is the gain of the BB amplifier. The effect of switching before this Miller capacitor is modeled with the  $L_3C_3$  tank, which offers extra OOB rejection. In contrast to a single balanced mixer, we use a balun-driven double-balanced mixer. Now each of the BB components is connected twice per period to the RF source, doubling the conduction time, compared to the single-end case. Therefore, the BB

resistance  $R_{\rm BB} \approx R_F/(1+A)$  is up-converted and becomes  $R_{\rm U} = 2\gamma R_{\rm BB}$ , where  $\gamma = 2/\pi^2$  for 4-path case [13]. Note that  $C_p$  and  $L_p$  in (4) and (5) only depend on the number of phases, the BB capacitance in a single path and the LO frequency. The mixer switches up-convert the BB low-pass impedance to an RF bandpass impedance. To be more precise, the switched-RC passive mixer in Fig. 8(a) performs frequency conversion and mixing. For a narrowband in-band signal close to the LO frequency, the capacitors contain a (quasi-) constant BB voltage. Hence a sinewave RF-excitation results in a staircase waveform response at  $V_{\text{IN,RF}}$  [1], as shown in the lower left corner of Fig. 8(a). The voltage difference between the sine and stair-case renders a "spiky" current with harmonic content [Fig. 8(a)], which is dissipated in signal-source-resistance  $0.5R_s$ . This dissipation can be modeled as an "harmonic shunt impedance"  $R_p \approx 4.3(0.5R_s)$  for the four-phase case [13]. Note that the capacitance of  $C_A$  does not affect this in-band  $R_p$ . Moreover, as  $C_B$  contains almost the same voltage as  $C_A$ , there is hardly any difference in the voltage across  $0.5R_s$ with or without  $C_B$ . Hence, only one  $R_p$  suffices to model the in-band loss of both the switched  $C_A$  and  $C_B$  in this receiver. Using the RLC model for the RX shown in Fig. 8(b) and solving the node equations at V<sub>IN,RF</sub> and V<sub>BPF,RF</sub>, we derived  $H_{o,RF}(s) = V_{BPF,RF}(s)/(V_s/2)$  as

$H_{0,RF}(s)$

$$=\frac{2R_{\rm p}(0.5R_{\rm s}+R_{\rm p})^{-1}(C_{\rm 1}C_{\rm 2}C_{\rm 3}R^{2}R_{\rm A})^{-1}s^{3}}{s^{6}+D_{\rm x}s^{5}+D_{\rm y}s^{4}+D_{\rm z}s^{3}+D_{\rm y}\omega_{\rm LO}^{2}s^{2}+D_{\rm x}\omega_{\rm LO}^{4}s+\omega_{\rm LO}^{6}}$$

(6)

$$D_{x} = \frac{2}{C_{1}R} + \frac{1}{C_{2}R} + \frac{2}{C_{3}R} + \frac{1}{C_{3}R_{U}} + \frac{1}{C_{1}R_{A}}$$

$$D_{y} = 3\omega_{LO}^{2} + \frac{L_{2}L_{3}(R + R_{U})}{\omega_{LO}^{-4}R^{2}R_{U}} + \frac{L_{1}L_{2}(R + R_{A})}{\omega_{LO}^{-4}R^{2}R_{A}} + \frac{L_{1}L_{3}(R + 2R_{U})(R + 2R_{A})}{\omega_{LO}^{-4}R^{2}R_{U}R_{A}}$$

$$D_{z} = \frac{2(L_{2}R_{U} + L_{3}(R + 2R_{U}))}{\omega_{LO}^{-4}RR_{U}} + \frac{L_{1}L_{2}L_{3}(R + R_{U} + R_{A})}{\omega_{LO}^{-6}R^{2}R_{U}R_{A}} + \frac{2L_{1}(R + 2R_{A})}{\omega_{LO}^{-4}RR_{A}}$$

where  $\omega_{\text{LO}}^{-2} = L_1 C_1 = L_2 C_2 = L_3 C_3$ ,  $R_A = (0.5 R_s) || R_p$  and  $R = R_{\text{VI}} = R_N$ . Assuming the  $R_s$  is given,  $R_{\text{VI}}$  and  $R_F$  are designed to provide in-band matching to it. Channel Bandwidth tuning can be realized by simultaneously changing all the capacitors with the same ratio. Substituting the component values [see Fig. 8(a), top right corner] in (4)–(6), and obtaining the corresponding RLC values, we can find the poles are located at  $j\omega_{\text{LO}} \pm 2\pi$  (5M) rad/s,  $j\omega_{\text{LO}} \pm 2\pi$  (58M) rad/s and  $j\omega_{\text{LO}} \pm 2\pi$  (120M) rad/s. Assuming  $R_F C_F \gg \omega_{\text{LO}}^{-1}$ , V<sub>BB</sub> at the BB amplifier input is a down-converted version of  $V_{\text{BFF,RF}}$ , and the voltage gain from  $V_{\text{RF}}$  to  $V_{\text{BB}}$  can be derived by dividing [13, eq. (4)] by[13, eq. (6)], resulting  $1/\sqrt{4\gamma}$  (= 0.9 dB) where  $\gamma$  is  $2/\pi^2$  for four-phase case. Hence, the gain of this

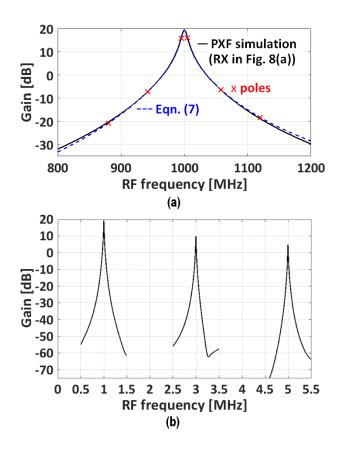

Fig. 9. (a) PXF simulation (sideband: -1, LO = 1 GHz) of the proposed receiver with ideal components and the calculated gain  $|V_0/V_s/2|$  in (7). (b) Broadband filter response up to 5th harmonic (sideband: -1, -2, -3, LO = 1 GHz).

receiver can be written as

$$\left|\frac{V_{\rm o}}{V_{\rm s}/2}\right| \approx |H_{\rm o,RF}(s)(\sqrt{4\gamma})^{-1}g_{\rm m}(r_{\rm o}||R_{\rm F})|.$$

(7)

To verify analysis, Fig. 9(a) shows a Spectre PSS/PXF simulation result for the receiver circuit in Fig. 8(a) and the estimate of the receiver gain of (7). As  $f_{\text{RX}} - f_{\text{TX}} < 200$  MHz for most LTE frequency bands, we focus on  $f_{\text{LO}} \pm 200$  MHz, and the fit is satisfactory.

Fig. 9(b) shows the filter response up to the 5th harmonics and the 1st-order roll-off in magnitude can be observed. The 2nd-order harmonic response is rejected due to differential architecture, while odd harmonic rejection is not implemented in this RX design, as in many other four-path I-Q receivers. In principle harmonic rejection can be achieved, as shown for instance in the eight-path receiver in [13].

## B. OOB Rejection of the Receiver

In the proposed receiver, the first V-V N-path BPF attenuates blockers but the OOB rejection is limited by the resistance of the mixer switches [1]. Instead of using capacitors to ground, the feedback capacitor across the BB amplifier is used to save area and provide higher feedback factor for better OOB linearity [20]. Here, the OOB rejection is ultimately limited due to the finite transconductance  $g_m$  of the BB amplifier. Thanks to the differential circuit symmetry, the BB output nodes I+, Q+, I-,

and Q- of the second V-I BPF stage show very low voltage swing, resulting in effective OOB-current by passing [see Fig. 8(a)].

#### C. Noise Performance

The noise factor F of the receiver can be calculated as the total output noise divided by the noise contribution due to the thermal noise from the antenna or signal source, modeled as  $\overline{v_{n,s}^2} = 4 \text{ kTR}_s$ . All the mixer switches are equal in Fig. 8(a).The resulting F of this RX can be derived as

$$F = 1 + \frac{(R_{\rm VI} + R_{sw})}{R_s} + \frac{(R_{\rm VI} + R_s + R_{sw})}{4.3R_s} + \frac{(R_{\rm VI} + R_s + R_{sw})^2}{\gamma (2R_F)R_s} + \frac{\overline{v_{n,in,A}^2} (4(R_s + R_{\rm VI} + R_{sw}) + 2R_{\rm BB})^2}{4 \text{ kT}R_s (4\gamma)(2R_{\rm BB})^2}.$$

(8)

An explanation is given in the following. The thermal noise of  $R_N$  and the corresponding mixer switch is suppressed by the switched capacitor  $C_B$  in Fig. 8(a) due to its notch function. The direct noise contribution from thermal noise of  $R_{\rm VI}$  and the mixer switch in series is  $(R_{\rm VI} + R_{\rm sw})/R_s$ . Moreover, noise degradation due to noise folding from odd harmonics of the mixing frequency occurs. Thermal noise of  $R_s$ ,  $R_{\rm VI}$ , and  $R_{sw}$  are hence down-converted and sampled [13], leading to a summation of  $4kT(R_s + R_{\rm VI} + R_{sw})/n^2$  terms, where n = 3, 5, 7, ... for a four-path mixer. This sums up to  $\approx 4kT(R_s + R_{\rm VI} + R_{sw})/4.3$ . The up-converted noise current induced by the BB feedback resistor  $R_F$  renders the term proportional to  $1/(2\gamma R_F)$ . Note that  $R_F$  is much higher than  $R_s$  primarily due to the negative feedback. Therefore, the noise contribution of  $R_F$  is minor. The input-referred noise of the BB amplifiers is  $v_{n,in,A}^2 = \overline{v_{n,out,A}^2} / \overline{A^2}$ , where  $\overline{v_{n,out,A}^2}$  is noise at the BB amplifier output and  $\sqrt{(v_{n,out,A}^2)} = 1.6 \text{ nV} / \sqrt{\text{Hz}}$ from simulation. The noise voltage due to source resistance at the BB amplifier input undergoes a voltage division with gain of  $\sqrt{4\gamma}$  and it is  $v_{n,s,BB}^2 = 4 \text{ kT}R_s(4\gamma)(2R_{BB}/(4(R_s +$  $(R_{\rm VI} + R_{\rm sw}) + 2R_{\rm BB}))^2$ , where  $R_{\rm BB}$  is  $R_F/(1+A)$ . Filling the design values in (8), NF of 3.9 dB at very low frequency is obtained.

# D. Influence of Parasitic Capacitance at the RF Input Port

Bottom-plate mixing can offer blocker rejection with significantly higher linearity than a conventional top-plate mixing *N*-path filter. However, it also brings some limitations. There is no isolation by the mixer switch between the RF input and filter capacitors when a switch is in its off-state, complicating the read-out of the BB signal across the capacitors. The floating filter capacitors will have a parasitic capacitance to substrate, which is directly connected to the RF input introducing signal loss<sup>2</sup>. In this design, metal-oxide-metal (MOM) capacitors were used, and the lowest layer was metal 3 instead of 1 to reduce parasitic capacitance is about 1.1% of MOM capacitance. As shown in Fig. 8(a), the total MOM

$<sup>^{2}</sup>$ The paracistic capacitance can be put only at bottom plate of the MOM capacitor on the switch side, but this has even larger disadvantage.

capacitance seen by RF input is  $4C_A + 4C_B$ . Since one of the bottom plates of  $C_A$  is connected to the symmetry point when the switch is on, the total MOM parasitic capacitance is  $0.011(4C_A \times 7/8 + 4C_B) \approx 4.4$  pF. As large mixer switches were applied for high linearity, substantial extra parasitic MOSFET junction and overlap capacitances are introduced at other nodes. The total unwanted parasitic capacitance  $C_s$  that is from RF input  $V_{\text{IN,RF}}^+$  ( $V_{\text{IN,RF}}^-$ ) coupled to ground in Fig. 8(a) is about 5.2 pF. It decreases the harmonic shunt impedance  $R_p(\omega_{\text{LO}})$  and increases the folded noise [14]. For a four-path mixer-first receiver,  $R_p(\omega_{\text{LO}})$  can be approximated as [14]:

$$R_p(\omega_{\rm LO}) \approx 4.3 R_{sw} (1 + (4 R_{sw} C_s \omega_{\rm LO} + R_{sw} / R_s)^{-1}).$$

(9)

The reduction of  $R_p(\omega_{\text{LO}})$  at higher  $\omega_{\text{LO}}$  causes gain, S<sub>11</sub> and NF degradation. Taking the parasitic capacitance  $C_s$  into account, the RX gain as a function of  $\omega_{\text{LO}}$  can be written as

$$\frac{2(R_{\rm in}(\omega_{\rm LO})||(j\omega_{\rm LO}C_s)^{-1})R_{\rm U}}{(0.5R_{\rm s} + R_{\rm in}(\omega_{\rm LO})||(j\omega_{\rm LO}C_s)^{-1})(R_{\rm VI} + R_{\rm U})} \times (\sqrt{4\gamma})^{-1}g_{\rm m}(r_{\rm o}||R_{\rm F})$$

(10)

where  $R_{\rm in}(\omega_{\rm LO})$  is  $R_p(\omega_{\rm LO})||(R_{\rm VI} + R_{\rm U})$ ,  $R_{\rm U} = 2\gamma R_{\rm F}/(1 + A)$ ,  $\gamma = 2/\pi^2$ ,  $A = g_m(r_o)|R_{\rm F}$  [see Fig. 8(b)].

The parasitic capacitance causes direct input attenuation and more harmonic folding noise [14]. Considering these mechanisms, the noise factor as a function of the LO frequency can be written as

$$F \approx 1 + \frac{(R_{\rm VI} + R_{sw})}{{\rm Re}(Z_s)} + \frac{({\rm Re}(R_{\rm VI} + Z_s + R_{sw}))^2}{{\rm Re}(Z_s){\rm Rp}(\omega_{\rm LO})}$$

(11)

where  $Z_s = R_s ||(j\omega_{\text{LO}}C_s)^{-1}$  and  $R_p(\omega_{\text{LO}})$  can be obtained from (9). Since the BB noise is a minor contribution as discussed in (8), it is neglected in (11).

Note that the center frequency of an *N*-path filter is controlled by LO; therefore, the parasitic capacitance does not influence the tuning range. However, there is one mixer switch connected to  $R_N$  of the notch filter while there are four mixer switches connected to  $R_{\rm VI}$  in Fig. 8(a). A difference of parasitic capacitance of three mixer switches in off-state is present. It causes small center frequency difference that slightly degrades gain and noise performance.

# V. MEASUREMENT RESULT AND COMPARISON

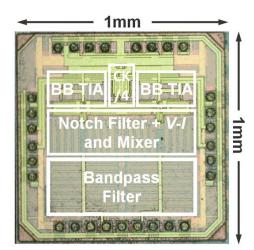

A test chip was fabricated in 1P7M TSMC 28-nm technology and packaged in a  $3 \times 3$  QFN package (i.e., the same chip was characterized in [8]). The total chip area including pads and decoupling capacitors is 1 mm<sup>2</sup> while the active area is 0.8 mm<sup>2</sup>. Fig. 10 shows the chip micrograph. The external differential clock is applied from the top side, while the RF input-signal is applied from the bottom to reduce coupling. An off-chip 10–8000 MHz 1:1 transformer (Mini-Circuits TCM1-83X+) serves as balun for single-to-differential conversion, while also providing impedance matching to the  $50-\Omega$  differential chip input. Both the balun and cable losses were de-embedded for all measurements except the  $S_{11}$ measurement.

Fig. 10. Chip microphotograph.

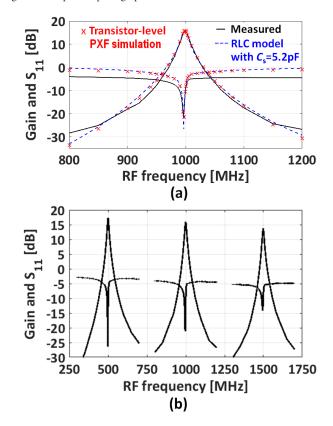

Fig. 11. (a) Measured and simulated gain and  $S_{11}$  versus RF frequency ( $f_{\text{LO}} = 1 \text{ GHz}$ ). (b) Measured gain and  $S_{11}$  for three LO frequencies.

# A. Gain and $S_{11}$

Because the BB amplifier is not able to directly drive a 50- $\Omega$  load, a low-noise external measurement buffer (TELE-DYNE LECROY AP033 Active Differential Probe) with differential high-impedance input and single-ended 50- $\Omega$  output impedance was added. A weak tone of -50 dBm is applied to the RF input, and the BB output is observed to obtain the conversion gain. Fig. 11(a) shows the measured voltage gain and  $S_{11}$  as a function of the RF input frequency for a 1-GHz LO. To compare measurement to theory, the RLC model in Fig. 8(b) was used and a shunt  $C_s$  of 5.2 pF

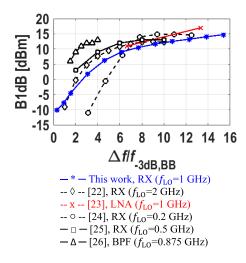

Fig. 12. Measured B1dB as a function of relative blocker frequency offset  $\Delta f/f_{-3dB,BB}$  compared with other blocker-tolerant RF front ends.

is added to the RF input. Applying (9),  $R_p(\omega_{LO})$  becomes 30  $\Omega$ . The single ended input impedance of this receiver  $R_{in}(\omega_{LO})$  is  $R_p(\omega_{LO})||(R_{VI}+R_{sw}+2\gamma R_{BB})$ , it becomes  $\approx$ 50  $\Omega$  differentially. The receiver conversion gain obtained from the RLC model can be computed by using (6) and (7), while  $R_p$  of (6) becomes  $R_p(\omega_{LO})||(j\omega C_s)^{-1}$  now. It is observed that both the gain and optimum  $S_{11}$  dip are shifted toward lower frequencies due to the presence of  $C_s$ , in agreement with the analysis in [13] and [21]. This issue can be addressed by introducing complex feedback with resistors [3] or adding a series inductor [21]. The measured gain is about 16 dB and the  $f_{-3dB,BPF}$  is about 13 MHz ( $f_{-3dB,BB} = 6.5$  MHz), while the filter roll-off from 20- to 200-MHz offset is about -32 dB [-34 dB from (6)] for the upper sideband, and -33 dB [-38 dB from (6)] for the lower sideband.

Note that the deviation between the measured  $S_{11}$  and the theoretical prediction is likely due to balun non-idealities. (Simulations were done with an ideal balun model.) Fig. 11(b) shows gain and  $S_{11}$  plots over three LO different frequencies to illustrate the filter tuning capability of the receiver.

# B. B1dB, IIP2, and IIP3

Fig. 12 shows the measured B1dB as a function of the relative frequency offset  $\Delta f/f_{-3dB,BB}$  for  $f_{LO} = 1$  GHz and a desired signal at 1.001 GHz ( $f_{BB} = 1$  MHz). Already at  $\Delta f/f_{-3dB,BB} > 3$ , B1dB is >0 dBm, while for  $\Delta f/f_{-3dB,BB} > 8$ , B1dB > +10 dBm. Note that this design only uses a 1.2-V supply. (The design in [23] artificially boosts B1dB by increasing the supply voltage introducing device reliability concerns.) To show this is competitive, Fig. 12 also shows results for several blocker-tolerant receivers that achieved > +10-dBm B1dB [22]–[24].

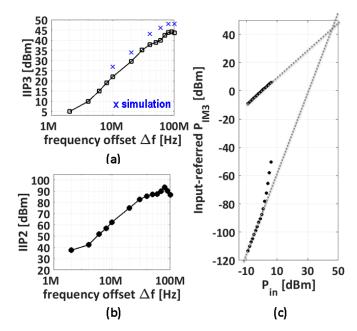

IIP3 and IIP2 measurements are performed by two-tone tests. Circulators that offer higher than 20-dB isolation are applied between the two blocker signal generators to prevent intermodulation in the test setup, so that over +55-dBm IIP3 was achieved in the test setup itself. For LTE radio applications, the transmitter signal frequency is lower than the receiver frequency for most of the bands. Therefore, the test

Fig. 13. Measured (a) IIP3, (b) IIP2 versus blocker frequency offset  $\Delta f$  at  $f_{\text{LO}} = 1$  GHz, and (c) measured  $P_{\text{IIM3}}$  versus  $P_{\text{in}}$  for  $\Delta f = 80$  MHz.

tones were chosen at  $f_1 = f_{LO} - \Delta f$  and  $f_2 = f_{LO} - 2\Delta f + f_{LO} + \Delta f$ 500 kHz for IIP3 measurements, and at  $f_1 = f_{\rm LO} - \Delta f$ and  $f_2 = f_{LO} - \Delta f + 500$  kHz for IIP2 measurements. This choice keeps the resulting IM3 or IM2 product at a constant BB frequency of 500 kHz. In a practical wireless communication system such as LTE, the frequency offset between TX and RX in FDD mode is specified in the standard. The very high IIP3 and IIP2 is only required at this specified frequency offset  $\Delta f$ . Measured IIP3 and IIP2 as a function of  $\Delta f$  for a 1-GHz LO are shown in Fig. 13. At  $\Delta f = 80$ MHz, very high IIP3 of +44 dBm and IIP2 of +90 dBm are achieved. As shown in Fig. 13(a), there is discrepancy between simulated and measured IIP3. It is due to the circuit mismatch and the amplitude and phase imbalance of the balun. Simulation shows that 10% amplitude imbalance causes 1-dB IIP3 degradation while 10% phase imbalance causes about 2-dB IIP3 degradation. Fig. 13(c) shows the input referred IM3 as a function of the blocker power for a 1-GHz LO and  $\Delta f$  = 80 MHz. The measured  $P_{\rm IIM3}$ follows the extrapolation line up to an input power as high as 0 dBm. Basically  $R_{sw} \ll R_s$  is required to achieve such high linearity, causing large switch gate capacitance. As the required power consumption of the clocking circuit to drive switches is proportional to the clock frequency and switch gate capacitance, there is a tradeoff between linearity and LO power.

In this receiver design, phase shifts in the LO between the bandpass and notch mixers will contribute to charge sharing between BB capacitors. To investigate how it influences the linearity, we deliberately add a delay on the LO clock that drives notch filter. Simulation shows that the IIP3 variation of this receiver is kept less than 0.5 dB, NF and gain variations are kept less than 0.1 dB when the clock delay between bandpass and notch is within 5 ps. The possible charge sharing has a minor impact on the linearity.

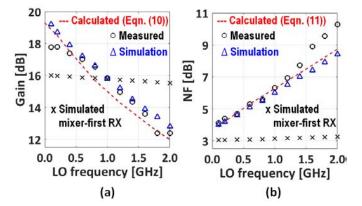

Fig. 14. (a) Gain and (b) DSB NF versus LO frequency of the proposed receiver and the conventional mixer-first receiver [3].

## C. NF and Gain Versus LO Frequency

Fig. 14(a) shows the measured and transistor-level (with QRC layout extraction) simulated gain as a function of LO frequency. The gain loss at higher  $f_{LO}$  is due to input impedance reduction as a result of parasitic capacitance  $C_s$  as discussed in Section IV-D. The measured conversion gain at a low LO frequency of 100 MHz is about 18 dB while the simulated gain is about 19 dB. This deviation is due to variation as a function of frequency in the output impedance of the on-board balun (35  $\Omega$ , instead of 50  $\Omega$ ). As a result, the harmonic shunt impedance and the RF input impedance will be smaller, and the conversion gain at the RF input becomes lower.

NF measurements were performed using the Y-factor method with an external noise source. As shown in Fig. 14(b), at low LO frequency of 100 MHz, NF is 4.2 dB. The parasitic capacitance  $C_s$  at RF input is not taken into account in (8) derived in Section IV-C. In the practical circuit, this lowers the impedance seen by the source voltage at higher RF frequencies. Therefore, the source resistance contributes a lower percentage of the total output noise at higher frequencies and NF increases.

The proposed receiver can achieve steeper filter roll-off and better linearity than a conventional mixer-first receiver [3]. However, the gain and NF of the proposed receiver degrade more rapidly at higher operating frequency. The simulated gain and NF as a function of LO frequency for a conventional mixer-first receiver [3] is also shown in Fig. 14 for comparison. Note that the same mixer switch size is applied but smaller BB feedback resistor is used for input matching in the conventional mixer-first receiver [3].

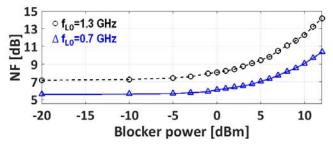

## D. Blocker NF

Fig. 15 shows the measured NF as a function of blocker power for 0.7- and 1.3-GHz LO-frequency, while the blocker offset was 80 MHz. The measured desensitization is only 0.6 dB for a 0-dBm blocker and 3.5 dB for a 10-dBm blocker at 0.7-GHz LO. Overall, the presence of strong blockers degrades NF due to reciprocal mixing and gain compression. Since the measured B1 dB is as high as +13 dBm, the blocker NF degradation is most likely due to reciprocal mixing which is proportional to blocker power and phase noise of LO. To obtain satisfactory measured blocker NF, two external

Fig. 15. Measured blocker NF (blocker frequency offset  $\Delta f = 80$  MHz) for  $f_{\text{LO}} = 0.7$  GHz and  $f_{\text{LO}} = 1.3$  GHz.

Fig. 16. IIP3 benchmark of blocker-tolerant RF front ends as a function of  $(\Delta f / f_{-3dB,BB})$ .

tunable narrowband BPFs in cascade were applied to the output of the signal generators used to supply  $4 \times LO$  for ensuring low phase noise. The clocking circuit consumes about 33 mW/GHz from 1.2-V supply to achieve a simulated phase noise of -170 dBc/Hz for 1-GHz LO at 80-MHz offset frequency. As also discussed in [27], generating an LO with such strict requirements is one of the biggest challenges of passive mixing SAW-less receiver designs.

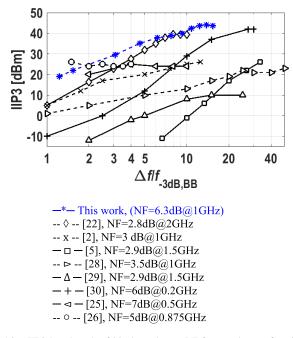

#### E. Performance Comparison

Fig. 16 shows an IIP3 benchmark of blocker-tolerant RF front ends as a function of  $\Delta f/f_{-3dB,BB}$ . The proposed bottom-plate mixing *N*-path filter with switch sharing improves both in-band and OOB linearity. Hence, this design achieves the highest reported linearity while achieving a moderate NF of 6.3 dB for a 1-GHz LO. A detailed performance summary and comparison is shown in Table I. Compared to prior art, the receiver achieves higher IIP3 and IIP2 for comparable NF and power consumption. This confirms the effectiveness of the higher order RF filtering provided by the proposed cascading of passive V-V and V-I *N*-path BPFs as well as the linearity improvement by bottom-plate mixing and switch sharing.

|                       | <i>JSSC</i> 10[3] | JSSC12[19]                        | JSSC13[2]                         | <i>RFIC15</i> [6] | <i>RFIC15</i> [5]              | RFIC15[23]      | RFIC17[22]                         | <i>ISSCC17</i> [25]              | <i>ISSCC18</i> [26]            | This Work                                   |

|-----------------------|-------------------|-----------------------------------|-----------------------------------|-------------------|--------------------------------|-----------------|------------------------------------|----------------------------------|--------------------------------|---------------------------------------------|

| Circuit type          | Receiver          | Receiver                          | LNA/Filter                        | Receiver          | Receiver                       | LNA/Filter      | Receiver                           | Receiver                         | BPF                            | Receiver                                    |

| Technology            | 65nm              | 40nm                              | 65nm                              | 28nm              | 65nm                           | 32nm SOI        | 45nm SOI                           | 65nm                             | 65nm                           | 28nm                                        |

| f <sub>RF</sub> [GHz] | 0.1-2.4           | 0.08-2.7                          | 0.1-1.2                           | 0.4-3.5           | 0.7-3.8                        | 0.4-6           | 0.2-8                              | 0.1-1                            | 0.8-1.1                        | 0.1-2.0                                     |

| Gain[dB]              | 40-70             | 72                                | 25                                | 35                | 40                             | 12              | 21                                 | 23                               | NA                             | 16                                          |

| BB BW[MHz]            | 10                | 2                                 | 4                                 | 15-50             | 5                              | 7.5             | 10                                 | 5                                | 20                             | 6.5                                         |

| OOB<br>IIP3[dBm]      | 25<br>Δƒ/BW=10    | 10<br>Δƒ/BW=5<br>13.5<br>Δƒ/BW=40 | 20<br>Δƒ/BW=5<br>26<br>Δƒ/BW=12.5 | 20.5<br>Δƒ/BW=3.3 | 0<br>Δƒ/BW=6<br>26<br>Δƒ/BW=20 | 36<br>Δƒ/BW=6.7 | 39<br>Δƒ/BW=8                      | 21<br>Δƒ/BW=2.4<br>24<br>Δƒ/BW=6 | 24<br>Δƒ/BW=2<br>25<br>Δƒ/BW=4 | 35<br>Δf/BW=4.6<br>44<br>Δf/BW=12.3         |

| OOB<br>IIP2[dBm]      | 56                | 55                                | NA                                | 64                | 65                             | NA              | 88                                 | 64                               | NA                             | 90                                          |

| B1dB[dBm]             | 10<br>Δƒ/BW=10    | 6<br>Δƒ/BW=5<br>2<br>Δƒ/BW=40     | 2<br>Δƒ/BW=5<br>7<br>Δƒ/BW=12.5   | 4.6<br>Δƒ/BW=3.3  | 20<br>Δƒ/BW=6<br>3<br>Δƒ/BW=20 | 11<br>Δƒ/BW=6.7 | 12<br>Δƒ/BW=8                      | 5<br>Δƒ/BW=2.4<br>12<br>Δƒ/BW=6  | 9<br>Δƒ/BW=2<br>13<br>Δƒ/BW=4  | 6<br>Δf/BW=4.6<br>13<br>Δf/BW=12.3          |

| NF[dB]                | 4±1               | 1.9<br>(@2GHz)                    | 2.8                               | 2.4-2.6           | 2.5-4.5                        | 3.6-4.9         | 2.3-5.4<br>(0.5-6GHz)              | 7                                | 5.0-8.6                        | 4.1-10.3                                    |

| OdBm<br>Blocker NF    | NA                | 4.1dB<br>@1.5GHz                  | NA                                | 6.5dB<br>@2GHz    | NA                             | NA              | 4.7dB<br>@1.4GHz                   | NA                               | NA                             | 8.1dB<br>@1.3GHz                            |

| Supply[V]             | 1.2/2.5           | 1.2/2.5                           | 1.2                               | 1/1.5             | 1.2                            | 2               | 1.2                                | 1.2/1                            | NA                             | 1.2/1.0                                     |

| Power<br>[mW]         | 37-70             | 27-60                             | 15-48                             | 38-75             | 27-75                          | 81-209          | LO:<br>30mW/GHz<br>BB Amp:<br>50mW | 64-84                            | 80-97                          | 34-96<br>LO:<br>33mW/GHz<br>BB Amp:<br>30mW |

TABLE I Result Summary and Comparison With Prior Arts

#### VI. CONCLUSION

In this paper, a high-linearity receiver combining 2-stage N-path filtering with passive mixing is proposed, analyzed, implemented, and evaluated. The N-path filter is a cascade of a passive V-V and a V-I BPF, enhancing selectivity. Very high linearity is achieved exploiting a bottom-plate mixing technique that improves both in-band and OOB linearity. Switch sharing further improves linearity and can offer an additional 9-dB IIP3 enhancement. Implemented in 28-nm CMOS, a high-linearity RX achieving +44-dBm IIP3, +90-dBm IIP2, +13-dBm B1dB with moderate NF of 6.3 dB at 1-GHz LO frequency is demonstrated, offering robustness to strong TX leakage.

## ACKNOWLEDGMENT

The authors would like to thank S. Reeves for chip layout, G. Wienk for PCB layout, and H. de Vries for measurement setup assistance.

#### REFERENCES

- A. Ghaffari, E. A. M. Klumperink, M. C. M. Soer, and B. Nauta, "Tunable high-Q N-path band-pass filters: Modeling and verification," *IEEE J. Solid-State Circuits*, vol. 46, no. 5, pp. 998–1010, May 2011.

- [2] M. Darvishi, R. van der Zee, and B. Nauta, "Design of active N-path filters," *IEEE J. Solid-State Circuits*, vol. 48, no. 12, pp. 2962–2976, Dec. 2013.

- [3] C. Andrews and A. C. Molnar, "A passive mixer-first receiver with digitally controlled and widely tunable RF interface," *IEEE J. Solid-State Circuits*, vol. 45, no. 12, pp. 2696–2708, Dec. 2010.

- [4] M. C. M. Soer, E. A. M. Klumperink, Z. Ru, F. E. van Vliet, and B. Nauta, "A 0.2-to-2.0 GHz 65 nm CMOS receiver without LNA achieving >11 dBm IIP3 and <6.5 dB NF," in *IEEE Int. Solid-State Circuits Conf. (ISSCC) Dig. Tech. Papers*, Feb. 2009, pp. 222–223 and 223a.

- [5] A. Nejdel, M. Abdulaziz, M. Törmänen, and H. Sjöland, "A positive feedback passive mixer-first receiver front-end," in *Proc. IEEE Radio Freq. Integr. Circuits Symp. (RFIC)*, May 2015, pp. 79–82.

- [6] C. Wu, Y. Wang, B. Nikolic, and C. Hull, "A passive-mixer-first receiver with LO leakage suppression, 2.6 dB NF, >15 dBm wide-band IIP3, 66 dB IRR supporting non-contiguous carrier aggregation," in *Proc. IEEE Radio Freq. Integr. Circuits Symp. (RFIC)*, May 2015, pp. 155–158.

- [7] M. Darvishi, R. van der Zee, E. A. M. Klumperink, and B. Nauta, "Widely tunable 4th order switched G\_m-C band-pass filter based on N-path filters," *IEEE J. Solid-State Circuits*, vol. 47, no. 12, pp. 3105–3119, Dec. 2012.

- [8] Y. Lien, E. Klumperink, B. Tenbroek, J. Strange, and B. Nauta, "A high-linearity CMOS receiver achieving +44 dBm IIP3 and +13 dBm B1 dB for SAW-less LTE radio," in *IEEE Int. Solid-State Circuits Conf. (ISSCC) Dig. Tech. Papers*, Feb. 2017, pp. 412–413.

- [9] N. Reiskarimian and H. Krishnaswamy, "Design of all-passive higherorder CMOS N-path filters," in *Proc. IEEE Radio Freq. Integr. Circuits Symp. (RFIC)*, May 2015, pp. 83–86.

- [10] M. C. M. Soer, E. A. M. Klumperink, P. T. de Boer, F. E. van Vliet, and B. Nauta, "Unified frequency-domain analysis of switched-series-RC passive mixers and samplers," *IEEE Trans. Circuits Syst. I, Reg. Papers*, vol. 57, no. 10, pp. 2618–2631, Oct. 2010.

- [11] S. Pavan and E. A. M. Klumperink, "Simplified unified analysis of switched-RC passive mixers, samplers, and N-path filters using the adjoint network," *IEEE Trans. Circuits Syst. I, Reg. Papers*, vol. 64, no. 10, pp. 2714–2725, Oct. 2017.

- [12] T. Iizuka and A. A. Abidi, "FET-R-C circuits: A unified treatment— Part II: Extension to multi-paths, noise figure, and driving-point impedance," *IEEE Trans. Circuits Syst. I, Reg. Papers*, vol. 63, no. 9, pp. 1337–1348, Sep. 2016.

- [13] C. Andrews and A. C. Molnar, "Implications of passive mixer transparency for impedance matching and noise figure in passive mixer-first receivers," *IEEE Trans. Circuits Syst. I, Reg. Papers*, vol. 57, no. 12, pp. 3092–3103, Dec. 2010.

- [14] D. Yang, C. Andrews, and A. Molnar, "Optimized design of N-phase passive mixer-first receivers in wideband operation," *IEEE Trans. Circuits Syst. I, Reg. Papers*, vol. 62, no. 11, pp. 2759–2770, Nov. 2015.

- [15] Z. Ru, E. A. M. Klumperink, and B. Nauta, "Discrete-time mixing receiver architecture for RF-sampling software-defined radio," *IEEE J. Solid-State Circuits*, vol. 45, no. 9, pp. 1732–1745, Sep. 2010.

- [16] A. Ghaffari, E. A. M. Klumperink, and B. Nauta, "Tunable Npath notch filters for blocker suppression: Modeling and verification," *IEEE J. Solid-State Circuits*, vol. 48, no. 6, pp. 1370–1382, Jun. 2013.

- [17] E. A. M. Klumperink and B. Nauta, "Systematic comparison of HF CMOS transconductors," *IEEE Trans. Circuits Syst. II, Analog Digit. Signal Process.*, vol. 50, no. 10, pp. 728–741, Oct. 2003.

- [18] B. Nauta, "A CMOS transconductance-C filter technique for very high frequencies," *IEEE J. Solid-State Circuits*, vol. 27, no. 2, pp. 142–153, Feb. 1992.

- [19] D. Murphy et al., "A blocker-tolerant, noise-cancelling receiver suitable for wideband wireless applications," *IEEE J. Solid-State Circuits*, vol. 47, no. 12, pp. 2943–2963, Dec. 2012.

- [20] W. Sansen, "Distortion in elementary transistor circuits," *IEEE Trans. Circuits Syst. II, Analog Digit. Signal Process.*, vol. 46, no. 3, pp. 315–325, Mar. 1999.

- [21] S. Pavan and E. Klumperink, "Analysis of the effect of source capacitance and inductance on *N*-path mixers and filters," *IEEE Trans. Circuits Syst. I, Reg. Papers*, vol. 65, no. 5, pp. 1469–1480, May 2017.

- [22] Y. Lien, E. Klumperink, B. Tenbroek, J. Strange, and B. Nauta, "A mixer-first receiver with enhanced selectivity by capacitive positive feedback achieving +39 dBm IIP3 and <3 dB noise figure for SAW-less radio," Proc. IEEE LTE in Radio Integr. Circuits (RFIC), 2017, Freq. Symp. Feb pp. 280-283.

- [23] C.-K. Luo, P. S. Gudem, and J. F. Buckwalter, "0.4–6 GHz,17-dBm B1 dB, 36-dBm IIP3 channel-selecting, low-noise amplifier for SAW-less 3G/4G FDD receivers," in *Proc. IEEE Radio Freq. Integr. Circuits Symp. (RFIC)*, May 2015, pp. 299–302.

- [24] Y. Xu and P. R. Kinget, "A switched-capacitor RF front end with embedded programmable high-order filtering," *IEEE J. Solid-State Circuits*, vol. 51, no. 5, pp. 1154–1167, May 2016.

- [25] S. Hameed and S. Pamarti, "A time-interleaved filtering-by-aliasing receiver front-end with >70 dB suppression at <4× bandwidth frequency offset," in *IEEE Int. Solid-State Circuits Conf. (ISSCC) Dig. Tech. Papers*, Feb. 2017, pp. 418–419.

- [26] P. Song and H. Hashemi, "A 13<sup>th</sup>-order CMOS reconfigurable RF BPF with adjustable transmission zeros for SAW-less SDR receivers," in *IEEE Int. Solid-State Circuits Conf. (ISSCC) Dig. Tech. Papers*, Feb. 2018, pp. 416–418.

- [27] H. Wu, M. Mikhemar, D. Murphy, H. Darabi, and M.-C. F. Chang, "A blocker-tolerant inductor-less wideband receiver with phase and thermal noise cancellation," *IEEE J. Solid-State Circuits*, vol. 50, no. 12, pp. 2948–2964, Dec. 2015.

- [28] H. Hedayati, V. Aparin, and K. Entesari, "A +22 dBm IIP3 and 3.5 dB NF wideband receiver with RF and baseband blocker filtering techniques," in *Symp. VLSI Circuits Dig. Tech. Papers*, Jun. 2014, pp. 1–2.

- [29] L. Zhicheng, M. Pui-In, and R. P. Martins, "A 0.028 mm<sup>2</sup> 11 mW single-mixing blocker-tolerant receiver with double-RF N-path filtering, S11centering, +13 dBm OB-IIP3 and 1.5-to-2.9 dB NF," in *IEEE Int. Solid-State Circuits Conf. (ISSCC) Dig. Tech. Papers*, Feb. 2015, pp. 1–3.

- [30] H. Westerveld, E. Klumperink, and B. Nauta, "A cross-coupled switch-RC mixer-first technique achieving +41 dBm out-of-band IIP3," in *Proc. IEEE Radio Freq. Integr. Circuits Symp. (RFIC)*, May 2016, pp. 246–249.

Yuan-Ching Lien (S'16) was born in Taipei, Taiwan. He received the B.S. and M.S. degrees in electrical engineering from National Taiwan University, Taipei.

In 2007, he joined MediaTek Inc., Hsinchu, Taiwan. From 2014 to 2018, he did Ph.D. research at the University of Twente, Enschede, The Netherlands. His research interests include continuous-time filters, Nyquist rate data converters, and reconfigurable RF front-ends.

**Eric A. M. Klumperink** (M'98–SM'06) was born in Lichtenvoorde, The Netherlands, in 1960. He received the B.Sc. degree from HTS, Enschede, The Netherlands, in 1982.

He worked in industry on digital hardware and software. In 1984, he then joined the University of Twente, Enschede, shifting focus to analog CMOS circuit research. This resulted in several publications and his Ph.D. thesis "Transconductance Based CMOS Circuits" in 1997. In 1998, he joined the IC-Design Laboratory, University of Twente, as an

Assistant Professor, and shifted research focus to RF CMOS circuits (e.g., sabbatical at the Ruhr Universitaet, Bochum, Germany). Since 2006, he has been an Associate Professor, teaching Analog and RF IC electronics and guiding Ph.D. and M.Sc. projects related to RF CMOS circuit design with a focus on software-defined radio, cognitive radio, and beamforming. He has authored or co-authored over 150 internationally refereed journal and conference papers, and was recognized as over 20 ISSCC paper contributor over from 1954 to 2013. He holds several patents.

Prof. Klumperink was a co-recipient of the ISSCC 2002 and the ISSCC 2009 "Van Vessem Outstanding Paper Award." He served as an Associate Editor for the IEEE TCAS-II from 2006 to 2007, the IEEE TCAS-I from 2008 to 2009, and the IEEE JSSC from 2010 to 2014, an IEEE SSC Distinguished Lecturer from 2014 to 2015, and a member of the technical program committees of ISSCC from 2011 to 2016 and the IEEE RFIC Symposium in 2011.

**Bernard Tenbroek** received the M.Sc. degree in electrical engineering from the University of Twente, Enschede, The Netherlands, in 1993, and the Ph.D. degree from the University of Southampton, Southampton, U.K., in 1997.

From 1997 to 1998, he was Research Fellow at the University of Southampton. From 1998 to 2000, he was a Staff Engineer with Asahi Kasei Microelectronics. From 2000 to 2008, he was a Design Manager at Analog Devices. In 2008, he joined the RF Design Center, MediaTek, Kent, U.K., as a Design

Engineering Manager, where he focused on advanced cellular transceivers. He has authored over 20 journal and conference papers. He holds two patents.

Dr. Tenbroek received the ISSCC Outstanding European Paper Award in 2007.

**Jon Strange** (M'00–SM'11) was born in Wigan, U.K, in 1963. He received the B.Sc. degree in physics from the University of Durham, Durham, U.K., in 1984, and the M.Sc. degree in microelectronics from the University of Edinburgh, Edinburgh, U.K., in 1985.

From 1985 to 1987, he was a Researcher with the VLSI Department, Thorn-EMI Central Research Laboratories, and from 1988 to 1991, he held several design and engineering management positions for LSI Logic. In 1991, he co-founded Mosaic Micro

Systems, Ltd., a RF and wireless design consultancy specializing in RF and radio system IC design which was acquired by Analog Devices in 1996. From 1996 to 2008, he was an Engineering Director within the RF and Wireless Business Unit Analog Devices Inc., responsible for RF IC product design. He is currently a Senior Director of RF Design and a fellow at Mediatek Wireless Ltd., Kent, U.K., responsible for developing cellular transceivers and related technologies for mobile platforms. He has authored or co-authored 15 technical conference and journal papers.

Mr. Strange holds 16 granted U.S. patents.

**Bram Nauta** (S'89–M'91–SM'03–F'08) was born in Hengelo, The Netherlands, in 1964. He received the M.Sc degree (*cum laude*) in electrical engineering and the Ph.D. degree in analog CMOS filters for very high frequencies from the University of Twente, Enschede, The Netherlands, in 1987.

In 1991, he joined the Mixed-Signal Circuits and Systems Department, Philips Research, Eindhoven, The Netherlands. In 1998, he returned to the University of Twente, Enschede, The Netherlands, where he is currently a Distinguished Professor, heading the

IC Design group. Since 2016, he has been a Chair with the EE Department. His current research interest is high-speed analog CMOS circuits, software-defined radio, cognitive radio, and beamforming.

Dr. Nauta is a member of the Royal Netherlands Academy of Arts and Sciences. He was a co-recipient of the ISSCC 2002 and 2009 "Van Vessem Outstanding Paper Award" and in 2014 he received the "Simon Stevin Meester" Award (500.000€), the largest Dutch national prize for achievements in technical sciences. He served as the Editor-in-Chief of the IEEE JOURNAL OF SOLID-STATE CIRCUITS (JSSC)from 2007 to 2010, and was the 2013 Program Chair of the International Solid State Circuits Conference (ISSCC). He is the President of the IEEE Solid-State Circuits Society from 2018 to 2019. He served as an Associate Editor for the IEEE TRANSACTIONS ON CIRCUITS AND SYSTEMS II from 1997 to 1999, and JSSC from 2001 to 2006. He was in the Technical Program Committee of the Symposium on VLSI circuits from 2009 to 2013 and is in the steering committee and program committee of the European Solid State Circuit Conference (ESSCIRC). He served as a Distinguished Lecturer of the IEEE.