# Highly Integrated ZVS Flyback Converter ICs With Pulse Transformer to Optimize USB Power Delivery for Fast-Charging Mobile Devices

Wei-Hsu Chang<sup>(D)</sup>, Yen-Ming Chen, Ching-Jan Chen<sup>(D)</sup>, *Senior Member, IEEE*, Pin-Ying Wang, Kun-Yu Lin, Chun-Ching Lee, Li-Di Lo, Jenn-Yu G. Lin, and Ta-Yung Yang

Abstract-Flyback converter with USB power delivery is widely used for fast-charging mobile devices. However, conventional solutions have issues such as lower efficiency, higher cost, a large number of external components, and lower loop gain bandwidth. In this article, a high-efficiency zero-voltage switching (ZVS) flyback converter with primary- and secondary-side control ICs is proposed to solve the aforementioned issues with high integration level. The proposed control replaces optocoupler to achieve ZVS and secondary-side-regulation (SSR) by a pulse transformer. The ICs further integrate the USB power delivery (PD) controller and the constant voltage (CV)/constant current (CC) loop compensation to reduce external components. The proposed control and small-signal model are illustrated and verified by the experiment. The control ICs were fabricated in a 180-nm BCD process. The implemented 20-V/3-A/60-W USB PD flyback converter achieved 93.5% maximum efficiency using Si power switches. The feasibility of the proposed converter is verified by a thorough test of programmable power supply (PPS) with various CC/CV levels and load/line transients.

*Index Terms*—Converter, constant voltage (CV)/constant current (CC), fast-charging, flyback converter, pulse transformer, USB power delivery (PD), zero-voltage switching (ZVS).

#### I. INTRODUCTION

U SB power delivery (PD) supporting up to 100 W (20 V/5 A) has become a popular standard for mobile devices' fast-charging solution [1]–[3]. An adapter with the USB-PD specification has the advantage of supplying various devices with a single converter. For example, the converter with the input from the grid can provide a 5-V dc output voltage for cellphone load and a 19-V dc output voltage for laptop computer load. Thus, the carrying adaptors and corresponding electronic trash can be reduced. Moreover, the extended specification of USB PD includes a programmable power supply (PPS) which is suitable for fast-charging mobile devices. An adaptor with PPS can dynamically adjust the

Manuscript received April 27, 2020; revised July 19, 2020; accepted August 25, 2020. Date of publication September 16, 2020; date of current version November 24, 2020. This paper was approved by Guest Editor Hoi Lee. (*Corresponding author: Wei-Hsu Chang.*)

Wei-Hsu Chang, Kun-Yu Lin, Chun-Ching Lee, Li-Di Lo, Jenn-Yu G. Lin, and Ta-Yung Yang are with Richtek Technology Corporation, Hsinchu 30288, Taiwan (e-mail: william\_chang@richtek.com).

Yen-Ming Chen, Ching-Jan Chen, and Pin-Ying Wang are with the Department of Electrical Engineering, National Taiwan University, Taipei 10617, Taiwan.

Color versions of one or more of the figures in this article are available online at http://ieeexplore.ieee.org.

Digital Object Identifier 10.1109/JSSC.2020.3021509

Travel Adapter USB Type-C Controller IC VIN\_AC VIN\_AC Win\_Etrocent Travel Adapter VBUS

Fig. 1. Power system with USB PD for smart phone fast charging.

constant voltage (CV) and constant current (CC) output from 3 to 21 V with 20-mV resolution and 1 to 5 A with 50-mA resolution, respectively. This extended and accurately controlled output voltage and current enables the fast-charging function of mobile devices which greatly reduces charging time and improves user experience.

Flyback converter with the secondary-side-regulation (SSR) control scheme is often adopted in the USB PD adaptor for fast charging [2]-[7]. Fig. 1 shows the power system for smartphone fast-charging. An adapter with flyback topology converts the universal ac, VIN\_AC, with 85-265 Vac to the dc output, VBUS. The flyback converter is widely used in below 100-W adapter applications due to its cost-effectiveness and electrical isolation of power transformer [6], [7]. The output of the adaptor is connected to the mobile device through USB type-C cable. USB PD protocol is implemented both in the adaptor and the mobile device to determine the output voltage and current supplied by the adaptor. Finally, a charger IC within the mobile device converts VBUS voltage to charge Li-ion battery. To meet such a wide range and fine resolution output voltage and current regulation, the flyback converter with the SSR control scheme providing the direct output voltage and current feedback is adopted [4]. Therefore, two ICs including primary-side (PS) and secondary-side (SS) controller ICs are required to control the PS switch SW<sub>PS</sub> and SS synchronous rectifier (SR) SW<sub>SR</sub> of flyback converter, respectively.

However, a flyback converter has issues to improve power conversion efficiency. A converter with higher efficiency reduces power loss and temperature rise, which are the keys for mobile charging. To increase the power conversion efficiency, using GaN devices or active clamp circuits is

This work is licensed under a Creative Commons Attribution 4.0 License. For more information, see https://creativecommons.org/licenses/by/4.0/

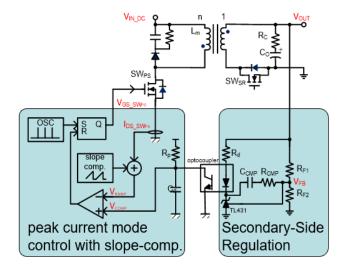

Fig. 2. Conventional flyback converter with SSR control.

possible solutions [7]–[10]. However, the number of external components and the cost is increased. Therefore, a technique to achieve zero-voltage switching (ZVS) at the PS switch by auxiliary turn-on the SR is used in this article [11]. This technique achieves higher efficiency than the quasi-resonance (QR) flyback approach [7], [12], [13]. This article further proposes the switch control method using the pulse transformer to achieve ZVS without extra component and added cost.

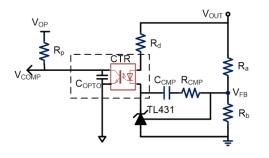

Besides, there are two issues for a conventional flyback converter with SSR control for USB PD, as shown in Fig. 2. The detail of Fig. 2 will be explained in Section III-C. First, an optocoupler is used to feedback the compensation signal from the SS to the PS with isolation [2], [5]–[7], [14]. The optocoupler has nonideal effects of current transfer ratio (CTR) variation with temperature/aging and extra low-frequency parasitic pole, resulting in the drawbacks such as lower loop gain bandwidth and possible stability issues of the feedback loop [2]. Second, the commercially available USB PD flyback converter solutions use an external USB PD controller IC and external shunt-regulator-based loop compensation. The loop compensation in the SS requires several external components including TL431,  $R_{F1}$ ,  $R_{F2}$ ,  $R_d$ , and compensation components R<sub>CMP</sub>, C<sub>CMP</sub>. Thus, component cost and board area are increased.

In this article, control ICs with high efficiency, high integration level, and reduced external components are proposed to solve the aforementioned issues of a flyback converter with USB PD. The ZVS/COMP transceiver with pulse transformer achieves both PS switch ZVS and compensation feedback from the SS to the PS. Thus, the converter achieves high efficiency without additional components and cost. Besides, it avoids the drawbacks of the optocoupler with a small pulse transformer, which package size is only 4.6 mm  $\times$  7 mm. To reduce the number of external components and make the adaptor more compact, the proposed ICs further integrate the USB PD controller and the CV/CC loop compensator with the internal programmable proportional–integral compensator (IPPIC).

The system overview of proposed control ICs is introduced in Section II. The concepts, circuit implementation, design, and small-signal model of the proposed ZVS flyback converter

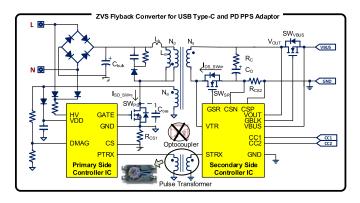

Fig. 3. Simplified circuit diagram of the proposed SSR ZVS flyback converter for the USB PD implemented by the PSC and SSC IC.

are illustrated in Section III. The measurement results are shown in Section IV, and Section V concludes this work.

## **II. SYSTEM OVERVIEW**

Fig. 3 shows the simplified circuit diagram of the proposed ZVS flyback converter, which includes the two-chip solution for SSR and USB PD. The two chips are the PS controller (PSC) and the SS controller (SSC), respectively. The control ICs achieve high efficiency, high integration level, and reduced external components. The ac power passes through a full bridge diode rectifier, an input capacitor  $C_{\text{bulk}}$ , and a flyback converter to generate a regulated dc output voltage  $V_{OUT}$ .  $L_m$  and  $L_K$  are the magnetizing inductance and leakage inductance of power transformer, respectively.  $N_{\rm p}$  and  $N_{\rm s}$  represent the turns of the transformer in the PS and SS.  $N_a$  stands for the turns of transformer auxiliary winding. PSC IC controls the switching of PS power switch SW<sub>PS</sub>; SSC IC controls the switching of SW<sub>SR</sub> in the SS.  $R_{CS1}$ is used to sense the PS current for the peak current mode control.  $R_{CS2}$  is used to sense the load current for the CC/CV regulation loop control. The output capacitor is represented as  $C_0$  in series with the equivalent series resistor (ESR)  $R_C$ . To get higher efficiency, ZVS control by the auxiliary SR switching is utilized to determine the turn-on timing of  $SW_{SR}$ and optimize efficiency. Besides, a pulse transformer is used to deliver the ZVS control signal and compensation signal. Compared with the conventional solution with TL431 and optocoupler, the integration level would be higher due to largely reduced external components.

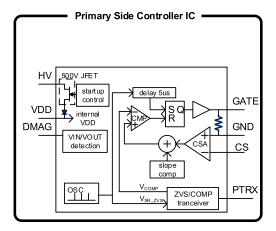

Fig. 4 shows the block diagram of the PSC IC. The IC has an HV pin to provide fast startup from the 85- to  $265-V_{ac}$  ac mains. A 600-V JFET is mounted in the same package with the PSC IC. The JFET is turned on during startup to quickly charge up VDD voltage. Then, the JFET is turned off after the power at the VDD pin is built-up by the auxiliary winding in order to reduce the quiescent current. The GATE pin switches the PS switch, SW<sub>PS</sub>, to deliver power to the output according to the loading condition. The peak current mode control with the slope compensation is used for the PWM control [5], [6]. The compensated signal comes from the ZVS/COMP transceiver at the PTRX pin. To isolate the ground of the PS and SS, a pulse transformer is used between PTRX and STRX.

Fig. 4. Block diagram of proposed PSC IC.

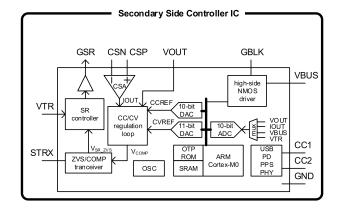

Fig. 5. Block diagram of proposed SSC IC.

There are four major functional blocks in the SSC IC including the SR controller, the internal CV/CC compensator, the ZVS/COMP transceiver, and the embedded Microcontroller Unit (MCU), as shown in Fig. 5. It is common to use the embedded 32-b ARM Cortex-M0 MCU to implement the USB Type-C PD controller IC due to the implementation requirement of the USB PD protocol. In the designed SSC IC, the MCU is not only used to implement the USB PD protocol but also controls and monitors the operating of the flyback converter to respond the smartphone during the fast charging. The MCU sets up the CV/CC compensator's reference DAC through the CC1 and CC2 pins according to the USB PD PPS protocol [1]. Besides, it also sets up various control parameters to optimize the converter's efficiency, stability, and transient response to meet fast-charging requests from the mobile device. By the SR controller, the flyback converter can achieve ZVS control by auxiliary SR switching. The VTR pin is used to sense the zero current in the SS and let the converter operate at DCM.

# III. PROPOSED ZVS FLYBACK CONVERTER ICS

In this section, the key proposed concepts, the circuit implementation, the design, and the small-signal model of the proposed ZVS flyback converter ICs are illustrated.

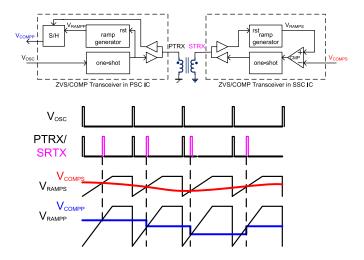

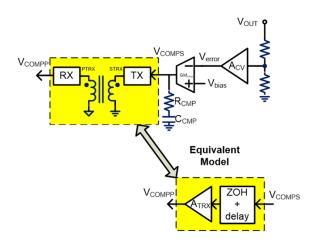

Fig. 6. ZVS/COMP transceiver function block.

## A. ZVS/COMP Transceiver

The top portion of Fig. 6 illustrates the functional block diagram of the ZVS/COMP transceiver in the PSC and SSC. The ZVS/COMP transceiver is used to transmit and receive the ZVS control signal and the compensation signal between the two galvanic isolated ICs from the pulse transformer. The bottom portion of Fig. 6 illustrates the steady-state waveforms of the converter. The inner oscillator generates pulses,  $V_{OSC}$ . It resets  $V_{RAMPP}$  and sends the pulse to PTRX to reset  $V_{\text{RAMPS}}$  through the pulse transformer. In SSC IC,  $V_{\text{COMPS}}$ , compensation signal from the internal CV/CC loop, crosses  $V_{\rm RAMPS}$  and generates one-shot pulse. This pulse sends to STRX through the pulse transformer. In PSC IC, this one-shot pulse is sent to the sample and hold (S/H) block. At this time,  $V_{\rm COMPP}$ , compensation signal value for the peak current mode control with the slope compensation, is equal to the instant value of  $V_{RAMPP}$ . As SRTX is close to PTRX,  $V_{COMPP}$  would be lower. On the contrary, when SRTX is far from PTRX,  $V_{\text{COMPP}}$  would be larger. By controlling  $V_{\text{COMPP}}$ , the output voltage of the flyback converter is regulated.

## B. ZVS Control by Auxiliary SR Switching

ZVS operation can improve converter efficiency by reducing switching loss. If the charge stored in the parasitic capacitance  $C_{\rm DS}$  does not release before the switch turns on, there would be a voltage VDS across the switch. Thus, the  $V_{\rm DS}$ and the channel current IDS would cause some switching loss  $P_{\rm switching\_loss} = V_{\rm DS} \times I_{\rm DS}$ . Besides, a dead time between the turn-on period of SW<sub>PS</sub> and SW<sub>SS</sub> is required to prevent the shoot-through phenomenon. However, long dead time may result in poor efficiency, so the accuracy of the dead-time period must be considered.

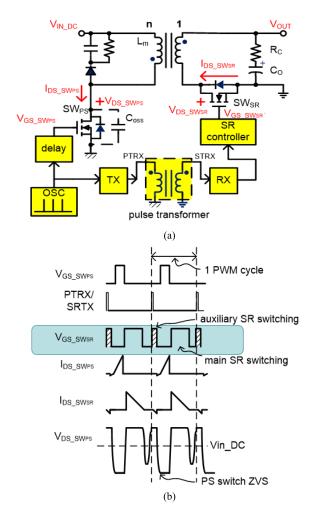

Fig. 7 shows the control method of auxiliary SR switching to achieve ZVS. By adding an auxiliary  $SW_{SR}$  switching, ZVS of  $SW_{PS}$  can be achieved without any extra components like active clamp circuits. After the SR controller receives oscillator signal through the pulse transformer,  $SW_{SR}$  makes the auxiliary switching and induces a negative current on SS. When the auxiliary  $SW_{SR}$  turns off, PS will generate negative

Fig. 7. Auxiliary SR switching control (a) function block and (b) waveform.

current to make the magnetizing inductor current continuously. This negative current will discharge Coss of  $SW_{PS}$  and pull down the voltage across  $SW_{PS}$ . After a delay and low drain voltage is detected,  $SW_{PS}$  turns on and achieves ZVS. After that,  $SW_{SR}$  turns on to achieve synchronous rectification.

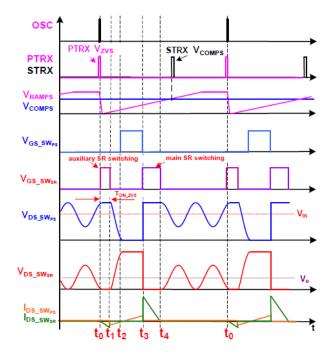

Fig. 8 illustrates the timing diagram of the proposed ZVS flyback converter. The auxiliary SR turn-on signal,  $V_{SR_ZVSP_{Tr}}$ , is triggered by the OSC in the PSC at the predetermined switching frequency and sent out from the PTRX to the STRX pin. After receiving this signal at the STRX pin, the SSC turns on SW<sub>SR</sub> with the programmable on-time,  $T_{ON_ZVS}$ , to create the negative current at the SS of the power transformer,  $I_{DS_SWSR}$ , from  $t_0$  to  $t_1$ . The magnitude of  $I_{DS_SWSR}$  is proportional to  $T_{ON_ZVS}$  and is set by the MCU based on the inductance of the power transformer, the parasitic capacitance at SW<sub>PS</sub>'s drain node,  $C_{OSS}$ , and the input and output voltage. When both SW<sub>PS</sub> and SW<sub>SR</sub> are off from  $t_1$  to  $t_2$ , the generated  $I_{DS_SWPS}$  discharges  $V_{DS}$  of SW<sub>PS</sub>,  $V_{DS_SWPS}$ , which is built by the charge stored in  $C_{OSS}$ , to achieve ZVS of SW<sub>PS</sub>.

When  $V_{DS_SWPS}$  detected at the DMAG pin of the PSC is lower than the set threshold, SW<sub>PS</sub> turns on at  $t_2$ . The on-time of SW<sub>PS</sub> is determined by the  $V_{COMPP}$  signal, which corresponds to  $V_{COMPS}$  in the SSC. SW<sub>SR</sub> turns on, while

Fig. 8. Timing diagram of the ZVS flyback converter.

SW<sub>PS</sub> turns off at  $t_3$ . When zero-current of SW<sub>SR</sub> is detected at the VTR pin, SW<sub>SR</sub> turns off at  $t_4$ .

For the heavy load condition of the power converter, the PSC and SSC enable the ZVS to improve the efficiency; for the light load condition, ZVS is disabled to achieve a standby power of lower than 30 mW.

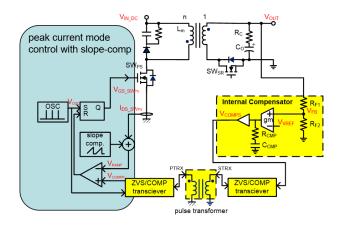

## C. Peak Current-Mode Control With Slope Compensation

Fig. 2 shows the circuit diagram of a conventional flyback converter with the optocoupler feedback. By the resistive divider comprising of  $R_{F1}$  and  $R_{F2}$ , the output voltage  $V_{OUT}$  is fed back to the error amplifier TL431. When  $V_{FB}$ , the resistive divider's voltage, is larger than the internal reference of TL431, the current of  $R_d$  would increase. Through the optocoupler, the current of the optocoupler's transistor would also increase to reduce  $V_{COMP}$ . By comparing  $V_{RAMP}$  and  $V_{COMP}$ , the duty cycle is determined. However, this method would need external components including TL431, resistors, and capacitors. Moreover, the optocoupler would have a larger delay time to deliver the signal. It would have a control accuracy issue.

The left portion of Fig. 9 illustrates the functional block diagram of the peak current mode control in the PSC. The current mode control is a dual loop control, which includes the outer voltage loop and the inner current loop. The outer voltage loop would sense the output voltage of the power stage and then generates the compensation signal through the ZVS/COMP transceiver and the pulse transformer to regulate the output voltage. The compensation signal from the outer voltage loop is compared with the current sensed by the inner current loop. From [18], a flyback converter with the peak current mode control is a two-pole two-zero system. To compensate the phase drop, an internal type II compensator is proposed to save external component counts. The so-called slope compensation

Fig. 9. Peak current mode control with slope compensation.

Fig. 10. IPPIC.

is used to improve current loop stability [19]. At the beginning of the  $V_{\text{GS}\_\text{SWPS}}$  duty cycle,  $V_{\text{OSC}}$  would be sent to the SR latch with a small delay. At this time,  $V_{\text{GS}\_\text{SWPS}}$  will be set to a high level to turn on the switch. Until  $V_{\text{CCMPP}}$  is larger than  $V_{\text{RAMP}}$ ,  $V_{\text{GS}\_\text{SWPS}}$  will be reset to a low level.

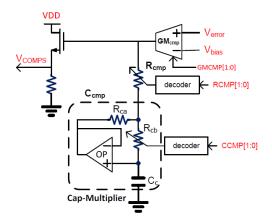

## D. IPPIC for SS Compensation

Fig. 10 shows the IPPIC circuit. In this IPPIC, the transconductance operational amplifier with  $R_{\rm cmp}$  and  $C_{\rm cmp}$  series at the output is used as a proportional-integral compensator. In the proposed SSR ZVS flyback converter design, because the PS uses the peak current mode control, the compensator only requires a type II OTA compensator, which provides one pole and one zero into the close loop transfer function of the system. The capacitance-multiplier circuit, which consists of  $R_{\rm ca}$ ,  $R_{\rm cb}$ , and a two-stage opamp with the common source amplifier, is used to reduce the capacitor's area.  $R_{\rm ca}$  is a 50k $\Omega$  resistor, while  $R_{\rm cb}$  is a resistor string formed by four resistors and controlled by a 2-bit register. Thus, the equivalent capacitance value,  $C_{\rm cmp}$ , is expressed as follows:

$$C_{\rm cmp} = \left(1 + \frac{R_{\rm cb}}{R_{\rm ca}}\right) C_{\rm C}.$$

(1)

With the cap-multiplier, the maximum capacitance could be 10 nF by 100\*100 pF. The parameters GM<sub>CMP</sub>,  $R_{CMP}$ ,

Fig. 11. (a) Internal CV/CC compensator circuit. (b) Error selector circuit.

and  $C_{\text{CMP}}$  in Fig. 10 could be programed by the MCU based on the different operating conditions of the converter. Therefore, the transfer function of  $V_{\text{error}}(s)$  to  $V_{\text{COMPS}}(s)$  in this IPPIC can be derived as

$$\frac{V_{\text{COMPS}}(s)}{V_{error}(s)} = \underbrace{gm \cdot R_{\text{cmp}}}_{\text{Proportional}} + \underbrace{\frac{gm}{C_{\text{cmp}}} \cdot \frac{1}{s}}_{\text{Integral}}.$$

(2)

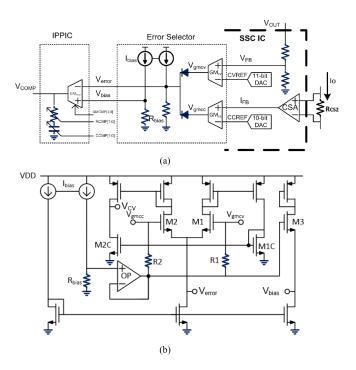

## E. Internal CV/CC Regulation Loop

To achieve accurately controlled output voltage and current for the fast-charging function of mobile devices, an internal CV/CC regulation loop is implemented. The top portion of Fig. 11(a) shows the internal CV/CC compensator circuit in the SSC. Two DACs with 11-bit and 10-bit resolution are used to set the reference voltage of the CV and CC loop, respectively. The feedback signal of the CV loop is sensed through a resistor divider from  $V_{OUT}$ , while the feedback signal of the CC loop is sensed through  $R_{CS2}$  in Fig. 3 to obtain  $I_0$  information. The dominated loop is selected by a diodelike circuit, error selector (ES). The IPPIC formed by the active gm-*RC* circuits is used to provide a proportional and an integral controller achieving high dc accuracy. Thus, the output voltage and output current can achieve 3–21 V with 20-mV resolution and 1–5 A with 50-mA resolution, respectively.

Fig. 11(b) shows the implementation of ES. The output currents of  $GM_{CV}$  and  $GM_{CC}$  flow into R2 and R1 to generate  $V_{gmcc}$  and  $V_{gmcv}$ , respectively. The differential pair composed of M1 and M2 forms a two diode like circuit. The error signal,  $V_{error}$ , is M1 and M2's source node. Thus, the differential pair compares the input CV and CC error signals,  $V_{gmcv}$  and  $V_{gmcc}$ . The larger one controls the output,  $V_{error}$ . M1C and M2C in companion with M1 and M2 form the output of the

Fig. 12. Conventional CV regulation loop.

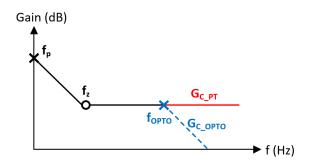

Fig. 13. Bode Plot of conventional type II compensator with optocoupler.

comparator,  $V_{CV}$ , which indicates the current dominated regulation loop is CV or CC loop.

#### F. Small-Signal Model

Fig. 12 shows the conventional CV regulation circuit. The optocoupler with the transfer gain, CTR, is usually used in the regulation loop for the isolation.

From the circuit in Fig. 12, the voltage gain from  $V_{\text{OUT}}$  to  $V_{\text{COMP}}$  ( $G_C$  OPTO) can be derived as

$$G_{C_{-}\text{OPTO}}(s) = \frac{V_{\text{COMP}}(s)}{V_{\text{OUT}}(s)}$$

$$= -\frac{CTR \cdot R_p}{R_a \cdot R_d} \cdot \frac{1}{sC_{\text{CMP}}} (1 + s(R_a + R_{\text{CMP}})C_{\text{CMP}})$$

$$\times \frac{1}{1 + sR_pC_{\text{OPTO}}}.$$

(3)

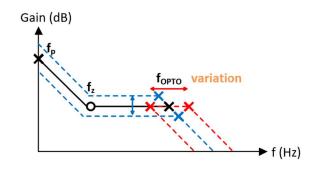

In (3),  $1/sC_{CMP}$  is the compensator's pole, and (1 +  $s(R_a + R_{\text{CMP}})C_{\text{CMP}})$  is the compensator's zero. Because of the parasitic capacitance  $C_{\text{OPTO}}$  of the optocoupler, the transfer function adds the extra parasitic pole at  $1/(1 + sR_PC_{OPTO})$ . Fig. 13 shows the Bode Plot of the conventional type II compensator with the optocoupler. COPTO increases as the current through the diode increases. Since this current may have some variation, the parasitic pole has a range and may limit the maximum bandwidth of the converter. In some applications, for example, while choosing PC817 as the optocoupler,  $C_{\text{OPTO}}$ would be up to 5 nF, and  $R_P$  might be 20 k $\Omega$  [2]. Thus, there would be an extra parasitic pole at 1.59 kHz, which would limit the loop bandwidth seriously. Moreover, the CTR has a large variation that causes the variation of the designed loop dc gain and bandwidth, resulting in possible stability issue as illustrated in (3).

Fig. 14. Proposed CV regulation loop and small-signal model.

Fig. 15. Comparison of compensator bode plots.

Fig. 14 shows the equivalent circuit model of the proposed CV regulation loop. Since the proposed SSR ZVS flyback converter replaces optocoupler by the pulse transformer, the optocoupler's parasitic pole does not appear in the loop gain. ZVS/COMP transceiver behavior can be modeled by a dc gain  $A_{\text{TRX}}$  and a zero-order-hold (ZOH) plus delay. Therefore, the transfer function from  $V_{\text{OUT}}$  to  $V_{\text{COMP}}$  with the pulse transformer ( $G_{C_PT}$ ) can be derived as

$$G_{C_PT}(s) = \frac{V_{\text{COMP}}(s)}{V_{\text{OUT}}(s)}$$

=  $-\frac{R_b}{R_a + R_b} \cdot A_{CV} \cdot GM_{\text{CMP}} \cdot A_{\text{TRX}}$

$\cdot \frac{1}{sC_{\text{CMP}}}(1 + sR_{\text{CMP}}C_{\text{CMP}}).$  (4)

Fig. 15 shows the comparison of the Bode Plot of the proposed compensator gain  $G_{C_PT}$  with  $G_{C_OPTO}$ . It can be seen that  $G_{C_OPTO}$  adds an extra parasitic pole at  $f_{OPTO}$ , which is proportional to  $1/(1 + sR_PC_{OPTO})$ . It reduces phase margin and the possibility to extend the control bandwidth of the loop gain.

For the proposed peak-current-mode control, the control-tooutput voltage gain  $G_{vc}(s)$  can be derived as (5) according to the model in [2]

$$G_{vc}(s) = A_{vc} \frac{\left(1 + \frac{s}{\omega_{\text{ESR}}}\right) \left(1 - \frac{s}{\omega_{RHP}}\right)}{\left(1 + \frac{s}{\omega_{P1}}\right) \left(1 + \frac{s}{\omega_{P2}}\right)}.$$

(5)

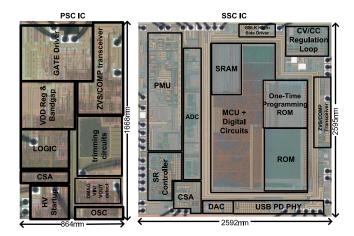

Fig. 16. Fabricated IC photograph of this work.

$G_{\rm vc}(s)$  is a system with two poles and two zeros. There is a dominant pole ( $\omega_{\rm P1}$ ) at low frequency, which relates mainly to load resistance when the other circuit parameters are kept constant. The other pole frequency ( $\omega_{\rm P2}$ ) is determined by the duty cycle and the switching frequency and is located at the high frequency. There is a left-half-plane zero ( $\omega_{\rm ESR}$ ), the location of which is only related to the characteristics of the output capacitor. The right-half-plane zero frequency ( $\omega_{\rm RHP}$ ) is determined by the switching frequency and the duty cycle. The equation of  $\omega_{\rm RHP}$  can be derived as  $\omega_{\rm RHP} = 2 f_S / D$  [2].

The CV loop gain of the system can be expressed as  $G_{\text{loop}}(s) = G_{vc}(s) \times G_{C_PT}(s)$ .  $G_{vc}(s)$  is the transfer function from  $V_{\text{comp}}$  to  $V_{\text{out}}$ , while  $G_{C_PT}(s)$  is the transfer function from  $V_{\text{out}}$  to  $V_{\text{comp}}$ . The multiplication of  $G_{vc}(s)$  and  $G_{C_PT}(s)$  forms the CV loop gain. The compensator's zero in  $G_{C_PT}(s)$  is used to cancel the power stage's dominant pole  $\omega_{\text{P1}}$  in  $G_{vc}(s)$ . By designing loop gain bandwidth smaller than  $\omega_{\text{RHP}}$ ,  $\omega_{\text{P2}}$ , and  $\omega_{\text{ESR}}$ , proper phase margin can be achieved [2]. Since  $G_{C_PT}(s)$  does not contain parasitic pole at  $f_{\text{OPTO}}$ , the loop gain bandwidth will not be limited by  $f_{\text{OPTO}}$ . Thus, the output voltage load transient response can be improved [5].

#### IV. EXPERIMENTAL VERIFICATION

Both the PSC and SSC IC are fabricated in an  $0.18-\mu m$  CMOS BCD process. Fig. 16 is the die photograph of these two ICs, and the chip areas are 1.44 and 6.73 mm<sup>2</sup>, respectively. The marked blocks can be mapped to Figs. 4 and 5.

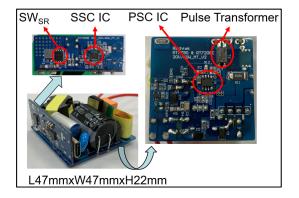

Fig. 17 is a fabricated adaptor with the proposed SSR ZVS flyback converter. Table I shows the key components value of the fabricated converter. The input voltage  $V_{in} = 90 \sim 265 \text{ V}_{ac}$ , output voltage  $V_{out} = 5 \sim 20 \text{ V}$ , maximum loading current  $I_{O_{MAX}} = 3 \text{ A}$ , so the maximum power of this converter is 60 W. Because this designed work does not need active-clamp circuits to achieve ZVS switching behavior, the total volume of the converter is only 48.598 cm<sup>3</sup>. The power density achieves 1.23 W/c.c (20 W/in<sup>3</sup>). Besides, the external components are muchly reduced as can be seen from the PS and SS printed-circuit-boards.

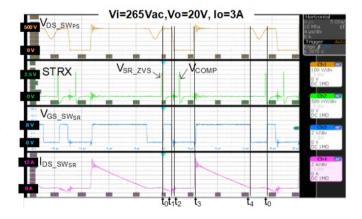

Fig. 18 shows the experimental result of the ZVS control under heavy load conditions. In STRX waveform,

Fig. 17. Fabricated adaptor with the proposed SSR ZVS flyback converter.

TABLE I Key Components Values of the Fabricated Converter

| Transformer       |                    |  |  |  |  |

|-------------------|--------------------|--|--|--|--|

| Core Size         | RM-8               |  |  |  |  |

| Material          | PC95               |  |  |  |  |

| Primary Inductor  | 210 $\mu$ H        |  |  |  |  |

| N <sub>P</sub>    | 30                 |  |  |  |  |

| Ns                | 5                  |  |  |  |  |

| Capacitors        |                    |  |  |  |  |

| C <sub>OUT</sub>  | 1.15 mF /25V       |  |  |  |  |

| C <sub>BULK</sub> | 100 µF /400V       |  |  |  |  |

| Resisters         |                    |  |  |  |  |

| R <sub>CS1</sub>  | 125 mΩ             |  |  |  |  |

| R <sub>CS2</sub>  | 5 mΩ               |  |  |  |  |

| Switches          |                    |  |  |  |  |

| SW <sub>PS</sub>  | IPA60R180P7, 180mΩ |  |  |  |  |

| SW <sub>sr</sub>  | BSC050N10NS5, 5mΩ  |  |  |  |  |

Fig. 18. Waveform of the ZVS control timing diagram (time scale:  $4 \mu$ s/div.).

$V_{\text{SR}_{ZVS}}$  represents the signal from PTRX through the pulse transformer at  $t_0$ . During  $t_0$  to  $t_1$ ,  $V_{\text{GS}_{SWSR}}$  would turn on to generate a negative current, which is shown in  $I_{\text{DS}_{SWSR}}$  waveform. After  $V_{\text{GS}_{SWSR}}$  turns off, the source–drain voltage of PS switch ( $V_{\text{DS}_{SWPS}}$ ) would drop down to zero at  $t_1$  to  $t_2$ . During  $t_2$  to  $t_3$ ,  $V_{\text{GS}_{SWPS}}$  turns on with zero-voltage switching behavior. At this time, the compensation signal is sent to PTRX through the pulse transformer for peak current

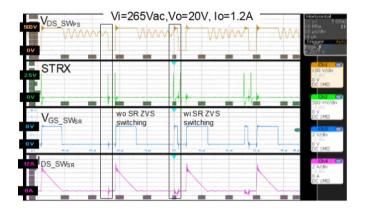

Fig. 19. Waveform ZVS control by auxiliary SR switching disabled at light-load (time scale:  $10 \ \mu s/div.$ ).

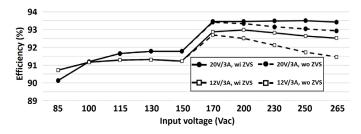

Fig. 20. Efficiency versus the input voltage.

mode control. During  $t_3$  to  $t_4$ ,  $V_{GS_SWSR}$  turns on for an SR. Finally,  $V_{GS_SWSR}$  turns off at  $t_4$  for DCM operation. Under the light load condition, the conduction loss and the switching loss caused by the negative current and auxiliary switching, respectively, for ZVS reduce the efficiency of the converter. Therefore, the ZVS control would be disabled when the output current is lower than 1.2 A. Fig. 19 shows the waveform with ZVS control by auxiliary SR switching disabled at light-load.

The efficiency versus the input voltage at 12- and 20-V fullload 3-A output with ZVS is shown in Fig. 20. The maximum efficiency of 93.5% is reached at 265  $V_{ac}/20$  V. The dotted line shows the efficiency when the proposed ZVS control by auxiliary SR switching is disabled. This indicates that this work provides a feasible way to improve the efficiency of the flyback converter with the Si-based power MOSFET. When the input voltage is higher than 170  $V_{ac}$ , the improvement of efficiency is about 1%. This is because PS switching loss increases with input voltage. At high input voltage conditions, ZVS behavior has significant improvement on efficiency. When the input voltage is lower than 170  $V_{ac}$ , the ZVS is disabled to reduce the payload of auxiliary SR switching, though the controller works at QR mode and still has high efficiency of more than 90%.

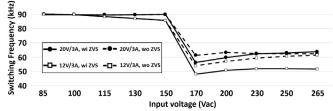

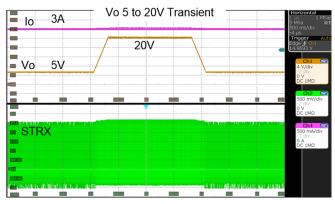

The frequency versus the input voltage at 12- and 20-V fullload 3-A output with ZVS is shown in Fig. 21. Fig. 22 shows reference voltage transient from 5 to 20 V for USB PD specifications. The output voltage can be regulated from 5 to 20 V when the output current is equal to 3 A. Besides, Table II shows the detailed experimental load regulations under

Fig. 21. Switching frequency versus the input voltage

Fig. 22. Reference voltage transient from 5 to 20 V at 3-A load current for USB PD specification (time scale: 500 ms/div.).

#### TABLE II

EXPERIMENTAL LOAD REGULATIONS UNDER DIFFERENT LOAD AND OUTPUT VOLTAGE

| Input       | Output  | Measured (V) |        |        | Load Regulation |

|-------------|---------|--------------|--------|--------|-----------------|

| Voltage     | Voltage | 0%           | 50%    | 100%   | Specification   |

| 90Vac/60Hz  | 5V      | 4.932        | 4.927  | 4.922  |                 |

| 265Vac/50Hz |         | 4.932        | 4.927  | 4.922  |                 |

| 90Vac/60Hz  | 9V      | 8.953        | 8.947  | 8.941  | Voir ± 5%       |

| 265Vac/50Hz |         | 8.953        | 8.946  | 8.940  |                 |

| 90Vac/60Hz  | - 15V   | 14.948       | 14.938 | 14.934 | VOUT 1 5%       |

| 265Vac/50Hz |         | 14.947       | 14.936 | 14.927 |                 |

| 90Vac/60Hz  | - 20V   | 19.961       | 19.944 | 19.942 |                 |

| 265Vac/50Hz |         | 19.960       | 19.939 | 19.928 |                 |

different load and output voltage. All the load regulations meet the specification of 5% error.

The experimental CV accuracies for various conditions are shown in Table II. With the test conditions of the universal input voltages, 0%/50%/100% of the full load currents, and the output voltage setting from 5 to 20 V, the measured output voltage error is less than 2.12%, which meets the load regulation specification.

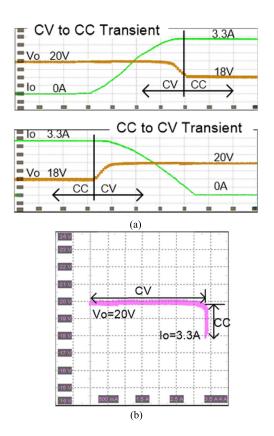

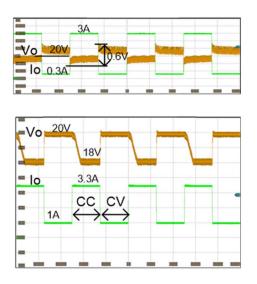

Fig. 23(a) shows the transient between CV and CC mode. The CC current threshold,  $I_{out\_cc\_set}$ , is 3.3 A. As load current is up to 3.3 A, the total system would enter CC mode. On the contrary, the system would enter CV mode when the output load is lower than 3 A. It can be seen that smooth mode

Fig. 23. CC/CV transient waveform. (a) CV-CC. (b) I-V curve.

Fig. 24. Dynamic load transient waveform. (a) Io < Iref. (b) Io > Ire.

transitions are achieved. The relationship between CC and CV is discussed in Fig. 23(b). It is obvious that the system would enter CC mode when the output load is closed to 3.3 A. Moreover, Fig. 24(a) illustrates the variation of output voltage when the output load is changed from 0.3 to 3 A. When the output load is changed from 1 to 3.3 A, the system would operate between CC mode and CV mode. As the waveform is shown in Fig. 24(b), the output voltage did not regulate after entering CC mode.

|                                        | This work               | innoSwitch3<br>[20] | APEC'18<br>[8]                     | TIA'17 [4]                | TIE'16<br>[13]   |

|----------------------------------------|-------------------------|---------------------|------------------------------------|---------------------------|------------------|

| Technology                             | 180nm BCD               | NR <sup>*</sup>     | NR                                 | NR                        | 0.35um BCD       |

| Topology                               | ZVS by SR               | QR                  | ACF                                | ZVS by SR                 | QR               |

| Power<br>MOSFET                        | Si                      | GaN                 | Si/GaN                             | Si                        | Si               |

| Number<br>of<br>primary-s<br>ideswitch | 1                       | 1                   | 2                                  | 1                         | 1                |

| Signal<br>Isolation                    | Magnetic                | Magnetic            | Optocoupler                        | Not need                  | Optocoupler      |

| IC Used<br>in<br>Converter             | PSC, SSC                | INN3379C-<br>H302   | UCC28780,<br>UCC27712,<br>UCC24612 | FPGA,<br>XMC4500<br>0 MCU | QR<br>controller |

| USB PD<br>Controller                   | Integrated              | External            | External                           | External                  | NR               |

| Regulation<br>Loops                    | Internal<br>CV/CC       | Internal<br>CV/CC   | External<br>CV                     | External<br>CV            | Internal<br>CV   |

| Max.<br>Power                          | 60W                     | 60W                 | 30W                                | 65W                       | 40W              |

| Power<br>Density                       | 1.132W/c.c              | 1.256W/c.c          | 1.83W/c.c                          | 0.885W/c.c                | NR               |

| Lm                                     | 210uH                   | 515uH               | 85uH                               | 77uH                      | 400uH            |

| Max.<br>Frequency                      | 90.01kHz                | 77.35kHz            | 180kHz                             | 270kHz                    | NR               |

| Input<br>Voltage                       | 85-265Vac               | 85-265Vac           | 70-320Vac                          | 120-230Vac                | 90-264Vac        |

| Max.<br>Output<br>V/I                  | 20V/3A                  | 20V/3A              | 20V/1.5A                           | 20V/3A                    | 14V/2.85A        |

| Max.<br>Efficiency                     | 93.5%                   | 93.8%               | Si: 93.5%;<br>GaN:95.8%            | 85%                       | 89.1%            |

| Die Size<br>[mm <sup>2</sup> ]         | PSC: 1.44,<br>SSC: 6.73 | NR                  | NR                                 | NR                        | 2.2              |

NR\*: Not reported.

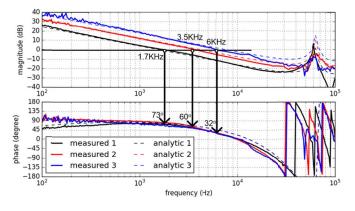

Fig. 25 illustrates the comparison between the smallsignal model and the measurement result of CV loop gains. With three different compensator designs, the crossover frequency would vary from 1.7 to 6 kHz. In these cases, the phase margins also vary from 72° to 32°. The small-signal model is almost fit with the experimental result. With this model, the phase margin of the loop gain can be determined precisely.

Table III summarizes the performance of this work and compares it with the prior-art designs. Not like the previous work [7], which integrates the primary power switch in one package [20], our solution uses an external Si power switch to get freedom on the power switch selection for different performance and cost requirements. Moreover, the thermal of the power switch can be better because it has its own package and can be positioned on the PCB freely without bundling the PSC IC. The efficiency of the designed SSR ZVS flyback converter with the proposed two ICs and Si power MOSFET for USB PD PPS applications is competitive with the published works with GaN switch or active clamped flyback (ACF) topology. Thus, the proposed ICs achieve similar high efficiency with lower cost because only one Si MOSFET PS switch is required. Reference [7], [20] uses GaN with the valley switching which does not achieve ZVS. Liu [8] uses

TABLE III Comparison Table

Fig. 25. Loop gain bode plot of CV mode.

ACF to achieve ZVS but with the cost of extra high side driver and GaN switch. The proposed solution is the optimization of cost and power efficiency. Even with lower cost, similar power density can be achieved with the comparison with other work. Furthermore, the proposed converter has fewer external components and a higher integration level by integrating the USB PD controller, internal CC/CV, and compensation components. The optocoupler for isolation is also replaced by a pulse transformer.

## V. CONCLUSION

A high-efficiency ZVS flyback converter is proposed with two control ICs for USB PD applications. The control replaces the optocoupler with a pulse transformer to transmit the SS-regulation signal to fulfill USB PD PPS for fast-charging mobile devices. ZVS signal for SR is also transmitted through the same pulse transformer to improve efficiency. The proposed two ICs are fabricated in 180-nm BCD process with chip areas of 1.44 and 6.73 mm<sup>2</sup>, respectively. The highly integrated ICs reduce the external components. The implemented 20-V/3-A/60-W USB PD flyback converter achieved 93.5% maximum efficiency using only Si power switches. The converter power density is 20 W/in<sup>3</sup>. The proposed ZVS control behavior is verified by the measured time waveform. A thorough test of USB PD specifications proves the feasibility of the proposed solution. The PPS test with various CC/CV levels show accurate SS regulations and smooth transitions between CC and CV modes.

#### REFERENCES

- USB Implementation Forum. (Jun. 2018). Universal Serial Bus Power Delivery Specifications. Rev. 3.0, Version 1.2. Accessed Nov. 29, 2019. [Online]. Available: https://www.usb.org/sites/default/files/USB% 20Power%20Delivery.zip

- [2] C.-J. Chen, C.-H. Cheng, P.-S. Wu, and S.-S. Wang, "Unified smallsignal model and compensator design of flyback converter with peakcurrent control at variable frequency for USB power delivery," *IEEE Trans. Power Electron.*, vol. 34, no. 1, pp. 783–793, Jan. 2019.

- [3] F. He, "USB port and power delivery: An overview of USB port interoperabiliy," in *Proc. IEEE Symp. Product Compliance Eng. (ISPCE)*, May 2015, pp. 1–5.

- [4] A. Connaughton, A. P. Talei, K. K. Leong, K. Krischan, and A. Muetze, "Investigation of a soft-switching flyback converter with full secondary side-based control," *IEEE Trans. Ind. Appl.*, vol. 53, no. 6, pp. 5587–5601, Nov. 2017.

- [5] C.-H. Cheng, C.-J. Chen, and S.-S. Wang, "An adaptive variablefrequency control with constant crossover frequency achieving fast transient response for Wide-Operation-Range flyback converter," *IEEE Trans. Power Electron.*, vol. 34, no. 6, pp. 5537–5548, Jun. 2019.

- [6] C.-H. Cheng, C.-J. Chen, and S.-S. Wang, "Small-signal model of flyback converter in continuous-conduction mode with peak-current control at variable switching frequency," *IEEE Trans. Power Electron.*, vol. 33, no. 5, pp. 4145–4156, May 2018.

- [7] Power Integration. (Jul. 2019). InnoSwitchTM 3-Pro Family. Datasheet, Rev. G. Accessed: Nov. 29, 2019. [Online]. Available: https://acdc. power.com/products/innoswitchfamily/]innoswitch3pro/?language=en

- [8] P.-H. Liu, "Design consideration of active clamp flyback converter with highly nonlinear junction capacitance," in *Proc. IEEE Appl. Power Electron. Conf. Expo. (APEC)*, Mar. 2018, pp. 783–790.

- [9] L. Xue and J. Zhang, "High efficient secondary-resonant active clamp flyback converter," *IEEE Trans. Ind. Electron.*, vol. 65, no. 2, pp. 767–770, Feb. 2018.

- [10] J. Zhang, X. Huang, X. Wu, and Z. Qian, "A high efficiency flyback converter with new active clamp technique," *IEEE Trans. Power Electron.*, vol. 25, no. 7, pp. 1775–1785, Jul. 2010.

- [11] X. Huang, W. Du, W. Yuan, J. Zhang, and Z. Qian, "A novel variable frequency soft switching method for flyback converter with synchronous rectifier," in *Proc. 25th Annu. IEEE Appl. Power Electron. Conf. Expo.* (APEC), Feb. 2010, pp. 1392–1396.

- [12] Y.-C. Kang, C.-C. Chiu, M. Lin, C.-P. Yeh, J.-M. Lin, and K.-H. Chen, "Quasiresonant control with a dynamic frequency selector and constant current startup technique for 92% peak efficiency and 85% light-load efficiency flyback converter," *IEEE Trans. Power Electron.*, vol. 29, no. 9, pp. 4959–4969, Sep. 2014.

- [13] J. Park et al., "Quasi-resonant (QR) controller with adaptive switching frequency reduction scheme for flyback converter," *IEEE Trans. Ind. Electron.*, vol. 63, no. 6, pp. 3581–3751, Jun. 2016.

- [14] Texas Instruments. (2014). Constant-Voltage Constant-Current Flyback Controller Using Opto-Coupled Feedback, UCC28740 Datasheet. Texas Instruments Document. [Online]. Available: http://www.ti.com/

- [15] (2012). Highly Integrated Green-Mode PWM Controller: FAN6862 Datasheet, Fairchild Semiconductor Corporation. [Online]. Available: http://www.fairchildsemi.com/

- [16] (2014). Green-Mode PWM Controller with Latch off Protections: LD7532 Datasheet, Leadtrend Technology. [Online]. Available: http://www.leadtrend.com.tw/

- [17] (2014). Constant-Voltage Constant-Current Flyback Controller using Opto-Coupled Feedback: UCC28740 Datasheet, Texas Instruments, 2014. [Online]. Available: http://www.ti.com/

- [18] W. Kleebchampee and C. Bunlaksananusorn, "Modeling and control design of a current-mode controlled flyback converter with optocoupler feedback," in *Proc. Int. Conf. Power Electron. Drives Syst.*, Nov. 2005, pp. 787–792.

- [19] H. M. Pang and P. M. H. Bryan, "A stability issue with current mode control flyback converter driving LEDs," in *Proc. IEEE 6th Int. Power Electron. Motion Control Conf.*, May 2009, pp. 1402–1406.

- [20] Power Integration. (Jul. 2019). 60W USB PD 3.0 Power Supply With 3.3V-21V PPS Output Using InnoswitchTM3-Pro GaN-Based INN3379C-H302 and VIA Labs VP302. Design Example Report. Accessed: Nov. 29, 2019. [Online]. Available: https://ac-dc.power.com/ design-support/reference-designs/design-examples/der-803-60watt-usbpd-3-pps-power-supply-using-innoswitch3-pro/?language=zh-hant

Wei-Hsu Chang was born in Taiwan in 1973. He received the B.S. and Ph.D. degree in electronics engineering from National Chiao-Tung University, Hsinchu, Taiwan, in 1996 and 2004, respectively.

From 2000 to 2003, he was a Visiting Scholar at the Microsensor and Actuator Technology of TU-Berlin, Berlin, Germany. In 2005, he joined Richtek Technology Corporation, Hsinchu, and serves as the Deputy of Technical RD Director of the AC–DC Business Unit. He focuses himself on the de–dc and ac–dc power management and motor control-related IC design.

Yen-Ming Chen was born in Taipei, Taiwan. He received the B.S. degree in electronics engineering from National Chiao Tung University, Hsinchu, Taiwan, in 2018. He is currently pursuing the Ph.D. degree with the Institute of Electrical Engineering, National Taiwan University, Taipei.

He is a member of the Power Electronics Laboratory, National Taiwan University. His research interests include the power management IC design and mixed-signal IC design.

**Chun-Ching Lee** received the B.S. and M.S. degrees in electrical engineering and computer science from National Taiwan University, Taipei, Taiwan, in 2001 and 2003, respectively.

In 2003, he joined Fairchild Semiconductor, Hsinchu, Taiwan, as an Analog IC Design Engineer. Since 2013, he has been with Richtek Technology Corporation, Hsinchu, Taiwan, as the Deputy Technical Manager at the AC–DC Business Unit. His research interests include the power management integrated circuits and the high-voltage high-

frequency ac-dc converters' IC design.

**Ching-Jan Chen** (Senior Member, IEEE) received the B.S. and Ph.D. degrees in electrical engineering from National Taiwan University, Taipei, Taiwan, in 2006 and 2011, respectively.

From 2010 to 2011, he was a Visiting Scholar at the Center of Power Electronic Systems (CPES), Virginia Tech., Blacksburg, VA, USA. From 2011 to 2015, he was a Senior Engineer with the IC Research and Development Department, Richtek Technology Corporation, Hsinchu, Taiwan. His work was focused on new control scheme development and IC

design of the voltage regulator controller for CPU power. In February 2015, he became an Assistant Professor with the Department of Electrical Engineering, National Taiwan University (NTU), where he is currently an Associate Professor. His research interests include modeling and control of dc–dc and ac–dc power converters, power conversion for CPU and mobile devices, and power IC design.

Dr. Chen was a recipient of the Young Researcher Award from the Ministry of Science and Technology, Taiwan, in 2016, the Outstanding Teaching Awards from NTU in 2020, and the Research Contribution Award from NTU EECS in 2020. He served as the session chair, topic chair, and financial chair in several IEEE conferences and competitions, such as ECCE, ECCE-Asia, International Future Energy Challenge (IFEC), IFEEC, WiPDA Asia, ITEC-Asia Pacific, and VLSI-DAT. He was the Secretary and then the Vice-Chair of the IEEE PELS Taipei Chapter from 2018 to 2020 and received the IEEE PELS Best Chapter Award in 2018.

**Li-Di Lo** was born in Taiwan. He received the B.S. degree in electronic engineering and the M.S. degree in electronic and information engineering from National Yunlin Technology University, Yunlin, Taiwan, in 2000 and 2003, respectively.

In 2008, he joined Richtek Technology Corporation, Hsinchu, Taiwan. He is a Technical Manager of the power electronic IC design at the AC–DC Business Unit. His research interest includes the development of the low power-loss and high-efficiency power converters.

Jenn-Yu G. Lin received the B.S. degree from National Cheng Kung University, Tainan, Taiwan, in 1986, the M.S. degree from Columbia University, New York, NY, USA, in 1990, and the Ph.D. degree from the Georgia Institute of Technology, Atlanta, GA, USA, in 1995, all in electrical engineering.

From 1986 to 1988, he served in the Taiwan Navy as an Ensign Officer. From 1988 to 1989, he was a Process Development Engineer with UMC, Hsinchu, Taiwan. From 1994 to 1997, he was a Senior Circuit Design Engineer with Texas Instruments, Dallas,

TX, USA. From 1998 to 2013, he was with System General Corporation, Hsinchu, and Fairchild Semiconductor, Hsinchu, where he was involved in power supply IC designs. From 2014 to 2016, he was with Voltafield Technology, Hsinchu, for geomagnetic sensor chip developments. Since 2016, he has been with Richtek Technology Corporation, Hsinchu, for power supply IC developments. He is the inventor of more than 60 U.S. patents.

**Pin-Ying Wang** received the B.S. degree in electronic and computer engineering from the National Taiwan University of Science and Technology, Taipei, Taiwan, in 2018. He is currently pursuing the M.S. degree in electrical engineering with National Taiwan University, Taipei.

His work focused on GaN-based dc-dc converters and IC design of GaN driver. His research interests include power electronics, dc-dc power converters and control, and power IC design.

**Kun-Yu Lin** was born in Pingtung, Taiwan. He received the B.S. degree in electrical engineering from National Chung Cheng University, Chiayi, Taiwan, in 2006, and the M.S. degree in electrical engineering from National Taiwan University, Taipei, Taiwan, in 2008.

Since 2008, he has been with Richtek Technology Corporation, Hsinchu, Taiwan, and serves as the Deputy Manager at the AC–DC Business Unit. His research interests include power management and power-integrated circuits.

**Ta-Yung Yang** received the B.S. degree in electronic engineering from the National Taiwan University of Science and Technology, Taipei, Taiwan, in 1983.

From 1985 to 2007, he was a CEO of System General Corporation, Hsinchu, Taiwan. From 2008 to 2013, he was with SVP technology of Fairchild Semiconductor, Hsinchu. Since 2014, he has been a CTO of Richtek Technology Corporation, Hsinchu, Taiwan. He holds more than 200 U.S. patents. His research interests include power electronics, power conversion, and motor control.