# A CMOS Dual-Polarized Phased-Array Beamformer Utilizing Cross-Polarization Leakage Cancellation for 5G MIMO Systems

Jian Pang<sup>®</sup>, Member, IEEE, Zheng Li, Graduate Student Member, IEEE, Xueting Luo,

Joshua Alvin, Student Member, IEEE, Rattanan Saengchan, Ashbir Aviat Fadila, Kiyoshi Yanagisawa,

Yi Zhang, Student Member, IEEE, Zixin Chen, Zhongliang Huang, Xiaofan Gu, Rui Wu<sup>®</sup>, Member, IEEE,

Yun Wang<sup>®</sup>, Member, IEEE, Dongwon You, Student Member, IEEE, Bangan Liu<sup>®</sup>, Member, IEEE,

Zheng Sun<sup>D</sup>, Graduate Student Member, IEEE, Yuncheng Zhang<sup>D</sup>, Graduate Student Member, IEEE,

Hongye Huang<sup>®</sup>, Graduate Student Member, IEEE, Naoki Oshima<sup>®</sup>, Member, IEEE,

Keiichi Motoi, Member, IEEE, Shinichi Hori, Member, IEEE, Kazuaki Kunihiro<sup>®</sup>, Member, IEEE,

Tomoya Kaneko, Member, IEEE, Atsushi Shirane, Member, IEEE,

and Kenichi Okada<sup>10</sup>, Senior Member, IEEE

Abstract-This article introduces a power-efficient and lowcost CMOS 28-GHz phased-array beamformer supporting fifthgeneration (5G) dual-polarized multiple-in-multiple-out (MIMO) (DP-MIMO) operation. To improve the cross-polarization (crosspol.) isolation degraded by the antennas and propagation, a power-efficient analog-assisted cross-pol. leakage cancellation technique is implemented. After the high-accuracy cancellation, more than 41.3-dB cross-pol. isolation is maintained along with the transmitter array to the receiver array. The element-beamformer in this work adopts the compact neutralized bi-directional architecture featuring a minimized manufacturing cost. The proposed beamformer achieves 22% per path TX-mode efficiency and a 4.9-dB RX-mode noise figure. The required onchip area for the beamformer is only 0.48 mm<sup>2</sup>. In over-the-air measurement, a 64-element dual-polarized phased-array module achieves 52.2-dBm saturated effective isotropic radiated power (EIRP). The 5G standard-compliant OFDMA-mode modulated signals of up to 256-QAM could be supported by the 64-element modules. With the help of the cross-pol. leakage cancellation technique, the proposed array module realizes improved DP-MIMO EVMs even under severe polarization coupling and rotation conditions. The measured DP-MIMO EVMs are 3.4%

Manuscript received August 16, 2020; revised November 4, 2020; accepted December 7, 2020. Date of publication January 6, 2021; date of current version March 26, 2021. This article was approved by Associate Editor Brian Ginsburg. This work was supported in part by the Ministry of Internal Affairs and Communications in Japan under Grant JPJ000254, in part by JSPS, in part by STAR, and in part by VDEC in collaboration with Cadence Design Systems, Inc., in part by Mentor Graphics, Inc., and in part by Keysight Technologies Japan, Ltd. (*Corresponding author: Jian Pang.*)

Jian Pang, Zheng Li, Xueting Luo, Joshua Alvin, Rattanan Saengchan, Ashbir Aviat Fadila, Kiyoshi Yanagisawa, Yi Zhang, Zixin Chen, Zhongliang Huang, Xiaofan Gu, Rui Wu, Yun Wang, Dongwon You, Bangan Liu, Zheng Sun, Yuncheng Zhang, Hongye Huang, Atsushi Shirane, and Kenichi Okada are with the Tokyo Institute of Technology, Tokyo 152-8552, Japan (e-mail: pangjian@ssc.pe.titech.ac.jp).

Naoki Oshima, Keiichi Motoi, Shinichi Hori, Kazuaki Kunihiro, and Tomoya Kaneko are with NEC Corporation, Kawasaki 211-8666, Japan.

Color versions of one or more figures in this article are available at https://doi.org/10.1109/JSSC.2020.3045258.

Digital Object Identifier 10.1109/JSSC.2020.3045258

in both 64-QAM and 256-QAM. The consumed power per beamformer path is 186 mW in the TX mode and 88 mW in the RX mode.

*Index Terms*—28 GHz, bi-directional, cancellation, CMOS, cross-polarization (cross-pol.) leakage, dual-polarized multiplein-multiple-out (DP-MIMO), fifth-generation mobile network, neutralization, phased array.

## I. INTRODUCTION

**MERGING** technologies are being developed to improve the wireless throughput in the fifth-generation (5G) mobile network enhanced mobile broadband (eMBB). High-performance and large-scaled millimeter-wave phased-array transceivers have been introduced and researched for delivering wideband data streams over long communication distance [1]–[18]. Further improvement on wireless data rate can be provided by the usage of multiple-in-multiple-out (MIMO) technique, while high power efficiency and low manufacturing cost features are required to be maintained for such 5G millimeter-wave MIMO systems.

Dual-polarized MIMO (DP-MIMO) transceivers are capable of transmitting two independent data streams simultaneously through the H-polarized (H-pol.) and V-polarized (V-pol.) waves. Spatial diversity is offered by the cross-polarization (cross-pol.) isolation of the dual-polarized antennas. In recent years, special attention have been focused on realizing low-cost and power-efficient 5G millimeter-wave DP-MIMO systems [6]–[11], [19]. Pang *et al.* [6] introduce an eight-element beamformer chip for 5G single-user DP-MIMO communications. The area-efficient bi-directional technique is utilized for minimizing the manufacturing cost. However, the performance of such a DP-MIMO transceiver is sensitive to the cross-pol. coupling from the antennas and the polarization rotation during propagation [20], [21]. Therefore, the achievable DP-MIMO EVMs and power efficiencies are limited.

This work is licensed under a Creative Commons Attribution 4.0 License. For more information, see https://creativecommons.org/licenses/by/4.0/

Kibaroglu *et al.* [7] and Nafe *et al.* [8] introduce a feed rotation technique to provide additional cross-pol. isolations between H-pol. and V-pol. signals, while the achieved isolation is direction-selective and still sensitive to the polarization coupling caused by the module placement and propagation.

To realize high-efficiency and low-cost 5G millimeter-wave DP-MIMO systems, this work introduces a 28-GHz CMOS phased-array beamformer chip. A cross-pol. leakage cancellation technique is implemented for improving the degraded cross-pol. isolation. The cross-pol. leakages are suppressed to lower than -40 dB along with the transmitter array to the receiver array after the cancellation. The consumed power for the canceller is 20 mW. This work also adopts the neutralized bi-directional architecture and power-efficient design to minimize the manufacturing cost and power dissipation. Over 22% maximum TX-mode efficiency and 4.9-dB RX-mode noise figure (NF) are obtained by each element-beamformer. The occupied area for each beamformer is only  $0.48 \text{ mm}^2$ . Due to the proposed cancellation technique, the 64H + 64Varray modules in this work can support 5G new radio (NR) standard-compliant DP-MIMO communication even under severe cross-pol. leakage conditions. The achieved TX-to-RX DP-MIMO EVMs are both 3.4% in 64-QAM and 256-QAM.

This article, which is an extension to [22], is organized as follows. A detailed analysis of the DP-MIMO capacity is provided in Section II. The specific requirements for the proposed cancellation circuits are also included in this section. Section III demonstrates the circuit implementations for the power-efficient canceller and the bi-directional beamformer. Section IV presents the results for the on-wafer measurement and the over-the-air (OTA) measurement. Finally, the conclusion is drawn in Section V.

### II. MILLIMETER-WAVE DP-MIMO COMMUNICATIONS

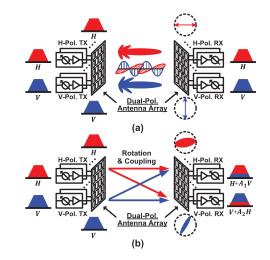

As demonstrated in Fig. 1(a), 5G millimeter-wave DP-MIMO systems utilize the cross-pol. isolation between H-pol. and V-pol. to simultaneously transmit two data streams. To evaluate the performance of DP-MIMO systems, the channel capacity under  $2 \times 2$  DP-MIMO configuration could be represented with (1) [23], [24]

$$C = B \log_2 \left[ \det \left( I + \frac{\gamma_0}{n} H^{\mathrm{H}} H \right) \right]$$

(1)

where *B* is the channel bandwidth and  $\gamma_0$  is the signal-to-noise ratio (SNR). n = 2 is selected here to keep the total transmitted power constant in DP-MIMO. The channel information is included in the 2 × 2 channel matrix *H*. For ideal line-of-sight (LOS) DP-MIMO operation, the H-pol. and V-pol. signals are completely isolated. Therefore, the channel matrix *H*<sub>ideal</sub> could be represented as follows:

$$\boldsymbol{H}_{\text{ideal}} = \begin{bmatrix} e^{j\varphi_{11}} & 0\\ 0 & e^{j\varphi_{22}} \end{bmatrix}$$

(2)

Fig. 1. (a) Ideal DP-MIMO operation. (b) DP-MIMO operation with rotation and coupling during propagation.

where  $\varphi_{11}$ , and  $\varphi_{22}$  denote the phase shifting caused by propagation. Considering a communication distance of d,  $\varphi_{11}$  and  $\varphi_{22}$  could be derived with  $2\pi (d/\lambda)$ . By applying  $H_{\text{ideal}}$  to (1), the ideal DP-MIMO channel capacity could be calculated with the following equation:

$$C_{\text{ideal}} = B \log_2 \left( 1 + \frac{\gamma_0}{2} \right)^2. \tag{3}$$

From (3), we can find that the channel capacity is significantly boosted by the usage of DP-MIMO in ideal condition, while, in real case, the arise of cross-pol. leakage will always limit the achievable DP-MIMO capacity. As shown in Fig. 1(b), both the coupling from the antenna and the polarization rotation due to module placement can generate such kind of leakages. To explore their influence to channel capacity, the channel matrix  $H_{\text{leak}}$  under leakage condition could be represented as follows:

$$\boldsymbol{H}_{\text{leak}} = \begin{bmatrix} \sqrt{1 - \alpha} e^{j\varphi_{11}} & \sqrt{\beta} e^{j\varphi_{21}} \\ \sqrt{\alpha} e^{j\varphi_{12}} & \sqrt{1 - \beta} e^{j\varphi_{22}} \end{bmatrix}.$$

(4)

$\sqrt{\alpha}$  and  $\sqrt{\beta}$  are the magnitudes of the cross-pol. leakage components, where  $0 \le \alpha \le 1$  and  $0 \le \beta \le 1$ . The phases of the leakages are denoted with  $\varphi_{12}$  and  $\varphi_{21}$ . The corresponding channel capacity  $C_{\text{leak}}$  could be derived by applying  $H_{\text{leak}}$  to (1). The calculated result is shown in (5) (shown in the bottom). If we assume that  $\alpha = \beta = A$  and  $\varphi_{21} - \varphi_{11} = \varphi_{12} - \varphi_{22} = \varphi$ , the channel capacity under leakage condition could be further simplified with the following equation:

$$C'_{\text{leak}} = B \log_2 \left[ \left( 1 + \frac{\gamma_0}{2} \right)^2 - \frac{\gamma_0}{2} A (1 - A) (\cos 2\varphi + 1) \right].$$

(6)

From (6), we can find the first term inside the brackets of  $C'_{\text{leak}}$  is the same with the one inside  $C_{\text{ideal}}$ , while the second term, which is always negative, represents the capacity degradation

$$C_{\text{leak}} = B \log_2 \left[ \left( 1 + \frac{\gamma_0}{2} \right)^2 - \frac{\gamma_0^2}{4} (\alpha + \beta - 2\alpha\beta + 2\sqrt{\alpha\beta(1 - \alpha)(1 - \beta)} \cos(\varphi_{12} + \varphi_{21} - \varphi_{11} - \varphi_{22}) \right]$$

(5)

50

40

30

20

10

0

-10

0.0

)P-MIMO C

0.1

Required SNR / TX Pout [dB/dBm] Required SNR

TX Pout per Path

TX Efficiency per Pa

5Gb/s

(a)

0.3

0.4

0.2

15%

10%

5%

0%

0.5

TX Efficiency per Path

$\varphi_0 = 0$

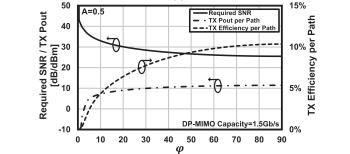

Fig. 2. Calculated required SNR, available TX output power, and TX efficiency against (a) A and (b)  $\varphi_0$ .

(b)

caused by the cross-pol. leakages. The worst condition is obtained when A = 0.5 and  $\varphi = 0^{\circ}$ . The corresponding channel capacity  $C''_{\text{leak}}$  could be represented with (7), which is the channel capacity for single-in-single-out (SISO) scenario

$$C_{\text{leak}}'' = B\log_2(1+\gamma_0). \tag{7}$$

To compensate for the degradation caused by the crosspol. leakage, the channel SNR  $\gamma_0$  is required to be improved. Fig. 2(a) and (b) demonstrates the required  $\gamma_0$  against *A* and  $\varphi$ , respectively. The DP-MIMO capacity is fixed with 1.5 Gb/s in this calculation, and the channel bandwidth is 100 MHz. In 5G millimeter-wave transceivers, the channel SNR  $\gamma_0$  is usually dominated by the transmitter side. Additional power back-off (PBO) will be required in the transmitter for improving  $\gamma_0$ . Thus, the system power efficiency will be, in turn, degraded. An example of explaining efficiency degradation is also presented in Fig. 2.

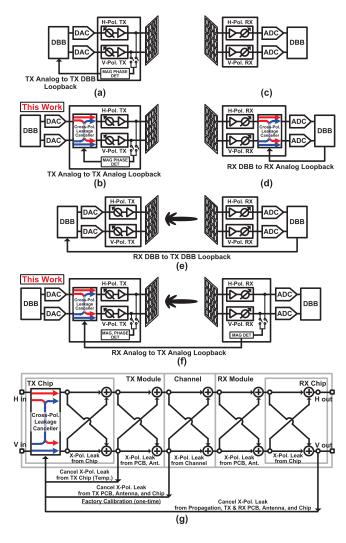

As shown in Fig. 3(c) and (d), conventional 5G MIMO operation usually relies on the receiver digital baseband (DBB) or an analog-domain leakage cancellation. However, the channel capacity cannot be recovered regarding severely coupled MIMO channels. In DP-MIMO, this situation becomes even worse because the H-pol. and V-pol. streams usually come from the same directions. In this condition, the transmitter EVM is required to be further improved, which leads to larger PBO and lower power efficiency as mentioned previously. To improve the DP-MIMO capacity without sacrificing power efficiency, the cross-pol. leakage cancellation is required to be performed at the transmitter Side. This function could be realized at the transmitter DBB, as shown in Fig. 3(a) and (e). However, the digital processing regarding multi-Gb/s

Fig. 3. Cross-pol. leakage cancellations with (a) TX analog-to-TX DBB loopback, (b) TX analog-to-TX analog loopback, (c) RX DBB, (d) RX DBB-to-RX analog loopback, (e) RX DBB-to-TX DBB loopback, and (f) RX analogto-TX analog loopback. (g) Signal flowchart for the proposed cancellation technique.

data rate in 5G is power-hungry. A further improvement will also be required for the digital-to-analog converters (DACs) to support accurate cancellation, which is power-consuming. Therefore, a power-efficient analog-assisted cross-pol. leakage cancellation technique is introduced in this work. Fig. 3(b) shows the operation of the proposed technique. A cross-pol. leakage canceller is utilized for generating the cancellation signals. Fig. 3(g) shows the signal flowchart of the proposed cancellation. The settings of the canceller could be initially decided by a one-time factory calibration. During the transmitter operation, a magnitude and phase loopback calibration could be performed to compensate for the temperature variation. Regarding severely coupled DP-MIMO channels, a receiver-to-transmitter loopback cancellation, similar to precoding, could be further performed, as shown in Fig. 3(f). If the latency requirement is relaxed, the strength of the leakage signals could be detected at the receiver side and sent back to the transmitter for this cancellation. The cross-pol.

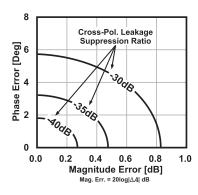

Fig. 4. Calculated cross-pol. leakage suppression ratio against  $\Delta A$  and  $\Delta \varphi$ .

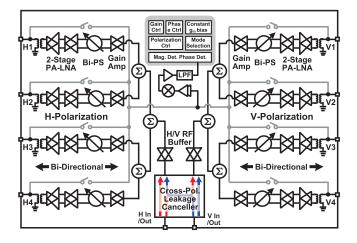

Fig. 5. Block diagram of the proposed bi-directional phased-array beamformer chip with cross-pol. leakage cancellation.

leakages introduced from the transmitter to the receiver could be canceled by the proposed cancellation technique in this condition.

The proposed canceller is designed based on the vector modulator. Regarding a leakage component  $A_L e^{j\varphi_L}$ , the achievable suppression ratio with a cancellation signal  $A_C e^{j\varphi_C}$  could be calculated with the following equation:

Leakage Supp.

$$= \frac{|A_L e^{j\varphi_L}|}{|A_L e^{j\varphi_L} + A_C e^{j\varphi_C}|}$$

$$= 20 \log \frac{1}{\sqrt{\Delta A^2 + 2\Delta A \cos \Delta \varphi + 1}} (\text{dB}) (8)$$

where  $\Delta A = \frac{A_C}{A_L}$  is the magnitude error and  $\Delta \varphi = \varphi_C - \varphi_L$  is the phase error. Fig. 4 presents the calculated suppression ratio against the corresponding  $\Delta A$  and  $\Delta \varphi$ . To maintain over 40-dB cross-pol. leakage suppression ratio,  $\Delta A$  should be less than 0.3 dB, and  $\Delta \varphi$  should be less than 1.8°. The proposed canceller is, therefore, designed with fine-grained phase tuning and magnitude tuning for a high-accuracy and fast cancellation.

### **III. CIRCUIT IMPLEMENTATION**

Fig. 5 shows the block diagram of the proposed 28-GHz beamformer chip. Area-efficient neutralized

bi-directional architecture is employed to share the same signal chain between the TX and RX [6]. Totally eight element-beamformers (4H + 4V) are integrated to support the DP-MIMO. In this work, the magnitude and phase-detection circuits along with on-chip coupling networks are implemented to the chip [12]. The output signals from each element-transmitter could be selected and distributed to the on-chip detection block through the coupling network. The signals will be down-converted to a much lower frequency for accurate detections. A cross-pol. leakage canceller mentioned in the previous section is also inserted at the H/V combining port for suppressing the cross-pol. leakage introduced from the polarization coupling and rotation. Low-cost, power-efficient, and high-performance 5G DP-MIMO systems could be maintained by this work. The detailed circuit implementation of the proposed beamformer chip will be introduced in the remaining part of this section.

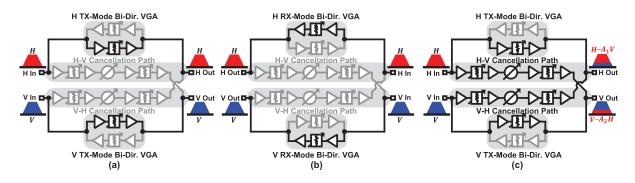

## A. Cross-Pol. Leakage Canceller

To improve the DP-MIMO EVMs and the corresponding system power efficiency, a high-accuracy cross-pol. leakage cancellation circuit is introduced in this work. Fig. 6 shows the block diagram of the proposed cross-pol. leakage canceller. It consists of two bi-directional variable gain amplifiers (VGAs) and two cross-pol. leakage cancellation paths. The proposed canceller can be configured into three operating modes. In the normal TX mode, the H/V bi-directional VGAs are operating in the TX mode, and the H/V cancellation paths are disabled. The RX mode operation is similar to the normal TX mode. Only the RX-mode H/V bi-directional VGAs are turned on to support the bi-directional operation. In the cross-pol. leakage cancellation mode, the cancellation paths are operating together with the TX-mode H/V bi-directional VGAs. The required H-to-V and V-to-H cancellation signals are created by the magnitude and phase control circuits along the cancellation paths.

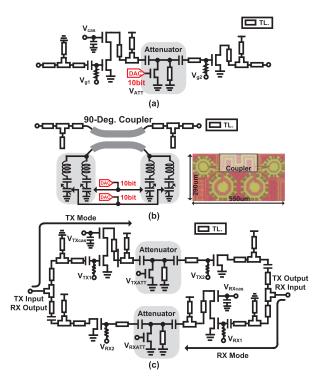

The cancellation path in this work is designed to realize the high-resolution and orthogonal magnitude and phase tunings. Each cancellation path includes two VGAs and a phase shifter. Fig. 7(a) shows the circuit schematic of the VGA. The VGA is designed with a cascode stage, a common-source stage, and an adjustable attenuator. The passive components for matching are designed based on the low-loss and configurable transmission lines (TLs) [25]. To realize high-resolution magnitude tuning, a 10-bit DAC is utilized to control the adjustable attenuator. A shunt TL stub is connected to the attenuator to compensate for the parasitic capacitance and suppressing the phase variation.

Fig. 7(b) shows the circuit schematic for the cancellation phase shifter. The reflection-type phase shifter is selected here to achieve fine phase shifting with minimized insertion loss and area [26], [27]. The 90° directional coupler is realized with two top thick metal layers. The phase difference between the through port and the coupling port is optimized in electro-magnetic (EM) simulations. The reflection load in this work includes two series *LC* resonators with different resonating points. The 360° gain-invariant phase-shifting could

Fig. 6. Block diagrams of the proposed cross-pol. leakage canceller in (a) TX mode, (b) RX mode, and (c) cross-pol. leakage cancellation mode.

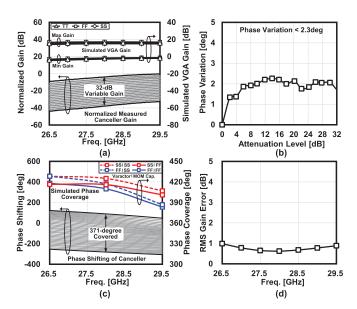

Fig. 8. (a) Measured variable gain of the cancellation path and simulated tuning range of a single-stage VGA. (b) Phase variation of the cancellation path during gain tuning. (c) Phase-shifting coverage and (d) the corresponding rms gain error of the cancellation path.

Fig. 7. Circuit schematics of (a) single-ended VGA, (b) reflection-type phase shifter in cancellation path, (c) and single-ended bi-directional VGA.

be obtained with the dual-voltage control. The occupied area for the phase shifter is 0.16 mm<sup>2</sup>. Further area reduction could be realized by using the switch-type phase shifters along with the resonator-based fine-tuning stage.

Fig. 7(c) presents the circuit schematic of the H/V single-ended bi-directional VGAs. Two single-direction VGA chains are directly combined for supporting the bi-directional operation with a minimized area. The mode selection is realized by switching the bias.

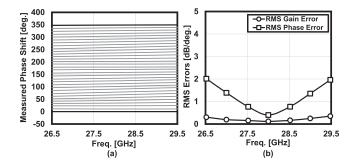

Fig. 8(a) and (b) summarizes the measured variable gain performance of the cancellation path with a 2-dB tuning step. The simulated single-stage VGA performance with transistor process corners is also included. Two VGAs in this work totally provide a 32-dB gain tuning range. The achieved tuning resolution is less than 0.2 dB with the help of the high-resolution DACs. Furthermore, the measured phase variation over all gain tuning states is less than  $2.3^{\circ}$  at 28 GHz. Phase-invariant gain tuning is obtained by the cancellation path. Fig. 8(c) and (d) presents the phase-shifting performance of the cancellation path. The simulated phase coverage over process corners of varactor and MOM capacitor is also included. The 360° phase shifting could always be achieved from 26.5 to 29.5 GHz in both simulation and measurement. The corresponding rms gain error over the whole 5G 28-GHz band is less than 0.98 dB.

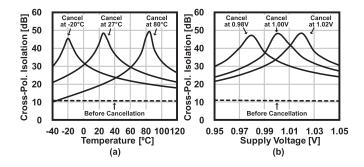

The cancellation performance in this work is further evaluated over temperature and supply voltage. Four H-pol. and four V-pol. transmitters along with the cancellation circuits are utilized for this simulation. The outputs of H-pol. transmitters and V-pol. transmitters are ideally combined, respectively. Before the cancellation, around -10-dB cross-pol. coupling is manually added between the output nodes of H-pol. and V-pol. transmitters. Fig. 9(a) demonstrates the H-to-V isolations with different cancellation temperatures. With a cancellation at 27°C, the cross-pol. isolation is always better than 20 dB from

Fig. 9. Simulated cross-pol. isolation against (a) temperature and (b) supply voltage.

$-40^{\circ}$ C to 120°C. Within 0°C–60°C, the cross-pol. isolation is better than 30 dB. Fig. 9(b) presents the H-to-V isolations over different supply voltages. With a cancellation at 1-V, the crosspol. isolation is always better than 23 dB considering  $\pm 5\%$ supply voltage variation.

## B. Neutralized Bi-Directional Gain Amplifier

In this work, the element-beamformer is designed based on the neutralized bi-directional architecture for saving chip area and manufacturing cost [6]. The occupied on-chip area for each beamformer is reduced to half by the bi-directional technique. As shown in Fig. 5, each beamformer in this work consists of a bi-directional gain amplifier, a bi-directional active vector-summing phase shifter, and a two-stage PA-LNA.

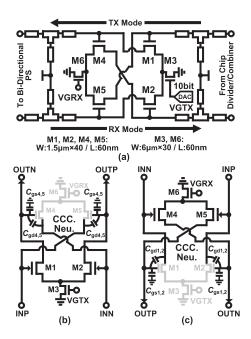

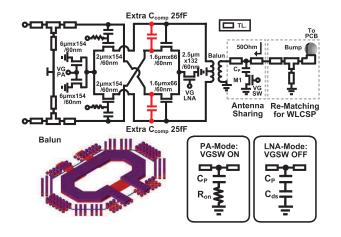

Fig. 10(a) shows the circuit schematic of the bi-directional gain amplifier. Two differential pairs in the cross-coupling connection are included in the neutralized bi-directional core. The mode selection of the core is realized by switching the tail transistors M3 and M6. Fig. 10(b) and (c) further explains the TX- and RX-mode core operations. By selecting the same transistor size among M1, M2, M4, and M5, the gate-drain capacitance neutralization could be maintained in both operating modes [28]-[30]. Improved amplifier gain and reverse isolation are achieved. Moreover, to minimize the required chip area, the TL-based passive matching components for the gain amplifier are shared between the TX mode and the RX mode. In millimeter-wave frequencies, the required matching conditions for the proposed core will not change dramatically during the mode switching. Therefore, properly sized TLs could be selected for realizing a low-loss matching in both TX and RX modes. A high-performance and area-efficient bidirectional amplifier could be realized.

Fig. 11(a) and (b) shows the simulated performance of the bi-directional gain amplifier. The achieved TX- and RX-mode gains are around 8 and 10 dB, respectively. Within 26.5–29.5 GHz, the return losses are always better than -8 dB. The power consumptions are 9 mW in the TX mode and 10 mW in the RX mode. Furthermore, orthogonal gain and phase tuning are always demanded by millimeter-wave beamformers for a simple control algorithm and fast calibration. In this work, the TX-mode amplifier is further reused as the VGA in each beamformer path. The tail bias is controlled by the high-resolution DACs for providing the fine gain tuning.

Fig. 10. (a) Circuit schematic of the neutralized bi-directional gain amplifier. Equivalent circuits of the proposed neutralized bi-directional core in (b) TX mode and (c) RX mode.

Fig. 11. Simulated S-parameters of the gain amplifier in (a) TX mode and (b) RX mode. Simulated (c) variable gain of the TX-mode amplifier and (b) corresponding phase variation at 28 GHz.

Fig. 11(c) and (d) demonstrates the VGA performance. The simulated gain coverage with transistor process corners is also shown in the figure. Due to the neutralized bi-directional technique, the phase variation during the gain tuning is suppressed by the gate–drain capacitance neutralization [31]. As shown in Fig. 11(d), within the 8-dB gain tuning range, the phase variation is less than  $2.5^{\circ}$  at 28 GHz.

Fig. 12. Circuit schematic of the proposed PA-LNA, antenna sharing, and rematching for WLCSP.

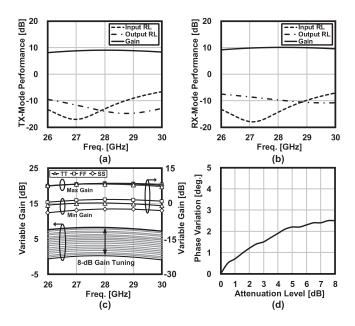

## C. PA-LNA

Compact and low-loss design of the antenna interface is essential for realizing low-cost and power-efficient 5G millimeter-wave phased-array transceivers. The PA power delivery and LNA NF are required to be optimized together with the TRX switch considering the insertion loss and chip area. Facing the complex modulated signals in 5G, the PA efficiency in the deep PBO region also demands further improvement [32], [33]. Moreover, the packaging design is critical to the overall performance of 5G millimeter-wave phased-array systems. Accurate package modeling and optimizations are required for decreasing the insertion loss. Due to the reduced array antenna pitch at millimeter-wave frequencies, minimized packaging size and chip area become significant not only for a reduced manufacturing cost but also for a low-loss distribution from the chip to the antenna.

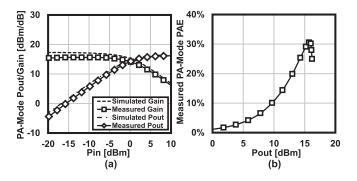

Fig. 12 shows the circuit schematic of the PA-LNA along with the packaging connection. To minimize the chip area cost, the unbalanced neutralized bi-directional technique is adopted in this work. Compared with the neutralized bi-directional technique mentioned in Section III-B, two extra capacitors C<sub>comp</sub> are attached to the LNA transistors for compensating the extra gate-drain capacitance from the PA transistors. Therefore, even with different transistor sizes, the unbalanced neutralized bi-directional core could still maintain the gate-drain capacitance neutralization in both the PA mode and the LNA mode. To improve the PA-mode power efficiency at the deep PBO region, the proposed PA is biased in class AB condition. An adaptive antenna sharing network is co-designed with the core circuits to improve the PA-mode power delivery and LNA-mode NF. At 28 GHz, the simulated insertion loss of the antenna sharing network is 0.5 dB in the PA mode and 1.5 dB in the LNA mode.

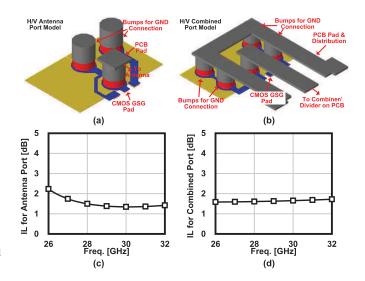

To minimize the implementation size and loss, the proposed chip is packaged with a wafer-level chip-scale package (WLCSP). The influence of the WLCSP is carefully modeled with EM simulation. Fig. 13(a) and (b) shows the package interconnection models for the H/V antenna port and the H/V combined input/output port, respectively. The

Fig. 13. EM simulation models for (a) H/V antenna port and (b) H/V combined input/output port WLCSP. Simulated packaging insertion loss, including the rematching for (c) H/V antenna port model and (d) H/V combined input/output port model.

Fig. 14. (a) Measured PA-mode linearity and (b) corresponding PAE.

signal interconnection is kept in GSG fashion all along with the chip pad to the PCB pad for better signal shielding. To compensate for the impedance mismatch, a TL-based re-matching network is further designed together with the models. Fig. 13(c) and (d) presents the simulated insertion loss after the compensation. Within the frequency range from 26.5 to 29.5 GHz, the introduced packaging loss is around 1.5 dB for both ports.

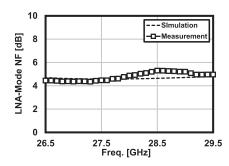

To evaluate the performance of the PA-LNA, a standalone PA-LNA excluding the WLCSP and re-matching network is fabricated for on-wafer measurement. Fig. 14(a) presents the measured PA-mode linearity. The achieved saturated output power is 16.2 dBm, and the output  $P_{1dB}$  is 13.4 dBm. Fig. 14(b) demonstrates the corresponding power-added efficiency (PAE). The proposed PA reports a maximum PAE of 30.7% including the TRX switch. Due to the class AB bias condition, the maintained PAE at 6-dB PBO is 11.5%. The measured LNA-mode NF is further shown in Fig. 15. Keysight PNA-X N5247A along with the cold-source method is used for the NF measurement. Within the frequency range of 26.5–29.5 GHz, the NF is from 4.3 to 5.3 dB.

Fig. 15. Measured LNA-mode NF.

Fig. 16. Block diagrams of (a) conventional active bi-directional phase shifter and (b) proposed balanced active bi-directional phase shifter. Operations of proposed phase shifter in (c) TX mode and (d) RX mode.

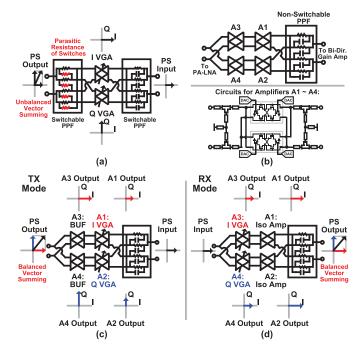

## D. Balanced Active Bi-Directional Phase Shifter

The usage of active phase shifters further helps the bi-directional beamformers to shrink in size [6]. The area consumption overhead for gain compensation, which is required in beamformers with passive phase-shifting solutions, can be removed. However, conventional active bi-directional vectorsumming phase shifters [see Fig. 16(a)] based on the switchable polyphase filters (PPFs) suffer from the imperfect switching operation [6]. Unbalanced vector summing is introduced by the parasitic resistance of switches. Complicated control tables are required for compensating for the magnitude and phase errors. In addition, the overall achievable RF-path gain is also degraded by the usage of multiple switchable PPFs.

To address these issues, Fig. 16(b) presents the balanced active bi-directional phase shifter in this work. The proposed phase shifter consists of a non-switchable PPF, bi-directional VGAs A1 and A3 for the I path, and bi-directional VGAs

Fig. 17. Simulated IRR of PPF over process corners after compensation.

A2 and A4 for the Q path. The VGA circuits for A1-A4 are similar to the neutralized bi-directional gain amplifier. Two bi-directional cores with flipped output are included for covering the complete 360° phase shifting in vector-summing operation. Fig. 16(c) and (d) further explains the TX- and RX-mode operations, respectively. In the TX mode, the generated I/Q signals by the PPF are first sent to A1 and A2. Due to their invariant input impedance, A1 and A2 will directly function as the I/Q VGAs. In this condition, A3 and A4 will be set with fixed gain and serve as another driving stage for the PA. Balanced I/Q summing and improved linearity over phase shifting could be achieved in the TX mode. In the RX mode, the PPF can operate as the quadrature adder with its reciprocal characteristic. However, the orthogonality of PPF is sensitive to the mismatch between the I/Q input impedances. Therefore, A3 and A4 in the RX mode will function as the I/Q VGAs, while A1 and A2 with fixed gain will serve as the isolation buffers. Identical I/Q input impedances could be provided to the PPF, and balanced vector summing could be realized also in the RX mode. Moreover, the overall gain performance of the proposed phase shifter is improved due to the usage of one single non-switchable PPF.

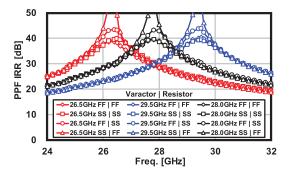

The non-switchable PPF used in this work is designed with tunable capacitance. It can be configured for different operating center frequencies. The frequency band from 26.5 to 29.5 GHz is covered by the PPF. The I/Q imbalance caused by the process variation could also be compensated by the tunable capacitance through a calibration. Fig. 17 shows the simulated image rejection ratio (IRR) of the PPF in corner conditions after the compensation. Process corners of the varactors and resistors are considered in this simulation. Considering the 400-MHz channel bandwidth defined in the 5G NR standard, the simulated IRRs are always better than 37.1 dB.

Fig. 18 demonstrates the measured phase-shifting performance of the proposed beamformer. The PPF setting is fixed in this measurement. The 360° phase shifting is covered by this work. From 26.5 to 29.5 GHz, the introduced rms phase error and rms gain error are less than 2° and 0.4 dB, respectively, without any compensation tables. The proposed phase shifter also realizes 13-dB gain in the TX mode and 10-dB gain in the RX mode. The PA could be directly driven by the phase shifter in this work. The area and power efficiencies of the proposed beamformer are further improved.

Fig. 18. Measured (a) phase shifting and (b) rms gain and phase errors for the proposed beamformer.

Fig. 19. Die micrograph with WLCSP.

TABLE I CORE AREA AND POWER CONSUMPTION BREAKDOWNS

| Block                 | Sub-Block             | Core Area<br>[mm <sup>2</sup> ] | PDC<br>[mW] |          |

|-----------------------|-----------------------|---------------------------------|-------------|----------|

| Element<br>Beamformer | PA-LNA                | 0.11                            | PA          | 132      |

|                       |                       |                                 | LNA<br>TX   | 50<br>39 |

|                       | Bi-Dir. Phase Shifter | 0.27                            | RX          | 19       |

|                       | Isolation Buffer      | 0.10                            | TX          | 10       |

|                       |                       |                                 | RX          | 11       |

| Comb.<br>Path         | RF Buffer & VGAs      | 0.30                            | TX          | 21       |

|                       |                       | 0.50                            | RX          | 32       |

|                       | Canceller             | 0.42                            | 10>         | <2       |

### **IV. MEASUREMENT**

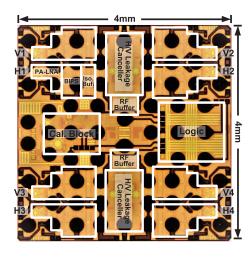

The proposed phased-array beamformer chip is fabricated in a 65-nm CMOS process with WLCSP. Fig. 19 shows the chip micrograph, including the package. The chip size is 4 mm  $\times$ 4 mm. Table I summarizes the core area consumption breakdown for the whole chip. The proposed element-beamformer based on the compact neutralized bi-directional architecture occupies only 0.48-mm<sup>2</sup> on-chip area. Table I also shows the power consumption breakdown. The proposed chip consumes 745 mW in the TX mode and 352 mW in the RX mode for each polarization. Thus, the power consumption for each

Fig. 20. Simulated and measured (a) TX-mode gain, (b) TX-mode linearity, (c) RX-mode gain, and (d) RX-mode NF.

element-beamformer is 186 mW in the TX mode and 88 mW in the RX mode. The cancellation path introduced in this work only consumes 10 mW. Due to the power-efficient circuits introduced in this work, a peak TX-mode efficiency of 22% per antenna path is achieved. High-efficiency and low-cost 5G millimeter-wave DP-MIMO systems could be realized by the proposed chip.

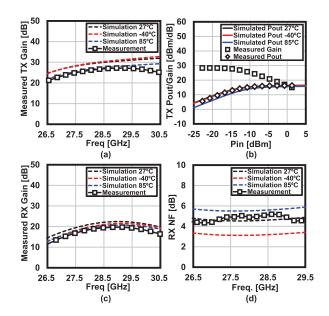

The on-wafer characteristics of the proposed chip are evaluated first. Fig. 20 summarizes the on-wafer measured performance of the single-path element-beamformer. The simulated performance with different temperatures is also provided. Fig. 20(a) and (c) shows the measured TX- and RX-mode frequency responses. Within 26.5–30.5 GHz, the proposed beamformer achieves around 25-dB gain in the TX mode and around 18-dB gain in the RX mode. Fig. 20(b) presents the TX-mode linearity. The measured on-wafer saturated output power is 16.1 dBm at 28 GHz. The corresponding output  $P_{1 dB}$ is 13.7 dBm. Fig. 20(d) demonstrates the measured RX-mode NF. At 28 GHz, the achieved NF is 4.9 dB.

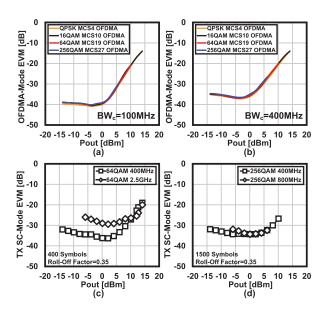

The TX-mode beamformer is further evaluated with the modulated signals. Single-carrier-mode (SC-mode) and standard-compliant 5G NR OFDMA-mode signals are utilized in this measurement. Fig. 21(a) and (b) presents the measured OFDMA-mode EVMs with 100- and 400-MHz channel bandwidths, respectively. The measured EVMs are normalized to the rms magnitude of the constellations. The peak-to-average power ratio (PAPR) for 400-MHz, 64-QAM OFDMA-mode modulated signal is 11.6 dB. When the output power  $P_{out}$  is low, the EVMs are dominated by the output noise floor. Therefore, in this region, the measured EVMs with 100-MHz bandwidth are better than the ones with 400-MHz bandwidth. When  $P_{\rm out}$  is large, the nonlinearity of the TX-mode beamformer mainly decides the achievable EVMs. Thus, the measured EVMs are almost the same between Fig. 21(a) and (b) in large  $P_{\rm out}$  region. This work achieves the minimum 64-QAM EVMs

Fig. 21. Measured OFDMA-mode EVMs with (a) 100-MHz bandwidth and (b) 400-MHz bandwidth for TX-mode beamformer. The 5G NR MCS index table 2 for PDSCH is applied (Table 5.1.3.1-2 in 3GPP TS 38.214 V16.1.0). Measured SC-mode EVMs in (c) 64-QAM and (d) 256-QAM for TX-mode beamformer.

Fig. 22. (a) Measured output power, output noise floor, IM3, and SNDR for RX-mode beamformer in normal-gain mode. (b) Measured RX-mode SNDRs with different gain settings.

of -40.3 dB with 100-MHz bandwidth and -37.0 dB with 400-MHz bandwidth. The measured 64-QAM output power is 7.1 dBm regarding an EVM of -25 dB. The 256-QAM output power of 2.5 dBm is also maintained with -32-dB EVM. Fig. 21(c) and (d) further demonstrates the measured EVMs with SC-mode modulated signals against the output power. Compared with the 5G NR OFDMA-mode signals, the SC-mode modulated signals have lower PAPRs (7.7 dB for 64-QAM and 8.2 dB for 256-QAM). Therefore, the EVMs of the TX-mode beamformer at large output power region are improved. With 400-MHz channel bandwidth, the TX-mode beamformer in this work can deliver 11-dBm SC-mode output power can also be supported in 256-QAM with -32.4-dB EVM.

Fig. 22(a) demonstrates the measured performance of the RX-mode beamformer. The output power, output noise floor, and IM3 are measured at 28 GHz against the input power. The input  $P_{1 \text{ dB}}$  is -29 dBm. The corresponding

Fig. 23. Photograph of proposed 64H + 64V phased-array module.

Fig. 24. (a) V-pol. and (b) H-pol. radiation patterns in azimuth plane for the proposed dual-polarized patch antenna.

signal-to-noise-and-distortion ratio (SNDR) is calculated with a 400-MHz channel bandwidth. In this work, the RX-mode beamformer achieves a peak SNDR of 41.2 dB. The measured dynamic range regarding a 25-dB SNDR is from -57 to -30 dBm. The SNDR at the high input power region could be further improved by reducing the RX-mode gain. Fig. 22(b) shows the RX SNDRs with different gain settings. With a -6.9-dB gain, the measured NF of the RX-mode beamformer is 16.3 dB at 28 GHz. The achieved SNDR is improved to -35.4 dB regarding an input power of -20 dBm.

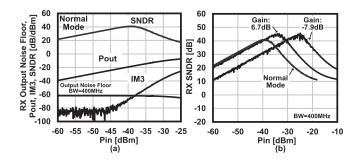

To evaluate the OTA performance of this work, the packaged chips are further implemented into the 64H + 64Vdual-polarized phased-array transceiver modules. Fig. 23 shows the photograph; 16 packaged chips are mounted to the backside of the module. Each chip has eight antenna ports and is connected to the  $2 \times 2$  dual-polarized antenna array in the frontside through the PCB vias. For distributing H-pol. and V-pol. signals among the chips, totally four 1-to-8 dividers/combiners are utilized on the PCB. To improve the cross-pol. isolation of the H/V signal distribution network, the ground-wall shieldings are included between the distributions. The simulated cross-pol. isolation for the H/V signal distribution network on the PCB is better than 37 dB from 26.5 to 29.5 GHz. In the frontside of the module, a  $16 \times 4$ dual-polarized antenna array is implemented. The antenna spacing is 6 mm. In this work, the dual-polarized antennas are fed in a non-rotated fashion. The identical spacing could be maintained between each feed point for suppressing the

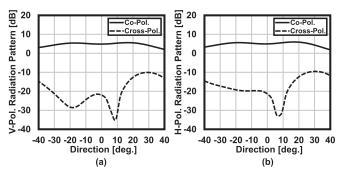

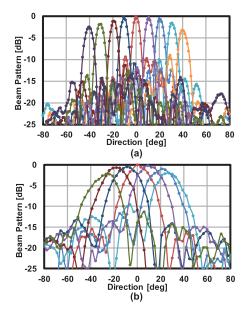

Fig. 25. Measured beam patterns in (a) azimuth plane and (b) elevation plane.

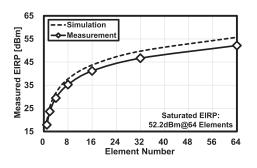

Fig. 26. Measured EIRPs against the number of TX-mode beamformers.

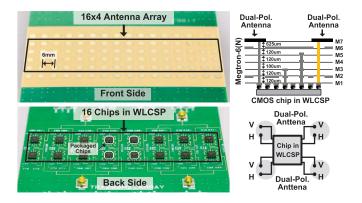

magnitude and phase errors. Fig. 24 shows the simulated radiation patterns in the azimuth plane for the dual-polarized patch antenna. The simulation frequency is 28 GHz. Including the feedlines, the antenna gain is around 5 dBi within  $-50^{\circ}$  to  $+50^{\circ}$  for both polarizations. At 0°, the H-to-V cross-pol. isolation is 26.7 dB, and the V-to-H cross-pol. isolation is 26.3 dB.

Fig. 25(a) demonstrates the measured V-pol. beam patterns in azimuth plane for the proposed phased-array module. The proposed module is capable of scanning the beam from  $-40^{\circ}$  to  $+40^{\circ}$ . The measured sidelobe level is always less than -9 dB without any amplitude tapering. The observed asymmetry of the beam patterns is possibly caused by the element pattern and the imperfections during the measurement. Fig. 25(b) presents the measured elevation-plane beam patterns within  $\pm 30^{\circ}$ . A 2 × 4 array is used in this measurement. The sidelobe level is always less than -9.6 dB. Fig. 26 shows the measured V-pol. effective isotropic radiated power (EIRP) against the activated element number. The saturated EIRP realized by 64 TX-mode beamformers is 52.2 dBm.

Two of the 64-element phased-array transceiver modules are evaluated in an SISO scenario with modulated signals.

| Modulation                    | QPSK                     | 16QAM                                                | 64QAM                  | 256QAM                 |

|-------------------------------|--------------------------|------------------------------------------------------|------------------------|------------------------|

| Mode                          | Single-Carrier<br>SISO   | Single-Carrier<br>SISO                               | Single-Carrier<br>SISO | Single-Carrier<br>SISO |

| Symbol rate                   | 2.5GSymbol/s             | 2.5GSymbol/s                                         | 2.5GSymbol/s           | 0.8GSymbol/s           |

| Data rate/BWc 5Gb/s           |                          | 10Gb/s                                               | 15Gb/s                 | 6.4Gb/s                |

| TX<br>Constellation           | * *                      | <pre>b * * * * * * * * * * * * * * * * * * * *</pre> |                        |                        |

| TX EIRP                       | 31.0dBm                  | 28.3dBm                                              | 27.9dBm                | 21.2dBm                |

| TX EVM (RMS)                  | -30.0dB                  | -29.3dB                                              | -29.4dB                | -34.3dB                |

| TX-to-RX EVM<br>(RMS) -22.5dB |                          | -22.2dB                                              | -22.3dB                | -28.4dB                |

| Modulation                    | QPSK                     | 16QAM                                                | 64QAM                  | 256QAM                 |

| Mode                          | OFDMA<br>SISO            | OFDMA<br>SISO                                        | OFDMA<br>SISO          | OFDMA<br>SISO          |

| MCS*                          | 5G NR MCS4               | 5G NR MCS10                                          | 5G NR MCS19            | 5G NR MCS27            |

| BWc 400MHz                    |                          | 400MHz                                               | 400MHz                 | 400MHz                 |

| TX<br>Constellation           | •••                      |                                                      |                        | 2<br>2                 |

|                               |                          | 42.8dBm                                              | 42.8dBm                | 40.2dBm                |

| TX EIRP                       | 43.2dBm                  | 42.0UBIII                                            | 42.000                 | 40.200111              |

| TX EIRP<br>TX EVM (RMS)       | 43.2dBm<br>-26.2dB(4.9%) | -26.0dB(5.1%)                                        | -25.8dB(5.2%)          | -29.9dB(3.2%)          |

"SG NK MCS Index table 2 for PUSCH is used. (Table 5.1.3.1-2 in 3GPP 15 38.214 V16.1.0).

"For OFDMA-mode measurement, 64-element array transmitter is used. For SC-mode measurement, 8-element array transmitter is used.

Fig. 27. Measured constellations and EVMs in SISO scenario.

In this measurement, one phased-array module is operating in the TX mode, while the other one is operating in the RX mode. The communication distance is 1 m, which is limited by the size of the microwave anechoic chamber. The beam direction is fixed with 0°. The SC- and OFDMA-mode modulated signals for the TX-mode module are generated by the Keysight arbitrary waveform generator (AWG) M8195A along with an up-conversion mixer. The LO for the up-conversion mixer is generated by the Keysight signal generator N5183B. The phase noise is low enough, which will not influence the measured EVMs. The received signals from the RX-mode module are directly analyzed by the Keysight real-time oscilloscope UXR0334A. The upper side of Fig. 27 presents the measured SC-mode constellations and EVMs. In SC-mode measurement, eight TX-mode beamformers and four RX-mode beamformers are activated. As shown in Fig. 27, the proposed module is capable of supporting maximum data rates of 5 Gb/s in QPSK, 10 Gb/s in 16-QAM, 15Gb/s in 64-QAM, and 6.4 Gb/s in 256-QAM. The corresponding TX-to-RX EVMs are -22.5, -22.2, -22.3, and -28.4 dB for QPSK, 16-QAM, 64-QAM, and 256-QAM, respectively. The bottom side of Fig. 27 demonstrates the measured constellations and EVMs with standard-compliant 5G NR OFDMA-mode signals; 64 TX-mode beamformers and four RX-mode beamformers are utilized in this measurement. The PBO of the TX-mode module is reduced for improving both the EIRP level and the transmitter power efficiency. Considering the increased EIRP from the TX side, the RX-mode beamformer in the low-gain mode is used in this measurement for improving the input-referred linearity. As shown in Fig. 27, the 64-element TX-mode module is capable of delivering 43.2-dBm EIRP in QPSK with -26.2-dB TX EVM, 42.8-dBm EIRP in 16-QAM with -26.0-dB TX EVM, 42.8-dBm EIRP in 64-QAM with

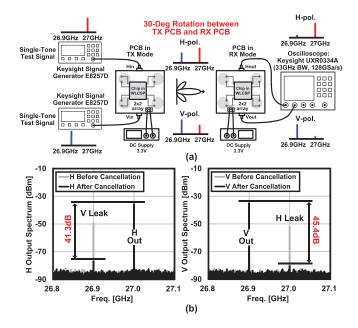

Fig. 28. (a) Equipment setup for cross-pol. leakage cancellation and (b) measured output spectra for H- and V-polarizations.

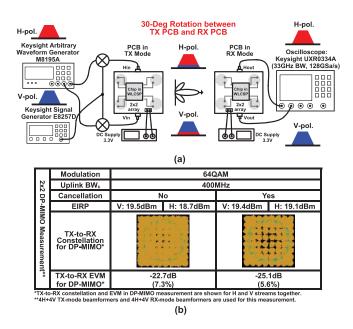

Fig. 29. (a) Equipment setup for DP-MIMO measurement and (b) performance summary before and after proposed cancellation.

-25.8-dB TX EVM, and 40.2-dBm EIRP in 256-QAM with -29.9-dB TX EVM. By de-embedding the ideal array gain (36.1 dB) and the simulated antenna gain (4.9 dBi), the average TX output power, including the packaging and implementation loss, is 1.8 dBm per path in 64-QAM. The measured TX-to-RX EVMs are -25.8 dB in QPSK, -25.5 dB in 16-QAM, -25.3 dB in 64-QAM, and -29.8 dB in 256-QAM.

As mentioned in Section II, the cross-pol. leakage introduced from the PCB and propagation will degrade the channel capacity of DP-MIMO systems. An analog-assisted cross-pol. leakage cancellation technique is proposed in this work to improve both the DP-MIMO EVM and the transmitter power

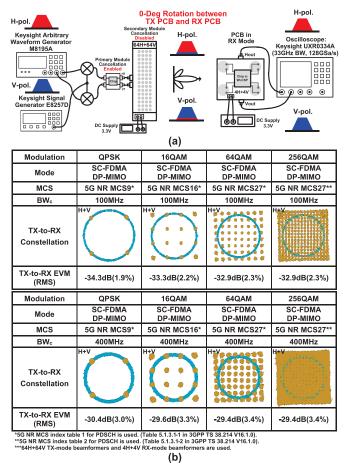

Fig. 30. (a) Equipment setup for primary-secondary DP-MIMO operation. (b) Measured DP-MIMO constellations and EVMs for 64H + 64V array module.

efficiency. Fig. 28(a) demonstrates the equipment setup and the cancellation procedure. In this measurement, 4H + 4VTX-mode beamformers and 4H + 4V RX-mode beamformers are adopted. To verify the cancellation performance over propagation, the TX- and RX-mode modules are placed with 30° rotation. Single-tone test signals with frequencies of 27.0 and 26.9 GHz are first sent to the H-pol. and V-pol. of the TX-mode module, respectively. At the RX side, the crosspol. leakage could be observed from the H-pol. and V-pol. output spectra. According to the leakage observed at the RX side, the canceller at the TX side is activated and configured to suppress the cross-pol. leakage. Fig. 28(b) shows the output spectra for the RX-mode module before and after the cancellation. Before the cancellation, around -15-dB crosspol. leakage could be observed for both H-pol. and V-pol. output spectra due to the rotation and coupling. After the cancellation, the V-to-H leakage is suppressed to -41.3 dB, while the H-to-V leakage is suppressed to -45.4 dB. The DP-MIMO performance before and after the cross-pol. leakage cancellation is also evaluated. Fig. 29(a) demonstrates the equipment setup. The settings for the TX- and RX-mode modules are kept the same as the ones used in Fig. 28. The rotation between the modules is also 30°. Two-stream 400-MHz standard-compliant 5G NR modulated signals in

|                                      | This                                            | work                | Qualcomm [1]                                          | IBM [10]                                   | UCSD [7]                              | Tokyo Tech [34]                                |

|--------------------------------------|-------------------------------------------------|---------------------|-------------------------------------------------------|--------------------------------------------|---------------------------------------|------------------------------------------------|

| Process 65nm CMOS                    |                                                 | CMOS                | 28nm CMOS                                             | $0.13 \mu m$ SiGe                          | $0.18 \mu m$ SiGe                     | 65nm CMOS                                      |

| Carrier Frequency 28GHz (n257)       |                                                 | (n257)              | 28GHz (n257)                                          | 28GHz                                      | 29GHz                                 | 28GHz (n257)                                   |

| TX P1dB/path                         | TX P1dB/path 13.7dBm                            |                     | 12.0dBm                                               | 14.0dBm                                    | 12.0dBm                               | 11.3dBm                                        |

| TX Psat/path                         | TX Psat/path 16.1dBm                            |                     | 14.0dBm                                               | 16.4dBm                                    | N/A                                   | 15.1dBm                                        |

| Saturated EIRP                       | 52.2                                            | dBm                 | 35.0dBm                                               | 54.0dBm                                    | 26.5dBm@P <sub>1dB</sub>              | 45.6dBm                                        |

| Saturated EIKr                       | (64 ele                                         | ements)             | (8 elements)                                          | (64 elements)                              | (4 elements)                          | (32 elements)                                  |

| RX NF                                | 4.9dB@28GHz                                     |                     | 4.4~4.7dB                                             | 6.0dB@28GHz                                | 4.8dB                                 | 4.2~5.0dB                                      |

| RMS Gain Error                       | 0.12dB                                          | B@28GHz N/A Gain    |                                                       | Gain Var.< 1.5dB                           | 0.6dB                                 | 0.2dB@28GHz                                    |

| RMS Phase Error                      | 0.4°@28GHz                                      |                     | N/A                                                   | < 1°@28GHz                                 | < 4°                                  | 0.4° @28GHz                                    |

| Integration/chip4×H-Beam<br>4×V-Beam |                                                 | ,                   | 24×TRX,<br>IF, LO                                     | 16×H-TRX,<br>16×V-TRX,<br>IF, LO (w/o PLL) | 4×H-Beamformer,<br>4×V-Beamformer     | 4×H-Beamformer,<br>4×V-Beamformer              |

| PDC/path                             | PDC/path TX:186mW<br>@16.1dBm/path<br>RX:88mW   |                     | TX:119mW(P <sub>1dB</sub> )<br>@11dBm/path<br>RX:42mW | TX:319mW<br>@16.4dBm/path<br>RX:206mW      | TX:220mW<br>RX:150mW                  | TX:232mW<br>@15.1dBm/path<br>RX:112mW          |

| Area/path                            | <b>th</b> 0.48mm <sup>2</sup>                   |                     | 0.68mm <sup>2</sup> *                                 | 2.55mm <sup>2</sup> *                      | 1.62mm <sup>2</sup> *                 | $0.58 \text{mm}^2$                             |

| 5G NR SISO<br>Modulation Supported   | 64-()AM 256-()AM                                |                     | QPSK,<br>16-QAM, 64-QAM<br>OFDMA-Mode                 | N/A                                        | N/A                                   | QPSK, 16-QAM,<br>64-QAM, 256-QAM<br>OFDMA-Mode |

| Cross-Pol. Leak Cancel               | Yes                                             |                     | No                                                    | No                                         | No                                    | No                                             |

| Rotation btw. TX & RX                | Yes                                             |                     | No                                                    | No                                         | No                                    | No                                             |

| Cross-Pol. Isolation                 | 41.3dB for V<br>45.4dB for H<br>(from TX to RX) |                     | N/A                                                   | N/A                                        | 36dB for V<br>27dB for H<br>(TX only) | 20.2dB<br>(TX only)                            |

| 5G NR<br>2x2 DP-MIMO                 | 64-QAM<br>EVM=3.4%                              | 256-QAM<br>EVM=3.4% | N/A                                                   | N/A                                        | 64-QAM(SC-Mode)<br>EVM=5.0%           | 64-QAM<br>EVM=4.9%                             |

TABLE II Performance Comparison of 28-GHz Phased-Array Transceivers Supporting DP-MIMO

\* Estimated from paper.

the SC-FDMA mode are generated simultaneously from the Keysight AWG M8195A. The data patterns are fully independent between these two data streams. The generated data streams are up-converted by two external mixers for the TX-mode module. The H-pol. and V-pol. output signals of the RX-mode module are directly analyzed by the Keysight real-time oscilloscope UXR0334A. Fig. 29(b) summarizes the measured TX-to-RX constellations and EVMs before and after the proposed cancellation. The output EIRPs for H- and V-pol. signals are kept the same for comparison. The achieved TX-to-RX EVM is improved from -22.7 to -25.1 dB in 64-QAM. The DP-MIMO EVMs, including the coupling and rotation, are improved with the help of the cross-pol. leakage cancellation technique. To perform the cross-pol. leakage cancellation for 64H + 64V TX-mode beamformers, the designed chip can operate in a primary-secondary configuration. As shown in Fig. 30(a), a 4H + 4V transceiver module with coaxial connector interface in this work could be utilized as the primary transceiver. It could provide cross-pol. cancellation function and input signal buffering for the secondary 64H + 64V TX-mode module. In this condition, the secondary 64H+ 64V TX-mode transceiver module will bypass the cancellation function and operates in normal TX mode. Fig. 30(b) demonstrates the measured DP-MIMO constellations and TXto-RX EVMs for 64H + 64V TX-mode beamformers and 4H + 4V RX-mode beamformers. With 100-MHz channel bandwidth, the measured TX-to-RX EVMs are -34.3 dB in QPSK, -33.3 dB in 16-QAM, -32.9 dB in 64-QAM, and -32.9 dB in 256-QAM. With 400 MHz, the achieved TXto-RX EVMs for QPSK, 16-QAM, 64-QAM, and 256-QAM are -30.4, -29.6, -29.4, and -29.4 dB, respectively. The

measured V-pol. and H-pol. EIRPs in 64-QAM with 400-MHz bandwidth are 38.4 and 38.6 dBm, respectively.

In Table II, this work is compared with several state-of-theart 28-GHz phased-array transceivers supporting DP-MIMO. With the proposed analog-assisted cross-pol. leakage cancellation technique, this work achieves over 40-dB cross-pol. isolation. The 64H + 64V phased-array transceiver modules in this work could support  $2 \times 2$  DP-MIMO communications. Moreover, the area-efficient neutralized bi-directional beamformer achieves 16.1-dBm TX-mode saturated output power and 22% per path peak TX-mode efficiency. The measured RX-mode NF is 4.9 dB at 28 GHz. The occupied on-chip area for each beamformer is only 0.48-mm<sup>2</sup> due to the completely shared circuits between TX and RX modes. Low-cost and power-efficient millimeter-wave DP-MIMO systems could be supported by this work for the 5G NR.

### V. CONCLUSION

In this work, an analog-assisted cross-pol. leakage cancellation technique is utilized for the 28-GHz DP-MIMO systems to improve the DP-MIMO EVMs and efficiency. Over 40-dB cross-pol. isolation is achieved after the proposed high-accuracy cancellation. The element-beamformer in this work maintains low-cost and high-efficiency features with the neutralized bi-directional architecture. The 16.1-dBm TX-mode saturated output power along with a 22% maximum TX-mode efficiency is realized with 0.48-mm<sup>2</sup> on-chip area. The proposed 64H + 64V array modules achieve 3.4% EVM with standard-compliant DP-MIMO signals in 256-QAM. Low-cost and high-efficiency 5G NR millimeter-wave DP-MIMO systems could be realized.

#### REFERENCES

- J. D. Dunworth *et al.*, "A 28 GHz bulk-CMOS dual-polarization phasedarray transceiver with 24 channels for 5G user and basestation equipment," in *IEEE Int. Solid-State Circuits Conf. (ISSCC) Dig. Tech. Papers*, Feb. 2018, pp. 70–72.

- [2] D. D. Maistro et al., "A 24.2-30.5 GHz quad-channel RFIC for 5G communications including built-in test equipment," in Proc. IEEE Radio Freq. Integr. Circuits Symp. (RFIC), Jun. 2019, pp. 283–286.

- [3] Y. Yoon et al., "A highly linear 28 GHz 16-element phased-array receiver with wide gain control for 5G NR application," in Proc. IEEE Radio Freq. Integr. Circuits Symp. (RFIC), Jun. 2019, pp. 287–290.

- [4] H. C. Park et al., "A 39 GHz-band CMOS 16-channel phased-array transceiver IC with a companion dual-stream IF transceiver IC for 5G NR base-station applications," in *IEEE Int. Solid-State Circuits Conf.* (*ISSCC*) Dig. Tech. Papers, Feb. 2020, pp. 76–78.

- [5] M.-Y. Huang and H. Wang, "A 27-to-41 GHz MIMO receiver with N-input-N-output using scalable cascadable autonomous array-based high-order spatial filters for instinctual full-FoV multi-blocker/signal management," in *IEEE Int. Solid-State Circuits Conf. (ISSCC) Dig. Tech. Papers*, Feb. 2019, pp. 346–348.

- [6] J. Pang et al., "A 28 GHz CMOS phased-array beamformer utilizing neutralized Bi-directional technique supporting dual-polarized MIMO for 5G NR," in *IEEE Int. Solid-State Circuits Conf. (ISSCC) Dig. Tech. Papers*, Feb. 2019, pp. 344–345.

- [7] K. Kibaroglu, M. Sayginer, A. Nafe, and G. M. Rebeiz, "A dualpolarized dual-beam 28 GHz beamformer chip demonstrating a 24 Gbps 64-QAM 2×2 MIMO link," in *Proc. IEEE Radio Freq. Integr. Circuits Symp. (RFIC)*, Jun. 2018, pp. 64–67.

- [8] A. Nafe, M. Sayginer, K. Kibaroglu, and G. M. Rebeiz, "2×64 dual-polarized dual-beam single-aperture 28 GHz phased array with high cross-polarization rejection for 5G polarization MIMO," in *IEEE MTT-S Int. Microw. Symp. Dig.*, Jun. 2019, pp. 484–487.

- [9] Y. Yin, S. Zihir; T. Kanar, and G. M. Rebeiz, "A 37-42 GHz 8×8 phasedarray for 5G communication systems with 48-50 dBm EIRP," in *IEEE MTT-S Int. Microw. Symp. Dig.*, Jun. 2019, pp. 480–483.

- [10] B. Sadhu et al., "A 28-GHz 32-element TRX phased-array IC with concurrent dual-polarized operation and orthogonal phase and gain control for 5G communications," *IEEE J. Solid-State Circuits*, vol. 52, no. 12, pp. 3373–3391, Dec. 2017.

- [11] H.-T. Kim *et al.*, "A 28 GHz CMOS direct conversion transceiver with packaged antenna arrays for 5G cellular system," in *Proc. IEEE Radio Freq. Integr. Circuits Symp. (RFIC)*, Jun. 2017, pp. 69–72.

- [12] Y. Wang *et al.*, "A 39-GHz 64-element phased-array transceiver with built-in phase and amplitude calibrations for large-array 5G NR in 65nm CMOS," *IEEE J. Solid-State Circuits*, vol. 55, no. 5, pp. 1249–1269, May 2020.

- [13] J. Pang et al., "A 28-GHz CMOS phased-array transceiver based on LO phase-shifting architecture with gain invariant phase tuning for 5G new radio," *IEEE J. Solid-State Circuits*, vol. 54, no. 5, pp. 1228–1242, Mar. 2019.

- [14] Y.-S. Yeh, E. Balboni, and B. Floyd, "A 28-GHz phased-array transceiver with series-fed dual-vector distributed beamforming," in *Proc. IEEE Radio Freq. Integr. Circuits Symp. (RFIC)*, Jun. 2017, pp. 65–68.

- [15] S. Mondal and J. Paramesh, "Power-efficient design techniques for mm-wave hybrid/digital FDD/full-duplex MIMO transceivers," *IEEE J. Solid-State Circuits*, vol. 55, no. 8, pp. 2011–2026, Aug. 2020.

- [16] R. Garg et al., "A 28 GHz 4-element MIMO beam-space array in 65 nm CMOS with simultaneous spatial filtering and single-wire frequencydomain multiplexing," in *IEEE Int. Solid-State Circuits Conf. (ISSCC) Dig. Tech. Papers*, Feb. 2020, pp. 80–82.

- [17] J. Park, S. Lee, D. Lee, and S. Hong, "A 28 GHz 20.3%-transmitterefficiency 1.5°-phase-error beamforming front-end IC with embedded switches and dual-vector variable-gain phase shifters," in *IEEE Int. Solid-State Circuits Conf. (ISSCC) Dig. Tech. Papers*, Feb. 2019, pp. 176–178.

- [18] A. G. Roy et al., "A 37-40 GHz phased array front-end with dual polarization for 5G MIMO beamforming applications," in *Proc. IEEE Radio Freq. Integr. Circuits Symp. (RFIC)*, Jun. 2019, pp. 251–254.

- [19] A. Chakrabarti, C. Thakkar, S. Yamada, D. Choudhury, J. Jaussi, and B. Casper, "A 64Gb/s 1.4pJ/b/element 60 GHz 2×2-element phasedarray receiver with 8b/symbol polarization MIMO and spatial interference tolerance," in *IEEE Int. Solid-State Circuits Conf. (ISSCC) Dig. Tech. Papers*, Feb. 2020, pp. 84–86.

- [20] S. O. Ajose, N. O. Sadiku, and U. Goni, "Computation of attenuation, phase rotation, and cross-polarization of radio waves due to rainfall in tropical regions," *IEEE Trans. Antennas Propag.*, vol. 43, no. 1, pp. 1–5, Jan. 1995.

- [21] S. Yamada *et al.*, "Cross-polarization discrimination and port-to-port isolation enhancement of dual-polarized antenna structures enabling polarization MIMO," *IEEE Antennas Wireless Propag. Lett.*, vol. 18, no. 11, pp. 2409–2413, Nov. 2019.

- [22] J. Pang et al., "A 28-GHz CMOS phased-array beamformer supporting dual-polarized MIMO with cross-polarization leakage cancellation," in Proc. IEEE Symp. VLSI Circuits, Jun. 2020, pp. 1–2.

- [23] E. Telatar, "Capacity of multi-antenna Gaussian channels," *Eur. Trans. Telecommun.*, vol. 10, no. 6, pp. 585–596, Nov. 1999.

- [24] E. Björnson, J. Hoydis, and L. Sanguinetti, "Massive MIMO networks: Spectral, energy, and hardware efficiency," *Found. Trends Signal Process.*, vol. 11, nos. 3–4, pp. 154–655, 2017.

- [25] J. Pang et al., "A 50.1-Gb/s 60-GHz CMOS transceiver for IEEE 802.11ay with calibration of LO feedthrough and I/Q imbalance," *IEEE J. Solid-State Circuits*, vol. 54, no. 5, pp. 1375–1390, May 2019.

- [26] P. Gu and D. Zhao, "Ka-band CMOS 360° reflective-type phase shifter with ±0.2 dB insertion loss variation using triple-resonating load and dual-voltage control techniques," in *Proc. IEEE Radio Freq. Integr. Circuits Symp. (RFIC)*, Jun. 2018, pp. 140–143.

- [27] F. Meng, K. Ma, K. S. Yeo, and S. Xu, "A 57-to-64-GHz 0.094-mm<sup>2</sup> 5-bit passive phase shifter in 65-nm CMOS," *IEEE Trans. Very Large Scale Integr. (VLSI) Syst.*, vol. 24, no. 5, pp. 1917–1925, May 2016.

- [28] W. L. Chan and J. R. Long, "A 58–65 GHz neutralized CMOS power amplifier with PAE above 10% at 1-V supply," *IEEE J. Solid-State Circuits*, vol. 45, no. 3, pp. 554–564, Mar. 2010.

- [29] D. Zhao and P. Reynaert, "A 60-GHz dual-mode class AB power amplifier in 40-nm CMOS," *IEEE J. Solid-State Circuits*, vol. 48, no. 10, pp. 2323–2337, Oct. 2013.

- [30] H. Asada, K. Matsushita, K. Bunsen, K. Okada, and A. Matsuzawa, "A 60 GHz CMOS power amplifier using capacitive cross-coupling neutralization with 16% PAE," in *Proc. 41st Eur. Microw. Conf.*, Oct. 2011, pp. 1115–1118.

- [31] T. Wu, C. Zhao, H. Liu, Y. Wu, Y. Yu, and K. Kang, "A 20~43 GHz VGA with 21.5 dB gain tuning range and low phase variation for 5G communications in 65-nm CMOS," in *Proc. IEEE Radio Freq. Integr. Circuits Symp. (RFIC)*, Jun. 2019, pp. 71–74.

- [32] F. Wang and H. Wang, "A 24-to-30 GHz watt-level broadband linear Doherty power amplifier with multi-primary distributed-activetransformer power-combining supporting 5G NR FR2 64-QAM with >19dBm average pout and >19% average PAE," in *IEEE Int. Solid-State Circuits Conf. (ISSCC) Dig. Tech. Papers*, Feb. 2020, pp. 362–364.

- [33] S. Li, M.-Y. Huang, D. Jung, T.-Y. Huang, and H. Wang, "A 28 GHz current-mode inverse-outphasing transmitter achieving 40%/31% PA efficiency at Psat/6dB PBO and supporting 15Gbit/s 64-QAM for 5G communication," in *IEEE Int. Solid-State Circuits Conf. (ISSCC) Dig. Tech. Papers*, Feb. 2020, pp. 366–368.

- [34] J. Pang et al., "A 28-GHz CMOS phased-array beamformer utilizing neutralized bi-directional technique supporting dual-polarized MIMO for 5G NR," *IEEE J. Solid-State Circuits*, vol. 55, no. 9, pp. 2371–2386, Sep. 2020.

**Jian Pang** (Member, IEEE) received the bachelor's and master's degrees from Southeast University, Nanjing, China, in 2012 and 2014, respectively, and the Ph.D. degree from the Department of Physical Electronics, Tokyo Institute of Technology, Tokyo, Japan, in 2019.

From 2019 to 2020, he was a Post-Doctoral Researcher with the Tokyo Institute of Technology, where he is currently a Special Appointed Assistant Professor, focusing on 5G millimeter-wave systems. His current research interests include high-data-rate

low-cost millimeter-wave transceivers, power-efficient power amplifiers for 5G mobile systems, multiple-in-multiple-out (MIMO), and mixed-signal calibration systems.

Dr. Pang was a recipient of the IEEE SSCS Student Travel Grant Award in 2016, the IEEE SSCS Predoctoral Achievement Award for the term 2018–2019, and the Seiichi Tejima Oversea Student Research Award in 2020. He also serves as a Reviewer for the IEEE JOURNAL OF SOLID-STATE CIRCUITS, IEEE TRANSACTIONS ON MICROWAVE THEORY AND TECH-NIQUES, IEEE TRANSACTIONS ON CIRCUITS AND SYSTEMS I & II, and IEEE MICROWAVE AND WIRELESS COMPONENTS LETTERS.

Zheng Li (Graduate Student Member, IEEE) received the B.E. and M.E. degrees in microelectronics and solid electronics from Xidian University, Xi'an, China, in 2014 and 2017, respectively. He is currently pursuing the Ph.D. degree in electrical and electronic engineering with the Tokyo Institute of Technology, Tokyo, Japan, with a focus on 5G RF front-end and system design.

His current research interests include millimeterwave CMOS wireless transceiver and 5G mobile systems.

**Kiyoshi Yanagisawa** received the B.E. and M.E. degrees in information science from Tohoku University, Sendai, Japan, in 1998 and 2000, respectively. From 2013 to 2019, he was with Rohde & Schwarz, Tokyo, Japan, where he was engaged in the test and measurement of wireless systems. He is currently a Researcher with the Department of Electrical and Electronic Engineering, Tokyo Institute of Technology, Tokyo, Japan. His current research interests include new technology in wireless systems and devices.

Mr. Yanagisawa is also a member of the Institute of Electronics, Information and Communication Engineers (IEICE).

**Xueting Luo** received the B.E. and M.E. degrees in electrical engineering from the Tokyo Institute of Technology, Tokyo, Japan, in 2018 and 2020, respectively.

She is currently with Sandisk Ltd., Yokohama, Japan.

Yi Zhang (Student Member, IEEE) received the B.E. degree in microelectronic science and engineering from the Southern University of Science and Technology, Shenzhen, China, in 2018, and the M.E degree in electrical and electronic engineering from the Tokyo Institute of Technology, Tokyo, Japan, in 2020, where he is currently pursuing the Ph.D. degree in electrical and electronic engineering.

His research interests include both analog and RF circuit design in millimeter-wave CMOS transceiver design for 5G mobile systems.

**Joshua Alvin** (Student Member, IEEE) received the B.E. degree in electrical and electronic engineering from the Tokyo Institute of Technology, Tokyo, Japan, in 2019, where he is currently pursuing the master's degree in electrical and electronic engineering.

**Zixin Chen** received the B.E. degree in microelectronic science and engineering from Xi'an Jiaotong University, Xi'an, China, in 2018, and the M.S. degree in electrical and electronic engineering from the Tokyo Institute of Technology, Tokyo, Japan, in 2020.

He is currently with Sony Semiconductor Solutions Corporation, Atsugi, Japan.

**Rattanan Saengchan** received the B.E. degree in electrical engineering from Chulalongkorn University, Bangkok, Thailand, in 2016, and the M.S. degree in electrical and electronic engineering from the Tokyo Institute of Technology, Tokyo, Japan, in 2020.

From 2016 to 2017, he was with Cypress Semiconductor, Bangkok. He is currently with Renesas Electronics Corporation, Tokyo.

**Zhongliang Huang** received the B.E. degree in electrical engineering from the University of Electronic Science and Technology of China, Chengdu, China, in 2016, and the M.S. degree in electrical and electronic from the Tokyo Institute of Technology, Tokyo, Japan, in 2020.

He is currently with Socionext Inc., Tokyo.

Ashbir Aviat Fadila received the B.S. degree in electrical engineering from the Institut Teknologi Bandung, Bandung, Indonesia, in 2015, and the M.S. degree in electrical and electronic engineering from the Tokyo Institute of Technology, Tokyo, Japan, in 2020, where he is currently pursuing the Ph.D. degree.

From 2015 to 2016, he was a Standard Cells Mask Layout Engineer with Marvell Technology Indonesia, Jakarta, Indonesia. From 2016 to 2017, he was a Research Assistant with the Institut Teknologi

Bandung, where he was involved in the research of SoC for IoT application. His current research interests include analog-mixed signals, data converters, and synthesizable analog circuits.

Xiaofan Gu received the B.E. degree in electrical engineering and automation from Wuhan University, Wuhan, China, in 2018, and the M.S. degree in electrical and electronic engineering from the Tokyo Institute of Technology, Tokyo, Japan, in 2020. She is currently with Micron Memory Japan, G.K., Kanagawa, Japan.

**Rui Wu** (Member, IEEE) received the B.S. and M.S. degrees from the University of Electronic Science and Technology of China, Chengdu, China, in 2006 and 2009, respectively, and the Ph.D. degree from the Tokyo Institute of Technology, Tokyo, Japan, in 2015.

From 2015 to 2018, he was a Post-Doctoral Researcher with the Tokyo Institute of Technology. Since 2018, he has been a Full Professor with the National Key Lab of Microwave Imaging Technology, Institute of Electronics, Chinese Academy of

Sciences, Beijing, China. His current research interests include RF/millimeterwave transceivers for radar and high data-rate wireless communications.

Zheng Sun (Graduate Student Member, IEEE) received the B.S. degree in information engineering from Southeast University, Nanjing, China, in 2014, and the M.S. degree in information, production, and systems engineering from Waseda University, Tokyo, Japan, in 2015. He is currently pursuing the Ph.D. degree in electrical and electronic engineering with the Tokyo Institute of Technology, Tokyo, Japan.

He has been involved in low-power RF, mixedsignal, and digital PLL designs. His current interests include transceivers for Bluetooth low energy,

LC-VCO for IoT applications, and harmonic suppression techniques for the power amplifier.

**Yun Wang** (Member, IEEE) received the B.S. and M.S. degrees from the University of Electronic Science and Technology of China, Chengdu, China, in 2011 and 2014, respectively, and the Ph.D. degree in physical electronics from the Tokyo Institute of Technology, Tokyo, Japan, in 2019.

He was an Intern with the Pohang University of Science and Technology, Pohang, South Korea, in 2013, and Device Technology Laboratories, NTT Corporation, Atsugi, Japan, in 2016. He is currently a Post-Doctoral Researcher with the Tokyo Institute of Technology. His research interests include CMOS radio frequency

(RF)/millimeter-wave wireless systems, 5G phased-array mobile system, and satellite communication (SATCOM).

Dr. Wang was the recipient of the IEICE Best Paper Award in 2018 and the Best Student Paper Award (1st Place) at the 2019 IEEE Radio Frequency Integrated Circuits Symposium (RFIC). He also serves as a Reviewer for IEEE JOURNAL OF SOLID-STATE CIRCUITS, IEEE TRANSACTIONS ON CIRCUITS AND SYSTEMS I, and the IEEE TRANSACTIONS ON MICROWAVE THEORY AND TECHNIQUES.

Yuncheng Zhang (Graduate Student Member, IEEE) received the B.S. and M.E. degrees in electrical engineering from the University of Science and Technology of China (USTC), Hefei, China, in 2013 and 2016, respectively. He is currently pursuing the Ph.D. degree with the Tokyo Institute of Technology, Tokyo, Japan.

His research interests include power-efficient wireless transceivers, all-digital phase-locked loops, and analog-to-digital converters.

**Dongwon You** (Student Member, IEEE) received the B.S. degree in electrical and computer engineering from Ajou University, Suwon, South Korea, in 2017, and the M.S. degree in electrical and electronic engineering from the Tokyo Institute of Technology, Tokyo, Japan, in 2019, where he is currently pursuing the Ph.D. degree in electrical and electronic engineering.

His current research interests include CMOS analog/RF/millimeter-wave transceiver systems, multiple-in-multiple-out (MIMO), mixed-signal,

wireless communication, and device modeling.

Science and Technology of China, Chengdu, China, in 2016, and the M.E. degree from the Tokyo Institute of Technology, Tokyo, Japan, in 2018, where he is currently pursuing the Ph.D. degree. His current research interests include mixed-signal

integrated circuits and frequency synthesizers. Mr. Huang is a scholarship recipient of the Watanuki International Scholarship Foundation in

Hongye Huang (Graduate Student Member, IEEE) was born in Guilin, China, in 1994. He received

the B.E. degree from the University of Electronic

the fiscal year 2020.

**Bangan Liu** (Member, IEEE) received the B.Eng. degree from Northwestern Polytechnical University, Xi'an, China, in 2011, the M.S. degree from the University of Science and Technology of China, Hefei, China, in 2014, and the Ph.D. degree from the Tokyo Institute of Technology, Tokyo, Japan, in 2019.

He was an Intern with the Apple Japan Design Center, Tokyo, in 2019. He is currently with Qualcomm Inc., San Diego, CA, USA, where he is involved in the development of high-performance cellular communication systems. His research inter-

ests include high-performance frequency synthesizers, fully synthesizable analog/RF circuits, high-performance wireless transceivers, and digital intensive/digitally assisted mixed-signal systems.

**Naoki Oshima** (Member, IEEE) received the B.E. and M.E. degrees in electrical engineering from Doshisha University, Kyoto, Japan, in 2006 and 2008, respectively.

In 2008, he joined NEC Corporation, Kawasaki, Japan, where he is currently with the System Platform Research Laboratories. His current research interests include RF circuit design for wireless communications, especially ultra-wideband and millimeter-wave applications.

Dr. Oshima is also a member of the Institute of Electronics, Information and Communication Engineers, Japan.

Keiichi Motoi (Member, IEEE) received the B.S. and M.S. degrees in physics from Keio University, Yokohama, Japan, in 2008 and 2010, respectively.

He joined NEC Corporation, Kawasaki, Japan, in 2010, where he has been engaged in the research and development of RF modules and RFIC circuits for wireless communication. His current interests include high-efficiency power amplifier architecture and IC/module implementation for mobile base stations and multi-mode/multi-band transceiver ICs for software-defined-radio systems.

Mr. Motoi is also a member of the Institute of Electronics, Information, and Communication Engineers (IEICE), Japan.

**Tomoya Kaneko** (Member, IEEE) received the B.S. degree in physics from the Tokyo University of Science, Tokyo, Japan, in 1984, and the M.S. degree in science from the University of Tsukuba, Tsukuba, Japan, in 1986.

He joined NEC Corporation, Kawasaki, Japan in 1986, where he has been engaged in the design and development of MMICs, MCMs, and sub-systems for radio communication systems. He is currently an Executive Specialist with the Wireless Network Development Division, NEC Corporation.

His current interests are millimeter-wave technologies and massive multiplein-multiple-out (MIMO) considering their application to gNB.

Mr. Kaneko has been serving as a TPC Member and an Overseas Advisor of the IEEE BiCMOS and Compound Semiconductor Integrated Circuits and Technology Symposium (BCICTS).

Atsushi Shirane (Member, IEEE) received the B.E. degree in electrical and electronic engineering and the M.E. and Ph.D. degrees in electronics and applied physics from the Tokyo Institute of Technology, Tokyo, Japan, in 2010, 2012, and 2015, respectively.

From 2015 to 2017, he was with Toshiba Corporation, Kawasaki, Japan, where he developed an 802.11ax Wireless LAN RF transceiver. From 2017 to 2018, he was with Nidec Corporation, Kawasaki, where he researched intelligent motor