# Energy Efficient Startup of Crystal Oscillators Using Stepwise Charging

Joeri B. Lechevallier<sup>®</sup>, *Graduate Student Member, IEEE*, Harijot Singh Bindra<sup>®</sup>, *Member, IEEE*, Ronan A. R. van der Zee<sup>®</sup>, *Member, IEEE*, and Bram Nauta<sup>®</sup>, *Fellow, IEEE*

*Abstract*—Crystal oscillators can be started up quickly by using energy injection techniques. However, the generation of the injection waveform, as well as driving the large capacitive load formed by the crystal, costs a large amount of energy. This article applies the concept of stepwise charging to reduce the energy required to drive the crystal. The energy required to generate the injection waveform by self-timed injection is reduced by using a discrete-time dynamic-bias comparator which uses a simple offset calibration method. Furthermore, the bridge switch resistance is varied dynamically through self-timed control logic to alleviate the accuracy-speed tradeoff. A prototype was manufactured in a 65-nm (triple-well) CMOS technology, which was tested with various crystals ranging from 24 to 50 MHz, improving upon the state of the art in energy consumption.

*Index Terms*— Capacitive load, crystal oscillators, duty cycling, energy injection, Internet of Things (IoT), low power, startup energy, startup time, stepwise charging.

#### I. INTRODUCTION

**E** NERGY is scarce in low-power wireless systems, such as wireless sensor nodes for Internet of Things (IoT), since they are usually powered from, e.g., a battery or energy harvester. To maximize battery life-or achieve a battery size reduction for the same lifetime-it is important to minimize the system's (average) power consumption. One method to minimize the power consumption is duty cycling, in which the device spends most of the time in a low-power sleep mode, only waking up briefly for transmit/receive events [1]. The required time to wake-up and the associated energy consumption can be a significant part of the overall energy consumption, especially if the transmit/receive events are short. One of the circuit blocks that has to be started when the device wakes up is the crystal oscillator that serves as a frequency reference. While the high-quality factor of a crystal resonator allows excellent phase noise, it also implies a long startup time. Even though the startup time of practical crystal oscillators has been pushed toward the lower limit in the recent literature, their startup energy consumption is still large.

Manuscript received September 16, 2020; revised November 29, 2020 and January 27, 2021; accepted February 15, 2021. This article was approved by Associate Editor Danielle Griffith. This work was supported by STW, the Dutch Technology Foundation, under Project 13769. (*Corresponding author: Ronan A. R. van der Zee.*)

The authors are with the Integrated Circuit Design Group, University of Twente, 7522NB Enschede, The Netherlands (e-mail: ronan.vanderzee@utwente.nl).

Color versions of one or more figures in this article are available at https://doi.org/10.1109/JSSC.2021.3061032.

Digital Object Identifier 10.1109/JSSC.2021.3061032

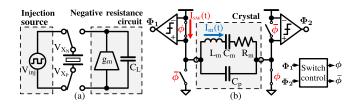

Fig. 1. Generic crystal oscillator.

This article presents techniques to reduce the energy required to start up crystal oscillators.

A generic crystal oscillator is shown in Fig. 1. The fundamental resonance mode of the crystal is usually modeled as a series *RLC* circuit that represents the mechanical resonance mode, in parallel to a capacitance  $C_P$  that models the crystal parasitics. The active circuit provides a capacitive load  $C_{\text{Load}}$  as specified by the crystal manufacturer, as well as a transconductance  $g_m$  to realize a negative resistance  $R_N$  that is large enough to compensate the crystal losses as to sustain oscillation. When the oscillator is started, the amplitude  $\hat{I}_m$  of the motional current  $I_m(t)$  grows from its initial value  $I_m(0)$  to the steady-state amplitude  $\hat{I}_{m,SS}$ , provided that the magnitude of  $R_N$  is larger than the crystal  $R_m$ . Up to recently, startup was typically achieved with a relatively low magnitude of  $R_N$  and from a small initial condition  $I_m(0)$  (circuit noise). This results in lengthy startup times in the order of milliseconds [2]–[7].

The startup time can be decreased by increasing the magnitude of  $R_N$  by changing  $g_m$  and/or  $C_{Load}$  during startup. The minimum startup time that can be achieved in this way is normally limited by  $C_P$  [7]–[11]. This limit can be overcome by making the active circuit appear inductive to (partially) cancel  $C_P$ . This can be achieved by capacitive loading of the internal nodes of a multistage amplifier [9], [10], [12], [13] or adding an active inductor circuit [14]. Although these solutions can achieve very low startup energy, it is difficult to exactly compensate  $C_P$ , resulting in relatively long startup times.

The fastest and most energy efficient circuits use an injection source to pre-energize the crystal, as shown in Fig. 2(a). By applying a voltage at exactly the resonance frequency for a duration  $T_{inj}$ , the amplitude  $\hat{I}_m(t)$  increases with every cycle, as shown in Fig. 3, ideally reaching the desired steady-state swing after  $T_{inj}$ . To achieve this, the injection signal should be in phase with the motional current  $I_m(t)$  during the entire injection period  $T_{inj}$ . Any injection frequency error leads to a phase shift building up over time, which reduces the motional current growth rate and maximum achievable amplitude.

0018-9200 © 2021 IEEE. Personal use is permitted, but republication/redistribution requires IEEE permission. See https://www.ieee.org/publications/rights/index.html for more information.

Fig. 2. (a) Energy injection concept. (b) Self-timed injection concept.

The injection source is usually a separate oscillator, with various techniques applied to achieve sufficient frequency accuracy over process, voltage and temperature (PVT) variations. Early publications attempt to calibrate the injection oscillator [15], [16]. Deliberately spreading the injection frequency over a certain bandwidth by chirping [8], [9] or dithering [14], [17], [18] guarantees crystal excitation over injection frequency variations. However, most of the energy is wasted as it is not within the crystal bandwidth. A more efficient method is to reduce the accumulated phase difference over time by injecting for a short time [19]. The resulting small crystal output voltage is then used to realigning the injection source to supply a further burst of energy once [20] or multiple times [21], [22].

Another method that does not require any precise injection oscillator is self-timed injection [23], as shown in Fig. 2(b). This technique uses comparators to detect the zero crossings of the motional branch current of the crystal, and uses this information to switch the voltage over the crystal. This ensures that the phases of  $V_{inj}$  and  $I_m$  are aligned and do not drift over time.

Regardless of the technique used for energy injection, in the most energy efficient implementations in the literature, more than 75% of the startup energy stems from driving the crystal [19], [20], [23]. Part of this energy is actually stored in the crystal oscillation, but most of it is lost. A small part of these losses stems from the switch drivers, as well as a negligible energy loss in the motional resistance. Most of the energy, however, is wasted in driving the large capacitive load at the crystal terminals, consisting of, e.g.,  $C_{\text{Load}}$ ,  $C_{\text{P}}$ , and parasitics.

To reduce this overhead,  $C_{\text{load}}$  can be disabled during startup [14], [23], and careful design minimizes the parasitics consisting of, e.g., on-chip and printed circuit board (PCB) traces or electrostatic discharge (ESD) protection. Nevertheless, the crystal  $C_P$  (typically in the order of pFs) is always charged and discharged at least hundreds of times during startup, wasting energy in each switching cycle.

Another way to reduce these  $CV^2$  losses is reducing the injection voltage. However, a large supply voltage is desirable, since the rate at which  $\hat{I}_m$  grows is proportional to  $V_{DD}$ , and hence startup time reduces. The drawback, however, is that the energy consumption scales with the supply voltage *squared*.

In this article, we propose a technique to reduce the energy required to drive the crystal by charging and discharging the output load in multiple steps. This technique is termed stepwise charging [24]. Furthermore, we propose improvements to the self-timed injection technique. This allows quick startup by using a large injection voltage without the associated energy

Fig. 3. Ideal energy injection waveforms [22].

penalty. Section II covers the theory of stepwise charging and its application to crystal oscillator startup. Section III covers the integration of the technique with a self-timed injection circuit, along with the improvements. Measurements on the manufactured prototype are covered in Section IV, then Section V discusses the results, and finally concluded by Section VI.

# II. CRYSTAL OSCILLATOR STARTUP WITH STEPWISE CHARGING

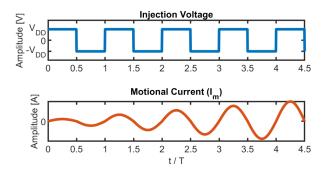

To achieve the injection waveforms shown in Fig. 3, both crystal terminals are alternately connected to the supply voltage and ground, as shown in Fig. 4(a). In each switch cycle, energy is injected into the crystals motional branch, consisting of  $L_{\rm m}$ ,  $C_{\rm m}$ , and  $R_{\rm m}$ . However, each switch cycle also charges various capacitors, including  $C_{\rm P}$ ,  $C_{\rm Load}$ , and parasitic capacitances from, e.g., the PCB, ESD protection, and bondpad capacitances, as illustrated in Fig. 4(b).

This circuit can be simplified by realizing that, from a switching point of view, the motional branch can be seen as an open due to the large inductance of  $L_{\rm m}$  (typically in the mH range). Furthermore, all capacitors can be lumped into two single-ended capacitances  $C_{\rm SE}$  to ground at each terminal, as well as a differential capacitance  $C_{\rm Diff}$ , as shown in Fig. 4(c).

Charging these capacitors costs energy. At every switch cycle (every T/2), one of the  $C_{\rm SE}$  is discharged and the other is charged to  $V_{\rm DD}$ , such that an amount of charge equal to  $\Delta Q = C \Delta V = C_{\rm SE} V_{\rm DD}$  is drawn from the supply. Furthermore,  $C_{\rm Diff}$  is charged from  $-V_{\rm DD}$  to  $+V_{\rm DD}$ , costing an amount of charge  $\Delta Q = C_{\rm Diff} \Delta V$ , with  $\Delta V = 2V_{\rm DD}$ . By adding the individual contributions, the energy delivered by the supply to charge  $C_{\rm SE}$  and  $C_{\rm Diff}$  in each *half* crystal cycle can be calculated as  $E = \Delta Q V_{\rm DD} = (C_{\rm SE} + 2C_{\rm Diff})V_{\rm DD}^2$ .

#### A. Stepwise Charging

The energy required to alternately charge and discharge a capacitor can be reduced by stepwise charging [24]. If, instead of directly charging a capacitor from 0 to  $V_{\text{DD}}$ , the capacitor is charged and discharged in N sequential steps of size  $V_{\text{DD}}/N$ , the energy consumption is reduced from  $CV^2$  to  $CV^2/N$ . This technique was successfully applied in several fields, including ADCs [25], [26], ultrasonic transceivers [27], touch-screen readout circuits [28], and class-D amplifiers [29].

Fig. 4. (a) H-bridge. (b) Model including parasitic capacitors. (c) Equivalent model of capacitors during switch cycle.

Fig. 5. Stepwise charging concept.

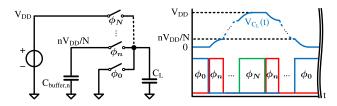

To understand this technique, consider a capacitor  $C_{\rm L}$  that is periodically charged to  $V_{\rm DD}$  and discharged to 0, as shown in Fig. 5. Before being fully charged to  $V_{\rm DD}$ ,  $C_{\rm L}$  is sequentially charged through each of the intermediate steps of size  $V_{\rm DD}/N$ from (large) buffer capacitors  $C_{\rm buffer,n}$  (with n = [1, N - 1]), assuming they are charged to  $n(V_{\rm DD}/N)$ . In this case, the supply  $V_{\rm DD}$  only has to supply an amount of charge equal to  $C_{\rm L}\Delta V = C_{\rm L}V_{\rm DD}N$ , which is N times less than if it would be directly charged to  $V_{\rm DD}$ , and hence N times less energy.

If  $C_{\text{buffer},n}$  is charged to  $n(V_{\text{DD}}/N)$ , the amount of charge on  $C_{\text{buffer},n}$  is balanced over an entire cycle, as a packet of charge equal to  $C_{\text{L}}V_{\text{DD}}N$  is *removed* from each  $C_{\text{buffer},n}$  every time  $C_{\text{L}}$  is *charged*, but the same amount of charge is *added* every time  $C_{\text{L}}$  is *discharged*.

When  $C_{\text{buffer},n}$  is initially empty, it delivers no charge in the first stepwise *charging* cycle. However, a packet of charge is dumped onto  $C_{\text{buffer},n}$  in the *discharge* cycle, thereby increasing the amount of charge stored on  $C_{\text{buffer},n}$ . In this way, the voltage on  $C_{\text{buffer},n}$  ( $V_{C_{\text{buffer},n}}$ ) converges toward  $nV_{\text{DD}}N$  with each consecutive cycle in what is essentially a self-stabilizing process [24]. It takes a time in the order of  $N(C_{\text{buffer},n}/C_L)$ for  $V_{C_{\text{buffer},n}}$  to stabilize to  $n(V_{\text{DD}}/N)$  [30].

$C_{\text{buffer},n}$  should not be too large, as it would take a long time before  $V_{C_{\text{buffer},n}}$  settles toward  $nV_{\text{DD}}N$ , which would compromise energy saving in the first few cycles. On the other hand,  $C_{\text{buffer},n}$  should be large enough  $(C_{\text{buffer},n} \gg C_{\text{L}})$  to be able to fully charge  $C_{\text{L}}$  to  $n(V_{\text{DD}}/N)$  as to save a factor Nin energy.

Note that the stepwise charging process requires no additional energy; no net charge is delivered by the supply, except when making the final step to  $V_{\text{DD}}$  [24]. All energy that is used to charge  $C_{\text{buffer},n}$  is recycled from  $C_{\text{L}}$ , which energy would otherwise have been wasted by dumping its charge to ground.

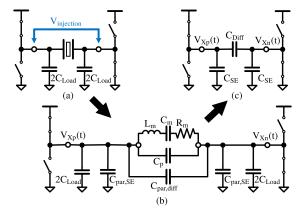

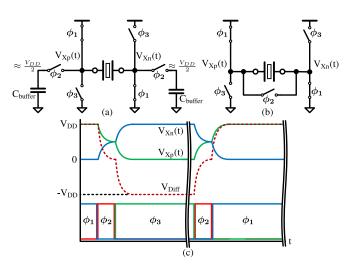

Fig. 6. (a) Two-step charging. (b) Simplified two-step charging. (c) Timing diagram.

## B. Application to XO Startup

The stepwise charging concept can be applied to crystal oscillators in several ways, since part of the capacitive load is differential and part of it is single ended, as discussed in the previous section. A few possible implementations of stepwise charging are discussed in Section II-A.

1) Two-Step Charging: Consider the case shown in Fig. 6(a), where the crystal is (dis)charged in two discrete time steps. The crystal node is connected to a voltage  $V_{DD}2$  before it is connected to the supply. Applying the model shown in Fig. 4(c), the energy to charge  $C_{SE}$  can be calculated as  $E_{SE} = C_{SE}V_{DD}^2$ , while  $C_{Diff}$  only has to be charged from 0 to  $V_{DD}$ . This results in  $E_{Diff} = C_{Diff}V_{DD}^2$ , saving a factor 2 compared with the conventional case.

Note that in this case, one of the crystal terminals is charged, while the other is discharged, and  $C_{\text{diff}}$  is effectively short-circuited. Therefore, the schematic can be simplified to Fig. 6(b), shorting the crystal terminals by a single switch and leaving out the buffer capacitors to save switch and capacitor area for the same energy reduction.

2) Four-Step Charging: Although (dis)charging in two steps halves the energy consumption, the supply still has to charge  $C_{\text{Diff}}$  from 0 to  $V_{\text{DD}}$  in a step equal to  $V_{\text{DD}}$ . The energy consumption can be further reduced by increasing the number of time steps to 4, by first charging  $C_{\text{Diff}}$  to  $V_{\text{DD}}$ 2, as shown in Fig. 7.  $C_{\text{SE}}$  still experiences the same voltage steps  $\Delta V$ , and hence equal energy consumption, but the supply is charging  $C_{\text{diff}}$  only from  $V_{\text{DD}}$ 2 to  $V_{\text{DD}}$ , costing only  $E_{\text{diff}} = C_{\text{Diff}} V_{\text{DD}}^2$ 2. Please note that the time that the crystal is connected to  $C_{\text{buffer}}$ is much shorter than the time that it is connected to  $V_{\text{DD}}$ .

By using stepwise charging, all energy stored in  $C_{\text{Diff}}$  and  $C_{\text{SE}}$  is redistributed before making the final step that charges either  $X_{\text{P}}$  or  $X_{\text{N}}$  toward the supply voltage. A comparison of the theoretical energy consumption using the proposed charging techniques is listed in Table I. Note that the total reduction factor for four-step charging depends on the ratio  $C_{\text{SE}}/C_{\text{Diff}}$  since a factor 2 is saved in charging  $C_{\text{SE}}$  but a factor 4 in  $C_{\text{Diff}}$ .

$\psi_{1}$   $\psi_{2}$   $\psi_{2}$   $\psi_{3}$   $\psi_{2}$   $\psi_{2}$   $\psi_{2}$   $\psi_{2}$   $\psi_{3}$   $\psi_{2}$   $\psi_{2}$   $\psi_{3}$   $\psi_{2}$   $\psi_{2}$   $\psi_{4}$   $\psi_{4}$   $\psi_{5}$   $\psi_{6}$   $\psi_{2}$   $\psi_{4}$   $\psi_{4}$   $\psi_{5}$   $\psi_{6}$   $\psi_{4}$   $\psi_{5}$   $\psi_{5}$   $\psi_{5}$   $\psi_{5}$   $\psi_{4}$   $\psi_{5}$   $\psi_{5$

Fig. 7. Four-step charging schematic and timing diagram.

TABLE I

ENERGY DELIVERED BY SUPPLY PER 1/2 CYCLE

|                 | C <sub>Diff</sub>             | C <sub>SE</sub>             | Total reduction<br>factor |

|-----------------|-------------------------------|-----------------------------|---------------------------|

| Conventional    | $2C_{Diff}V_{DD}^2$           | $C_{SE}V_{DD}^2$            | 1                         |

| 2-step charging | $C_{Diff}V_{DD}^2$            | $\frac{1}{2}C_{SE}V_{DD}^2$ | 2                         |

| 4-step charging | $\frac{1}{2}C_{Diff}V_{DD}^2$ | $\frac{1}{2}C_{SE}V_{DD}^2$ | 2-4                       |

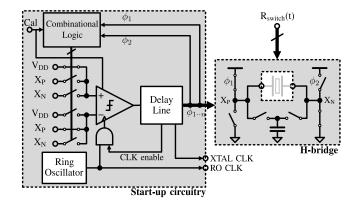

Fig. 8. Startup circuit block diagram.

## **III. PROTOTYPE CIRCUIT IMPLEMENTATION**

The proposed four-step injection is integrated in a crystal oscillator circuit as a proof of concept. A block diagram of the startup circuitry is shown in Fig. 8. The startup principle is self-timed injection, where the crystal voltage is reversed every time the motional branch current changes sign [23]. The change of the sign of the crystal current is detected by a comparator that senses the voltage over the bridge switches. At every positive comparator decision, the delay line generates the switch timing for the H-bridge to go through the stepwise charging sequence as described in Section II-B2).

The work in [23] uses a relatively large differential pair to achieve an acceptable offset, which decreases speed and increases power consumption. In this work, we propose to use a discrete-time comparator, running at a much higher (non-critical) clock rate than the crystal frequency. The delay from zero-crossing to comparator output is maximum one comparator clock cycle, which is lower than the delay for

Fig. 9. Comparator and offset compensation schematic.

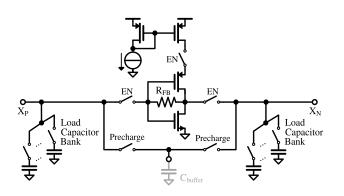

the continuous comparator used in [23]. A simple offset calibration scheme is used to reduce the offset, allowing the input differential pair to be relatively small, thereby increasing the energy efficiency of the comparator. A single comparator is used, with combinational logic and switches connecting the appropriate nodes to the comparator inputs. A calibration mode connects both comparator inputs to  $V_{\rm DD}$  to allow offset compensation.

The injection timing is governed by the crystal through the zero-crossings of  $I_m$ , and not the comparator clock source. Hence, the frequency stability and phase noise requirements on the clock source are very relaxed, as long as it is running at a rate well above the crystal frequency. A simple minimum-sized current-starved ring oscillator (RO) is used, which is tunable between 200 MHz and 2 GHz. This comparator clock is disabled during stepwise charging (and steady-state operation) to save comparator energy and prevent false comparator decisions.

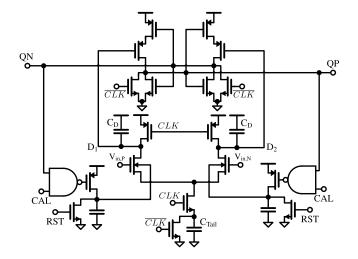

## A. Comparator

The comparator is implemented as a dynamic bias latchtype comparator, as shown in Fig. 9, which offers high speed for a low energy consumption [31]. The comparator does not use any static bias current. Furthermore, by setting the ratio  $C_{\rm D}/C_{\rm Tail}$ , the pre-amplifier is quenched during the comparison time as soon as the common-mode voltage drop  $\Delta V_{\rm D}$  at the pre-amplifier drain nodes  $D_1$  and  $D_2$  triggers the latch stage. This reduces the amount of charge required per comparison to  $C_{\rm D}\Delta V_{\rm D}$  instead of the conventional  $C_{\rm D}V_{\rm DD}$ . The comparator is sized for up to 2-GHz clock speed and 0.3-mV input-referred noise, which is low enough to detect zero-crossings of  $I_{\rm m}$  in the first few cycles of startup. Comparator noise mainly affects the timing in the first few cycles, when the detected voltage is small due to the small motional current. As the amplitude of the motional current grows, the error due to noise becomes smaller. Since energy is injected over hundreds of cycles, any variation in  $\hat{I}_{m,SS}$  due to variation in the initial cycles is small. Comparator noise is dominated by thermal noise like in [31]. (Low frequency) flicker noise is suppressed by the

Fig. 10. Delay line block and timing diagram.

offset calibration that runs at the beginning of each startup event. Note that any residual low-frequency noise components might slightly shift the phase of the injected waveform in the beginning, but this phase error does not accumulate over time.

By tuning the body potentials of the input differential pair, the offset can be reduced [32], [33]. In this work, both comparator inputs are shorted to  $V_{\rm DD}$  during calibration, and depending on the comparator output, using a triple-well structure, one of the body potentials is increased, such that the offset converges toward zero. The number of clock cycles for offset calibration is programmable, and is set high enough to cancel the expected worst case offset. The calibration is run every time the crystal oscillator is started as to ensure that the offset is affected by neither temperature variations nor leakage of the capacitors that store the body potential. Monte-Carlo simulation without and with offset cancellation shows a reduction of the 1- $\sigma$  offset from 7.5 mV to only 72  $\mu$ V.

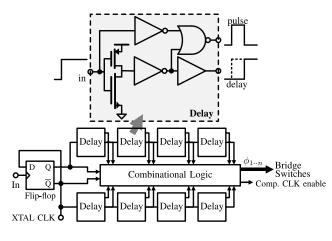

# B. Delay Line

Fig. 10 shows the block diagram of the delay line. Each positive comparator decision triggers the D flip-flop, which toggles the bridge output with intermediate stepwise charging. Delay elements consisting of inverters with long channel length generate pulses and delayed signals [25], which are used to generate the non-overlapping timing signals  $\phi_{1...n}$  for the bridge through combinational logic.

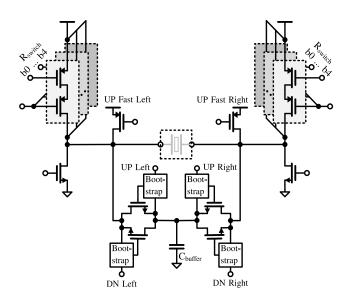

# C. Bridge

Fig. 11 shows the schematic of the bridge. In addition to the switch timing, as shown in Fig. 7, large switches ("UP Fast Left" and "UP Fast Right") to  $V_{DD}$  are briefly enabled to quickly pull up the crystal nodes before the relatively high-resistance sensing switches take over. These sensing switches are binary tunable in a binary fashion over a range of 18–600  $\Omega$  and enable measurement of the motional current  $I_m(t)$ .

The switches that connect the crystal to  $C_{\text{buffer}}$  are bootstrapped to achieve low switch resistance. The voltage at the crystal node is lower than  $V_{C_{\text{buffer}}}$  (typically  $\sim V_{\text{DD}}/2$ ) during stepwise charging, but higher during stepwise discharging.

Fig. 11. Bridge schematic.

If the switch would be bootstrapped with respect to a fixed terminal this could cause the voltage over the gate oxide to become higher than  $V_{DD}$ , which could cause breakdown of the gate oxide. To prevent this, the stepwise charging switches are implemented as two pairs of bootstrapped switches that are bootstrapped with respect to  $V_{C_{buffer}}$  and the crystal nodes for the charge and discharge cycle, respectively.

The analysis on stepwise charging in Section II-B assumes full settling of the crystal node when stepwise charging and discharging. This can be achieved with very large switches, which, however, not only requires large drivers and hence increased power consumption but also introduces a significant OFF-state leakage current. This current flows through the measurement resistor, generating an offset for the zero-crossing detection of  $I_m$ . This imposed an upper limit on the switch size.

The switch size also has an influence on the energy reduction. The theoretical energy reduction calculations presented in Section III-B assume full settling to the stepwise voltages. Assuming that  $C_{\text{buffer}}$  is much larger than the capacitive loading ( $C_{\text{buffer}} \gg C_{\text{diff}}$  and  $C_{\text{SE}}$ ), the intermediate steps settle exponentially with a time constant  $\tau = R_{\text{stepwise}}C_{\text{eff}}$ , where  $R_{\text{stepwise}}$  is the resistance of the bootstrapped switches and  $C_{\text{eff}}$ is the effective capacitive load  $C_{\text{eff}} = C_{\text{SE}} + C_{\text{diff}}$  at one of the crystal terminals.

For a settling time  $t_{\text{step}}$ , when charging from 0 to  $V_{\text{DD}}2$ , instead of reaching  $V_{\text{DD}}2$ , only  $(V_{\text{DD}}/2)(1 - e^{-(t_{\text{step}}/\tau)})$  is reached. More charge is drawn from the supply, and the energy saving is reduced to  $\frac{1}{2}(1 - e^{-(t_{\text{settle}}/\tau)})$ . Suitable values for the settling time are 2–4 time constants [24].

As discussed in Section II-B,  $C_{\text{buffer}}$  should neither be too large, as it would take a long time before it is charged and energy is saved, nor too small, as it would not be able to fully charge the load. The optimum depends on the number of startup cycles, output load, and overhead, and can be found by simulation. However, the total energy consumption is only weakly dependent on the size of  $C_{\text{buffer}}$ , which is

Fig. 12. Circuit block diagram and timing diagram.

Fig. 13. Steady-state oscillator schematic.

implemented as a fixed capacitor of 137 pF in our design. For the 32-MHz crystal,  $C_{\text{buffer}}$  is charged to 90% of its final value in 20 cycles. MOS and metal-oxide-metal (MOM) capacitors are stacked on top of each other to minimize chip area. Note that the load capacitor bank can be partially reused for this purpose. MOS leakage discharges  $C_{\text{buffer}}$  with a time constant of about 17 ms. Because of the relatively long time of inactivity between successive startup events, this means that  $C_{\text{buffer}}$  is (almost) completely discharged every time the crystal oscillator is started.

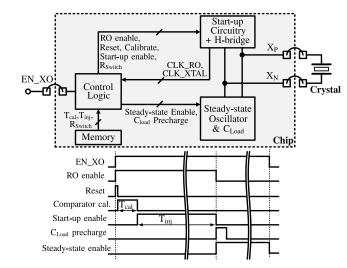

## D. Full-Chip Overview

A block diagram of the entire chip, as well as a timing diagram of the startup sequence, is shown in Fig. 12. A single enable signal starts the crystal oscillator. When this signal (EN\_XO) is enabled, the control logic block resets all timers and enables the RO. Comparator offset calibration is active for a programed amount of cycles of the RO,  $T_{cal}$ . After this, the self-timed injection startup circuitry is enabled to inject energy in the crystal. The value of  $R_{switch}$  is varied through programed values during the first 16 cycles of startup, reducing  $R_{switch}$  as the amplitude of the oscillation  $I_m$  grows. This alleviates the tradeoff between current detection sensitivity and delay encountered in [23]. After a programed amount of cycles

Fig. 14. Simulated waveforms for a 32-MHz crystal, injecting for 400 cycles.

TABLE II Simulated Energy Breakdown for a 32-MHz Crystal for 400 Drive Cycles

| Tashniqua                          | w/o stepwise | Stepwise charging     |                |  |  |  |

|------------------------------------|--------------|-----------------------|----------------|--|--|--|

| Technique                          | charging     | Same T <sub>inj</sub> | Same Amplitude |  |  |  |

| T <sub>inj</sub> (us)              | 10.36        | 10.36                 | 12.66          |  |  |  |

| Bridge (nJ)                        | 7.98         | 4.63                  | 5.99           |  |  |  |

| Switch drivers +<br>bootstrap (nJ) | 0.20         | 0.48                  | 0.59           |  |  |  |

| Crystal $(\hat{I}_m)$ (nJ)         | 1.35         | 0.91                  | 1.35           |  |  |  |

| Capacitive load (nJ)               | 6.43         | 3.24                  | 4.05           |  |  |  |

| Startup circuits (nJ)              | 1.63         | 1.65                  | 2.01           |  |  |  |

| Total (nJ)                         | 9.61         | 6.28                  | 8.00           |  |  |  |

of the crystal, as counted from CLK\_XTAL, the steady-state oscillator is enabled.

The steady-state oscillator core is a Pierce oscillator, as shown in Fig. 13. Switches enable the bias current and (dis)connect the oscillator core to the crystal. The 31-pF load capacitor bank consists of 1-pF unit elements to accommodate crystals with various load capacitances. To reduce the time required to (dis)charge  $C_{\text{load}}$ , the output nodes are briefly connected to  $C_{\text{buffer}}$  to quickly charge these nodes to approximately  $V_{\text{DD}2}$  when the steady-state oscillator is enabled.

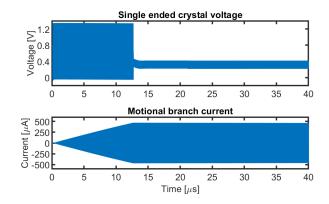

# E. Simulation Results

Fig. 14 shows transient simulation results for a 32-MHz crystal, showing swift settling to steady state after injecting energy for 400 programed cycles. Full-chip transient noise simulations over 100 different noise seeds show a worst case variation of  $\hat{I}_{\rm m}(T_{\rm inj})$  within 3.1% of its nominal value, with a 1- $\sigma$  of 1.1%. This shows that neither comparator noise nor other noise sources significantly affect the startup process. Monte-Carlo simulation over mismatch shows a variation of  $\hat{I}_{\rm m}(T_{\rm inj})$  with  $\sigma = 1.4\%$  and a worst case deviation less than 5%, which demonstrates robustness against mismatch. Simulations over process corners show, without changing any settings, less than 15% variation of  $\hat{I}_{\rm m}(T_{\rm inj})$ .

Table II shows the simulated energy breakdown, with and without stepwise charging. To simulate the case without stepwise charging, the delay line is modified to skip stepwise charging. The rest of the circuitry is identical and includes the proposed improvements to self-timed

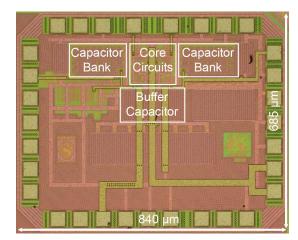

Fig. 15. Chip photograph.

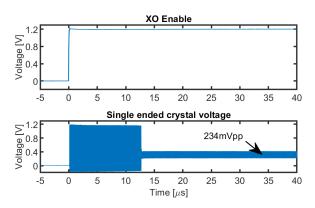

Fig. 16. Measured single-ended output for a 32-MHz crystal, injecting for 400 cycles at T = 20 °C.

injection. The contribution of the bridge energy to the total energy consumption is divided into three parts. First is the overhead of switch drivers and bootstrap circuits. Second, the energy that is stored in the crystal calculated as  $\frac{1}{2}L_{\rm m}\hat{I}_{\rm m}^2$ , and lastly, the energy required to drive the capacitive load.

For an equal number of drive cycles, the capacitive losses are reduced by a factor > 2. However, the amplitude at the fundamental frequency of the injection waveform is lower than  $(4/\pi)V_{\rm DD}$  due to the time required for stepwise charging. Therefore, for the same  $T_{ini}$ , the reached amplitude and crystal energy are lower when using stepwise charging compared with conventional injection. A larger number of drive cycles are required, to reach the same amplitude, as shown in the third column of Table II. The increased injection time costs additional energy in startup circuitry as well as more cycles of driving the capacitive load. Nonetheless, the overall energy consumption is lower when using stepwise charging. Combined with the other proposed techniques, this results in a low startup energy consumption. This work aims for minimum  $E_{\text{start}}$  and, therefore, implements the four-step charging technique. If chip area is of importance, the two-step charging technique that was proposed in Section II-B can be used instead, at the expense of saving less energy.

Fig. 17. Measured frequency settling for a 32-MHz crystal, for 400 drive cycles at T = 20 °C. (a) Coarse frequency scale. (b) Fine frequency scale.

# **IV. MEASUREMENT RESULTS**

Fig. 15 shows a photograph of the prototype as fabricated in a 65-nm CMOS process. The chip was wirebonded to a QFN package and clamped to a PCB, on which the crystal voltages are buffered by off-the-shelf amplifiers (LTC6268) in unity-gain configuration. The circuit was tested with various crystals in the range of 24–50 MHz in various package sizes, showing reliable startup. The presented measurements are performed using a 24 MHz (TXC 7V-24.000MAAE-T), a 32-MHz crystal (Murata XRCGB32M000F2P00R0), and two different 50-MHz crystals (Abracon ABM3-50.000MHZ-D2Y-F-T and TXC 7M-50.000MAHV-T), respectively.

Fig. 16 shows the measured startup transient for the 32-MHz crystal in a  $2 \times 1.6 \text{ mm}^2$  package. At t = 0, the oscillator enable signal is triggered, and after a brief comparator calibration time of approximately 130 ns, energy injection starts. After the programed 400 drive cycles, the oscillator quickly settles to its steady state.

Fig. 17(a) shows the measured frequency settling, showing frequency variations around the fundamental frequency due to comparator noise during injection. Nevertheless, the frequency converges toward the crystal frequency as the amplitude grows. As with any injection technique, slight frequency variations are visible after switching to steady state, caused by excitation of the crystal spurious tones during injection. Assuming that a phase-locked loop (PLL) would normally filter out these spurs, the frequency settling of the fundamental tone can be measured by choosing the center frequency and demodulation bandwidth such that the spurious tones fall out of band. This measurement is shown in Fig. 17(b), showing quick settling to a frequency error less than 20 ppm.

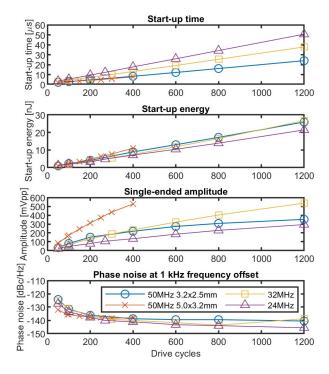

Fig. 18. Measured startup time and energy as well as steady-state amplitude and phase noise against number of drive cycles at 20  $^\circ$ C.

TABLE III Measured Energy Breakdown for Different Crystals for 400 Drive Cycles

| Crystal (MHz) | E <sub>total</sub> (nJ) | E <sub>bridge</sub> (nJ) | E <sub>Start-up</sub> (nJ) |

|---------------|-------------------------|--------------------------|----------------------------|

| 24            | 4.1                     | 3.5                      | 0.6                        |

| 32            | 7.1                     | 5.3                      | 1.8                        |

| 50            | 7.5                     | 5.5                      | 2.0                        |

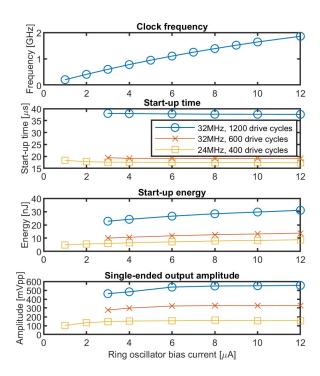

Fig. 18 shows the measured performance as function of the number of programed drive cycles for a few crystals, showing increased amplitude and improved phase noise, at a cost of increased energy consumption. Crystals in larger packages generally have a lower  $L_m$  [17], but a larger  $C_P$ . A lower  $L_m$ implies a larger slope  $d\hat{I}_{\rm m}(t)/dt$ , and the required injection time to reach a given steady-state motional current  $\hat{I}_{m,SS}$ scales proportional with  $L_m$  [19]. Larger crystals, therefore, require a shorter injection time compared with smaller crystals, thereby reducing startup time. On the other hand, the increased  $C_{\rm P}$  implies a larger energy consumption per injection cycle. To reach an equal output amplitude, however, the overall startup energy is lower due to the reduced injection time. Since a fixed delay is used for the generation of the stepwise charging pulses, the effective phase shift of the injection waveform is larger for higher frequency crystals. Hence, the growth in amplitude drops off faster for the 50-MHz crystal, while the amplitude growth of the 24-MHz crystal is closer to linear.

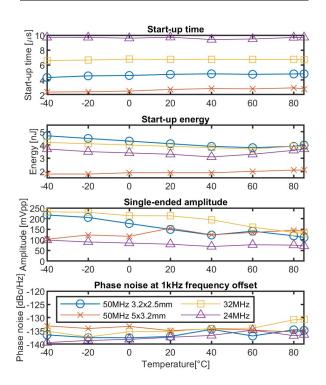

Fig. 19 shows the measured startup time and energy over temperature variations, where the settings are kept constant, except for the data points at 60  $^{\circ}$ C and higher, for which the switch resistance setting is lowered to achieve reliable startup.

The measured energy breakdown is listed in Table III, where  $E_{\text{Bridge}}$  is the energy consumed by the bridge, and  $E_{\text{Start-up}}$

TABLE IV Performance Over Samples for a 32-MHz Crystal for 200 Drive Cycles

| Sample | T <sub>start</sub><br>(μs) | E <sub>start</sub><br>(nJ) | Single-ended<br>Amplitude<br>(mVpp) | Phase noise<br>@ 1kHz<br>(dBc/Hz) |

|--------|----------------------------|----------------------------|-------------------------------------|-----------------------------------|

| 1      | 7.0                        | 3.6                        | 128                                 | -139.5                            |

| 2      | 7.2                        | 3.5                        | 133                                 | -139.9                            |

| 3      | 7.1                        | 3.6                        | 129                                 | -139.4                            |

| 4      | 7.0                        | 3.7                        | 125                                 | -139.4                            |

Fig. 19. Measured startup time and energy as well as steady-state amplitude and phase noise over temperature, for an injection time of 200 cycles (93 for the 50-MHz 5  $\times$  3.2 mm<sup>2</sup> crystal).

comprises the energy consumption by all other blocks (startup circuitry, RO, enable logic, etc.). The number of drive cycles was set to 400 to allow comparison to the simulation results in Table II. To demonstrate robustness over samples, four different dies were tested using identical settings, except for the number of drive cycles, which was set to 200. Table IV lists the measured performance, showing a marginal variation between samples. The spread originates mostly from the steady-state settling time. To demonstrate robustness against RO frequency, performance is measured over RO bias, as shown in Fig. 20.

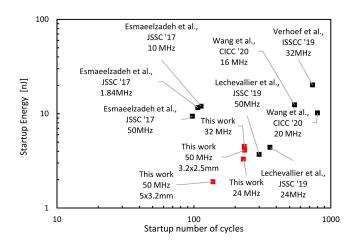

# V. COMPARISON

A fair comparison between different startup techniques is difficult since the startup energy is dependent on the number of drive cycles, which in turn depends on the steady-state swing,  $L_{\rm m}$ ,  $C_{\rm Load}$ , and injection amplitude. To enable fair comparison with the state of the art, the prototype was tested using the same crystal as in [19] and [23] (50 MHz). Lechevallier *et al.* [23] used a 7-pF  $C_{\rm load}$  compared with 9 pF in [19], which resulted in a (9/7) times higher steady-state amplitude

|                                              | JSSC'19<br>[20]               | ISSCC'19<br>[21]                    | JSSC'18<br>[19]                 | ESSCIRC'19<br>[12]                    | CICC '20<br>[13]          | JSSC'19<br>[23]      | This work                                   |         |         |         |

|----------------------------------------------|-------------------------------|-------------------------------------|---------------------------------|---------------------------------------|---------------------------|----------------------|---------------------------------------------|---------|---------|---------|

| CMOS process (nm)                            | 65                            | 55                                  | 65                              | 65                                    | 65                        | 22 FD-<br>SOI        | 65                                          |         |         |         |

| Supply voltage (V)                           | 1.0                           | 1.2                                 | 1                               | 1.2                                   | 1.2                       | 0.8                  | 1.15                                        | 1.2     | 1.2     | 1.2     |

| Core area (mm <sup>2</sup> )                 | 0.07                          | 0.05                                | 0.09                            | 0.006                                 | 0.046                     | 0.02                 | 0.07                                        |         |         |         |

| Frequency (MHz)                              | 54                            | 32                                  | 50                              | 16                                    | 20                        | 50                   | 24                                          | 32      | 50      | 50      |

| Package size (mm)                            | N/A                           | N/A                                 | 5.0x3.2                         | N/A                                   | N/A                       | 5.0x3.2              | 3.2x2.5                                     | 2.0x1.6 | 3.2x2.5 | 5.0x3.2 |

| Load capacitance (pF)                        | 6                             | 6                                   | 9                               | 8                                     | 4                         | 7                    | 12                                          | 6       | 8       | 7       |

| Differential steady-state<br>amplitude (Vpp) | 0.7                           | 0.75                                | 0.25                            | 0.6                                   | N/A                       | 0.32                 | 0.16                                        | 0.26    | 0.30    | 0.32    |

| Steady-state power<br>consumption (µW)       | 198                           | N/A                                 | 195                             | 70                                    | 169                       | 51                   | 19                                          | 70      | 36      | 32      |

| Phase noise at 1 kHz<br>offset (dBc/Hz)      | -139.5                        | N/A                                 | N/A                             | N/A                                   | -146.6 @<br>10kHz         | -123                 | -137.4                                      | -136.9  | -136.2  | -135.5  |

| Start-up time (µs)                           | 19                            | 23                                  | 1.95                            | 150                                   | 30                        | 6                    | 9.7                                         | 7.2     | 4.7     | 2.8     |

| Temperature range (°C)                       | -4085                         | -40-140                             | -4085                           | N/A                                   | -20-100                   | -4085                | -40-85                                      |         |         |         |

| Start-up time variation<br>over temperature  | ±1%                           | ±11%                                | 10%                             | N/A                                   | N/A                       | 23%                  | 3.1%                                        | 2.8%    | 10.3%   | 18.9%   |

| Start-up time (cycles)                       | 1026                          | 736                                 | 98                              | 2400                                  | 600                       | 300                  | 233                                         | 230     | 235     | 138     |

| Start-up Energy (nJ)                         | 35‡                           | 20                                  | 9.4                             | 10.5                                  | 11.1                      | 3.7                  | 3.3                                         | 3.6     | 4.1     | 1.9     |

| Technique                                    | 2-step<br>energy<br>injection | Synchronized<br>energy<br>injection | Precisely<br>timed<br>injection | Negative<br>resistance<br>boost (NRB) | NRB +<br>DPW<br>injection | Self-timed injection | Self-timed injection + stepwise<br>charging |         |         |         |

TABLE V Comparison With Prior Art

† ESTIMATED BY MULTIPLYING STEADY-STATE POWER CONSUMPTION AND START-UP TIME

**‡ INCLUDING CLOCK BUFFER POWER**

Fig. 20. Measured performance against RO bias current at 20  $^\circ\mathrm{C}.$

compared with [19], while startup was not affected since  $C_{\text{load}}$  is disconnected during startup. In this work, we used the same  $C_{\text{load}}$  and output amplitude as [23] in the measurements on the 50-MHz 5 × 3.2 mm<sup>2</sup> crystal. Although this work uses 65-nm technology with a 1.5× higher supply voltage than [23] that used 22-nm technology, startup requires almost 2× less energy and startup is more than 2× faster. Table V compares

Fig. 21. Startup energy versus startup time of the state of the art.

the proposed work with the state of the art. Fig. 21 compares the startup time and energy of crystal oscillators having low startup time (<1000 cycles) and energy (<100 nJ). This work is among the lowest startup times for the lowest energy consumption.

# VI. CONCLUSION

This article presented several techniques to reduce the startup energy of crystal oscillators using energy injection. By using the concept of stepwise charging, the energy consumption associated with (dis)charging the capacitive load is reduced. In addition, the self-timed energy injection technique is improved by the use of a discrete-time, dynamic-bias comparator. This reduces energy consumption and injection delay and allows a simple offset calibration scheme to be applied. Furthermore, the self-timed control logic with dynamic switch resistance relaxes the speed-accuracy tradeoff. Together, these techniques enable energy efficient generation of the injection signal in self-timed injection. The manufactured proof-of-concept achieves the state-of-the-art performance, starting up in just 2.8  $\mu$ s for only 1.9 nJ.

#### ACKNOWLEDGMENT

The authors would like to thank HiSilicon and EUROPRAC-TICE for silicon donation, as well as Gerard Wienk from the University of Twente, Enschede, The Netherlands, for his valuable computer-aided design (CAD) support.

#### REFERENCES

- K. Philips, "Ultra low power short range radios: Covering the last mile of the IoT," in *Proc. 40th Eur. Solid State Circuits Conf. (ESSCIRC)*, Sep. 2014, pp. 51–58.

- [2] R. van Langevelde, M. van Elzakker, D. van Goor, H. Termeer, J. Moss, and A. J. Davie, "An ultra-low-power 868/915 MHz RF transceiver for wireless sensor network applications," in *Proc. IEEE Radio Freq. Integr. Circuits Symp.*, Jun. 2009, pp. 113–116.

- [3] Y. Chang, J. Leete, Z. Zhou, M. Vadipour, Y.-T. Chang, and H. Darabi, "A differential digitally controlled crystal oscillator with a 14-bit tuning resolution and sine wave outputs for cellular applications," *IEEE J. Solid-State Circuits*, vol. 47, no. 2, pp. 421–434, Feb. 2012.

- [4] D. Griffith, F. Dulger, G. Feygin, A. N. Mohieldin, and P. Vallur, "A 65 nm CMOS DCXO system for generating 38.4 MHz and a real time clock from a single crystal in 0.09 mm2," in *Proc. IEEE Radio Freq. Integr. Circuits Symp.*, May 2010, pp. 321–324.

- [5] M.-D. Tsai, C.-W. Yeh, Y.-H. Cho, L.-W. Ke, P.-W. Chen, and G.-K. Dehng, "A temperature-compensated low-noise digitallycontrolled crystal oscillator for multi-standard applications," in *Proc. IEEE Radio Freq. Integr. Circuits Symp.*, Jun. 2008, pp. 533–536.

- [6] J. Lin, "A low-phase-noise 0.004-ppm/step DCXO with guaranteed monotonicity in the 90-nm CMOS process," *IEEE J. Solid-State Circuits*, vol. 40, no. 12, pp. 2726–2734, Dec. 2005.

- [7] A. Rusznyak, "Start-up time of CMOS oscillators," *IEEE Trans. Circuits Syst.*, vol. CS-34, no. 3, pp. 259–268, Mar. 1987.

- [8] S. Iguchi, H. Fuketa, T. Sakurai, and M. Takamiya, "Variation-tolerant quick-start-up CMOS crystal oscillator with chirp injection and negative resistance booster," *IEEE J. Solid-State Circuits*, vol. 51, no. 2, pp. 496–508, Feb. 2016.

- [9] K.-M. Lei, P.-I. Mak, M.-K. Law, and R. P. Martins, "A regulation-free sub-0.5-V 16-/24-MHz crystal oscillator with 14.2-nJ startup energy and 31.8-μw steady-state power," *IEEE J. Solid-State Circuits*, vol. 53, no. 9, pp. 2624–2635, Sep. 2018.

- [10] M. Miyahara, Y. Endo, K. Okada, and A. Matsuzawa, "A 64μs start-up 26/40MHz crystal oscillator with negative resistance boosting technique using reconfigurable multi-stage amplifier," in *Proc. IEEE Symp. VLSI Circuits*, Jun. 2018, pp. 115–116.

- [11] E. A. Vittoz, M. G. R. Degrauwe, and S. Bitz, "High-performance crystal oscillator circuits: Theory and application," *IEEE J. Solid-State Circuits*, vol. 23, no. 3, pp. 774–783, Jun. 1988.

- [12] O. Abdelatty et al., "A low power Bluetooth low-energy transmitter with a 10.5nJ startup-energy crystal oscillator," in Proc. IEEE 45th Eur. Solid State Circuits Conf. (ESSCIRC), Sep. 2019, pp. 377–380.

- [13] X. Wang and P. P. Mercier, "An 11.1nJ-Start-up 16/20 MHz crystal oscillator with multi-path feedforward negative resistance boosting and optional dynamic pulse width injection," in *Proc. IEEE Custom Integr. Circuits Conf. (CICC)*, Mar. 2020, pp. 1–4.

- [14] A. Karimi-Bidhendi, H. Pu, and P. Heydari, "Study and design of a fast start-up crystal oscillator using precise dithered injection and active inductance," *IEEE J. Solid-State Circuits*, vol. 54, no. 9, pp. 2543–2554, Sep. 2019.

- [15] S. A. Blanchard, "Quick start crystal oscillator circuit," in Proc. 15th Biennial Univ./Government/ Ind. Microelectron. Symp., 2003, pp. 78–81.

- [16] Y.-I. Kwon, S.-G. Park, T.-J. Park, K.-S. Cho, and H.-Y. Lee, "An ultra low-power CMOS transceiver using various low-power techniques for LR-WPAN applications," *IEEE Trans. Circuits Syst. I, Reg. Papers*, vol. 59, no. 2, pp. 324–336, Feb. 2012.

- [17] D. Griffith, J. Murdock, and P. T. Roine, "A 24 MHz crystal oscillator with robust fast start-up using dithered injection," in *IEEE Int. Solid-State Circuits Conf. (ISSCC) Dig. Tech. Papers*, Jan. 2016, pp. 104–105.

- [18] M. Scholl *et al.*, "A 32 MHz crystal oscillator with fast start-up using dithered injection and negative resistance boost," in *Proc. IEEE 45th Eur. Solid State Circuits Conf. (ESSCIRC)*, Sep. 2019, pp. 49–52.

- [19] H. Esmaeelzadeh and S. Pamarti, "A quick startup technique for high-Q oscillators using precisely timed energy injection," *IEEE J. Solid-State Circuits*, vol. 53, no. 3, pp. 692–702, Mar. 2018.

- [20] K. M. Megawer *et al.*, "A fast startup CMOS crystal oscillator using two-step injection," *IEEE J. Solid-State Circuits*, vol. 54, no. 12, pp. 3257–3268, Dec. 2019.

- [21] B. Verhoef, J. Prummel, W. Kruiskamp, and R. Post, "A 32 MHz crystal oscillator with fast start-up using synchronized signal injection," in *IEEE Int. Solid-State Circuits Conf. (ISSCC) Dig. Tech. Papers*, Feb. 2019, pp. 304–305.

- [22] A. Karimi-Bidhendi and P. Heydari, "A study of multi-phase injection on accelerating crystal oscillator start-up," *IEEE Trans. Circuits Syst. II, Exp. Briefs*, vol. 67, no. 12, pp. 2868–2872, Dec. 2020.

- [23] J. B. Lechevallier, R. A. R. Van Der Zee, and B. Nauta, "Fast & energy efficient start-up of crystal oscillators by self-timed energy injection," *IEEE J. Solid-State Circuits*, vol. 54, no. 11, pp. 3107–3117, Nov. 2019.

- [24] L. J. Svensson and J. G. Koller, "Driving a capacitive load without dissipating fCV<sup>2</sup>," in *Proc. IEEE Symp. Low Power Electron.*, Oct. 1994, pp. 100–101.

- [25] M. van Elzakker, E. van Tuijl, P. Geraedts, D. Schinkel, E. A. M. Klumperink, and B. Nauta, "A 10-bit Charge-Redistribution ADC Consuming 1.9 uW at 1 MS/s," *IEEE J. Solid-State Circuits*, vol. 45, no. 5, pp. 1007–1015, May 2010.

- [26] H. S. Bindra, A.-J. Annema, S. M. Louwsma, and B. Nauta, "A 0.2–8 MS/s 10b flexible SAR ADC achieving 0.35–2.5 fJ/conv-step and using self-quenched dynamic bias comparator," in *Proc. Symp. VLSI Circuits*, Jun. 2019, pp. C74–C75.

- [27] K. Chen, H.-S. Lee, A. P. Chandrakasan, and C. G. Sodini, "Ultrasonic imaging transceiver design for CMUT: A three-level 30-vpp pulseshaping pulser with improved efficiency and a noise-optimized receiver," *IEEE J. Solid-State Circuits*, vol. 48, no. 11, pp. 2734–2745, Nov. 2013.

- [28] J. Park, Y.-H. Hwang, J. Oh, Y. Song, J.-E. Park, and D.-K. Jeong, "A mutual capacitance touch readout ic with 64% reduced-power adiabatic driving over heavily coupled touch screen," *IEEE J. Solid-State Circuits*, vol. 54, no. 6, pp. 1694–1704, Jun. 2019.

- [29] J. Fritzin, C. Svensson, and A. Alvandpour, "Design and analysis of a class-D stage with harmonic suppression," *IEEE Trans. Circuits Syst. I, Reg. Papers*, vol. 59, no. 6, pp. 1178–1186, Jun. 2012.

[30] L. J. Svensson and J. Koller, "Adiabatic charging without inductors,"

- [30] L. J. Svensson and J. Koller, "Adiabatic charging without inductors," Univ. Southern California-Inf. Sci. Inst., Marina del Rey, CA, USA, Tech. Rep. ACMOS-TR-3a, Feb. 1994.

- [31] H. S. Bindra, C. E. Lokin, D. Schinkel, A.-J. Annema, and B. Nauta, "A 1.2-V dynamic bias latch-type comparator in 65-nm CMOS with 0.4-mV input noise," *IEEE J. Solid-State Circuits*, vol. 53, no. 7, pp. 1902–1912, Jul. 2018.

- [32] J. Lu and J. Holleman, "A low-power high-precision comparator with time-domain bulk-tuned offset cancellation," *IEEE Trans. Circuits Syst. I, Reg. Papers*, vol. 60, no. 5, pp. 1158–1167, May 2013.

- [33] J. Yao, J. Liu, and H. Lee, "Bulk voltage trimming offset calibration for high-speed flash ADCs," *IEEE Trans. Circuits Syst. II, Exp. Briefs*, vol. 57, no. 2, pp. 110–114, Feb. 2010.

**Joeri B. Lechevallier** (Graduate Student Member, IEEE) received the B.Sc. and M.Sc. (*cum laude*) degrees in electrical engineering from the University of Twente, Enschede, The Netherlands, in 2012 and 2014, respectively, where he is currently pursuing the Ph.D. degree with the Integrated Circuit Design Group.

In 2021, he joined VDL ETG T&D Hengelo.

Harijot Singh Bindra (Member, IEEE) received the B.Tech. degree in electronics and communication engineering from Punjabi University, Patiala, India, in 2008, the M.Tech. degree in VLSI design from IIT Delhi, New Delhi, India, in 2012, and the Ph.D. degree (*cum laude*) from the University of Twente, Enschede, The Netherlands, in 2019.

From 2008 to 2010, he was a Scientist with the Indian Space Research Organization, Chandigarh, India, where he was involved in the semi-conductor design and fabrication facility. From 2012 to 2014,

he was a Senior Design Engineer with Cadence Design Systems, Noida, India, where he worked on high-speed serial links, clock, and data recovery circuits and equalizers. He is currently an Assistant Professor with the Integrated Circuit Design Group, University of Twente. His current research interests include ADCs, low-voltage low-energy circuit design, equalizers, and clocking and data recovery circuits.

Dr. Bindra was a recipient of the University Gold Medal in B.Tech. degree and was awarded the Graduate Scholarship during his master's degree from Cadence Design Systems Inc. He serves as a Reviewer for the IEEE JOURNAL OF SOLID-STATE CIRCUITS.

**Ronan A. R. van der Zee** (Member, IEEE) received the M.Sc. degree (*cum laude*) in electrical engineering and the Ph.D. degree in high efficiency audio amplifiers from the University of Twente, Enschede, The Netherlands, in 1994 and 1999, respectively.

In 1999, he joined Philips Semiconductors, Nijmegen, The Netherlands, where he worked on class AB and class D audio amplifiers. In 2003, he joined the IC-Design Group, University of Twente. His research interests include linear and switching power amplifiers, RF front ends, and ultralow-power radio.

**Bram Nauta** (Fellow, IEEE) was born in Hengelo, The Netherlands, in 1964. He received the M.Sc. degree (*cum laude*) in electrical engineering and the Ph.D. degree in analog CMOS filters for very high frequencies from the University of Twente, Enschede, The Netherlands, in 1987 and 1991, respectively.

In 1991, he joined the Department of Mixed-Signal Circuits and Systems, Philips Research, Eindhoven, The Netherlands. In 1998, he returned to the University of Twente, where he is currently a Distinguished

Professor and heading the IC Design Group. From 2016 to 2020, he also served as the Chair of the Department of EE, University of Twente. His current research interest is high-speed analog CMOS circuits, software defined radio, cognitive radio, and beamforming.

Dr. Nauta is a member of the Royal Netherlands Academy of Arts and Sciences (KNAW). He was a co-recipient of the ISSCC 2002 and 2009 "Van Vessem Outstanding Paper Award" and received the "Simon Stevin Meester" Award (500.000€) in 2014, the largest Dutch National Prize for achievements in technical sciences. He served as the Editor-in-Chief of the IEEE JOURNAL OF SOLID-STATE CIRCUITS (JSSC) from 2007 to 2010, and he was the 2013 Program Chair of the International Solid State Circuits Conference (ISSCC). He served as the President of the IEEE Solid-State Circuits Society from 2018 to 2019. Also, he served as an Associate Editor for IEEE TRANSACTIONS ON CIRCUITS AND SYSTEMS II: EXPRESS BRIEFS from 1997 to 1999 and JSSC from 2001 to 2006. He was in the Technical Program Committee of the Symposium on VLSI Circuits from 2009 to 2013 and served in the Steering Committee and Program Committee from 1999 to 2017 of the European Solid State Circuit Conference (ESSCIRC). He served two terms as a Distinguished Lecturer of the IEEE.