# A 16-Channel Neural Recording System-on-Chip with CHT Feature Extraction Processor in 65nm CMOS

Arda Uran, *Student Member, IEEE*, Kerim Ture, Cosimo Aprile, Alix Trouillet, Florian Fallegger, Emilie C. M. Revol, *Student Member, IEEE*, Azita Emami, *Senior Member, IEEE*, Stéphanie P. Lacour, *Member, IEEE*, Catherine Dehollain, *Member, IEEE*, Yusuf Leblebici, *Fellow, IEEE*, and Volkan Cevher, *Senior Member, IEEE*

Abstract—Next generation invasive neural interfaces require fully implantable wireless systems that can record from a large number of channels simultaneously. However, transferring the recorded data from the implant to an external receiver emerges as a significant challenge due to the high throughput. To address this challenge, this paper presents a neural recording system-on-chip that achieves high resource and wireless bandwidth efficiency by employing on-chip feature extraction. An energy-area efficient 10-bit 20 kS/s front-end amplifies and digitizes the neural signals within the LFP and AP bands. The raw data from each channel is decomposed into spectral features using a Compressed Hadamard Transform (CHT) processor. The selection of the features to be computed is tailored through a machine learning algorithm, such that the overall data rate is reduced by 80% without compromising classification performance. Moreover, the CHT feature extractor allows waveform reconstruction on the receiver side for monitoring or additional post-processing. The proposed approach was validated through in vivo and offline experiments. The prototype fabricated in 65nm CMOS also includes wireless power and data receiver blocks to demonstrate the energy and area efficiency of the complete system. The overall signal chain consumes 2.6 µW and occupies 0.021 mm<sup>2</sup> per channel, pointing towards its feasibility for thousand-channel single-die neural recording systems.

Index Terms—Neural recording, implantable system-on-chip (SoC), resource efficiency, Compressed Hadamard Transform (CHT), wireless power and data transfer (WPDT), seizure detection, spreading depolarization (SD), machine learning.

This text serves as a placeholder for the manuscript details such as the date of reception, the date of revision, the date of publication and the Guest Editor. It should be replaced by the actual details if the paper is accepted. This work was supported by the European Research Council (ERC) under the European Union's Horizon 2020 research and innovation programme (grant agreement n° 725594 - time-data), Hasler Foundation (project number 16066), Bertarelli foundation, and SNSF Grant CRSII5\_183519.

A. Uran, A. Trouillet, F. Fallegger, E. C. M. Revol, S. P. Lacour, C. Dehollain, and V. Cevher are with École polytechnique fédérale de Lausanne, 1015 Lausanne, Switzerland. e-mail: arda.uran@epfl.ch.

K. Ture was with École polytechnique fédérale de Lausanne, 1015 Lausanne, Switzerland. He is now with University College London, London, WC1E 6BT United Kingdom.

C. Aprile was with École polytechnique fédérale de Lausanne, 1015 Lausanne, Switzerland. He is now with Kandou Bus, 1015 Lausanne, Switzerland. A. Emami is with California Institute of Technology, Pasadena, CA 91125 USA.

Y. Leblebici was with École polytechnique fédérale de Lausanne, Lausanne, 1015 Switzerland. He is now with Sabanci University, Istanbul, 34956 Turkey. Color versions of one or more of the figures in this paper are available online at http://ieeexplore.ieee.org.

Digital Object Identifier XX.XXXX/XXXX.XXXXXXXXX

### I. Introduction

Invasive brain recordings can provide insight into neural mechanisms with high spatiotemporal resolution. They have been utilized to identify biomarkers for the treatment of neurological disorders such as epilepsy and Parkinson's disease. Moreover, these recordings are instrumental for emerging brain-machine interfaces that can restore lost motor functions in paralyzed patients [1]–[5].

Despite the promise of invasive brain recording, the translation of its applications from proof-of-concept to clinical therapies is a slow process. This is partly due to the fact that the standard clinical practice requires the implanted electrodes to be tethered to external instruments, limiting patient mobility and posing infection risks. Therefore, wireless neural recording systems have started to gain attention as a more practical alternative [6].

A straightforward wireless neural recording system transmits the raw data generated by the sensing front-end to an external receiver as illustrated in Fig. 1(a). However, as the number of channels reach beyond a thousand [7], [8], the wireless transmission of the large amount of data emerges as a great challenge due to the limits of the available wireless standards. To illustrate, a 1000-channel system with 10-bit resolution and 20 kS/s sampling rate produces 200 Mb/s throughput, whereas the bandwidth supported by off-the-shelf implant-grade components is below 1 Mb/s [9], and the reported values in the literature can reach only up to tens of Mb/s [10].

Compression methods for neural signals have focused on reducing the data rate with acceptable loss in visual quality. Threshold coding [11], [12] is a common method that discards the low-energy spectral components to save bandwidth. However, due to the low-pass nature of neural signals, it eliminates mostly high-frequency components which may carry significant information during a neural event. Another method is compressed sensing (CS) [13], [14] where fewer samples are transmitted than prescribed by Shannon's sampling theorem. Nevertheless, the recovery of the signal requires solving an underdetermined system of equations, which is prone to producing artifacts. Such losses or corruptions may adversely affect the performance of the subsequent detection algorithms, even though the visual fidelity is high on average.

Given the dimensionality of multichannel neural signals and

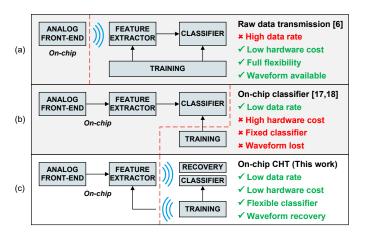

Fig. 1. Comparison of the previous and the proposed neural recording approaches.

their implicit relationship with the target outcome, machine learning (ML) has gained popularity as the end user of the recordings [5], [15], [16]. Therefore, recent efforts have focused on implementing on-chip classifiers as depicted in Fig. 1(b). Although this approach would process the raw signals locally and eliminate the need for high-rate data transmission, an on-chip ML implementation requires a large silicon area due to intensive computations and memory needs, even with a simple algorithm and a moderate number of channels. To illustrate, the single-die demonstration in [17] allocated 3.31 mm<sup>2</sup> to classify seizures from 32 channels, which accounted for more than half of the total chip area. In [18], a separate 3.5 mm<sup>2</sup> chip was dedicated to classification, in addition to the 8-channel sensing front-end chip. Limited flexibility is also a disadvantage for on-chip classification hardware since the algorithm has to be optimized and fixed at the implant level.

Extracting multichannel information from large-scale neural recording systems is an outstanding challenge due to the information loss in compression and the hardware cost of on-chip ML. To this end, we propose a neural recording system-on-chip (SoC) with an on-chip feature extractor that achieves 80% data reduction over raw data transmission while preserving the application-specific information content of the transmitted neural recordings. As depicted in Fig. 1(c), the features to be extracted by the SoC are determined by jointly training the on-chip feature extractor and the off-chip classifier on patient-specific datasets, which has not yet been explored to the best of our knowledge. Consequently, the transmitted data does not suffer from information loss and maintains over 90% sensitivity in classification at the reduced data rate. Moreover, the proposed Compressed Hadamard Transform (CHT) features can still be used for waveform reconstruction at the receiver side with 23 dB signal-to-noise ratio (SNR).

The scalable data path of the SoC combines the analog front end (AFE) presented in [19] with a CHT feature extraction processor in a per-channel arrangement. The CHT processor decomposes the raw signal into its spectral components with much lower energy and area cost compared to previous feature extraction methods thanks to its hardware-friendly nature. The

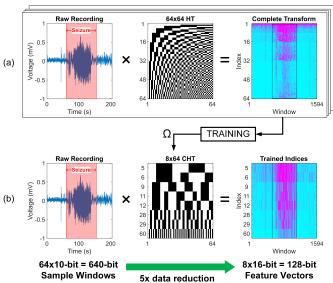

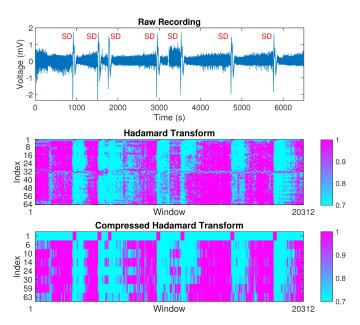

Fig. 2. (a) A seizure event within a raw recording can be identified from its Hadamard transform (HT). (b) Selecting 8 of the most descriptive indices  $(\Omega)$  via training on an example dataset forms the Compressed Hadamard Transform (CHT). The resulting data volume is reduced by 5 times.

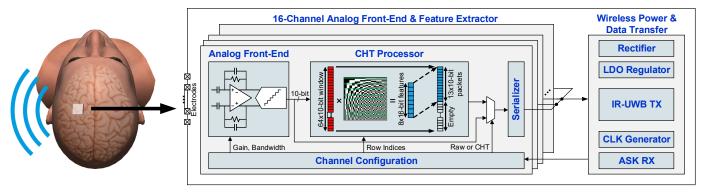

SoC also includes wireless power and data transfer (WPDT) blocks to demonstrate the overall cost of recording from sensing to transmission. The 2.9  $\mu$ W power and 0.021 mm<sup>2</sup> area consumption per channel demonstrate the feasibility of the proposed approach for neural recording systems with over 1000 channels.

This article expands the work presented in [20] by providing a detailed description of the CHT concept, its application as a neural feature extractor and/or data compressor, and its hardware implementation. The organization of the article is as follows: Section II introduces the CHT concept and its use in neural signal processing. Section III describes the proposed system architecture and its building blocks, namely the AFE, the CHT processor, and the WPDT subsystem. Section IV presents the *in vivo* and offline experimental results for waveform reconstruction, epileptic seizure detection and spreading depolarization (SD) event identification. Finally, Section V summarizes and concludes the study.

## II. COMPRESSED HADAMARD TRANSFORM

Many neural recording applications such as speech synthesis, seizure detection, and adaptive deep brain stimulation use spectral band energies as biomarkers [4], [15], [21]. Conventionally, these features can be extracted on-chip using finite impulse response (FIR) filter banks, Fast Fourier Transform (FFT) or Discrete Wavelet Transform (DWT) processors [17], [18], [22], which are expensive computations that require many multiply-and-accumulate operations and on-chip storage for the coefficients. Therefore, these methods are not suitable for resource-constrained large-scale neural recording.

In this work, we focus on Hadamard transform due to its significant hardware advantages. Compared to other classes of Fourier transforms like FFT, the main advantage of Hadamard

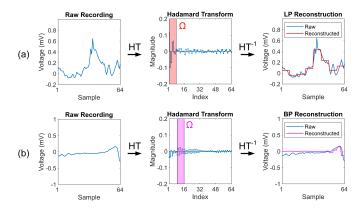

Fig. 3. Illustration of the reconstruction property of the CHT features. (a) Reconstruction from the first 8 indices behave as a low-pass filter. (b) Reconstructions from higher index groups behave as band-pass filters.

transform is that its coefficients are either +1 or -1, corresponding to additions or subtractions. Moreover, these coefficients can be generated on-the-fly by a logic circuit which alleviates the need for a coefficient memory. Therefore, Hadamard transform is a hardware-friendly option for extracting spectral information from neural data.

Although Hadamard transform is not an exact frequency transform FFT, it still allows correlating low or high-frequency activity to a neurological outcome. Fig. 2(a) illustrates a time-series containing a seizure event, and its spectrogram constructed by applying a 64-by-64 Hadamard transform on 64-sample windows. The seizure interval in this example can be clearly identified from the spectrogram thanks to the increased activity, especially at higher indices. Moreover, we observe that some indices exhibit a sharper contrast in energy content compared to the others. Therefore, computing and transmitting only the descriptive indices instead of the complete transform would be sufficient for classification purposes, as illustrated in Fig. 2(b).

Identifying the most descriptive indices is not straightforward given the large datasets and the patient-to-patient variability of the signals. Therefore, the correct subset must be learned via a machine learning algorithm that maximizes the classification performance. The selection problem can be formally described similar to learning-based compressive subsampling (LBCS) as presented in [23]. Consider the following mathematical model where a signal  $\mathbf{x} \in \mathbb{R}^N$  is converted to its compressed representation  $\mathbf{y} \in \mathbb{R}^M$  with M < N:

$$\mathbf{y} = \mathbf{P}_{\Omega} \boldsymbol{H} \mathbf{x} , \qquad (1)$$

where  $\boldsymbol{H}$  is the Hadamard transform basis and  $\mathbf{P}_{\Omega}$  is a subsampling operator that selects the rows of  $\boldsymbol{H}$  indexed by the set  $\Omega$ . Suppose that we have an annotated dataset where  $\mathscr{X} = \{\mathbf{x}_1, \mathbf{x}_2, ..., \mathbf{x}_k\}$  represents k different measurements, and  $\mathscr{Y} = \{\mathbf{y}_1, \mathbf{y}_2, ..., \mathbf{y}_k\}$  represents their binary annotations. The  $\Omega$  that yields the best classification performance can be found by solving the following minimization problem:

$$\hat{\Omega} = \underset{\Omega, |\Omega| = M}{\operatorname{arg \, min}} \sum_{j=1}^{k} |\mathbf{y}_{j} - f(\mathbf{P}_{\Omega} \mathbf{H} \mathbf{x}_{j})|, \qquad (2)$$

where f is the classifier model. In plain words, (2) learns the  $\Omega$  that extracts the most descriptive indices of the Hadamard transform. We term the customized matrix  $\mathbf{P}_{\Omega}\mathbf{H}$  as the CHT matrix.

Aside from dimensionality reduction and hardware simplicity, another important benefit of the CHT feature extractor is that its output can still be used to reconstruct the waveform at the receiver side by taking the inverse transform, which is a linear computation that can be performed in real time. If the set  $\Omega$  is chosen as the lowest M indices, the reconstructed waveform will be the low-pass filtered version of the raw signal as in Fig. 3(a). This selection leverages the low-pass characteristic of the neural signals, thus retains most of the energy content. Similarly, band-pass filters can be realized by choosing higher index groups as shown in Fig. 3(b).

# III. SYSTEM-ON-CHIP ARCHITECTURE

Fig. 4 displays the block diagram of the presented integrated circuit. The system comprises of 16 configurable channels, each with an individual AFE and a CHT feature extraction processor. This modular nature of the system allows it to be scaled linearly to any number of channels. Each channel can be configured to output the features computed by the CHT processor, or the raw data from the AFE. The WPDT subsystem is responsible for powering the system and sending out the aggregated channel outputs via the ultra-wideband (UWB) transmitter. The following subsections describe each building block in detail.

# A. Analog Front-End

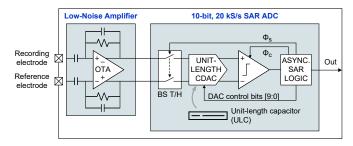

The AFE amplifies, filters, and digitizes the neural signals (local field potentials (LFPs) and action potentials (APs)) coming from the electrodes, which typically have amplitudes ranging from 10  $\mu V$  to 1 mV, and occupy the frequency range up to 10 kHz. Fig. 5 shows the AFE architecture, which was originally proposed in [19]. The capacitively-coupled lownoise amplifier (CC-LNA) provides 40 dB gain and limits the bandwidth to 8 kHz before digitization. The amplified signal is digitized by the 10-bit, 20 kS/s asynchronous successive approximation register (SAR) analog-to-digital converter (ADC).

The CC-LNA is based on a two-stage inverter-based operational transconductance amplifier (OTA). The DC offsets on the electrodes are rejected via AC coupling, and the DC bias at the input of the OTA is set through feedback resistors constructed by diode-connected pMOS transistors. Although the coupling capacitors (2 pF) occupy a large area, the overall AFE maintains a small footprint thanks to the area savings on the ADC side.

The SAR ADC comprises of a bootstrapped track-and-hold switch (BS T/H), a capacitive digital-to-analog converter (CDAC), a dynamic double-tail comparator, and an asynchronous logic circuit that implements the SAR operation. The critical block in this ADC is the CDAC. In a traditional binary weighted capacitor array, the weights are built by replicating a unit capacitor, thus the area of the array grows exponentially with resolution ( $\propto 2^{N_B}$ ). The unit-length CDAC in this

Fig. 4. Functional block diagram of the presented system-on-chip.

Fig. 5. Analog front-end block diagram showing the low-noise amplifier and the analog-to-digital converter [19].

ADC is built using unit-length capacitors (ULCs), where the weights are set by adjusting the length difference between two differential capacitors [24]. As a result, the overall unit-length CDAC area grows linearly with resolution ( $\propto N_B$ ). Moreover, the ULC array is constructed using higher metal layers and placed over the other active circuits with shielding in between to further reduce the footprint. These savings at the ADC side thanks to the unit-length CDAC results in a state-of-the-art overall energy-area figure of merit (E-A FoM) with 0.78 fJ mm²/conv. step. More details about this AFE architecture and its measurements can be found in [19].

# B. Compressed Hadamard Transform Processor

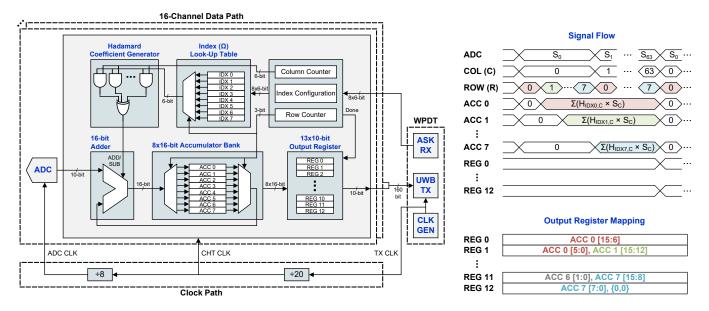

Fig. 6 shows the block diagram of the CHT processor and its flow of operation. The data path of the processor implements the matrix product of a 64-sample input window with 8 selected rows from the 64-by-64 Hadamard matrix according to (1). Since the Hadamard coefficients are  $\pm 1$ , the product can be implemented by adders/subtractors instead of multipliers. 16-bit adder width is required since 64 successive additions are performed on the 10-bit ADC samples (10+log(64)=16).

The 8 rows to be computed are configured into a look-up table based on the feature importance training on the dataset. This provides power and area savings since only the patient-specific descriptive features are computed during the operation instead of the full transform. As the look-up table is populated at the start of the operation, the communication from outside to the implant does not need to be in real time.

A bank of 8 16-bit accumulators, corresponding to 8 selected rows, hosts the intermediate results during the 64

cycles. Row and column counters keep track of the operation sequence. The selected row index is fetched from the configurable look-up table based on the current row counter value. The Hadamard coefficient corresponding to the selected row index and the column counter value is generated on-the-fly by a combinational logic circuit, without a coefficient memory.

The clock path of the processor contains frequency dividers that generate the clocks for the ADC and the CHT processor. The master transmitter clock runs at 3.2 MHz for this 16-channel prototype for 10-bit 20 kS/s sampling. As the CHT processor computes 8 features with a single shared adder/subtractor, its clock runs 8 times faster than the ADC clock.

Each channel can be configured individually to output either the the features computed by the CHT processor or the raw data from the AFE. When raw data is sent, the CHT processor is bypassed and the 10-bit stream is transmitted. When features are sent, the 64-sample window reduces to a feature vector of 8 features and the bit size increases from 10 bits to 16 bits. To simplify the output mapping of the individually configurable channels, the  $8\times16$ -bit features are mapped onto a  $13\times10$ -bit output register as seen in Fig. 6 (right-bottom) which is then fed into the global 10-bit data stream and sent out by the UWB transmitter.

The absence of a coefficient memory and multipliers is the main hardware advantage of the CHT over commonly used operations such as FFT, DWT, and FIR filtering. Moreover, the transformation of the  $64\times10$ -bit input window into the  $8\times16$ -bit feature vector yields an overall data reduction of 80%. This means that 5 times more channels can be recorded at the same data rate with respect to raw data transmission. To illustrate, the number of channels that could be accommodated by a 40 Mb/s UWB transmitter could be increased from 200 to 1000.

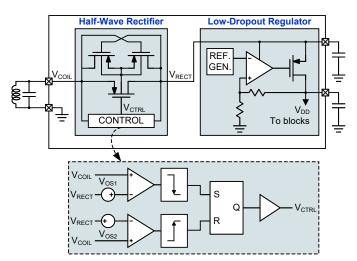

### C. Wireless Power and Data Transfer

The on-chip power receiver blocks are shown in Fig. 7. The induced AC power on the antenna is first rectified to DC by a delay-compensated active half-wave rectifier, which is composed of a P-channel metal-oxide-semiconductor (PMOS) pass transistor and control circuitry. The pass transistor charges the 400 nF off-chip reservoir capacitor only when the input is higher than the output, and turns off otherwise, hence

Fig. 6. Digital hardware implementation of the Compressed Hadamard Transform processor, its signal flow diagram, and the output register mapping.

Fig. 7. Schematics of the active half-wave rectifier and the LDO regulator.

the half-wave operation. The bulk of the pass transistor is dynamically biased by a composite PMOS diode to reduce the pass transistor's resistance and leakage. The timing of the switch is controlled by two comparators that detect the sign changes at the input and the output. The gate of the pass transistor is driven by a buffer stage. To improve the efficiency of the rectifier, the delay of the comparators and the gate driver are compensated by introducing offset to the comparators such that the control circuit is triggered before the input changes its sign. The rectifier is followed by an low-dropout (LDO) regulator. The regulator provides 1 V output, stabilized by a 200 nF off-chip load capacitor.

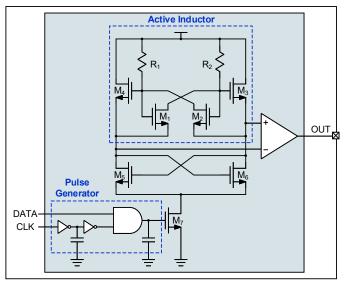

The uplink communication for this prototype is established by an impulse radio ultra-wideband (IR-UWB) transmitter. The IR-UWB pulses are generated by modulating a carrier frequency with fixed-duration pulses. The absence of a constantly-running carrier enables high energy-efficiency, which makes it an attractive method for implant use. Moreover,

Fig. 8. Schematic of the IR-UWB transmitter.

since the standard uses a very wide bandwidth (3.1-10.6 GHz), the link is robust against deviations in center frequency due to process variation.

The schematic of the IR-UWB transmitter is drawn in Fig. 8. The 6 GHz carrier frequency is generated by a an active inductor-based LC oscillator. The active inductor takes much less silicon area than a regular spiral inductor as it is built using only transistors (M1-M4) and resistors (R1-R2). The pulse generator modulates the carrier frequency by driving the tail transistor (M7) of the oscillator. If the data to be sent is logic '1', the oscillator turns on for 1.8 ns mandated by the delay on the clock line. The power consumption of the transmitter is data-dependent as the oscillator turns on only for transmitting logic '1'.

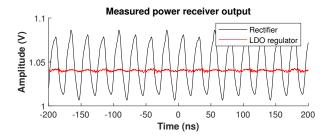

Fig. 9 displays the measured rectified and regulated wave-

Fig. 9. Measured waveforms at the output of the power receiver blocks.

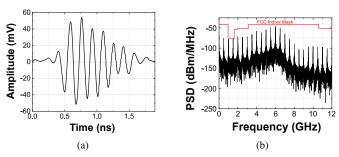

Fig. 10. Measured UWB pulse characteristics (a) in time and (b) frequency domains

forms at the output of the power receiver blocks. The power conversion efficiency of the rectifier is 71% (for 401.45  $\mu$ W output power). The power supply rejection ratio of the regulator is 20 dB, and the line and load regulation values are 37.5 mV/V and 2.04 mV/mA, respectively.

Fig. 10 shows the UWB pulse characteristics in time and frequency domains. The power spectral density (PSD) of the transmitted pulses complies with the indoor emission mask regulated by the Federal Communications Commission [25]. For this 16-channel prototype, the UWB transmitter is expected to work at 3.2 Mb/s in raw data transmission mode (200 kb/s per channel), and 640 kb/s in CHT feature transmission mode (40 kb/s per channel). The maximum pulse repetition frequency of the transmitter circuit was measured to be 200 MPulse/s. However, operating the wireless link at this rate would increase susceptibility to strong inter-symbol interference and result in a high bit error rate, which is the principal reason that prevents raw data transmission from a thousand channels or more. On the other hand, applying onchip feature extraction reduces the effective data rate of the system, thus relaxes the link requirements.

It is important to note that the main purpose of including the WPDT subsystem in this work is to accurately compute the total power and area consumption of the proposed neural recording approach. A fully operational wireless link would require building an external UWB receiver as well, which is beyond the scope of this paper. Therefore, the results presented in Section IV were obtained using a wired connection.

# IV. EXPERIMENTAL RESULTS

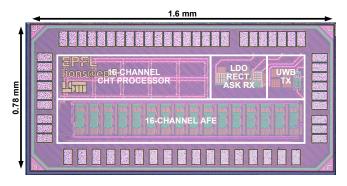

Fig. 11 displays the 16-channel prototype fabricated in TSMC 65nm 6X1Z1U LP CMOS process. The dimensions including the pad frame are 1.6 mm by 0.78 mm, and the core blocks occupy a total of 0.382 mm<sup>2</sup>.

Fig. 11. Micrograph of the 16-channel wireless neural recording SoC fabricated in TSMC 65nm LP process.

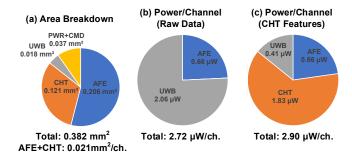

Fig. 12. Power and area breakdowns of the wireless neural recording SoC.

Fig. 12(a) presents the area breakdown of the chip. The total area of the CHT processor is 0.121 mm<sup>2</sup>, which is equivalent to 84k NAND2 gates in a 65nm standard cell library. The area per channel including the AFE and the CHT processor is 0.021 mm<sup>2</sup>. The total power consumption of the chip is 401.45 µW including the power and command receiver (355 µW). The pie charts in Fig. 12(b) and Fig. 12(c) show the power breakdown of the system for raw data and CHT feature transmission modes, respectively. The power consumption of the CHT processor is 1.83 µW/channel. However, the data-dependent power consumption of the UWB transmitter decreases by 5 times from 2.06 µW/channel to 0.41 µW/channel when features are transmitted, which largely compensates for the power overhead of the feature extractor. In total, the power overhead of CHT feature extractor is 6.7% compared to raw data transmission.

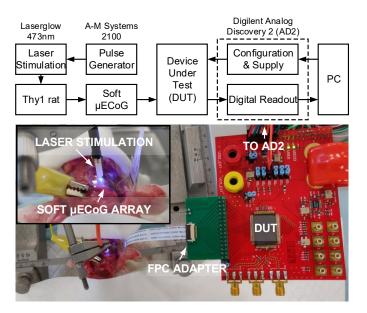

# A. Waveform Reconstruction

The reconstruction mode operation was validated *in vivo* using the experiment setup shown in Fig. 13 (following all relevant ethical regulations and as approved by the Veterinary Office of the canton of Geneva (Switzerland) under license number 32846). We used a Thy1 transgenic rat model (NBRP 0685, Kyoto, Japan), that expresses light sensitive ion channels in the cortex. Upon illumination with a blue laser diode, pyramidal neurons are excited and create action potentials that can be recorded at the surface of the brain. A large craniotomy was performed, then a custom 16-channel soft microelectrocorticography (µECoG) array was placed epidurally over the exposed cortex. The array was microfabricated using thin-film and silicon processing technology, similar to the e-dura process

Fig. 13. Test setup for the in vivo validation of the reconstruction mode.

[26], [27], and it was connected to the test board hosting the prototype chip using a flex cable. The test board was interfaced to a PC using a logic analyzer, where a Python script configures the chip and visualizes the recorded data in real time.

The optical stimulation was delivered using a diode-pumped solid-state blue laser (473 nm, 100mW max power, Laserglow Technologies) coupled via a FC/PC terminal connected to a 200  $\mu$ m core optical fiber (ThorLabs). Using a micromanipulator, the fiber was placed at the center of the  $\mu$ ECoG array. The frequency and duration of the laser pulses were set as 1 Hz and 100 ms by the pulse stimulator.

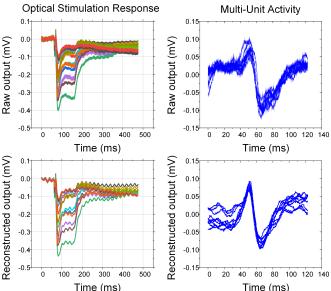

The chip was configured to output first raw data, then the lowest 8 Hadamard indices for reconstruction, and the outputs were reconstructed in software using a linear decoder. Fig. 14 compares the raw (top) and low-pass reconstructed (bottom) waveforms recorded at different time windows. The plots on the left correspond to the optically-induced activity from all channels, and the plots on the right correspond to spontaneously captured multi-unit activities. The low-pass reconstruction discards the high-frequency components, thus appears smoothed.

To assess the reconstruction quality quantitatively, the prerecorded raw signals from the iEEG.org dataset [28] was fed to the CHT processor, and the outputs were reconstructed in software as in Fig. 3(a). The average SNR of the lowpass reconstructed waveforms with respect to the original raw signal was found as 23 dB. This value is greater than what has been reported for random-sampling compression methods like compressive sensing (~10 dB) [13], [14], [29] at similar compression ratios because the low-pass indices capture the most of the energy content in neural signals.

# B. Epileptic Seizure Detection

Epileptic seizure detection has been a popular benchmark for neural signal classifiers due to the availability of large

Fig. 14. Raw (top) and low-pass reconstructed (bottom) multichannel waveforms obtained during the *in vivo* experiment.

datasets containing hours of recordings from numerous patients. Moreover, the widespread use of spectral features for seizure detection makes it a reasonable task for demonstrating the efficacy of the proposed approach. In this work the classification experiments were performed on two seizure datasets: CHB-MIT [30] and iEEG.org [28].

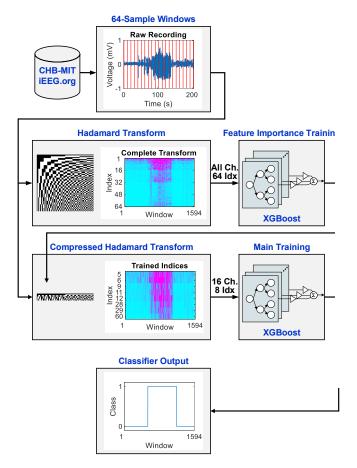

The software processing pipeline is described in Fig. 15. The raw time-series signals were first requantized to 10 bits, then reorganized into 64-sample non overlapping windows to be compatible with the designed CHT processor. In order to standardize the different number of channels, an initial training was performed to select the most descriptive 16 channels per patient and 8 Hadamard indices per channel. The learned indices and the raw data from the learned channels are then fed to the CHT hardware, whose output is processed by the off-chip classifier.

The classifier was implemented in software as an ensemble of 8 binary decision trees with a maximum depth of 4. A binary decision tree compares the input feature vector with a series of thresholds to output a probability. The tree ensemble produces the final decision as the weighted sum of the different tree outputs to accommodate variability in the data. The training of this model was done in Python language using the XGBoost package [31]. A new model was trained for each study to avoid underfitting due to the large patient-to-patient variations. The patient data was partitioned into sequences where each sequence was at least one hour long and contains at least one seizure. The sequences were then split into training and test sets for leave-one-out cross-validation.

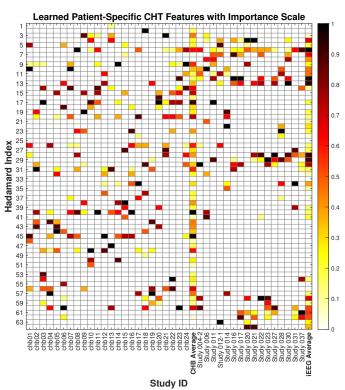

Although the lowest indices carry the most of the energy in the raw signal as discussed in Section II, Fig. 16 shows that the higher indices contain significant more information for seizure classification. For the CHB-MIT dataset, the index ranges 15-20 and 40-45 have significantly higher importance. If we relate these indices to frequencies with 256 S/s sampling rate, they

Fig. 15. Processing pipeline of the classification experiments.

correspond to 30-40 Hz (low- $\gamma$ ) and 80-90 Hz ( $\gamma$ ) bands, respectively. For the iEEG.org dataset, the important index ranges are 5-15, 28-30 and 57-64, which correspond to 20-60 Hz (low- $\gamma$ ), 110-120 Hz (high- $\gamma$ ), and 220-250 Hz (ripple) bands respectively with 500 S/s sampling rate. These findings are in accordance with the epilepsy literature suggesting the utility of high-frequency oscillations (HFOs) for seizure detection [32]. In most threshold-based compression methods, these components would be discarded as they carry little energy and do not contribute to achieving a high post-reconstruction SNR. Training finds the most descriptive indices per patient, which leads to a high sensitivity rate.

Fig. 17 presents the results obtained for each study in the two datasets containing a total of 283 seizures from 40 patients. For most patients, all seizures could be detected with no false alarms. The average sensitivity for the CHB-MIT dataset was 92%, and reaches 97.8% if the two outliers (chb06 and chb16) are excluded. The false alarm rate (FAR) is 0.117/hour which corresponds to around 3 false alarms per day. The average sensitivity for the iEEG.org dataset is 90.5% and the FAR is 0.171/hour, corresponding to around 4 false alarms per day.

# C. Spreading Depolarization Detection

SDs are pathological electrical waves propagating at the surface of the cortex, which are observed in a number of ill-

Fig. 16. Learned CHT indices for each study in the CHB-MIT and iEEG.org datasets. The color bar indicates the importance scale of the 8 selected indices out of 64.

| CHB-MIT Dataset |         |        |             | iEEG.org Dataset |             |         |        |             |         |

|-----------------|---------|--------|-------------|------------------|-------------|---------|--------|-------------|---------|

| Study ID        | # Seiz. | # Det. | Sensitivity | FAR              | Study ID    | # Seiz. | # Det. | Sensitivity | FAR     |

| chb01           | 7       | 7      | 100%        | 0.143/h          | Study 004-2 | 3       | 3      | 100%        | 0.000/h |

| chb02           | 3       | 3      | 100%        | 0.000/h          | Study 006   | 4       | 2      | 50%         | 0.125/h |

| chb03           | 7       | 7      | 100%        | 0.140/h          | Study 011   | 3       | 3      | 100%        | 0.000/h |

| chb04           | 4       | 4      | 100%        | 0.667/h          | Study 012-1 | 6       | 4      | 67%         | 0.250/h |

| chb05           | 5       | 5      | 100%        | 0.000/h          | Study 014   | 8       | 7      | 88%         | 0.000/h |

| chb07           | 3       | 3      | 100%        | 0.000/h          | Study 016   | 7       | 7      | 100%        | 0.714/h |

| chb08           | 5       | 5      | 100%        | 0.000/h          | Study 017   | 9       | 9      | 100%        | 0.000/h |

| chb09           | 4       | 4      | 100%        | 0.333/h          | Study 020   | 8       | 7      | 88%         | 0.438/h |

| chb10           | 7       | 7      | 100%        | 0.000/h          | Study 021   | 9       | 8      | 89%         | 0.722/h |

| chb11           | 3       | 3      | 100%        | 0.000/h          | Study 022   | 7       | 7      | 100%        | 0.000/h |

| chb12           | 27      | 26     | 96%         | 0.000/h          | Study 023   | 4       | 4      | 100%        | 0.250/h |

| chb13           | 10      | 9      | 90%         | 0.286/h          | Study 027   | 6       | 6      | 100%        | 0.000/h |

| chb14           | 8       | 8      | 100%        | 0.000/h          | Study 028   | 9       | 6      | 67%         | 0.111/h |

| chb15           | 20      | 20     | 100%        | 0.000/h          | Study 030   | 8       | 8      | 100%        | 0.063/h |

| chb17           | 3       | 3      | 100%        | 0.667/h          | Study 031   | 4       | 4      | 100%        | 0.000/h |

| chb18           | 5       | 5      | 100%        | 0.000/h          | Study 037   | 8       | 8      | 100%        | 0.063/h |

| chb19           | 3       | 3      | 100%        | 0.000/h          | Total       | 103     | 93     | 90.5%       | 0.171/h |

| chb20           | 8       | 8      | 100%        | 0.000/h          |             |         |        |             |         |

| chb21           | 4       | 4      | 100%        | 0.000/h          |             |         |        |             |         |

| chb22           | 3       | 3      | 100%        | 0.000/h          |             |         |        |             |         |

| chb23           | 7       | 5      | 71%         | 0.333/h          |             |         |        |             |         |

| chb24           | 16      | 15     | 94%         | 0.000/h          |             |         |        |             |         |

| chb06           | 10      | 2      | 20%         | 0.000/h          |             |         |        |             |         |

| chb16           | 8       | 3      | 38%         | 0.400/h          |             |         |        |             |         |

| Total           | 162     | 157    | 97.8%       | 0.117/h          |             |         |        |             |         |

Fig. 17. Summary of the classification results on the CHB-MIT and iEEG.org datasets.

nesses such as traumatic brain injury or stroke. Their presence reveals metabolic and electrical instability of the brain and serves as a direct measure of neuronal health and potential ongoing lesion growth [33]. Although SDs monitoring could serve as a critical diagnostic tool in the intensive care unit, it is rarely exploited in clinics in part because of the difficulty of monitoring the multichannel data continuously by clinicians, as it is currently done with 6-contact electrode strips [33], [34]. Therefore, methods to extract and transmit large-scale

| TABLE I    |                           |    |  |  |  |  |  |

|------------|---------------------------|----|--|--|--|--|--|

| COMPARISON | WITH THE STATE OF THE ART | ۲. |  |  |  |  |  |

|                                            | TBCAS'16 [14]      | JSSC'17 [10]  | JSSC'18 [17]   | JSSC'20 [22]       | ISSCC'18 [18]      | This work                          |

|--------------------------------------------|--------------------|---------------|----------------|--------------------|--------------------|------------------------------------|

| Technology                                 | 180 nm             | 130 nm        | 130 nm         | 40 nm              | 180 nm             | 65 nm                              |

| V <sub>DD</sub> [V]                        | 1.8**              | 1.2           | 1.2            | 0.58               | 1.5                | 1                                  |

| Number of Channels                         | 16                 | 64            | 32             | 14                 | 8                  | 16                                 |

| Blocks Included                            | AFE+COMP+TX        | AFE+FE+CLF+TX | AFE+FE+CLF     | FE+CLF             | AFE+FE+CLF         | AFE+FE+TX                          |

| Total Area [mm <sup>2</sup> ]              | 1.68               | 3.86          | 7.59           | 2.56               | 5.83               | 0.382                              |

| Total Power [mW]                           | 0.254              | 0.47*         | 0.714**        | 1.9                | 0.013**            | 0.0464*                            |

| Feature Extractor / Compressor             | CS                 | FIR+PLV       | FIR+PLV/SE/CFC | FFT+SE             | DWT+KDE            | СНТ                                |

| Waveform Reconstruction                    | Yes                | No            | No             | No                 | No                 | Yes                                |

| Compression Ratio                          | 8                  | =             | -              | -                  | -                  | 5‡‡                                |

| Reconstruction SNR [dB]                    | 9.78               | =             | -              | -                  | -                  | 23                                 |

| Compressor power [µW/channel]              | 4.81               | =             | -              | -                  | -                  | 1.83                               |

| Compressor area [mm <sup>2</sup> /channel] | 0.015 <sup>‡</sup> |               | -              | _                  | -                  | 0.0076                             |

| Dimensionality Reduction                   | -                  | -             | Autoencoder    | mRMR               | ICA                | XGBoost                            |

| Feature Dimension                          | -                  | n/r           | 125            | 16                 | 48                 | 128                                |

| Feature Computation                        | -                  | Fixed         | Fixed          | Fixed              | Fixed              | Adaptive                           |

| Feature Extractor Area [mm <sup>2</sup> ]  | -                  | 1.285         | 0.475‡         | 0.618 <sup>‡</sup> | 0.817 <sup>‡</sup> | 0.121                              |

| Classification Rate [class/s]              | -                  | n/r           | 4              | 11.1               | 0.074              | 312.5                              |

| Energy/Classification [μJ]                 | -                  | n/r           | 168.6          | 170.9              | 14.2               | 0.149 <sup>†</sup>                 |

| Classifier Algorithm                       | -                  | Threshold     | SVM            | SVM                | SVM                | XGBoost DT                         |

| Dataset                                    | -                  | Custom        | EU             | CHB-MIT            | CHB-MIT            | CHB-MIT                            |

| Sensitivity                                | -                  | 75%           | 100%           | 96.6%              | 97.8%              | 97.8% <sup>††</sup>                |

| False Alarm Rate/Specificity               | -                  | 0.5/h         | 0.81/h         | 0.28/h             | 99.7%              | $0.12/\mathrm{h}^{\dagger\dagger}$ |

<sup>\*</sup> Power management blocks excluded. \*\* Estimated from the reported values. ‡ Estimated from the micrograph.

<sup>##</sup> Effective ratio including the bit width increase. † Total energy for AFE, FE and TX combined. †† Off-chip classifier.

Fig. 18. Dimensionality reduction using CHT of cortical activity from one electrode containing induced SDs.

information from multichannel data to automated SD detection algorithms are of high interest.

To test the applicability of the proposed CHT approach for identifying SDs in large-scale recordings, we performed an *in vivo* experiment where SDs were chemically induced through topical applications of potassium chloride (following all rel-

evant ethical regulations and as approved by the Veterinary Office of the canton of Geneva (Switzerland) under license number 33223). The raw data was prerecorded using a soft electrode array (3 by 3 grid of 500 µm diameter electrodes [27]) connected to a wireless recording system (Multi Channel Systems W2100, 0.01 Hz high pass filter, 2 kHz sampling rate). The subsequent processing was performed on the CHT hardware.

The raw recorded brain signal on one electrode (sampled at 2 kHz) is shown in Fig. 18 (top) as well as its complete Hadamard transform (center), and its CHT (bottom). The complete 64-by-64 Hadamard transform enables the systematic detection of the SD waves characteristics (increased low-frequency activity and decreased high-frequency activity). The proposed CHT approach captures the information content with only 8 indices.

## D. Discussion

Table I summarizes the performance of the presented neural recording SoC and compares it with previous works implementing on-chip compression [14] and classification [10], [17], [18], [22]. The proposed on-chip feature extraction approach has several advantages. First, the CHT processor occupies only 0.121 mm² for 16-channels, which is much less than the conventional feature extractors based on FFT, DWT, and FIR filters. Secondly, this work computes only the most descriptive features that are identified and configured by the learning algorithm, instead of applying dimensionality reduction on all

computed features. As a result, the output data rate could be reduced by 5 times while achieving a similar seizure detection performance. Thirdly, the CHT features allow waveform reconstruction on the receiver side for monitoring or further post-processing. The process-normalized hardware efficiency of CHT is similar to a multiplierless and memoryless CS [14] implementation, with higher reconstruction quality at a similar compression rate. Finally, the combined energy cost of sensing (AFE), processing, (CHT), and transmitting UWB per feature vector (0.149  $\mu J$ ) is much less than the cost of an on-chip classifier. Therefore, the proposed approach makes it feasible to send multichannel data to off-chip, more advanced and flexible classifiers.

# V. CONCLUSION

Future neural recording systems have to be fully implantable and operated wirelessly to decrease infection risks and increase patient independence. Nevertheless, the data throughput requirement of massively parallel recordings cannot be met with current wireless solutions for implants. In this paper, we presented a neural recording system-on-chip with on-chip feature extraction capability to tackle the data rate bottleneck. The chip extracts spectral features on-chip using versatile and hardware-friendly CHT, which are then sent out to an off-chip classifier to maintain algorithm flexibility. This configuration not only relaxes the hardware constraints but also enables versatility for facilitating different classification purposes. The selection of the features to be sent out is driven by the feature importance training of the off-chip classifier which ensures that only relevant information is transmitted. As a result, the transmitted data rate is reduced by 80% without compromising the detection performance. A second mode of operation for the CHT feature extractor is waveform reconstruction, which can be used for algorithm calibration, clinical research, and debugging. The 16-channel prototype in 65nm CMOS containing the AFE, the CHT processor, and the WPDT subsystem achieves 2.9 µW power and 0.021mm<sup>2</sup> area per channel. These results would enable massively parallel neural recording systems even with strict resource limitations. For example, a thousandchannel system would be feasible within a single 4 mm by 5 mm chip with 2.9 mW power consumption and 40 Mb/s data rate using the proposed approach.

## REFERENCES

- L. R. Hochberg *et al.*, "Neuronal ensemble control of prosthetic devices by a human with tetraplegia," *Nature*, vol. 442, no. 7099, pp. 164–171, Jul. 2006.

- [2] L. R. Hochberg *et al.*, "Reach and grasp by people with tetraplegia using a neurally controlled robotic arm," *Nature*, vol. 485, no. 7398, pp. 372–375, May 2012.

- [3] N. C. Swann et al., "Gamma oscillations in the hyperkinetic state detected with chronic human brain recordings in Parkinson's disease," J. Neurosci., vol. 36, no. 24, pp. 6445–6458, Jun. 2016.

- [4] B. Jarosiewicz and M. Morrell, "The RNS system: brain-responsive neurostimulation for the treatment of epilepsy," *Expert Rev. Med. Devices*, pp. 1–10, Sep. 2020.

- [5] J. G. Makin et al., "Machine translation of cortical activity to text with an encoder-decoder framework," Nat. Neurosci., vol. 23, no. 4, pp. 575– 582, Apr. 2020.

- [6] J. D. Simeral et al., "Home use of a percutaneous wireless intracortical brain-computer interface by individuals with tetraplegia," *IEEE Transac*tions on Biomedical Engineering, vol. 68, no. 7, pp. 2313–2325, 2021.

- [7] E. Musk, "An integrated brain-machine interface platform with thousands of channels," J. Med. Internet Res., vol. 21, no. 10, p. e16194, Oct. 2019.

- [8] S. Wang et al., "A compact quad-shank CMOS neural probe with 5,120 addressable recording sites and 384 fully differential parallel channels," *IEEE Trans. Biomed. Circuits Syst.*, vol. 13, no. 6, pp. 1625–1634, Dec. 2019.

- [9] Microsemi Corporation, "ZL70103 medical implantable rf transceiver dataheet revision 2," 2015.

- [10] H. Kassiri et al., "Rail-to-rail-input dual-radio 64-channel closed-loop neurostimulator," *IEEE J. Solid-State Circuits*, vol. 52, no. 11, pp. 2793– 2810, 2017.

- [11] A. M. Kamboh et al., "Area-power efficient vlsi implementation of multichannel dwt for data compression in implantable neuroprosthetics," *IEEE Transactions on Biomedical Circuits and Systems*, vol. 1, no. 2, pp. 128–135, 2007.

- [12] G. Gagnon-Turcotte et al., "Smart autonomous electro-optic platforms enabling innovative brain therapies," *IEEE Circuits and Systems Maga*zine, vol. 20, no. 4, pp. 28–46, 2020.

- [13] F. Chen et al., "Design and analysis of a hardware-efficient compressed sensing architecture for data compression in wireless sensors," *IEEE Journal of Solid-State Circuits*, vol. 47, no. 3, pp. 744–756, 2012.

- [14] X. Liu et al., "A fully integrated wireless compressed sensing neural signal acquisition system for chronic recording and brain machine interface," *IEEE Transactions on Biomedical Circuits and Systems*, vol. 10, no. 4, pp. 874–883, 2016.

- [15] G. K. Anumanchipalli et al., "Speech synthesis from neural decoding of spoken sentences," *Nature*, vol. 568, no. 7753, pp. 493–498, Apr. 2019.

- [16] K. H. Park et al., "Clinical outcome prediction from analysis of microelectrode recordings using deep learning in subthalamic deep brain stimulation for Parkinson's disease," PLoS One, vol. 16, no. 1, p. e0244133, Jan. 2021.

- [17] G. O'Leary et al., "NURIP: Neural interface processor for brain-state classification and programmable-waveform neurostimulation," *IEEE J. Solid-State Circuits*, vol. 53, no. 11, pp. 3150–3162, Nov. 2018.

- [18] Y. Wang et al., "26.3 A closed-loop neuromodulation chipset with 2-level classification achieving 1.5V pp CM interference tolerance, 35db stimulation artifact rejection in 0.5ms and 97.8% sensitivity seizure detection," in 2020 IEEE Int. Solid- State Circuits Conf. -. IEEE, Feb. 2020, pp. 406–408.

- [19] A. Uran et al., "An AC-coupled wideband neural recording front-end with sub-1 mm<sup>2</sup>xfJ/conv-step efficiency and 0.97 NEF," IEEE Solid-State Circuits Lett., vol. 3, pp. 258–261, 2020.

- [20] A. Uran et al., "A 16-channel wireless neural recording system-on-chip with CHT feature extraction processor in 65nm CMOS," in 2021 IEEE Cust. Integr. Circuits Conf. IEEE, Apr. 2021, pp. 1–2.

- [21] A. Goyal et al., "The development of an implantable deep brain stimulation device with simultaneous chronic electrophysiological recording and stimulation in humans," Biosens. Bioelectron., vol. 176, p. 112888, Mar. 2021.

- [22] S.-A. Huang et al., "A 1.9-mW SVM processor with on-chip active learning for epileptic seizure control," *IEEE J. Solid-State Circuits*, vol. 55, no. 2, pp. 452–464, Feb. 2020.

- [23] C. Aprile et al., "Adaptive learning-based compressive sampling for low-power wireless implants," *IEEE Trans. Circuits Syst. I Regul. Pap.*, vol. 65, no. 11, pp. 3929–3941, Nov. 2018.

- [24] P. Harpe, "A compact 10-b sar adc with unit-length capacitors and a passive fir filter," *IEEE Journal of Solid-State Circuits*, vol. 54, no. 3, pp. 636–645, 2019.

- [25] Federal Communications Commission, "15.517 Technical requirements for indoor UWB systems," Code Fed. Regul. Title 47 Telecommun.

- [26] G. Schiavone et al., "Soft, implantable bioelectronic interfaces for translational research," Adv. Mater., vol. 32, no. 17, p. 1906512, Apr. 2020

- [27] F. Fallegger et al., "MRI-compatible and conformal electrocorticography grids for translational research," Adv. Sci., vol. 8, no. 9, p. 2003761, May 2021

- [28] "International epilepsy electrophysiology portal. Accessed: 2020. [Online]. Available: www.ieeg.org."

- [29] M. Shoaran et al., "Compact low-power cortical recording architecture for compressive multichannel data acquisition," *IEEE Transactions on Biomedical Circuits and Systems*, vol. 8, no. 6, pp. 857–870, 2014.

- [30] A. Shoeb, "Application of machine learning to epileptic seizure onset detection and treatment," Ph.D. dissertation, Massachusetts Institute of Technology, 2009.

- [31] T. Chen and C. Guestrin, "XGBoost: A scalable tree boosting system," in Proc. 22nd ACM SIGKDD Int. Conf. Knowl. Discov. Data Min. New York, NY, USA: ACM, Aug. 2016, pp. 785-794.

- [32] M. Zijlmans et al., "High-frequency oscillations as a new biomarker in epilepsy," Ann. Neurol., vol. 71, no. 2, pp. 169-178, Feb. 2012.

- [33] J. A. Hartings et al., "Prognostic value of spreading depolarizations in patients with severe traumatic brain injury," JAMA Neurol., vol. 77, no. 4, p. 489, Apr. 2020.

- [34] J. P. Dreier et al., "Recording, analysis, and interpretation of spreading depolarizations in neurointensive care: Review and recommendations of the COSBID research group," J. Cereb. Blood Flow Metab., vol. 37, no. 5, pp. 1595-1625, May 2017.

Florian Fallegger received his B.S. (2013) from the Ecole Polytéchnique Fédérale de Lausanne (EPFL) and his M.S. (2015) from the Eidgenössische Technische Hochschule Zürich (ETHZ) in materials science and engineering. He received his PhD (2020) at the EPFL, where he worked on the fabrication and reliability of implants made from soft silicones. He used these conformable devices for recording and modulation in the brain and spinal cord in translational large animal models. His current research interest are soft implants for seamless interface within

the body, hybrid integration of active electronics, medical packaging and translational neuroengineering.

Arda Uran (S'17) received the B.Sc. degree in electronics and communication engineering from Istanbul Technical University (ITU), Istanbul, Turkey in 2015, and the M.Sc. degree in electrical engineering from Swiss Federal Institute of Technology in Lausanne (EPFL), Lausanne, Switzerland in 2017, where he is currently pursuing the Ph.D. degree in microelectronics. Since 2017, he has been with the Laboratory for Information and Inference Systems (LIONS) and the Microelectronic Systems Laboratory (LSM) at EPFL. His research interests include

energy-efficient implantable integrated circuits, wideband phase-locked loops, and high-performance data converters.

Kerim Ture received the B.Sc. degrees in electrical and electronics engineering and physics from Bogazici University, Istanbul, Turkey, in 2012, and the M.Sc. degree in electrical and electronics engineering and the Ph.D. degree in microsystems and microelectronics from the Swiss Federal Institute of Technology, Lausanne (EPFL), Lausanne, Switzerland, in 2014 and 2019, respectively. Since 2015, he has been with the Radio Frequency Integrated Circuits Group (RFIC) at EPFL. His research interests include low-power analog/mixed-signal and

radio frequency integrated circuits design for wireless sensor systems and implantable biomedical applications.

Cosimo Aprile received the B.S. degree in electronic engineering from the Politecnico di Torino, Italy, in 2010, and the joint M.S. degree in micro and nanotechnologies for ICTs from the Swiss Federal Institute of Technology, Lausanne (EPFL), Switzerland, the Institut National Polytechnique de Grenoble, and the Politecnico di Torino in 2012. Since July 2018, Cosimo is involved in analog/mixed signal circuit design in Kandou Bus, which is an innovative company in the high-speed and energy efficient chipchip link in the electronics industry. Prior to this,

Cosimo received his Ph.D at EPFL in 2018, were he was advised by Prof. Volkan Cevher and Prof. Yusuf Leblebici. During his doctoral research, he published papers related to high speed analog circuit design, signal processing and analog/mixed signal integrated circuits design for optimized information extraction from signals or data volumes.

Alix Trouillet received the B.S. degree in Biochemistry from the University of Cergy-Pontoise, France in 2006, and the M.S. degree in Pathophysiology from Pierre et Marie Curie University (UPMC), Paris 6, France, in 2008. She obtained her Ph.D. in Neuroscience in 2014 from University Paris 6 working on retinal degenerative diseases at the Vision Institute in Paris. Between 2015 and 2018 she was a postdoctoral fellow at Stanford University, CA, USA in the department of Otolaryngology working on pathophysiology of mechanotransduction in models

of deafness. In 2019, she joined the Laboratory of Soft Bioelectronic Interfaces at EPFL in Geneva, Switzerland where she is currently a research scientist. Her work includes translational study towards the development of a new auditory brainstem implant to restore hearing as well as fundamental research in sensory restoration in rodents using cortical stimulation.

Emilie C. M. Revol (S'21) received her B.Sc. (2016) in Life Sciences and M.S. degree (2019) in Bioengineering with a minor in Neuroprosthetics from the Ecole Polytechnique Fédérale de Lausanne. She is currently pursuing a PhD degree in the Laboratory for Soft Bioelectronic Interfaces in the EPFL Center of Neuroprosthetics. Her main research interest lie at the interface between engineering and neurosciences: implant design for cortical recording and modulation in various physiological phenomena, including auditory activity and spreading depolarisa-

Azita Emami (M'05-SM'17) received the B.S. degree from the Sharif University of Technology, Tehran, Iran, in 1996, and the M.S. and Ph.D. degrees in electrical engineering from Stanford University, Stanford, CA, USA, in 1999 and 2004, respectively., From 2004 to 2006, she was with the IBM Thomas J. Watson Research Center, Yorktown Heights, NY, USA. In 2007, she joined the California Institute of Technology (Caltech), Pasadena, CA, USA, where she is currently the Andrew and Peggy Cherng Professor of electrical engineering

and medical engineering, and an Investigator with the Heritage Medical Research Institute, Bakersfield, CA, USA. She also serves as the Executive Officer (Department Head) for electrical engineering with Caltech. Her current research interests include integrated circuits and systems, integrated photonics, wearable and implantable devices for neural recording, neural stimulation, sensing, and drug delivery., She was an IEEE SSCS Distinguished Lecturer from 2017 to 2018. She serves as an Associate Editor for the IEEE Journal of Solid State Circuits (JSSC).

Stéphanie P. Lacour (M'03) holds the Bertarelli Foundation Chair in Neuroprosthetic Technology at the School of Engineering at the Ecole Polytechnique Fédérale de Lausanne. She received her PhD in Electrical Engineering from INSA de Lyon, France, and completed postdoctoral research at Princeton University (USA) and the University of Cambridge (UK). She joined EPFL in 2011. Since January 2017, she is full professor in Microengineering and Bioengineering at EPFL. She is a cofounding member and current director of EPFL

Center for Neuroprosthetics, located at Campus Biotech Geneva, an EPFL associated campus. She is the recipient of the 2006 MIT TR35, the ERC StG in 2011, the ERC CG in 2016, and was nominated a 2015 Young Global Leader by the World Economic Forum.

Catherine Dehollain (M'93) received the master's degree in electrical engineering and the Ph.D. degree from the Ecole Polytechnique Federale de Lausanne (EPFL), Lausanne, Switzerland, in 1982 and 1995, respectively. From 1982 to 1984, she was a Research Assistant with Electronics Laboratories (LEG), EPFL. In 1984, she joined the Motorola European Center for Research and Development, Geneva, Switzerland, where she designed integrated circuits applied to telecommunications. In 1990, she joined EPFL as a Senior Assistant with the Chaire

des Circuits et Systemes, where she was involved in impedance broadband matching. Since 1995, she has been responsible for the RFIC Group, EPFL, for RF activities. She has been the technical project manager of the European projects, Swiss CTI projects, and the Swiss National Science Foundation projects, dedicated to RF wireless micro-power sensor networks and mobile phones. Since 1998, she has been a Lecturer with EPFL in the area of RF circuits, electric filters, and low power CMOS analog circuits. From 2006 to 2014, she was a Maitre d'Enseignement et de Recherche (MER) with EPFL. Since 2014, she has been an Adjunct Professor with EPFL. She is the author or coauthor of seven scientific books and 190 scientific publications. Her current research interests include biomedical remotely powered sensors, RFIDs, RF circuits, low-power analog circuits, and electrical filters.

Yusuf Leblebici (M'90–SM'98–F'10) received the B.Sc. and M.Sc. degrees in electrical engineering from Istanbul Technical University, Istanbul, Turkey, in 1984 and 1986, respectively, and the Ph.D. degree in electrical and computer engineering from the University of Illinois at Urbana–Champaign, Champaign, IL, USA, in 1990. Since 2002, he has been a Chair Professor with the Swiss Federal Institute of Technology (EPFL), Lausanne, Switzerland, and the Director of the Microelectronic Systems Laboratory. In November 2018, he was appointed as

the President of Sabanci University. He has authored or coauthored seven textbooks and more than 400 articles published in various journals and conferences. His research interests include design of high-speed CMOS digital and mixed-signal integrated circuits, computer-aided design of VLSI systems, intelligent sensor interfaces, neuromorphic circuit and system concepts, and VLSI reliability analysis. In 2020, he has received the Electrical and Computer Engineering Distinguished Alumni Award from the University of Illinois at Urbana-Champaign (UIUC). He has served as an Associate Editor of the IEEE Transactions on Circuits and Systems and IEEE Transactions on Very Large Scale Integration (VLSI) Systems. He was elected as a Distinguished Lecturer of the IEEE Circuits and Systems Society from 2010 to 2011.

Volkan Cevher (S'95–M'06–SM'10) received the B.Sc. (valedictorian) degree in electrical engineering from Bilkent University, Ankara, Turkey, in 1999, and the Ph.D. degree in electrical and computer engineering from the Georgia Institute of Technology, Atlanta, GA, USA, in 2005.,He was a Research Scientist with the University of Maryland at College Park, College Park, MD, USA, from 2006 to 2007, and Rice University, Houston, TX, USA, from 2008 to 2009. He is currently an Associate Professor with the École Polytechnique Fédérale de Lausanne,

Lausanne, Switzerland, and a Faculty Fellow with the Electrical and Computer Engineering Department, Rice University. His current research interests include signal processing theory, machine learning, convex optimization, and information theory, Dr. Cevher was a recipient of the IEEE Signal Processing Society Best Paper Award in 2016, the Best Paper Award at CAMSAP in 2015, the Best Paper Award at SPARS in 2009, and the ERC CG in 2016 and the ERC StG in 2011.