# A 40-nm Cryo-CMOS Quantum Controller IC for Superconducting Qubit

Kiseo Kang<sup>®</sup>, Graduate Student Member, IEEE, Donggyu Minn<sup>®</sup>, Graduate Student Member, IEEE, Seongun Bae<sup>®</sup>, Jaeho Lee<sup>®</sup>, Seokhyeong Kang<sup>®</sup>, Member, IEEE, Moonjoo Lee, Ho-Jin Song<sup>®</sup>, Senior Member, IEEE, and Jae-Yoon Sim<sup>®</sup>, Senior Member, IEEE

Abstract—This article presents a cryo-CMOS quantum controller IC for superconducting qubits. The proposed globally synchronized clock system internally generates different local oscillator (LO) frequencies using multiple phase-locked loops (PLLs) driven by a common reference clock. It provides flexibility in spectral management as well as scalability for expansion to a large-scale quantum controller. The test chip includes two PLLs, four pulse modulator channels, and two receiver channels. Implemented chip in 40-nm CMOS shows full functionalities at 3.5 K. The designed pulse modulator circuits are verified with the specifications for expected fidelity of 99.99%.

Index Terms—Cryo-CMOS, direct digital synthesis (DDS), quantum computing, quantum controller, superconducting qubit.

### I. Introduction

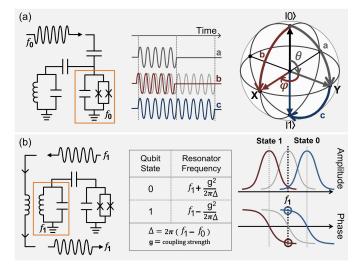

ITH a remarkable achievement in the number of superconducting qubits, the next-step research toward the realization of a fault-tolerant scalable quantum computer is addressing challenges in scalable hardware system development [1], [2]. The superconducting qubit is an *LC* resonator with a nonlinear inductor formed by the Josephson junction whose inductance is quantized by energy states [3], [4], [5], [6]. The superconducting qubit can be designed to have a specific natural frequency that makes a transition between the states  $|0\rangle$  and  $|1\rangle$ . The state of the qubit can be controlled through microwaves at the natural qubit frequency [7].

The state of a single qubit can be represented as a point on a Bloch sphere. Controlling the state corresponds to a rotation of the point on the Bloch sphere [8]. The phase of the driving microwave signal at the qubit frequency is the angle of the rotation projected on the *XY*-plane [see

Manuscript received 15 April 2022; revised 27 June 2022, 2 August 2022, and 8 August 2022; accepted 9 August 2022. Date of publication 25 August 2022; date of current version 24 October 2022. This article was approved by Associate Editor Fabio Sebastiano. This work was supported in part by the National Research Foundation (NRF) through the Korea Ministry of Science and ICT under Grant 2019R15A1027055 and in part by NRF-2019-Global Ph.D. Fellowship Program and IC Design Education Center (IDEC). (Corresponding author: Jae-Yoon Sim.)

The authors are with the Department of Electronic and Electrical Engineering, Pohang University of Science and Technology, Pohang 37673, South Korea (e-mail: kiseo@postech.ac.kr; dkminn89@postech.ac.kr; bsu93@postech.ac.kr; jhlee96@postech.ac.kr; shkang@postech.ac.kr; moolee@postech.ac.kr; hojin@postech.ac.kr; jysim@postech.ac.kr).

Color versions of one or more figures in this article are available at https://doi.org/10.1109/JSSC.2022.3198663.

Digital Object Identifier 10.1109/JSSC.2022.3198663

Fig. 1. Superconducting qubit whit (a) state control and (b) readout.

Fig. 1(a)]. The total amount of microwave energy determines the amount of the rotation [6], [7], [8], [9], [10], [11]. The natural frequency for the superconducting qubit is typically designed to be 4.5–6 GHz with a difference of tens of MHz between neighboring qubits. The state of a qubit is read through an additional resonator whose frequency is tuned at 6.5–8 GHz. Since the resonator is coupled to the qubit, the state of the qubit would be reflected at the resonant frequency through dispersive interaction [6], [7], [8], [9], [10], [11], [12]. Therefore, the state of a superconducting qubit can be sensed by measuring either the magnitude or the phase of the probing signal coupled with the resonator [see Fig. 1(b)].

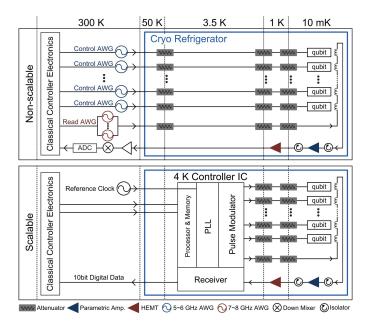

The requirement of multiple cables per qubit for control and readout becomes the major challenge in the system development as the number of qubits increases. To reduce the number of cables for the readout, the states of multiple qubits with different resonant frequencies could be simultaneously read using a single microwave feedline [13], [14]. However, reducing the number of cables for the readout only is a temporary measure, and the total number of cables to the room temperature eventually increases proportionally to the exponentially growing number of qubits. This issue in scalability leads to extensive research to develop a microsystem sitting at the 4 K stage in the same dilution refrigerator to control thousands or millions of qubits at 10 mK (see Fig. 2)

Fig. 2. Quantum computer setups for superconducting qubits.

[13], [15]. There have been cryo-CMOS IC implementations of microwave pulse modulators for the spin qubits [16], [17], [18], [19]. The pulse modulation with the direct frequency synthesis demonstrated the feasibility of driving multiple spin qubits using frequency-division multiplexing (FDM) and time-division multiplexing (TDM) [16], [17], [18], [19]. Reference [16] reported the first implementation of a cryo-CMOS system-on-chip (SoC) including both read and write chains for the spin qubits. However, the previous works used external local oscillator (LO) sources for frequency synthesis. External feeding of LO requires a precise matching; otherwise, a failure would cause a significant LO leakage to the qubit driving channel through PCB traces, resulting in an ac-Stark shift of the qubit state by unwanted tones at near-resonance.

For the superconducting qubits, the Josephson parametric amplifier (JPA), as the first-stage amplifier in the readout channel, shows a near-quantum-limited noise level in a bandwidth of ~GHz [20]. The FDM-based readout has been demonstrated using a wideband JPA at 10 mK followed by an HEMT-based low-noise amplifier (LNA) at 4 K [21]. Since this low-noise legacy receiver chain greatly relieves the burden on noise performance, the receiver frontend integrated into the CMOS SoC at 4 K can support a stable wideband amplification for the subsequent processing by analog-to-digital conversion.

Unlike the readout, however, multiple access has been hardly considered for the driving of the superconducting qubits. Compared to the qubits based on the spin energy (e.g., semiconductor, trapped-ion, and diamond), the superconducting qubit has a much shorter energy relaxation time  $(T_1)$  of  $10-100~\mu s$ . Thus, superconducting qubits should be driven in a short pulse of 15-30 ns for each gate operation so that many gate operations could be completed within the given coherence time. However, the shorter pulsewidth brings about a sacrifice of spectral selectivity resulting in a nonnegligible spectral leakage. Considering a finite anharmonicity separation

of 150–350 MHz between the frequencies  $\omega_{01}$  (for  $|0\rangle \rightarrow |1\rangle$ ) and  $\omega_{12}$  (for  $|1\rangle \rightarrow |2\rangle$ ) as well as the spectral leakage, the use of FDM or TDM with a single RF cable would not be feasible. Therefore, the major challenge in the driving of superconducting qubits is the low-power implementation of individual pulse modulators per qubit [22], [23], [24]. In addition to the challenges in low-power implementation, the internal generation of thousands or millions of qubit frequencies also presents a still another tough problem in spectrum management. The previous works assume the use of a common LO frequency for the single-sideband (SSB) mixing in direct frequency synthesis [23], [24]. The synchronized driving of the thousands or millions of internal LO buffers brings about a huge simultaneous switching noise. The synchronized LO tone will dominate the spectrum of power lines over the whole chip, resulting in a significant LO leakage that could destroy the gate fidelity.

This article presents a cryo-CMOS controller IC with a globally synchronized clock system. It includes multiple phase-locked loops (PLLs) for the internal generation of LOs. There has been previous demonstration on including a PLL for internal LO generation for the readout of spin qubits with FDM [25]. This work proposes employing multiple PLLs, which enables managing different LO frequencies with each PLL responsible for one LO frequency for a group of qubits, where the group can be selected out of thousands or millions of qubits. Employing multiple PLLs enables managing different LO frequencies with each PLL responsible for one LO frequency for a group of qubits, where the group can be selected out of thousands or millions of qubits. As the number of PLLs for different LOs increases, the LO leakage is effectively suppressed by uniformly distributing the LO power in a band of frequency. It provides a similar effect to the spread spectrum clock generation which is a common way to overcome the issues of electromagnetic interference (EMI) in wireline communication. In addition, the internal generation of LOs by the PLLs provides an extra benefit of global synchronization. By applying a common reference clock (~500 MHz) to all the PLLs, the whole system using different LOs can be synchronized to the given reference clock. Though this prototype chip demonstrates a small system with two PLLs for thepulse modulator and the receiver channels, respectively, the architecture can be readily expandable to a larger system with a number of PLLs. Implemented chip in 40-nm CMOS shows full functionalities at 3.5 K. This article is an extended version of one presented at the international solid-state circuits conference (ISSCC) [26]. The original chip at ISSCC has a problem with configurations, so only a few configurations were allowed in the test. The measurements reported in this article have been conducted with a revised chip in which the configuration block was modified to have larger setup/hold margins. It enables an optimal setting of PLLs and results in an improvement of the integrated jitter from 274 to 115 fs.

## II. ARCHITECTURE

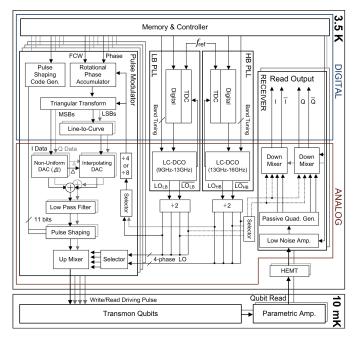

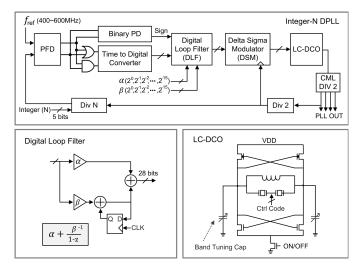

Fig. 3 shows the overall block diagram of the proposed quantum controller IC. It consists of four sets of pulse

Fig. 3. Overall circuit schematic of the proposed cryo-CMOS controller IC.

modulators, two sets of receiver frontend, and two digital PLLs (DPLLs). These blocks and a memory for storing instructions and data are managed by a global controller operating in a single clock system. The pulse modulator uses direct digital synthesis (DDS) and SSB mixing to generate the frequency and the phase needed for individual qubit control. As a result, an internally generated intermediate frequency (IF) is added to or subtracted from an LO frequency provided by one of the two PLLs. The two integer-N DPLLs receive a common reference clock. They have an identical architecture with programmable bandwidth and multiplication factors. One is for a low-band (LB) PLL for the qubit driving, and the other is for a high-band (HB) PLL for the qubit readout. Each has an LC-based digitally controlled oscillator (DCO) with a dedicated frequency tuning range. The LB- and HB-PLLs have lock ranges of -13 and 1-16 GHz, respectively. Their outputs are divided by 2 to provide quadrature phases. The pulse modulator selects one of LB- and HB-PLL as the LO source to synthesize pulses for control and readout, respectively. The LO frequency is divided by 8 or 16 to use as the system clock.

The role of the receiver chain is to develop the inputsignal to have an appropriate voltage swing for the baseband processing. The receiver chain consists of a CMOS LNA, a passive quadrature generation network, and two I/Q down-conversion mixers. The receiver operates at 5–7.25 GHz. The superposition of different tones under the FDM raises the peak-to-average power ratio (PAPR) of the input waveform. Therefore, the LNA is required to provide a stable wideband amplification with enough dynamic range. There are two known ways for the down-conversion: 1) differential RF with quadrature LO mixing and 2) quadrature RF with differential LO mixing. In this work, the latter was adopted to reduce the number of LO buffers, hence reducing the power consumption. The quadrature-balanced layout matching was easier for the RF signal than for the LO signal that includes longer routings.

### III. SPECIFICATION

The gate fidelity of the currently available superconducting quantum processor is at the level of 99.9% [27]. Thus, the target specifications for the overall circuit operation of the proposed work were set for an error rate of less than 0.01%. The error is caused by imperfections of analog circuit operation, finite resolution of digital control, and phase noise at the pulse modulator output. To achieve the target error rate of 0.01%, the effects of individual error contributors need to be much lower than 0.01%.

### A. Digital Control

The DDS-based microwave frequency generation is performed by SSB mixing of a digitally synthesized IF and the LO. The waveform of the generated pulse output,  $P_{OUT}(t)$ , is

$$P_{\text{OUT}}(t) = A(t)\sin\{(\omega_{\text{LO}} + \omega_{\text{IF}})t + \phi_{\text{IF}}\}\tag{1}$$

where A(t) represents the shape of the pulse amplitude of the microwave and  $\phi_{\rm IF}$  is the initial phase of the IF. The total amount of microwave energy in A(t) is determined by a combined control of the height and width of A(t). Controlling A(t) with more than 9b resolution is required for an error rate of 0.01% [8].

The phase error in  $\phi_{\rm IF}$  should be less than 0.7° for an error rate of less than 0.01% [8]. The phase of IF,  $\phi_{\rm IF}$ , remains constant at  $P_{\rm OUT}(t)$  by continuous accumulation of a frequency code using a 15b digital accumulator. The 15b expression would be enough for the error rate of less than 0.01. For example, when driven with a 1.5-GHz system clock, the 15b resolution leads to an error rate of 0.002% with a Rabi frequency of 5 MHz [28].

# B. Spectrum Management

The energy at unwanted tones needs to be suppressed by more than 40 dB for an error rate of 0.01%. The conservative target for the suppression of relative power at  $\omega_{12}$  needs to be set to 50 dB [8]. However, suppressing all the tones other than the target tone by 50 dB is very difficult because of the nonlinear operation of analog circuits, mismatches among the cells in the DAC, and various interferences from a number of other pulse modulators. It should be noted that the tone at  $\omega_{12}$ causing  $|1\rangle \rightarrow |2\rangle$  transition is the major factor that degrades the gate fidelity. The proposed architecture of multiple LOs gives great benefits in avoiding the spectral leakage at the $\omega_{12}$ . Since  $\omega_{12}$  is at 150–350 MHz lower than  $\omega_{01}$ , the LO can be set to be far from  $\omega_{12}$ . In addition, by positioning the synthesized  $\omega_{01}$  at the left-hand side of LO in SSB mixing, the chances of the image frequency of the SSB falling at  $\omega_{12}$ can also be avoided.

# C. Phase Noise

The individual effects of noise are reflected in the phase noise at the output of the pulse modulator. Since the phase noise indicates the spectral density of the synthesized output, the total noise power can be estimated by integrating the phase noise up to a band of interest (~10 MHz offset). The phase

error of less than  $0.7^{\circ}$  for an error rate of less than 0.01% corresponds to an integrated jitter of 350 fs<sub>rms</sub> at 5.5 GHz [8]. The jitter at the synthesized output is affected by both LO and IF paths, including jitter terms in (a) leads to

$$\begin{split} P_{\text{OUT}}(t) &= A(t) \sin[\omega_{\text{LO}}\{t + j_{\text{LO}}(t)\} \\ &+ \omega_{\text{IF}}\{t + j_{\text{IF}}(t)\} + \phi_{\text{IF}}] \\ &= A(t) \sin\left[(\omega_{\text{LO}} + \omega_{\text{IF}})\left\{t + \frac{\omega_{\text{LO}}}{\omega_{\text{LO}} + \omega_{\text{IF}}}j_{\text{LO}}(t) \right. \\ &\left. + \frac{\omega_{\text{IF}}}{\omega_{\text{LO}} + \omega_{\text{IF}}}j_{\text{IF}}(t)\right\} + \phi_{\text{IF}}\right] \end{split}$$

where  $j_{LO}(t)$  and  $j_{IF}(t)$  represent jitters at IF and LO frequencies, respectively. In the LO path, extra circuit-induced thermal noise would be added to the initial phase noise of LO at the PLL output. They are caused by an inevitable delay by routings, LO buffers, and SSB mixer circuits. The jitter at  $P_{\text{OUT}}(t)$  is also affected by the IF path. The sinusoidal waveform of IF is built by the sampling of DAC. Since the system clock for the sampling is provided by dividing the same LO, the low-frequency parts of  $j_{LO}(t)$  and  $j_{IF}(t)$  are strongly correlated in a frequency band of interest up to 10 MHz, or  $j_{LO}(t) = j_{IF}(t)$ . Thus, the base for the best achievable integrated jitter at  $P_{OUT}(t)$  is the same as that of the PLL output. Note that if  $j_{LO}(t)$  and  $j_{IF}(t)$  are not correlated, that is, using two different sources for the IF and the LO, the integrated jitter at  $P_{\rm OUT}(t)$  would be decreased by  $(\omega_{\rm LO}^2+\omega_{\rm IF}^2)^{1/2}/(\omega_{\rm LO}+\omega_{\rm IF})$ or increased by  $(\omega_{LO}^2 + \omega_{IF}^2)^{1/2}/(\omega_{LO} - \omega_{IF})$ , depending on the selection of the band side of SSB mixing. Taking individual noise contributions into account, the target integrated jitter at the PLL output must be much smaller than 350 fs<sub>rms</sub> for an error rate of 0.01%. The target jitter for the PLL can be reasonably set to about 100 fs<sub>rms</sub> [8].

### D. Receiver Chain

For a wideband operation, a multistage topology of LNA with a transformer load was proposed to achieve a sub-1-dB NF at cryogenic temperature for a direct readout of spin qubits [29]. This work adopts a similar multistage topology to support the wideband readout of superconducting qubits for the FDM. As the inductive source degeneration provides a favorable structure for the frequency tuning as well as for the noise matching, the three stages were, respectively, designed to be tuned at different frequency bands for a wideband operation. In addition, care needs to be taken for the amplification of -80 dBm ( $VP-P=63.2~\mu V$  at  $50~\Omega$ ) to have an appropriate output voltage swing for the next baseband processing. In this work, the target gain of the LNA was set to 40 dB.

The receiver chain assumes that -125 dBm output from a qubit readout resonator [30] is preprocessed by the traditional low-noise legacy amplification stages, for example, a 15 dB-gainJPA at 10 mK as the first stage and a 30 dB-gain HEMT LNA at 4 K as the second stage. Thus, the role of the receiver chain is to amplify the -80-dBm signal using a wideband CMOS LNA as the third stage so that the next

Fig. 4. Pulse modulator block diagram.

stage can support the FDM-based readout. Considering the combined NF of three amplification stages,  $F = F_1 + (F_2-1)/G_1 + (F_3-1)/(G_1G_2)$ , the effect of the third stage on the overall NF in a whole readout system is less than 0.1 dB unless the NF of the third stage does not exceed 30 dB. So, the noise performance is no more a major factor in the design of LNA. In the down-conversion mixer, gain and phase mismatches in the double-balanced circuit structure can also induce a finite image rejection ratio (IRR). Though it raises the noise floor by a factor of  $1 + 10^{((-IRR/10))}$ , its effect on the input-referred noise of the receiver chain becomes reduced to less than 0.1 dB by the LNA gain of 40 dB. The whole receiver chain in this prototype was designed to dissipate less than 20 mW. It would be further reduced by the optimization of circuits in continued research.

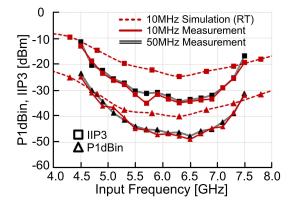

According to the analysis of the required measurement time for superconducting qubits, a high fidelity can be achieved for the readout of multiple qubits with 30–40 MHz separations between the resonator frequencies [21]. Considering the IF band of less than 500 MHz, the design of the proposed receiver chain assumed, supporting an FDM-based readout up to 8 qubits with 50-MHz separations. The superposition of different tones modulated in the way of phase shift keying (PSK) raises the PAPR in the input signal. The PAPR with an 8-qubit FDM is about 10 dB [31]. The required P1dBin of the LNA can be derived as -80 dBm (each tone) + 10 dB $(\sim 8 \text{ tones}) + 10 \text{ dB (PAPR)} = -60 \text{ dBm}$ . Using commonly used calculations for IIP3, which is 9.6 dB higher than P1dBin, the corresponding IIP3 should be -50 dBm. Note that IIP3 is a standard term for the indication of linearity with a two-tone test. According to the relationship in the signal-to-distortion ratio between two-tone and multiple tones [32], an additional 3 dB margin is required on the IIP3 for the case of eight tones to secure the same level of a signal-to-distortion ratio at the band edge. It leads to an IIP3 target of -47 dBm.

### IV. CIRCUIT DESCRIPTION

## A. Pulse Modulator

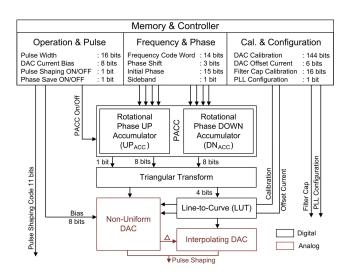

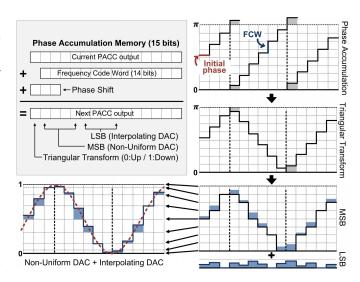

1) Direct Digital Synthesizer: The frequency and the phase of the IF tones are processed in the digital domain. Fig. 4 shows

the overall block diagram of the proposedpulse modulator that consists of a digital part for IF synthesis and an analog part for DAC-based sinusoid generation. The phase and the frequency of IF are generated using a 15b rotational phase accumulator (PACC) operating at the system clock which is divided by N from the PLL output (N=8 at LB-PLL, N=16 at HB-PLL). Starting from an initially given 14b phase code, the PACC accumulates a 14b frequency-code word (FCW). Thus, the PACC output represents the phase at the frequency given by the FCW.

The digital processing gives flexibility in supporting various options for qubit control. The information includes pulse duration, pulse shape, and the number of the same pulses to be consecutively repeated in time. A local register file is also employed to store 16 sets of FCW and the amount of phase shift so that thepulse modulator could support consecutive 16 switching of the frequency and the phase of IF in real-time. Extra 3b are allocated to provide eight cases of the phase shift with  $a\pi/4$  step. A 1b, named sideband, indicates the selection of the high or the low side in the SSB mixing. This sideband selection is realized by switching the connections of the in-phase (I) and quadrature-phase (I) of the IF.

Note that the pulse modulator produces the microwave output only when the qubit is used in a quantum gate. It should be synthesized on demand through an SSB mixing using an LO. Since a qubit can be involved in a number of quantum gates, the phase evolution of the used qubit should be tracked in time so that the qubit can be used by other quantum gates later. Thus, the phase of the driving pulse for a qubit should be coherent throughout the quantum algorithm until the state is measured. In the DDS approach, it can be achieved by holding the phase of the IF signal instead of holding the phase of the microwave frequency. When a qubit enters on standby until the next use, the phase-save is turned on. It makes the PACC only keep accumulating the given FCW.

We propose a triangular transformation that converts the PACC output to a triangle-shaped transition. It is a digital preprocessing to help build a sinusoidal shaping in digital-to-analog conversion. For the implementation of the triangular transform, the PACC employs two accumulators (ACCs),  $UP_{AC}C$  and  $DN_{AC}C$ , respectively. The former increases the output by adding the FCW, while the latter decreases it by subtracting the FCW starting from the same initial phase. The triangular transform is realized by alternately taking the next 8b from the outputs of the two accumulators according to the MSB of the  $U_{PACC}$  output. The 8b becomes four MSBs and LSBs to the following DAC (see Fig. 5).

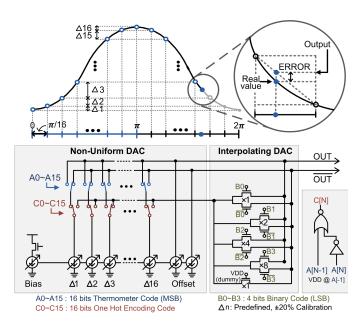

2) DAC: Fig. 6 shows a detailed circuit schematic of DAC. The four MSBs can be interpreted as quantized 16 levels of the triangular waveform, while the four LSBs indicate 16 cases of residue. The MSBs are input to a nonuniform DAC. The LSBs are processed by a Line-to-Curve block for curvature compensation and then passed to an interpolating DAC. The nonuniform DAC has 16 current sources driven by a 16b thermometer code converted from the MSB code. The 16 current sources are responsible for 16 nonuniform steps,  $\Delta 1-\Delta 16$ , which are precalculated to effectively approximate a sinusoid. Each step corresponds to an incremental amplitude change of

Fig. 5. Conceptual illustration of the proposed DAC-based synthesis.

Fig. 6. Circuits for DACs.

the sinusoid for a phase change of  $\pi/16$ , respectively. As a result, the triangular transition in the digital domain can be translated into a sinusoidal transition in the analog domain. Though the number of steps is only 16, the optimization of custom-defined steps does not have a limit in resolution. Employing only 16 current sources with differential switching enables a high-speed DAC operation up to 1.5 GHz. Bias for the overall current level can be adjusted with an 8b code.

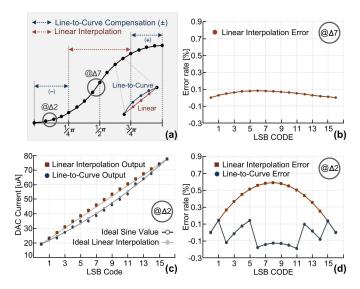

The quantized steps are further fractionalized by the interpolating DAC driven by the four LSBs. One of 16 current sources to be fractionalized is bypassed by the interpolating DAC. The selected current source sees the input resistance of the interpolating DAC. Since the differential switch turns on only one transistor, the current source sees a constant input resistance of  $1/(16 \cdot g_m)$  regardless of the interpolating code (B0–B3), while the ratio between the two input resistances to OUT and  $\overline{OUT}$  is given by the code. A linear interpolation

Fig. 7. Curvature compensation (a) with a Line-to-Curve transformation, (b) linear interpolation error at  $\Delta 7$ , (c) simulated DAC current at  $\Delta 2$ , and (d) effect of Line-to-Curve at  $\Delta 2$ .

divides the selected current into two branches of the differential outpu according to the ratio. Therefore, the interpolating DAC adds the residue to the output of the nonuniform DAC. The differential output of the whole DAC becomes

$$DAC_{out}(k) = \sum_{i=1}^{k-1} \Delta_i + \frac{LSB}{16}(\Delta_k)$$

(3)

where k represents the value of MSB.

The linear interpolation eventually causes a systematic error because it approximates the curved shape with a straight line (see Fig. 7). Simulation reveals > 0.5% error in the edge codes  $(\Delta_1 - \Delta_4 \text{ and } \Delta_{13} - \Delta_{16})$  while it keeps <0.2% error in the middle codes ( $\Delta_5$ - $\Delta_{12}$ ). The large error in the edge codes is caused not only by an inherent difference between the line and the curve, but also by a failure of ideal interpolation. As the difference between OUT and OUT increases, the transistor whose drain node is connected to the lower voltage would fail to keep operating at the saturation region. It becomes more serious in edge codes where the voltage swing between OUT and OUT approaches the maximum. Those errors can be reduced by preprocessing the LSB values with a digitaldomain Line-to-Curve mapping. A lookup table (LUT) is employed for this compensation. The LUT is used only for the eight cases of the MSBs ( $\Delta_1$ - $\Delta_4$  and  $\Delta_{13}$ - $\Delta_{16}$ ). The LUT receives 4b LSBs as the address and outputs a 4b content. There are two LUTs for the concave and convex conversions, respectively. With the total cost of only 128b (=2 LUTs  $\times$ 16 contents  $\times$  4b) for the two LUTs, the error can be reduced to less than 0.2%. Equation (1) is then modified to

$$DAC_{out}(k) = \sum_{i=1}^{k-1} \Delta_i + \frac{f(LSB)}{16}(\Delta_k).$$

(4)

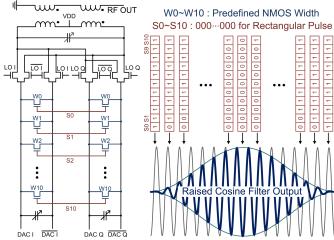

3) Envelope Shaping: The DAC output is followed by an optional raised-cosine envelope shaper before being mixed with quadrature LO phases. For the raised cosine filtering,

Fig. 8. Circuit schematic of raised cosine pulse shaping filter.

a shunt-based envelope shaping is applied to the output of the DAC. Fig. 8 shows a circuit schematic for the envelope shaping. Since the DAC generates a sinusoidal current output in a differential form, the amplitude modulation is performed by controlling the conductance of MOS-based shunt resistance. It can be simply achieved by monotonically decreasing or increasing the number of turn-on MOS switches implemented with 11 predefined-sized transistors. The switching is driven by the same system clock which is divided from the LO. The pulse modulator circuit supports two cases of pulse shaping, that is, the raised cosine by monotonic switching and the rectangular by setting all the 11b to 0. The pulse shaping does not require additional power consumption in the analog part. Advanced pulse shaping for derivative removal by an adiabatic gate (DRAG) to reduce spectral leakage was not considered in this work.

4) Considerations for Cryogenic Circuit Design: There have been a number of literature on the characterizations of CMOS devices at cryogenic temperature. The cryo-CMOS experiences all the increases in threshold voltage, mobility, and subthreshold slope [15], [33]. With these characteristics, the functionality of CMOS circuits at 4 K has been verified in the prior works [15], [16], [17], [18], [19], [22], [23], [24], [27]. The increased mobility results in about a 30% increase in the on-current of switches, enabling a high-speed digital operation at a faster clock [15], [33]. On the other hand, the increased threshold voltage can cause increased sensitivity to supply variations of digital circuits. So, the digital blocks in this work were designed to have more setup and hold margins. For analog circuits, the increase in the subthreshold slope can degrade the device matching characteristics. To mitigate the effect of mismatches among the current sources in DAC, a larger voltage (0.62 V) was used as the gate-to-source bias with long channel devices (L = 200 nm) for the current sources. The increased mismatch in the double-balanced mixer circuit causes a larger LO leakage. To compensate for the effect of mismatch, each DAC accompanies an extra branch for a variable current offset tuned by a 3b calibration code.

Fig. 9. Circuit diagram of PLL.

### B. Phase-Locked Loop

The operation of an analog PLL strongly relies on the optimized design of the charge pump and the loop filter. However, the CMOS at cryogenic temperature suffers from significant changes in threshold voltage, mobility, subthreshold slope, as well as degraded matching characteristics [15], [33], [34]. Since the SPICE model for cryo-CMOS was not available in this work, we employed an integer-N DPLL architecture that can be characterized by programmable loop filter coefficients and a feedback factor. The two PLLs for HB and LB receive a common reference clock in a range of 300-500 MHz for global synchronization of the whole system to a single time reference. Each PLL includes an LC-DCO with band-tuning MIM capacitors driven by a 5b code (see Fig. 9). The frequency of LC-DCO is controlled by a 127b thermometer code with each bit setting the bias of individual MOS capacitors. This digital control has a frequency resolution of 0.5 MHz in the selected frequency band. The TDC was designed to have a time resolution of 0.5 ps in a conversion range of 10 ps. The loop dynamics are programed by two coefficients of the loop filter,  $\alpha$  and  $\beta$ , responsible for the proportional and integral paths, respectively. The former dominantly affects the stability, while the latter effectively changes the loop bandwidth.

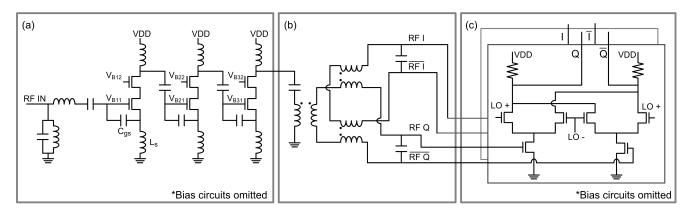

### C. Receiver

The receiver chain consists of an LNA, a passive quadrature generation network, and two I/Q down-conversion mixers (see Fig. 10). Since the commercial foundry does not provide the process design kit (PDK) for cryo-CMOS, sensitive RF circuits should be designed to secure stable operation using the available models at room temperature. To reduce the sensitivity to the threshold voltage change, the biases were set for the transistors to operate with a higher gate-to-source voltage. Careful considerations were also given to keep enough margin for stability in the design of LNA since it would experience an increased gain at cryogenic temperature. However, overall improvements in gain and noise performance are expected by an increased transconductance and a decreased passive loss at the cryogenic temperature [33], [35].

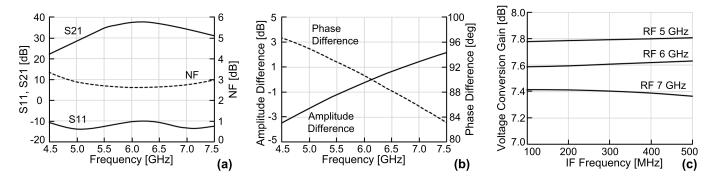

1) Low-Noise Amplifier: The LNA is formed with three stages of a single-ended cascode amplifier with an inductive source degeneration. Since the cascode configuration inherently curtails the coupling between the input and the output, it improves the stability and gives more degrees of freedom for input and output matching. The inductive source degeneration has been widely adopted to achieve the input matching with good noise performance. The real part of the input impedance is given as

$$R(Z_{\rm in}) = \frac{g_m * L_s}{C_{\rm gs}} \approx \omega_T L_s \tag{5}$$

where  $\omega_T$  represent the transit frequency [36]. The nonzero imaginary part of the input impedance can be compensated by adding a reactance part (e.g., an inductor in series). The same circuit topology is used for the three stages with interstage matchings. Placing similar inductors at the drain and the source in each stage gives extra benefits of a similar layout between the upper and the lower parts of the LNA. It further improves stability by balancing the feedback paths of opposite polarity. The first stage of LNA includes additional circuits for the protection of electrostatic discharge (ESD). A shunt LC and a series inductor are employed to achieve the ESD protection as well as a wideband input matching. Simulation at room temperature shows a gain of over 30 dB in a wideband of 5.5–7 GHz with  $S_{11}$  of <–10 dB. The NF is <3 dB in the frequency band of interest [see Fig. 11(a)].

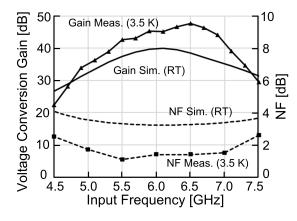

2) Quadrature Generation Network: The mixer projects the RF signal to the domain of LO for the down-conversion. There are two ways to perform the down-conversion: 1) mapping differential RF signal to quadrature LO and 2) mapping quadrature RF signal to differential LO. In this work, the latter was adopted to save power consumption by using only two LO buffers in the mixer stage. In addition, the quadraturebalanced layout for the individual RF signal is easier than for the common LO, which would be used by multiple pulse modulators. The quadratics of RF were obtained by a passive quadrature generation network with coupled inductors [37]. The single-ended LNA output is first converted to a differential signal by a balun. It is then subsequently processed with two transformers to produce quadrature RF signals. A shunt capacitor is added at each output for fine adjustment of the phase difference between I and Q. This quadrature RF generation scheme based on the passive transformer network causes inevitable mismatches in gain and phase as the frequency band is widened. Simulation shows that the designed quadrature network has a gain mismatch of <2 dB and a phase mismatch of  $<5^{\circ}$  in a frequency range of 5.2–7.3 GHz [see Fig. 11(b)]. However, the effect of mismatches can be easily corrected by baseband digital processing after analogto-digital conversion. The gain and phase mismatches can also induce a finite tone at the image frequency. Calculation from Section III-D shows that the mismatches result in an IRR of 18.2 dB. This corresponds to a degradation of NF by less than 0.1 dB. Two double-balanced mixers are used for the downconversion. Fig. 11(c) shows simulated voltage conversion gain using high-side LO frequencies of 5-7 GHz, respectively, when converted IF is in 100-500 MHz.

Fig. 10. Circuit schematic of the receiver chain consisting of (a) LNA, (b) quadrature generation network, and (c) down-conversion mixer.

Fig. 11. Simulation results (room temperature) of (a) the LNA, (b) quadrature generation network, and (c) down-conversion mixer.

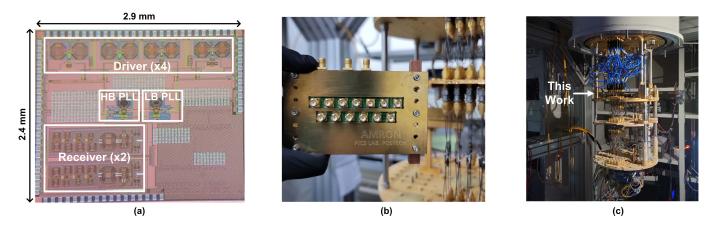

Fig. 12. (a) Chip microphotograph, (b) PCB frame, and (c) test setup for 3.5 K measurements.

# V. MEASUREMENT

The chip was implemented using a standard 40-nm CMOS process. Fig. 12(a) shows a microphotograph. The chip and electrical components were mounted on a PCB. The PCB is fastened to a frame made of copper and brass to be fixed on the 4 K flange in the dilution refrigerator for thermal anchoring. The SMA connectors are used to feed power and microwave signals to the PCB [see Fig. 12(b)]. Fig. 12(c) shows the test setup. Measurements started when the refrigerator reached 3 K. The temperature was maximally elevated to 3.5 K by thermal dissipation during the measurements. The measurements include the effect of cable connections from

300 to 4 K followed by connections back to 300 K. The loss by cables and PCB traces is calibrated by testing the difference between the cases with and without the chip on PCB. The pulse modulator dissipates 8.3 mW by the analog part and 3.8 mW by the digital part while operating at 1.25 GHz. The power consumption by the LB- and the HB-PLL is 12.5 and 14.6 mW, respectively. The receiver chain dissipates 20 mW per channel.

### A. Pulse Modulator

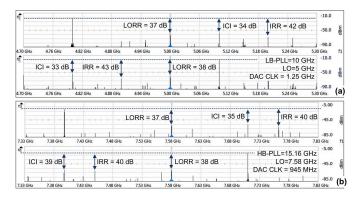

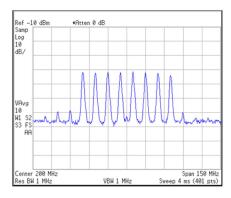

Fig. 13 shows measured results while two adjacentpulse modulators were operating simultaneously. The pulse

Fig. 13. Measured spectrums of the pulse modulator outputs at 3.5 K while two channels are being simultaneously driven by (a) LB-PLL and (b) HB-PLL.

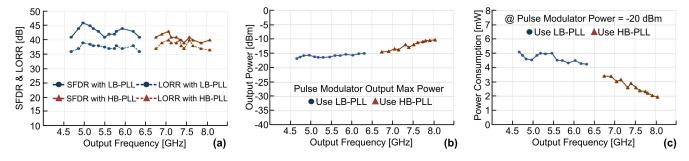

modulators independently control the frequency, phase, and pulsewidth. Fig. 13(a) is when the LB-PLL was used as the LO source. The LB-PLL was configured to generate 10 GHz. It is then divided by 2 for the quadrature LO at 5 GHz. The system clock for digital circuits is 1.25 GHz that is obtained by dividing the LO by 4. The two pulse modulators generate IF frequencies of +100 and -200 MHz, synthesizing 5.1 and 4.8 GHz, respectively, using the single LO at 5 GHz. The output shows an IRR of >42 dB and an LO rejection ratio (LORR) of >37 dB. Fig. 13(b) is when the HB-PLL was used as the LO source. The output of 15.16 GHz is divided by 2 for the quadrature LO at 7.58 GHz. A division by 8 provides the system clock of 0.945 GHz. The two pulse modulators synthesize +7.396 and 7.91 GHz with IF frequencies of -184 and +130 MHz, respectively. It shows an IRR of >40 dB and an LORR of >37 dB. The interchannel interference (ICI) needs to be also considered because its tone might be close to the frequency of qubit under control. The suppression of ICI was >33 dB in this work. Since the ICI is mainly caused by on-chip coupling from other output through the common ground line, it could be further reduced by the separation of the ground of the last-stage transformer of the pulse modulator. The bandwidth of the pulse modulator is 4.6–6.3 and 6.7–8.1 GHz when used with LB- and HB-PLL, respectively. The measured LORR and SFDR are summarized in Fig. 14(a).

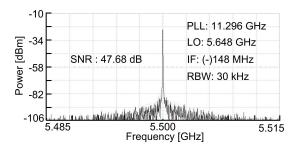

The maximum output power from the pulse modulator is over -17 dBm in the whole frequency range [see Fig. 14(b)]. The power dissipated by the proposed pulse modulator for the generation of the output power of -20 dBm is kept to be less than 5 mW [see Fig. 14(c)]. Fig. 15 shows the spectrum of the driver output measured with a resolution bandwidth (RBW) of 30 kHz. However, the noise floor in this figure has little meaning since it was limited by the minimum level given by residual noise in the equipment at room temperature. Nevertheless, the measurement shows that the power at the signal is enough to thermalize with attenuators for driving the qubits at 10 mK. In this implementation, the pulse modulator was designed to deliver sufficient power so that the test board could be verified both at 300 and 4 K. Since the driving power for qubit control should be in the level of -70 dBm(at Rabi frequency of 50 MHz) [38], the use of additional

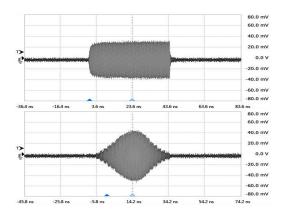

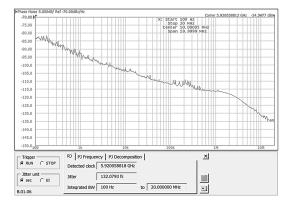

attenuator was assumed when the chip is used at 4 K. The power consumption by the pulse modulator might be further reduced if the chip is dedicated for use at 4 K. However, there should be extra efforts for more precise calibration to scale down the LO leakage as well. Fig. 16 shows measured output waveforms for the two cases of pulse shaping, rectangular, and raised cosine, respectively. Fig. 17 shows the phase noise of the synthesized output of the modulator. It is generated with 6.08-GHz LO from LB-PLL and -160 MHz IF. It includes all the noise from the LB-PLL, LO buffer, and the pulse modulator. The total integrated jitter from 100 Hz to 20 MHz is 132 fs<sub>rms</sub> that meets the specification for the 0.01% error rate.

# B. Phase-Locked Loop

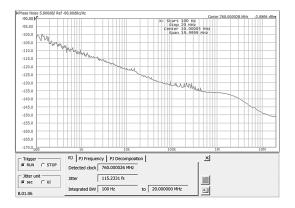

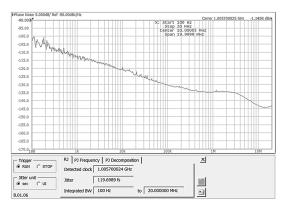

The two PLLs show similar noise performance. Fig. 18 shows the phase noise of the LB-PLL output at 12.16 GHz. The output is externally monitored through a division by 16. The integrated jitter is 115 fs<sub>rms</sub>, achieving a figure-of-merit (FoM),  $10 \times \log(\sigma(s)^2 P(mW))$ , of -247.8 dB. Fig. 19 is the phase noise of the HB-PLL output at 16.08 GHz. The integrated jitter is 119 fs<sub>rms</sub> with an FoM of -246.7 dB.

### C. Receiver

The measurement includes SMA connectors and traces on the PCB. Simulation results at room temperature are also added for comparison. Fig. 20 shows measured single-tone gain and NF of the whole receiver chain as the input signal frequency varies from 4.5–7.5 GHz. Since the equipment is typically terminated at 50  $\Omega$ , whereas the designed receiver chain has a 500- $\Omega$ -load impedance at the output, an external matching network for a 500-50-Ω transformation was implemented on PCB to measure the voltage gain of the receiver chain. The measured result was then converted on a 500- $\Omega$  domain to calculate the voltage conversion gain. Note that the output of the receiver chain is at the IF-band (100-500 MHz). Measuring a low-frequency output is not sensitive to the frequency dependence of the matching network. The gain and noise performances strongly rely on the intrinsic device characteristics at 3.5 K. The increased device gain and decreased loss of passive components at cryogenic temperature elevate the conversion gain by more than 5 dB in the band of interest [33], [35]. The Y-factor method was used for the measurement of NF. To get rid of the effect of fixtures (cables, connectors, etc.), identical routings from and to the chip on 3.5 K were also installed for the post de-embedding process. The measured minimum NF was 1.1 dB at 5.5 GHz. Fig. 21 shows linearity characteristics measured with 50-MHz spaced two tones. The increased IMD3 compared to the simulated value at room temperature can also be explained by the increased conversion gain. For the verification of the receiver chain in the FDM environment, eight tones from test equipment were applied as the input. Due to the limit in the frequency range of the available equipment, the eight tones are separated by 10 MHz instead of 50 MHz. Based on similar results from two-tone tests with 10 and 50 MHz spacing, this

Fig. 14. Measured performance of the pulse modulator at 3.5 K. (a) SFDR and LORR, (b) maximum output power, and (c) power consumption by analog block.

Fig. 15. Measured SNR of the pulse modulator at 3.5 K.

Fig. 16. Measured output waveforms of the pulse modulator at 3.5 K with different pulse shaping configurations.

Fig. 17. Measured phase noise of the pulse modulator output at 3.5 K.

result would be well matched to the case with 50-MHz spacing. Fig. 22 shows the spectrum at the receiver output when the average input power of eight tones is -57.5 dBm. The

Fig. 18. Measured phase noise of the LB-PLL output at 3.5 K.

Fig. 19. Measured phase noise of the HB-PLL output at 3.5 K.

input power was intentionally raised during this measurement so that the distortion tone below the residual noise floor of the spectrum analyzer could be elevated and clearly seen. In this case, the signal-to-distortion ratio at the band edge was 27 dB. This corresponds to the worst-case IIP3 of -44 dBm  $(-57.5 + 0.5 \times 27)$  for the case of band edge, still meeting the target (> -47 dBm).

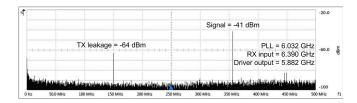

# D. TX-to-RX Leakage

There would be a leakage from the qubit driving path to the qubit readout path when their circuits operate simultaneously. Fig. 23 showsthe measured output of a receiver chain when the input signal is at 6.390 GHz, while a pulse modulator generates 5.882 GHz. The applied power at the

TABLE I

PERFORMANCE SUMMARY AND COMPARISON

|                             |         | This Work                                                | ISSCC'22 [24]                   | ISSCC'21 [16]                                                  | VLSI'21 [23]                   | ISSCC'20 [17]                   | JSSC'19 [8]                           |

|-----------------------------|---------|----------------------------------------------------------|---------------------------------|----------------------------------------------------------------|--------------------------------|---------------------------------|---------------------------------------|

| Operating<br>Temperature    |         | 3.5 K                                                    | 3 K                             | 4 K                                                            | 77 K                           | 3 K                             | 3 K                                   |

| Qubit Platform              |         | Transmons                                                | Transmons                       | Spin Qubits                                                    | Transmons                      | Spin Qubits                     | Transmons                             |

| Target fidelity             |         | 99.99% (expected)                                        | N/A                             | 99.99%                                                         | N/A                            | 99.99%                          | 99.99%                                |

| Power                       | Analog  | Modulator: 8.3 mW <sup>a</sup><br>Readout: 20 mW/channel | Modulator: 11.4 mW <sup>a</sup> | Modulator: 40.1 mW <sup>a</sup><br>Readout: 10.6 mW/qubit      | Modulator. 5.5 mW <sup>a</sup> | Modulator: 28.5 mW <sup>a</sup> | Modulator:<br>2 mW/qubit <sup>a</sup> |

|                             | Digital | 3.8 mW @1.25 GHz                                         | 11.6 mW @1 GHz                  | 10-140 mW <sup>b</sup> @1.6 GHz                                | 2.6 mW @1 GHz                  | 330 mW @1 GHz                   | N/A                                   |

| Freq. Range                 |         | 4.6-8.1 GHz @>-17 dBm                                    | 4.5-5.5 GHz @>-19 dBm           | 11-17 GHz @ >-10 dBm                                           | 2-7 GHz @>-28 dBm              | 2-20 GHz @ >-45 dBm             | 4-8 GHz                               |

| Multiplexing                |         | Driver: 1 qubit<br>Read: 8 qubits <sup>d</sup>           | Driver: 1 qubit                 | Drive: 16 qubits <sup>c,d</sup><br>Read: 6 qubits <sup>d</sup> | Drive: 1 qubit                 | Drive: 32 qubits c,d            | Driver: 1 qubit                       |

| LO Generation               |         | Yes, PLL x 2                                             | No, Off-Chip                    | No, Off-Chip                                                   | No, Off-Chip                   | No, Off-Chip                    | No, Off-Chip                          |

| Sampling Rate               |         | Up to 1.5 GS/s                                           | Up to 1 GS/s                    | Up to 2.5 GS/s                                                 | Up to 2 GS/s                   | Up to 1 GS/s                    | Up to 1 GS/s                          |

| DRAG pulse                  |         | No                                                       | YES                             | YES                                                            | No                             | YES                             | No                                    |

| Driver<br>Integrated Jitter |         | < 140 fs                                                 | N/A                             | N/A                                                            | N/A                            | N/A                             | N/A                                   |

| Chip Area                   |         | 5.3 mm <sup>2</sup>                                      | 1.6 mm <sup>2</sup> /channel    | 16 mm <sup>2</sup>                                             | 0.39 mm <sup>2</sup> /channel  | 4 mm <sup>2</sup> /channel      | 1.6 mm <sup>2</sup>                   |

| Technology                  |         | 40 nm Bulk CMOS                                          | 14 nm FinFET                    | 22 nm FinFET CMOS                                              | 40 nm Bulk CMOS                | 22 nm FinFET CMOS               | 22 nm Bulk CMOS                       |

| Receiver           | This Work               | ISSCC'21 [39]      | ISSCC'21 [40]    |  |

|--------------------|-------------------------|--------------------|------------------|--|

| Bandwidth          | 5-7.25 GHz <sup>e</sup> | 5–6.5 GHz          | 6-8 GHz          |  |

| Conversion Gain    | Max. 47 dB (V/V)        | Max. 70 dB (P/P)   | Max. 58 dB (P/P) |  |

| Noise Figure f     | 1.1 dB                  | 0.55 dB            | 0.6 dB           |  |

| P1dB <sub>IN</sub> | >-49 dBm                | >-85 dBm           | -58.4 dBm        |  |

| IIP3               | >-35 dBm                | >-72 dBm           | -50.8 dBm        |  |

| LO Generation      | Yes, PLL                | Yes, PLL           | No, External     |  |

| Power              | 20 mW/channel           | 75 mW <sup>g</sup> | 66 mW            |  |

| Technology         | 40 nm Bulk CMOS         | 40 nm CMOS         | 40 nm Bulk CMOS  |  |

| PLL               | This Work             | CICC'21 [41]         |  |

|-------------------|-----------------------|----------------------|--|

| Architecture      | DPLL                  | DAPLL <sup>h</sup>   |  |

| Area              | 0.068 mm <sup>2</sup> | 0.14 mm <sup>2</sup> |  |

| Power             | 12.5 mW               | 2.7 mW               |  |

| Supply Voltage    | 1.05 V                | 1.1 V                |  |

| Frequency Range   | 9-13 GHz <sup>i</sup> | 9.4-11.6 GHz         |  |

| Integ. RMS Jitter | 115 fs [100Hz-20MHz]  | 44.8 fs [10k-30MHz]  |  |

| FoM               | -247.8 dB             | -262.7 dB            |  |

| Technology        | 40 nm Bulk CMOS       | 40 nm CMOS           |  |

a: Power/qubit under active control b: Depending on activity c: TDM d: FDM e: IF BW = 400MHz e: Min. value f: LNA+Mixer+IF g: LB-PLL i: DA-baised charge-sampling PLL

Fig. 20. Measured conversion gain of the designed receiver at 3.5 K.

receiver input and the generated pulse modulator output were -80 and -39 dBm, respectively. The receiver LO for the down-conversion was 6.032 GHz. The two tones at 150 MHz (-64 dBm) and 358 MHz -41 dBm) correspond to the unwanted TX-to-RX leakage and desired input, respectively, showing a 25-dB suppression of the TX output during a 39-dB amplification of the RX input. Since the signal level (-41 dBm) is 23 dB higher than the leakage level (-64 dBm), the TX-to-RX leakage barely affects the signal readout. The modulator output of -39 dBm is still enough level to drive qubits with a subsequent attenuation. The small separation of 150 MHz between the TX and RX bands can be regarded

Fig. 21. Measured P1dBin and IIP3 of the designed receiver at 3.5 K.

to be the worst case. When the same testwas conducted with a 1500-MHz separation, the TX-to-RX leakage was further reduced from -64 to -86 dBm.

## E. Comparison

Table I compares the performance with the previously reported works. This work proposes a quantum controller SoC architecture synchronized with a single time reference by generating multiple LOs using on-chip PLLs. The chip is verified at 3.5 K, while two adjacent driving pulse modulators were operating simultaneously.

To claim fidelity, the term "expected fidelity" was used in this work considering that the experiments with real qubits

Fig. 22. Measured receiver output with eight-tone input at 3.5 K.

Fig. 23. Measured TX-to-RX leakage at 3.5 K.

were not conducted. In addition, its use is limited for the pulse modulator since there has been no clear specifications with supporting measurements for the fidelity of the readout under the FDM environment. The 99.99% fidelity is based on the spectral purity of the pulse modulator output for driving a single qubit. A high-quality factor  $(>10^7)$  of a superconducting qubit indicates that the band of interest is narrow. The tone at  $\omega_{12}$ , if it exists, would be the major factor that degrades the gate fidelity. Therefore, the required SFDR of each pulse modulator for single qubit is that the power at  $\omega_{12}$  should be lower than 40 dB compared to the power at  $\omega_{01}$ , while keeping a good SNR and a low phase error for the 99.99% fidelity. Though the ICI and LORR in this work exceed allowable levels, they can be avoided by the flexibility in the selection of LOs with the proposed architecture using multiple PLLs.

# VI. CONCLUSION

The two major challenges in the design of a cryo-CMOS quantum controller SoC for superconducting qubits are 1) lowpower implementation of the pulse modulator per qubit and 2) suppression of unwanted tones at  $\omega_{01}$  and  $\omega_{12}$ . There have been two approaches to addressing those challenges. The one is to assign a dedicated LO per qubit for driving pulse modulation. Since the LO frequency itself is the qubit frequency  $(\omega_{01})$ , this approach provides benefits in spectrum management by minimizing the chances of frequency mixing with different tones. However, the LO should not be turned off because the phase of the driving pulse for a qubit should be kept to be coherent throughout the quantum algorithm. Therefore, the power consumption from the LOs for individual qubits would eventually exceed the cooling power budget as the number of qubits exponentially grows. In addition, since the LO frequency is tuned to  $\omega_{01}$ , a small leak of the LO power can even result in an unwanted state transition. Thus, the LO must be stringently isolated from the qubit when it is not driven. The other approach is the generation of frequencies with DDS through SSB mixing using a common LO. Since the DDS supports frequency generation on demand, the pulse modulator can be turned off when the qubit is not used in a quantum gate. Though this approach can provide effectiveness in power management, the use of common LO can bring about a large synchronized noise at LO frequency.

This work proposes an approach with PLLs for the internal generation of multiple LOs. anaging different LOs with multiple PLLs provides an effective way of suppressing the LO leakage by uniformly distributing the LO power in a wide frequency range. It not only gives the flexibility in optimal profiling of spectrums for high gate fidelity, but also enables the scalability in building hardware for a large-scale quantum controller. The proposed architecture including two PLLs to generate two different LOs for 4.5–6 and 6.5–8 GHz was implemented in 40-nm CMOS. The chip is verified with full functionalities at 3.5 K, while two adjacent driving pulse modulators were operating simultaneously.

### REFERENCES

- [1] F. Arute *et al.*, "Quantum supremacy using a programmable superconducting processor," *Nature*, vol. 574, no. 7779, pp. 505–510, 2019.

- [2] Y. Wu et al., "Strong quantum computational advantage using a superconducting quantum processor," Phys. Rev. Rett., vol. 127, Oct. 2021, Art. no. 180501.

- [3] J. Clarke and F. K. Wilhelm, "Superconducting quantum bits," *Nature*, vol. 453, pp. 1031–1042, Jun. 2008.

- [4] M. H. Devoret and R. J. Schoelkopf, "Superconducting circuits for quantum information: An outlook," *Science*, vol. 339, no. 6124, pp. 1169–1174, Mar. 2013.

- [5] J. M. Gambetta, J. M. Chow, and M. Steffen, "Building logical qubits in a superconducting quantum computing system," NPJ Quantum Inf., vol. 3, no. 1, pp. 1–7, Dec. 2017.

- [6] J. Koch et al., "Charge-insensitive qubit design derived from the Cooper pair box," Phys. Rev. A, Gen. Phys., vol. 76, no. 4, Oct. 2007, Art. no. 042319.

- [7] P. Krantz, M. Kjaergaard, F. Yan, T. P. Orlando, S. Gustavsson, and W. D. Oliver, "A quantum engineer's guide to superconducting qubits," *Appl. Phys. Rev.*, vol. 6, no. 2, Jun. 2019, Art. no. 021318.

- [8] J. C. Bardin et al., "Design and characterization of a 28-nm bulk-CMOS cryogenic quantum controller dissipating less than 2 mW at 3 K," IEEE J. Solid-State Circuits, vol. 54, no. 11, pp. 3043–3060, Nov. 2019.

- [9] J. P. G. van Dijk, E. Charbon, and F. Sebastiano, "The electronic interface for quantum processors," *Microprocessors Microsyst.*, vol. 66, pp. 90–101, Apr. 2019.

- [10] J. C. Bardin, D. Sank, O. Naaman, and E. Jeffrey, "Quantum computing: An introduction for microwave engineers," *IEEE Microw. Mag.*, vol. 21, no. 8, pp. 24–44, Aug. 2020.

- [11] A. Blais, R.-S. Huang, A. Wallraff, S. M. Girvin, and R. J. Schoelkopf, "Cavity quantum electrodynamics for superconducting electrical circuits: An architecture for quantum computation," *Phys. Rev. A, Gen. Phys.*, vol. 69, no. 6, Jun. 2004, Art. no. 062320.

- [12] A. Opremcak et al., "Measurement of a superconducting qubit with a microwave photon counter," Science, vol. 361, no. 6408, pp. 1239–1242, 2018.

- [13] J. M. Hornibrook et al., "Cryogenic control architecture for large-scale quantum computing," Phys. Rev. A, Gen. Phys., vol. 3, no. 2, Feb. 2015, Art. no. 024010.

- [14] J. Heinsoo et al., "Rapid high-fidelity multiplexed readout of superconducting qubits," Phys. Rev. A, Gen. Phys., vol. 10, no. 3, Sep. 2018, Art. no. 034040.

- [15] B. Patra et al., "Cryo-CMOS circuits and systems for quantum computing applications," *IEEE J. Solid-State Circuits*, vol. 53, no. 1, pp. 309–321, Jan. 2018.

- [16] J.-S. Park et al., "13.1 A fully integrated cryo-CMOS SoC for qubit control in quantum computers capable of state manipulation, readout and high-speed gate pulsing of spin qubits in Intel 22nm FFL FinFET technology," in *IEEE Int. Solid-State Circuits Conf. (ISSCC) Dig. Tech. Papers*, Feb. 2021, pp. 208–210.

- [17] B. Patra et al., "19.1 A scalable cryo-CMOS 2-to-20GHz digitally intensive controller for 4×32 frequency multiplexed spin qubits/transmons in 22nm FinFET technology for quantum computers," in *IEEE Int. Solid-State Circuits Conf. (ISSCC) Dig. Tech. Papers*, Feb. 2020, pp. 304–306.

- [18] J. Park et al., "A fully integrated cryo-CMOS SoC for state manipulation, readout, and high-speed gate pulsing of spin qubits," *IEEE J. Solid-State Circuits*, vol. 56, no. 11, pp. 3289–3306, Nov. 2021.

- [19] J. P. G. Van Dijk et al., "A scalable cryo-CMOS controller for the wideband frequency-multiplexed control of spin qubits and transmons," *IEEE J. Solid-State Circuits*, vol. 55, no. 11, pp. 2930–2946, Nov. 2020.

- [20] O. Naaman, D. G. Ferguson, A. Marakov, M. Khalil, W. F. Koehl, and R. J. Epstein, "High saturation power Josephson parametric amplifier with GHz bandwidth," in *IEEE MTT-S Int. Microw. Symp. Dig.*, Jun. 2019, pp. 259–262.

- [21] D. Sank et al., "Fast scalable state measurement with superconducting qubits," 2014, arXiv:1401.0257.

- [22] J. C. Bardin et al., "29.1 A 28nm bulk-CMOS 4-to-8GHz İ2 mW cryogenic pulse modulator for scalable quantum computing," in IEEE Int. Solid-State Circuits Conf. (ISSCC) Dig. Tech. Papers, Feb. 2019, pp. 408–456.

- [23] K. Kang *et al.*, "A 5.5 mW/channel 2-to-7 GHz frequency synthesizable qubit-controlling cryogenic pulse modulator for scalable quantum computers," in *Proc. Symp. VLSI Circuits*, Jun. 2021, pp. 1–2.

- [24] D. J. Frank et al., "A cryo-CMOS low-power semi-autonomous qubit state controller in 14nm FinFET technology," in *IEEE Int. Solid-State* Circuits Conf. (ISSCC) Dig. Tech. Papers, Feb. 2022, pp. 360–362.

- [25] Y. Peng, A. Ruffino, T.-Y. Yang, J. Michniewicz, M. F. Gonzalez-Zalba, and E. Charbon, "A cryo-CMOS wideband quadrature receiver with frequency synthesizer for scalable multiplexed readout of silicon spin qubits," *IEEE J. Solid-State Circuits*, vol. 57, no. 8, pp. 2374–2389, Aug. 2022.

- [26] K. Kang et al., "A cryo-CMOS controller IC with fully integrated frequency generators for superconducting qubits," in IEEE Int. Solid-State Circuits Conf. (ISSCC) Dig. Tech. Papers, Feb. 2022, pp. 362–364.

- [27] R. Barends et al., "Superconducting quantum circuits at the surface code threshold for fault tolerance," *Nature*, vol. 508, no. 7497, pp. 500–503, 2014.

- [28] J. P. G. van Dijk, B. Patra, S. Pellerano, E. Charbon, F. Sebastiano, and M. Babaie, "Designing a DDS-based SoC for high-fidelity multi-qubit control," *IEEE Trans. Circuits Syst. I, Reg. Papers*, vol. 67, no. 12, pp. 5380–5393, Dec. 2020.

- [29] Y. Peng, A. Ruffino, and E. Charbon, "A cryogenic broadband sub-1-dB NF CMOS low noise amplifier for quantum applications," *IEEE J. Solid-State Circuits*, vol. 56, no. 7, pp. 2040–2053, Jul. 2021.

- [30] J. C. Bardin, D. Sank, O. Naaman, and E. Jeffrey, "Quantum computing: An introduction for microwave engineers," *IEEE Microw. Mag.*, vol. 21, no. 8, pp. 24–44, Aug. 2020.

- [31] S. Hussain and Y. Louet, "Peak to average power ratio analysis of multicarrier and multi-standard signals in software radio context," in *Proc.* 3rd Int. Conf. Inf. Commun. Technol., From Theory Appl., Apr. 2008, pp. 1–5.

- [32] N. B. Carvalho and J. C. Pedro, "Multi-tone intermodulation distortion performance of 3rd order microwave circuits," in *IEEE MTT-S Int. Microw. Symp. Dig.*, Jun. 1999, pp. 763–766.

- [33] R. M. Incandela, L. Song, H. Homulle, E. Charbon, A. Vladimirescu, and F. Sebastiano, "Characterization and compact modeling of nanometer CMOS transistors at deep-cryogenic temperatures," *IEEE J. Electron Devices Soc.*, vol. 6, pp. 996–1006, 2018.

- [34] P. A. T Hart, M. Babaie, E. Charbon, A. Vladimirescu, and F. Sebastiano, "Characterization and modeling of mismatch in cryo-CMOS," *IEEE J. Electron Devices Soc.*, vol. 8, pp. 263–273, 2020.

- [35] B. Patra, M. Mehrpoo, A. Ruffino, F. Sebastiano, E. Charbon, and M. Babaie, "Characterization and analysis of on-chip microwave passive components at cryogenic temperatures," *IEEE J. Electron Devices Soc.*, vol. 8, pp. 448–456, 2020.

- [36] B. Razavi, RF Microelectronics, 2nd ed. Upper Saddle River, NJ, USA: Prentice-Hall, 2012.

- [37] J. S. Park, S. Kousai, and H. Wang, "A fully differential ultra-compact broadband transformer based quadrature generation scheme," in *Proc. IEEE Custom Integr. Circuits Conf.*, Sep. 2013, pp. 1–4.

- [38] J. C. Bardin, D. H. Slichter, and D. J. Reilly, "Microwaves in quantum computing," *IEEE J. Microw.*, vol. 1, no. 1, pp. 403–427, Jan. 2021.

- [39] A. Ruffino, Y. Peng, T.-Y. Yang, J. Michniewicz, M. F. Gonzalez-Zalba, and E. Charbon, "13.2 A fully-integrated 40-nm 5–6.5 GHz cryo-CMOS system-on-chip with I/Q receiver and frequency synthesizer for scalable multiplexed readout of quantum dots," in *IEEE Int. Solid-State Circuits Conf. (ISSCC) Dig. Tech. Papers*, Feb. 2021, pp. 210–212.

- [40] B. Prabowo et al., "13.3 A 6-to-8GHz 0.17 mW/qubit cryo-CMOS receiver for multiple spin qubit readout in 40nm CMOS technology," in *IEEE Int. Solid-State Circuits Conf. (ISSCC) Dig. Tech. Papers*, Feb. 2021, pp. 212–214.

- [41] J. Gong, E. Charbon, F. Sebastiano, and M. Babaie, "A 2.7 mW 45fs<sub>rms</sub>-jitter cryogenic dynamic-amplifier-based PLL for quantum computing applications," in *Proc. IEEE Custom Integr. Circuits Conf. (CICC)*, Apr. 2021, pp. 1–2.

**Kiseo Kang** (Graduate Student Member, IEEE) received the B.S. and M.S. degrees from the Pohang University of Science and Technology (POSTECH), Pohang, South Korea, in 2018 and 2020, respectively, where he is currently pursuing the Ph.D. degree all in electronic and electrical engineering.

His research interests include mixed-signal circuits and cryo-CMOS circuits for quantum computing.

**Donggyu Minn** (Graduate Student Member, IEEE) received the B.S. and M.S. degrees from the Pohang University of Science and Technology (POSTECH), Pohang, South Korea, in 2015 and 2017, respectively, where he is currently pursuing the Ph.D. degree all in electronic and electrical engineering.

Since 2017, he has been with Samsung Electronics Company Ltd., Suwon, South Korea, as an mm-Wave RFIC Design Engineer. His research interest includes cryo-CMOS IC for quantum computers.

Seongun Bae received the B.S. degree in electronic and electrical engineering from Pohang University of Science and Technology (POSTECH), Pohang, South Korea, in 2016, where he is currently pursuing the Ph.D. degree all in electronic and electrical engineering.

His research interests include analog and digital frequency synthesizers.

**Jaeho Lee** received the B.S. and M.S. degrees from the Pohang University of Science and Technology (POSTECH), Pohang, South Korea, in 2019 and 2021, respectively, where he is currently pursuing the Ph.D. degree all in electronic and electrical engineering.

His research interests include analog-to-digital converters and cryo-CMOS circuits for quantum computing.

Seokhyeong Kang (Member, IEEE) received the B.S. and M.S. degrees in electrical engineering from Pohang University of Science and Technology, Pohang, South Korea, in 1999 and 2001, respectively, and the Ph.D. degree from the VLSI CAD Laboratory, University of California at San Diego, San Diego, CA, USA, in 2013.

He was with the System-on-Chip (SoC) Development Team, Samsung Electronics, Suwon, South Korea, from 2001 to 2008, and he was with the Design Automation Team, Qualcomm

Technologies, San Diego, from 2013 to 2014. He was a Professor with the Department of Electrical Engineering, Ulsan National Institute of Science and Technology, Ulsan, South Korea, from 2014 to 2018. He has been a Professor with the Department of Electrical Engineering, Pohang University of Science and Technology, since 2018. His research interests include algorithms and methodologies for the computer-aided design of VLSI circuits.

**Ho-Jin Song** (Senior Member, IEEE) received the M.S. and Ph.D. degrees in electronics engineering from Gwangju Institute of Science and Technology (GIST), Gwangju, South Korea, in 2001 and 2005, respectively.

From 2005 to 2006, he was with the Center for Hybrid Optical Access Networks (CHOAN), GIST, as a Research Professor, and was engaged in research on radio-over-fiber technologies cooperating with the Local Multipoint Distribution Service (LMDS) wireless systems operating at 26 and 28 GHz.

He joined NTT Microsystem Integration Laboratories, Nippon Telegraph and Telephone Corporation (NTT), Atsugi, Kanagawa, Japan, in 2006, he has been working on the development of millimeter-wave and sub-terahertz wave systems for communications, sensing, imaging, radar, and measurement applications operating at above 100 GHz utilizing both high-speed electronic and photonic technologies. In 2015, he was named a Distinguished Research Scientist of NTT Laboratories. Since 2016, he has been an Associate Professor of electrical engineering with Pohang University of Science and Technology (POSTECH), Pohang, Gyeongbuk, South Korea. He has more than 100 peerreviewed international journal and conference publications in mm/THz-wave ICs, microwave photonics, and system demonstrations. He also holds more than 20 patents filed in Japan and Korea. His research area covers millimeter and terahertz ICs based on InP, SiGe, and Si-CMOS electronics, their packaging technologies, novel terahertz metamaterial components, and photonic integrated circuits with silicon photonic technologies for wireless communications, sensing, radar, and bioimaging applications. In addition, he is also interested in wireless front-haul network systems and millimeterwave RF front-ends for the 5G massive MIMO systems.

Prof. Song was awarded the Best Thesis Award from the Gwangju Institute of Science and Technology in 2005, the Young Scientist Award of the Spectroscopical Society of Japan in 2010, the IEEE Microwave Theory and Techniques Society (MTT-S) Tatsuo Itoh Prize in 2014, and the Best Industrial Paper Award at IEEE Microwave Theory and Techniques Society International Microwave Symposium (MTTS-IMS)2016 in 2016.

From 2012 to 2014, he was a Post-Doctoral Researcher with ETH Zurich, Zürich, Switzerland. From 2014 to 2018, he was a Post-Doctoral Fellow with the Institute for Quantum Optics and Quantum Information (IQOQI), University of Innsbruck, Innsbruck, Austria. From 2018 to 2020, he was a Research Fellow with CEA Saclay, Gif-sur-Yvette, France. Since 2020, he has been an Assistant Pro-

fessor with the Department of Electrical Engineering, Pohang University of Science (POSTECH), Pohang, South Korea. His research interests include quantum optics and quantum information.

Dr. Lee was a recipient of the Lise Meitner Fellowship of the Austrian Academy of Science in 2015.

Jae-Yoon Sim (Senior Member, IEEE) received the B.S., M.S., and Ph.D. degrees in electronic and electrical engineering from the Pohang University of Science and Technology (POSTECH), Pohang, South Korea, in 1993, 1995, and 1999, respectively.

From 1999 to 2005, he was a Senior Engineer with Samsung Electronics, Suwon, South Korea. From 2003 to 2005, he was a Post-Doctoral Researcher with the University of Southern California, Los Angeles, CA, USA. From 2011 to 2012, he was a Visiting Scholar with the University of

Michigan, Ann Arbor, MI, USA. In 2005, he joined POSTECH, where he is currently a Professor. Since 2019, he has been the Director with the Scalable Quantum Computer Technology Platform Center, Korea, nominated by the Korea Ministry of Science and Information and Communication Technology (ICT). His research interests include sensor interface circuits, high-speed serial/parallel links, phase-locked loops, data converters, security, and quantum computing.

Dr. Sim was a co-recipient of the Takuo Sugano Award from the IEEE International Solid-State Circuits Conference (ISSCC) in 2001 and a recipient of the Special Author-Recognition Award from ISSCC in 2013. In 2020, he received the Scientist of the Month Award sponsored by the Ministry of Science and ICT of Korea. He has been an IEEE Distinguished Lecturer from 2018 to 2019. He has served on the Technical Program Committees for the ISSCC, the IEEE Symposium on VLSI Circuits, and the IEEE Asian Solid State Circuits Conference.