# A Time-Mode-Modulation Digital Quadrature Power Amplifier Based on 1-bit Delta–Sigma Modulator and Hybrid FIR Filter

Yuncheng Zhang<sup>10</sup>, Member, IEEE, Zheng Sun<sup>10</sup>, Member, IEEE, Bangan Liu<sup>10</sup>, Member, IEEE,

Junjun Qiu<sup>®</sup>, Member, IEEE, Dingxin Xu<sup>®</sup>, Graduate Student Member, IEEE,

Yi Zhang<sup>10</sup>, Graduate Student Member, IEEE, Xi Fu<sup>10</sup>, Member, IEEE, Dongwon You, Member, IEEE,

Hongye Huang<sup>10</sup>, Graduate Student Member, IEEE, Waleed Madany<sup>10</sup>, Graduate Student Member, IEEE,

Ashbir Aviat Fadila<sup>10</sup>, Graduate Student Member, IEEE, Zezheng Liu<sup>10</sup>, Graduate Student Member, IEEE,

Wenqian Wang, Graduate Student Member, IEEE, Yuang Xiong<sup>D</sup>, Graduate Student Member, IEEE,

Atsushi Shirane, Member, IEEE, and Kenichi Okada<sup>D</sup>, Fellow, IEEE

Abstract—This article proposes a time-mode-modulation (TMM) digital quadrature power amplifier (PA), which can realize high power efficiency at power back-off (PBO) by applying the 1-bit delta-sigma modulator (DSM) and hybrid finite impulse response (FIR) filter. The 1-bit DSM and digital mixer encode the multi-bit baseband I/Q input signal into a 1-bit signal for on/off controlling the 1-bit PA to realize the TMM operation. Capacitor arrays are not required in the proposed PA, and redundant power dissipation on charging the capacitor array in conventional switched capacitor PAs (SCPAs) is avoided. Furthermore, a hybrid FIR filter comprising a two-tap digital FIR filter and a two-tap transformer (XFMR) combined semi-digital FIR filter suppresses the DSM quantization noise (QN) to avoid efficiency degradation. The XFMR combined semi-digital FIR filter is insensitive to mismatches, which maintains the high linearity of the 1-bit TMM PA. The proposed TMM PA is fabricated in 65-nm CMOS. Without digital pre-distortion (DPD), it achieves 26.4% power-added efficiency (PAE) with 40-MSymbol/s 64-quadrature amplitude modulation (QAM) signal and 20.9% PAE with 20-MSymbol/s 256-QAM signal at 2.6 GHz.

*Index Terms*—Delta-sigma modulator (DSM), finite impulse response (FIR) filter, power amplifier (PA), quadrature, transformer.

# I. INTRODUCTION

**S**PECTRAL efficiency is crucial in modern wireless communication standards to satisfy the ever-increasing demand for higher data throughput with highly congested spectrum resources. Information-dense higher order quadrature amplitude modulation (QAM), such as 256 QAM [1], is widely

Manuscript received 26 August 2023; revised 21 November 2023; accepted 23 December 2023. This article was approved by Associate Editor Mototsugu Hamada. This work was supported in part by the National Institute of Information and Communications Technology (NICT) under Grant JPJ012368C00801, in part by the Ministry of Internal Affairs and Communications (MIC) under Grant JPJ000254, in part by the Support for Tokyo Tech Advanced Researchers (STAR), and in part by the VLSI Design and Education Center (VDEC) in collaboration with Cadence Design Systems Inc. and Mentor Graphics Inc. (*Corresponding author: Yuncheng Zhang.*)

The authors are with the Department of Electrical and Electronic Engineering, Tokyo Institute of Technology, Tokyo 152-8550, Japan (e-mail: zhangyc23@ssc.pe.titech.ac.jp).

Color versions of one or more figures in this article are available at https://doi.org/10.1109/JSSC.2023.3349002.

Digital Object Identifier 10.1109/JSSC.2023.3349002

used to improve spectrum efficiency. However, high-order modulation schemes often produce an output signal with a high peak-to-average power ratio (PAPR). This causes the power amplifier (PA) to work at power back-off (PBO). Nevertheless, the power efficiency of PA at the PBO region is usually low. Therefore, as the most power-hungry building block in a wireless transceiver, the PBO power efficiency of the PA must be improved to enhance the system efficiency and extend the battery lifetime of handheld devices. Moreover, the linearity of the PA is also important, since a very low error vector magnitude (EVM) is required to demodulate the high-order QAM signal.

1

With the scaling down of the CMOS process and the decreasing breakdown voltage, the linear PA will work in a smaller quiescent current, and the efficiency is limited. Moreover, the linearity also degrades with the limited voltage headroom. On the contrary, digital switching type PAs, such as Class-D and Class-E, can benefit from the scaling down of CMOS and achieve higher switching speed and lower loss. Therefore, digital PAs are widely used to implement RF transmitters (TXs) [2], [3], [4], [5], [6], [7], [8], [9], [10], [11], [12].

Several TX architectures adopting digital PAs are investigated, such as envelope elimination and restoration (EER) [13], polar modulation [8], [9], [10], [11], [12], [14], out phasing [15], and RF pulsewidth modulation [16]. However, converting the input signal from the Cartesian domain (I and Q inputs) to a polar coordinate system (amplitude and phase) is required in these structures. Such conversion substantially extends the bandwidth of the output amplitude and phase signal, and a wide-bandwidth phase modulator is inevitable in digital polar TXs, which introduces additional non-linearity and power consumption. On the other hand, digital quadrature TXs [6], [7], [17], [18] do not suffer from the bandwidth extension and offer a simple structure without a complex phase modulator, which is a good candidate for achieving high system efficiency.

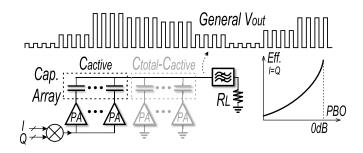

Nevertheless, the widely used switched capacitor PA (SCPA) shows degraded PBO efficiency. A capacitor-based voltage divider (Fig. 1) in SCPA precisely controls the output

© 2024 The Authors. This work is licensed under a Creative Commons Attribution 4.0 License. For more information, see https://creativecommons.org/licenses/by/4.0/

Fig. 1. Block diagram of a conventional SCPA.

Fig. 2. Block diagram of a conventional VMD SCPA.

amplitude by changing the ratio of the active and total capacitance. However, redundant charge/discharge of the capacitor array introduces power loss, which causes rapid efficiency degradation at PBO [19].

Several techniques have been proposed to enhance the PBO efficiency of SCPA. In Class-G SCPAs [20], an additional supply rail is added to create an efficiency peak at 6-dB PBO, at the cost of additional power management hardware. In sub-harmonic switching (SHS) SCPAs [21], [22], PA switches at one-third of the carrier frequency to add an efficiency peak of 9.5-dB PBO. However, SHS SCPA requires harmonic traps in the matching networks, which suffer from area penalty.

Voltage-mode Doherty (VMD) [23], [24] is another method to improve the PBO efficiency of SCPA. As shown in Fig. 2, VMD SCPA comprises two identical SCPAs, the main PA and the auxiliary PA. At 0-dB PBO, both PAs work at their peak outputs. At 6-dB PBO, the auxiliary PA is turned off, while the main PA works at its peak output, generating an output voltage equal to half of the peak output voltage. Therefore, the capacitor array is not required at 6-dB PBO, and the efficiency at 6-dB PBO is equal to the peak efficiency. VMD PA can only achieve operation without capacitor array at 0/6-dB PBO. Switched capacitor operation is still required at other PBO levels to cover the full amplitude range. Therefore, efficiency at other PBO levels is low due to the capacitor array loss.

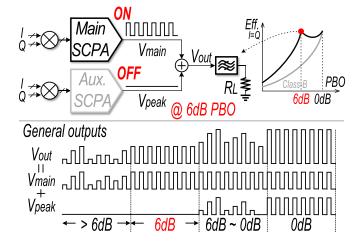

Unlike the VMD PA, which implements on/off control of the PA in the voltage domain, in this article, we propose a time-mode-modulation (TMM) PA that realizes the on/off

Fig. 3. (a) Block diagram of the proposed TMM PA with 1-bit output. (b) Conceptual non-linearity comparison with conventional VMD PA.

PA control in the time domain [25], as shown in Fig. 3(a). At 6-dB PBO, the TMM PA is turned on for one carrier cycle and turned off for the next cycle. In this way, the average fundamental output voltage will be half the peak output voltage, which is 6-dB PBO. Since TMM PA does not need a capacitor array at 6-dB PBO, there is no capacitor array loss, and its efficiency at 6-dB PBO is expected to be the peak efficiency. To extend the TMM operation to PBO levels other than 0/6 dB without using a switched capacitor array, 1-bit delta-sigma modulators (DSMs) and digital signal processing (DSP) are utilized. The DSMs upsample the multi-bit I/Qinputs and convert them to 1 bit. Next, the DSP and the mixer encode the DSM outputs into a 1-bit PA input signal. The 1-bit PA input signal controls the on/off of the 1-bit digital PA for TMM operation. As a result, the amplitude information is encoded into the density of the output pulses. In the general output voltage depicted in Fig. 3(a), more pulses represent higher output power, and fewer pulses represent lower output power. Therefore, the capacitor array is completely eliminated to realize modulation, and the efficiency is expected to be the peak efficiency at any PBO levels (suppose the ideal PA cell and capacitor array loss is the only source of power loss).

Moreover, VMD SCPA suffers from non-linearities caused by the mismatches between the main and auxiliary SCPAs. For example, the gain and delay mismatches between the two sub-PAs introduce AM–AM and AM–PM distortion, respectively [Fig. 3(b)]. In quadrature digital PAs, extremely complex 2-D digital pre-distortion (DPD) must be applied to linearize the PA [26], [27], which introduces additional power consumption and hardware overhead at the system level. On the contrary, in the proposed TMM PA, only one PA cell is used, and the output is a two-level signal. Therefore, the proposed TMM is intrinsically linear, and power-consuming DPD can be avoided.

This article is organized as follows. Section II introduces the operation principle of prior arts. Section III introduces the proposed TMM PA with a hybrid finite impulse response (FIR) filter. Section IV analyzes circuit non-ideal factors. Section V introduces the system implementation. Measurement results are provided in Section VI, and Section VII concludes this article.

## **II. OPERATION PRINCIPLE OF PRIOR ARTS**

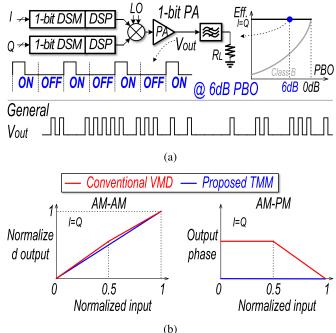

The most important step in realizing the TMM is to encode the multi-bit I and Q inputs into 1 bit. Several DSM-based TX architectures have been investigated. In the digital TX based on 1-bit bandpass (BP) DSM [29], direct conversion is realized in the digital domain. The local oscillator (LO) signal upconverts the baseband I/Q signal to yield the digital modulated signal at the carrier frequency. The 1-bit BP-DSM converts the modulated signal into 1 bit, and the noise shaping suppresses the quantization noise (QN) in the signal band. A digital clock at least twice the carrier frequency is required to ensure the carrier is within the Nyquist bandwidth. Therefore, the digital logic and the 1-bit digital PA are switching at a high-speed clock, which is extremely power-consuming. Nevertheless, modern wireless communications are conducted at GHz carriers. Therefore, multi-GHz DSP is necessary to implement this structure, which is difficult using the CMOS process. For example, to support communication at 3.5-GHz carrier, Maehata et al. [30] adopt an extremely high clock frequency of 10 GHz.

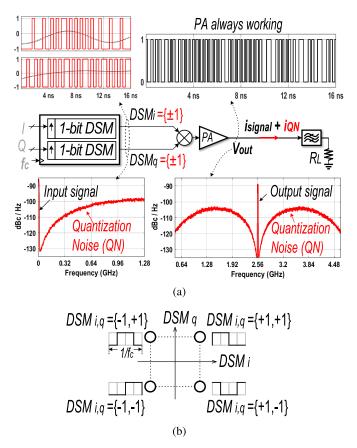

Unlike the 1-bit BP-DSM-based TX, the TX based on 1-bit low-pass (LP)-DSM is depicted in Fig. 4(a) [28], which relaxes the clock requirements. Since BP-DSM is not the target of this article, in the following context, DSM refers to LP-DSM unless otherwise mentioned. In Fig. 4(a), the DSMs clocked at the carrier frequency  $f_c$  convert the *I* and *Q* inputs into 1 bit. The 1-bit DSM outputs DSM<sub>i</sub> and DSM<sub>q</sub> toggles between ±1. When the *I* or *Q* input to the DSM is positive, DSM outputs more +1 than -1 s, and vice versa. When the input is near zero, the DSM outputs an equal number of +1 and -1 s. Fig. 4(a) (top left) shows the example of DSM waveforms.

Next, the digital mixer upconverts the DSM outputs into 1-bit PA input at the RF frequency. Since the output of each DSM can only be either +1 or -1, the mixer will only have four different input combinations, namely, [+1, +1], [-1, +1], [-1, -1], [-1, +1]. According to the specific input combination, the mixer selects a 1-bit signal with one of four different phases (45°, 135°, 225°, 315°) as the output, as shown in Fig. 4(b). The 1-bit mixer output then drives the 1-bit PA. The two-level PA output voltage is shown in Fig. 4(a) (top right).

Although conventional 1-bit DSM-based TX can encode multi-bit I and Q inputs into 1-bit PA output, the DSM introduces large QN when converting the multi-bit input into 1 bit. Fortunately, the DSM has a high sampling rate and a high-pass noise transfer function (NTF), which can suppress the QN at the signal band around dc [Fig. 4(a) (bottom left)], and ensures a decent signal-to-noise ratio (SNR). Nevertheless,

Fig. 4. (a) Block diagram, waveform, and spectra of conventional 1-bit DSM-based TX [28]. (b) Output waveforms of the mixer.

the QN is pushed to high frequencies by the NTF. After the mixer upconverts the DSM outputs to the carrier frequency, the modulation signal and the QN are both converted to the carrier frequency. The QN near the carrier frequency  $f_c$  is low, while the QN at other frequencies is high, as shown in the output voltage spectrum in Fig. 4(a) (bottom right).

Besides the modulation signal, the QN in the output voltage  $V_{out}$  will also stimulate a current ( $i_{QN}$ ) in the load, which draws current from the supply and increases power consumption. Therefore, the ideal PA power efficiency can be given by (assume ideal PA and QN are the only source of power loss)

$$\eta_{\rm ideal} = \frac{P_{\rm out}}{P_{\rm out} + P_{\rm QN}} \tag{1}$$

where  $P_{\text{out}}$  and  $P_{\text{QN}}$  are the power of the modulated signal and QN, respectively.

Equation (1) indicates that the DSM QN will severely degrade the power efficiency. To make matters worse, the DSM output cannot be 0 in this architecture. Thus, the PA is always working and cannot be turned off for TMM operation to save power.

# III. PROPOSED TMM PA WITH TRANSFORMER COMBINED FIR FILTER

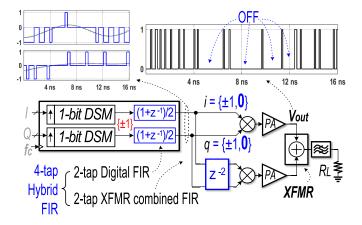

According to the analysis of Section II, we should have two design targets: suppress the DSM QN and realize the TMM operation by turning off the PA. In the proposed architecture shown in Fig. 5, a hybrid FIR filter is proposed to achieve both targets simultaneously.

Fig. 5. Block diagram and waveform of the proposed TMM PA with hybrid FIR filter.

## A. Achieving TMM Operation

As shown in Fig. 5, the applied four-tap hybrid FIR filter comprises two parts: the two-tap digital FIR filter after the DSM and the following two-tap transformer combined semidigital FIR filter. Since the DSM output can be +1 or -1, the output becomes  $\pm 1, 0$  after passing through the digital FIR filter, as shown in Fig. 5 (top left). Unlike the conventional 1-bit DSM-based quadrature PA, in the proposed PA, the mixer input can be 0. This is crucial because the 0 can turn off the PA for TMM operation.

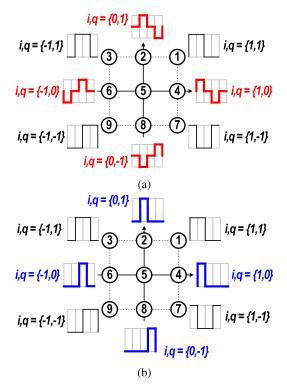

On the other hand, the i and q outputs of the digital FIR filter are 2-bit signals (one sign bit); each has three different states. Therefore, the mixer will have nine different input combinations. The conventional mixer shown in Fig. 4(a) cannot be utilized. The digital mixers widely used in the switched-capacitor-based digital TXs [31], [32] can achieve the upconversion of the 2-bit input, as shown in Fig. 6(a). In the conventional mixer mapping schemes, 50% duty cycle signals with four different phases (45°, 135°, 225°, 315°) represent the four states (states 1, 3, 7, and 9) of which  $i \neq 0$ AND  $q \neq 0$ . Three-level signals with four different phases  $(0^\circ, 90^\circ, 180^\circ, 270^\circ)$  represent the four states (2, 4, 6, and 8) of which  $i \neq 0$  OR  $q \neq 0$ . Furthermore, in the remaining OFF state when i = q = 0, the mixer output is 0 (state 5). Although this mixer can achieve upconversion, the three-level output requires a 2-bit PA, which may cause non-linearity and degrade the EVM.

To encode the 2-bit DSM outputs into two-level PA output, the mixer mapping scheme shown in Fig. 6(b) is proposed. Note that when  $i \neq 0$  AND  $q \neq 0$  (states 1, 3, 7, and 9), the output of the proposed mixer is 50% duty cycle two-level signal with four different phases, which is the same as the outputs of the conventional mixer. However, when  $i \neq 0$ OR  $q \neq 0$  (states 2, 4, 6, and 8), outputs of the proposed mixer are two-level 25% duty cycle signals with four different phases. In the remaining OFF state when i = q = 0, the mixer output is 0 (state 5) to turn off the PA for TMM operation. Fig. 5 (top right) shows the output waveform of the proposed PA. The PA output is an intrinsically linear two-level signal, and the PA can be turned off to realize the proposed TMM operation.

Fig. 6. Output voltages of (a) conventional digital mixer for digital quadrature PAs [31], [32] and (b) the proposed mixer.

## B. DSM QN Suppression Using Hybrid FIR Filter

In the proposed PA architecture shown in Fig. 5, the digital FIR filter outputs i/q are upconverted by the proposed mixer and drive one sub-PA. i/q are delayed by two carrier cycles, then upconverted, and drive another sub-PA. The two sub-PA outputs are combined through a transformer (XFMR). Since the digital i/q signal is delayed in the digital domain and combined in the analog domain, this forms a two-tap XFMR combined semi-digital FIR filter. Unlike [32], which adopts a switched capacitor array to combine the semi-digital FIR filter outputs and results in large power loss, we choose the XFMR to combine the FIR outputs that avoid the capacitor array loss for high power efficiency. Considering the two-tap digital FIR filter, we can derive that the output voltage of the proposed PA should be

$$V_{\text{out}} = \text{DSM}_{i/q} \times \frac{1}{2} \left( 1 + z^{-1} + z^{-2} + z^{-3} \right) \times \text{LO}_{i/q}.$$

(2)

Therefore, a four-tap FIR response is implemented in the proposed PA with a two-feed XFMR.

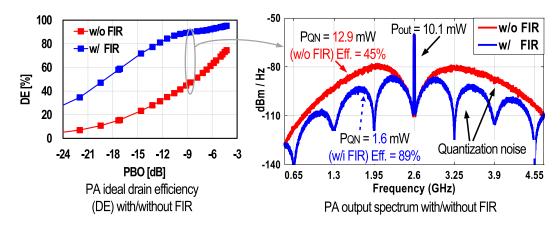

Fig. 7 shows the simulated output spectrum and ideal efficiency [see (1)] of the proposed TMM PA with and without the four-tap hybrid FIR filter (without the FIR filter, it will become a conventional 1-bit DSM-based digital quadrature PA discussed in Section III). In the simulation, 20-MSymbol/s 64-QAM signal is adopted as the input, and the first-order DSMs clocked at  $f_c = 2.6$  GHz convert the input into 1 bit. Since the on-chip matching network usually has a BP filter characteristic that can suppress some of the DSM QN, a BP filter with a Q value of 2 is added at the PA output for a more accurate simulation of the QN power.

ZHANG et al.: TMM DIGITAL QUADRATURE PA BASED ON 1-bit DSM AND HYBRID FIR FILTER

Fig. 7. [Rev. 1.1] [Rev. 2.8] Simulation results of the proposed TMM PA with and without the proposed FIR filter.

It can be seen from Fig. 7 that the proposed hybrid FIR filter significantly reduces the DSM QN power in the proposed PA. The associated ideal efficiency is improved compared with the case without FIR. At around 9-dB PBO, the output power is 10.1 mW, while the QN power with and without the FIR filter is 1.6 and 12.9 mW, respectively. The FIR filter contributes to around  $8 \times$  QN power suppression. The ideal efficiency at this point improves from only 45% to 88%. However, increasing the number of FIR taps will further increase the QN suppression and improve efficiency. Nevertheless, combining more FIR taps requires either a more complex transformer that introduces significant area overhead or a multi-bit PA that suffers from low PBO efficiency.

## **IV. CIRCUITS NON-IDEALITIES**

For further analysis, the non-ideal factors of the circuits should be considered.

#### A. PA With Non-Ideal Components

In the proposed structure, a 1-bit PA is adopted. A Class-D PA is chosen over Class-E PA, because Class-D PA requires fewer passive components and is, thus, more area-efficient. Although the theoretical efficiency of a Class-D PA is 100%, however, several non-ideal effects must be considered when implementing the PA, including conduction loss, switching loss, and passive loss [19], [24], [26]. Suppose  $R_{\rm ON}$  is the switch-ON resistance of the PA, and conduction loss is the power dissipated in  $R_{\text{ON}}$ .  $C_{\text{par}}$  is the parasitic drain capacitance, which is charged at every rising edge of the PA output and causes switching loss. The passive matching network of the PA also attenuates the output power by a factor of  $\alpha$ , which is passive loss. Note that  $R_{ON}$  decreases and  $C_{par}$  increases when the transistor size increases. The product of  $R_{\rm ON}C_{\rm par}$  is a constant, and we can define the totem pole driver figure of merit  $f_{SW} = 1/(2\pi R_{ON}C_{par})$  [23]. Advanced process and good layout can improve  $f_{SW}$ .

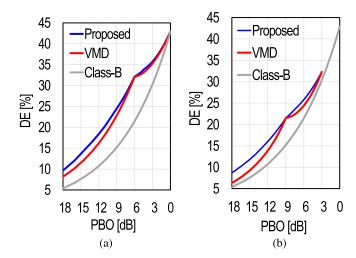

The drain efficiency (DE) of the proposed TMM PA and the conventional VMD PA at different phases, including QN and all aforementioned non-ideal factors, is simulated and plotted versus PBO levels in Fig. 8. Fig. 8(a) and (b) shows the simulated results at 45° (I = Q) and 0° (I = 0), respectively.

Fig. 8. Simulated efficiency of the proposed TMM PA and conventional VMD PA at different angles. Simulation including QN and non-ideal circuits (load  $R_L = 5 \Omega$ ,  $R_{\rm ON}/R_L = 1/5$ ,  $f_{\rm SW} = 25$  GHz,  $\alpha = 0.7$ , and quality factor of the load  $Q_{\rm loaded} = 2$ ). (a) I = Q, 45°. (b) I = 0, 0°.

Here, we can see that the DE of the proposed PA outperformed the conventional VMD PA at different angles (I = Q and I = 0). The efficiency is significantly improved compared with normalized Class-B PA.

## B. Gain and Delay Mismatches Between the Two Sub-PAs

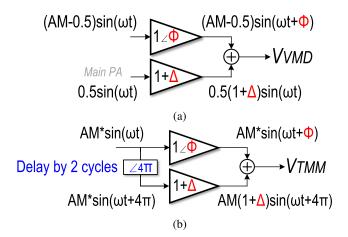

The proposed PA uses two sub-PA cells to construct the XFMR combined FIR filter. The effect of mismatches between the two sub-PAs should be analyzed. Fig. 9(a) shows the simplified mismatch model of a VMD PA when 0.5 < AM < 1, where AM is the normalized amplitude control code. The main PA is working at its peak (normalized amplitude 0.5), and its output suffers from a gain mismatch of  $\Delta$ . The peak PA output suffers from a phase shift of  $\phi$  caused by the delay mismatch between the two sub-PAs. Therefore, according to the phasor addition theory, suppose  $\phi$  is small and  $\cos \phi \approx 1$ ,  $\sin \phi \approx \phi$ , the output voltage of VMD PA is

$$V_{\rm VMD} = (AM + 0.5\Delta) \times \sin(\omega t + \theta)$$

(3)

$$\theta = \arctan \frac{AM - 0.5}{AM + \Delta} \phi.$$

(4)

Fig. 9. Simplified mismatch model for (a) VMD PA and (b) proposed TMM PA with XFMR combined FIR filter.

Considering the situation of AM < 0.5, when peak PA is off, and only the main PA is working, the output gain ( $G_{\text{VMD}}$ ) and phase (Ph<sub>VMD</sub>) of VMD PA are given by

$$G_{\rm VMD} = \begin{cases} 1, & 0 < \rm{AM} < 0.5\\ 1 + 0.5\Delta/\rm{AM}, & 0.5 < \rm{AM} < 1 \end{cases}$$

(5)

$$Ph_{VMD} = \begin{cases} \phi, & 0 < AM < 0.5\\ \arctan \frac{AM - 0.5}{AM + 0.5\Lambda}\phi, & 0.5 < AM < 1. \end{cases}$$

(6)

Similarly, Fig. 9(b) shows the mismatch model for TMM PA with XFMR combined FIR filter. The output of the two sub-PAs has a delay of two cycles, translating into a phase shift of  $4\pi$ . Similarly, the output gain ( $G_{\text{TMM}}$ ) and phase (Ph<sub>TMM</sub>) of the proposed PA are given by

$$G_{\rm TMM} = 1 + 0.5\Delta \tag{7}$$

$$Ph_{TMM} = \arctan \frac{1}{2+\Delta}\phi.$$

(8)

It can be concluded from the above equations that the mismatches lead to AM-dependent gain and phase in the conventional VMD PA, which gives rise to non-linearity. On the contrary, the output gain and phase of the proposed PA are constant and not input-dependent. Therefore, the proposed PA is not sensitive to mismatches and is still intrinsically linear.

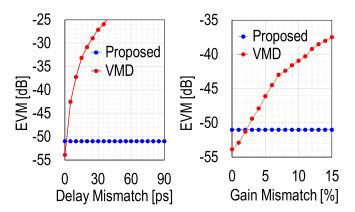

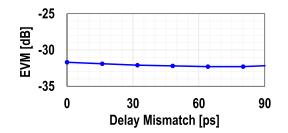

Behavioral simulation is performed to verify the previous calculations. A 20-MSymbol/s 64-QAM signal at a 2.6-GHz carrier is applied to both the VMD PA and the proposed TMM PA to verify the effect of mismatches on the signal integrity. Simulated EVMs with different mismatches are plotted in Fig. 10. The EVM of conventional VMD PA degrades rapidly with the increase of gain/delay mismatches, while the EVM of the proposed PA does not change, which proves that the proposed PA is not sensitive to mismatches. It should be mentioned that the delay mismatch will affect the FIR filter response, which causes ripple in the signal band. However, this is not a problem, since equalizers are widely adopted in the demodulators of modern wireless standards to compensate for the in-band gain variation. Therefore, the equalizer is enabled in the simulations of Fig. 10.

IEEE JOURNAL OF SOLID-STATE CIRCUITS

Fig. 10. Simulated EVM versus gain and delay mismatches between the two sub-PAs.

#### V. IMPLEMENTATION OF THE PROTOTYPE

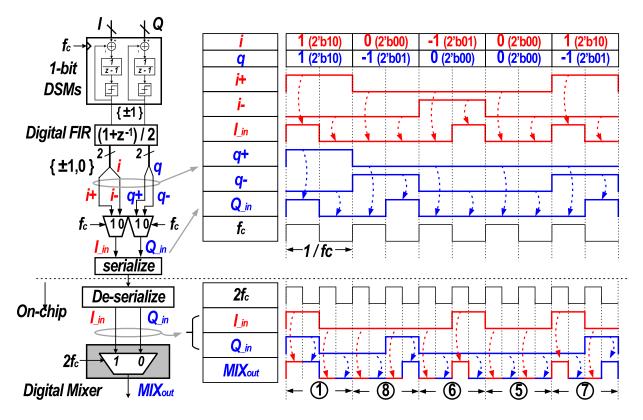

# A. Implementation of the Mixer

Fig. 11 shows the implementation of the proposed mixer in Fig. 6(b). *I* and *Q* are the baseband input signals, which are then encoded into 1 bit by the DSMs clocked at carrier frequency  $f_c$ . Next, DSM outputs are processed by the two-tap digital FIR filter. The 2-bit outputs of digital FIR are denoted as *i* and *q* in Fig. 11. *i*+ and *i*- are the MSB and LSB of *i*, respectively. q+ and q- are the MSB and LSB of *q*, respectively. Note that *i* and *q* are not encoded in standard digital format, i.e., 2's complement. They are encoded in a special way, as shown in Fig. 11 (top right). The three different values of *i* and q, -1, 0, and 1, are represented by the 2-bit digital codes 10, 00, and 01, respectively. Therefore, when i = 1, i + = 1 and i - = 0.

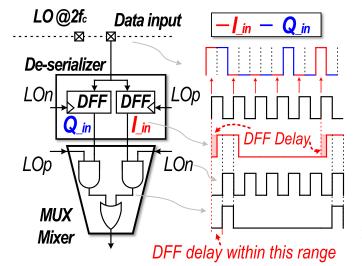

The mixer is realized in a two-step manner. The square-wave signal at  $f_c$  drives two 2:1 multiplexers (MUXs), which convert i+, i-, q+, and q- into 1-bit signals  $I_{in}$  and  $Q_{in}$ .  $I_{in}$  and  $Q_{in}$  serves as the input to the on-chip digital mixer. The on-chip digital mixer is another 2:1 MUX, but is driven by a square wave at twice the carrier frequency  $2f_c$ .

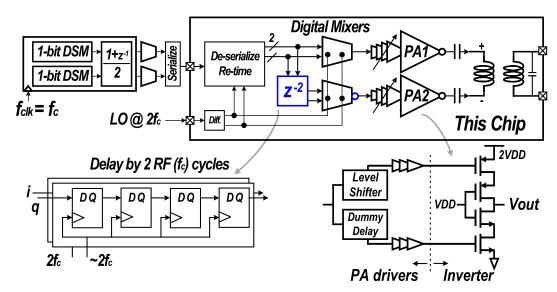

# B. Implementation of the Overall PA

Fig. 11 also shows some waveform examples of the mixing process. Since DSM and digital FIR are clocked at  $f_c$ , i and q will update every RF cycle  $(1/f_c)$ . In the off-chip MUX, the  $I_{in} = i +$  for the first half RF cycle, and  $I_{in} = i -$  for the next half RF cycle.  $Q_{in}$  is generated in the same way. Therefore, the sequence of  $I_{in} = [i+,i-]@2f_c$  and  $Q_{in} = [q+,q-]@2f_c$ . A square wave at  $2f_c$  drives the on-chip MUX. Therefore, its output updates every 1/4 RF cycles, and mixer output sequence MIX<sub>out</sub> =  $[I_{in}, Q_{in}]@4f_c = [i+,q+,i-,q-]@4f_c$ . According to the i and q value in Fig. 11, the mixer should generate states 1, 8, 6, 5, and 7 in Fig. 6(b), sequentially. When comparing the waveform of MIX<sub>out</sub> with the states in Fig. 6(b), it can be seen that the two-step MUX-based mixer in Fig. 11 correctly realizes the mixing scheme in Fig. 6(b).

Fig. 12 shows the circuits of the implemented chip. The DSM is clocked at the carrier frequency to maximize the oversampling ratio of the DSM to increase the SNR. For a 20-MSymbol/s input signal with 8-dB PAPR and 2.6-GHz

ZHANG et al.: TMM DIGITAL QUADRATURE PA BASED ON 1-bit DSM AND HYBRID FIR FILTER

Fig. 11. Implementation of the proposed mixer and the waveform example.

Fig. 12. Block diagram and circuits of the implemented chip.

clock, the DSM yields 52-dB SNR. High-speed digital logic, including DSMs and the digital FIR filters, is realized offchip. The 2-bit input to the mixers is serialized to 1-bit and given to the chip. Therefore, we can reduce one input pad on the chip and use a normal ground–signal–signal–ground (GSSG) probe to measure the chip. The input is deserialized on-chip, then delayed, and drives the digital mixers. The chip's input LO is a square-wave signal at twice the carrier frequency. The LO is converted to a differential signal and clocks the on-chip de-serializer, re-timers, and mixers. Since the clock is twice the carrier frequency, four D-flip-flops (DFFs) are utilized to generate the delay of two RF cycles to form the two-tap XFMR combined semi-digital FIR filter. In the PA, 2.4-V supply and cascaded transistors are used to increase the output power [20]. Outputs of the two PAs are combined with an on-chip XFMR. In this implementation, we can demonstrate the working principle of the proposed PA without on-chip DSMs. However, implementing DSM is crucial, since it may be challenging to design high-speed logic, and the high-speed digital circuits may be powerhungry. Using commercial digital synthesis tools, we have synthesized the error-feedback DSMs and digital FIR filters.

Fig. 13. Circuits of the de-serializer and the skew-free mixer.

The digital logics, including DSMs and digital FIR filters, can satisfy the timing requirements under 0.9 V/125 °C/ss-corner, 1.0 V/25 °C/tt-corner, and 1.1 V/-40 °C/ff-corner with 2.6-GHz clock. The power consumption is only 1 mW from post-layout simulations, which will have a negligible influence on the system's power efficiency.

# *C. Circuit Implementation of the De-Serializer and On-Chip Mixer*

A big issue for the DSM-based PAs is the clock skew when re-timing the input digital signal [33]. However, in this chip, the on-chip mixer is realized skew-free. As depicted in Fig. 13, mixer inputs  $I_{in}$  and  $Q_{in}$  are serialized and given to the chip as the data input. Therefore,  $I_{in}$  and  $Q_{in}$  in the data input are interleaved. The de-serializer comprises two DFFs clocked by LOp and LOn. As shown in Fig. 13 (right), data input is re-timed by the rising edge of LOp and yields the  $I_{in}$  signal. The DFF will inevitably introduce a delay to its output, and the edge of  $I_{in}$  will lag LOp.  $I_{in}$  is then combined with LOn by an AND gate in the mixer. As we can see from the figure, if the rising edge of  $I_{in}$  is between the rising edge of LOp and LOn, the mixer can be skew-free. The delay between the rising edges of LOp and LOn is  $1/4f_c$ , which means that the DFF delay should be smaller than  $1/4 f_c$ . Suppose the carrier frequency  $f_c = 2.5$  GHz. DFF delay should be smaller than 100 ps, which can be satisfied in modern fine-line CMOS technologies.

## VI. MEASUREMENT RESULTS

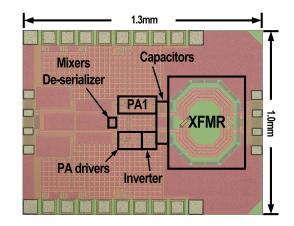

A prototype chip is fabricated in a 65-nm CMOS process. Fig. 14 shows the chip micrograph. In the measurements, input signals to the chip are calculated using MATLAB, which are then loaded into an arbitrary waveform generator (AWG), Keysight M8195A. The AWG exports the input signals to the chip. A BALUN, Marki BAL-0006, converts the differential output of the PA into single-ended. Keysight UXR captures and demodulates the PA outputs.

Fig. 14. Chip micrograph.

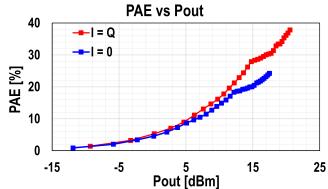

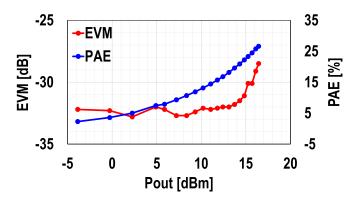

Fig. 15. Measured PAE versus output power with CW input.

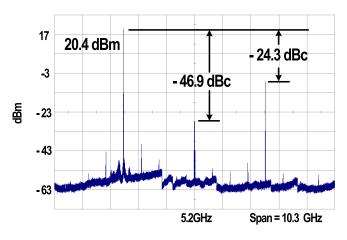

Fig. 16. Measured spectrum and harmonics with CW input.

#### A. CW Measurements

In continuous-wave (CW) measurements, the DSM inputs are swept from the minimum to the maximum for I = Qand I = 0 path. A spectrum analyzer captures the power of the PA output (loss of off-chip BALUN and cable are de-embedded). Fig. 15 shows the power-added efficiency (PAE) versus output power. At a 2.6-GHz carrier, the proposed PA achieves 20.6-dBm peak output power, with a peak PAE of 37.8% under a 2.4-V supply. The PAE at 6-dB PBO of I = Qpath is 28.5%,  $1.51 \times$  higher than the typical Class-B PA. Note that the power consumption of both the PA stage (inverter) and the PA drivers is included when calculating PAE. Fig. 16

ZHANG et al.: TMM DIGITAL QUADRATURE PA BASED ON 1-bit DSM AND HYBRID FIR FILTER

Fig. 17. Measured PAE and EVM versus output power with 20-MSymbol/s 256-QAM signal at 2.6-GHz carrier.

Fig. 18. Measured constellation and close-in spectrum with 20-MSymbol/s 256-QAM signal at 2.6-GHz carrier.

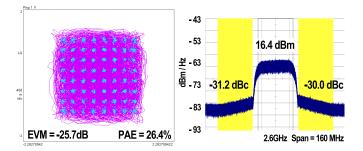

Fig. 19. Measured constellation and close-in spectrum with 40-MSymbol/s 64-QAM signal at 2.6-GHz carrier.

shows the measured spectrum and harmonics of the proposed PA. The second and third harmonics are -46.9 and -24.3 dBc, respectively.

#### **B.** Modulation Measurements

DPD is not applied in modulation measurements because of the good linearity provided by the proposed PA. With 20-MSymbol/s 256-QAM signal at 2.6-GHz carrier, the measured PAE and EVM versus output power is plotted in Fig. 17. At 14.3-dBm output power, the EVM is -31.5 dB, with a PAE of 20.9%, and Fig. 18 shows the measured constellation and close-in spectrum. The ACPR is -34.7/-33.8 dBc. Fig. 19 shows the measured constellation and close-in spectrum with 40-MSymbol/s 64-QAM signal. A high efficiency of 26.4% is achieved at 16.4-dBm output power, with an EVM of -25.7 dB. The ACPR is -31.2/-30.0 dBc.

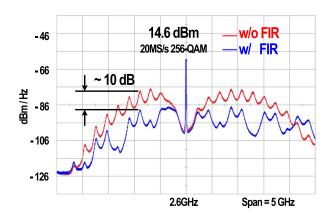

The far-out spectrum of the proposed PA with and without the proposed hybrid FIR filter is depicted in Fig. 20.

Fig. 20. Measured far-out spectrum with and without the hybrid FIR filter.

Fig. 21. Measured EVM versus delay mismatches.

Fig. 22. Measured EVM versus PAE and comparison with prior arts.

Around 10-dB QN reduction is observed, contributing to high efficiency.

To prove the insensitivity to delay mismatches of the proposed PA, mixers are bypassed, and the two AWG outputs directly give the input signal to the PA. The delay mismatch of the two sub-PAs is controlled by changing the AWG output delays. Fig. 21 shows the measured EVM versus delay mismatch. The EVM has less than 1-dB variation with a delay mismatch as large as 90 ps.

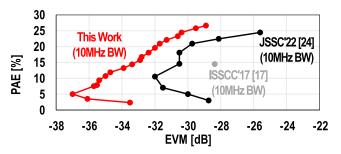

Table I summarizes the performance of the proposed PA and compares it with other digital PAs. Compared with other DPD-less digital quadrature PAs [17], [22], at similar EVM levels, the proposed PA achieves higher efficiency and wider bandwidth. Also, it also supports 256 QAM. A 10-MSymbol/s 256-QAM signal is applied to the proposed PA to compare with [17] with similar bandwidth. Fig. 22 shows the measured PAE and EVM plots. The proposed PA achieves lower EVM and higher efficiency than prior arts at similar bandwidth. The proposed DPD-less TMM PA achieves comparable or better EVMs than digital PAs using DPDs [20], [21], [22], [34], [35], [36], demonstrating its good linearity. The PAE is also comparable to polar PAs. The hybrid FIR filter suppresses the

|          | Tech. | PA<br>Structure |            | Freq.<br>[GHz] | PA          | Peak  |            | Average       |       |         |       |         | OOB       | HD2      | Core   |       |

|----------|-------|-----------------|------------|----------------|-------------|-------|------------|---------------|-------|---------|-------|---------|-----------|----------|--------|-------|

|          | [nm]  |                 |            |                | VDD         | Pout  | PAE        | MOD.          | BW    | BW Pout | PAE   | EVM     | DPD       | Emission | /HD3   | Area  |

|          | լոույ |                 | Structure  | [0112]         | [V]         | [dBm] | [%]        | mobi          | [MHz] | [dBm]   | [%]   | [dB]    | ]         | [dBc/Hz] | [dBc]  | [mm2] |

| This     | 65    |                 | 1bit DSM   |                | 2.4         | 20.6  | 37.8       | 256QAM        | 20 14 | 14.3    | 20.9  | -31.5   |           | -105.3   | -46.9  | 0.34  |

| Work     | 0.5   |                 | Hybrid FIR | 2.6            | 2.4         | 20.0  | 57.0       | 64QAM         | 40    | 16.4    | 26.4  | -25.7   |           | -105.5   | /-24.3 | 0.54  |

| ISSCC'17 | 28    |                 | Doherty    | 2.5            | 1.1         | 28.6  | 35         | LTE           | 5     | 20.7    | 14.6  | -30     |           | N.A.     | N.A.   | 1.14  |

| [17]     | 20    |                 | SCPA       |                |             |       |            |               |       |         |       |         |           |          |        | *     |

| JSSC'22  | 55    |                 | Doherty    | 0.85           | 2.4         | 29.3  | 43         | 64QAM<br>LTE  | 10    | 22*     | 10*   | -30* No | No        | N.A.     | N.A.   | 1.2   |

| [24]     | 55    |                 | SCPA       |                |             |       |            |               |       | 23.6    | 24.4  | -25.6   | .5.6      |          |        |       |

| TMTT'19  | 28    | Quad            | 1bit DSM   | 0.9            | 1           | 4.6   | 28.2       | LTE           | 10    | -1.2    | 8.6   | N.A.    |           | -120 *   | N.A.   | 0.047 |

| [32]     | (SOI) |                 | FIR C-DAC  |                |             |       |            |               |       |         |       |         |           |          |        | #     |

| JSSC'09  | 90    |                 | 1bit DSM   | 0.65           | 1           | 3.1   | N.A.       | QPSK          | 5     | -3.9    | 1     | -38.1   |           | -89 *    | N.A.   | 0.15  |

| [28]     | 90    |                 |            |                |             |       |            |               |       |         |       |         |           |          |        | #     |

| JSSC'21  | 40    |                 | Doherty    | 2.8            | 1.1         | 24.2  | 32.7       | 256QAM        | 10    | 16.2    | 18.9  | -32.3   | Off-chip  | -102     | -25    | 0.83  |

| [18]     | 40    |                 | SCPA       |                |             |       |            |               |       |         |       |         |           |          | /-20   | 0.85  |

| JSSC'21  | 65    |                 | Class-G    | 2.2            | 2.55        | 27.8  | 32.1       | 1024QAM       | 20    | 21      | 18.4  | -43     | Off-chip  | N.A.     | N.A.   | 0.9   |

| [26]     | 65    |                 | Doherty    | 2.2            | /1.25       |       |            |               |       |         |       |         |           |          |        |       |

| JSSC'13  | 65    |                 | Class-G    | 2.15           | 2.8<br>/1.4 | 24.3  | 43.5<br>#  | 64QAM<br>WLAN | 20    | 16.8    | 33    | -30.8   | No        | -120.5   | N.A.   | 0.13  |

| [20]     | 65    |                 | SCPA       | 2.15           |             |       |            |               |       |         |       |         |           |          |        | #     |

| JSSC'19  | 65    |                 | Class-G    | 2.25           | 3.6         | 26.8  | 49.3       | 16QAM         | 5     | 16.6    | 35.7  | -26     | Off-chip  | N.A.     | -26    | 1#    |

| [21]     | 65    | - Polar         | SHS SCPA   | 2.23           | /2.4        |       | (DE)#      | OFDM          |       |         | (DE)# |         |           |          | /-46   | 1#    |

| JSSC'19  | 65    |                 | Class-G    | 1.9            | 3.6<br>/2.4 | 30    | 45.9       | 16QAM         | 5     | 22.8    | 31.4  | -24.7   | Off-chip  | N.A.     | N.A.   | 4.5 * |

| [22]     | 0.5   |                 | SHS SCPA   |                |             |       | (DE)       | OFDM          | 5     | 22.0    | (DE)  |         |           |          |        |       |

| JSSC'23  | 40    | rotar           | Reconfig   | 2.4            | 2.5         | 32.7  | 35.5       | 256QAM        | 25    | 24.5    | 18.9  | -32.1   | Off-chip  | -108.2   | N.A.   | 0.99  |

| [34]     | 40    |                 | XFMR SCPA  |                | 2.3         |       |            |               |       |         |       |         |           |          |        |       |

| JSSC'23  | 40    |                 | Doherty    | 1.8            | 2.5         | 28.9  | 37.2       | 256QAM        | 25    | 21.5    | 33.1  | -33.9   | Self-Cal. | -114     | -41.9  | 0.76  |

| [35]     | 40    |                 | SCPA       |                |             |       |            |               |       |         | (DE)  |         | (42.4 mW) |          | /-28.9 |       |

| JSSC'16  | 65    |                 | Doherty    | 3.71           | 2 71 3      | 26.7  | 43<br>(DE) | 64QAM         | 1     | 16.8    | 24.5  | -28     | Bias-     | N.A.     | N.A.   | 1.76  |

| [36]     | 05    |                 | Class-G    | 5./1           | /1.65       | 20.7  |            |               |       |         | (DE)  |         | Tuning    | IN.A.    |        | *     |

TABLE I Performance Comparison With Other Digital PAs

\* Estimated from reported figures. # Off-chip inductors for matching networks.

DSM QN to improve efficiency, and the out-of-band emission is much smaller than the DSM-based TX without the FIR filter [28]. However, the out-of-band DSM QN is still higher than the emission of other SCPAs. Marin et al. [32] proposed to use a multi-tap FIR filter based on capacitor digital-to-analog converter (C-DAC) to suppress the DSM QN. Nevertheless, the switched capacitors in the C-DAC introduce significant power loss, and the efficiency degrades severely. Therefore, how to reduce DSM QN without sacrificing efficiency remains an open question.

# VII. CONCLUSION

This article demonstrates a TMM digital quadrature PA with a hybrid FIR filter. The 1-bit PA is turned on and off sequentially to realize the TMM for efficiency improvement. The proposed TMM does not require a lossy capacitor array and is, thus, power-efficient. It is also intrinsically linear, since the output is 1 bit. The multi-bit I/Q input signals are encoded into 1-bit PA control code using 1-bit DSMs, a two-tap digital FIR filter, and the proposed digital mixer. A hybrid FIR filter comprising the two-tap digital FIR and another two-tap XFMR combined semi-digital FIR filter is also proposed to suppress the DSM QN to enhance efficiency. The XFMR combined FIR filter does not suffer from circuit mismatches. The implemented PA achieves state-of-the-art power efficiency and linearity at the same time. It can support 20-MSymbol/s 256 QAM without applying DPD with a PAE over 20%.

#### REFERENCES

J. Campos, Understanding the 5G NR Physical Layer, vol. 111. Santa Rosa, CA, USA: Keysight Technologies Release, 2017.

- [2] R. B. Staszewski et al., "All-digital PLL and transmitter for mobile phones," *IEEE J. Solid-State Circuits*, vol. 40, no. 12, pp. 2469–2482, Dec. 2005.

- [3] D. D. Wentzloff and A. P. Chandrakasan, "A 47pJ/pulse 3.1-to-5 GHz all-digital UWB transmitter in 90 nm CMOS," in *IEEE Int. Solid-State Circuits Conf. (ISSCC) Dig. Tech. Papers*, Feb. 2007, pp. 118–591.

- [4] Y. Park and D. D. Wentzloff, "An all-digital 12 pJ/pulse IR-UWB transmitter synthesized from a standard cell library," *IEEE J. Solid-State Circuits*, vol. 46, no. 5, pp. 1147–1157, May 2011.

- [5] P. A. J. Nuyts, P. Singerl, F. Dielacher, P. Reynaert, and W. Dehaene, "A fully digital delay line based GHz range multimode transmitter frontend in 65-nm CMOS," *IEEE J. Solid-State Circuits*, vol. 47, no. 7, pp. 1681–1692, Jul. 2012.

- [6] P. Eloranta, P. Seppinen, S. Kallioinen, T. Saarela, and A. Parssinen, "A multimode transmitter in 0.13 μm CMOS using direct-digital RF modulator," *IEEE J. Solid-State Circuits*, vol. 42, no. 12, pp. 2774–2784, Dec. 2007.

- [7] A. Pozsgay, T. Zounes, R. Hossain, M. Boulemnakher, V. Knopik, and S. Grange, "A fully digital 65nm CMOS transmitter for the 2.4-to-2.7 GHz WiFi/WiMAX bands using 5.4GHz  $\Delta\Sigma$  RF DACs," in *IEEE Int. Solid-State Circuits Conf. (ISSCC) Dig. Tech. Papers*, Feb. 2008, pp. 360–619.

- [8] Z. Boos et al., "A fully digital multimode polar transmitter employing 17b RF DAC in 3G mode," in *IEEE Int. Solid-State Circuits Conf.* (*ISSCC*) Dig. Tech. Papers, Feb. 2011, pp. 376–378.

- [9] A. Ravi et al., "A 2.4-GHz 20–40-MHz channel WLAN digital outphasing transmitter utilizing a delay-based wideband phase modulator in 32-nm CMOS," *IEEE J. Solid-State Circuits*, vol. 47, no. 12, pp. 3184–3196, Dec. 2012.

- [10] J. Chen, L. Rong, F. Jonsson, G. Yang, and L.-R. Zheng, "The design of all-digital polar transmitter based on ADPLL and phase synchronized  $\Delta\Sigma$  modulator," *IEEE J. Solid-State Circuits*, vol. 47, no. 5, pp. 1154–1164, May 2012.

- [11] L. Ye, J. Chen, L. Kong, E. Alon, and A. M. Niknejad, "Design considerations for a direct digitally modulated WLAN transmitter with integrated phase path and dynamic impedance modulation," *IEEE J. Solid-State Circuits*, vol. 48, no. 12, pp. 3160–3177, Dec. 2013.

ZHANG et al.: TMM DIGITAL QUADRATURE PA BASED ON 1-bit DSM AND HYBRID FIR FILTER

- [12] A. Ba et al., "A 1.3 nJ/b IEEE 802.11ah fully-digital polar transmitter for IoT applications," *IEEE J. Solid-State Circuits*, vol. 51, no. 12, pp. 3103–3113, Dec. 2016.

- [13] K. Oishi et al., "A 1.95 GHz fully integrated envelope elimination and restoration CMOS power amplifier using timing alignment technique for WCDMA and LTE," *IEEE J. Solid-State Circuits*, vol. 49, no. 12, pp. 2915–2924, Dec. 2014.

- [14] Y. Zhang et al., "A 29% PAE 1.5bit-DSM-based polar transmitter with spur-mitigated injection-locked PLL," in *Proc. IEEE Symp. VLSI Circuits*, Jun. 2020, pp. 1–2.

- [15] H. Xu, Y. Palaskas, A. Ravi, M. Sajadieh, M. A. El-Tanani, and K. Soumyanath, "A flip-chip-packaged 25.3 dBm class-D outphasing power amplifier in 32 nm CMOS for WLAN application," *IEEE J. Solid-State Circuits*, vol. 46, no. 7, pp. 1596–1605, Jul. 2011.

- [16] J. S. Walling et al., "A class-E PA with pulse-width and pulse-position modulation in 65 nm CMOS," *IEEE J. Solid-State Circuits*, vol. 44, no. 6, pp. 1668–1678, Jun. 2009.

- [17] A. Passamani, D. Ponton, E. Thaller, G. Knoblinger, A. Neviani, and A. Bevilacqua, "13.9 A 1.1 V 28.6dBm fully integrated digital power amplifier for mobile and wireless applications in 28nm CMOS technology with 35% PAE," in *IEEE Int. Solid-State Circuits Conf.* (*ISSCC*) Dig. Tech. Papers, Feb. 2017, pp. 232–233.

- [18] H. J. Qian, B. Yang, J. Zhou, H. Xu, and X. Luo, "A quadrature digital power amplifier with hybrid Doherty and impedance boosting for complex domain power back-off efficiency enhancement," *IEEE J. Solid-State Circuits*, vol. 56, no. 5, pp. 1487–1501, May 2021.

- [19] S.-M. Yoo, J. S. Walling, E. C. Woo, B. Jann, and D. J. Allstot, "A switched-capacitor RF power amplifier," *IEEE J. Solid-State Circuits*, vol. 46, no. 12, pp. 2977–2987, Dec. 2011.

- [20] S.-M. Yoo et al., "A class-G switched-capacitor RF power amplifier," IEEE J. Solid-State Circuits, vol. 48, no. 5, pp. 1212–1224, May 2013.

- [21] A. Zhang and M. S. Chen, "A subharmonic switching digital power amplifier for power back-off efficiency enhancement," *IEEE J. Solid-State Circuits*, vol. 54, no. 4, pp. 1017–1028, Apr. 2019.

- [22] A. Zhang and M. S. Chen, "A watt-level phase-interleaved multisubharmonic switching digital power amplifier," *IEEE J. Solid-State Circuits*, vol. 54, no. 12, pp. 3452–3465, Dec. 2019.

- [23] V. Vorapipat, C. S. Levy, and P. M. Asbeck, "Voltage mode Doherty power amplifier," *IEEE J. Solid-State Circuits*, vol. 52, no. 5, pp. 1295–1304, May 2017.

- [24] Y. Li et al., "A 15-bit quadrature digital power amplifier with transformer-based complex-domain efficiency enhancement," *IEEE J. Solid-State Circuits*, vol. 57, no. 6, pp. 1610–1622, Jun. 2022.

- [25] Y. Zhang et al., "A time-mode-modulation digital quadrature power amplifier based on 1-bit delta-sigma modulator and transformer combined FIR FIIter," in *Proc. IEEE Symp. VLSI Technol. Circuits (VLSI Technol. Circuits)*, Jun. 2023, pp. 1–2.

- [26] S.-C. Hung, S.-W. Yoo, and S.-M. Yoo, "A quadrature class-G complexdomain Doherty digital power amplifier," *IEEE J. Solid-State Circuits*, vol. 56, no. 7, pp. 2029–2039, Jul. 2021.

- [27] W. Yuan, V. Aparin, J. Dunworth, L. Seward, and J. S. Walling, "A quadrature switched capacitor power amplifier," *IEEE J. Solid-State Circuits*, vol. 51, no. 5, pp. 1200–1209, May 2016.

- [28] A. Frappe, A. Flament, B. Stefanelli, A. Kaiser, and A. Cathelin, "An all-digital RF signal generator using high-speed ΔΣ modulators," *IEEE J. Solid-State Circuits*, vol. 44, no. 10, pp. 2722–2732, Oct. 2009.

- [29] T. Maehata, S. Kameda, and N. Suematsu, "High ACLR 1-bit direct radio frequency converter using symmetric waveform," in *Proc. 42nd Eur. Microw. Conf.*, Oct. 2012, pp. 1051–1054.

- [30] T. Maehata, S. Kameda, and N. Suematsu, "1-bit band-pass deltasigma modulator with parallel IIR form for concurrent multiband digital transmitter," *IEICE Trans. Commun.*, vol. E100.B, no. 7, pp. 1152–1159, 2017.

- [31] H. Jin, D. Kim, and B. Kim, "Efficient digital quadrature transmitter based on IQ cell sharing," *IEEE J. Solid-State Circuits*, vol. 52, no. 5, pp. 1345–1357, May 2017.

- [32] R.-C. Marin, A. Frappe, B. Stefanelli, P. Cathelin, A. Cathelin, and A. Kaiser, "Digital RF transmitter with single-bit  $\Delta\Sigma$  M-driven switched-capacitor RF DAC and embedded band filter in 28-nm FD-SOI," *IEEE Trans. Microw. Theory Techn.*, vol. 67, no. 7, pp. 3200–3209, Jul. 2019.

- [33] Y. Zhang, B. Liu, J. Qiu, A. Shirane, and K. Okada, "A 1-bit-DSM-based digital polar power amplifier supporting 1024-QAM," *IEEE Solid-State Circuits Lett.*, vol. 5, pp. 130–133, 2022.

- [34] B. Yang, H. J. Qian, T. Wang, and X. Luo, "A CMOS wideband wattlevel 4096-QAM digital power amplifier using reconfigurable powercombining transformer," *IEEE J. Solid-State Circuits*, vol. 58, no. 2, pp. 357–370, Feb. 2023.

- [35] H. Tang, H. J. Qian, B. Yang, and X. Luo, "A self-calibration SCPA with storage capacitor array supporting 64-/256-/1024-QAM," *IEEE J. Solid-State Circuits*, vol. 58, no. 5, pp. 1241–1255, May 2023.

- [36] S. Hu, S. Kousai, and H. Wang, "A broadband mixed-signal CMOS power amplifier with a hybrid class-G Doherty efficiency enhancement technique," *IEEE J. Solid-State Circuits*, vol. 51, no. 3, pp. 598–613, Mar. 2016.

**Yuncheng Zhang** (Member, IEEE) received the B.S. and M.E. degrees in electrical engineering from the University of Science and Technology of China (USTC), Hefei, China, in 2013 and 2016, respectively, and the Ph.D. degree from the Tokyo Institute of Technology, Tokyo, Japan, in 2022.

In 2022, he joined the Tokyo Institute of Technology as a Post-Doctoral Researcher, where he is currently a Specially Appointed Assistant Professor. His research interests include power-efficient wireless transceivers, all-digital phase-locked loops, and

analog-to-digital converters.

Dr. Zhang was a recipient of the Best Design Award at the IEEE/ACM ASP-DAC University Design Contest in 2021.

Zheng Sun (Member, IEEE) was born in Yancheng, China, in 1993. He received the B.S. degree in information engineering from Southeast University, Nanjing, China, in 2014, the M.S. degree in information, production, and systems engineering from Waseda University, Fukuoka, Japan, in 2015, and the Ph.D. degree in physical electronics from the Tokyo Institute of Technology, Tokyo, Japan, in 2021.

From April 2021 to July 2021, he was a Post-Doctoral Researcher with the Tokyo Institute of Technology. He is currently with Apple Inc., Tokyo,

working on wireless connectivity. He was involved in low-power transceivers for the Internet-of-Things, mixed-signal circuits, and low-power digital phaselocked loop (PLL) designs. His research interests include transceivers for Bluetooth low energy, low-power/high-performance *LC*-voltage-controlled oscillator (VCO) for ISM/5G applications, and ultra-low-jitter PLLs for 5G cellular and harmonic suppression techniques for the power amplifier.

Dr. Sun serves as a reviewer for IEEE TRANSACTIONS ON MICROWAVE THEORY AND TECHNIQUES, the *Microelectronics Journal* published by Elsevier, and IEEE TRANSACTIONS ON VERY LARGE SCALE INTEGRATION SYSTEMS.

**Bangan Liu** (Member, IEEE) received the B.Eng. degree from Northwestern Polytechnical University, Xi'an, China, in 2011, the M.S. degree from the University of Science and Technology of China, Hefei, China, in 2014, and the Ph.D. degree from the Tokyo Institute of Technology, Tokyo, Japan, in 2019.

He has interned/worked with Apple and Qualcomm. He is currently with NVIDIA, Santa Clara, CA, USA. His research interests include frequency synthesizers, digital-intensive/digitally assisted mixed-signal systems, and RF/mm-Wave circuits.

Dr. Liu serves as a reviewer for the IEEE JOURNAL OF SOLID-STATE CIRCUITS, IEEE TRANSACTIONS ON CIRCUITS AND SYSTEMS—I, and IEEE TRANSACTIONS ON MICROWAVE THEORY AND TECHNIQUES.

**Junjun Qiu** (Member, IEEE) received the B.Sc. degree in electrical and electronic engineering from the East China University of Science and Technology, Shanghai, China, in 2016, and the M.E. and Ph.D. degrees in electrical and electronic engineering from the Tokyo Institute of Technology, Tokyo, Japan, in 2018 and 2022, respectively.

In 2023, she joined the Qualcomm Radio Frequency Integrated Circuit (RFIC) Design Group, where she is currently a Senior Engineer. At Qualcomm, she focuses on frequency synthesizer

for wireless transceivers. She was focusing on fully synthesizable digital baseband circuit design for sub-GHz wireless transceiver system. Her current research interests include high-performance phase-locked loop design and mixed-signal wireless communication system design.

Ms. Qiu was a recipient of the IEEE SSCS Student Travel Grant Award in 2020 and the Predoctoral Achievement Award in 2021 and 2022.

**Dingxin Xu** (Graduate Student Member, IEEE) received the B.Eng. degree from the Southern University of Science and Technology, Shenzhen, China, in 2018, and the M.Eng. degree from the Tokyo Institute of Technology, Tokyo, Japan, in 2020, where he is currently pursuing the Ph.D. degree in electronic engineering.

In the summer of 2023, he was an Intern with the RF/Analog Department, Qualcomm, San Diego, CA, USA, where he was designing frequency synthesizer in advanced technology node. His current research interests include mixed-signal circuit and frequency synthesizer design.

Mr. Xu was a recipient of the Tokyo Tech Advanced Human Resource Development Fellowship for Doctoral Students from 2021 to 2023 and the ISSCC 2023 Student-Research-Preview Poster Award. He has served as a reviewer for IEEE TRANSACTIONS ON CIRCUITS AND SYSTEMS—I (TCAS-I).

Yi Zhang (Graduate Student Member, IEEE) received the B.E. degree in microelectronic science and engineering from the Southern University of Science and Technology (SUSTech), Shenzhen, China, in 2018, and the M.E. degree in electrical and electronic engineering from the Tokyo Institute of Technology, Tokyo, Japan, in 2020, where he is currently pursuing the Ph.D. degree in electrical and electronic engineering.

His research interests include both mixed-signal circuit design for millimeter-wave CMOS phased-

array transceiver and power-efficiency receiver (RX) design for 5G and beyond-5G communication systems.

**Xi Fu** (Member, IEEE) received the B.E. degree (Hons.) from the Dalian University of Technology, Dalian, Liaoning, China, in 2017, and the M.E. and Ph.D. degrees from the Department of Electrical and Electronic Engineering, Tokyo Institute of Technology (Tokyo Tech), Tokyo, Japan, in 2019 and 2022, respectively.

He is currently a Post-Doctoral Researcher at the Tokyo Institute of Technology. His current research interests are CMOS radio frequency (RF)/millimeter-wave/terahertz/analog transceivers,

phased-array transceivers, mixed-signal systems, 5G/6G mobile systems, device modeling, and satellite communication systems.

Dr. Fu was a recipient of the Japanese Government [the Ministry of Education, Culture, Sports, Science, and Technology of Japan (MEXT)] Scholarship, the IEEE Solid-State Circuits Society (SSCS) Predoctoral Achievement Award in 2023, the RFIC Symposium Best Paper Award in 2019, the IEEE International Solid-State Circuits Conference (ISSCC) Student-Research Preview Poster Award in 2022, and the IEEE SSCS Student Travel Grant Award in 2022. He serves as a reviewer for IEEE TRANSACTIONS ON MICROWAVE THEORY AND TECHNIQUES (TMTT), IEEE TRANSACTIONS ON VERY LARGE SCALE INTEGRATION SYSTEMS (TVLSI), the IEEE SOLID-STATE CIRCUITS LETTERS (SSC-L), IEEE TRANSACTIONS ON CIRCUITS AND SYSTEMS—II (TCAS-II), and IEEE TRANSACTIONS ON CIRCUITS AND SYSTEMS—II (TCAS-II).

**Dongwon You** (Member, IEEE) received the B.S. degree in electrical and computer engineering from Ajou University, Suwon, South Korea, in 2017, and the M.S. and Ph.D. degrees in electrical and electronic engineering from the Tokyo Institute of Technology (Tokyo Tech), Tokyo, Japan, in 2019 and 2023, respectively.

He is currently a Post-Doctoral Researcher at the Tokyo Institute of Technology. His current research interests include CMOS RF/millimeter-wave/analog transceiver systems, MIMO, mixed-signal, wireless communication, phased-array system, and satellite communication.

Dr. You was a recipient of the IEEE SSCS Student Travel Grant Award in 2022, the Best Student Paper Award (First Place) at the 2019 IEEE Radio Frequency Integrated Circuits Symposium (RFIC), and the First Place in the IEEE Microwave Theory and Techniques Society MTT-Sat Challenge in 2023. He also serves as a reviewer for the IEEE JOURNAL OF SOLID-STATE CIRCUITS, IEEE TRANSACTIONS ON MICROWAVE THEORY AND TECHNIQUES, and *IEEE Microwave Magazine*.

**Hongye Huang** (Graduate Student Member, IEEE) was born in Guilin, China, in 1994. He received the B.E. degree from the University of Electronic Science and Technology of China, Chengdu, China, in 2016, and the M.E. degree from the Tokyo Institute of Technology, Tokyo, Japan, in 2018, where he is currently pursuing the Ph.D. degree.

His current research interests include mixed-signal integrated circuits and frequency synthesizers.

Mr. Huang was a recipient of the Scholarship from the Watanuki International Scholarship Foundation

in fiscal years 2020 and 2021.

**Waleed Madany** (Graduate Student Member, IEEE) received the B.Sc. and M.Sc. degrees in electrical engineering from Aswan University, Aswan, Egypt, in 2012 and 2017, respectively. He is currently pursuing the Ph.D. degree with the Tokyo Institute of Technology, Tokyo, Japan.

His current research interests include fully synthesizable DPLL for frequency syntheses, clock generation, and digital calibrations for mixed-signal integrated circuits.

Ashbir Aviat Fadila (Graduate Student Member, IEEE) received the B.Sc. degree in electrical engineering from the Institut Teknologi Bandung, Indonesia, in 2015, and the M.E. degree in electrical and electronic engineering from the Tokyo Institute of Technology, Tokyo, Japan, in 2020, where he is currently pursuing the Ph.D. degree.

After graduating, he worked as a Standard Cells Mask Layout Engineer at Marvell Technology, Jakarta, for a year. From 2016 to 2017, he served as a Research Assistant at his alma mater, where

his work focused on developing systems on chip (SoCs) designed for the Internet-of-Things (IoT) applications. His research now revolves around analog-mixed-signal processing, data converters, and the design of synthesizable analog circuits.

Zezheng Liu (Graduate Student Member, IEEE) received the B.Sc. degree from the University of Electronic Science and Technology of China (UESTC), Chengdu, China, in 2019, and the M.E. degree in electrical and electronic engineering from the Tokyo Institute of Technology, Tokyo, Japan, in 2021, where he is currently pursuing the Ph.D. degree.

His research interests include mixed-signal circuit and frequency synthesizer design. ZHANG et al.: TMM DIGITAL QUADRATURE PA BASED ON 1-bit DSM AND HYBRID FIR FILTER

Wenqian Wang (Graduate Student Member, IEEE) was born in Xuancheng, China. He received the B.Eng. degree from the School of Microelectronics, Xidian University, Xi'an, China, in 2019, and the master's degree from the Tokyo Institute of Technology, Tokyo, Japan, in 2021, where he is currently pursuing the Ph.D. degree.

His current research interests include analog and mixed-signal circuits, as well as frequency synthesizers.

Atsushi Shirane (Member, IEEE) received the B.E. degree in electrical and electronic engineering and the M.E. and Ph.D. degrees in electronics and applied physics from the Tokyo Institute of Technology, Tokyo, Japan, in 2010, 2012, and 2015, respectively.

From 2015 to 2017, he was with Toshiba Corporation, Kawasaki, Japan, where he developed an 802.11ax wireless LAN RF transceiver. From 2017 to 2018, he was with Nidec Corporation, Kawasaki, where he researched intelligent motors

with wireless communication. He is currently an Associate Professor with the Laboratory for Future Interdisciplinary Research of Science and Technology, Institute of Innovative Research, Tokyo Institute of Technology. His current research interests include RF CMOS transceivers for the IoT, 5G, satellite communication, and wireless power transfer.

Dr. Shirane has been a member of the Technical Program Committee for IEEE International Solid-State Circuits Conference Student Research Preview since 2019. He is a member of the IEEE Solid-State Circuits Society and the Institute of Electronics, Information, and Communication Engineers (IEICE).

Kenichi Okada (Fellow, IEEE) received the B.E., M.E., and Ph.D. degrees in communications and computer engineering from Kyoto University, Kyoto, Japan, in 1998, 2000, and 2003, respectively.

From 2000 to 2003, he was a Research Fellow with the Japan Society for the Promotion of Science, Kyoto University. In 2003, he joined the Tokyo Institute of Technology, Tokyo, Japan, as an Assistant Professor, where he is currently a Professor of electrical and electronic engineering. He has authored or coauthored more than 500 journal and conference

papers. His current research interests include millimeter-wave and terahertz CMOS wireless transceivers for 20/28/39/60/77/79/100/300 GHz for 5G, WiGig, satellite and future wireless systems, digital PLL, synthesizable PLL, atomic clock, and ultra-low-power wireless transceivers for Bluetooth low-energy, and sub-GHz applications.

Prof. Okada is a member of the Institute of Electronics, Information and Communication Engineers (IEICE), the Information Processing Society of Japan (IPSJ), and the Japan Society of Applied Physics (JSAP). He was a recipient or co-recipient of the Ericsson Young Scientist Award in 2004, the A-SSCC Outstanding Design Award in 2006 and 2011, the ASP-DAC Special Feature Award in 2011, the Best Design Award in 2014 and 2015, the MEXT Young Scientists' Prize in 2011, the JSPS Prize in 2014, the Suematsu Yasuharu Award in 2015, the MEXT Prizes for Science and Technology in 2017, the RFIT Best Paper Award in 2017, the IEICE Best Paper Award in 2018, the RFIC Symposium Best Student Paper Award in 2019, the IEICE Achievement Award in 2019, the DOCOMO Mobile Science Award in 2019, the IEEE/ACM ASP-DAC Prolific Author Award in 2020, the Kenjiro Takayanagi Achievement Award in 2020, the KDDI Foundation Award in 2020, the IEEE CICC Best Paper Award in 2020, and more than 50 other international and domestic awards. He is/was a member of the technical program committees of the IEEE International Solid-State Circuits Conference (ISSCC), the VLSI Circuits Symposium, the European Solid-State Circuits Conference (ESSCIRC), the Radio Frequency Integrated Circuits Symposium (RFIC), and the Asian Solid-State Circuits Conference (A-SSCC). He is/was also a Guest Editor and an Associate Editor of IEEE JOURNAL OF SOLID-STATE CIRCUITS (JSSC), an Associate Editor of IEEE TRANSACTIONS ON MICROWAVE THEORY AND TECHNIQUES (T-MTT), and a Distinguished Lecturer of the IEEE Solid-State Circuits Society (SSCS).

Yuang Xiong (Graduate Student Member, IEEE) received the B.Eng. degree from Beihang University, Beijing, China, in 2019, and the M.Eng. degree from the Tokyo Institute of Technology, Tokyo, Japan, in 2022, where he is currently pursuing the Ph.D. degree in electronic engineering.

He is working on mixed-signal circuit design and current interests include IoT transceivers.