# FlexWatts: A Power- and Workload-Aware Hybrid Power Delivery Network for Energy-Efficient Microprocessors

| Jawad Haj-Yahya <sup>§</sup> | Mohammed Alser <sup>§</sup> |                     |      | Jeremie S. Kim <sup>§</sup>      | Lois Orosa <sup>§</sup> |

|------------------------------|-----------------------------|---------------------|------|----------------------------------|-------------------------|

| Efraim Rotem*                | Avi Mende                   | elson <sup>†‡</sup> | Anup | am Chattopadhyay <sup>‡</sup>    | Onur Mutlu <sup>§</sup> |

| <sup>§</sup> ETH Zürich      | *Intel                      | <sup>†</sup> Techni | on   | <sup>‡</sup> Nanyang Technologic | al University           |

Modern client processors typically use one of three commonlyused power delivery network (PDN) architectures: 1) motherboard voltage regulators (MBVR), 2) integrated voltage regulators (IVR), and 3) low dropout voltage regulators (LDO). We observe that the energy-efficiency of each of these PDNs varies with the processor power (e.g., thermal design power (TDP) and dynamic power-state) and workload characteristics (e.g., workload type and computational intensity). This leads to energyinefficiency and performance loss, as modern client processors operate across a wide spectrum of power consumption and execute a wide variety of workloads.

To address this inefficiency, we propose FlexWatts, a hybrid adaptive PDN for modern client processors whose goal is to provide high energy-efficiency across the processor's wide range of power consumption and workloads. FlexWatts provides high energy-efficiency by intelligently and dynamically allocating PDNs to processor domains depending on the processor's power consumption and workload. FlexWatts is based on three key ideas. First, FlexWatts combines IVRs and LDOs in a novel way to share multiple on-chip and off-chip resources and thus reduce cost, as well as board and die area overheads. This hybrid PDN is allocated for processor domains with a wide power consumption range (e.g., CPU cores and graphics engines) and it dynamically switches between two modes: IVR-Mode and LDO-Mode, depending on the power consumption. Second, for all other processor domains (that have a low and narrow power range, e.g., the IO domain), FlexWatts statically allocates off-chip VRs, which have high energy-efficiency for low and narrow power ranges. Third, FlexWatts introduces a novel prediction algorithm that automatically switches the hybrid PDN to the mode (IVR-Mode or LDO-Mode) that is the most beneficial based on processor power consumption and workload characteristics.

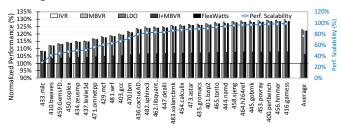

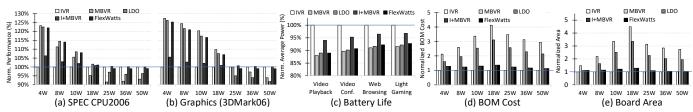

To evaluate the tradeoffs of PDNs, we develop and open-source PDNspot, the first validated architectural PDN model that enables quantitative analysis of PDN metrics. Using PDNspot, we evaluate FlexWatts on a wide variety of SPEC CPU2006, graphics (3DMark06), and battery life (e.g., video playback) workloads against IVR, the state-of-the-art PDN in modern client processors. For a 4W thermal design power (TDP) processor, FlexWatts improves the average performance of the SPEC CPU2006 and 3DMark06 workloads by 22% and 25%, respectively. For battery life workloads, FlexWatts reduces the average power consumption of video playback by 11% across all tested TDPs (4W–50W). FlexWatts has comparable cost and area overhead to IVR. We conclude that FlexWatts provides high energy-efficiency across a modern client processor's wide range of power consumption and wide variety of workloads, with minimal overhead.

# 1. Introduction

Architecting an efficient power delivery network (PDN) for client processors (e.g., tablets, laptops, desktops) is a wellknown challenge that has been hotly debated in industry and academia in recent years. Due to multiple constraints, a modern client processor typically implements only one of three types of commonly-used PDNs: 1) motherboard voltage regulators (MBVR [29, 41, 63, 97]), 2) low dropout voltage regulators (LDO [15, 18, 111, 112, 113, 120]), and 3) integrated voltage regulators (IVR [21, 61, 88, 117]). We find that the energy-efficiency of each of the three different commonly-used PDN types varies differently with the processor power (e.g., thermal design power (TDP<sup>1</sup>) and dynamic power-state) and workload characteristics (e.g., workload type and computational intensity). Particularly, each PDN is designed for energy-efficient operation at a different TDP, power-state, workload type, and workload computational intensity. This leads to energy-inefficiency and performance loss as modern client processors operate across a wide range of power consumption and execute a wide variety of workloads.

Architects of modern client processors typically build a *single* PDN architecture (i.e., MBVR, IVR, or LDO) that supports *all* TDPs of a client processor family for two reasons. First, doing so allows system manufacturers to configure a processor's TDP (known as configurable TDP [5,63, 132] or cTDP) to enable the processor to operate at higher or lower performance levels, depending on the available cooling capacity and desired power consumption. For example, the Intel Skylake processor uses an MBVR PDN [26, 117] for all TDP ranges (from 3*W* [56] to 91*W* [57]) and recent AMD client processors use an LDO PDN [3, 4, 15, 18, 111, 112], while enabling cTDP [56, 57]. Second, it reduces non-recurring engineering (NRE [81]) cost and design complexity to allow competitive product prices and enable meeting of strict time-to-market requirements.

Modern client processors operate across a *wide power range* (i.e., the range of power consumption between under lightload and heavy-load) for two reasons. First, modern workloads have a wide range of computational intensity (leading to between tens of milliwatts of power consumption, e.g., for an idle workload that is in Connected-Standby power-mode [42], to tens of watts on average, e.g., for a workload that activates Turbo Boost [98]). Second, processors must support multiple market segments that have very different TDPs. For example, the recent Intel Skylake processor architecture can scale from nearly 3*W* [56] of TDP (for passively-cooled small systems, e.g., a tablet) up to 91*W* [57] of TDP (for a high-performance

<sup>&</sup>lt;sup>1</sup>As the processor dissipates power, the temperature of the silicon junction  $(T_j)$  increases,  $(T_j)$  should be kept below the maximum junction temperature  $(T_{jmax})$ . Overheating may cause permanent damage to the processor. Hence, every processor has a thermal design power (TDP) limit.

desktop computer). The recent AMD client processors follow similar trends [3, 4, 15, 18, 111, 112].

Based on our empirical evaluations, we find that a single PDN architecture, which supports a wide power range is energy-inefficient. For instance, the IVR PDN is energyinefficient for low-TDP processors (e.g., tablets, convertible laptop-tablets), while the MBVR and the LDO PDNs are energyinefficient for high-TDP processors (e.g., high performance laptops, desktops). We also observe that even if we build a dedicated PDN matching the TDP of the processor, e.g., IVR PDN for high-TDP processors and MBVR or LDO PDN for low-TDP processors, these processors will still suffer from significant energy inefficiency because 1) the IVR PDN is energy-inefficient in high-TDP processors when running a computationally light workload, 2) a low-TDP processor can potentially execute computationally heavy workloads that exceed the TDP, e.g., via Turbo Boost [98], and 3) the TDP of modern client processors can be dynamically configured using cTDP [5, 132].

Various works focus on improving the processor PDN using various techniques (e.g., thermal-aware voltage regulators (VRs) [72], re-configurable PDN [32], VR phase scaling [11], VR efficiency-aware power management [12], on-chip VRs for fast DVFS [53, 73, 137], voltage stacking [33, 90, 142], PDNs for waferscale processors [90], voltage noise reduction [16, 35, 36, 44, 74, 84, 95, 96, 108, 119], voltage noise modeling [141, 143], multiple voltage domains [100, 138], voltage optimizations [115], and adaptive DVFS [22, 91]). These works focus on adapting power management techniques that already exist in modern client processors (such as voltage noise reduction and modeling, power management techniques that optimize VR efficiency, using fast VRs for better DVFS, utilizing on-chip VRs for building multiple voltage domains to improve energy-efficiency), but they do not alleviate the inherent energy inefficiencies of commonly-used PDNs in *client* processors due to operating across a wide range of power and wide variety of workloads.

In this paper, we propose FlexWatts, a power- and workloadaware hybrid adaptive PDN whose goal is to maintain high energy efficiency in a modern client processor throughout the processor's wide spectrum of power and workloads with a low bill of materials (BOM<sup>2</sup> [66]) and board area overhead. FlexWatts is based on three key ideas. First, FlexWatts combines IVRs and LDOs in a novel way to share multiple on-chip and off-chip resources and thus reduce BOM, as well as board and die area overheads. This hybrid PDN is allocated for processor domains with a wide power consumption range (e.g., CPU cores and graphics engines) and it dynamically switches between two modes, IVR-Mode and LDO-Mode, depending on the power consumption. For example, when a domain operates under high power conditions (e.g., high TDP, power-hungry applications), it uses the PDN in IVR-Mode. Otherwise (e.g., low TDP, light-load), it uses the PDN in LDO-Mode. Second, for all other processor domains (that have a low and narrow power range, e.g., the IO domain), FlexWatts statically allocates offchip VRs that have high energy-efficiency for low and narrow power ranges. Third, FlexWatts introduces a new prediction

algorithm that automatically switches the hybrid PDN to the mode (i.e., IVR-Mode or LDO-Mode) that is predicted to be the most beneficial based on processor power consumption and workload characteristics.

To assess the tradeoffs of commonly-used PDNs, and architect a PDN that is highly efficient in the metrics of interest (e.g., energy consumption, performance, board area, BOM), an accurate *architecture-level* quantitative analysis of these metrics is needed. Unfortunately, no model or tool is available to the computer architecture research community for such analysis. To this end, we develop *PDNspot*, a validated architectural open-source PDN framework whose goal is to enable architects to study the tradeoffs of various PDNs. PDNspot provides a versatile framework that enables multidimensional architecture-space exploration of modern processor PDNs. PDNspot evaluates the effect of multiple PDN parameters, TDP, and workloads on the metrics of interest. We open-source PDNspot [104].

Using PDNspot, we evaluate FlexWatts on a wide variety of SPEC CPU2006, graphics (3DMark06), and battery life (e.g., video playback) workloads against IVR [21], the state-of-theart PDN in modern client processors. For a 4*W* TDP processor, FlexWatts improves the average performance of the SPEC CPU2006 and 3DMark06 workloads by 22% and 25%, respectively. For battery life workloads, FlexWatts reduces the average power consumption of video playback by 11% across all tested TDPs (4*W*-50*W*). FlexWatts has comparable BOM and area overhead to IVR.

This paper makes the following major contributions:

- We introduce FlexWatts, a novel adaptive hybrid PDN that maintains high efficiency and high performance in metrics of interest in client processors across a wide spectrum of power consumption and workloads. To our knowledge, FlexWatts is the *first* hybrid PDN to use two types of *onchip* voltage regulators (IVR and LDO) to simultaneously leverage the advantages of both.

- We develop a versatile framework, PDNspot, that enables multi-dimensional architecture-level exploration of modern processor PDNs. To our knowledge, PDNspot is the first tool that can evaluate the effects of multiple PDN parameters, TDP, and workloads characteristics on prominent system metrics such as energy consumption, performance, board area, and bill of materials (BOM). We open-source PDNspot [104].

- We provide a thorough experimental evaluation of the power, performance, area, and BOM of IVR, MBVR, LDO, and FlexWatts PDNs across various processor TDPs and workloads. Our evaluation shows that our new adaptive hybrid PDN, FlexWatts, provides large benefits in metrics of interest (performance, energy, cost, area) with minimal overhead, compared to the state-of-the-art PDN.

#### 2. Background

We provide the necessary background on the architecture of a modern client processor and its power delivery network (PDN), the electrical system that provides supply voltage to the transistors within an integrated circuit via voltage regulators.

<sup>&</sup>lt;sup>2</sup>Given a specific product, a BOM is a list of its immediate components with which it is built and the components' relationships.

We also explain some of the parameters (e.g., tolerance band and load-line) that affect the system-level efficiency of PDNs.

# 2.1. PDNs in Modern Client Processors

**Architecture.** To illustrate the usage of a PDN in modern client processors, we first summarize the architecture of Intel's client processor [8, 20, 21, 83, 101] in Table 1. Similar architectures are widely used for modern processors from various vendors, such as AMD, IBM, and ARM [15, 18, 89, 94, 111, 112, 120].

Table 1: Summary of the processor architecture

| Domain                            | Description                                                   |  |  |

|-----------------------------------|---------------------------------------------------------------|--|--|

| Two CPU Cores                     | Single clock domain to all cores. Clock frequency can         |  |  |

| (Core 0/1)                        | scale from 0.8GHz to 4GHz                                     |  |  |

| Graphics Engines<br>(GFX)         | GFX frequency can scale from 0.1GHz to 1.2GHz                 |  |  |

| Last Level Cache                  | The LLC size scales proportionally to the                     |  |  |

| (LLC)                             | CPU core and graphics engine frequencies                      |  |  |

| System-Agent <sup>3</sup><br>(SA) | The SA includes a memory controller, display controller,      |  |  |

|                                   | IO fabric, and other IPs (e.g., Camera, PCIe, Voice), each of |  |  |

|                                   | which operate at a fixed frequency (not scaled with load)     |  |  |

| Input/Output                      | Includes the processor IOs, such as DDRIO, display            |  |  |

| (IOs)                             | IO, which operate at fixed frequencies                        |  |  |

**Power Delivery Networks.** The Power Delivery Network (PDN) is the electrical system that provides supply voltage to the transistors within an integrated circuit (IC) or domain (e.g., CPU core, graphics engine) in a processor. The objective of a PDN in a processor is to provide a stable desired voltage to each processor domain. Particularly, a PDN should support three distinct capabilities: 1) supply a stable voltage to each processor domain, 2) provide transient current required by a processor domain, and 3) filter out the noise currents injected by a processor domain [64, 116, 123].

A PDN consists of 1) a *power supply* (e.g., power supply unit (PSU) or battery), which provides high voltage (e.g., 7.2–20V) to the motherboard, 2) *voltage regulators* (VRs) (also known as DC–DC converters), used in either one or two stages to reduce the voltage level from the power supply to the desired operational voltage for a domain (typically 0.5–1.1V), 3) a *network of interconnections*, which distributes the voltage from the voltage regulators to the PDN components and processor domains, 4) *decoupling capacitors* distributed on the motherboard, package, and die, which act as reservoirs to store charge and reduce voltage noise from instantaneous current draw, and 5) *powergates* to turn off a processor domain when it is idle. Before discussing the common PDN designs in more detail, we first discuss types of voltage regulators, an essential component in PDNs for converting voltage.

#### 2.2. Voltage Regulators (VRs)

The main objective of a voltage regulator (VR) is to convert the input voltage level to another voltage level. There are multiple types of VRs and each has pros and cons with respect to power conversion efficiency, voltage noise, design complexity and size. In this section, we describe the switching VR (SVR), and the low dropout VR (LDO VR), each of which are key components (on-chip and/or off-chip) in modern client processor PDNs. **Switching Voltage Regulator (SVR).** Modern processors typically use a step-down SVR (i.e., a buck converter [49,73,93]), which converts the input voltage level to a lower voltage level. An SVR consists of an inductor, diode, capacitor, switch, and control modules. Traditionally, SVRs are placed on the *motherboard*. However, recent PDN designs *integrate* SVRs into the chip package and die [21,61,88,117]. The main advantage of an SVR over other types of VRs is its ability to maintain a high power conversion efficiency (typically >80%) even if the output voltage is very different from the input voltage. Unfortunately, SVR has four main disadvantages compared to other VR types: 1) complicated design, 2) high cost, 3) high voltage noise, and 4) it requires a large difference in the input/output voltage levels [68] (i.e., voltage headroom, e.g., a minimum difference of 0.6V for an input voltage of 1.8V).

Low Dropout Voltage Regulator (LDO VR). An LDO VR is a type of linear voltage regulator [64, 79, 85] that consists of a power switch, a differential amplifier (error amplifier), and resistors. The LDO VR has four advantages over an SVR: an LDO VR 1) is immune to switching noise due to the absence of capacitors, 2) has a simpler and smaller design as it does not include large inductors, 3) can regulate the output voltage even when the input voltage level is very close to the output voltage level, 4) even operate in *bypass-mode* [112], in which the input voltage signal is directly connected to the output to avoid voltage regulation, and 5) can have higher efficiency than an SVR when the input voltage level is very close to the output voltage level (e.g., input/output voltage of 1V/0.9V). However, the main disadvantage of the LDO VR is its inefficiency in converting the input voltage if it is very different from the output voltage (e.g., input/output voltage of 1V/0.5V).

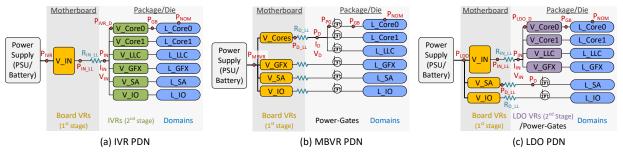

#### 2.3. Power Delivery Network

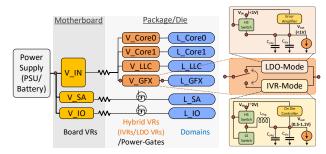

Fig. 1 shows the high-level organization of each of the three commonly-used PDNs in modern client processors: 1) *integrated voltage regulator* (IVR [21,61,88,117]; Fig. 1(a)), 2) *motherboard voltage regulator* (MBVR [29,41,63,97]; Fig. 1(b)), and 3) *low dropout voltage regulator* (LDO VR [15,18,111,112,113,120]; Fig. 1(c)).

Integrated Voltage Regulator (IVR) PDN. The IVR PDN is a state-of-the-art PDN in modern client processors and is used in Intel's 4th, 5th, and 10th generation Core processors [21, 61,88]. The IVR PDN integrates most of the SVR components (i.e., diodes, capacitors, control modules, and switches) into the processor die while some components are placed on the package (e.g., interconnections) and off-chip (e.g., inductors). Since circuit elements in modern processors cannot tolerate the high input voltage of a power supply (7.2-20V) due to their small process technology node size, the IVR PDN regulates voltage in *two-stages*, as illustrated in Fig. 1(a). The first stage of voltage conversion is handled by a single motherboard SVR (i.e., V\_IN VR), which converts input voltage from the power supply unit (PSU) or battery (7.2-20V) to a level typically less than 2V (e.g., 1.8V). The second stage is handled by an integrated SVR (i.e., IVR), which is a sequential buck converter that converts the input voltage (i.e., output of the first stage VR) to the desired voltage level (typically 0.5-1.1V) of a processor domain (e.g., a CPU core). In a processor, multiple IVRs are

<sup>&</sup>lt;sup>3</sup>The System-Agent houses the traditional North Bridge and contains several modules such as the memory and IO controllers [38, 122, 129].

used (e.g., six as shown in Fig. 1(a)) to supply different voltage levels to each processor domain.

The IVR PDN has two main advantages over other PDNs: 1) it enables fast voltage level changes, 2) it reduces a chip's input (i.e., output of the first stage VR into the processor die) current by using a high input voltage level (e.g., 1.8V compared to 0.5-1.1V using a traditional MBVR), thereby reducing  $I^2R$  power losses, and reduces the maximum current (i.e.,  $Icc_{max}$ ) requirement of the first stage VR. However, the IVR PDN has three main disadvantages over other PDNs: 1) low power-conversion efficiency in computationally light workloads due to the two-stage voltage regulation [41], 2) high design complexity as it is normally designed along with the chip, which adds extra design constraints and consumes silicon die area [86], and 3) higher sensitivity to di/dt noise than the MBVR PDN due to a limited amount of decoupling capacitors available on the processor's die [86].

Motherboard Voltage Regulator (MBVR) PDN. The MBVR PDN is the traditional PDN for processors and is used in Intel's 2nd, 3rd, 6th, 7th, 8th and 9th generation Core processors [29, 63, 97, 130, 131]. As shown in Fig. 1(b), the MBVR PDN uses several one-stage motherboard SVRs and multiple on-chip power-gates. An MBVR PDN has four advantages over other PDNs: 1) it decouples the VR design from the processor design, thereby reducing system design complexity, 2) heat generated due to VR power conversion losses is kept outside the processor chip, 3) it enables placing enough decoupling capacitors on motherboard, package and die (due to the long path from processor die to the off-chip VR) to reduce voltage noise, and 4) it is efficient at executing computationally light workloads. However, the MBVR PDN has two major disadvantages: 1) voltage level changes are slow as the VR is far from the load (i.e., processor domain), and 2) computationally-intensive (high current) workloads suffer high  $I^2R$  power losses due to high processor input current and high impedance (load-line) on the path from the board VRs to the processor domains.

**Low Dropout Voltage Regulator (LDO) PDN.** The LDO PDN is used in AMD's recent Zen [15, 111, 112] processors. As shown in Fig. 1(c), the LDO PDN statically allocates two types of VRs to different domains based on their power demands: it allocates 1) one-stage motherboard SVRs (similar to MBVR PDN) to domains with a low and narrow power range (e.g., IO and SA) and 2) two-stage VRs for domains with wide power range (e.g., CPU cores, graphics engines, and LLC). The

first stage is a single motherboard SVR (i.e.,  $V_{\_IN}$  VR) and the second stage is an integrated LDO VR. Multiple LDO VRs are used (e.g., four as shown in Fig. 1(c)) which supply different voltage levels to each of the processor domains. For the two-stage VR, the processor's power management unit adjusts  $V_{\_IN}$  to the maximum voltage required across all domains. For domains that require the same voltage level as the input voltage, the domain's LDO VR operates in *bypass-mode* to avoid voltage regulation by simply connecting the input voltage signal to the output. For other domains that require a lower voltage, the LDO VR adjusts the input voltage by operating in *regulation-mode*. For idle domains, the LDO VR acts as a *power-gate*.

The LDO PDN has three advantages over other PDNs: it 1) requires less board area compared to the MBVR PDN, 2) is simpler than the IVR PDN as the integration of an LDO VR into the die is simpler than that of an SVR, 3) has higher powerconversion efficiency than an IVR PDN when running computationally light workloads. However, the LDO PDN has two main disadvantages compared to other PDNs: 1) low powerconversion efficiency in computationally intensive workloads due to the high processor input current and high impedance (load-line) on the path from the board VRs to the processor domains, and 2) higher design complexity than MBVR as it is designed along with the chip, which adds extra design constraints and complexity to the power management algorithms.

#### 2.4. VR and PDN Parameters

**Power-Conversion Efficiency** ( $\eta$ ). The ratio of the total output power ( $P_{out}$ ) of a VR to the total input power ( $P_{in}$ ) is known as *Efficiency* ( $\eta$ ) as given in Equation 1.

Efficiency =

$$\eta = \frac{P_{out}}{P_{in}} = \frac{P_{out}}{P_{out} + P_{loss}}$$

(1)

For an SVR, power-conversion efficiency is not constant, but rather a function of: 1) the load current and 2) the input and output voltages [12, 34, 39, 40]. The LDO VR power-conversion efficiency,  $\eta_{LDO}$ , is the ratio of the desired output voltage,  $V_{out}$ , to the input voltage,  $V_{in}$ , times the LDO VR *current efficiency* (typically around 99% in a modern LDO VR [50, 79]), thus  $\eta_{LDO} \approx V_{out}/V_{in}$ .

The power-conversion efficiency is also defined for the *entire PDN*, also known as the PDN **end-to-end power-conversion efficiency (ETEE)**. ETEE of a PDN at a given time is the ratio between the total load's nominal power (i.e., the sum of all

Figure 1: The three commonly-used PDNs in client processors. The processor consists of six loads: two CPU cores, a last-levelcache (LLC), graphics engines (GFX), system-agent (SA), and IO. (a) The IVR PDN uses one off-chip VR (V\_IN) and six different on-chip IVRs (V\_Core0/1, V\_LLC, V\_GFX, V\_SA and V\_IO). (b) The MBVR PDN uses four off-chip VRs (V\_Cores, V\_GFX, V\_SA and V\_IO) and six on-chip power-gates. (c) The LDO PDN uses three off-chip VRs (V\_IN, V\_SA and V\_IO), four on-chip LDO VRs (V\_Core0/1, V\_LLC, V\_GFX), and two on-chip power-gates.

loads' nominal power<sup>4</sup>) and the effective power consumed by the main power supply (e.g., battery, PSU).

**VR Tolerance Band (TOB).** The tolerance band (TOB) of a VR [58] is the maximum voltage variation for the VR across temperature, manufacturing variation, and age factors (e.g.,  $V_{TOB} = 25 mV$ ). The standard VR TOB can be sliced into three main categories: controller tolerance, current sense variation, and voltage ripple. The supply voltage is maintained at a higher value than the nominal voltage required by the load, to compensate for TOB voltage variations. This excess voltage due to the TOB leads to wasted power that cannot be utilized by the load.

**Application Ratio (AR).** AR is a term used in power/performance modeling to quantify the *computational intensity* of a workload [34]. AR describes the switching rate of a processor component (e.g., CPU core, graphics engine, IO) for a workload when compared to the highest possible power,  $P_{peak}$ , that can be consumed by the most computationally-intensive workload (i.e., also known as the *power-virus* workload [31, 77, 88]). AR and  $P_{peak}$  can be estimated 1) offline using power modeling tools such as McPAT [77], SYMPO [31] or Intel's Blizzard [9]), and 2) at runtime using *activity sensors* implemented in the processor components [7, 10, 19, 30, 78, 102, 110, 126].

**Load-line.** The load-line or adaptive voltage positioning [59] is a model that describes the voltage and current relationship under a given system impedance ( $R_{LL}$ ). This relationship is defined as:  $V_{cc} = V_{IN} - V_{TOB} - R_{LL} \cdot I_{cc}$  where  $V_{cc}$  and  $I_{cc}$  are the voltage and current at the load, respectively.  $V_{TOB}$  is the tolerance band (TOB) voltage variation and  $V_{IN}$  is the input voltage to the system. From this equation, we can see that the voltage at the load input ( $V_{cc}$ ) decreases when the current of the load ( $I_{cc}$ ) increases (e.g., when running a workload with a high AR). Therefore, to keep the voltage at the load ( $V_{cc}$ ) above a minimum functional voltage under even the most computationally-intensive workload (i.e., *power-virus* [31, 77, 88], for which AR=1), the input voltage ( $V_{IN}$ ) is set to a level that provides enough guardband.

#### 3. PDNspot

We develop PDNspot, a framework that models the three commonly-used PDNs in modern client processors, evaluating multiple metrics of interest (i.e., performance, energy, BOM, and board area). PDNspot provides a versatile framework that enables multi-dimensional architecture-space exploration of modern processor PDNs. PDNspot evaluates the effect of multiple PDN parameters, TDP, and workloads on the metrics of interest. In this section, we present the core models of PDNspot: 1) an end-to-end power-conversion efficiency (ETEE) model for each PDN that we use to assess the average power and current consumption of a PDN, 2) board area and BOM models, and 3) a performance model of the processor that we use to assess each PDN's impact on performance.

# 3.1. End-to-End Power-Conversion Efficiency (ETEE) Modeling

We present three high-level *power models*. Each model takes multiple inputs (main inputs tabulated in Table 2) to calculate the end-to-end power consumption of a domain (shown on the right side of each PDN in Fig. 1), starting from nominal power of each load ( $P_{NOM}$ , in Fig. 1) until the power supply (shown on the left side of each PDN in Fig. 1). The calculations follow the symbols shown in Fig. 1 on each PDN to estimate the total power (i.e.,  $P_{IVR}$ ,  $P_{MBVR}$ , and  $P_{LDO}$ ) consumed by the main power supply (i.e., PSU or battery).

We calculate the end-to-end power-conversion efficiency (ETEE) of each PDN as the ratio of the total input power of the PDN (i.e., the sum of the nominal input power of all loads,  $\sum P_{NOM}$ ) to the total effective power (i.e.,  $P_{IVR}$ ,  $P_{MBVR}$ , and  $P_{LDO}$ ) consumed by the main power supply. We begin by discussing MBVR PDN modeling as it is the simplest PDN.

Table 2: Main parameters used in our PDNspot models

| Parameter                                  | IVR                                                                                                       | MBVR                                | LDO                             |  |  |

|--------------------------------------------|-----------------------------------------------------------------------------------------------------------|-------------------------------------|---------------------------------|--|--|

| Load-line Impedance $R_{LL}$ (m $\Omega$ ) | IN = 1                                                                                                    | Cores, GFX, SA, IO = 2.5, 2.5, 7, 4 | IN, SA, IO = 1.25, 7, 4         |  |  |

| VR Tolerance Band TOB (mV)                 | 18-22                                                                                                     | 18-20                               | 16-18                           |  |  |

| On-chip VR Efficiency $\eta$ (%)           | 81%-88%                                                                                                   | -                                   | $(V_{out}/V_{in}) \cdot 99.1\%$ |  |  |

| Off-chip VR Efficiency $\eta$ (%)          | η <sub>IN,GFX,SA,IO</sub> (V <sub>in</sub> , V <sub>out</sub> , I <sub>out</sub> , power-state) = 72%-93% |                                     |                                 |  |  |

| Leakage Fraction $F_L$ (%)                 | 20%–45% depending on the domain                                                                           |                                     |                                 |  |  |

| Cores Nom. Power P <sub>NOM</sub> (W)      | 0.6 W-30 W for TDP range 4-50 W                                                                           |                                     |                                 |  |  |

| LLC Nom. Power P <sub>NOM</sub> (W)        | 0.5 W - 4 W for TDP range 4-50 W                                                                          |                                     |                                 |  |  |

| GFX Nom. Power P <sub>NOM</sub> (W)        | 0.58W-29.4W for TDP range 4-50W                                                                           |                                     |                                 |  |  |

| PG Impedance $R_{PG}$ (m $\Omega$ )        | $1-2m\Omega$ depending on the domain                                                                      |                                     |                                 |  |  |

MBVR PDN Power Modeling. In order to calculate the total power consumption of the MBVR, denoted by  $(P_{MBVR})$ , we first calculate  $P_{GB}$ , which is the power consumption after applying a voltage guardband on the nominal power  $P_{NOM}$ . This voltage guardband,  $V_{GB}$ , guarantees proper circuit timing across voltage variations ( $V_{TOB}$  explained in Sec. 2.4). The leakage and dynamic power consumption scale differently as voltage increases from  $V_{NOM}$  to  $V_{NOM} + V_{GB}$  (i.e., when nominal voltage,  $V_{NOM}$ , is increased by a voltage guardband,  $V_{GB}$ ). The dynamic power consumption is proportional to the voltage squared (i.e.,  $(\frac{V_{NOM}+V_{GB}}{V_{NOM}})^2$ ), while the leakage power consumption scales exponentially with voltage and depends on several other parameters such as threshold voltage, temperature, and other design and fabrication characteristics [34, 39, 40, 45, 64]. As an approximation, we use a model based on polynomial curve fitting, where leakage power scales polynomially with supply voltage (i.e.,  $(\frac{V_{NOM}+V_{GB}}{V_{NOM}})^{\delta}$ ). We validate our model with measurements on a commercial client processor (Intel Core i7-6600U Processor [55]). Assuming the same temperature, the leakage power scales by the power of  $\delta = \sim 2.8$  proportional to voltage scaling. We assume a leakage fraction  $(F_L)$  of 45% for the graphics domain and 22% for the rest (e.g., cores, LLC, SA) similarly to Rusu *et al.* [103]. Therefore,  $P_{GB}$  can be calculated with Equation 2.

$$P_{GB} = P_{NOM} \cdot \left[ F_L \cdot \left( \frac{V_{NOM} + V_{GB}}{V_{NOM}} \right)^{\delta} + (1 - F_L) \cdot \left( \frac{V_{NOM} + V_{GB}}{V_{NOM}} \right)^2 \right]$$

(2)

For domains with power-gates (e.g.,  $L\_Core0/1$  and  $L\_LLC$  in Fig. 1(b)), there is an additional voltage drop on the power-gate ( $V_{PG}$ , e.g., 10 mV) due to its impedance ( $R_{PG}$ ). The power consumption ( $P_{PG}$  in Fig. 1(b)), due to this increase in the

<sup>&</sup>lt;sup>4</sup>A load's nominal power at a given time is a function of the load's 1) power state (e.g., active vs. idle), 2) activity factor, 3) frequency, 4) nominal voltage, and 5) temperature [34, 39, 40, 45].

supply voltage, is calculated similarly to Equation 2 (i.e., by assigning in the equation:  $V_{PG}$ ,  $P_{GB}$ ,  $(V_{NOM} + V_{GB})$  instead of  $V_{GB}$ ,  $P_{NOM}$ ,  $V_{NOM}$ , respectively).

Next, we need to compensate for the voltage drop on the load-line impedance ( $R_{LL}$ , discussed in Sec. 2.4) by raising the on-board VR output voltage (i.e., applying a voltage guardband). The voltage guardband needs to account for the maximum possible voltage drop, which is attained when the processor consumes the maximum possible power, P<sub>peak</sub>, by running the most computationally-intensive workload, which is also known as a power-virus workload [31, 77, 88]. Next we attain,  $P_D$ , the total power consumption of a group of domains which share the same off-chip VR (e.g., {*Core*0, *Core*1, *LLC*}, {*GFX*}), by summing all  $P_{PG}$  values from each domain,. We use the application ratio (AR, discussed in Sec. 2.4), to obtain  $P_{peak}$  by scaling  $P_D$  using the AR, i.e.,  $P_{peak} = P_D / AR$ . The corresponding calculation for the voltage and power after accounting for the voltage drop on the load-line impedance of each group of domains (i.e.,  $R_{D \ LL}$  in Fig. 1(b)) is shown by Equations 3 and 4, respectively.

$$V_{D\_LL} = V_D + \frac{P_{peak}}{V_D} \cdot R_{D\_LL} \quad (3) \qquad P_{D\_LL} = V_{D\_LL} \cdot I_D = V_{D\_LL} \cdot \frac{P_D}{V_D} \quad (4)$$

The total power,  $P_{MBVR}$ , consumed from the battery/PSU is obtained by summing the effective power of each domain, which can be calculated by dividing the output power of each on-board VR by its power conversion efficiency ( $\eta_D$ ) as shown in Equation 5.

$$P_{MBVR} = \sum \frac{P_{D\_LL}}{\eta_D}$$

(5)

**IVR PDN Power Modeling.** Using the same approach for modeling MBVR PDN power consumption, we calculate the total power of an IVR PDN,  $P_{IVR}$ , consumed from the battery/PSU, as shown in Fig. 1(a). We calculate  $P_{GB}$  by applying a voltage guardband due to the VR tolerance band (i.e., TOB, discussed in Sec. 2.4) using Equation 2.  $P_{IVR_D}$  (in Fig. 1(a)) is the power consumption after accounting for the IVR loss at a specific domain. Given the IVR power conversion efficiency  $\eta_{IVR}$ ,  $P_{IVR_D}$  can be calculated using Equation 6.

$$P_{IVR\_D} = \frac{P_{GB}}{\eta_{IVR}} \tag{6}$$

Next we calculate  $P_{IN}$  (shown in Fig. 1(a)) by summing the power consumed by all domains connected to  $V_{\_IN}$  VR (i.e.,  $P_{IN} = \sum P_{IVR\_D}$ ). Similarly to the MBVR PDN, the voltage ( $V_{IN\_LL}$ ) and power consumption ( $P_{IN\_LL}$ ) after accounting for the voltage drop on the load-line impedance (i.e.,  $R_{IN\_LL}$ ) are calculated with Equations 7 and 8, respectively, whereas  $P_{IN_{peak}} = P_{IN}/AR$ . Finally, we obtain the total power ( $P_{IVR}$ ) consumed from the battery/PSU by dividing the output power (i.e.,  $P_{IN\_LL}$ ) of the  $V_{IN}$  VR by the power conversion efficiency of the  $V_{IN}$  VR (i.e.,  $\eta_{IN}$ ), as shown in Equation 9.

$$V_{IN\_LL} = V_{IN} + \frac{P_{IN_{peak}}}{V_{IN}} \cdot R_{IN\_LL}$$

(7)

$$P_{IN\_LL} = V_{IN\_LL} \cdot \frac{P_{IN}}{V_{IN}} \quad (8) \qquad \qquad P_{IVR} = \frac{P_{IN\_LL}}{\eta_{IN}} \quad (9)$$

**LDO PDN Power Modeling.** Similarly to the other two models,  $P_{GB}$  (shown in Fig. 1(c)) is calculated using Equation 2.

For the four domains with LDO VRs (i.e.,  $L\_Core0/1$ ,  $L\_LLC$  and  $L\_GFX$  domains), we calculate the power of each domain after including the LDO VR power conversion losses, denoted by  $P_{LDO\_D}$  in Fig. 1(c).  $P_{LDO\_D}$  is obtained by dividing the output power of the LDO ( $P_{GB}$ ) by the power conversion efficiency of the LDO ( $\eta_{LDO}$ ) as shown in Equation 11.  $\eta_{LDO}$  is the ratio of the desired output voltage to the input voltage multiplied by the LDO VR current efficiency ( $I_{effi}$ , e.g., 99%), as shown in Equation 10. Next, we obtain the power that each LDO domain consumes from the shared VR ( $V\_IN$ ) using two steps. First, we sum the power of each LDO domain to obtain  $P_{IN}$  (i.e.,  $P_{IN} = \sum P_{LDO\_D}$ ). Second, we calculate the power consumption ( $P_{IN\_LL}$ ) after accounting for the voltage drop on the load-line impedance (i.e.,  $R_{IN\_LL}$ ) using Equations 7 and 8 (similar to the calculations in IVR PDN power modeling).

$$\eta_{LDO} = \frac{V_{OUT}}{V_{IN}} \cdot I_{effi} \qquad (10) \qquad \qquad P_{LDO\_D} = \frac{P_{GB}}{\eta_{LDO}} \qquad (11)$$

For domains that use motherboard VRs (i.e.,  $L\_SA$  and  $L\_IO$ ), we calculate the power ( $P_D\_LL$ ) that each of these domains consumes from the motherboard VRs (i.e.,  $V\_SA$  and  $V\_IO$ ) using Equations 3 and 4 (similar to our calculations in MBVR PDN power modeling). Finally, the total power (i.e.,  $P_{LDO}$ ) that the LDO PDN consumes from the battery/PSU is calculated by summing the power that each motherboard VR consumes from the battery/PSU as shown in Equation 12.

$$P_{LDO} = \frac{P_{IN\_LL}}{\eta_{IN}} + \sum \frac{P_{D\_LL}}{\eta_D}$$

(12)

# 3.2. Board Area and BOM Modeling

The board area and BOM of an off-chip VR are functions of mainly the maximum current ( $Icc_{max}$ ) that the VR can support.  $Icc_{max}$  is the maximum current that the VR must be electrically designed to support. Exceeding the the  $Icc_{max}$  limit can result in irreversible damage to the VR or the processor's chip [34,39, 40, 59, 62, 80, 86, 135, 141]. A higher  $Icc_{max}$  implies a larger VR and higher cost. VR sharing between multiple domains (e.g., the LDO PDN shares  $V\_IN$  VR for cores, LLC, and graphics as shown in Fig. 1(c)) effectively reduces the maximum current required,  $Icc_{max}$ , thereby reducing the area and BOM of the off-chip VR.

To reduce system area and cost, many platforms use a *power* management integrated circuit (PMIC [52, 109, 134]) that incorporates multiple VRs (and other functions) into one integrated circuit. In our model, the VR area and cost are calculated based on the *Icc<sub>max</sub>* requirements for each domain of a PDN. We assume an optimized solution with a PMIC for processors with TDPs up to 18 *W* for all PDNs. Higher-TDP processors typically use a traditional voltage regulator module (VRM [59]) instead of a PMIC due to the high current requirements of these processors [52, 109]. We obtain the actual mapping between the *Icc<sub>max</sub>* and the area/cost directly from *Texas Instruments* VR vendor [118].

#### 3.3. Processor Performance Modeling

To understand the impact of PDN end-to-end powerconversion efficiency (ETEE) on workload *performance* of a client processor, we build a performance model. Our performance model aims to estimate the performance improvement of a CPU- (graphics-) intensive workload when increasing the power-budget allocated to the CPU cores (graphics engines).

We build the performance model of the compute domain (i.e., CPU cores and graphics engines) using empirical measurements on a real system in three steps. First, we run a CPU- (graphics-) intensive workload with high performance-scalability<sup>5</sup>, e.g., 416.gamess of SPEC CPU2006 [114] (3DMark06 [124]), on a real Intel Skylake system, whose specifications are in Table 3. Second, we sweep the frequency of CPU cores (graphics engines) in steps of 100MHz (50MHz), the finest CPU core (graphics engine) frequency granularity that the Skylake architecture supports. Third, we measure the total power consumption of the processor and log the increase in power consumption compared to the measurement done in the previous (i.e, lower) frequency. By doing so, we build power-frequency curves that we use along with the workload's performance-scalability to estimate performance as a function of power.

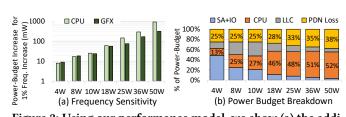

Using our performance model, we plot in Fig. 2(a) the additional power-budget required (y-axis) to increase the clock frequency of a CPU/graphics domain by 1% when running CPU-/graphics-intensive workloads, relative to the baseline frequency of each TDP (x-axis). We observe that, compared to a high-TDP (e.g., 50W) processor, a low-TDP (e.g., 4W) processor requires only a small amount of power (e.g.,  $\sim 9mW$ ) to increase the clock frequency of a CPU/graphics domain by 1%. Fig. 2(b) shows the percentage (y-axis) of the total TDP power-budget (x-axis) that is allocated to the CPU-cores, LLC, IO and SA, and PDN power losses for a CPU-intensive workload (no budget is allocated to graphics in this workload). In each TDP, we use the PDN among three commonly-used PDNs (i.e., MBVR, IVR, LDO) that maximizes PDN power loss (e.g., IVR for 4W and MBVR for 50W), to show the effect of using an unoptimized PDN on different processor domains' power budgets. We find that in a low-TDP processor, a relatively small fraction (e.g., only 13% of a 4W TDP) is allocated to CPU-cores compared to a higher-TDP processor (e.g., about 52% of a 50W TDP), while PDN power loss is 25% or more (i.e., ETEE of 75% or less). If we use a PDN with a higher ETEE for each TDP (e.g., 5% higher ETEE, which translates to 5% lower PDN power loss), we can increase the CPU-cores' power-budget by the spared power on PDN loss (e.g., 5%), thereby increasing the workload's performance. We illustrate the impact of a PDN's ETEE with the following example.

**Impact of PDN ETEE on System Performance.** For a 4W TDP processor, the domains' nominal power consumption (i.e., the sum of each domain's nominal power consumption) is approximately 3W. To find the total processor power consumption, we must account for the PDN power conversion loss by dividing the domains' nominal power consumption by the PDN's ETEE. Therefore, the PDN's ETEE can dictate the amount of remaining power budget for reallocation across the

Figure 2: Using our performance model, we show (a) the additional power-budget required (y-axis) to increase the clock frequency of a CPU/graphics by 1% when running CPU-/graphicsintensive workloads, relative to the baseline frequency of each TDP (x-axis), and (b) percentage (y-axis) of the total TDP power-budget (x-axis) that is allocated to CPU-cores, LLC, IO and SA, and PDN power loss for a CPU-intensive workload.

domains to improve system performance. For example, we can increase the CPU-cores' clock frequency by 1% for each 9mW increase in the CPU-cores' power budget at a 4W TDP (shown in Fig. 2(a)).

To show how even a small difference in ETEE can have a significant impact on system performance, assume we have two PDNs: 1)  $PDN_1$  with  $ETEE_1=75\%$ , and 2)  $PDN_2$  with  $ETEE_2=80\%$ . The total processor power consumption of  $PDN_1$  and  $PDN_2$  are 4W (3W/0.75) and 3.75W (3W/0.8), respectively. According to our model (shown in Fig. 2(a)), the additional 250mW (4W - 3.75W) saved by using  $PDN_2$  (instead of  $PDN_1$ ) could be allocated to increasing the CPU cores' clock frequency by 28%. This would increase the performance of a highly-scalable workload by 28%.

#### **3.4. PDNspot Assumptions and Limitations**

Assumptions. Our PDNspot model makes three main assumptions. First, PDNspot assumes that the system operates within a thermal design power (TDP) limit. The power management unit allocates 1) a power-budget to the SA and IO domains, which have nearly constant power consumption across different TDPs, and 2) the remaining power-budget to the compute domain (cores and graphics). The compute domain power-budget is divided between the cores and the graphics engines based on the running workload (e.g., CPU- versus graphics-intensive workload). Second, PDNspot assumes the same routing resources for all PDNs. Therefore, for PDNs in which multiple domains share a single VR (e.g., IVR, LDO), the routing resources of these domains are combined. Third, PDNspot assumes that all voltage emergencies are handled by both 1) existing decoupling capacitors and 2) existing architectural techniques. This is a reasonable assumption for modern client processors [7, 102, 112].

**Limitations.** Our PDNspot model has two main limitations. First, the model predicts the ETEE based on average values of inputs over a time interval (e.g., during residency in a power state). To provide the dynamic ETEE of a workload (e.g., during multiple system power states within a workload), PDNspot should be run for each time interval separately with the appropriate input for the examined time interval. However, this is not a big limitation since doing so can be automated (e.g., using a script) once data for multiple intervals is collected. Second, the model considers the processor and the off-chip VRs as a single thermal domain (i.e., as sharing the same TDP), which is true for many systems [92]. However, the PDNspot model does not provide the effect of thermals on power and

<sup>&</sup>lt;sup>5</sup>We define performance scalability of a workload with respect to CPU frequency as the performance improvement the workload experiences with unit increase in frequency, as described in [46, 139]. Modern processors predict the performance-scalability of a workload at runtime using performance counters [139]. The performance-scalability metric is used by current power management algorithms, such as Intel's SpeedShift [98] and EARtH [27], which first appeared in the Intel Skylake processor [8].

performance for a system in which the processor and off-chip VRs are in two different thermal domains.

# 4. PDNspot Validation

PDNs in modern client processors have complex designs, and they involve several components integrated on die, package, and board. For example, the IVR design includes multiple components such as 1) buck regulator bridges [21], 2) control modules that generate the pulse width modulation (PWM) signals [49, 73, 93] and activate IVR phases, 3) air core inductors (ACI) [21,49], and 4) Metal Insulator Metal (MIM) capacitors [21]. In addition, several IVR parameters (e.g., thresholds for voltage-regulator power-states) and algorithms (e.g., phaseshedding management) are typically configured and tuned post-silicon. Therefore, modeling these designs with, for example, SPICE [87] is inaccurate and unsuitable for validating our power models. Instead, we obtain the input parameters (shown in Table 2) to PDNspot and validate the three power models of PDNspot with real experimental data from our lab that we collect using two different sets of benchmark traces that are typically used to evaluate client processors.

In this section, we present the 1) experimental setup used to obtain PDNspot model parameters, 2) methodology for obtaining PDNspot model parameters, and 3) PDNspot validation process.

#### 4.1. Experimental Setup

**System Setup.** To measure power and validate our power models, we use two systems with the configurations shown in Table 3. Intel Broadwell and Skylake architectures use IVR [88] and MBVR [26] PDNs, respectively.

| Table 3: | Processor | configurations | and | <b>PDNs</b> |

|----------|-----------|----------------|-----|-------------|

|----------|-----------|----------------|-----|-------------|

|            | 1) i7-5600U [54] Broadwell architecture |  |  |

|------------|-----------------------------------------|--|--|

| Processors | PDN topology: IVR [88]                  |  |  |

|            | 2) i7-6600U [55] Skylake architecture   |  |  |

|            | PDN topology: MBVR [26]                 |  |  |

|            | L3 (LLC) cache: 4 MB.                   |  |  |

|            | Process technology node: 14 nm          |  |  |

| Memory     | DDR3L-1600 MHz [65], non-ECC,           |  |  |

|            | dual-channel, 8 GB capacity             |  |  |

|            | <b>.</b> ,                              |  |  |

**Benchmark Traces.** To obtain the input parameters (shown in Table 2) for our models and validate the models, we use approximately 5000 traces from a wide variety of benchmarks, typically used in evaluating client processors. We use ~3000 single threaded traces, ~1200 multi-programmed traces, and ~750 graphics traces comprising of 1) representative CPU- and graphics-intensive workloads including SPEC CPU2006 [114], Sunspider [128], PhotoShop [2], Illustrator [1] SYSmark [14], HandBrake [133], 3DMark06 [124], Crysis [28], 2) representative battery life workloads such as office productivity workloads (e.g., MobileMark [13]), video conferencing and streaming workloads, and web-browsing workloads [6], and 3) synthetic traces of power-virus [26] for each domain, which can be generated using tools such as McPAT [77], SYMPO [31] or Intel's Blizzard [9].

**Power Measurements.** For the platform *power measurements*, we use a Keysight N6705B DC power analyzer [69] equipped with an N6781A source measurement unit (SMU) [70]. The N6705B (equipped with N6781A) accuracy is around 99.975% [70]. The power analyzer measures and logs the instantaneous power consumption of different device components. Keysight's control and analysis software [69] is used for data visualization and measurement management. For more detail, we refer the reader to the Keysight manual [69] and to our prior work [42].

#### 4.2. Obtaining PDNspot Model Parameters

We describe the process we use to obtain each of the input parameters to PDNspot models. A summary of the main parameters is shown in Table 2.

**VR Efficiency Curves – Input Parameters.** We measure two sets of parameters for 1) *on-chip VR efficiency* (i.e.,  $\eta_{IVR}$  and  $\eta_{LDO}$ ) and 2) *off-chip VR efficiency* (i.e.,  $\eta_{VIN}$ ,  $\eta_{GFX}$ ,  $\eta_{SA}$ , and  $\eta_{IO}$ ). We perform the measurements on our systems across multiple values in the operational range of the 1) VR input voltage (e.g., 7.2V, 9V, 12V for off-chip VR; 1.6V and 1.8V for IVR), 2) VR output voltages (e.g., 0.5V, 0.6V, 0.7V, 1V, 1.8V), and 3) load current.

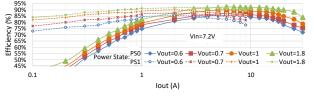

We measure the off-chip VR efficiency ( $\eta_{VIN}$ ,  $\eta_{GFX}$ ,  $\eta_{SA}$ , and  $\eta_{IO}$ ) by 1) connecting the VR input (output) to channel A (B) of the DC power analyzer, which we configure as the power supply (DC electronic load) [71]. This setup enables us to 1) measure the input and output power, and 2) sweep over the ranges of the load current, output voltage and input voltage values, and log the data into the host PC that runs the control and analysis software. We also measure the efficiency for each VR power-state for VRs that support multiple power-states (e.g.,  $V_{IN}$  supports PS0, PS1, PS3 and PS4). Fig. 3 shows the efficiency curves for the off-chip VRs (i.e.,  $V_{COre}$ ,  $V_{GFX}$ ,  $V_{SA}$ ,  $V_{IO}$  and  $V_{IN}$ ) as a function of multiple output voltages, one input voltage (7.2V) and two VR power-states (PS0 and PS1).

Figure 3: Off-chip VR efficiency curves as a function of: 1) output current (Iout, x-axis), 2) output voltage (Vout), 3) VR power-states (only PS0 and PS1 shown), and 4) input voltage (Vin, only 7.2V is shown).

We measure *IVR efficiency* ( $\eta_{IVR}$ ) using the Broadwell processor. Since the IVR is integrated into the processor, it is impossible to disconnect the native load (e.g., cores, graphics engines) and connect a high current load directly to the output of an IVR. Therefore, to measure the IVR efficiency, we operate the processor in a special Design For Test (DFT) mode [21]. We also operate the processor clock tree at varying frequencies to enable a large effective adjustable load current. We measure the current and voltage at the output and input (i.e., output of the  $V_{IN}$  in Fig. 1) of the IVR [21]. Next, we calculate the input and output power and plot the efficiency curves as a function of load current and output voltage. Table 2 (On-chip VR Efficiency) shows the range of the measured IVR efficiency

(81%–88%). The actual curves in PDNspot plot the efficiency as a function of input voltage, output voltage and output current.

We measure the *LDO VR efficiency* ( $\eta_{LDO}$ ) in two steps. First, since the LDO VR is not implemented in our experimental systems, we emulate the LDO VR static behavior using the power-gates that exist in the MBVR PDN of the Skylake processor, a technique<sup>6</sup> which is used by Intel [79] to implement an LDO VR. Second, we measure the input and output power of the LDO VR under varying load current, input and output voltages and plot the efficiency curves. The LDO VR efficiency is the ratio between the output and the input voltage times the ratio between input and output current (also known as current efficiency), i.e.,  $\eta_{LDO} = (V_{OUT}/V_{IN}) \cdot (I_{OUT}/I_{IN})$ . Our measurements show that the current efficiency, i.e.,  $I_{OUT}/I_{IN}$ , is more than 99% as tabulated in Table 2.

**Nominal Power of Domains – Input Parameter.** We measure the *nominal power* ( $P_{NOM}$ ) input parameter of each domain (i.e., cores, LLC, graphics, SA, and IO) directly on the Skylake system when running traces of single threaded, multi-threaded and graphics workloads. We log the measured power of each trace and its application ratio (i.e., AR, discussed in Sec. 2.4).

**Other Input Parameters**. We measure the *Load-line impedance* ( $R_{LL}$ ) from a domain's input to the output of the offchip VRs for each domain directly on Skylake and Broadwell Systems. We measure *peak-power* (i.e.,  $P_{peak}$ ) when running power-virus traces. We estimate *leakage-power fraction* ( $F_L$ ) using a post-silicon technique, thermal conditioning [23,25,47], by 1) increasing the processor temperature while running a load with constant voltage and frequency (i.e., constant dynamic power), 2) measuring the associated changes in power consumption, and 3) extrapolating the domain's power fraction which is affected by temperature, as the leakage power depends exponentially on temperature whereas the dynamic power is not affected by temperature [34, 39, 40, 64].

#### 4.3. PDNspot Validation

We validate PDNspot by comparing the predicted ETEE obtained from each PDNspot model (i.e., IVR, MBVR, and LDO) with the ETEE measurements on *real* systems.

<sup>6</sup>By controlling the number of the conducting power-gate transistors and their gate voltages, the power-gate behaves like an LDO VR. The actual LDO VR implementation has additional circuitry (e.g., to handle load transient response, digital control of the LDO VR output). To validate PDNspot, we use as reference the total power consumption of real Intel processors (Broadwell, Skylake, and Skylake with emulated LDO PDN) *measured* from the main power supply (battery/PSU) for each of the PDNs ( $P_{IVR}$ ,  $P_{MBVR}$ , and  $P_{LDO}$ ). We use PDNspot to obtain the *predicted* power consumption of each PDN. We use a subset (200) of the benchmark traces (single-thread, multi-programmed, and graphics described in Sec. 4.1) that have various application ratios (AR). We calculate the measured (predicted) ETEE of each PDN by dividing the total nominal power consumption (i.e., PDN output power) by the measured (predicted) total power consumption (i.e., PDN input power). Finally, we calculate the accuracy of PDNspot by comparing the measured ETEE to the predicted ETEE of each PDN.

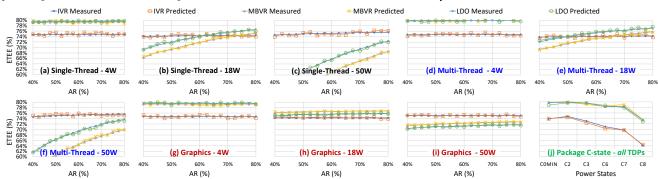

We find that our three IVR, MBVR and LDO PDN models in PDNspot have an average (min/max) *accuracy* of 99.1% (98.7%/99.3%), 99.4% (98.9%/99.7%), and 99.2% (98.6%/99.6%), respectively, across all our 200 workloads. Fig. 4(a–i) shows the validation results (measured vs. predicted ETEEs) for 4*W*, 18*W*, 50*W* TDPs when running single-threaded, multi-programmed, and graphics traces with an AR between 40% to 80%. Fig. 4(j) shows the results for the battery life related power-states: C0 with minimum frequency ( $C0_{MIN}$ ) and package C-states (C2/3/6/7/8) [34, 39, 40].

# 5. Motivation: PDN Inefficiencies in Client Processors

This section makes three key empirical observations about the three most commonly-used PDN architectures (i.e., IVR [21, 61, 88], MBVR [29, 63, 97], LDO [15, 18, 111, 112, 113, 120]) in modern high-end client processors to motivate the need for a hybrid and adaptive PDN that leverages the advantages of each one of the three PDN architectures.

We use our validated model, PDNspot, to evaluate the efficiency of the three PDNs. We estimate the off-chip current consumption, ETEE with breakdown into multiple sources of power-conversion losses, and average power consumption of a processor using each of the three PDNs. We use a total of 300 CPU-intensive, graphics-intensive, and video playback workload traces to evaluate each PDN.

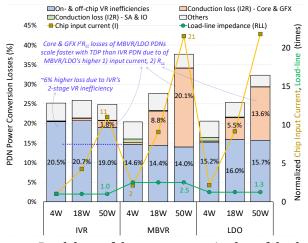

Based on our evaluation results shown in Figures 4 and 5, we make three key observations.

Figure 4: PDNspot validation results. (a)-(i) End-to-End power-conversion efficiency (ETEE) for single-threaded, multi-threaded and graphics traces at 4W, 18W and 50W TDP with varying application ratios (AR). (j) shows the results for battery life related power-state: C0 with minimum frequency (C0MIN) and package C-states (C2/3/6/7/8) [34, 39, 40].

Figure 5: Breakdown of the power conversion loss of the three PDNs when running a CPU-intensive workload (AR=56%) at 4W, 18W, and 50W TDPs. Conduction loss ( $I^2R$ ) and on-chip & off-chip VR infficiencies are the most prominent losses. Normalized (to IVR PDN) chip input current (I, i.e., from off-chip VRs) and load-line impedance ( $R_{LL}$ ) are shown as line plots.

**Observation 1.** We observe that when executing CPU- and graphics-intensive workloads, the IVR PDN has a *lower* ETEE at the 4*W* TDP (Figures 4.a,d,g) and a *higher* ETEE at the 50*W* TDP (Figures 4.c,f,i) compared to MBVR and LDO PDNs across the entire range of tested ARs. The ETEE *crossover point*, at which the IVR ETEE becomes higher than the MBVR/LDO ETEE, exists at some TDP between 4*W* and 50*W*.

Fig. 5 provides more insight into this observation with breakdowns of PDN power conversion loss. We find that at 4W TDP, the dominating contributor to the PDN power conversion loss are the on-chip and off-chip VR inefficiencies. At 4W TDP, the IVR PDN has a lower ETEE than the MBVR and LDO PDNs due to the higher power conversion inefficiencies of the IVR PDN's on-chip and off-chip VRs. At a 50W TDP, we find that MBVR and LDO PDNs have lower ETEEs due to their high  $I^2 R$ loss in core and graphics domains. The high  $I^2R$  loss is due to: 1) a  $\sim 2 \times$  higher chip input current in the MBVR and LDO PDNs compared to the IVR PDN<sup>7</sup>, and 2) a  $2.5 \times / 1.3 \times$  higher load-line impedance  $(R_{LL})$  in the MBVR/LDO PDNs compared to the IVR PDN<sup>8</sup>. We conclude that the MBVR and LDO PDNs are more efficient at a low TDP (e.g., 4W) compared to the IVR PDN, while the IVR PDN is more efficient at a high TDP (e.g., 50W).

**Observation 2.** We observe that the PDN ETEE is affected not only by the TDP (as discussed in Observation 1) but also by the workload's Application Ratio (AR) and the workload type, i.e., single-threaded, multi-threaded, and graphics.

Fig. 4(a–i) shows that the MBVR and LDO PDN ETEEs increases with AR, which is most pronounced at 18W and 50 W TDPs. This phenomenon is due to the load-line (described on Sec. 2), which results in a lower voltage-guardband when running workloads with higher ARs.

Fig. 4(b,e,h) show that the single-thread, multi-thread, and graphics workloads (all at the same TDP of 18W) have different ETEE curves. For example, for the graphics workload in Fig. 4(h), the IVR PDN is less efficient than the other two PDNs for the entire AR range (with a crossover point around 21W TDP, not shown in Fig. 4, at which the IVR ETEE becomes higher than the MBVR/LDO ETEE), while the other two workloads have crossover points at different ARs within the 18W TDP.

Fig. 4(a-f) shows that the LDO ETEE is higher than the MBVR ETEE for CPU-intensive (single- and multi-threaded) workloads, but is lower than the MBVR ETEE for graphicsintensive workloads. Note that the LDO inefficiency is more dominant in graphics workloads, due to the high voltage difference between the core and graphics domains because in graphics-intensive workloads, the graphics-engine runs at relatively high frequencies (and voltages) while cores are kept at low frequencies (and voltages). Therefore, the LDO PDN 1) sets the off-chip (i.e., first stage) VR voltage to the high voltage level required by the graphics-engines (e.g., 0.9V) while activating the graphics-engines' on-chip LDO (i.e., second-stage) VR in bypass-mode, and 2) uses the core's on-chip LDO (i.e., second-stage) VR to regulate the voltage down to the low voltage level required by the core (e.g., 0.5V). Doing so, results in very low power conversion efficiency of the core's LDO VR (e.g.,  $\sim 0.5/0.9 = 55\%$ , as discussed in Sec. 2.2), thereby reducing the ETEE of the LDO PDN.

We conclude that, in addition to the TDP, the AR and workload type have significant effects on each PDN's ETEE. Particularly, lowering the workload's AR degrades the ETEE of MBVR and LDO PDNs due to load-line effect, while using graphics-intensive workloads reduce the LDO ETEE compared to CPU-intensive workloads due to the high voltage requirement difference between the core and graphics domains.

**Observation 3.** We observe that the ETEE of the IVR PDN is significantly lower than that of MBVR and LDO PDNs for computationally light workloads (e.g., video playback, web browsing, office productivity applications [6, 13, 14]) and low-power states across *all* TDPs. Fig. 4(j) shows the ETEE of the three PDNs in 1)  $C0_{MIN}$ , an active power-state in which the core and graphics domains operate at their *lowest* frequencies, and 2) package C-states (C2, C3, C6, C7, and C8 [34,39,40]), low power-states of the processor. The processor uses these power-states, for *all* TDPs, to reduce energy consumption (thereby increasing battery life of battery-powered devices) when the processor runs a light (i.e., low computational intensity) workload or once the processor is partially/fully idle. We explain the effects of ETEE in these power-states on battery life using a video playback workload example.

The video playback [6] workload is a computationally *light* workload that operates in three main power-states during each video-frame. First, a  $C0_{MIN}$  power-state, which consumes  $P_{C0_{MIN}}=2.5W$  nominal power for  $R_{C0_{MIN}}=10\%$  ( $R_{C0_{MIN}}$  is the residency of power state  $C0_{MIN}$  in terms of the fraction of execution time) of the frame's time. In this state, the cores and graphics engines prepare a video-frame and store it in main memory. Second, a C2 power-state, which consumes  $P_{C2}=1.2W$  nominal power for  $R_{C2}=5\%$  of the frame's time. The cores and graphics engines are idle (power-gated) in this state.

$<sup>^7{\</sup>rm The~IVR~PDN}$  reduces the chip input current because it uses high input voltage from the first-stage VR into the chip (Sec. 2).

$<sup>^{8}</sup>$  The IVR and LDO PDNs have lower  $R_{LL}$  compared to MBVR because both IVR and LDO PDNs share routing resources from external VRs into the chip's package and die.

In C2, the display-controller fetches part of the frame from main memory into a local buffer inside the display controller. Third, a C8 power-state, which consumes  $P_{C8}=0.13W$  nominal power for  $R_{C8}$ =85% of the frame's time. In C8, the display controller reads frame data from its local buffer and displays it on the display panel, while the rest of the processor is idle (e.g., main memory is in self-refresh). We calculate the average power of the video playback workload by summing the fractional power of each power-state taking into account the ETEE in each state (denoted by  $\eta_{C0_{MIN},2,8}$  ). Hence, the average power is given by:  $P_{C0_{MIN}} \cdot R_{C0_{MIN}} / \eta_{C0_{MIN}} + P_{C2} \cdot R_{C2} / \eta_{C2} + P_{C8} \cdot R_{C8} / \eta_{C8}$ . The video playback average-power results (shown in Fig. 8(c)) show that MBVR and LDO PDNs have 12% and 11% lower average power, respectively, than the IVR PDN. We conclude that the IVR PDN is energy-inefficient for computationally-light workloads, which negatively impacts both energy consumption and battery life.

**Summary.** We conclude that there is no single PDN for modern client processors that maintains a high ETEE across all TDPs, workload types and application ratios (ARs). These observations motivate us to build a *hybrid* and *adaptive* PDN that utilizes the advantages of each one of the three PDN architectures, as we describe in Sec. 6.

#### 6. FlexWatts

We present *FlexWatts*, a hybrid adaptive PDN for modern processors that maintains a high ETEE for the wide power consumption range and workload diversity of client processors. FlexWatts is based on three key ideas. First, it combines IVRs and LDOs in a novel way to share multiple on-chip and off-chip resources and thus reduce BOM, as well as board and die area overheads, as illustrated in Fig. 6. This hybrid PDN is allocated for processor domains with a wide power consumption range (e.g., CPU cores and graphics engines) and it dynamically switches between two modes, IVR-Mode and LD0-Mode, based on the efficiency of each mode, using a special power-management flow. Second, FlexWatts statically allocates an off-chip VR to each system domain with a low and narrow power consumption range (i.e., SA and IO domains). This is because unlike in compute domains, the power consumption of the system-agent (SA) and IO domains does not significantly scale with TDP (as shown earlier in Fig. 2(b)) or workload's AR. Thus, it is more energy-efficient to place each of them on a dedicated off-chip VR compared to using an on-chip VR<sup>9</sup>. Third, FlexWatts introduces a new prediction algorithm that automatically determines which PDN mode (IVR-Mode or LDO-Mode) would be the most beneficial based on system and workload characteristics. For example, FlexWatts can operate in LDO-Mode (IVR-Mode) when the processor runs a light (heavy) workload such as video playback (Turbo Boost), or when the processor operates at low (high) TDP such as 4W(50W). FlexWatts uses a runtime ETEE prediction algorithm to select the operation mode (i.e., LDO-Mode or IVR-Mode) that maximizes ETEE.

**Hybrid PDN and Resource Sharing.** We build the FlexWatts PDN by modifying a baseline IVR PDN, shown in Fig. 1(a), in

Figure 6: Our hybrid adaptive PDN (FlexWatts). FlexWatts uses an off-chip VR to each system domain with a low and narrow power consumption range (i.e., SA and IO domains). For system domains with a wide power consumption range (e.g., CPU cores and graphics engines), FlexWatts allocates a hybrid PDN. This hybrid PDN can dynamically switch between two modes, IVR-Mode and LD0-Mode, based on the expected ETEE benefits of each mode for the current workload and power consumption. The hybrid PDN shares between IVR and LDO modes 1) on-chip resources such as the high-side (HS) NMOS power switch in the IVR PDN as illustrated on the right side, and 2) off-chip VRs (V\_IN).

two ways. First, we replace the two on-chip IVRs of the SA and IO domains (i.e., V\_SA and V\_IO IVRs) with two off-chip VRs and two on-chip power-gates, as illustrated in Fig. 6. Second, we implement hybrid VRs, which extend each of the remaining IVRs (i.e., V\_Core0/1, V\_LLC and V\_GFX IVRs in Fig. 1(a)) by implementing an LDO VR using the existing resources of the IVR, as illustrated in Fig. 6 (right side). By doing so, we enable a *hybrid PDN* that has two modes of operation, IVR-Mode and LDO-Mode, with low cost and low area overhead. As illustrated in Fig. 6, each hybrid VR shares between the two modes 1) on chip resources such as the high-side (HS) NMOS power switch [21], and decoupling capacitors (both on package and on die) of the baseline on-chip IVR, and 2) off-chip VRs (i.e., *V\_IN*). We use the HS power-switch to implement the LDO VR, similar to Luria et al. [79], a work carried out by Intel that utilizes the power-gate's power-switch to implement an LDO VR. This architecture enables both PDN modes to share routing resources and the power grid across board, package, and die during operation, as illustrated in Fig. 6.

**Voltage Noise-Free Mode-Switching.** FlexWatts modeswitching transitions the hybrid PDN between two modes (IVR-Mode and LD0-Mode). Carrying out the mode-switching while the compute domains are active may introduce *voltage noise* because the two modes have very different operation principles. In IVR-Mode, the off-chip VR ( $V_{\_IN}$ ) is set to a relatively high-voltage (e.g., 1.8V) and the on-chip IVRs regulate the voltage to the level the domain needs (e.g., 0.6V-1.1V). In LD0-Mode,  $V_{\_IN}$  voltage is set to the *maximum* voltage required by all domains (e.g., 0.6V-1.1V) and the on-chip LDOs regulate this maximum voltage to the level the domain needs. Therefore, the mode-switching should configure the on-chip and off-chip VRs and change their voltage levels while transitioning from one mode to the other.

To prevent any *voltage noise* during mode-switching, FlexWatts performs mode-switching while the compute domains are *idle*. To do so, we 1) place the processor in an idle power-state for a short period, 2) configure the hybrid PDN and update the on-chip and off-chip VR levels, and 3) exit the idle

<sup>&</sup>lt;sup>9</sup>AMD uses the same strategy for their LDO PDNs [112] (Fig. 1(c))

power-state and resume the processor with the new PDN mode. To this end, we utilize a power-management flow that places the processor into the idle power-state, (which exists in most modern processors [26,34,39,40,42,43,48,51,121]), in which the cores, LLC, and graphics units are turned off after their contexts are saved into a dedicated SRAM. We leverage the C6 package C-state power management firmware flow [42] to implement FlexWatts's mode-switching transition flow. FlexWatts takes the following three steps to switch between two PDN modes.

First, the power management unit (PMU) places the system into the package C6 idle power state during which the PMU saves the context<sup>10</sup> of the hybrid PDN domains (i.e., the CPU cores, LLC, and graphics) and turns off their clock and voltage. Second, the PMU performs the actual mode switching actions of the hybrid PDN by 1) adjusting the  $V_{IN}$  VR voltage to a level suitable for the new mode (i.e., 1.8V for IVR-Mode, or 0.6V-1.1V for LD0-Mode), and 2) configuring the hybrid VRs to operate in the new mode (as illustrated in Fig. 6). Third, the PMU exits the package C6 idle power-state and switches to the active state. Doing so allows the processor to resume execution while the hybrid PDN domains use the new PDN mode.

**Runtime PDN Mode-Prediction Algorithm.** So far, we explained how to switch between two PDN modes (i.e., modeswitching flow) without describing *when* to switch. FlexWatts relies on our new runtime mode-prediction algorithm whose goal is to predict which PDN mode, among the two modes, IVR-Mode and LD0-Mode, provides the best end-to-end powerconversion efficiency (ETEE).

As shown in Fig. 4, ETEE is a function of 1) the AR and the workload type (i.e., single-thread, multi-thread, and graphics), and 2) the TDP and the power-state of the system. ETEE depends on the AR due to the load-line effect (discussed in Sec. 2.4) and shown in Equation 3. The workload type affects ETEE because each of the three workload types stresses the underlying power delivery network differently, as explained in Sec. 3.1.

Algorithm 1 depicts our mode prediction algorithm. The *key* idea of our algorithm is two-fold. First, we store two sets of ETEE curves inside the PMU firmware, one set for the IVR PDN and the other set for the LDO PDN. A PDN ETEE curve set is a multidimensional table<sup>11</sup> that includes an ETEE curve corresponding to a TDP for each workload type (i.e., three curves for each TDP point). Each ETEE curve stores the ETEE values as a function of the AR (as shown in Fig. 4(a-i)). We also include one ETEE curve for power states (as shown in Fig. 4(j)). Second, for every *evaluation interval* (e.g., 10ms), we estimate each of the algorithm's input parameters (i.e., TDP, AR, workload type, and power-state). We use the estimated parameters to access the corresponding ETEE curve to obtain the ETEE values for both IVR-mode and LDO-mode. The algorithm chooses the mode that maximizes the ETEE.

Next, we explain how we estimate the inputs to our algorithm (i.e., TDP, AR, workload type, and power-state) at runtime.

| Algorithm | 1 | FlexWatts | Mode | Pred | liction | A | lgorit | hm |

|-----------|---|-----------|------|------|---------|---|--------|----|

|-----------|---|-----------|------|------|---------|---|--------|----|

- 1: **procedure** Determine\_FlexWatts\_Mode

- 2: Input: TDP, AR, WL\_TYPE, PS /\*power-state\*/

- 3: **Output**: PDN\_Mode (IVR-Mode or LDO-Mode)

- 4: IVR\_ETEE = estimate\_IVR\_ETEE (TDP,AR,WL\_TYPE,PS)

- 5: LDO\_ETEE = estimate\_LDO\_ETEE (TDP,AR,WL\_TYPE,PS)

- 6: **if**  $IVR\_ETEE \ge LDO\_ETEE$

- 7: return IVR-Mode

- 8: else return LDO-Mode

- 9: end procedure

**Runtime Estimation of the Algorithm Inputs.** The PMU of a modern processor uses the TDP, AR, workload-type, and power-state in multiple power management algorithms such as 1) power-budget management (PBM) algorithm [24, 26, 101], 2) Turbo Boost algorithm [26, 98, 101], and 3) system maximum current protection [7, 102].

The runtime-configured TDP value is available to the PMU [5, 132]. To estimate the AR, the PMU uses activity sensors [7, 10, 19, 30, 78, 102, 110, 126] that are implemented in multiple domains of the Intel Skylake processor [19, 26, 102, 110]. These activity sensors estimate each domain's activity using internal events in each domain, such as active execution ports in the core, memory stalls, type of instructions being executed (e.g., scalar, vector instructions of 128-bits/256-bits/512-bits). A dedicated weight is associated with each event, and the weighted sum of the events in a domain is periodically (e.g., every millisecond) sent to the PMU. The weights of the activity sensors are calibrated post-silicon to provide a proxy of the AR.

The PMU estimates the *workload-type* (WL\_TYPE) based on the power-state (i.e., active/idle) of the cores and graphics engines. For example, if the graphics engines are active, then the workload-type is set to graphics, while if more than one core is active and the graphics engines are idle, then it is set to multi-threaded.

The *power-state*, i.e., package power-state, of the processor is known to PMU firmware as the PMU carries out the transitions from one package C-state to another [34, 39, 40].

**FlexWatts Overhead.** We estimate the latency of our FlexWatts *mode switching* flow with techniques used by previous works that estimate the package C-state latencies [105,106]. We find that 1) placing the processor into package C6 power state takes  $45\mu s$  (without voltage changes), 2) adjusting the on-chip and off-chip VR voltage levels (assuming a latency of  $\leq 2\mu s$  for on-chip VRs [21,79], and a slew rate of 50  $mV/\mu s$  [60] for off-chip VRs) takes  $19\mu s$ , and 3) exiting the C6 power state takes about  $30\mu s$ . Hence, the overall flow takes nearly  $94\mu s$ . It should be noted that the DVFS (P-state) latency on Intel processor's internal state, which shows that the FlexWatts flow latency is within an acceptable range.

The *area overhead* of FlexWatts over the IVR PDN is minimal. The additional area required to implement the LDO mode using the IVR resources (i.e., the high-side NMOS power switch) is around  $0.041 mm^2$  [79] at 14nm process technology node. This corresponds to only 0.04% and 0.03% of the Intel dual and quad core client die sizes [129], respectively.