# Morpheus: Extending the Last Level Cache Capacity in GPU Systems Using Idle GPU Core Resources

\*Sina Darabi $^\dagger$  \*Mohammad Sadrosadati $^\S$  Joël Lindegger $^\S$  Negar Akbarzadeh $^\dagger$  Mohammad Hosseini $^\sharp$  Jisung Park $^\S \nabla$  Juan Gómez-Luna $^\S$  Hamid Sarbazi-Azad $^{\dagger \ddagger}$  Onur Mutlu $^\S$

<sup>†</sup>Sharif University of Technology §ETH Zürich <sup>‡</sup>Institute for Research in Fundamental Sciences (IPM) <sup>∇</sup>POSTECH\*

Graphics Processing Units (GPUs) are widely-used accelerators for data-parallel applications. In many GPU applications, GPU memory bandwidth bottlenecks performance, causing underutilization of GPU cores. Hence, disabling many cores does not affect the performance of memory-bound workloads. While simply power-gating unused GPU cores would save energy, prior works attempt to better utilize GPU cores for other applications (ideally compute-bound), which increases the GPU's total throughput.

In this paper, we introduce Morpheus, a new hardware/software co-designed technique to boost the performance of memory-bound applications. The key idea of Morpheus is to exploit unused core resources to extend the GPU last level cache (LLC) capacity. In Morpheus, each GPU core has two execution modes: compute mode and cache mode. Cores in compute mode operate conventionally and run application threads. However, for the cores in cache mode, Morpheus invokes a software helper kernel that uses the cores' on-chip memories (i.e., register file, shared memory, and L1) in a way that extends the LLC capacity for a running memory-bound workload. Morpheus adds a controller to the GPU hardware to forward LLC requests to either the conventional LLC (managed by hardware) or the extended LLC (managed by the helper kernel). Our experimental results show that Morpheus improves the performance and energy efficiency of a baseline GPU architecture by an average of 39% and 58%, respectively, across several memory-bound workloads. Morpheus' performance is within 3% of a GPU design that has a quadruple-sized conventional LLC. Morpheus can thus contribute to reducing the hardware dedicated to a conventional LLC by exploiting idle cores' on-chip memory resources as additional cache capacity.

# 1. Introduction

Graphics Processing Units (GPUs) are widely-used accelerators, especially for data-parallel applications with high arithmetic intensity (i.e., arithmetic instructions executed per byte accessed from memory). GPUs rely on managing execution resources for a large number of Single-Program-Multiple-Data (SPMD) threads to exploit this arithmetic intensity and overlap the long memory access latencies with computation [1-3].

Unfortunately, the maximum performance of a GPU is often limited by the available memory bandwidth [4], causing con-

siderable underutilization of GPU cores, i.e., GPU cores are frequently idle (waiting for memory accesses) during application execution time. This is the case for many important generalpurpose GPU applications, such as kmeans [5], mri-gri [6], and cfd [5], which are memory-bound in nature due to their low arithmetic intensity [5, 6]. As a result, we do not need to use all available GPU cores to saturate the performance of these applications. To demonstrate this, we experimentally study (using an NVIDIA RTX 3080 GPU [7] and Accel-Sim [8]) the performance of 14 memory-bound applications as we scale the number of GPU cores. Our experiments reveal that, on average across the 14 applications, only 56% of the GPU cores are enough to saturate performance (see §3 for more details). Hence, the remaining 44% of the GPU cores, on average, can remain unused (i.e., no threads scheduled onto them) without hurting performance of memory-bound applications.

Several prior works (e.g., [9-18]) make similar observations and propose to have *only* a *subset* of the available GPU cores execute memory-bound application threads, and leverage the remaining GPU cores in one of three ways: (1) *power-gating* these cores to save energy [9], (2) using them for *redundant execution* of the *already running* memory-bound application for better reliability [10, 11], and (3) *co-scheduling* additional *compute-bound* applications to these cores to increase GPU's total throughput [12-18]. In contrast, **our goal** is to boost the performance of a memory-bound application using a number of GPU cores that are not useful for executing application threads.

To this end, we propose *Morpheus*. <sup>1</sup> The key idea of Morpheus is to reserve a number of GPU cores to use their on-chip memory (i.e., register files, shared memory, and L1 cache) as an extension of the shared last level cache (LLC, e.g., the shared L2 cache in NVIDIA GPUs). Doing so can improve the performance of memory-bound applications due to two main reasons. First, a larger LLC reduces the number of off-chip memory accesses, thereby enabling more threads to run effectively since the system is not memory bandwidth bottlenecked any more. Second, a larger LLC reduces memory access latency, which can improve performance.

Morpheus introduces two execution modes (compute and

<sup>\*</sup>Sina Darabi and Mohammad Sadrosadati are co-primary authors.

<sup>&</sup>lt;sup>1</sup> "Morpheus" because we dynamically morph, parts of GPU hardware (in a logical sense) to meet memory-bound applications' needs.

cache) for every GPU core. A core in compute mode behaves like a regular core in conventional GPUs, i.e., it executes application threads. A core in cache mode lends its on-chip memory space to extend the effective shared LLC size via a hardware/software co-designed technique. A GPU core in cache mode runs a software helper kernel, called the extended LLC kernel, that stores the extended LLC tag/data arrays inside the GPU core's local register file, shared memory, and L1 cache. We add a hardware controller, called the *Morpheus controller*, to support access to the extended LLC. The Morpheus controller performs three main tasks: it (1) forwards each LLC request to either the conventional LLC or the extended LLC, depending on the requested memory address (i.e., LLC set number), (2) tracks outstanding extended LLC requests, and (3) predicts the outcome of an extended LLC lookup (hit/miss), so that it forwards *only* the requests that are predicted to be hit in the extended LLC to GPU cores in cache mode, which mitigates the overhead of extended LLC misses. The Morpheus controller uses Bloom filters [19] for hit/miss prediction, providing zero false-negative and negligible false-positive rates.

To improve the effectiveness of Morpheus, we employ two optimization techniques on top of our basic design. First, we increase the effective capacity of the extended LLC by employing a cache compression technique in the extended LLC kernel. Second, we accelerate the data array access in the extended LLC by adding a new specialized instruction to the GPU instruction set architecture. This new instruction enables indirectly addressing a register, i.e., reading from a register whose index is determined by accessing the value in another register.

To evaluate the effectiveness of Morpheus, we first measure the bandwidth, access latency, and energy consumption of the extended LLC via real-system experiments using an NVIDIA RTX 3080 GPU (§5). We then use the measured performance and energy numbers for the extended LLC in the AccelSim simulator [8] to estimate the effect of Morpheus on overall GPU performance and energy consumption. Our experimental results show that Morpheus improves overall GPU performance and energy efficiency by an average of 39% and 58%, respectively, compared to the baseline NVIDIA RTX 3080 GPU architecture, across 14 memory-bound applications. Morpheus performs within 3% of a conventional GPU design that has a quadruple-sized conventional LLC (assuming *no* latency overhead for the larger conventional LLC).

We make the following contributions:

- We propose Morpheus, the first technique that leverages some GPU cores' on-chip memories to extend the total GPU last-level cache capacity.

- We introduce two new mechanisms that Morpheus employs: (1) a software helper kernel to extend the LLC using the on-chip memory resources of GPU cores that are in cache mode, and (2) a hardware controller that enables accesses to *both* the conventional LLC and the extended LLC.

- We evaluate Morpheus and show that it significantly improves performance and energy. It also enables a 4× larger cache without requiring new hardware resources for it.

# 2. Background

A GPU program is composed of a number of kernels that are executed using Single-Program-Multiple-Data (SPMD) threads [20]. These threads are partitioned into multiple blocks, or Cooperative Thread Arrays (CTAs) [20]. CTAs are then assigned to Single-Instruction-Multiple-Data (SIMD) cores for execution, called Streaming Multiprocessors (SMs) on NVIDIA GPUs. Each SM contains multiple CUDA cores, special-function units (e.g., cos, sin and tan), shared memory, L1 cache and thousands of registers. SMs are connected to several memory partitions using an on-chip interconnection network. Each memory partition includes one or multiple LLC banks, a memory controller, and a main memory (GDDRx/HBMx). Threads inside each CTA are grouped into warps. Threads within a warp execute the same instruction on different data items in a lock-step manner. The warp scheduler time-multiplexes warps, and assigns warps to the execution units.

# 3. Motivation

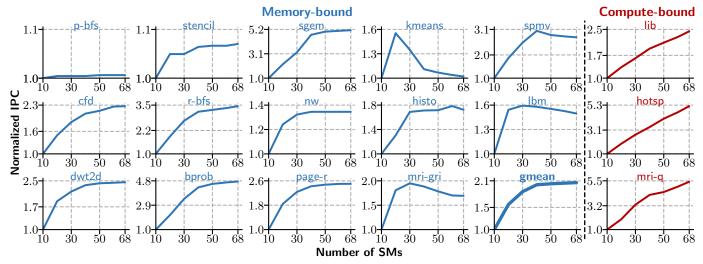

Memory-bound applications cannot fully utilize the compute throughput of GPUs as they are bottlenecked by the limited memory bandwidth. This causes long memory access latencies, which cannot be hidden via thread-level parallelism, causing core idleness and performance saturation [4, 21-29]. To illustrate this observation, we experimentally study the performance of 17 applications (14 memory-bound and 3 computebound) as we scale the number of GPU cores using AccelSim [8] (see §6 for our methodology). Figure 1 illustrates the results for a baseline GPU architecture that resembles an NVIDIA RTX 3080 [7]. The x-axes correspond to the number of GPU cores (SMs), ranging from 10 (chosen empirically) to 68 (the total SM count in an RTX 3080). The y-axes correspond to the normalized performance for each application. We normalize the performance of each application to its performance when using 10 SMs for readability.

We make two key observations. First, performance *gradually saturates* (i.e., stops increasing) as the number of SMs increases for 9 of the memory-bound applications (p-bfs, cfd, dwt2d, stencil, r-bfs, bprob, sgem, nw, page-r). In contrast, the performance of the compute-bound applications continues to increase with more SMs. Second, performance *decreases* sharply after a certain number of SMs for 5 of the memory-bound applications (kmeans, histo, mri-gri, spmv, lbm). For example, after more than 20 SMs are used for the kmeans application, performance drops greatly and the performance of the application with 68 SMs is almost the same as it is with 10 SMs, which is 50% lower than with 20 SMs. We conclude that limiting the number of SMs running a memory-bound application (after some SM count) not only does *not* significantly hurt performance but can even *improve* performance in some cases.

Leveraging our key observations, we aim to reserve a number of SMs and use their on-chip memory (i.e., register file, shared memory, and L1 cache) to extend the overall LLC capacity and, thus, improve GPU performance for memory-bound

Figure 1: Normalized GPU performance (IPC) of 14 memory-bound and 3 compute-bound applications

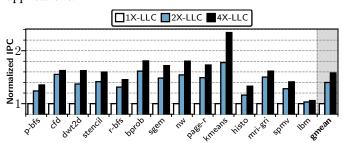

applications. To quantify the benefits of potentially having a larger LLC for memory-bound applications, we repeat our previous experiment with 2× and 4× LLC sizes, compared to the baseline 5-MiB LLC of an NVIDIA RTX 3080. We vary the number of GPU cores in these two evaluated GPU designs (2× and 4× larger LLCs) and measure overall performance for each case. Figure 2 shows the maximum performance that we observe while varying the number of GPU cores for 14 representative memory-bound applications. We normalize the performance results of each application to the case of a baseline 5-MiB LLC. We observe that both 2× and 4× LLC sizes improve the performance of all evaluated memory-bound applications. In particular, a 4× larger LLC improves performance by as much as 2.34× (kmeans), and by 1.57× on average (geometric mean). We conclude that a larger LLC effectively and consistently improves the performance of memory-bound applications.

Figure 2: Effect of larger LLC sizes ( $2 \times$  and  $4 \times$  the size of the baseline LLC) on performance (normalized IPC relative to the baseline LLC) of 14 memory-bound applications

**Our goal** in this work is to design a mechanism that can leverage the on-chip memory units of a number of GPU cores (that are otherwise not beneficial), to effectively extend the overall LLC capacity for memory-bound GPU applications, so as to increase performance.

# 4. Morpheus

We introduce Morpheus, a hardware/software co-designed technique to alleviate the memory bottleneck on GPUs. The key idea of Morpheus is to reserve a number of GPU cores and use their on-chip memory units (i.e., register file, shared memory, and L1 cache) as an extension of the GPU's LLC. In Morpheus, each GPU core has two working modes, *compute mode* and *cache mode*. Cores in compute mode behave exactly like the cores in existing GPUs and execute application threads. In contrast, cores in cache mode execute a software helper kernel (called the *extended LLC kernel*) to extend the LLC capacity by exploiting the storage capacity of their local on-chip memory units. This additional LLC capacity provided by the cores in cache mode is called the *extended LLC*.

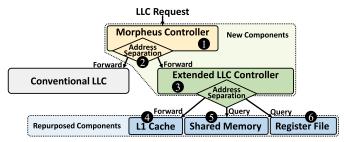

Figure 3 gives a conceptual overview of the LLC lookup procedure in Morpheus. An LLC request in a Morpheus-enabled GPU first arrives at the *Morpheus controller* (1) in Figure 3). The Morpheus controller forwards the LLC request to either the conventional LLC (which works exactly as in existing GPUs) or the *extended LLC* (which we propose). The forwarding decision is based on a static address mapping scheme, called *address separation* 2. An access to the extended LLC is served by the *extended LLC controller* 3 using the on-chip memory units of cores in cache mode. The extended LLC controller either *forwards* a given request to the core's L1 cache 4, or *directly queries* the register file 5 or shared memory 6. The forwarding or querying decision is based on the same static address separation principle as in the Morpheus controller.

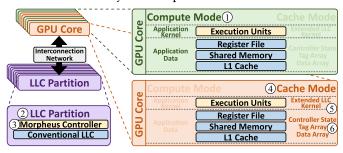

Morpheus implements the Morpheus controller as a new hardware unit per LLC partition and the extended LLC controller as software (i.e., the extended LLC kernel) running on cores in cache mode. Figure 4 shows a pictorial example of a Morpheus-enabled GPU with these new components. An LLC request originates from a core in compute mode (1) in Figure 4) and moves through the interconnection network to an LLC partition 2 based on a static address mapping scheme, similar to the one used in a conventional GPU. In

Figure 3: Conceptual overview of Morpheus

a Morpheus-enabled GPU, a hardware implementation of the Morpheus controller local to the LLC partition (3) then either forwards the request to the local conventional LLC, or through the interconnection network to the responsible GPU core running in cache mode (4) based on a static address separation scheme (§4.1.1). The responsible cache mode GPU core is determined by the address separation scheme. The extended LLC controller is implemented as multiple instances of a software helper kernel (the extended LLC kernel) running on cores in cache mode (5). This kernel queries one of the local memory units (6) for each incoming request, based on a static address separation scheme (§4.1.1), and sends the response over the interconnection network back to the Morpheus controller (3). If the request is a hit in the extended LLC, the cache block is sent over the interconnection network to the GPU core that initially issued the LLC request (1). If the request is a miss in the extended LLC, it is treated exactly like an LLC miss in a conventional GPU by the LLC partition.

Figure 4: GPU structure with Morpheus

The rest of this section explains Morpheus' key mechanisms in detail. §4.1 describes our hardware implementation of the Morpheus controller. §4.2 describes our software implementation of the extended LLC controller using the extended LLC kernel. §4.3 introduces two optimization techniques on top of our basic design to improve the effectiveness of Morpheus.

### 4.1. Morpheus Controller

This unit has three main tasks: (1) separating LLC requests between the conventional LLC and the extended LLC, (2) handling communication between the extended LLC and the LLC partition, and (3) predicting the outcome of the extended LLC lookup (hit/miss), so that the Morpheus controller forwards only the requests that are predicted to be hits in the extended LLC to GPU cores in cache mode, which mitigates the overhead of extended LLC misses. Figure 7 shows the main components

in the Morpheus controller. In this section, we describe each component in detail.

**4.1.1. Address Separation.** Since a Morpheus-enabled GPU employs two distinct LLCs (i.e., the conventional LLC and the extended LLC), there should be a mechanism to map each cache block to one of these LLCs. To this end, Morpheus divides the memory address space statically into two partitions proportional in size to the conventional and extended LLC capacity. The conventional LLC is responsible for caching the first partition, while the extended LLC is responsible for caching the second. When the Morpheus controller receives an LLC request, a unit called *address separator* checks whether or not the set number is in the range of memory addresses served by the extended LLC. If so, the unit forwards the LLC request to the next unit in the Morpheus controller, the *hit/miss predictor*. Otherwise, the conventional LLC handles the request exactly the same way as done in the conventional GPU architectures.

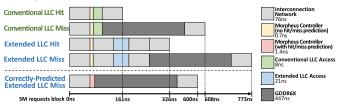

**4.1.2. Hit/Miss Prediction.** Misses in the extended LLC are more expensive in terms of latency compared to misses in the conventional LLC. Figure 5 breaks down the latencies of hits and misses in both the conventional and extended LLC (see §6 for our methodology). We observe that misses in the conventional LLC take 608ns to be served, while misses in the extended LLC take 773ns (i.e., 27% longer). This is due to two main reasons. First, an extended LLC miss adds a round trip interconnection network latency (two grey boxes in Figure 5) compared to a conventional LLC miss, to move the request and response between the Morpheus controller and a GPU core in cache mode. Second, the latency for accessing the extended LLC is longer than for the conventional LLC, because in the extended LLC, tag lookups and data array accesses have to be managed by the extended LLC kernel (i.e., in software).

Figure 5: Timelines for LLC hits, misses, and predicted misses on a Morpheus-enabled GPU

We mitigate the overhead of extended LLC misses using a hit/miss predictor. After the address separation mechanism in the Morpheus controller determines that a given request falls into the extended LLC's address space, the hit/miss predictor decides if the request is likely to be a hit in the extended LLC. If the request is predicted to be a hit, the Morpheus controller forwards the request to the extended LLC. Otherwise, the Morpheus controller directly accesses the off-chip DRAM to serve the memory request.

Figure 5 shows the timeline for a correctly-predicted extended LLC miss. If a miss is predicted correctly, it avoids the unnecessary latency of (1) an interconnection network roundtrip, and (2) querying the tag array with the extended

LLC kernel. Thus, correctly-predicted extended LLC misses can be serviced as fast as conventional LLC misses.

To maintain correctness in the presence of the hit/miss predictor, we must understand if and which types of mispredictions are acceptable. We observe that it is acceptable to falsely predict a request as an LLC hit when in reality the request is a miss. This is because the predicted LLC hit causes a lookup in the extended LLC, at which point the misprediction will be discovered. Nevertheless, such false positives are undesirable, because they increase the latency of extended LLC misses to the same latency as if there were no hit/miss prediction. In contrast, falsely predicting a request as an LLC miss even though the requested address is in the LLC can violate both coherence and consistency guarantees. For example, if a request to a dirty cache block is falsely predicted as an LLC miss, the requesting core will receive an out-of-date value from main memory, which violates basic cache correctness. Thus, for correctness, the hit/miss predictor must not produce such false negatives, or otherwise it should recover from its mispredictions such that no correctness problems appear.

We design our hit/miss predictor using Bloom filters [19]. Bloom filters are a good fit for our requirements because they provide fast and low-cost set membership queries without false negatives. In our hit/miss predictor, a Bloom filter represents the LLC blocks which are currently in a given extended LLC set. To avoid increasingly frequent false positives, the Bloom filters must be cleared regularly, after which there is a risk for *false negatives*. We next describe an algorithm using two Bloom filters, which are cleared alternately, thus avoiding false negatives.

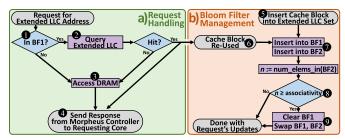

The key idea of our extended LLC hit/miss prediction algorithm is to track the blocks currently in the LLC set using two Bloom filters per extended LLC set, BF1 and BF2. BF1 and BF2 are updated upon every access to the extended LLC set, such that at any given time, (1) BF1 contains at least all the cache blocks currently in the extended LLC set, and (2) BF2 contains the *n* most recently used cache blocks in the extended LLC set. Invariant (1) guarantees the absence of false negatives when querying BF1 with requested extended LLC addresses, i.e., BF1 can be used to safely predict if a request will hit in the extended LLC set. Invariant (2) enables eventually replacing BF1 with BF2, when BF2 contains all cache blocks in the extended LLC set ( $n \ge$  associativity). The benefit of eventually replacing BF1 with BF2 is that BF2 does not (yet) contain any evicted cache blocks, thus producing fewer false positives than the old BF1. In contrast, BF1 may contain multiple evicted cache blocks. We explain in detail how the hit/miss predictor queries BF1, and how BF1 and BF2 are updated upon every access to the extended LLC set to maintain invariants (1) and (2).

Figure 6(a) shows a flow diagram of how the Morpheus controller with the hit/miss predictor serves an extended LLC request. To make a hit/miss prediction for some LLC request, the hit/miss predictor queries BF1 with the LLC request's ad-

Figure 6: Flowchart of the extended LLC hit/miss predictor

dress (1) in Figure 6). It predicts a hit when the address is found in BF1, and a miss otherwise. This cannot produce false negatives, since invariant (1) guarantees that BF1 contains all blocks currently in the extended LLC set, and Bloom filters do not produce false negatives. Upon a predicted extended LLC hit, the algorithm queries the address in the extended LLC 2. Upon a (predicted or actual) extended LLC miss, the Morpheus controller accesses the requested block in DRAM instead 3. Finally, the response is sent from the Morpheus controller to the core that issued the request 4.

Figure 6(b) shows a flow diagram of how the hit/miss predictor updates BF1 and BF2 for a given extended LLC access to maintain invariants (1) and (2). Upon an access (i.e., when a cache block is inserted into the set (5 in Figure 6), or a cache block in the set is re-used **6**), the accessed cache block is inserted into both Bloom filters **7**. This trivially maintains invariant (1), because any inserted extended LLC block will also be in BF1. Invariant (2) is maintained because before the insertion, BF2 contained the nold most recently used blocks, and after the insertion BF2 contains either the  $n=n_{old}+1$  most recently used blocks (if the used block was not in BF2 before) or the  $n=n_{old}$  most recently used blocks (if the used block was already in BF2). After n becomes as large as the set's associativity **8**, all future predictions can be made by querying BF2 instead of BF1, without risking false negatives. This is because the extended LLC uses the LRU (least recently used) replacement policy and BF2 contains the *n* most recently used blocks, thus if n is as large as the set's associativity, BF2 is guaranteed to contain all blocks that are in the LLC set. Thus, the contents of BF1 are cleared, BF1 and BF2 are swapped, and the scheme repeats **9**.

**Cost.** Assuming each Bloom filter is 32 bytes in size, and up to 256 extended LLC sets per LLC partition, the hit/miss predictor requires 32B×2×256=16KiB of Bloom filter storage in each LLC partition.

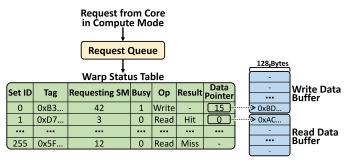

**4.1.3. Extended LLC Query Logic Unit.** The Morpheus controller includes a hardware unit called the *extended LLC query logic unit* to track and manage outstanding extended LLC requests. Figure 7 shows the four main components in the extended LLC query logic unit, namely the *request queue*, the *warp status table*, the *read data buffer*, and the *write data buffer*. We explain each component in this section.

**Request Queue.** For simplicity, each extended LLC kernel warp serves only a single extended LLC request at a time in Morpheus. To avoid clogging the interconnection network

$<sup>^2{\</sup>rm Counting~Bloom~filters}$  [30] would support individual element removal instead, but require more bits compared to standard Bloom filters.

Figure 7: Extended LLC Query Logic Unit

with backlogged request bursts, we introduce a request queue, which buffers any requests to the extended LLC. A given request is de-queued as soon as the warp assigned to the request's extended LLC set is ready to serve a new request. When dequeued, the request's metadata is written to the corresponding row in the warp status table. If the request is a write, the payload data is written to the write data buffer.

Warp Status Table. The warp status table has one row per set in the current LLC partition, tracking the status of the extended LLC kernel warp that is assigned to each set. Each row has fields for the current request's tag, the origin of the request, a *busy* bit (indicating if the warp is currently serving a request), an *op* field (indicating if the request is a read or write), a *result* field (indicating if the request is a hit or a miss in the extended LLC), and a pointer to either the read or write data buffer entry for the payload data. The warp status table is memory-mapped, thus the extended LLC kernel warps can read from and write to it with regular load/store instructions.

We size the warp status table based on the maximum number of sets in the extended LLC. We assume an NVIDIA RTX 3080 GPU as the baseline, which has 10 LLC partitions, 68 SMs, and 48 warps per SM (and thus, up to 48 extended LLC sets per SM in cache mode). We assume that up to 75% of all SMs can be in cache mode, based on Figure 1, where GPU performance starts to saturate after using at least 25% of the SMs for computation. Under these assumptions, Morpheus can provide up to 2448 extended LLC sets, i.e., about 256 sets per LLC partition. As a result, the warp status table has 256 rows in each Morpheus controller of a Morpheus-enabled NVIDIA RTX 3080 GPU.

Read and Write Data Buffers. The read and write data buffers hold payload data from requests to the extended LLC. For example, when a write request arrives at the extended LLC query logic unit, it includes a dirty cache block (e.g., 128 bytes) to write to the extended LLC. These 128 bytes are written to an entry in the write data buffer, and the data pointer in the warp status table is updated to point to that entry. Read requests work analogously, with the difference that the extended LLC kernel writes the requested cache block to the read data buffer entry instead. Like the warp status table, the read and write data buffers are memory-mapped, and thus extended LLC kernel warps can read from and write to them with simple load/store instructions.

#### 4.2. Extended LLC Controller

Morpheus implements the extended LLC controller as a soft-ware helper kernel, called the *extended LLC kernel*, that performs three main tasks: (1) storing and updating the extended LLC tags and data in the local memory units of a GPU core operating in cache mode (§4.2.1-4.2.2), (2) executing simple operations (e.g., increment) on the extended LLC blocks needed for *atomic* instructions (§4.2.3), and (3) identifying the correct memory unit to perform these operations on, based on a static address separation mechanism.

Morpheus schedules one copy of the extended LLC kernel on each GPU core that is operating in cache mode. The extended LLC kernel uses the maximum number of warps in each GPU core, and each warp handles *exactly* one extended LLC set. The extended LLC kernel effectively uses all of the local memory units of GPU cores operating in cache mode to store the extended LLC data and metadata (e.g., tags, valid bits, dirty bits), except for a number of registers that the extended LLC kernel reserves as *auxiliary registers* for its own operation. In this section, we explain only the first and second tasks of the extended LLC kernel since the third task, i.e., address separation, is analogous to the address separation in the Morpheus controller (§4.1.1), with the only difference being that the address space is divided proportionally to the respective *memory units*' capacities instead.

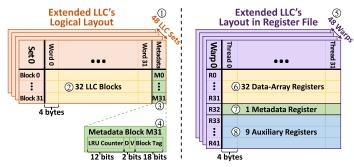

**4.2.1. Extended LLC via Register File.** In this section, we describe how the extended LLC kernel (1) lays out the extended LLC blocks' tags and data in the register file, and (2) accesses and updates them.

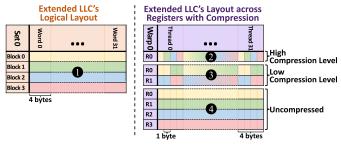

**Extended LLC Layout in the Register File.** Figure 8 shows how the extended LLC kernel lays out 48 sets of a 32-way set-associative extended LLC in the register file of a GPU core operating in cache mode. This example assumes a baseline NVIDIA RTX 3080 [7] GPU, with up to 48 active warps per SM, and 42 registers per warp.

The extended LLC kernel uses the register file to store a number of extended LLC sets (e.g., 48) ①, for each set a number of cache blocks (e.g., 32 blocks of 128 bytes each) ②, and for each block a metadata block ③ containing the block's LRU counter, dirty bit, valid bit, and tag ④. Each extended LLC set ① is stored in the registers of exactly one warp ⑤. Each data block of a set ② is stored in exactly one warp register, called a *data-array register* ⑥. The metadata blocks ③ are coalesced into a single warp register, called the *metadata register* ⑦, such that thread i holds block i's metadata block. The remaining *auxiliary registers* are used for extended LLC kernel execution (8).

In this configuration of 48 extended LLC sets per GPU core operating in cache mode, 32 blocks per set, and 128 bytes per block, each GPU core operating in cache mode adds  $48 \times 32 \times 128B = 192$ KiB capacity to the extended LLC by using the space in the GPU core's register file.

**Extended LLC Tag Lookup.** When a warp executing the extended LLC kernel receives an extended LLC request for its set, the warp executes a tag lookup procedure to determine if

Figure 8: Each out of the 48 warps in an SM in cache mode implements one fully associate cache set (e.g., set 0) with several cache blocks (e.g., 32).

the request is a hit in the set, and if so, which cache block in the set was hit. To this end, the warp compares the tag of the request address to the tags of extended LLC blocks stored in its metadata register  $R_M$  (e.g.,  $R_{32}$  in Figure 8).

Algorithm 1 shows the pseudo code for the tag lookup procedure in the extended LLC kernel. The procedure receives the tag of the extended LLC request as the input and returns the outcome of the lookup ("HIT=True" and the "BLOCK\_INDEX" of the corresponding cache block, or "HIT=False") as the output. Algorithm 1 assumes that the request's tag is in the auxiliary register  $R_{\alpha u x_0}$  (e.g.,  $R_{33}$  in Figure 8) for all threads, i.e., there are 32 copies of the tag.

Each thread of the warp is assigned to a cache block (Block 0-31 in Figure 8) and corresponding metadata block (M0-M31 in Figure 8), such that all following operations run in parallel for all cache blocks. First, each thread ensures that its assigned metadata block in  $R_M$  (e.g.,  $R_{32}$  in Figure 8) is valid by checking the valid bit (line 2). Second, each thread compares the tag in its assigned metadata block to the request's tag in  $R_{aux_0}$ , and stores the result in an auxiliary register (e.g.,  $R_{aux_1}$ ) (line 3). Third, the comparison result of each thread is shared among all threads as a 32-bit bitvector and written into  $R_{aux_2}$  using the ballot\_sync instruction [20] (line 4). If  $R_{\alpha ux_2}$  is non-zero, one of the tags in the metadata blocks must have matched the request's tag, i.e., the request is a hit (lines 5-6). In this case, the 0-based index of the first 1-bit in  $R_{aux_2}$  is obtained using the ffs instruction [20] (line 7). This index is the index of the cache block whose metadata matched the request's tag. Finally, the LRU counters are updated (lines 8-12).

Handling Extended LLC Hits. After detecting an extended LLC hit, the corresponding warp in the extended LLC kernel should move the cache block from the register file to the *read data buffer* in the Morpheus controller (§4.1.3). In this section, we explain how the warp in the extended LLC kernel reads the register that contains the requested cache block.

After the *tag lookup* procedure, the corresponding extended LLC kernel warp has the index of the matching cache block available (e.g., in  $R_{aux_3}$ ). To retrieve the matching cache block's data, the extended LLC kernel warp should access the register whose index equals the value of  $R_{aux_3}$ . For example, if  $R_{aux_3}$  is equal to 5,  $R_5$  should be accessed. This register file access is *indirect*, i.e., it requires reading from a register whose

# **Algorithm 1** Extended LLC Tag Lookup – Register File

```

Input: Extended LLC Request's Tag (Rauxo)

Output: HIT:bool, and if HIT=True, BLOCK_INDEX:int (Raux3)

1: procedure Tag Lookup//executed by an extended LLC kernel warp of 32 threads

2:

R_{aux_1} \leftarrow Valid(R_M) //ensure the block is valid

R_{aux_1} \leftarrow R_{aux_1} \& \& (R_{aux_0} == Tag(R_M)) / \text{match request tag to metadata}

3:

- \_ballot\_sync(0xffffffff, R_{aux_1}) //share R_{aux_1} between all

4:

threads as a 32-bit vector

if (R_{aux_2}) then //one of the bits is non-zero because there was a hit

5:

R_{aux_3} \leftarrow \_ffs(R_{aux_2}) - 1 //get the 0-based index of the non-zero bit

6:

HIT ← True

7:

BLOCK_INDEX \leftarrow R_{aux_3}

8:

if (thread\_idx == R_{aux_3}) then //reset the LRU counter of the hit block

9:

10:

LRU\_Counter(R_M) \leftarrow 0xfff

11:

else//decrement the LRU counters of all other blocks

LRU\_Counter(R_M) \leftarrow LRU\_Counter(R_M) - 1

12:

end if

13:

14:

else

15:

HIT ← False

16:

end if

17: end procedure

```

index is determined by accessing the value in another register. An indirect register file access is not straightforward, because many existing GPU ISAs (e.g., [20]) only provide instructions for accessing the register file with an immediate (constant) index.

To enable indirect register accesses, we define a procedure called *Indirect-MOV*. The key mechanism is to implement a switch-case structure in the procedure. The procedure 1) allocates each case to access a specific register index, and 2) selects the corresponding case using the target register index (e.g., the value of  $R_{aux_3}$ ). Algorithm 2 illustrates how we implement the Indirect-MOV procedure using the instructions already present in an existing GPU ISA [20].<sup>3</sup> The procedure uses the brx.idx instruction [20]. This instruction is a branch instruction that gets a list of branch targets (i.e., T<sub>List</sub>) and an index as input. The control flow jumps to the branch targets at the specified index. The Indirect-MOV procedure uses the the target LLC block index (e.g., the value of  $R_{aux_3}$ ) as the input to the brx.idx instruction. The procedure defines 32 branch targets ( $L_0$ - $L_{31}$ ), each is allocated to access the corresponding data-array register. For example, the branch targets L0 and L31 are to access the cache blocks in registers  $R_0$  and  $R_{31}$ , respectively.

Handling Extended LLC Misses. The warp in the extended LLC kernel that services the extended LLC request handles an extended LLC miss in four steps. First, the warp accesses main memory to bring the requested cache block. Note that main memory accesses from the extended LLC kernel bypass the conventional LLC. Second, to free space in the extended LLC for the to-be-inserted block, the warp selects the victim extended LLC block based on the *LRU* replacement policy. To this end, the warp determines which extended LLC block has the lowest LRU counter. Third, the warp checks the dirty bit of the victim extended LLC block and writes it back to the main memory if it is dirty. Fourth, the warp writes the new extended LLC block into the register file using the *Indirect-MOV* procedure (Algorithm 2).

$<sup>^3</sup>$ We optimize *Indirect-MOV* by adding a new instruction to the ISA in §4.3.

# Algorithm 2 Indirect-MOV Algorithm

13:

return

14: end procedure

#### Input: BLOCK\_INDEX:int $(R_{aux_3})$ Output: Requested Extended LLC Block $(R_{aux_0})$

procedure Indirect-MOV //The goal is to implement register indirect access, reading from a register whose index is determined by accessing the value in another register. This procedure is critical for accessing data-array registers in the extended LLC kernel.

```

T<sub>list</sub>: .Branch Targets L<sub>0</sub>, L<sub>1</sub>, L<sub>2</sub>, ..., L<sub>31</sub>; //Define 32 branch targets,

each is allocated to access a specific register index.

```

```

3:

@p brx.idx R_{aux_3}, T_{list}; //Branch to label L_i specified by the target LLC

block index i=R_{aux_3}

MOV\ R_0, R_{\alpha u x 0} //Access data-array register R_0 if target LLC block index is

5:

0

return

6:

7:

L_1:

MOV R<sub>1</sub>, R<sub>qux0</sub> //Access data-array register R<sub>1</sub> if target LLC block index is

8:

9:

10:

11:

L_{31}:

MOV R_{31}, R_{\alpha u \times 0} //Access data-array register R_{31} if target LLC

12:

block index is 31

```

**4.2.2. Extended LLC via Unified L1/Shared-memory.** We explain how the extended LLC kernel uses the L1 cache and shared memory as the extended LLC.

L1 cache. Morpheus assigns a portion of the extended LLC to the L1 cache of each GPU core that is in cache mode. When a warp executing the extended LLC kernel receives a request that should be serviced in the L1 cache, the warp simply forwards the request to the L1 cache by executing GPU load and store instructions. If the request hits in the L1 cache, the responsible warp in the extended LLC kernel responds to the Morpheus controller through the extended LLC query logic unit. Otherwise, the L1 cache accesses the main memory to service the miss request. Note that the Morpheus controller ensures that an L1 cache miss from a GPU core that is in cache mode bypasses the conventional LLC and directly accesses main memory.

Shared Memory. Morpheus assigns a portion of the extended LLC to the shared memory. Since shared memory does not have a hardware unit for storing the tags (unlike the L1 cache), the extended LLC kernel stores the tags of the extended LLC blocks assigned to the shared memory inside the register file instead. The advantage of this approach is that a register file access is faster than shared memory access, which accelerates the tag lookup procedure. The tag lookup procedure is similar to the procedure shown in Algorithm 1. To access an extended LLC block, the extended LLC kernel calculates the address of the block's data in shared memory based on the extended LLC set number and the cache block index from the tag lookup procedure.

**4.2.3. Supporting Atomic Instructions in the Extended LLC.** Modern GPUs execute global memory atomic operations via single SASS instructions that run on atomic units in the conventional LLCs [31, 32], which is critical for performance of GPU applications with inter-CTA synchronization. Morpheus supports global memory atomic operations in the extended

LLC, as we explain next. First, the warp handling an extended LLC request performs atomic operations using the functional units inside the SMs in cache mode, no matter which on-chip memory inside an SM in cache mode has the corresponding block. Second, the Morpheus controller guarantees the atomicity in the extended LLC since several threads cannot access the same extended LLC block at the same time. This is because: (1) each cache block in the extended LLC is assigned to exactly one warp in the extended LLC kernel, and (2) each warp completes one extended LLC request before starting to service another request.

# 4.3. Optimizing Morpheus

We describe two optimization techniques on top of the basic Morpheus design we introduced in §4-4.2. First, the flexibility of the extended LLC kernel enables low-cost implementation of cache optimization techniques, such as cache compression, resizing cache blocks, and online modification of the replacement policy. As a case study, we discuss how to use cache compression in Morpheus (§4.3.1). Second, the extended LLC needs the *Indirect-MOV* procedure that we implement using the *brx.idx* instruction in basic Morpheus (see Algorithm 2). However, having architectural support for this operation can accelerate the data array access. We provide new architectural support for the *Indirect-MOV* instruction in §4.3.2.

**4.3.1.** Cache Compression. Queries to, insertions to, and evictions from the register file and shared memory partitions of the extended LLC always go through the extended LLC kernel<sup>4</sup>. Hence, the extended LLC kernel can manipulate them in a way that is transparent to the rest of the system. Our goal is to leverage this opportunity for increased extended LLC capacity. To this end, we propose a cache compression scheme on top of Morpheus. The key idea is to use the extended LLC kernel to store compressed (where possible) versions of the extended LLC blocks, thereby increasing the number of blocks in each extended LLC set, and thus the effective capacity of the extended LLC. The extended LLC kernel compresses any inserted extended LLC block, stores the compressed version in the register file or shared memory, and serves requests by decompressing the blocks upon a hit. In this section, we describe our mechanism in detail.

An inserted or updated (i.e., written-to) 128-byte extended LLC block is grouped into one of three *compression levels* that we define as follows: (1) the *high* compression level includes extended LLC blocks that can be compressed 4-fold into 32 bytes, (2) the *low* compression level includes extended LLC blocks that can be compressed 2-fold into 64 bytes, and (3) the *uncompressed* level includes extended LLC blocks that could not be compressed. Figure 9 shows how logical 128-byte extended LLC blocks 1 are laid out in the register file, depending on their respective compression level 2 3 4. Blocks in the *high* 2 and *low* 3 compression levels are laid out across reg-

$<sup>^4</sup>$ Note that insertions to and evictions from the L1 partition of the extended LLC do *not* go through the extended LLC kernel, because the L1 cache handles them in hardware.

isters in a strided and interleaved manner with strides 4 and 2, respectively. Blocks in the *uncompressed* level are laid out exactly like they were without our compression scheme 4. For example, for the *high* compression level, four extended LLC blocks 1 are stored in a single warp register of 32×4 bytes 2, such that they occupy the first, second, third and fourth bytes of each thread, respectively.

Since the compression levels of cache blocks cannot be known ahead of time, the number of warp registers allocated to each compression level should be adapted dynamically. Our mechanism initially assigns all registers to the uncompressed level. Then, over epochs of n cycles (we empirically choose n=10,000), the number of cache blocks in the high, low and uncompressed levels are counted. At the end of each epoch, the number of registers assigned to each compression level is updated based on the counter values.

We employ the Base-Delta-Immediate (BDI) compression algorithm [33] due to its simplicity and good cache compression ratios. The BDI algorithm works as follows: First, the input cache block is divided into segments (e.g., 4 bytes each). Second, one of these segments (e.g., the first) is designated as the *base* segment and copied to the output. Third, only the *deltas* (arithemtic differences) of the remaining segments from the base segment are copied to the output [33]. The achieved compression ratio depends on how large the deltas are. For example, if all segments are very similar to the base segment, the deltas are small and can be stored in only a few bits for each delta. We consider 4-byte segments in our implementation and store the base segments of compressed blocks in auxiliary registers.

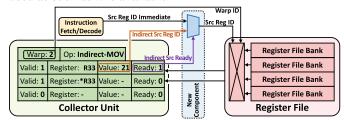

Figure 9: Layout of compressed cache blocks across registers

**4.3.2. Indirect-MOV Instruction.** The Indirect-MOV procedure (§4.2.1) is required for indirectly addressing registers in the extended LLC kernel. Our software implementation of the Indirect-MOV procedure (Algorithm 2) is very portable and flexible because it uses only instructions from NVIDIA's existing PTX ISA [20]. However, it is inefficient and slow for two reasons. First, it executes three instructions (i.e., *brx.idx*, *MOV*, and *return*) to perform a single indirect register access. Second, two of these instructions (i.e., *brx.idx* and *return*) are branches, which cause irregular control flow.

To improve the efficiency of the Indirect-MOV procedure, we introduce a new instruction in the GPU ISA that can perform Indirect-MOV natively via minor modifications to existing hardware. Like the software implementation of Indirect-MOV,

the new Indirect-MOV instruction conceptually (1) accesses the register file to read the source register  $R_{Src}$ , (2) re-accesses the register file to read the indirectly addressed register  $R[R_{Src}]$ , and (3) moves the value from  $R[R_{Src}]$  to the destination register  $R_{dest}$ .

To support this instruction in GPU hardware, we modify the register file architecture. The key idea is to support two sequential register file reads for the Indirect-MOV instruction. We slightly modify the operand collectors in the register file to support these sequential reads. The operand collector first accesses the register file using the register number specified in the instruction to read a 1024-bit warp register. Then, the operand collector uses the first eight least significant bits of the read register value as the next register number. The operand collector then re-accesses the register file with this new register number. The read value is then written to the destination register using the regular MOV instruction's data path in the pipeline. Figure 10 illustrates our changes to the baseline operand collector. We add a single multiplexer per operand collector to select between the two different sources of the register number: (1) the immediate source register number from the instruction, (2) the value loaded from a register. The multiplexer is controlled by the ready bit of the register number loaded from a register, i.e., the indirect register number is used as soon as it is available.

Figure 10: Native hardware implementation of Indirect-MOV

# 5. Characterization of the Extended LLC Kernel

We implement the extended LLC kernel, as described in §4.2, and evaluate it on a real GPU. Our goal is to obtain relevant metrics that characterize the extended LLC kernel and the different implementation alternatives (i.e., combinations of register file, L1, and shared memory). We evaluate four relevant metrics for the extended LLC: (1) storage capacity, (2) access latency, (3) access bandwidth, and (4) energy per byte. We use these metrics to (i) determine the implementation alternative that provides the best tradeoff, and (ii) properly configure our simulation of the extended LLC in our cycle-level GPU simulator (see §6), to evaluate the effectiveness of Morpheus at boosting GPU performance of real-world memory-bound applications (§7).

**Methodology.** We implement and evaluate the extended LLC kernel on a real NVIDIA RTX 3080 GPU [7]. Our implementation faithfully follows the description in §4.2. However, since there is no actual Morpheus controller (§4.1) in a real state-of-the-art GPU, we emulate the warp status table (§4.1.3) by

placing a similar data structure, which contains the addresses of the extended LLC to access in our evaluation, in the conventional LLC. The latency of an access to this emulated warp status table is similar to an access to the warp status table in the Morpheus controller, since the Morpheus controller sits inside the LLC partition (see Figure 4).<sup>5</sup>

We implement three variants of the extended LLC kernel: (1) extended LLC via register file, (2) extended LLC via L1, and (3) extended LLC via shared memory. For each of them, we experiment with different numbers of warps of the extended LLC kernel on a single GPU core. Each warp is in charge of one set of the extended LLC. Thus, the larger the number of warps, the smaller the extended LLC sets are (because of the fixed size of memory storage). Each extended LLC variant and number of warps offers a different tradeoff in terms of capacity, latency, bandwidth, and energy/byte.

To measure the extended LLC capacity, we calculate the available space for the extended LLC data array per GPU core in cache mode. This depends on the size of the actual storage (i.e., register file, shared memory, L1) and the space needed for auxiliary purposes (e.g., the execution context of extended LLC kernel). To measure the extended LLC access latency, we use the Nsight profiler tool [35] and the cudaEventElapsedTime API [34]. To measure the extended LLC access bandwidth, we first measure the number of accesses per second by dividing the total number of extended LLC accesses (100 million accesses in our experiments) by the total time takes to service all extended LLC accesses. Second, we multiply the resulting accesses per second by 128 (the extended LLC block size in bytes) to calculate the extended LLC bandwidth in bytes per second (B/s). To measure the extended LLC energy per byte, we first measure the average GPU power consumption using nvidia-smi [20] while servicing 100 million accesses to the extended LLC. Second, we calculate the total energy consumption by multiplying the measured power consumption with the total time it takes to service these extended LLC requests. Third, we divide the total energy consumption by the number of extended LLC accesses to obtain the energy per access. Fourth, we divide the energy per access by 128 (the extended LLC block size in bytes) to calculate the extended LLC energy per byte (J/B).

**Extended LLC Capacity.** Figure 11(a) reports the extended LLC capacity per GPU core in cache mode for different implementations using various numbers of warps, i.e., 1, 8, 16, 32, and 48. We make four key observations. First, the extended LLC capacity is substantial per GPU core in cache mode. For example, when using 8 warps for the extended LLC via register file (providing 239 KiB capacity) and 8 warps for the extended LLC via L1 (providing 128 KiB capacity), the extended LLC

capacity is 367 KiB per GPU core in cache mode.<sup>6</sup> Second, the capacity of the extended LLC via register file varies with the number of warps. This is due to two main reasons. First, using fewer than eight warps, the extended LLC kernel cannot utilize the total register file capacity since the extended LLC capacity is limited to the maximum number of registers per thread (i.e., 256). Third, using eight warps results in the maximum extended LLC capacity via register file (i.e., 239 KiB). Using more than eight warps leads to smaller extended LLCs via register file due to allocating a higher number of registers for auxiliary purposes (e.g., the execution context of the extended LLC kernel warps). Fourth, the capacity of the extended LLC via L1 and via shared memory does not change with the number of warps. This is because the extended LLC kernel allocates the whole space of each of these two memories (L1 and shared memory) to the extended LLC data array no matter how many warps the kernel uses.

Figure 11: Characterization of the extended LLC using a real GPU [7]. a) extended LLC capacity, b) extended LLC access latency, c) extended LLC access bandwidth, and d) extended LLC energy per byte.

<sup>&</sup>lt;sup>5</sup>We ensure that (1) the data structure that emulates the warp status table resides in the conventional LLC (and not L1 cache) using the *ld.global.cg* instruction [34], and (2) the data structure fits completely in the conventional LLC so that all accesses (after the initialization phase of the extended LLC kernel) to this data structure hit in the conventional LLC.

<sup>&</sup>lt;sup>6</sup>Note that using shared memory would not further increase the extended LLC capacity in this case. This is because the L1 and shared memory are unified in modern NVIDIA GPUs, i.e., the sum of L1 and shared memory space in a core is at most their total unified storage capacity (e.g., 128 KiB in an NVIDIA RTX 3080 [7]).

Extended LLC Access Latency and Bandwidth. Figures 11(b) and 11(c) report the extended LLC access latency and bandwidth, respectively, for different implementations using various numbers of warps, i.e., 1, 8, 16, 32, and 48. We make five key observations. First, the extended LLC access latency (≥300 ns) is almost two times longer than the conventional LLC access latency (~160 ns [31, 36]). The longer access latency of the extended LLC compared to the conventional LLC is mainly because of the round trip interconnect latency from the Morpheus controller to the GPU core in cache mode and from the GPU core in cache mode to the Morpheus controller. However, the extended LLC access latency is still approximately 2× faster than accessing off-chip memory (~600ns [31, 36]). Second, the extended LLC access bandwidth per GPU core in cache mode is 37 GB/s using the register file implementation and 48 warps. The bandwidth of each conventional LLC partition is around 300 GB/s [31, 36], and thus eight GPU cores in cache mode can collectively provide the same bandwidth as one conventional LLC partition. Third, increasing the number of warps of the extended LLC kernel in all three implementations results in higher extended LLC bandwidth at the cost of longer access latency. Increased access latency with more warps is mainly due to the fact that the corresponding warp servicing a request to the extended LLC needs to wait until its scheduling slot, and the waiting time becomes longer when using more warps. Fourth, the extended LLC via register file has both lower latency and higher bandwidth for almost all warp counts, compared to the extended LLC via shared memory and via L1. This is because the register file has a lower access latency and a higher access bandwidth compared to shared memory and L1.7 Fifth, the bandwidth of the extended LLC in the best case (i.e., the extended LLC via register file using 48 warps) is still less than 40 GB/s, which is one order of magnitude lower than the bandwidth of the register file (1 TB/s). This is because the interconnection network connecting LLC partitions to GPU cores significantly bottleneck the bandwidth of the extended LLC via register file (and similarly via shared memory and via L1).

To further analyze the effect of the interconnection network, we *ideally exclude* the interconnection network from the extended LLC accesses. To this end, we (1) assume the address of the extended LLC request is already ready in an *auxiliary* register of the SM operating in cache mode and (2) let the SM operating in cache mode discard the response instead of sending it over the interconnection network. We observe that the access bandwidth of the extended LLC via register file, shared memory, and L1 using 48 warps becomes 290 GB/s, 106 GB/s, and 97 GB/s, which is 7.8×, 3.4×, and 3.5× higher than the *non-ideal* versions, respectively. Hence, a better interconnect design could significantly improve the performance of the extended LLC.

Extended LLC Energy per Byte. Figure 11(d) reports energy

per byte results for different implementations using various numbers of warps, i.e., 1, 8, 16, 32, and 48. Note that the energy per byte results take into account the energy consumed by all the components included in the extended LLC accesses, i.e., GPU cores in cache mode (executing the extended LLC kernel), interconnect, and the conventional LLC banks. We make three key observations. First, The extended LLC energy per byte in the best case (extended LLC via register file and using 48 warps) is 53 pJ which is approximately 5.3× the energy per byte of the conventional LLC ( $\sim 10$  pJ [37]). Despite its high energy consumption compared to the conventional LLC, the extended LLC can reduce GPU energy consumption by reducing the number of energy-hungry off-chip memory accesses. Second, increasing the number of warps in the extended LLC kernel significantly reduces energy per byte for all implementations. This is because using more warps increases the extended LLC's throughput, without significantly increasing power consumption, leading to lower energy per byte. Third, the extended LLC via register file has a lower energy per byte for all warp counts compared to the extended LLC via L1 and via shared memory. This is mainly due to the fact that a register file access consumes less energy compared to an access to the L1 or shared memory [37].

Combining different extended LLC versions. Our characterization of the extended LLC shows that the extended LLC via register file outperforms other implementations in terms of capacity, access latency, access bandwidth, and energy per byte. However, to utilize all on-chip memories of a GPU core in cache mode and thus enable larger extended LLC capacities, the extended LLC kernel aims to combine the implementation via register file with the implementation via L1 and/or via shared memory. To this end, the extended LLC kernel allocates a number of warps to the implementation via register file, and the remaining number of warps to the implementations via L1 and shared memory. We only consider the combination of the extended LLC via register file and via L1 since L1 and shared memory are unified in our evaluated GPU system (i.e., combining the extended LLC via L1 and via shared memory does *not* provide a larger extended LLC capacity).

We use our characterization results to optimize the number of warps the extended LLC kernel should allocate to each of the two extended LLC kernel implementations (via register file and via L1) to design a high-capacity and high-performance extended LLC. (1) The extended LLC kernel should allocate more than 8 warps to the implementation via register file to better utilize the register file capacity (Figure 11(a)). (2) The extended LLC kernel should allocate fewer than 48 warps to the implementation via register file to be able to allocate a number of warps to the implementation via L1. (3) Among the remaining options (8, 16, or 32 warps), using 32 warps in the extended LLC kernel via register file results in higher access bandwidth (Figure 11(c)) and lower energy per byte (Figure 11(d)), while the access latency is almost equal to the case of using 8 warps (Figure 11(b)). Hence, the extended LLC kernel combines the extended LLC via register file and via L1

$<sup>^7\</sup>mathrm{The}$  access latency of the register file, shared memory, and L1 are 2, 25, and 34 ns, respectively [8]. The access bandwidth of the register file, shared memory, and L1 are 1 TB/s, 170 GB/s, and 170 GB/s, respectively [8, 31, 36].

by allocating 32 and 16 warps to each of these two implementations, respectively. Using our characterization, we observe that for each GPU core operating in cache mode, the extended LLC via *register file+L1* has 328 KiB capacity, 185ns average access latency, 34GB/s average access bandwidth, and 61pJ average energy per byte. We use this extended LLC implementation to evaluate the effectiveness of Morpheus to boost the performance of memory-bound applications.

# 6. Methodology

Simulation methodology. We evaluate Morpheus using the AccelSim [8] cycle-level simulator. We model our baseline after the NVIDIA Ampere 3080 GPU [7]. Table 1 shows the simulation parameters modeling our baseline. To evaluate energy consumption, we use AccelWattch [37] embedded in AccelSim as the state-of-the-art GPU energy model.

Table 1: Baseline GPU configuration

| Parameter                 | Value               |

|---------------------------|---------------------|

| Number of SMs             | 68                  |

| Scheduler                 | Two-Level [18, 38]  |

| GPU Memory Interface      | 320-bit GDDR6X [39] |

| GPU Memory Capacity       | 10 GiB              |

| Conventional LLC Capacity | 5 MiB               |

| L1/Shared-Memory Capacity | 128 KiB per SM      |

| Register File Capacity    | 256 KB per SM       |

Applications. We randomly choose 14 memory-bound and 3 compute-bound applications from four benchmark suites, Rodinia [5], Parboil [6], Pannotia [40] and ISPASS [41]. Our methodology to categorize applications into memory-bound and compute-bound groups is based on our experiment in §3. The performance of the compute-bound applications to increases (linearly) with more GPU cores. In contrast, the performance of the memory-bound applications either saturates or decreases sharply after a certain number of GPU cores. Table 2 shows the applications we choose, their names, and their types (memory-bound or compute-bound). We run each application either entirely, or until the application reaches two billion executed instructions.

**Table 2: Evaluated Applications**

| Application                                   | Name    | Type          |  |  |  |

|-----------------------------------------------|---------|---------------|--|--|--|

| Breadth-First Search [6]                      | p-bfs   | Memory-bound  |  |  |  |

| Computational fluid dynamics [5]              | cfd     | Memory-bound  |  |  |  |

| Discrete Wavelet Transform (2D) [5]           | dwt2d   | Memory-bound  |  |  |  |

| Stencil [6]                                   | stencil | Memory-bound  |  |  |  |

| Breadth-First Search [5]                      | r-bfs   | Memory-bound  |  |  |  |

| Back Propagation [5]                          | bprob   | Memory-bound  |  |  |  |

| sgemm [6]                                     | sgem    | Memory-bound  |  |  |  |

| Needleman-Wunsch [5]                          | nw      | Memory-bound  |  |  |  |

| Page Rank [40]                                | page-r  | Memory-bound  |  |  |  |

| K-means [5]                                   | kmeans  | Memory-bound  |  |  |  |

| Histogram [6]                                 | histo   | Memory-bound  |  |  |  |

| Magnteic Resonance Imaging-Gridding [6]       | mri-gri | Memory-bound  |  |  |  |

| Sparse-Matrix Dense-Vector Multiplication [6] | spmv    | Memory-bound  |  |  |  |

| Lattice-Boltzmann [6]                         | lbm     | Memory-bound  |  |  |  |

| LIBOR Monte Carlo [41]                        | lib     | Compute-bound |  |  |  |

| HotSpot [5]                                   | hotsp   | Compute-bound |  |  |  |

| Magnetic Resonance Imaging - Q [6]            | mri-q   | Compute-bound |  |  |  |

**Evaluated Systems.** We evaluate six systems. (1) *BL*: baseline

system that models a GPU architecture with the parameters reported in Table 1. BL employs all available GPU cores (i.e., 68) for application execution. To provide a fair comparison, we add the extra on-chip storage in Morpheus, the 16-KiB Bloom filters (§4.1.2) and the 5-KiB extended LLC query logic unit (§4.1.3) per LLC partition (overall; 21 KiB×#partitions = 210 KiB), to the conventional LLC capacity. (2) IBL: improved baseline system where we use the number of GPU cores that provides the maximum performance for each application and power-gate the remaining cores. Table 3 (second row) reports the number of GPU cores we use for each application in IBL. (3)  $IBL-4 \times -LLC$ : IBL with  $4 \times$  the LLC size. We increase the total LLC capacity by increasing the number of the LLC banks (without adding any latency and power impact). (4) Frequency-Boost: IBL with higher frequency memory system components, including the interconnection network, conventional LLC, and off-chip DRAM channels. This system uses the energy saved by power-gated GPU cores in IBL to increase the clock frequency of the aforementioned components in the GPU memory system by 10%-20% depending on the number of power-gated cores. (5) *Unified-SM-Mem*: *IBL* that has a larger L1 data cache capacity by using methods from prior works on unifying L1 data cache, shared memory, and the register file [42, 43]. Our baseline architecture (BL) already unifies L1 data cache and shared memory. In *Unified-SM-Mem*, we add the amount of unused register file space to the L1 data cache (without additional latency impact). (6) Different versions of Morpheus with and without our various optimizations, namely Morpheus-Basic, Morpheus-Indirect-MOV, Morpheus-Compression, and Morpheus-ALL. For all Morpheus variants, we determine the number of GPU cores in cache mode that results in the highest performance per application offline.<sup>8</sup> Table 3 (third and fourth rows) reports the number of GPU cores in compute mode for Morpheus-Basic and Morpheus-ALL. We observe that Morpheus-ALL uses a larger number of GPU cores in compute mode because it employs cache compression (§4.3.1), which enables larger extended LLC capacities per SM in cache mode, which in turn enables higher performance with more application threads.

#### 7. Evaluation

We evaluate the effectiveness of Morpheus compared to different baselines. §7.1 shows the overall effect of Morpheus on GPU performance. §7.2 evaluates the effect of Morpheus on GPU energy efficiency. §7.3 analyzes the effectiveness of our Bloom filter-based hit/miss predictor design. §7.4 shows the effect of Morpheus on on-chip and off-chip bandwidth utilization. §7.5 studies the storage and power overheads of Morpheus.

<sup>&</sup>lt;sup>8</sup>This is a static version of Morpheus in which we adjust the number of SMs in cache mode before running the application. If the best configuration per application is not known prior to execution, we could use online profiling techniques similar to prior work [44-46] on top of Morpheus, to learn the best configuration for a running application and dynamically adjust the number of cores in cache mode. We leave the use of online profiling techniques with Morpheus to future work.

Table 3: Number of GPU cores executing application threads for different evaluated systems (#available GPU cores is 68).

| Application    | p-bfs | cfd | dwt2d | stencil | r-bfs | bprob | sgem | nw | page-r | kmeans | histo | mri-gri | spmv | lbm | lib | hotsp | mri-q |

|----------------|-------|-----|-------|---------|-------|-------|------|----|--------|--------|-------|---------|------|-----|-----|-------|-------|

| IBL            | 68    | 68  | 68    | 68      | 68    | 68    | 68   | 68 | 68     | 24     | 53    | 34      | 42   | 34  | 68  | 68    | 68    |

| Morpheus-Basic | 32    | 42  | 42    | 50      | 34    | 39    | 48   | 18 | 42     | 37     | 47    | 36      | 44   | 32  | 68  | 68    | 68    |

| Morpheus-ALL   | 40    | 55  | 54    | 56      | 37    | 41    | 54   | 26 | 46     | 47     | 52    | 43      | 47   | 36  | 68  | 68    | 68    |

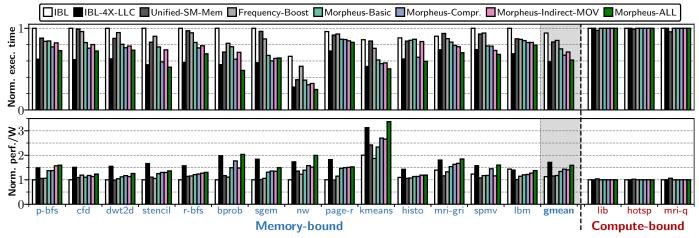

# 7.1. Performance Analysis

To study the effectiveness of Morpheus at improving GPU performance, we measure application execution times on *nine* different systems, namely BL, IBL, IBL- $4\times$ -LLC, Frequency-Boost, Unified-SM-Mem, Morpheus-Basic, Morpheus-Compression, Morpheus-Indirect-MOV, and Morpheus-ALL (see §6 for details of each evaluated system). Figure 12 (top) shows the results. The x-axis shows applications in two groups, memory-bound and compute-bound. The y-axis shows the application execution time (the lower the better) normalized to the baseline (BL) system.

We make five key observations. First, Morpheus (i.e., Morpheus-ALL) improves performance greatly with all its optimizations over all real baselines and across all memory-bound applications. Specifically, Morpheus significantly improves GPU performance by an average of 27% over the best real baseline (i.e., Unified-SM-Mem) and by 39%, 32%, and 29% over BL, IBL, and Frequency-Boost, respectively. Second, Morpheus performs within 3% of an ideal baseline with 4× the LLC (i.e., IBL- $4 \times -LLC$ ) at only small overhead (see §7.5). Third, Morpheus-Compression improves performance by an average of 9% over Morpheus-Basic, by providing a larger extended LLC capacity. Fourth, Morpheus-Indirect-MOV improves performance by an average of 4% over *Morpheus-Basic*, by providing a lower extended LLC access latency. Fifth, Morpheus does not affect the performance of compute-bound applications since all GPU cores stay in compute mode for such applications. We conclude that Morpheus is highly effective at improving the performance of memory-bound GPU applications.

# 7.2. Energy Efficiency Analysis

To study the effect of Morpheus on GPU energy efficiency, we calculate GPU *performance/watt* by dividing the overall GPU IPC by GPU average power consumption for each of the nine systems we evaluate. Figure 12 (bottom) reports the results, where the y-axis shows performance/watt (the higher the better). We normalize the results to the performance/watt of the baseline (*BL*) system.

We make four key observations. First, Morpheus (i.e., *Morpheus-ALL*) improves GPU energy efficiency greatly over all real baselines and across all memory-bound applications. Morpheus provides 58%, 38%, 35%, and 33% better energy efficiency compared to *BL*, *IBL*, *Unified-SM-Mem*, and *Frequency-Boost*, on average, respectively. Morpheus' energy efficiency improvement is due to (1) reducing the number of energy-hungry off-chip memory accesses and (2) Morpheus' large speedups over all real baselines (§7.1). Second, the energy efficiency of the *Morpheus-ALL* system is within 6% of that of the *IBL-4×-LLC* system, for which we *ideally* assume *no* power and latency impact while using a 4× larger LLC. Third,

Morpheus-Compression and Morpheus-Indirect-MOV improve the energy efficiency of Morpheus-Basic by 8% and 5%, on average, respectively. Fourth, Morpheus slightly reduces the performance/watt of compute-bound applications (less than 1%) compared to the baseline (BL) system due to the power consumption overhead of the Morpheus controller (see §7.5 for our overhead analysis). A more optimized Morpheus can power-gate the Morpheus controller completely for compute-bound applications to avoid the power overhead for such workloads [47-50]. We conclude that Morpheus is highly effective at improving the energy efficiency of memory-bound GPU applications.

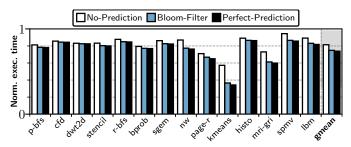

#### 7.3. Effect of Hit/Miss Prediction

To study the effectiveness of Morpheus' hit/miss prediction technique at improving Morpheus' performance, we compare the execution time of the 14 memory-bound applications on a *Morpheus-Basic*-enabled GPU with three hit/miss prediction designs: (1) our Bloom-Filter design (§4.1.2), (2) No-Prediction, where we disable the hit/miss prediction technique and immediately forward all extended LLC requests to the extended LLC, and (3) Perfect-Prediction, where we assume 100% accuracy for the hit/miss prediction technique. Figure 13 reports the execution time results normalized to the baseline system (BL). We make two key observations. First, No-Prediction has a 9% higher execution time compared to the Bloom-Filter design, on average. Second, Bloom-Filter's results are within 1% of Perfect-Prediction. We conclude that hit/miss prediction is important for Morpheus' performance and that our predictor design is very effective.

# 7.4. On-Chip & Off-Chip Bandwidth Analysis

To further analyze the sources of Morpheus' performance improvement, we study the effect of Morpheus on (1) *LLC throughput*, (2) *interconnect performance*, and (3) *off-chip bandwidth utilization*.

LLC throughput. In this study, we aim to measure (1) by how much Morpheus improves the LLC throughput and (2) determine the reasons for the LLC throughput increase. To this end, we measure the LLC (both the conventional LLC and extended LLC) throughput for four systems, *BL, IBL, Morpheus-ALL*, and *larger-LLC*. The goal of evaluating the *larger-LLC* system is to distinguish between two different benefits of Morpheus on LLC (larger LLC capacity and higher number of LLC banks). In *larger-LLC*, we increase the conventional LLC size to be exactly the same as the total LLC capacity in *Morpheus-ALL* (i.e., conventional LLC + extended LLC) without increasing the number of conventional LLC banks. This is to isolate the

Figure 12: Comparison of eight GPU systems' execution time (top) and performance/watt (bottom) for 14 memory-bound and 3 compute-bound applications, normalized to the baseline system (BL)

Figure 13: Effect of hit/miss prediction on execution time for 14 memory-bound applications with *Morpheus-Basic*, normalized to the baseline system (BL)

effect of an increased LLC capacity (relative to *BL*) from the effect of an increased number of banks. The LLC capacity of *larger-LLC* varies between applications, as it depends on the number of cores operating in cache mode in *Morpheus-ALL*, which is determined on a per application basis.

We make two key observations. First, *Morpheus-ALL* improves the LLC throughput by an average of 75% and 68% (up to 374% and 236%) compared to *BL* and *IBL*, respectively. Second, the *larger-LLC* system improves LLC throughput by an average of 42% compared to *BL*. We conclude that *Morpheus-ALL*'s higher throughput comes from *both* (1) increasing the LLC capacity and (2) increasing the number of banks.

**Interconnect Performance.** Morpheus increases the load on the interconnection network by servicing the extended LLC requests through it. We study the performance of the GPU interconnection network in Morpheus. We measure the overall network injection rate, network throughput, and average interconnect latency for two designs, *BL* and *Morpheus-ALL*. We make three key observations. First, *Morpheus-ALL* increases the load of the on-chip network by 97% compared to *BL*, on average. Second, both network injection rate and throughput increase in *Morpheus-ALL* by the same amounts, showing that the GPU interconnection network does *not* saturate due to handling more traffic. Third, the higher load causes 7% longer average network latency compared to *BL*. We observe *no* over-

all application performance loss due to the longer average network latency.

**Off-chip Bandwidth Utilization.** To study the effect of Morpheus on off-chip bandwidth utilization, we measure the off-chip bandwidth utilization for two systems, *IBL* and *Morpheus-ALL*. We observe that *Morpheus-ALL* reduces off-chip bandwidth utilization by an average of 17% compared to *IBL*. This is mainly due to the fact that the larger LLC enabled by Morpheus reduces the number of off-chip main memory requests. To further analyze the reason behind the bandwidth utilization reduction, we measure the LLC MPKI (misses per kilo instructions) for both *IBL* and *Morpheus-ALL*. We observe that *Morpheus-ALL* reduces the LLC MPKI by 47% compared to *IBL*.

# 7.5. Overhead Analysis

We analyze the storage and power overheads of the additional hardware required by Morpheus (i.e., the Morpheus controller). **Storage cost.** The Morpheus controller has two main storage components: the hit/miss prediction unit (§4.1.2) and the extended LLC query unit (§4.1.3). The hit/miss prediction unit has 16-KiB of Bloom filter storage per LLC partition. The extended LLC query unit has a 5-KiB on-chip storage per LLC partition to store the request queue, warp status table, and read/write data buffers (§4.1.3). Overall, Morpheus adds 21 KiB per LLC partition; which is approximately 4% of the conventional LLC capacity per LLC partition in the NVIDIA RTX 3080 GPU.

**Power Consumption.** We measure the power consumption of the additional hardware required by Morpheus using (1) CACTI 6.5 [51] for storage units and (2) the synthesized Verilog HDL models with the NanGate 45nm open cell library [52] for logic units. We observe that the Morpheus controller imposes a 0.93% overhead to the total GPU power consumption. Note that we already take into account Morpheus' power consumption overhead for the energy efficiency analysis in §7.2.

# 8. Related Work

To our knowledge, this is the first work to propose extending the GPU last-level cache capacity by repurposing the on-chip memory units (i.e., register files, L1 caches, scratchpad memories) of otherwise unused GPU cores. In this section, we briefly review related work in four GPU domains: (1) *increasing cache capacity*, (2) *increasing interconnection network performance*, (3) *controlling cache contention*, and (4) *helper threads*.