# Security, Performance and Energy Implications of Hardware-assisted Memory Protection Mechanisms on Event-based Streaming Systems

Christian Göttel, Rafael Pires, Isabelly Rocha, Sébastien Vaucher, Pascal Felber, Marcelo Pasin, Valerio Schiavoni University of Neuchâtel, Switzerland — first.last@unine.ch

# I. HARDWARE-ASSISTED MEMORY PROTECTION MECHANISMS

Major cloud providers such as Amazon [1], Google [2] and Microsoft [3] provide nowadays some form of infrastructure as a service (IaaS) which allows deploying services in the form of virtual machines [4], containers [5] or bare-metal [6] instances. Although software-based solutions like homomorphic encryption exit, privacy concerns [7] greatly hinder the deployment of such services over public clouds. It is particularly difficult for homomorphic encryption to match performance requirements of modern workloads [8]. Evaluating simple operations on basic data types with HElib [9], a homomorphic encryption library, against their unencrypted counter part reveals, that homomorphic encryption is still impractical under realistic workloads.

In recent attempts to enable privacy-preserving operations, publish/subscribe systems among other types of communication services have received much attention. Meanwhile, Intel and AMD have introduced hardware-assisted memory protection mechanisms inside x86 processors to provide answers overcoming the limitation of current software-based solutions. With the launch of the Skylake generation, Intel added a new technology called Software Guard Extension (SGX) [10] to their processors. SGX allows applications to create secure enclaves protecting the confidentiality and integrity of data and its associated code during execution. An application has to be signed and shipped as an unencrypted shared library (respectively a shared object on Linux systems) in order to be executed in an enclave. Execution of an enclave on a genuine Intel processor with enabled SGX technology can be ensured by a remote attestation protocol. The enclave is stored in the enclave page cache (EPC) when executed; a limited memory area predefined at boot time. Page eviction is handled by the SGX driver and confidentiality, integrity, replay and tamper protected by the *memory encryption engine* (MEE) [11]. AMD's recently introduced Zen microarchitecture is capable of transparently encrypting memory pages using their novel technologies Secure Memory Encryption (SME) and Secure Encrypted Virtualization (SEV). SME and SEV make use of ephemeral encryption keys required by an AES engine located on the core's memory controller. While SME

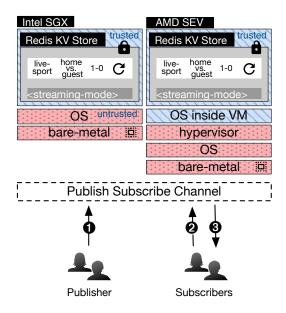

Fig. 1: Architecture of our system and differences when deployed with Intel SGX and AMD SEV-ES. The components with a diagonally hatched pattern on a blue background are trusted, those with a dotted red background are untrusted, respectively. Redis is configured in *streaming-mode* [13].

creates a single key to encrypt the entire system's memory, SEV can generate and assign a key to a limited number of distinct virtual machines and a single hypervisor running on the processor. The creation of the memory keys is delegated to the *secure processor* (SP), an ARM TRUSTZONE-enabled system-on-chip (SoC) embedded on-die [12].

### II. ARCHITECTURE

We designed and implemented a simple yet pragmatic eventbased streaming system to evaluate our execution. The core of our system consists of a key-value store with native support to register and trigger callback functions associated to CRUD operations (*i.e.*, create, read, update, delete) on key-value entries. These callback functions implement matching filters for subscribers of a publish/subscribe system, that will receive events upon notification of the channel.

The main components of the event-based streaming system are depicted in Figure 1 with Intel SGX (left) and AMD

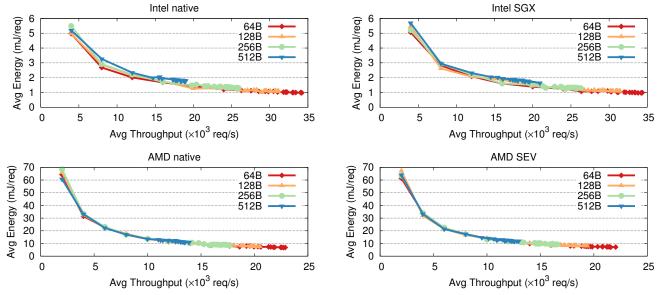

Fig. 2: Macro-benchmark: energy cost of publish/subscribe.

SEV (right). All potentially sensitive components *i.e.*, the key-value store and its content, the callback functions and the endpoints of the publish/subscribe channels, have to be protected by SGX or SEV. However, only the key-value store entries are considered to be protected by SGX or SEV in our implementation. Furthermore, we do not include other additional stages in the processing pipeline nor do we explicitly include broker or broker overlays [14]. Under these carefully controlled conditions side-effects of SGX and SEV can be better highlighted on the main processing node, in particular memory-bound operations and their energy cost.

The workflow of operations is as follows. First, a subscriber manifests its interests by subscribing to the channel (Figure 1-1). Then, publishers start emitting events with a given content, e.g., the results of a sport event (Figure 1-1). As soon as the content is updated, a callback function is triggered (Figure 1-1). Finally, the potential subscriber(s) receive the event (Figure 1-1).

# III. IMPLEMENTATION

The architecture was implemented on top of well-known open-source systems and libraries. Redis [15] (v4.0.8), an efficient and lightweight in-memory key-value store, is used as core component. It also features a built-in publish/subscribe system, which is exploited in order to realize our experimental platform. Publishers and subscribers connect to the channels provided by Redis using Jedis [16] (v2.9.0) Java bindings for Redis. The callback system is implemented by leveraging Redis' ability to load external modules [17]. Despite Redis being a single threaded application, modules can be run in a multi-threaded setup.

While applications run under AMD SEV do not require any changes, they do need to be modified under Intel SGX. Graphene-SGX [18] is a library allowing to run unmodified applications inside enclaves and was used for this benchmark.

In order to run unmodified applications under SGX, a manifest file has to be provided to Graphene-SGX specifying the resources, *e.g.*, shared libraries, files, network endpoints, which the enclave is allowed to make use of. The manifest file is pre-processed by an auxiliary tool generating signatures that are later checked by the Graphene loader.

Various workloads were injected using YCSB [19], v0.12.0 commit 3d6ed690, to record latency, throughput, performance and energy values.

## IV. EVALUATION

The benchmark measures the latency from the moment a publisher emits a new event until the moment all subscribers receive the content of the event. Four different configurations of the system are evaluated: (i) Intel without SGX protection, (ii) with SGX by leveraging Graphene, (iii) AMD without memory protection and (iv) AMD with SEV. Publishers are configured such that they inject new events at fixed throughputs with fixed message sizes ranging from 64 B up to 512 B.

Measured latencies for smaller message sizes are consistently lower for higher throughputs (requests/second). The cost of serialization reduces the efficiency of our system for larger message sizes. A pairwise comparison of the configurations for Intel and AMD reveals how these memory protection mechanisms are negatively affecting the observed latencies, which is particularly evident for Intel configurations. This observation is further confirmed by bandwidth usage values.

The energy cost of messages send over the publish/subscribe system is shown in Figure 2. As the system begins to occupy a significant amount of the machine's resources, energy consumption begins to increase at a linear rate relative to the target throughput. This behavior is reflected by the decreasing energy cost per message before reaching a minimal energy cost.

Memory requirements do not exceed the available EPC for the Intel configurations under these evaluation settings.

Consequently, the measurements indicate that both memory protection mechanisms consume an even amount of energy compared to their native setup.

Due to the energy being recorded for the entire system using an external power measurement device, it becomes difficult to make an implication on the energy consumption of the memory protection mechanisms. In a next step we are developing tools to measure the energy consumption of precesses at a much finer grained level, for instance the processor's core. Such tools would then give us the opportunity to observe in more detail the influence of memory protection mechanisms on processes and assist in the development of novel security and energy-aware system components.

### ACKNOWLEDGMENTS

The authors would like to thank Christof Fetzer for the discussions on hardware-assisted memory protection mechanisms. The research leading to these results has received funding from the European Union's Horizon 2020 research and innovation programme under the LEGaTO Project (legatoproject.eu), grant agreement No 780681.

### REFERENCES

- [1] (2016, Nov. 30) Coming Soon: Amazon EC2 C5 Instances, the next generation of Compute Optimized instances. About AWS, What's New. Amazon Web Services, Inc., 2016. Accessed on: 2018-03-05. [Online]. Available: http://amzn.to/2nmIiH9

- [2] B. Darrow. (2017, Feb. 24) Google Is First in Line to Get Intel's Next-Gen Server Chip. Fortune. Time Inc., 2017. Accessed on: 2018-03-05. [Online]. Available: http://for.tn/2lLdUtD

- [3] M. Russinovich. (2017, Sep. 14) Introducing Azure Confidential Computing. Microsoft Azure Blog. Microsoft Corporation, 2017. Accessed on: 2018-03-05. [Online]. Available: https://azure.microsoft.com/ en-us/blog/introducing-azure-confidential-computing/

- [4] (2018) Amazon EC2. Amazon Web Services, Inc., 2018. Accessed on: 2018-03-05. [Online]. Available: https://aws.amazon.com/ec2/

- [5] (2018) Kubernetes Engine. Google Cloud. Google LLC, 2018. Accessed on: 2018-03-05. [Online]. Available: https://cloud.google.com/kubernetes-engine/

- [6] J. Barr. (2017, Nov. 28) Amazon EC2 Bare Metal Instances with Direct Access to Hardware. AWS News Blog. Amazon Web Services, Inc., 2017. Accessed on: 2018-03-05. [Online]. Available: http://amzn.to/2j0bQuo

- [7] S. Pearson and A. Benameur, "Privacy, Security and Trust Issues Arising from Cloud Computing,"

- [8] M. Naehrig, K. Lauter, and V. Vaikuntanathan, "Can Homomorphic Encryption Be Practical?" Proc. 3rd ACM Workshop Cloud Comput. Security Workshop,

- 2010 IEEE 2nd Int. Conf. Cloud Comput. Technol. Sci., ser. CloudCom '10. IEEE Computer Society, Nov. 2010, pp. 693–702. [Online]. Available: https://doi.org/10.1109/CloudCom.2010.66 ser. CCSW '11. ACM, 2011, pp. 113–124. [Online]. Available: http://doi.acm.org/10.1145/2046660.2046682

- [9] S. Halevi and V. Shoup, "Design and Implementation of a Homomorphic-Encryption Library," IBM Research, Yorktown Heights, NY, USA, Tech. Rep., Nov. 30 2012. [Online]. Available: https://researcher.watson.ibm. com/researcher/files/us-shaih/he-library.pdf

- [10] V. Costan and S. Devadas, "Intel SGX Explained," *IACR Cryptology ePrint Archive*, vol. 2016, no. 86, pp. 1–118, Feb. 2017. [Online]. Available: https://eprint.iacr.org/2016/086

- [11] S. Gueron, "A Memory Encryption Engine Suitable for General Purpose Processors." *IACR Cryptology ePrint Archive*, vol. 2016, no. 204, pp. 1–14, 2016.

- [12] D. Kaplan, J. Powell, and Woller, T. "AMD Encryption," Memory **AMD** Developer Central, Advanced Micro Devices, Inc., pp. 1-12,Apr. 21 2016. [Online]. Available: https://developer.amd.com/wordpress/media/2013/12/ AMD\_Memory\_Encryption\_Whitepaper\_v7-Public.pdf

- [13] J. L. Carlson. (2013, Jun.) Redis in action eBook. Redis Streaming. Redis Labs. Accessed on: 2018-04-28. [Online]. Available: https://redislabs.com/ebook/part-2-core-concepts/ chapter-8-building-a-simple-social-network/ 8-5-streaming-api/

- [14] P. Eugster, P. Felber, R. Guerraoui, and A.-M. Kermarrec, "The Many Faces of Publish/Subscribe," ACM Comput. Surveys (CSUR), vol. 35, no. 2, pp. 114–131, Jun. 2003. [Online]. Available: http://doi.acm.org/10.1145/857076.857078

- [15] "Redis," 2018, Accessed on: 2018-03-05. [Online]. Available: https://redis.io/

- [16] "Jedis," 2018, Accessed on: 2018-03-11. [Online]. Available: https://github.com/xetorthio/jedis

- [17] "Redis Modules," 2018, Accessed on: 2018-03-12. [Online]. Available: https://redis.io/modules

- [18] C. che Tsai, D. E. Porter, and M. Vij, "Graphene-SGX: A Practical Library OS for Unmodified Applications on SGX," USENIX ATC'17, pp. 645–658.

- [19] B. F. Cooper, A. Silberstein, E. Tam, R. Ramakrishnan, and R. Sears, "Benchmarking cloud serving systems with YCSB," Proc. 1st ACM Symp. Cloud Comput., ser. SoCC '10. ACM, Jun. 2010, pp. 143–154.