# Multi-Casting Mesh AER: A Scalable Assembly Approach for Reconfigurable Neuromorphic Structured AER Systems. Application to ConvNets

C. Zamarreño-Ramos, A. Linares-Barranco, T. Serrano-Gotarredona, and B. Linares-Barranco

Abstract—This paper presents a modular, scalable approach to assembling hierarchically structured neuromorphic AER (Address Event Representation) systems. The method consists of arranging modules in a 2D mesh, each communicating bidirectionally with all four neighbors. Address events include a module label. Each module includes an AER router which decides how to route address events. Two routing approaches have been proposed, analyzed and tested, using either destination or source module labels. Our analyses reveal that depending on traffic conditions and network topologies either one or the other approach may result in better performance. Experimental results are given after testing the approach using high-end Virtex-6 FPGAs. The approach is proposed for both single and multiple FPGAs, in which case a special bidirectional parallel-serial AER link with flow control is exploited, using the FPGA Rocket-I/O interfaces. Extensive test results are provided exploiting convolution modules of  $64 \times 64$  pixels with kernels with sizes up to  $11 \times 11$ , which process real sensory data from a DVS (Dynamic Vision Sensor) retina. One single Virtex-6 FPGA can hold up to 64 of these convolution modules, which is equivalent to a neural network with  $262 \times 10^3$  neurons and almost 32 million synapses.

# I. INTRODUCTION

AER (Address-Event-Representation) is now a popular "virtual wiring" technique for interconnecting spiking neuromorphic systems [1]-[33]. The high-speed available for digital inter-chip communications is exploited in AER to timemultiplex numerous synaptic connections between neurons, which only need to be active during a spike (also called event) transmission. In AER, whenever a spiking neuron in a chip (or module<sup>1</sup>) generates a spike, its "address" (or any given ID) is written on a high speed digital bus and sent to the receiving neuron(s) in one (or more) receiver module(s). In general, AER processing modules require at least one AER input port and one AER output port. As neuromorphic systems scale up in size, complexity, and functionality, researchers have been developing more complex and smarter AER "variations" to maintain the efficiency, reconfigurability and reliability of the ever growing target systems they want to build.

Authors are with the Instituto de Microelectrónica de Sevilla (IMSE-CNM-CSIC). Av. Américo Vespucio s/n, 41092 Sevilla, Spain. Copyright (c) 2011 IEEE. Personal use of this material is permitted. However, permission to use this material for any other purposes must be obtained from the IEEE by sending an email to pubs-permissions@ieee.org.

<sup>1</sup>Throughout the paper we will be referring to generic AER modules, where a module can be one chip, several chips grouped into a PCB, several PCBs, or even a part of a chip or FPGA. One chip/FPGA could therefore hold several AER modules as well as AER buses.

In the following Section we review a set of approaches for large scale reconfigurable AER systems that have been proposed by different researchers, ranging from the sharing of a single AER bus by all AER modules, to the use of multiple independent buses or mesh type arrangements of modules which exploit communication techniques from the NoC (Network-on-Chip) research community.

# II. REVIEW OF AER APPROACHES FOR LARGE SCALE SYSTEMS

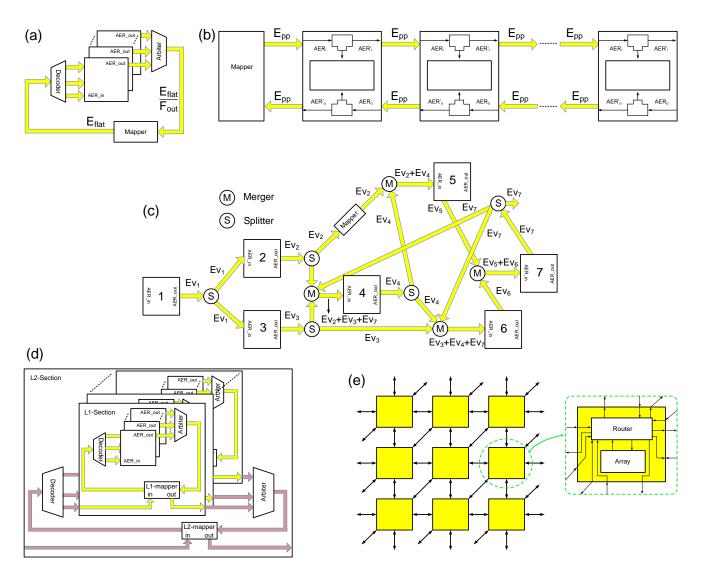

Table I summarizes a set of AER assembly techniques proposed in literature for tackling the growth of AER based processing systems. The simplest form of a generic AER concept for use in a large scale multi-module spiking neuromorphic system is illustrated in Fig. 1(a). Let us call it "Flat-AER". Each module can contain, for example, an array of neurons. Each neuron is assigned a unique global address, which identifies the module it belongs to and its position inside the module. This way, the address space of all modules' input and output AER ports is the same. All modules share a single external AER bus [3]-[9]. Connectivity between neurons is configurable and set by a look-up-table in the external programmable "Mapper". Multi fan-out can be programmed in the mapper by repeating multiple destination addresses for each incoming address. Similarly, synaptic weighting can also be implemented by programming destination address repetitions. However, event repetition (for either fan-out or weighting) severely penalizes the AER bus communication bandwidth. To overcome this, some reported neuron chips allow for an additional synaptic weight parameter to be programmed into the mapper together with the event address [7], [10]. Alternatively, some other reported neuron chips include a built-in mechanism which will implement a given fan-out and synaptic weighting from a single input event (as in pre-wired diffusive networks [11], [12] or more elaborate computational hardware [13], [18], [22], [24]). In this case, the mapper would only need to repeat an event if it is destined for neurons belonging to different modules. Normally, event addresses represent neurons. However, in some reported neuron chips that include a number of physical synapses per neuron [6], the input address can represent one specific synaptic input. In this case, the address spaces at the mapper input and output would be different, as they represent different elements.

*Flat-AER* is simple and easy to build, configure, and use. It requires a mapper memory with as many positions as there are

neurons in the system. However, the main limitation of flat-AER is its communication bandwidth. Since every single event produced by any neuron has to travel through the single AER bus and Mapper, the system's maximum total event traffic is limited by the bus bandwidth. If  $N_{tot}$  is the total number of neurons,  $f_n$  is the mean spike rate per neuron and  $F_{out}$  the average fan-out per neuron (spike repetitions introduced by the mapper to emulate the projection fields and/or synaptic weighting), the event arrival rate  $\lambda$  at the Mapper output channel is [34]  $\lambda = N_{tot} f_n F_{out}$ . If  $E_{flat}$  is the physical channel bandwidth, then the channel service rate is  $\mu = E_{flat}$ and the average time an event waits to be serviced is (assuming an M/M/1 queue model [35])  $\bar{t}_q = 1/(\mu - \lambda)$ . Consequently, the absolute maximum communication bandwidth (number of events per unit time) Ev this approach can handle is obtained when  $\lambda = E_{flat}$  and is

$$Ev_{max} = N_{tot} f_n \Big|_{max} = \frac{E_{flat}}{F_{out}} \tag{1}$$

Given  $Ev_{max}$ , it is possible to estimate the maximum allowable number of neurons for such communication architecture

$$N_{tot\_max} = \frac{Ev_{max}}{f_n} \tag{2}$$

Note that, in general and specially for rate encoded weights,  $F_{out} = n_{RF} \times n_W$  ( $n_{RF}$  is the projection field size and  $n_W$  is the synaptic weight dynamic range) can become significantly large. For example, if the projection field has a size of  $n_{RF} = 11 \times 11$  neurons and weights can have integer values ranging from  $n_W = 1$  to 32, then  $F_{out} = 3872$ .

Reported AER-bus bandwidths are presently below 100Meps (mega events per second) for point-to-point links [3]–[7], [11]–[13], [18], [22], [24]–[28], [36]–[38], although cases have been reported of high density channels and multiplexing techniques being used to achieve higher event rates [8], [33]. Flat-AER therefore allows for a total communication bandwidth in the range of  $10^8eps$  down to  $10^4eps$ , depending on fan-out.

Having several modules sharing the same physical lines degrades speed proportionally to the number of modules [26]. This can be overcome by using *Broadcast-Mesh-AER*.

"Broadcast-Mesh-AER" uses multiple point-to-point AER buses [25]-[27]. Fig. 1(b) shows its corresponding 1-D version. Each neuron in each module also has a unique global flat address. Each module has an AER input event path and an AER output event path, each with an AER input port and an AER output port. AER input events received at the input **AERi** port are sent to the module neuron array but are also passed through to the next module, via output port **AERi'**. This way, input events "hop" from module to module via independent AER point-to-point links. Consequently, the speed at each AER link is optimum and events are copied more efficiently in a pipeline fashion. Output events generated in each module also "hop" from module to module through AERo and AERo' ports until they reach the Mapper. In this scheme all input events coming from the Mapper are broadcast to all modules, and each module checks if the event is destined to the local neural array [25], [26]. However, overall network connectivity information is contained in the global mapper, and can be totally reconfigured by reprogramming the mapper (as in the *Flat-AER* approach).

One major claim of this approach is that the channel bandwidth of each point-to-point link  $E_{pp}$  improves proportionally with the number of chips  $N_{ch}$  in the network, with respect to the *Flat-AER* case where  $N_{ch}$  chips share the same AER bus<sup>2</sup> as in Fig. 1(a). The channel bandwidth of a point-to-point link  $E_{pp}$  is constant, while that of a multiple fan-out link  $E_{flat}$  degrades with the number of destination chips  $N_{ch}$ . More precisely, for typical PCBs, the bandwidth improvement of a point-to-point link is

$$E_{pp} \approx 2\left(N_{ch} - 1\right) E_{flat} \tag{3}$$

The network now has  $N_{ch}$  point-to-point links, which allows for a total communication bandwidth of  $E_{pp} \times N_{ch}$ . However, each event has to be copied to each link, so the maximum event rate is

$$Ev_{max} = \frac{E_{pp}N_{ch}}{F_{out}N_{ch}} = \frac{E_{pp}}{F_{out}} \tag{4}$$

Bandwidth is thus improved by improving  $E_{pp}$  with respect to  $E_{flat}$  proportionally to the number of chips [26].

Both Flat-AER and Broadcast-Mesh-AER use a common global flat address space and, in principle, allow for any arbitrary interconnect topology. However, practical neuromorphic systems have a pre-established hierarchical structure, depending on the functionality they implement. This has been exploited by other researchers to assemble scalable multimodule systems with independent AER-links, where each link is a physical plugged-in point-to-point bus-wire [28]. This is illustrated in Fig. 1(c), where AER splitters (blocks labeled "S" in Fig. 1(c)) and mergers (blocks labeled "M" in Fig. 1(c)) are also used for branching or de-branching links. A splitter block receives one input AER channel and replicates the traffic for n different output channels, while a merger block multiplexes n input AER channels into a single output channel. All physical links are point-to-point. In this "Pre-Structured **AER**" approach the address space is local to the neurons writing to or reading from an AER link. Optionally, local mappers can be inserted in a link to adapt address spaces from an output to an input (for example, to perform subsampling, address rotations, bit reallocations, etc.). In this approach no global Mapper is required, as the connectivity is pre-wired, and events do not need to travel through all the links. The number of links scales with the number of modules, so communication bandwidth saturation is much less likely to occur as systems scale up. However, system reconfiguration is laborious as it has to be done manually by re-plugging bus-wires, splitters, mergers, mappers, and processing modules.

In this case each point-to-point channel receives events from only a small fraction of the modules/chips. In general, we can define an effective number of independent channels  $M_{eff}$  as a fraction of the total number of chip modules  $M_{eff} = \alpha N_{ch}$ . The network maximum communication bandwidth would then be

<sup>&</sup>lt;sup>2</sup>For a more detailed explanation see [26].

TABLE I

MULTI-MODULE AER ADDRESSING SCHEMES

|            |                                               | Flat<br>AER<br>[7] | Broadcast<br>Mesh AER<br>[25]–[27] | Pre-<br>Structured<br>AER [28] | Hierarchical<br>Fractal<br>AER [29] | Router<br>Mesh<br>AER [30],<br>[31] | Cross-<br>Point<br>Interc. [32] | Multi-<br>Casting<br>Mesh<br>AER |

|------------|-----------------------------------------------|--------------------|------------------------------------|--------------------------------|-------------------------------------|-------------------------------------|---------------------------------|----------------------------------|

| Addressing | Address space                                 | flat               | flat                               | local                          | local                               | flat                                | local                           | flat                             |

|            | Broadcast to all modules                      | Yes                | Yes                                | No                             | No                                  | No                                  | No                              | No                               |

|            | Local Routing Tables to define global network | No                 | No                                 | No                             | Yes                                 | Yes                                 | Yes                             | Yes                              |

|            | Single global mapper                          | Yes                | Yes                                | No                             | No                                  | No                                  | No                              | No                               |

| Props.     | isolated neurons                              | Yes                | No                                 | No                             | Yes                                 | No                                  | No                              | No                               |

| Module Pro | neurons with synapses                         | No                 | Yes                                | Yes                            | No                                  | Yes                                 | Yes                             | Yes                              |

|            | events with synaptic weighting                | Yes                | No                                 | No                             | Yes                                 | No                                  | No                              | No                               |

|            | projection fields with synaptic weighting     | No                 | Yes                                | Yes                            | No                                  | Yes                                 | Yes                             | Yes                              |

|            | physical synapses                             | No                 | Yes                                | No                             | Yes                                 | No                                  | Yes                             | No                               |

Fig. 1. Illustration of different multi-module AER assembly options: (a) Flat-AER, (b) Broadcast-Grid-AER, (c) Pre-Structured-AER, (d) Hierarchical-Fractal-AER, (e) Router-Mesh-AER.

$$Ev_{max} = M_{eff}E_{pp} = \alpha N_{ch}E_{pp} \tag{5}$$

Parameter  $F_{out}$  does not appear anywhere, since the projection fields and synaptic weighting are now implemented inside each event-processing module. As an illustrative example, Fig. 1(c) has  $N_{ch}=7$  modules, each generating an output event rate  $Ev_i$ . The distribution of splitters and mergers determine potential bottlenecks as

$$Ev_{1_{max}} \le E_{pp}$$

,  $Ev_{2_{max}} + Ev_{4_{max}} \le E_{pp}$

$Ev_{2_{max}} + Ev_{3_{max}} + Ev_{7_{max}} \le E_{pp}$

$Ev_{5_{max}} + Ev_{6_{max}} \le E_{pp}$

$Ev_{3_{max}} + Ev_{4_{max}} + Ev_{7_{max}} \le E_{pp}$  (6)

under these constraints, the absolute maximum capacity of this particular network can be obtained by applying constraint optimization to eqs. (6), resulting in

$$Ev_{max} = \sum Ev_{i_{max}} =$$

$$= \left(1 + \frac{1}{2} + \frac{1}{4} + \frac{1}{2} + \frac{1}{2} + \frac{1}{2} + \frac{1}{4}\right) E_{pp} = 4E_{pp}$$

(7)

Thus, in this case  $M_{eff}=4$  and  $\alpha=M_{eff}/N_{ch}=0.57$ . In this approach the optimum point-to-point bandwidth  $E_{pp}$  is therefore further improved, proportionally to the number of chips (by a factor  $\alpha N_{ch}=M_{eff}=4$ , in this case).

Joshi et al. recently suggested a "Hierarchical-Fractal-AER" approach [29], illustrated in Fig. 1(d), which extends the basic Flat-AER concept of Fig. 1(a) in a hierarchical fashion. It exploits the assumption that nearby neurons are more heavily interconnected than more distant ones. Address space is expanded as events need to climb up in the hierarchy. This way, more intense local traffic is transferred very fast in parallel at the numerous lower level modules, while longer range but sparser traffic needs to traverse levels of hierarchy and is slower. Disregarding the traffic at the higher hierarchies, if  $M_{L1}$  is the number of lowest level  $L_1$  parallel sections and  $N_{L1}$  the number of chips per  $L_1$  section ( $N_{ch} = M_{L1} \times N_{L1}$ ), then the absolute maximum network bandwidth would be

$$Ev_{max} = M_{L1} \frac{E_{hier}}{F_{out}} \tag{8}$$

with  $E_{pp} \approx 2 \left( (N_{ch}/M_{L1}) - 1 \right) E_{hier}$ . This way, maximum network bandwidth can be expressed as

$$Ev_{max} \approx \frac{1}{2} \frac{N_{ch}}{N_{L1}^2} \frac{E_{pp}}{F_{out}} = \frac{1}{2} \frac{M_{L1}}{N_{L1}} \frac{E_{pp}}{F_{out}}$$

(9)

Depending on the ratio  $M_{L1}/N_{L1}$  a considerable improvement can be achieved with respect to *Flat-AER*.

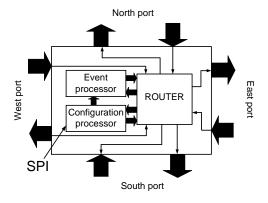

Another approach, illustrated in Fig. 1(e), is what we call here "Router-Mesh-AER" [30]. Here again neurons have a global flat address which identifies their module and their address within the module, but there is no external Mapper

through which all events have to pass. Instead, the mapping table is contained within a "Router" in each module. The router also decides the ports through which an event is sent to reach its destination module. Events are therefore not broadcast to all modules, but optimum "hop" paths are established in a multicast fashion. The main problem is that a very large mapping table needs to be programmed in each module. However, to simplify these tables, optimizations can be computed for each module router depending on the system topology, and default routing paths can be established for event addresses not listed in the tables [30]. This mesh approach has been traditionally used in NoC (Network on Chip) [39] topologies to assemble high performance multi-core processor systems for high performance computing applications [40]-[42]. The maximum network bandwidth for mesh type approaches will be computed in the next Section.

Another approach currently being developed, but at wafer scale [32], exploits massive programmable cross-point interconnects to reconfigure the network topology. We have included this method in Table I for comparison, although we are focusing more on multi-chip systems. Nonetheless, this wafer scale approach also includes off-wafer re-routing (and event re-timing) procedures for longer range and delay-controlled interconnects [33].

In all of the previously listed methods that use a global flat address space, each event includes a module ID that corresponds to the module where the event was generated. Let us call this "Source-driven" coding. However, it is also possible to label the event with the ID of the destination module instead. Let us call this "Destination-driven" coding.

In this paper we will consider a type of Pre-Structured-AER approach. However, instead of having manually pluggable links, modules are arranged in a 2D-Mesh while inter-module links are configured through in-module routers. We call this "Multi-Casting-Mesh-AER". The approach is similar to the "Router-Mesh-AER" except that the module router tables only contain information on the module-to-module links, instead of the full inter-neuron connectivity. We will analyze both 'source-driven' and 'destination-driven' codings and will show experimental results from example vision processing systems implemented on FPGA prototyping boards, based on Convolutional Neural Networks (ConvNets) [43]–[47].

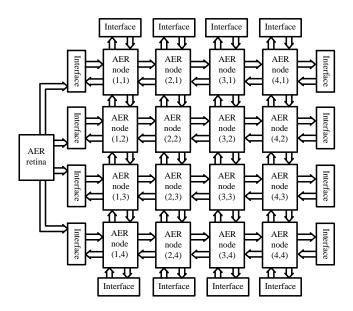

Fig. 2 shows the 2D network topology we used for *Multi-Casting-Mesh-AER*. The modules communicate bidirectionally and orthogonally with their neighbors through point-to-point AER links. The number of links in the network (and, thus, the network bandwidth) depends on the number of links per module. For the case shown in Fig. 2, each node has 4 links. If the mesh has  $N_{ch} = M_1 M_2$  modules, the total number of inter-module links is  $^3 N_l = 2[(M_1 - 1)M_2 + (M_2 - 1)M_1] = 4M_1M_2 - 2(M_1 + M_2) \approx 4N_{ch}$ . Each event needs to hop through a number of links to travel from its source module to its destination module. Let us call  $n_h$  the average number of hops per traveling event. This average number  $n_h$

$^3$ For the specific *Router-Mesh-AER* shown in Fig. 1(e) there are 6 intermodule links, thus  $N_l=2[(M_1-1)M_2+(M_2-1)M_1+(M_1-1)(M_2-1)]=6M_1M_2-4(M_1+M_2)+2\approx 6N_{ch}$ . In a 2D mesh, up to 8 links per module are possible. In a 3D mesh, up to 26 links per module are possible.

is application specific, but would usually be in the order of a fraction of  $M_1$  or  $M_2$ . The network absolute maximum bandwidth is

$$Ev_{max} = \frac{N_l}{n_h} \frac{E_{pp}}{F_{Mout}} \tag{10}$$

where  $F_{Mout}$  is the module fan-out, representing the number of routing paths a single event is sent through in order to reach all its destination nodes.

Table II summarizes how the absolute maximum communication bandwidth  $Ev_{max}$  scales with number of chips  $N_{ch}$ for the different multi-chip approaches. From eq. (2), the maximum allowable number of neurons  $N_{tot\_max}$  would also scale proportionally to  $Ev_{max}$  (for a fixed  $f_n$ ). We can see that for Flat-AER,  $Ev_{max}$  (and  $N_{tot\_max}$ ) scales down with  $N_{ch}$ , while for Broadcast-Mesh-AER,  $Ev_{max}$  (and  $N_{tot\_max}$ ) stays constant. Hierarchical-Fractal-AER can be made to scale efficiently depending on the relative choice of  $M_{L1}$  and  $N_{L1}$ . For example, if  $N_{L1}$  is fixed, then  $Ev_{max}$  would scale linearly with  $N_{ch}$ . All three approaches (Flat, Broadcast-Mesh, Hierarchical-Fractal) are penalized by neuron fan-out  $F_{out}$ . Pre-Structured-AER is the most efficient, as it scales linearly with  $N_{ch}$  and has no fan-out penalty. However, it is not practical from a reconfigurability point of view. The 2D mesh-based approaches scale linearly with  $N_{ch}$ , although term  $n_h$  might have (square-root or log-type) dependence on  $N_{ch}$ depending on the specific application. However, the module fan-out  $F_{Mout}$  penalty is usually relatively small.

# III. ROUTING IN MULTI-CASTING-MESH-AER

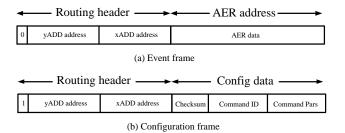

In Fig. 2, each module in the mesh is identified by a 2D index (xNODE, yNODE). From now on let us call each module in this 2D mesh an AER-node. The internal structure of an AER-node is shown in Fig. 3. It contains a Router, a local Event Processor (or neuron/synapse array), and a Configuration Processor (to set configurable parameters in the Event *Processor* or *Router*). The *Router* receives external events from the four neighbors and, based on its programmed routing tables, decides whether to send them to the local processors or to other neighbors. For events generated by the internal Event Processor, the Router adds the corresponding node index and sends them through the programmed ports. Thus, the Router introduces a network layer between the processing units' logic layer and the physical layer implementation. A heading bit distinguishes between configuration commands to be handled by the Configuration Processor, and data events to be handled by the Event Processor. The Configuration *Processor* can also receive commands through an SPI (Serial Peripheral Interface) connection. Other heading information identifies the node 2D index (xNODE, yNODE) coded in the event. This index identifies either the source node sending the event to the mesh (in the case of a Source-Driven addressing scheme), or the destination node in the mesh to which the event is being sent (in the case of a *Destination-Driven* addressing scheme). Each addressing mode has pros and cons which are analyzed throughout the paper. For both cases, Fig. 4 shows the proposed 32-bit event format containing two fields:

Fig. 2. 2D Network Topology for Multi-Casting-Mesh-AER. Each node is identified by the address field (xNODE, yNODE).

Fig. 3. Example of AER node for a multi-node multi-link AER system.

Fig. 4. Events format with headers added for routing purposes.

|            | Flat AER [7]                    | Broadcast<br>Mesh AER<br>[25]–[27] | Pre-Structured<br>AER [28] | Hierarchical<br>Fractal AER<br>[29]     | Router Mesh<br>AER [30]             | Pre-Struc.<br>Mesh AER              |

|------------|---------------------------------|------------------------------------|----------------------------|-----------------------------------------|-------------------------------------|-------------------------------------|

| $Ev_{max}$ | $\frac{E_{pp}}{2N_{ch}F_{out}}$ | $\frac{E_{pp}}{F_{out}}$           | $\alpha N_{ch} E_{pp}$     | $\frac{N_{ch}E_{pp}}{2N_{L1}^2F_{out}}$ | $\frac{6N_{ch}E_{pp}}{n_hF_{Mout}}$ | $\frac{4N_{ch}E_{pp}}{n_hF_{Mout}}$ |

${\bf TABLE~II}$  Scaling of Communication Bandwidths in Multi-Chip AER Schemes

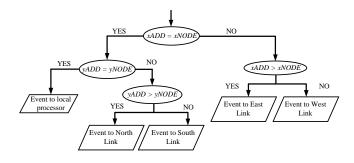

Fig. 5. Destination-driven routing algorithm for handling incoming events. (*xNODE*, *yNODE*) is the local node address and (*xADD*, *yADD*) is the event destination address.

- **Routing header:** the most significant bit is used to distinguish between data event (first bit is '0') or configuration command (first bit is '1'). The next 8 bits are used to code the destination or source node ID. Coordinates *xADD* and *yADD* are represented using 4 bits for each one.

- Upper layer data: the remaining 23 bits contain the event/command data. If it is a configuration command, it contains a command description, for example, a checksum, a command identifier and command parameters.

# A. Destination-Driven Routing Algorithm

In this algorithm, the destination node address is written in the routing header. When the event arrives at a network node, the router analyzes the addressing header and decides the output port to which the event is to be forwarded. If the destination address corresponds to the node address, the event is sent to the local processor. If this is not the case, the event is routed in accordance with the algorithm represented in Fig. 5: it compares the event destination address xADD and yADD with the present node address xNODE and yNODE to decide the output port to which the event is to be forwarded. Using the geographical information contained in the destination address, the event is routed to the neighbor node with the shortest path to the destination in terms of the number of hops. As the router only has to compare two 4-bit digital words, the hardware required can be very simple and the routing operation can be performed on the fly. The algorithm in Fig. 5 gives priority to xADD. This is called dimension-ordered routing and tends to concentrate the traffic in one dimension (horizontal, in this case). To avoid this, routers which give priority to yADD can be alternated with those priming xADD, balancing the situation. However, this may yield to deadlock situations [48] and should be analyzed carefully for each case. On the other hand, dimension-ordered routing (with bi-directional links) is known to be deadlock-free [49], [50].

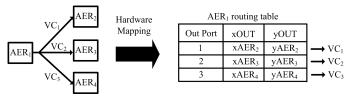

Fig. 6. Routing table for cloning output events in the destination driven algorithm. Left: Example logic diagram (schematics) showing the logic (virtual) connections between a source module  $AER_1$  and three destination nodes  $AER_{2-4}$ . Right: Routing table showing the output event header to be added (xOUT,yOUT) and the port through which it is to be sent.  $VC_i$  (i=1,2,3) represents a virtual connection between the source node  $AER_1$  and the destination nodes  $AER_{i-1}$ .  $(xAER_i,yAER_i)$  (i=2,3,4) is the network address of node  $AER_i$ .

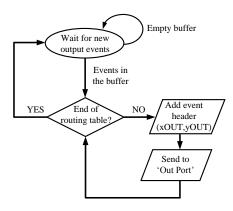

Fig. 7. Output event management in the destination-driven routing algorithm. Values for "xOUT", "yOUT" and "Out Port" are read from the routing table, as in the Fig. 6 example.

Besides managing the traffic coming from the neighboring chips, the router also inserts headers for the new events created in the local processor. The local router clones each newly created event as many times as the number of destination nodes (or virtual connections  $VC_i$ ) there are for that event. For each clone, or virtual connection  $VC_i$ , the router adds the destination node address and sends it to one of the local output ports. This is organized in a routing table which is read for every new event. Every entry in this table has an output destination address and an output port that transmits the event. The routing table organization is illustrated in Fig. 6, for the case of one node  $AER_1$  having three virtual connections  $VC_1 - VC_3$  to three other nodes  $AER_2$ - $AER_4$ . Fig. 7 shows the flow diagram for the output event management in the destination-driven routing algorithm.

Fig. 8. Source-driven routing algorithm.

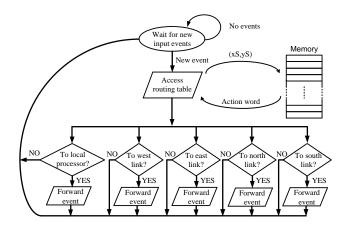

#### B. Source-Driven Routing Algorithm

In the source-driven option, the router receives information about the source address that generated the event. Hence, all the nodes must store information about all the possible source addresses that they can receive. When a new event is received, the router searches for the source address in a local user configurable connection memory. This memory codes all the operations that should be performed when a source address is received: forwarding the event to one or more output ports, routing it to the local processor, or both at the same time. The input routing algorithm for the source-driven solution is shown in Fig. 8.

The user can program connectivity maps by setting the elements of the connection memory. Each node locally stores its connection memory with its own routing actions for all the possible source addresses. Each position of this memory corresponds to each of the possible 8 bit source addresses and stores a 5-bit digital word. When one of those bits is at high level, it indicates that the event must be transmitted through the interface associated with that bit position.

This feature allows replication of events at intermediate network nodes. This is done by activating several bits in the connection memory position of the received source address. The event will be transmitted through the selected output interfaces. The programmed tasks can be performed in parallel because they do not require any shared resources. Output virtual connections from the same node can share the same initial segments of a route and clone events closer to the destination nodes, as opposed to the destination-driven case where the full route is cloned.

Local processor output event stream management is greatly simplified in the source-driven option. The source address is added to all the events that must be transmitted through the network. The only configuration parameter is the output port or ports that must transmit this information to get their final destination. By sending the same event through different output ports the user can balance the network traffic load and improve overall latency, because this reduces the event rate on critical physical links which may otherwise get saturated.

#### C. Comparison between both algorithms

Any node interconnection map can be implemented using either of the proposed routing algorithms. However, each solution offers certain advantages with respect to the other in terms of connectivity features. We will focus the different algorithms impact on parameters such as latency, network event traffic (the number of events transmitted through the network) and the hardware resources needed for the router implementation.

In terms of hardware complexity, the source-driven implementation needs a more sophisticated routing algorithm. This increased complexity leads to longer delays in the router event processing, increasing the latency associated with event transmission. The destination-driven router takes this decision on the fly, taking into account only the node address and the information contained in the incoming event. The latency penalty caused by the source-driven router is strongly dependent on the shared connection memory implementation and its arbitration mechanism. This memory block is large and results in an important area overhead.

The source driven algorithm provides the system designer with more freedom to balance event traffic and design routes through the networks. For any source-to-destination route, the designer can insert detours, de-branchings, and local event clonings at any intermediate node of the route to balance and optimize overall traffic. On the other hand, the destination driven algorithm creates pre-determined routes along the network, and the designer can only change the output ports of the source module of a route. Also, for the destination-driven case, the events that have to reach several modules necessarily have to be cloned at the source module. However, in the source-driven case, multiple module destination events can be cloned at intermediate route points. This alleviates overall traffic and makes the average effective module fanout ( $F_{Mout}$  in eq. (10)) smaller.

# D. Deadlock in NoC type systems

Deadlock in Network-on-chip (NoC) or Network-on-Board (NoB) mesh-type systems is an issue of primary concern among researchers and developers. A deadlock situation can happen if routing paths form closed loops [48]. The result is that all sender ports in the loop are requesting to send an event, while at the same time all receiver ports in the loop cannot acknowledge because they cannot take a new event before their corresponding sender port drops an event. This is a very well known and studied problem in mesh type communicating structures. In order to avoid such situations one solution is to route the paths in such a way that no closed loops are formed. In the example systems we provide in this paper we did not encounter any deadlock situation because the ConvNet examples provided are all feed-forward systems. However, in general one may encounter situations where feedback paths need to be implemented, thus increasing chances of forming closed loops. Consequently, when assigning routing paths and output ports within the routers, care must be taken to avoid closed loops, thus eliminating the possibilities for

Fig. 9. Destination-driven router block diagram.

deadlock situations. Since the routers we are using have bidirectional data paths between nearest neighbours and events can be routed to four output ports per module, there is a lot of flexibility for avoiding closed loops.

# IV. ROUTER DESIGN DETAILS

The routing algorithms described above should be implemented efficiently and with a minimum hardware cost. This Section describes hardware implementations focusing on design issues that must be faced to reduce routing processing times, while keeping lightweight implementations.

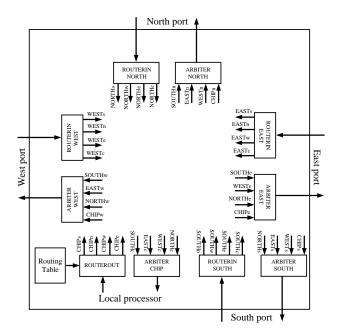

# A. Destination-Driven Router

Fig. 9 shows a block diagram of the destination-driven router circuit. The traffic through any of the input channels is processed by a *ROUTERIN* block that implements the destination-driven routing algorithm. A highly parallel hardware architecture has been chosen to reduce routing processing times. The goal is to separate the event streams that do not need to use the same channel. For example, a stream that is being transmitted from the west to the east port, never interferes with another stream that is being transmitted from the north to the south port. This is only possible if the shared routing resources are reduced to a minimum by replicating them in the architecture.

Routing is defined by user provided parameters. The first parameter is the node address which is used to identify the node in the network topology. The second parameter is the routing table that contains the information needed to communicate with the node's target destinations. Every entry in this routing table is a 10 bit word in which the 8 least significant bits are used to code the destination address and the

2 most significant bits are used to specify the corresponding output ports (as in Fig. 6).

The basic building blocks of the destination-driven router architecture are:

- ROUTERIN: this block receives the input stream coming from an input channel and implements the routing algorithm described in Fig. 5. It decides the output interface to which the event is to be forwarded, by comparing the input event address (xADD, yADD) with the userspecified local node address (xNODE, yNODE). The AER handshaking protocol is also used to transfer events between different blocks internally. Handshaking is used here for flow control purposes as the individual processor operation is stopped when a network communication link cannot transmit events. In these overflow situations, the router does not send the acknowledge back until there are hardware resources free to process the event. Each ROUTERIN block has four independent output interfaces connected to the output channel access arbiters or to the local processor arbiter.

- **ARBITER:** this block manages access to an output channel for the events coming from the *ROUTERIN* blocks or from the local processor. The *ARBITER* scans its four input AER interfaces to detect any new event. If an event is detected, it takes control of the output channel. If another event from any other interface arrives while the output channel is busy, the resource is not assigned until the current event releases the shared resource. If several input interfaces want to take control of the shared resource at the same time and the block is busy transmitting an event, the *ARBITER* gives lower priority to the last interface attended. Therefore, the arbitration mechanism prevents a fast input interface from monopolizing the shared resource. Note that all arbiters are synchronous circuits driven by the common FPGA clock.

- **ROUTEROUT:** this block implements the algorithm described in Fig. 7 to manage events coming from the local processor. This block reads the routing table row by row to add the proper header to the event, forwarding it through the specified output interface. For this purpose, the *ROUTEROUT* block has four output interfaces connected to the north, south, east and west arbiters. To improve router parallelism, the routing table is divided for every output port. This way, if an event has to be transmitted through different output ports, this can be done in parallel.

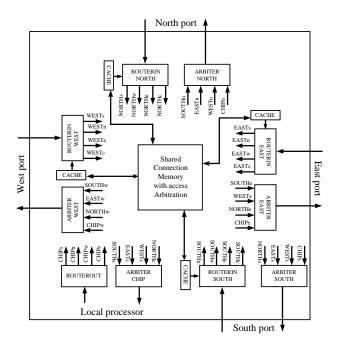

# B. Source-Driven Router

Fig. 10 shows the block diagram of the source-driven router. The building blocks used are very similar to those described for the destination-driven router. However, the *ROUTERIN* and *ROUTEROUT* blocks have very different internal structures due to the differences in the routing algorithm. In the source-driven option, all the blocks have to read a shared connection memory containing the routing information. The implementation of an efficient shared access scheme for this memory can dramatically reduce the delay time associated with the routing event process. The router contains the following blocks:

Fig. 10. Source-driven router block diagram.

- **ROUTERIN**: this block analyzes events coming from the input channel to extract the source address. This address is used to access a shared RAM connection memory of 256 positions containing the routing algorithm information. The word read from the connection memory codes the output port(s) that the event must be routed to. When this task is done, the behavior of this block is exactly the same as in the destination-driven router.

- Local Cache: every event that is routed in the sourcedriven solution needs a memory access and all the ROUTERIN blocks can read the memory at the same time. However, in a real network each input block will process a limited number of flows. This means that the addresses that every ROUTERIN block is going to read will be repeated very often and will only constitute a small part of the total address space. To speed up this process, the ROUTERIN block first consults a dedicated cache memory that stores the most common accessed address content. When the routing algorithm needs to access a shared memory position, the ROUTERIN block checks the cache memory and searches for this word. If it is found in the cache, the event is routed and there is no need to access the shared RAM. If the word is not found, the block reads the shared RAM and stores the word on its own cache.

- **ROUTEROUT** is greatly simplified because neither an event has to be replicated nor the same header has to be added to all the events. In this case, every time an event coming from the local processor is detected, the router node address is added and the event is sent to the corresponding output port(s).

- Shared Connection Memory: this block stores the configuration words that code the routing actions to be taken

for each possible source address. All the *ROUTERIN* blocks need to read this memory when they receive a source address that they have not previously stored in their local cache. An arbitration mechanism is needed to avoid conflicts when several *ROUTERIN* blocks need to access the shared memory. This mechanism ensures that only one *ROUTERIN* block has control over the address bus of the shared memory.

#### C. FPGA Implementations Comparison

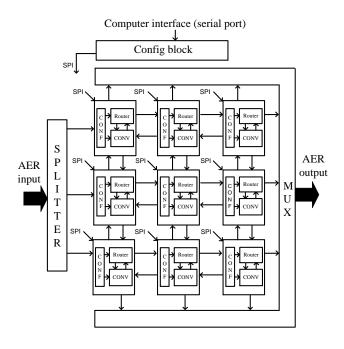

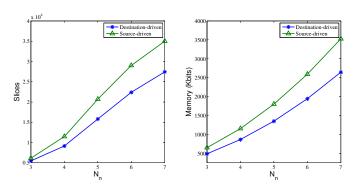

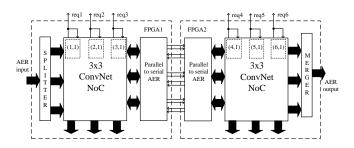

In order to compare the two router implementations in a multi-module system, we analyzed the impact of implementing different size networks on a Virtex-6 FPGA prototyping system. As unit-module we used a VHDL description of an event-driven programmable-kernel 2D AER-Convolutionprocessor for vision applications, capable of handling programmable kernels of size up to  $11 \times 11$  on pixel arrays of size  $64 \times 64$  [51]. Each VHDL ConvModule uses register RAM to store pixel states and kernel values. For each pixel state and each kernel weight we use an 8-bit register. The Virtex-6 could hold up to 64 of these Convolution modules, programmed with any arbitrary interconnection map. Fig. 11 illustrates the case of a  $3 \times 3$  Convolution network. Inputs to the network were provided through 3 input ports, connected to an AER splitter receiving a unique external input AER flow and replicating it over the three inputs. Every network node included one of the previously described routers, the convolution block, and a dedicated configuration processor with an SPI. This interface was fed by a global configuration controller that received all the configuration data (like router tables, and convolution processor parameters) from a host computer. The rest of peripheral modules could connect one of their AER outputs to a multiplexer block connected in turn to the external FPGA. This way, such peripheral modules were able to send their outputs to any of the multiplexer inputs to allow external monitoring of the AER flow. Fig. 12 shows the FPGA occupation ratios for different network sizes (where the number of nodes is  $N_n \times N_n$ ) in terms of occupied slices and memory resources. The destination-driven routing solution needed less hardware resources in terms of memory and slices than the source-driven implementation. Note that a  $7 \times 7$  grid of these Convolution modules implemented a neural network with  $7 \times 7 \times 64 \times 64 = 196k$  neurons (for k = 1024) and an equivalent number of  $196k \times 11 \times 11 = 24.3$  million synapses. Since each convolution module only had to store one kernel of  $11 \times 11$  8-bit words, the total physical RAM memory needed to store  $7 \times 7$  kernels was 5929 bytes. The RAM required to hold all 8-bit neural states was 196KB. Consequently, the limiting factor in this particular case was the number of slices available in the FPGA and not its memory.

#### V. NETWORK EXTENSION TO MULTIPLE FPGAS

The examples illustrated in Section IV were synthesized on a single Virtex-6 FPGA. To allow modular scalability to arbitrary size multi-module networks, provisions for multi-FPGAs (or multi-chips, in case of ASICs) needed to be made. AER links inside the FPGA were made using parallel

Fig. 11. Block diagram for the network on chip implementation.

Fig. 12. Slice and memory occupation in an  $N_n \times N_n$  node ConvNet implementation. The LX240 Virtex-6 FPGA used in the experiments have 37680 slices and 14976 Kb of block RAM.

AER buses. However, this was not realistic for a multi-FPGA realization because of the excessive number of resulting pins. Fortunately, high-end FPGAs include state-of-the-art serial links, like the Rocket I/O. In this Section we describe a way of extending each asynchronous bidirectional AER link to use available Rocket I/O serial interfaces, using neither dedicated handshaking lines (such as Ack and Rqst), nor an extra LVDS pair [38]. When the event rate transmitted in one direction exceeds the processing speed of the receiving module, a stop command is transmitted in the opposite direction. This way, flow control is implemented in both directions just by using the two required LVDS cable pairs for bidirectional serial transmission. For this purpose we used the 8b/10b encoding scheme, as this allows for 12 special characters, commonly called K-characters. We used these characters to implement idle commas (to keep the link synchronized during the absence of address events) and flow control commands. Note that this is standard industry practice.

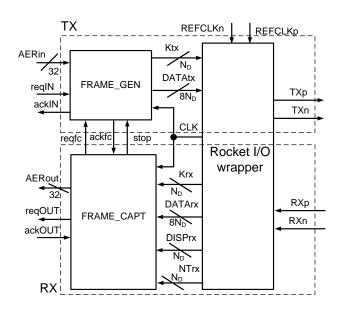

Fig. 13 shows the full duplex serial Rocket I/O AER link

Fig. 13. Full-duplex Rocket I/O based parallel-serial AER link with flow control capability.

with flow control capability. The Xilinx CORE Generator tool provides a wrapper to interface with the FPGA dedicated hardware. It defines the signals that the user must generate in order to send and receive data over this link. The data width interface,  $N_D$  in Fig. 13, is user-configurable in 8, 16 or 32 bits. TXp-TXn and RXp-RXn represent the serial output interface and REFCLKp and REFCLKn the reference clock used by the Rocket I/O circuitry to generate the transmission frequency.

The  $FRAME\_GEN$  block handshakes the input parallel AER stream and sends  $8N_D$  bits at every rising edge of the master clock CLK provided by the Rocket I/O circuitry. If there is no user data to transmit, the interface sends a comma character represented by a K-character of the 8b/10b code.  $FRAME\_CAPT$  receives the continuous data stream coming out from the channel, analyzes it, discards the commas and frames the parallel AER events, implementing the handshaking with the next processing block. Signals Ktx and Krx are activated when a K-character is transmitted or received, respectively. The receiver also uses the information provided by signals DISPrx and NTrx to detect possible transmission errors. DISPrx indicates a disparity error in the 8b/10b words received and NTrx is actived when the received word is not a valid code character.

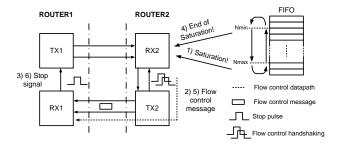

Fig. 14 illustrates the full-duplex flow control mechanism implemented through signals *reqfc*, *ackfc* and *stop* in Fig. 13. The figure illustrates the case of ROUTER1 sending events to ROUTER2. The ROUTER2 RX2 *FRAME\_CAPT* block (see Fig. 13) writes each incoming event in a FIFO memory, which is read by the router when there are new events to be processed. If the ROUTER1 TX1 transmission event rate is faster than the ROUTER2 RX2 handling capabilities, the number of elements stored in the FIFO will increase. If ROUTER1 TX1 keeps sending new events, the FIFO would overflow and information would be lost. The *FRAME\_CAPT*

Fig. 14. Flow control mechanism in a full-duplex link.

block detects when the number of elements is greater than a user-defined threshold  $N_{max}$  (see '1)' in Fig. 14) and sends a flow control message using a K-character via the ROUTER2 transmitting channel TX2 (see '2)' in Fig. 14). This message request is made by activating reafc and it will be processed with the highest priority by the ROUTER2 TX2  $FRAME\_GEN$  block. When the flow control message is sent, the ROUTER2 TX2  $FRAME\_GEN$  block acknowledges the transmission using ackfc.

When the ROUTER1 RX1 FRAME\_CAPT block detects the flow control K-character, it automatically stops event transmission, asserting signal stop (see '3)' in Fig. 14). In an overflow situation, the AER acknowledge signal ackIN is not activated even when the request signal is asserted and the AER data flow is stopped. The ROUTER2 RX2 FRAME\_CAPT block monitors the receiving FIFO until the number of elements falls below a second user-defined threshold  $N_{min}$  (see '4)' in Fig. 14). From this point on, the overflow situation is considered finished and the flow control message is sent to ROUTER1 RX1 (see '5)' in Fig. 14). When it is received, the stop signal is deasserted (see '6)' in Fig. 14) and the transmission flow is resumed.

The ROUTER1 sender keeps transmitting events while the flow control mechanism is in operation. To ensure that no events are lost during traffic peaks, the time needed to stop the transmitter when an overflow situation is detected must fulfill the inequality

$$T_{DET1} + T_{PROP} + T_{STOP} \le (N_F - N_{max}) T_{TX,EV}$$

(11)

where  $T_{DET1}$  is the time needed to detect the overflow situation and generate the flow control message,  $T_{PROP}$  is the channel propagation time and  $T_{STOP}$  is the time required to stop the transmitter. The maximum number of FIFO elements is represented by  $N_F$  and  $T_{TX,EV}$  is the transmission event period that is causing the overflow.

It would be desirable for the transmission to begin as soon as possible after a flow control pause. For this purpose, the flow control mechanism has to ensure that there will be events stored in the FIFO waiting to be processed by the router after the recovery. To maximize the receiver event rate, we can impose the following restriction on the  $N_{min}$  value

$$T_{DET2} + T_{PROP} + T_{START} \le N_{min} T_{RX,EV} \tag{12}$$

where  $T_{DET2}$  is the time needed to detect the end of an overflow situation,  $T_{START}$  is the time required to start the

transmitter again and  $T_{RX,EV}$  corresponds to the receiver event processing time (or the inverse of the event rate).

#### VI. SYSTEM LEVEL DESIGN CONSIDERATIONS

Several analysis and optimization methodologies for 2D mesh connected networks have been proposed in literature [52], [53]. The 2D communication layer is analyzed from a traffic management perspective using queuing theory to find network parameters such as latency, queue delays or queue occupation rates. All these parameters are strongly influenced by the application, because they depend on the network topology (physical and logical) and the traffic rates generated by the processors. On the other hand, optimization procedures for massively parallel architectures [54] have been successfully applied to neuromorphic systems which integrate millions of neurons [9]. Here we will rely on analysis techniques for 2D mesh networks, and use the results to suggest ways to optimize the implementations. The study will be centered on our convolution unit network implementations, but it can be easily extended to other neuron array schemes. We will analyze two points of view: hardware resource requirements and event traffic.

#### A. Hardware Resource Requirements

AER convolution modules and network circuits employ a certain amount of resources (logic area and memory) which must fit within the selected implementation platform. This resource consumption will be related to the number of AER modules and the neuron array sizes. In general, an  $N_{units}$  AER system requires an area of

$$A_{total} = N_{units} \left( A_{conv} + A_{router} \right) + A_{prog} \tag{13}$$

where  $A_{conv}$ ,  $A_{router}$ , and  $A_{prog}$  are the areas used by one convolution processor, one router, and the overall SPI programming circuitry. Let every convolution module have a maximum kernel size of  $N_{ker} \times N_{ker}$  and every weight be coded with W bytes. If convolution modules integrate an array of  $N_{arr} \times N_{arr}$  neurons the state of which is represented by S bytes, the area taken up by a ConvModule is given by

$$A_{conv} = N_{arr}^2 A_{reg}(S) + N_{ker}^2 A_{reg}(W) + A_{logic}$$

(14)

where  $A_{reg}(x)$  is the area of a register of x bytes, and  $A_{logic}$  is the area taken up by the additional logic of the convolution module implementation, which depends on  $N_{arr}$ , W and S.

For the routers, as we discussed previously, the simplicity of the destination driven algorithm needs less logic resources  $A_{logic,dest}$  than the source driven  $A_{logic,sour}$ . Furthermore, the source driven approach needs extra memory to store the routing actions for all possible source addresses in the network (coded in 5 bits). This extra memory is implemented through local registers and uses an area  $A_{reg}(x)$ , where x is number of bytes. Since routing actions only require 5 bits, x=(5/8)y where y is the number of memory positions. If  $N_{add}$  bits are used to code the network addresses, the router areas can be expressed as

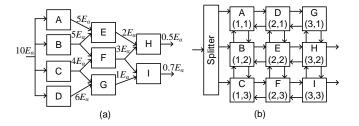

Fig. 15. Example AER system to study system level characterization methodology. (a) Logical description of the network and event rates for each logical (virtual) channel. Parameter  $E_{\alpha}$  has units of event rate (events per second) and the traffic loads at the different nodes are expressed in terms of  $E_{\alpha}$ . By sweeping  $E_{\alpha}$  we can analyze the impact of traffic scaling and saturation in the network. (b) Physical implementation on the structured-grid-AER infrastructure and corresponding mapping of the logical modules (A to I) on the physical 2D grid.

$$A_{router,dest} = A_{rlogic,dest} \tag{15}$$

$$A_{router,sour} = A_{rlogic,sour} + A_{reg}(\frac{5}{8} \times 2^{N_{add}})$$

(16)

The total number of neurons which can be integrated in the system is  $N_{units}N_{arr}^2$  and the maximum number of kernel weights is  $N_{units}N_{ker}^2$ . Taking into consideration the previous resource analysis, the total RAM memory bytes M needed for both routing algorithms can be written as

$$M_{dest} = N_{units} \left( N_{ker}^2 W + N_{arr}^2 S \right) \tag{17}$$

$$M_{sour} = N_{units} \left( N_{ker}^2 W + N_{arr}^2 S + \frac{5}{8} \times 2^{N_{add}} \right) \quad (18)$$

# B. Event Traffic Estimation

One of the most important parameters of any AER communication scheme is the event transmission latency between processing blocks. The AER mesh architecture used in this paper can be studied using an analytical model for NoC performance analysis [52], where routers are modeled as a collection of FIFO buffers with five input/output channels (north, south, east, west and local interfaces). This model computes the network queue occupation at every interface of each router assuming that event rates for all network channels are known parameters. These rates are strongly dependent on the specific application and can be easily estimated through a behavioral level simulation.

For example, Fig. 15(a) shows the logic network topology of a specific pre-structured AER system. This network can be simulated behaviorally to obtain the average event rates at each connection (virtual channel). The event rates at each connection are expressed in term of a reference event rate  $E_{\alpha}$ , which can be swept to study changing traffic conditions. To map the logic network onto the physical 2D mesh of nodes, the first step is the "placement" of modules, which is illustrated in Fig. 15(b). The second step is to assign a route (or list of

nodes) for events going from a source node s to a destination node d. Let us call this list of route nodes  $\Pi_{sd}$ . Each route corresponds to a virtual connection in the logic network. Once the module placement and route lists  $\Pi_{sd}$  are established we know the event rates at the input and output router channels.

Let  $l_{ijr}$  be the event rate at input channel i routed to output channel j in router r. For each router, we can define a  $5 \times 5$  forwarding probability matrix where element  $f_{ijr}$  corresponds to the probability that an event which arrives at interface i will leave the router through interface j. These probabilities can be computed for every router in the network as

$$f_{ijr} = \frac{l_{ijr}}{\lambda_{rj}} \quad i, j \in [1, 5], \quad r \in [1, N_{unit}]$$

$$\lambda_{rj} = \sum_{k=1}^{5} l_{ikr}$$

$$(19)$$

In the network the events from different routes have to share common resources to reach their final destination. If two events want to use the same resource, arbiters grant access and make some events wait in their queues until the resource becomes available. The forwarding matrix can be used to compute the contention probabilities  $c_{ijr}$  for each router, i.e., the probability that channels i and j compete for the same output, as:

$$c_{ijr} = \sum_{k=1}^{5} f_{ikr} f_{jkr} \quad \forall i \neq j \quad c_{ij} = 1 \quad \forall i = j$$

(20)

The router forwarding matrix  $F_r = [f_{rij}]_{5\times 5}$  and the contention matrix  $C_r = [c_{ijr}]_{5\times 5}$  describe the routers' traffic management. It can be demonstrated [52] that the average number of events per queue  $N_r = [N_{rj}]_{5\times 1}$  at each router can be computed as:

$$N_r = \left(I - t_r \Lambda_r C_r\right)^{-1} \Lambda_r \bar{R_r} \tag{21}$$

where scalar  $t_r$  is the mean event processing time in the router and  $\Lambda_r = [\lambda_{rj}]_{j=r}$  is a diagonal matrix made up of the total event rates through the 5 input interfaces.  $[\bar{R}_r]_{5\times 1}$  is the residual time matrix, which represents the amount of time that a new event has to wait in the queue until the event which occupied the shared resource at the moment the new event arrived finishes its processing. Solving eq. (21) and applying Little's theorem [55], we can compute the mean waiting time in channel j of router r as  $W_{rj} = N_{rj}/\lambda_{rj}$ . This way, the total latency of one node-to-node hop is  $N_{rj} + t_r + t_{tx}$ , where  $t_{tx}$  is the transmission time through the inter-node physical channel. The total latency of an event traveling from source node s to destination node d is therefore

$$L_{sd} = \sum_{(r,j)\in\Pi_{sd}} (W_{rj} + t_r + t_{tx})$$

(22)

This analysis methodology will be applied to the example system of Fig. 15 in Section VIII where the network traffic will be estimated for a source driven and a destination driven solution. Moreover, we will discuss how to use this analysis procedure to improve network performance by varying some of the implementation parameters. Note that, given a logical network together with virtual connection event rates, it is only necessary to establish a node "placement" and the route lists  $\{\Pi_{sd}\}$ . The other computations (from eqs. (19) to (22)) are quite straightforward, given parameters  $t_r$ ,  $\Lambda_r$ ,  $\bar{R}_r$  and  $t_{tx}$ . The result is the route delays  $\{L_{sd}\}$  from which the maximum can be identified as its main timing bottleneck

$$L_{max} = max\{L_{sd}\} \tag{23}$$

The designer must then adapt the node "placement" and route lists  $\{\Pi_{sd}\}$  to minimize  $L_{max}$ .

#### VII. EXPERIMENTAL RESULTS

In this Section we provide experimental results by implementing the above mentioned concepts on Virtex-6 hardware using Xilinx ML-605 development boards. First we show the characterization results of the Full-Duplex Rocket-I/O-Based AER parallel-serial interface described in Section V. An example of a multi-module AER processing system which consists of an array of Gabor filters implemented on a single FPGA is then described. After that, a second system, implementing a multi-layer feed-forward Convolutional Neural Network on a single FPGA, is described. Next, we check the maximum capacity of a single FPGA, and finally we provide results for a multi-layer feed-forward ConvNet for character recognition.

# A. Full-Duplex Parallel-Serial AER Interface

The ML-605 development board provides twenty independent full-duplex Rocket I/O serial ports, eight of which are available through an 8x PCIe connector. We used a dedicated board to adapt this connector to 16 independent SMA (Sub-Miniature version A coaxial RF connector) pairs, thus making it possible not only independently to test and characterize several transmitters and receivers, but also to interconnect them. Some extra test circuits were added inside the FPGA, such as an event generator and an event consumer/analyzer, both with independent programmable event rates. This allowed us to force overflow situations and test the flow control dynamics, while detecting errors between the sent and received events.

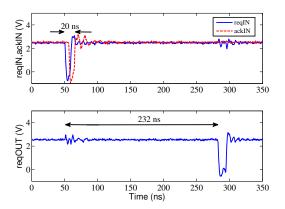

The timing characteristics of the serial link are given by its latency and maximum event rate. To characterize latency, two independent Full-Duplex AER serial links were interconnected (each with two high speed wires), and the delay between the 'reqIN' (see Fig. 13) of the first one and the 'reqOUT' of the second one was measured. This latency included the delay introduced by the 8b/10b encoders and decoders, phase alignment buffers, comma detection circuits, etc. To measure this latency, a very low event rate was programmed, so that consecutive events were sufficiently spaced in time. The measured latency was 232ns for a 2.5Gps bit rate, as shown in Fig. 16. The maximum event rate supported by the Rocket I/O could be characterized by analyzing the input AER handshaking (reqIN, ackIN) cycle duration which is

Fig. 16. Interface input (reqIN, ackIN) and output request (reqOUT) when the link operates with very sparse events to measure the input to output event latency.

highlighted in Fig. 16 as 20ns. This would result in 50Meps (mega events per second) maximum possible event rate for 32-bit events.

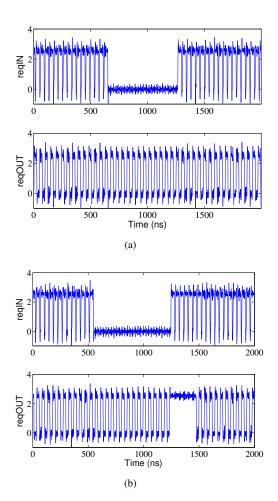

Fig. 17 illustrates the flow control operation. The event generator in the transmitter was set intentionally to 26Meps event rate, while the event consumer in the receiver was set to have an event consumption rate of 20Meps. This led to overflow in the receiving FIFO. It can be seen how the transmitter was stopped when the flow control message was received and started over again when the overflow situation was overcome. Two different overflow behaviors were possible depending on the chosen  $N_{max}$  or  $N_{min}$  values. If these were optimally programmed, there was no stop in the output event flow, as shown in Fig. 17(a). On the other hand, pauses appeared if the receiver processed all the events stored in the FIFO before the flow control message arrived at the transmitter. This situation is illustrated in Fig. 17(b).

#### B. Routers with Parallel-Serial Interfaces

The routers described in Section III were complemented with four Full-Duplex Rocket-I/O-based AER parallel-serial interfaces (see Fig. 13), to test the performance for multi-FPGA event routing. Table III shows the Virtex-6 occupation statistics associated with both implementations. For the destination-driven router, clock frequency could be set up to 250MHz resulting in 2.5Gbps serial bit rate. However, for the source-driven router, clock frequency could only be set up to 200MHz because of the higher complexity, resulting in a 2Gbps bit rate. The latency introduced by the routers can be measured by looking at the delay between the regOUT signal of the input full-duplex Rocket-I/O serial-to-parallel interface and the reqIN signal of the output full-duplex Rocket-I/O parallel-to-serial interface. This latency was 12.5ns for the destination-driven router and 20ns for the source-driven router, in non-overflow situations. In the case of the source-driven router the received address was also stored in local cache. Otherwise, the latency became 30ns.

The destination-driven router could handle a maximum 32-bit event rate of  $E_{pp}=27Meps$ , which corresponds to 37ns for completion of the handshaking cycle. On the other hand,

TABLE III  $Router\ implementation\ statistics\ for\ the\ DD$  (destination-driven) and the SD (source-driven) routers.

| Resources                | DD router | SD router | Total FPGA |

|--------------------------|-----------|-----------|------------|

| Occupied slices          | 1121      | 1400      | 37680      |

| Occupied RAMB18E1 blocks | 0         | 1         | 832        |

| Rocket I/O transceivers  | 4         | 4         | 20         |

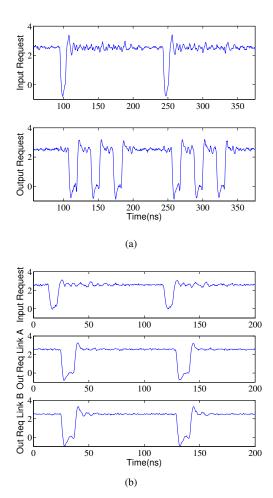

the source-driven router could handle up to  $E_{pp}=17.5 Meps$  maximum event rate, or 57ns handshaking cycle. Although event transmission in destination-driven routing is faster, it is also true that events have to be transmitted multiple times when destinations are multiple. In this case, if the multiple events are routed through the same port, there will be a considerable delay penalty as shown in Fig. 18(a). However, most of the time it is also possible to replicate events through (up to four) different ports, as shown in Fig. 18(b), to avoid this penalty.

# C. Single-FPGA Implementation of Gabor Filter Array

As a first illustration of multi-module operation we implemented a  $3\times 3$  array of orientation extraction 2D-Gabor

Fig. 17. Interface input (reqIN) and output request (reqOUT) in overflow with (a) optimum  $N_{max}$ - $N_{min}$  election and (b) non-optimum  $N_{max}$ - $N_{min}$  election leading to pauses in the output flow

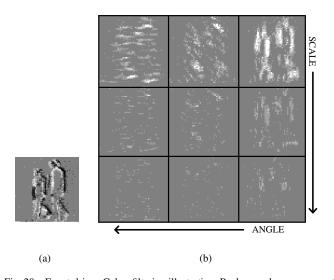

filters of different scales and angles on a single Virtex-6. The kernels are shown in Fig. 19. The implemented structure follows the diagram in Fig. 11 and received sensory input from an AER DVS retina [56], [57]. The convolution filters used a modified version of a previously reported VHDL ConvModule [51], with its random Poisson distributed readout mechanism replaced by a plain compare-and-fire mechanism. All filter outputs were routed to one of the multiplexer inputs and captured off-chip with an AER data logger [58]. Fig. 20 shows the sensor and the nine filter output events collected during the same period of 160ms, while the retina was observing two walking persons.

Event-driven convolution processors present the "pseudo-simultaneity" property [22], [24]: during a given time interval, the input flow of events (representing the input scene) is simultaneous to the output flow of events (representing the filtered input scene). This is because events are processed as they arrive with delays shorter than the average interevent time. For the convolution modules we were using, event processing time for  $11 \times 11$  kernels was about  $3\mu s$ . The input event flow provided by a  $128 \times 128$  pixel DVS retina when observing people walking was in the range of 10-50keps (kilo

Fig. 18. (a) Output event replica when the same event must be transmitted to different destinations using the same output port. (b) Parallel transmission of events coming from the local processor that must be transmitted through different output ports A and B.

Fig. 19. Kernels in the bank of Gabor filters for the three chosen orientations and scales.

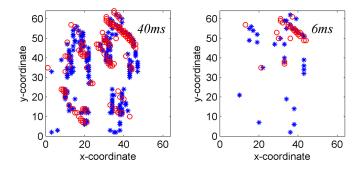

events per second). Consequently, a Gabor filter output event representing an angle at a given scale was available as soon as sufficient input events representing this feature were received, plus the extra  $3\mu s$  for processing the last one. This is illustrated in Fig. 21, where a  $-45^{\circ}$  filter provides output events as soon as enough input events are received which are aligned in short  $-45^{\circ}$  edges. Stars represent input events and circles output events. The left most subfigure shows the input and output events collected during 40ms. As can be seen, there are  $-45^{\circ}$  oriented input segments present during these 40ms that are readily detected by output events during these same

Fig. 20. Event-driven Gabor filtering illustration. Background gray represents zero activity pixels, brighter pixels are active pixels sending positively signed events, darker pixels are active pixels sending negatively signed events. (a) Input scene captured by the DVS retina, with pixel activity of both signs. (b) Results of the 3x3 bank of Gabor filters and sign rectification, so that only positive events result.

Fig. 21. Illustration of pseudo-simultaneity of event-driven convolutional filtering with a Gabor filter for detection of  $-45^{\circ}$  oriented edges. The two subfigures represent the x/y projection of events captured during 40ms and 6ms. Convolution module input events are represented by stars and output events by circles. One can see that input events representing  $-45^{\circ}$  edges are detected during the same 40ms or even 6ms they appear.

Fig. 22. Diagram of 3x6 Gabor Filter Array Implementation in two FPGAs

40ms. Furthermore, for the right most subfigure we can also see this but for a time interval of only 6ms. Consequently, in event-driven feature extraction, a given feature is detected as soon as enough representative input events are received. Thus, recognition delay would be determined mainly by the event statistics provided by the sensor, not the processing delay of the event-driven ConvNet.

# D. Multi-FPGA Implementation of Gabor Filter Array

In order to illustrate the use and operation of the Full-Duplex Rocket-I/O-Based Parallel-Serial Interfaces described in Section V.A, we implemented a  $3 \times 6$  array of Gabor filters in 2 FPGAs. The corresponding diagram is shown in Fig. 22. The retina events were fed through port 'AER input' and an in-FPGA splitter replicated them on three rows. Node routers were programmed so that the retina events would be copied horizontally from node to node inside each FPGA and also from FPGA1 to FPGA2. To transfer the output events produced by each node (or Gabor filter), the routers were also programmed to copy all output events horizontally from node to node and from FPGA1 to FPGA2. At the right end of all three rows there was an in-FPGA merger block that merged the three flows into a single output port, where an AER data logger board [58] was used to capture and timestamp events. The flow between the two FPGAs was fed through three Full-Duplex Rocket-I/O-Based Parallel-Serial Interfaces.

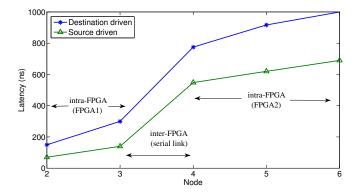

To analyze the impact of event hopping from node to node (either intra-FPGA) we programmed the same Gabor filter into all nodes in the first row. The Gabor filter

Fig. 23. Latency between nodes for the experiment described in Fig. 22 for the destination and source driven routing algorithms.

output flow was routed to the west and north channels at each node to observe the output and measure the latencies between the first output node (1,1) and the other nodes (j,1) with j=2...6. These latencies could be measured by observing the delays between request signals  $req_j$  (j=2...6) and  $req_1$ .

The measured delays of  $req_j$  with respect to  $req_1$  are shown in Fig. 23, for destination and source driven algorithms. Every in-FPGA network hop added a latency of 150ns for the destination driven algorithm and 70ns for the source driven algorithm. For the inter-FPGA hops an additional 350ns was added to the routing delay, for both routing algorithms. Note that here the source-driven case presents lower latency than the destination-driven case. This is because of the massive retina event cloning for the destination-driven case, because each retina event has to be cloned for each destination Gabor filter. Therefore, event traffic is much higher in the destination-driven case for this particular arrangement.

# E. Testing Single-FPGA Maximum Capacity

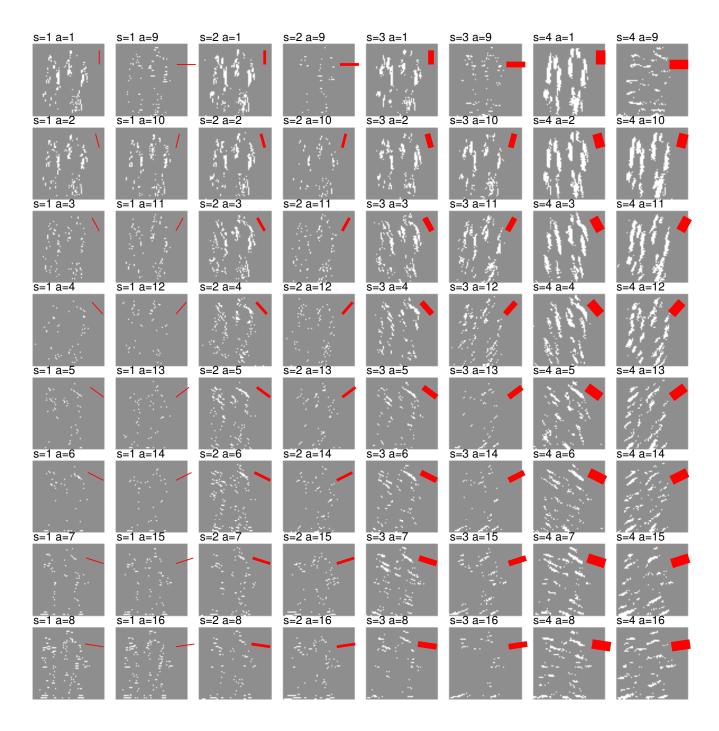

So far, in each FPGA we had programmed nine  $64 \times 64$ pixel ConvModules to verify the operation of routers and interfaces. In order to test the maximum capacity of one Virtex-6 FPGA, we checked the maximum of Gabor filters it could hold, together with their routers, peripheral interfaces, SPI configuration circuitry, and input splitter. We used the destination-driven routers, as they are more efficient in terms of FPGA resources. We were able to have the FPGA hold a total of 64 Gabor filters<sup>4</sup>, each with  $64 \times 64$  pixels and kernels of size  $11 \times 11$ . The ConvModule array, together with the 1x8 input splitter circuit, the configuration infrastructure through the serial port and the output channels read-out circuitry occupied 32720 slices, representing 86% of the Virtex6 FPGA capacity. Internal memory occupation was 15% for the 36K RAM blocks and 18% for the 18K RAM blocks. We programmed a Gabor filter array by sweeping four scales and 16 angles. Fig. 24 shows the collected output events for the 64 filters in the same 160ms time window, while the input DVS retina was observing the same two persons walking, shown in Fig. 20(a). Note that, in this case, one single FPGA was emulating a system with  $N_{neurons} = 64 \times 64 \times 64 = 2.62 \times 10^5$  neurons and  $N_{synapses} = N_{neurons} \times 11 \times 11 = 3.17 \times 10^7$  synapses.

Since the network had a total of  $N_l=216$  inter-module links, each with  $E_{pp}=27Meps$  (as it is destination-driven), the mesh could communicate a total of up to  $N_lE_{pp}=5.8Geps$  of 32-bits each. However, this number needs to be divided by the average number of hops per event  $n_h$  and the average number of module fan-out  $F_{Mout}$ , to determine the effective (non-cloned) events traveling through the network. Both numbers  $n_h$  and  $F_{Mout}$  are problem specific, and can be optimized for each case. In this particular case average  $n_h$  was around 4, while the average  $F_{Mout}$  was about 3 and average  $F_{Mout}$  about 2.

#### F. Multi-Module Multi-Layer ConvNet Recognition Example

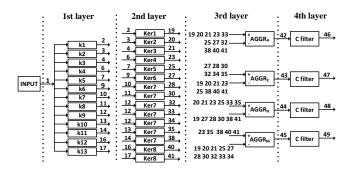

The previously described arrays of Gabor filters represent a one-layer neural system, where all modules (filters) received the same replica from the input sensor. The example illustrated in this Section is a multi-layer Convolutional Neural Network that performs a previously reported character recognition task which has been verified using an AER event-driven simulator with user-defined behaviorally-described event-processing modules [59], [60]. It is loosely based on Fukushima's neocognitron [61] or Serre's hierarchical network [62]. Here we used the same  $64 \times 64$  convolution module as above (a modified version of the one in [51]) to assemble the 36-node Convolution Neural Network shown in Fig. 25. For this, a 2Darray of  $6 \times 6$  AER-nodes was synthesized in a single FPGA. The heuristically chosen kernels [59], [60] are illustrated in Fig. 26. Kernels k1 to k13 performed feature extraction for the 1st layer. Kernels Ker1 to Ker6 were used for the 15 filters in the second layer. Convolution outputs were always half-wave rectified (events were assigned a positive sign). The layer 2 output virtual channels (labeled 19 to 41 in Fig. 25) were fed to four modules labeled  $AGGR_i$  in Fig. 25. These were not ConvModules, but plain arrays of integrate-and-fire neurons. Each  $AGGR_i$  module included an AER-merger at its input to merge the traffic from several virtual channels, while forcing their sign bit. For example, module  $AGGR_i$ merged events from virtual channels  $\{19, 20, 21, 23, 33\}$  and  $\{25, 27, 32, 38, 40, 41\}$ , while forcing a positive sign bit for the first set and a negative sign bit for the second set. Finally, the 4th layer performed 4 convolutions in parallel, all with the same kernel KerC in Fig. 26.

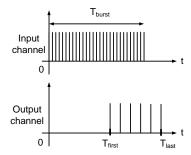

The system was stimulated with bursts of events representing three different versions of letters A, C, H, and M. Bursts had between 200 to 400 events and lasted from about 0.5 to 1ms. Fig. 27 shows the main timing properties in this set-up. An input stimulus burst lasts for a time  $T_{burst}$ . At one of the four output recognition channels (nodes '46' to '49' in Fig. 25) the first output event appears at time  $T_{first}$  and the output burst lasts until time  $T_{last}$ . Table IV summarizes the measured

<sup>&</sup>lt;sup>4</sup>The corresponding VHDL description is available upon request.

$<sup>^5 \</sup>mathrm{Assuming}$  a 2r retina event rate and an r average filter output event rate, the total cloned event rate would be  $E_{max} = \overline{n_h}(2r \times 64 + r \times 64),$  while the effective uncloned rate would be  $E_{eff} = 2r + 64r.$  This results in  $E_{max}/E_{eff} = \overline{F_{Mout}n_h} = 2.91\overline{n_h}.$

Fig. 24. Output captured from the 64 Gabor filter array. Four scales (s = 1, ...4) and 16 angles (a = 1, ...16) were swept. Gray scale represents the number of events integrated in every address position in a 160ms temporal window. Background gray is zero output, while bright pixels represent active pixels. The rotated red bar in each subfigure indicates angle and scale (thickness) of the corresponding Gabor filter.

timing results  $(T_{burst}, T_{first}, T_{last})$  and also the number of events per output burst for each letter presentation. On average, correct recognition output spikes (which start at time  $T_{first}$ ) appeared at about half-way through the input stimulus burst  $0.5 \times T_{burst}$  and lasted until shortly after the input stimulus burst had finished.

#### VIII. DISCUSSION

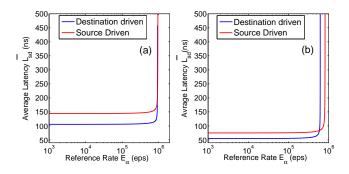

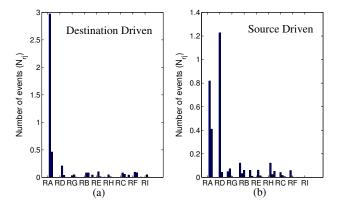

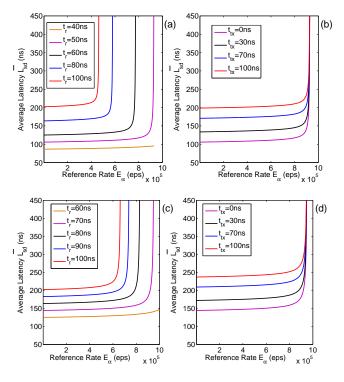

In this Section we will briefly illustrate the system level analysis methodology presented in Section VI with the simple example shown in Fig. 15. This example is not optimized to achieve best performance, but is merely intended to show how we can analyze the network using queuing theory and how this can help us in making design decisions. Fig. 15(a) shows the logical connections (virtual channels) between blocks (nodes) and the event rate at each channel. Average channel