# A 2.6 $\mu$ W Monolithic CMOS Photoplethysmographic (PPG) Sensor Operating With 2 $\mu$ W LED Power for Continuous Health Monitoring

Antonino Caizzone, *Student Member, IEEE*, Assim Boukhayma, *Member, IEEE*, and Christian Enz, *Fellow, IEEE*

Abstract—Photoplethysmography (PPG) enables wearable vitals monitoring. Nevertheless, it is still limited by the few mA of the LEDs driving current. We present a PPG sensor integrating an array of dedicated pinned-photodiodes (PPD) with a full readout chain integrated in a 0.18  $\mu m$  CMOS Image Sensor (CIS) process. The sensor features a total input referred noise of 0.68 e-rms per PPD, independently of the input light, and achieves a 4.6  $\mu W$  total power consumption, including the 2  $\mu W$  LED power, at 1.38 bpm heart rate average error.

*Index Terms*—Array, CIS, CMOS, LED, low-power, low-noise, Photodetector, PPD, PPG, wearable.

## I. INTRODUCTION

OWADAYS continuous and reliable health monitoring is becoming more and more important. Modern lifestyle often comes at the cost of increased stress levels and uncontrolled diets. According to [1] 13% of the world adult population are today obese, meaning 650 million individuals having higher probability of cardio-vascular diseases (CVDs) and diabetes. In addition, the global population is getting older and older. As reported in [2] we have already reached the point of having more seniors than juniors. Without a significant change of the modern lifestyle the healthcare costs are expected to explode the countries' budgets. Indeed, according to [3] the global healthcare spending is supposed to increase at an annual rate of 4.1%between 2017 and 2021. In this perspective, photoplethysmography (PPG) is a key technology allowing non-invasive monitoring of crucial vital indicators such as the heart rate (HR), the oxygen saturation  $(SpO_2)$  and the blood pressure.

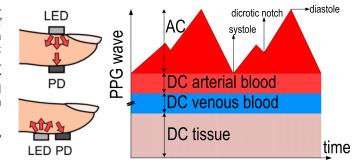

A PPG signal is obtained by shining light from an LED at a given wavelength, visible or infrared, into an human tissue, e.g. finger, forehead, ear lobs. As shown Fig. 1, a photodetector (PD) detects the light transmitted through or reflected from the tissue and transforms it into a photogenerated current. The detected signal, i.e. PPG, consists of two different components: a large

Manuscript received July 9, 2019; revised September 3, 2019; accepted September 25, 2019. Date of publication October 2, 2019; date of current version December 31, 2019. This paper was recommended by Associate Editor A. J. Burdett. (Corresponding author: Antonino Caizzone.)

The authors are with the Integrated Circuits Laboratory, Ecole Polytechnique Federale de Lausanne (EPFL), CH-2000 Neuchatel, Switzerland (e-mail: antonino.caizzone@epfl.ch; assim.boukhayma@epfl.ch; chrisitan.enz @epfl.ch).

Color versions of one or more of the figures in this article are available online at http://ieeexplore.ieee.org.

Digital Object Identifier 10.1109/TBCAS.2019.2944393

Fig. 1. Sensor set-up for a PPG measurement and the DC and AC components of a PPG signal.

DC (quasi-static) component corresponding to the light diffusion through tissues and non-pulsatile blood layers, and a small AC (pulsatile) part due to the diffusion through the arterial blood. The AC component is only a very small fraction (typically 0.2% to 2%) of the DC one, depending on the body location and the skin tone [4]. Such small AC/DC ratio is called Perfusion-Index (PI).

Today, the total PPG sensor power consumption is dominated by the few tens of mA current used for driving the LEDs. Different solutions have been proposed to solve this bottle-neck, either by reducing the LED duty cycle at uniform sampling [5], [6] or by non-uniform sub-sampling [7], [8]. A heart-beat-locked loop system that significantly reduces the LED power has recently been demonstrated in [9]. However, this power reduction increases the complexity of the proposed solution since it requires a non-trivial heart beat prediction scheme. Moreover, the power saving intrinsically hinders the full PPG wave representation. In addition, most systems presented in the literature or proposed on the market implement off-chip PDs. An off-chip PD comes with a non-negligible parasitic capacitance, ultimately limiting the noise performance and the speed/power of the analog front-end (AFE) [10]. Indeed, as shown in [10], at low light condition, the SNR of a PD-based AFE significantly degrades when increasing the size of the PD and therefore its capacitance. In addition, using an off-chip PD limits the PPG sensor integration on silicon resulting into a larger area and more cost.

To the best author's knowledge, the work in [11] is the first academic solution showing the full integration of the PD area, into a single-PPG chip. Despite the PD integration on silicon, this

work comes with a power consumption in the order of several mWs, which is very large for any possible application into a wearable platform. The more recent work in [12] also shows an interesting PPG sensor integrating on silicon an array of PDs. Despite the very promising power results, it is not clear how the LED power consumption (most power hungry element of a PPG sensor) is actually evaluated, given the sampling frequency in the hundred kHz.

Recently we have presented a fully integrated sensor addressing the power issue by combining a high sensitivity PD together with an ultra-low noise and low power readout chain [13]. Compared to conventional solution, this work achieves the same signal-to-noise ratio (SNR) at a significantly lower LED power. This PPG sensor integrates an array of pinned-photodiodes (PPD), commonly used in CMOS imagers for achieving subelectron noise [14]. The PPDs array is implemented on the same chip together with the AFE including the analog-to-digital conversion (ADC). The full CMOS integration allows to dramatically reduce the parasitic capacitance at the sensing node leading to a larger conversion gain and a lower noise. This approach also provides higher miniaturization and lower cost compared to traditional solutions with off-chip PDs. The use of an array additionally enables spatial averaging leading to further noise reduction. Consequently, the LED power can be reduced dramatically. A prototype has been implemented in a 0.18  $\mu$ m CMOS Image Sensor (CIS) process, achieving 4.6  $\mu$ W total power consumption, including 1.97  $\mu$ W LED power, at 1.38 bpm HR average error.

This paper extends the work presented in [13]. It is organized as follows: Section II overviews the operations behind a PPD device and its competitive advantage versus a conventional PD for the PPG application. Section III presents the full sensor architecture and operation principle. Sections IV and V report the full PPG sensor characterization. Sections VI and VII compares this work with the State-of-the-Art and concludes the paper, respectively.

# II. A PPD BASED PPG SENSOR

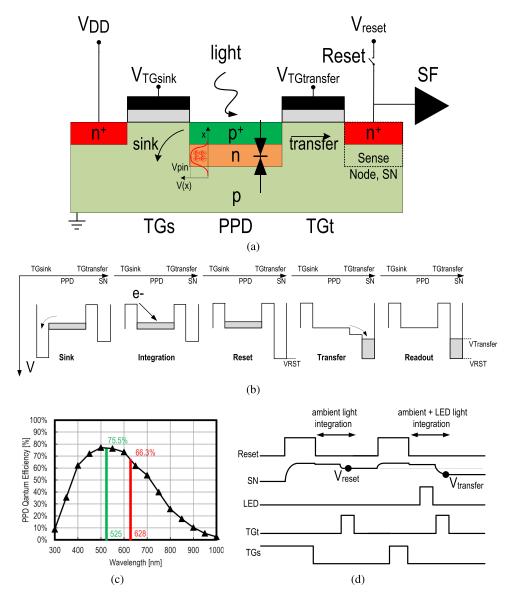

Historically, PPDs have been first developed for chargedcoupled device (CCD) technology for their enhanced performances, such as low dark current and good effective quantum efficiency (EQE), as illustrated in Fig. 2(c) [14]. A PPD consists of a np junction buried under a shallow highly doped p+ thin layer, as sketched in Fig. 2(a). A PPD behaves as a charge well where the photogenerated electrons can be stored. As shown in Fig. 2(a) the potential across the two junctions takes its maximum (pin voltage,  $V_{pin}$ ) in the depleted n region. Due to the electric field in the depleted region, the photogenerated electrons are attracted by the maximum potential across the junction. The transfer gate (TG) is used to control the potential barrier at the edge of the PPD and consequently allowing the accumulated charge to move towards the Sense Node (SN). When the TG voltage is low enough, the potential under the transfer gate is lower than the pin voltage of the PPD, allowing the photogenerated electrons to be integrated in the potential well. Moreover, the TG isolates the SN capacitance from the PPD one, leading to a lower SN capacitance and hence a larger voltage on the SN. The SN is simply a n+p junction capacitance. The voltage at the surface of the n+ layer is initially set, during the reset phase, to a high voltage,  $V_{reset}$ , in the 2.5 to 3.3 V range creating a depletion at the n+p interface. At first, the reset level is sensed, i.e.  $V_{reset}$ . After sensing the reset, the TG voltage is increased creating a depletion layer under the TG. The potential under the TG is larger than  $V_{pin}$ , but still lower than  $V_{reset}$ . During this time, i.e. transfer, the depletion layers will merge leading to the photogenerated electrons to diffuse towards the larger SN potential. The charge diffusion to the SN causes its voltage to drop from  $V_{reset}$  to  $V_{transfer}$ , with a step proportional to the quantity of photogenerated electrons, i.e. impinging light. This step is processed by the read-out circuitry by subtracting the reset level. This operation is called Correlated-Double Sampling (CDS) and not only subtracts the reset level, but as well reduces the low-frequency read-out noise and the kTC noise sampled at the level of the sense node during the reset operation, [15], [16]. The above-mentioned operations, i.e. SN reset, charge integration and transfer, can be described by the hydraulic model as in Fig. 2(b).

Nowadays, PPDs are the key ingredients of CMOS image sensors (CIS), thanks to the lower dark current and a lower noise achieved due to the CDS reference. Several markets including security, scientific imaging and medical are relying today on this technology. The excellent performance of a PPD device make it particularly suitable for the PPG application. Indeed, an on-chip high sensitivity and low noise PD can significantly reduce the LED power needed to target a specific SNR. Since the LED is the most power hungry part of a PPG chain, this would dramatically enhance the PPG sensor's battery lifetime. A double TG PPD device, as shown in Fig. 2(a), is the best fit for the PPG application. Indeed, the double TG scheme, i.e. TGsink (TGs) and TGtransfer (TGt), allows to precisely control the amount of charges integrated in the PPD well and eventually reaching the SN for read-out. This scheme is actually helpful for any application needing a consistent amount of impinging photons, to avoid any possible well saturation. In addition, controlling precisely the photoelectrons' integration means avoiding any possible LED light waste, leading to a power efficient lighting scheme. Another competitive advantage of the double TG scheme is the capability of efficiently canceling the ambient light (AL) thanks to the CDS. The timing diagram of the ambient light cancellation (ALC) is shown in Fig. 2(d). As explained above, it consists of two successive readouts having as light source the AL and the AL+LED, respectively. With respect to Fig. 2(b),  $V_{reset}$  and  $V_{transfer}$  are the SN voltages due to the AL and the AL + LED light integration and transfer, respectively. As discussed above, the CDS scheme will differentiate the two samples leading to an efficient ALC. The double TG scheme and the  $\mu$ s transfer PPD operations guarantee that the AL, both natural and artificial, integrated within the two windows is the same. This will be further detailed in Section III-2.

# III. PPG SENSOR ARCHITECTURE

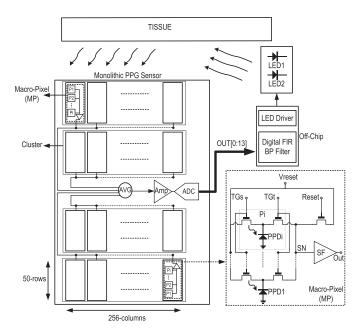

The block diagram of the PPG sensor is shown in Fig. 3. The proposed solution consists of a fully integrated chip embedding

Fig. 2. PPD device: (a) double TG PPG cross section, (b) PPD hydraulic equivalent model, (c) PPD EQE, (d) Conventional PPD readout timing diagram, (e) Modified timing diagram for ALC.

an array of PPDs, a passive averaging block, a switched-cap (SC) amplifier and an ADC, which will be described in details below.

1) A PPD Array: As discussed in Section II, a PPD is intrinsically a diffusion-based device. For this reason, a PPD cannot operate correctly with a pitch size considerably larger than a few hundred  $\mu$ m, not to end up with an inefficient charge transfer and also losing the advantage of having a low dark current, [14], [17], [18]. In addition, a larger pixel comes with a larger parasitic capacitance which ultimately affects the noise performance. With these considerations, an array of double TG PPDs has been designed, as shown in Fig. 3. Placing the PPDs into an array eases the engineering trade-off between the possible achievable dynamic range and the overall noise performance. The total number of pixels has been chosen according to the target SNR. Indeed, the design of a PPG sensor should meet at

least the SNR requirement of 28.5 dB, to achieve an accuracy within 2% of the peripheral oxygen saturation [5].

Accounting for the light shot noise only, the SNR is equal to

$$SNR = \frac{N_{AC}}{\sqrt{\sigma_{shot}^2}} = \frac{PI \cdot N}{\sqrt{N}},$$

(1)

where N is the number of impinging photons and PI the perfusion index. Rounding 28.5 dB to decimal 30 and considering a worst case PI value of 0.2%, Eq. (1) can be solved for N, leading to  $N=225\cdot 10^6$ . If one considers a PPD well saturation,  $N_{sat}$  of  $6.4\cdot 10^3$ , as in [14], then the number of pixels needed to cope with the SNR requirement is

$$pixels = \frac{N}{N_{cat}} = \frac{225 \cdot 10^6}{6.4 \cdot 10^3} = 35156.$$

(2)

Fig. 3. Block diagram of the proposed monolithic PPG sensor. The implemented ASIC consists of an array of macro-pixels, as photosensitive area, an averaging block, an amplifier and an ADC.

Eq. (1) considers the shot noise only. Another important noise source is the quantization noise and the electronic read-out noise, which modify Eq. (1) to

$$SNR = \frac{N_{AC}}{\sqrt{\sigma_{shot}^2 + \sigma_{ADC}^2 + \sigma_r^2}} = \frac{PI \cdot N}{\sqrt{N + \frac{\Delta^2}{12} + \sigma_r^2}}, \quad (3)$$

where  $\Delta$  is the quantization step (assuming uniform quantization) which depends on the full-scale range (FSR) and the chosen bit resolution,  $N_{bit}$ , and  $\sigma_r$  the read noise standard-deviation (STD). Accounting for these additional noise sources and keeping a margin of some dBs on the SNR requirement, the chosen number of pixels was 51200.

Indeed, the photosensitive area consists of four clusters of 50 rows and 256 columns, meaning 51200 total pixels, as discussed above. The 50 pixels along the i-column are assembled in a macro-pixel (MP), as shown in Fig. 3. The pixels of one MP share the same source-follower (SF) saving power while maintaining a reasonably low parasitic capacitance at the shared SN. The spatial averaging is done in two steps: first, a charge averaging on the shared SN within the same column and, second, a voltage averaging among the 1024 columns at the SFs output. This leads to a considerable shot and read noise reduction, together with a full pre-filtering of the PPG signal itself. In addition to the noise optimization, the proposed pixel achieves between 66% and 75%EQE for the selected LED wavelengths as shown in Fig. 2(c), further reducing the LED power needed for achieving the target SNR [5]. It should be mentioned that the full integration of the PPD in silicon offers an excellent EQE within the visible range, but comes at the cost of less sensitivity in the infrared region.

Next, the PPG signal is amplified by a low noise programmable gain SC amplifier.

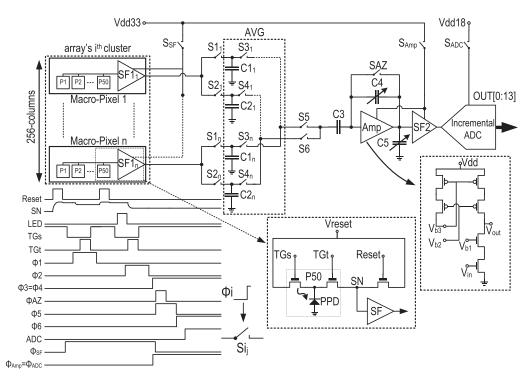

2) Switched-Cap Averaging and Amplifier: Fig. 4 shows the circuit implementation with the related timing diagram. The sense nodes, shared by 50 PPDs and corresponding to the SFs inputs, are first reset. Meanwhile, each individual PPD starts integrating the impinging light corresponding to the AL. In order to precisely control the light-induced charge integration, the PPDs are first emptied by the sink switch TGs. At the end of the first integration phase, the generated photoelectrons are transferred, via the transfer gate TGt, to the SNs. The capacitance of each SN, shared by the 50 pixels along the same column, converts the integrated photoelectrons into a voltage and performs the charge averaging across the 50 rows. After the transfer is completed the SF output voltages are sampled on capacitors  $C1_i$  via  $S1_i$ . Next, the SNs are reset again and the LED is pulsed on. As above, the PPDs precisely integrate the LED light superimposed to AL, and the related voltage level is sampled on  $C2_i$ , via  $S2_i$ , being  $C2_i = C1_i = 0.5$  pF. The power switch SSF is only closed during this charge transfer and sampling phase for minimal power consumption. By closing  $S3_i$  and  $S4_i$  all the capacitors  $C1_i$  and  $C2_i$  related to the same sample are connected in parallel and share their charge, resulting into a voltage equal to the passive spatial average of the array pixel output samples. In addition, the large capacitor resulting from the parallel connection of multiple column-level capacitors acts as a large hold capacitor for the following stage. The full averaging operation comes with a shot noise variance reduction of 50x1024 and a read noise variance reduction of 1024. In order to extract the difference of the two averaged samples, corresponding to the AL and the AL plus LED light, a SC amplifier is operated as shown in Fig. 4. First, the averaged AL sample is stored in C3, via S5 and SAZ. This phase enables to autozero the amplifier which is key for offset and 1/f noise reduction [15]. Then, SAZ is opened and the charge stored in C3 (2 pF) is transferred to C4. At the closing of S6, the amplified difference between the two average values is obtained at the amplifier's output, leading to an efficient AL cancellation. The amplifier embeds a programmable gain (set by the value of C4), from 1 to 32 to adapt to different operating conditions. It then drives an incremental ADC, through SF2. The power switches SAmp and SADC are only closed at the beginning of the array averaging and opened after the digitization.

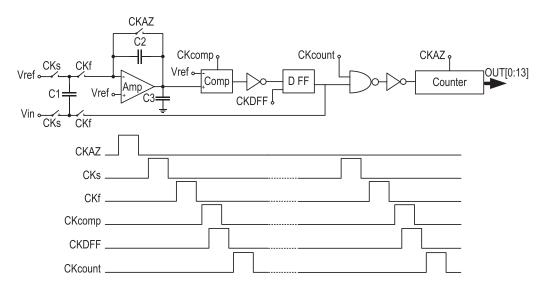

3) A Low-Power Incremental ADC With up to 14 Bits Resolution: The block diagram of the low-power incremental ADC is shown in Fig. 5. Incremental ADCs are often the best choice for low frequency and high resolution sensor interface [19]. An incremental ADC works as a  $\Delta\Sigma$  ADC, but with a periodic reset at the end of the conversion cycle. The overall ADC is operated at 1.8 V power supply, apart from the four input switches CKs and CKf which are driven at a 3.3 V gate voltage to cope with the amplifier's output that can take values larger than 1.8 V.

The designed ADC consists at first of a passive subtractor  $(\Delta)$  followed by an operational transconductor amplifier (OTA)-based SC integrator  $(\Sigma)$ . At the beginning of the ADC operation, the SC-OTA is autozeroed, during phase CKAZ. In addition, it resets the SC-OTA feedback capacitor and the asynchronous counter, determining the stop condition for the ADC. During the next phase CKs, the output of SF2, Vin, is subtracted from

Fig. 4. Architecture of the monolithic PPG sensor and detailed schematic of the OTA used in the amplifier, the averaging block, together with the timing diagram.

Fig. 5. Full schematic of the on-chip incremental ADC with the related timing diagram.

the ADC reference voltage, Vref. The difference between the two is integrated by the integrator, during phase CKf. Apart from CKAZ, all the ADC phases happen at 10 MHz frequency. The larger the input subtraction, the faster the SC-OTA output reaches Vref, causing the latched comparator (Comp) to move from logic state 0 to 1, during phase CKcomp. In CKDFF, a D-Flip Flop (DFF) tracks this new value and, thanks to a feedback loop, imposes to the SC-OTA to revert the direction of integration. The number of times Comp toggles from 0 to 1 is counted by an asynchronous counter, during phase CKcount.

In other words, a small input signal will see the Comp output more often at 0 rather than 1, determining a low final count. On the contrary, a large input signal will immediately make the SC-OTA output reach Vref, determining the Comp output to stay much often to 1 rather than 0, so consequently a large final count.

One of the advantages of this design relies on the tunable ADC resolution. Indeed, a larger resolution is achieved by making the counter counts for a longer time. At 10 MHz frequency operations, resetting the counter after  $409.6 \,\mu s$  and  $1.6 \,ms$  means

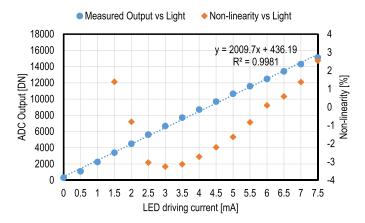

Fig. 6. Measured chip light-to-digital conversion linearity.

reaching 12 bits and 14 bits, respectively. The ADC power consumption is dominated by the OTA static current, 12  $\mu$ A at 1.8 V supply, which guarantees the right settling time.

#### IV. CHARACTERIZATION

Light to Digital Conversion: The linearity of the light to digital conversion for the PPG monolithic chip is shown in Fig. 6. The sensor is exposed to an LED shining at increasing driving current and the resulting output digital number is acquired. The programmable amplifier gain has been set to 8 which enables a wide range of emitting light conditions without saturation. With the exception of sub-mA LED operations, the chip shows  $\pm 3\%$  non-linearity in the light to digital conversion. Note that this includes all the sources of non-linearity from the LED, the readout chain to the ADC. On the other hand, as described in Section I the PPG signal consists of a relatively large DC component that can change due to respiration, AL conditions, skin tone and LED-PD distance [4]. Hence, the PPG signal is generally maintained around half of the full dynamic range, which means, with respect to Fig. 6, keeping the ADC output around 7000 DN, (Digital Numbers). In this condition, the non-linearity is less than  $\pm 1\%$ .

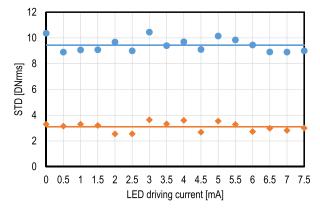

Total Noise: Fig. 7 shows the overall sensor's output noise standard deviation (STD). The STD remains constant across the dynamic range, demonstrating the effectiveness of the shot noise reduction by the spatial averaging mechanism, as discussed in Section III-2. In other words, the shot noise is maintained negligible in the working conditions. The total noise measured at the output of an off-chip 11 taps FIR low-pass filter is 3.1 DNrms in average corresponding to an input-referred noise as low as  $0.68~e-_{\rm rms}$  per PPD, thanks to the noise shaping introduced by the incremental ADC. Indeed, the noise measured directly at the output of the ADC corresponds to  $9.43~DN_{\rm rms}$ . This accounts for all the noise components including the readout noise, quantization noise, shot noise and LED flicker noise.

*ADC*: In order to assess our ADC design, the Walden Figure-of-Merit (FoM) defined as

$$FoM_w = \frac{Power}{2^{ENOB} \cdot 2BW},\tag{4}$$

- Measured Noise STD ADC output vs Light

- ◆ Measured Noise STD Off-chip Digital Low-Pass filter output vs Light

Fig. 7. Total noise STD shown both at the output of the ADC and an off-chip 11 taps FIR digital low-pass filter.

TABLE I ADC CHARACTERIZATION

| Parameters        | [19]                                        | This work |      |       |  |  |  |  |

|-------------------|---------------------------------------------|-----------|------|-------|--|--|--|--|

| Technology [nm]   | 65                                          | 180       |      |       |  |  |  |  |

| ENOB [bit]        | 14.78                                       | 10.44     | 11.7 | 12.08 |  |  |  |  |

| $FoM_w[pJ/conv.]$ | 0.76                                        | 0.79      | 1.33 | 4.09  |  |  |  |  |

| BW[kHz]           | 0.25                                        | 9.76      | 2.44 | 0.61  |  |  |  |  |

| $Area[mm^2]$      | 0.2                                         | 0.0089*   |      |       |  |  |  |  |

| Note              | *included a counter-based decimation filter |           |      |       |  |  |  |  |

has been considered, where Power is the overall ADC power consumption, ENOB the effective number of bits, accounting for the Signal-to-Noise-and-Distortion (SINAD), and BW the maximum signal bandwidth. The FoM, the lower the better, is expressed in pJ/conv. - step [19]. In our design, the maximum signal BW depends on the chosen resolution. Indeed, as shown in Section III-3, lower resolutions come with faster conversions and consequently larger allowable signal BW. The results are shown in Table I. Our design reaches almost the same FoM as the reference work [19], but at much lower area and larger signal bandwidth despite a less advanced technology node (180 nm) in our case compared to [19] (65 nm). On the other hand, this is achieved at a lower ENOB.

## V. PPG MEASUREMENTS

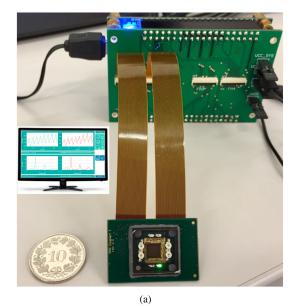

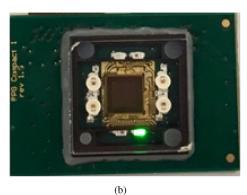

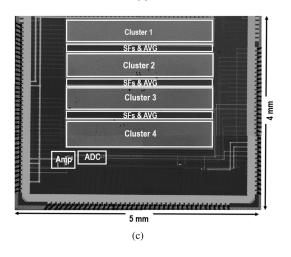

Measurement Set-up: The measurement set-up and the micrograph die photo of the  $0.18~\mu m$  chip are shown in Fig. 8(a) and Fig. 8(c), respectively. The experimental set-up of Fig. 8(a) consists of a field-programmable-gate-array (FPGA) board driving the PPG chip. By the means of an UART protocol, the chip's data are real-time streamed out to a computer, via the FPGA, for displaying or processing. The chip and the LEDs (all surrounding the chip) are placed on a compact board, shown in Fig. 8(b). The latter measures 2 cm by 3 cm and allows PPG measurements on different body locations. Two LED families, each one both in green and red, have been chosen and both are mounted on the PCB. Visible LEDs, green and red, have been preferred so to match the maximum EQE of the array,

Fig. 8. (a) Measurement set-up consisting of an FPGA device interfacing with an application running on a computer and the monolithic PPG sensor on a compact board, (b) Zoom on the compact evaluation board of 2 cm by 3 cm, (c) Micrograph of the monolithic PPG sensor, 4 mm by 5 mm.

as presented in Fig. 2(c). The LEDs are driven off-chip by the means of discrete current sources and switches. The silicon and the LEDs are protected by a plastic 3D-printed case which has been sealed by a highly-transparent glass. To enhance the quality of the PPG reading, particular attention has been dedicated to the realization of this compact board. Indeed, while engineering a

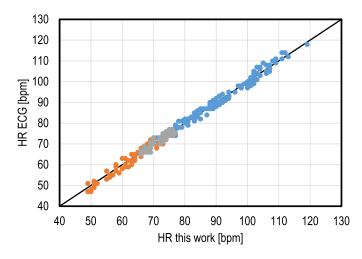

Fig. 9. Correlation of HR data between this work and a commercial ECG chest strap. The experiment has been carried out at 4.6  $\mu$ W total power (LED+AFE+ADC) on three healthy individuals (each color representing one person).

PPG module the direct light cross-talk between the LED and the PD, the PD-LED distance and the LED's height versus the PD's are particularly important variables that can ultimately enhance or deteriorate the PPG readings [4].

8) In-Vivo PPG Measurements: An in-vivo acquisition of PPG has been performed in reflection mode on the index finger. Fig. 9 shows a comparison between the HR directly extracted from the sensor output and a commercial ECG chest strap. The comparison features a HR average error and max error of 1.38 bpm and 3 bpm, respectively. These measurements have been taken on three healthy male subjects for a total of 222 measurements. These measurements have been obtained with a sampling frequency of 40 Hz, an average LED driving power of 1.97  $\mu$ W (red light), at a duty cycle of 0.07%, and a readout (AFE+ADC) average power consumption of 2.63  $\mu$ W only. This is obtained, referring to Fig. 4, by closing SSF for 80  $\mu$ s and SAmp with SADC for 0.5 ms.

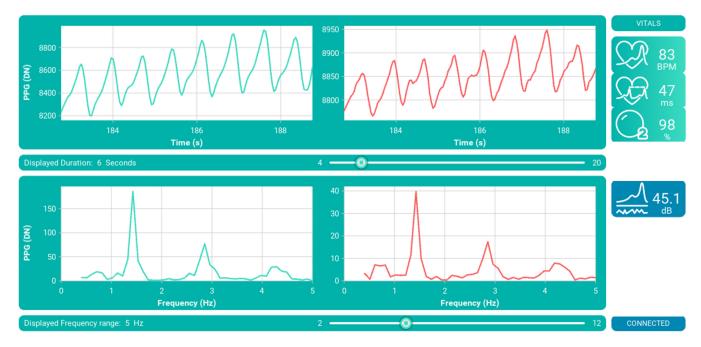

In Fig. 12 two PPG signals are shown, both recorded on the index finger. The PPG signals are recorded and displayed thanks to an application running on a computer whose interface is shown in Fig. 12. The two signals are recorded for a green and red LED and shown both in time and frequency domain. For both the emitting wavelengths, the Fast-Fourier-Transform (FFT) shows a clear signal component with a measured SNR of 45.1 dB for the green channel at a sampling frequency of 25 Hz. Due to the lower tissue absorption encountered by the red light, the measured PI for the red channel is roughly 4 times lower giving rise to an SNR of about 33 dB. Together with the recorded PPG signals, Fig. 12 displays the real-time HR, heart rate variability (HRV) and  $S_nO_2$ . Indeed, the measured SNR on the two channels clearly overcomes the requirements for a reliable  $S_pO_2$  measurement, as discussed in Section III-1. Regarding the  $S_pO_2$  measurement, it should be highlighted that the difference in the extinction coefficient of oxygenated and deoxygenated haemoglobin at the green wavelength is comparable with the difference at near-infrared (800 nm), [20]. Moreover, the choice of the visible range fits best the EQE of our PPD, Fig. 2(c), further reducing the needed LED power. The measurements as in Fig. 12 have been performed at a total power consumption (LED Green+LED Red+AFE+ADC) of 44  $\mu$ W, out of which only 35  $\mu$ W are burnt by the LEDs.

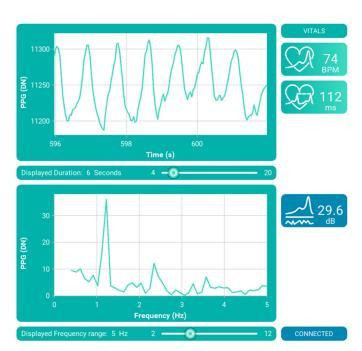

Fig. 13 displays a real time PPG signal recorded on the wrist for the green channel at a total power consumption (LED+AFE+ADC) of 29  $\mu$ W, out of which only 20  $\mu$ W are burnt by the LED. Despite the severe challenges at the wrist location due to the extremely low PI, the recorded SNR of 29.6 dB is sufficient for the strict requirement around the measure of the  $S_pO_2$ . Unlike Fig. 9, measurements in Figs. 12 and 13 have been obtained with a sampling frequency of 25 Hz and a duty cycle of 0.7%. The reported power consumption is obtained, referring to Fig. 4, by closing SSF for 400  $\mu$ s and SAmp with SADC for 2.5 ms. The objective behind Fig. 9 is to report the lowest power consumption which is still enough to guarantee reliable HR monitoring versus a gold standard. Figs. 12 and 13 show, respectively, how much power overhead one has to account while using this sensor for more constrained applications, such as the  $S_pO_2$ , or more challenging body locations, such as the wrist.

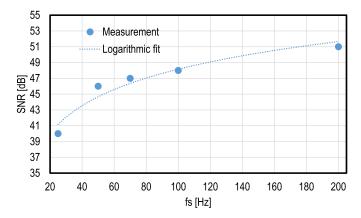

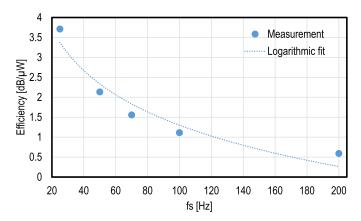

9) SNR vs Sampling Frequency: the objective of this section is to show how the measured SNR of the PPG signal changes with respect to the sampling frequency,  $f_s$ . The SNR has been measured on the same subject and identical body location, i.e. finger, in order to to avoid any possible measurement mismatch. The SNR is evaluated by considering the total PPG AC signal power carried by the fundamental frequency,  $f_{AC}$ , and the two harmonics,  $2f_{AC}$  and  $3f_{AC}$ , versus the noise floor, as reported in the following equation

$$SNR_{measured} = 10 \log_{10} \left( \frac{S_{f_{AC}}^2 + S_{2f_{AC}}^2 + S_{3f_{AC}}^2}{N_{floor}^2} \right). \tag{5}$$

For the experiment,  $f_s$  has been swept from 25 Hz to 200 Hz, whose span guarantees a quite versatile field of use. During the measurement the subject's HR has ranged between 72 bpm and 75 bpm, meaning an  $f_{AC}$  of 1.2 Hz and 1.25 Hz, respectively. Obviously, a larger  $f_s$  comes with a larger LED and chip power consumption. In order to account for the increased power, a FoM has been introduced

$$FoM = \frac{SNR_{measured}}{Power_{total}},$$

(6)

expressed in  $dB/\mu W$ , which reports the overall sensor efficiency. Fig. 10 shows how the measured SNR changes according to  $f_s$ . Increasing  $f_s$  results into an SNR increase. On the other hand, this translates into a consistent power increase which reduces the sensor efficiency. Indeed, as shown in Fig. 11, the maximum sensor efficiency is reached for  $f_s$  equal to 25 Hz.

Fig. 10 shows that the SNR depends logarithmically on  $f_s$ . This can be explained by the effect of the sampling frequency on the noise floor in the Nyquist band. Indeed the PPG signal is sampled without any anti-alising filter, which results into aliasing. In the Nyquist band the noise floor is amplified by the undersampling factor [15], which is inversely proportional

Fig. 10. Measured SNR vs  $f_s$  and logarithmic fit.

Fig. 11. Measured sensor efficiency vs  $f_s$  and logarithmic fit.

to  $f_s$ . This linear behavior is transposed into a logarithm one by Eq. (5) which confirms the trends reported in Figs. 10 and 11.

## VI. DISCUSSION AND COMPARISON TO STATE-OF-THE-ART

The measurement results of the proposed PPG sensor, presented in the previous sections, are summarized and compared to the most recent and relevant state-of-the-art's work in Table II. Table II shows that the proposed new sensor architecture comes with a dramatic power saving. Indeed, the enhanced sensitivity and noise performance of our chosen photodetecting scheme enable a significant power saving leading to the record low level of 4.6  $\mu$ W, LED included. This is about from 10 to 100 times lower than state-of-the-art [5]–[7], [9], [12]. Moreover, this record low power performance doesn't come at the cost of a low SNR. Indeed, the measured SNR, even at low sampling frequency, is larger than the one provided in state-of-the-art which is often lower than 40 dB [5], [6].

The improvements achieved in this work were obtained by carefully re-shaping the photodetecting scheme and AFE. Indeed, the excellent sensitivity, EQE and noise performance of PPDs enable a consistent reduction of the needed LED power to target a specific SNR. The PPDs have been integrated into an array, this enabling spatial averaging and a consistent noise reduction. The number of PPDs has been carefully chosen based

Fig. 12. Measured PPG raw signals at the finger for two emitting wavelengths, green and red. The real-time HR, HRV,  $S_pO_2$  are displayed from the top to the bottom, respectively. The measured SNR is related to the green channel.

Fig. 13. Measured PPG raw signals at the wrist for the green channel. The real-time HR, HRV and SNR are displayed from the top to the bottom, respectively.

on an SNR and dynamic range analysis. This accounts for both the most important noise sources and the minimum number of impinging photons guaranteeing enough SNR at the fairly low PI of the PPG signal.

The biggest challenge to efficiently reduce the PPG sensor power consumption comes from the LEDs driving current. Indeed, due to the intrinsic limitations coming from the biological tissues [4] the LED driving current should be large enough to ensure enough light reflection. This becomes even more severe in the presence of dark skin tones. State-of-the-art's works have mostly focused on reducing the LED power by heavily duty-cycling the light emission. At first, this has happened at uniform sampling [5], [6], even though the reached total power consumption is still in the order of several hundreds of  $\mu$ W, as shown in Table II.

The works in [7], [8] have presented for the first time a non-uniform, i.e. compressive, sampling PPG sensor. Indeed, the PPG signal is sparse in the frequency domain and this can be exploited to achieve a strong reduction of the LED duty-cycle and generally speaking of the average sampling frequency. A duty-cycle as low as 0.0125% and an effective sampling frequency of 4 Hz have been obtained, as shown in Table II. Although the compressive sampling scheme comes with competitive advantages, on the other hand this is still challenging. Indeed, it requires a tight synchronization of all the system's components and reconstructing the compressive-sampled data requires additional power. Consequently, even for this work, the reached total power consumption is still in the order of several hundreds of  $\mu$ W, as shown in Table II.

A heart-beat-locked loop system that significantly reduces the LED power by activating the light emission only during the PPG peaks has been recently demonstrated in [9]. However, this power reduction comes at the cost of more complexity since it requires a non-trivial heart beat prediction scheme and intrinsically hinders the full PPG wave representation.

The proposed solution relying on a PPD array enables the full integration of the photosensitive area together with the AFE. Indeed, an off-chip PD comes with a non-negligible parasitic capacitance, ultimately limiting the noise performance and the speed/power of the AFE. Moreover, it increases the

| Reference                     | This work   | [5]      | [6]      | [7]     | [9]    | [11]       | [12]                 |

|-------------------------------|-------------|----------|----------|---------|--------|------------|----------------------|

| Year                          | 2019        | 2013     | 2015     | 2016    | 2018   | 2015       | 2017                 |

| <b>Technology</b> $[nm]$      | 180         | 350      | 180      | 180     | 180    | 350        | 180                  |

| Supply Voltage [V]            | $3.3/1.8^a$ | 3.3      | 1.8      | 1.2     | 3.3    | 3.3        | NA                   |

| Sampling Frequency $[Hz]$     | 40          | 100      | 165      | 4       | 100    | 10000      | 160000               |

| LED Duty Cycle [%]            | 0.07        | 3        | 0.7      | 0.0125  | 0.0175 | NA         | $10^{b}$             |

| Full Integration <sup>c</sup> | Yes         | No       | No       | No      | No     | Yes        | Yes                  |

| Avg HR Error [bpm]            | $1.38^{d}$  | NA       | NA       | NA      | NA     | NA         | NA                   |

| Max HR Error [bpm]            | 3           | NA       | NA       | 10      | 2.1    | $NA^e$     | NA                   |

| <b>LED Power</b> $[\mu W]$    | 1.97-26.6   | 309-1360 | 120-1125 | 43-1200 | 16-520 | NA         | NA                   |

| AFE+ADC Power $[\mu W]$       | 2.63        | 528      | 216      | 172     | 27.4   | NA         | 13-14.4 <sup>f</sup> |

| <b>TOT Power</b> $[\mu W]^g$  | 4.6         | 837      | 336      | 215     | 43.4   | $4600^{h}$ | NA                   |

|                               |             |          |          |         |        |            |                      |

TABLE II

SUMMARY OF THE PPG SENSOR PERFORMANCE WITH COMPARISON TO STATE-OF-THE-ART

- a ADC supplied at 1.8 V

- <sup>b</sup> Reported data for LED pulsed operations

- <sup>c</sup> Photosensitive area+AFE+ADC

- <sup>d</sup> Measured at 4.6 µW total power vs a commercial ECG chest strap on 222 measurements on three healthy individuals, as in Fig. 9

- $^e$  The work focuses on the  $S_p O_2$  accuracy

- f LED Pulsed operations

- g Best case from the given data for the HR mode

- h Supposed to be dominated by the digital processing unit

silicon area. The recent work in [12] shows an interesting PPG sensor integrating on silicon an array of PDs with distributed 1b delta-sigma light-to-digital converter. Despite the achieved power consumption is very promising versus the state-of-the-art's work, this doesn't account for the LED driving current which is supposed to be quite large given the fairly high sampling frequency.

# VII. CONCLUSION

This work demonstrates that an array of PPDs can dramatically reduce the PPG sensor total power consumption. Indeed, an extremely low noise and high sensitivity photodetector accompanied by an ultra low noise and low power AFE represent the two key ingredients for reducing the LED power consumption.

Compared to recent state-of-the-art this work comes with the lowest power consumption. Moreover, among the most relevant state-of-the-art's works, this is the only solution featuring a full integration of the photosensitive area together with the AFE and the ADC at an extremely low power consumption, i.e. smaller than 10  $\mu$ W, this accounting both for the LED and the AFE+ADC. This last feature added to the extremely low power consumption and excellent signal quality makes this solution a serious answer to the increasing demand of continuous and reliable health monitoring devices.

## REFERENCES

- "Obesity and Overweight," World Health Organization, Geneva, Switzerland, 2018.

- [2] "World Population Prospects: The 2010 Revision—Adapted from Global Health & Aging," World Health Organization, Geneva, Switzerland, 2011.

- [3] "2018 Global Health Care Outlook—The evolution of smart health care," Deloitte, New York, NY, USA, 2018.

- [4] J. G. Webster, Design of Pulse Oximeters. Bristol, PA, USA: Philadelphia: Inst. Phys. Pub., 1997.

- [5] K. N. Glaros and E. M. Drakakis, "A sub-mW fully-integrated pulse oximeter front-end," *IEEE Trans. Biomed. Circuits Syst.*, vol. 7, no. 3, pp. 363–375, Jun. 2013.

- [6] E. S. Winokur, T. O'Dwyer, and C. G. Sodini, "A low-power, dual-wavelength photoplethysmogram (PPG) SoC with static and time-varying interferer removal," *IEEE Trans. Biomed. Circuits Syst.*, vol. 9, no. 4, pp. 581–589, Aug. 2015.

- [7] P. V. Rajesh et al., "A 172μ W compressive sampling photoplethysmographic readout with embedded direct heart-rate and variability extraction from compressively sampled data," in Proc. IEEE Int. Solid-State Circuits Conf., 2016, pp. 386–387.

- [8] V. R. Pamula et al., "A 172 µW compressively sampled photoplethys-mographic (PPG) readout ASIC with heart rate estimation directly from compressively sampled data," *IEEE Trans. Biomed. Circuits Syst.*, vol. 11, no. 3, pp. 487–496, Jun. 2017.

- [9] D. Jang and S. Cho, "A 43.4 µW photoplethysmogram-based heart-rate sensor using heart-beat-locked loop," in *Proc. IEEE Int. Solid - State Circuits Conf.*, 2018, pp. 474–476.

- [10] A. Caizzone, C. Enz, and A. Boukhayma, "Comprehensive noise analysis in PPG read-out chains," in *Proc. Int. Conf. Noise Fluctuations*, 2017, pp. 1–4.

- [11] D. He *et al.*, "A single-chip CMOS pulse oximeter with on-chip lockin detection," *Sensors*, vol. 15, no. 7, pp. 17076–17088, 2015. [Online]. Available: http://www.mdpi.com/1424-8220/15/7/17076

- [12] H. Kim and D. Jee, "A < 25  $\mu$ W CMOS monolithic photoplethysmographic sensor with distributed 1b delta-sigma light-to-digital convertor," in *Proc. 43rd IEEE Euro. Solid State Circuits Conf.*, 2017, pp. 55–58.

- [13] A. Caizzone, A. Boukhayma, and C. Enz, "A 2.6μ W monolithic CMOS photoplethysmographic sensor operating with 2μ W LED power," in *Proc. IEEE Int. Solid- State Circuits Conf.*, 2019, pp. 290–291. doi: 10.1109/ISSCC.2019.8662404.

- [14] A. Boukhayma, A. Peizerat, and C. Enz, "A sub-0.5 electron read noise VGA image sensor in a standard CMOS process," *IEEE J. Solid-State Circuits*, vol. 51, no. 9, pp. 2180–2191, Sep. 2016.

- [15] C. Enz and G. C. Temes, "Circuit techniques for reducing the effects of opamp imperfections: Autozeroing, correlated double sampling, and chopper stabilization." *Proc. IEEE*, vol. 84, no. 11, pp. 1584–1614, Nov. 1996.

- [16] A. Caizzone, C. Enz, and A. Boukhayma, "An accurate kTC noise analysis of CDS circuits," in *Proc. 16th IEEE Int. New Circuits Syst. Conf.*, 2018, pp. 22–25.

- [17] A. Boukhayma, C. Enz, and A. Peizerat, "Temporal readout noise analysis and reduction techniques for low-light CMOS image sensors," *IEEE Trans. Electron. Devices*, vol. 63, no. 1, pp. 72–78, Jan. 2016.

- [18] A. Boukhayma, A. Peizerat, and C. Enz, "Noise reduction techniques and scaling effects towards photon couting CMOS image sensors," *Sensors*, vol. 16, no. 4, Apr. 2016, Art. no. 514.

- [19] C.-H. Chen, Y. Zhang, T. He, and G. C. Temes, Micropower Incremental Analog-to-Digital Converter. Cham, Switzerland: Springer, 2016.

- [20] C. Lochner, Y. Khan, A. Pierre, and A. Arias, "All-organic optoelectronic sensor for pulse oximetry," *Nature Commun.*, vol. 5, Dec. 2014, Art. no. 5745.

Antonino Caizzone (S'17) was born in Milazzo, Italy, on March 20th, 1991. He received the bachelor degree in electronic engineering from the University of Catania, Catania, Italy, in 2013 and two masters in micro and nanotechnology from Grenoble Institute of Technology, Grenoble, France and Polytechnique of Turin, Turin, Italy, respectively, in 2015. He is currently working toward the Ph.D. at the 'Ecole Polytechnique Fédérale de Lausanne (EPFL), Lausanne, Switzerland, under the supervision of Prof. Enz and Dr. Boukhayma, on the subject of ultra-low

noise and low power sensors for healthcare. Between 2012 and 2013 he worked with STMicroelectronics, Catania, Italy, as an Intern on the design of analog electronics on plastic substrate. In 2014, he worked with Georgia Tech. Atlanta, GA, USA, as a Visiting Researcher on the subject of energy harvesters.

Assim Boukhayma (M'18) was born in Rabat, Morocco, on February 5th, 1988. He received the Ph.D. degree from the Ecole Polytechnique Fédérale de Lausanne (EPFL), Lausanne, Switzerland, on the subject of ultra low noise CMOS image sensors. He is currently a Research Team Leader with the Integrated Circuits Laboratory, EPFL. From 2012 to 2016, he worked at Commissariat al'Energie Atomique (CEA-LETI), Grenoble, France, in the frame of his Ph.D. research. In 2012, he did the M.Sc. Internship at CEA-LETI, Grenoble, France, on the design of a

low-noise CMOS THz camera. He was the recipient of the Springer Thesis Award in recognition for his outstanding Ph.D. research.

Christian Enz (F'19) received the M.S. and Ph.D. degrees in electrical engineering from the 'Ecole Polytechnique Fédérale de Lausanne (EPFL), Lausanne, Switzerland, in 1984 and 1989, respectively. In 1999, he joined the Swiss Center for Electronics and Microtechnology (CSEM), Neuchtel, Switzerland, where he launched and led the RF and Analog IC Design group. In 2000, he was promoted to Vice President, heading the Microelectronics Department, which became the Integrated and Wireless Systems Division in 2009 In 2013, he joined EPFL as a Full

Professor, where he is currently the Director of the Institute of Microengineering, Neuchâtel, Switzerland, and also the Head of the Integrated Circuits Laboratory (ICLAB), Neuchâtel, Switzerland. His current research interests include the very low-power analog and RC IC design and semiconductor device modeling.