#### **General Disclaimer**

### One or more of the Following Statements may affect this Document

- This document has been reproduced from the best copy furnished by the organizational source. It is being released in the interest of making available as much information as possible.

- This document may contain data, which exceeds the sheet parameters. It was furnished in this condition by the organizational source and is the best copy available.

- This document may contain tone-on-tone or color graphs, charts and/or pictures, which have been reproduced in black and white.

- This document is paginated as submitted by the original source.

- Portions of this document are not fully legible due to the historical nature of some

of the material. However, it is the best reproduction available from the original

submission.

(NASA-CR-168992) ARCHITECTURE FOR VISI DESIGN OF MEED-SCLOMON ENCOLERS (Jet Propulsion Lab.) 51 p HC A04/MF A61

N82-25801

CSCL 09B

Unclas 27981

G3/60

# Architecture for VLSI Design of Reed-Solomon Encoders

K. Y. Liu

June 8, 1981

# NASA

National Aeronautics and Space Administration

Jet Propulsion Laboratory California Institute of Technology Pasadena, California

# Architecture for VLSI Design of Reed-Solomon Encoders

K. Y. Liu

June 8, 1981

National Aeronautics and Space Administration

Jet Propulsion Laboratory California Institute of Technology Pasadena, California The research described in this publication was carried out by the Jet Propulsion Laboratory, California Institute of Technology, under contract with the National Aeronautics and Space Administration.

#### ACKNOWLEDGMENT

This document consolidates one phase of research under the NASA End-to-End Information System (NEEDS) program and the LSI Product Assurance Technology program spongored by the Chief Engineer's Office at NASA. The author expresses his gratitude to Dr. A. J. Ferrari, J. A. Hunter, Richard B. Miller, and R. H. Nixon for their support which made this publication possible. Also, the author thanks Dr. J. J. Lee, M. Perlman, and R. F. Rice for their comments and suggestions. Finally, the author thanks J. T. Sumida and J. C. Packard for providing the detailed logic design and fabrication, respectively.

#### ABSTRACT

In this document, the logic structure of a universal VLSI chip called the symbol-slice Reed-Solomon (RS) encoder chip is presented. An RS encoder can be constructed by cascading and properly interconnecting a group of such VLSI chips. As a design example, it is shown that a (255,223) RS encoder requiring around 40 discrete CMOS IC's may be replaced by an RS encoder consisting of four identical interconnected VLSI RS encoder chips. Besides the size advantage, the VLSI RS encoder also has the potential advantages of requiring less power and having a higher reliability.

## TABLE OF CONTENTS

| I.     | INTRODUCTION                                                                          | 1-1          |

|--------|---------------------------------------------------------------------------------------|--------------|

| II.    | BASIC CONCEPTS OF FINITE FIELDS                                                       | 2-1          |

| III.   | REED-SOLOMON ENCODING PROCEDURES                                                      | 3-1          |

| IV.    | SYMBOL-SLICE VI.SI RS ENCODER ARCHITECTURE                                            | 4 – 1        |

|        | 4.1 VLSI RS ENCODER USING THE ROW PARTITIONING TECHNIQUE                              | <b>4 –</b> 3 |

|        | 4.1.1 Generator Polynomial Coefficients Table                                         | 4-3          |

|        | 4.1.2 Finite Field Multiplier                                                         | 4-6          |

|        | 4.1.3 Input and Feedback Control Switches                                             | 4-6          |

|        | 4.1.4 Input/Output Data Connections                                                   | 4-8          |

|        | 4.2 VLSI RS ENCODER USING THE COLUMN PARTITIONING TECHNIQUE                           | 4-9          |

| V.     | PERFORMANCE OF THE VLSI RS ENCODER SYSTEM                                             | 5 <b>-</b> 1 |

| VI.    | CONCLUSIONS                                                                           | 5 <b>–</b> 1 |

| REFERI | ENCES                                                                                 | <b>≀</b> −1  |

| APPEN  | DIX                                                                                   |              |

|        | VLSI REED-SOLOMON ENCODER FOR THE PROPOSED NASA/ESA TELEHETRY CHANNEL CODING STANDARD | \ <b>-</b> 1 |

#### LIST OF FIGURES

| Figure |                                                                                                                                                                     |   | Page |

|--------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------|---|------|

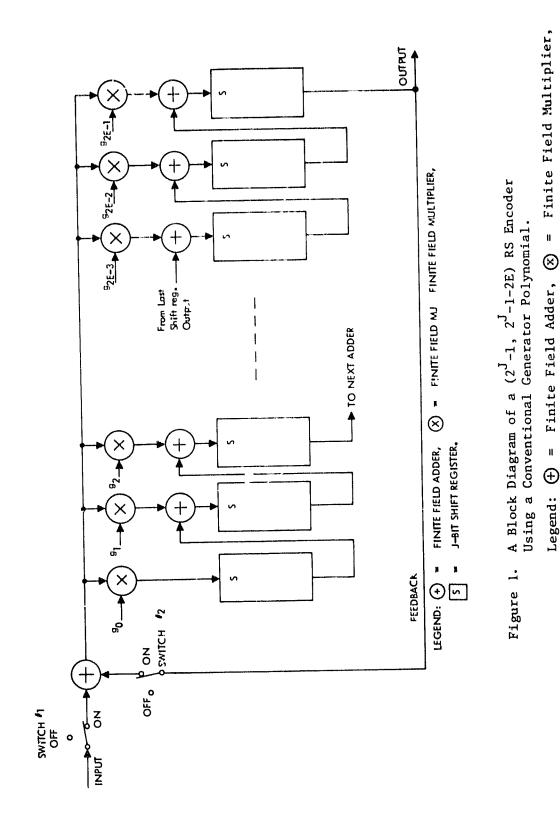

| 1      | A Block Diagram of a $(2^J-1, 2^J-1-2E)$ RS Encoder Using a Conventional Generator Polynomial                                                                       | • | 3-2  |

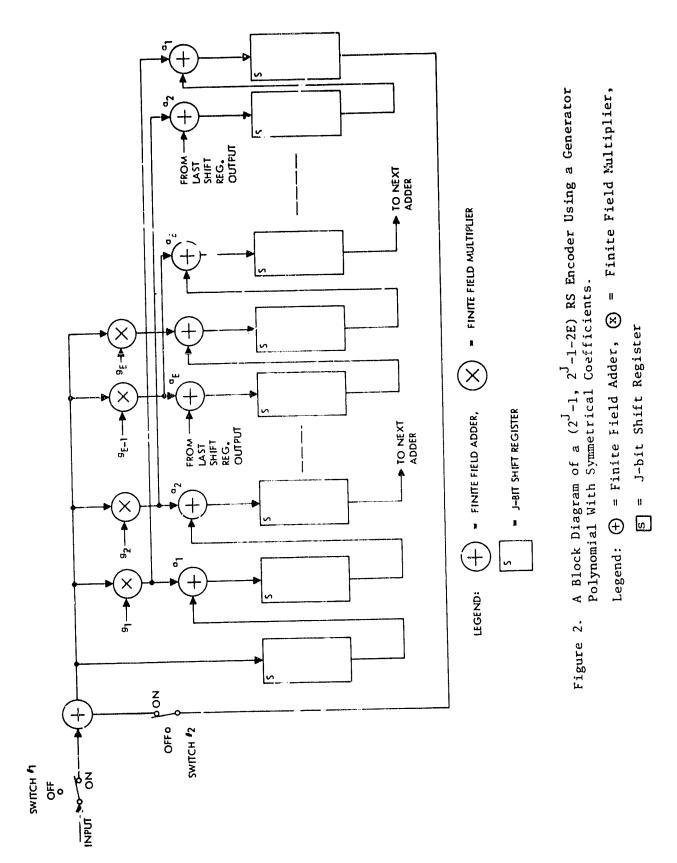

| 2      | A Block Diagram of a (2 $^{\rm J-1}$ , 2 $^{\rm J-1-2E}$ ) RS Encoder Using a Generator Polynomial With Symmetrical Coefficients                                    | • | 3-5  |

| 3      | Code Array Structure and Order of Symbol Transmission For Type B Interleaving, Where Interleaving Level = I                                                         |   | 3-6  |

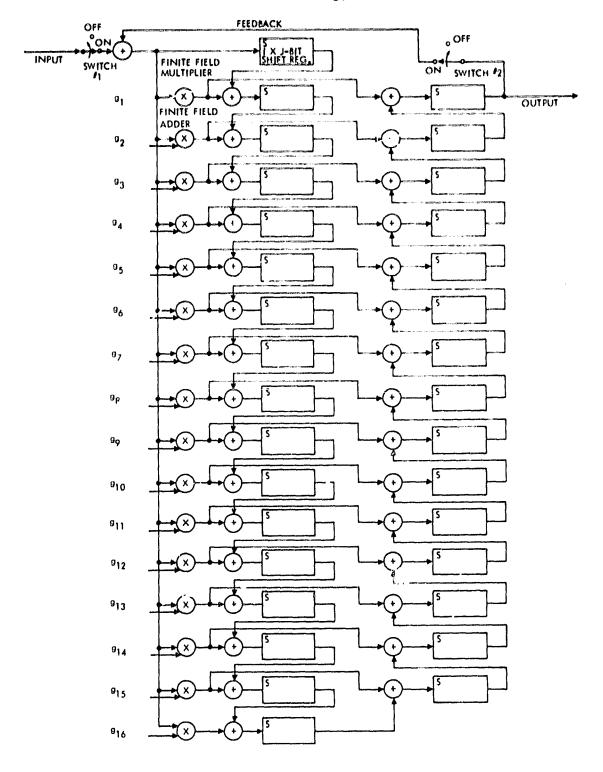

| 4      | A Block Diagram of a (255,223) RS Encoder With Interleaving Level I and                                                                                             |   | 3-8  |

|        | $g(x) = \prod_{i=1}^{143} (x - a^i)$                                                                                                                                |   |      |

| 5      | VLSI RS Encoder Chip Logic Structure (Row Partitioning)                                                                                                             |   | 4-4  |

| 6      | VLSI RS Encoder System Diagram (Row Partitioning)                                                                                                                   |   | 4-5  |

| 7      | Logic Structure of a Serial-Parallel Finite Field Multiplier Which Performs $\alpha^1$ * $\alpha^1$ Modulo $\alpha^8$ + $\alpha^4$ + $\alpha^3$ + $\alpha^2$ + 1    |   | 4-7  |

| 8      | VLSI RS Encoder Chip Logic Structure (Column Partitioning)                                                                                                          |   | 4-10 |

| 9      | Inter-Chip Connection Diagram (Column Partitioning)                                                                                                                 |   | 4-11 |

| 10     | Throughput Improvement by Multiplexing VLSI RS Encoder Chips (Row Partitioning Version)                                                                             |   | 5-2  |

| A1     | Logic structure of a serial-parallel finite field multiplier which performs $\alpha^1 * \alpha^j \mod \alpha = \alpha^8 + \alpha^7 + \alpha^2 + \alpha + 1 + \dots$ |   | ۸6   |

### LIST OF TABLES

| Table |                                                                                                                                     | Page  |

|-------|-------------------------------------------------------------------------------------------------------------------------------------|-------|

| 1     | Exponents versus elements in a finite field GF( $2^8$ ) generated by the primitive polynomial $x^8 + x^4 + x^3 + x^2 + 1 \dots$     | . 2-6 |

| 2     | Elements versus exponents in a finite field $GF(2^8)$ generated by the primitive polynomial $x^8+x^4+x^3+x^2+1$                     | . 2-7 |

| 3     | Generator Polynomial Coefficients for g (x) = $\prod_{i=112}^{143}$ (x - $\alpha^{i}$ )                                             | . 3-4 |

| A1    | Elements versus exponents in a finite field GF( $2^8$ ) generated by the primitive polynomial $x^8 + x^7 + x^2 + x + 1 \dots \dots$ | . Λ4  |

| A2    | Generator Polynomial Coefficients for                                                                                               |       |

|       | $g(x) = \prod_{j=1,2}^{143} (x - \alpha^{ij})$ , where j=1,7,11,13,19,23,37 and 43                                                  | . A-5 |

#### SECTION I

#### INTRODUCTION

Reed-Solomon (RS) codes (Ref. 1) are nonbinary BCH codes. These codes can correct both random and burst errors over a communication channel. Recently concatenated coding systems using RS codes as the outer codes have been proposed for space communication to achieve very low error probabilities (Refs. 2 to 7). Several deep space flight projects such as the Voyager at Uranus encounter, the Galileo, and the International Solar Polar Mission (ISPM) have also considered using the concatenated RS/Viterbi channel coding scheme. Hence RS codes are quite important for space communications.

The complexity of an RS encoder is proportional to the errorcorrecting capability of the code, the speed of the encoding, and the interleaving

level used (Ref. 4). For reliable space communication there is a need to use RS

codes with large error-correcting capability and large interleaving level (Refs.

4, 5, 8, and 9. Hence one is especially interested in minimizing the complexity

of RS encoders for space communication applications. In a spacecraft the power,

size, and reliability requirements are usually quite severe. Thus there is considerable interest in a VLSI (Very Large Scale Integration) RS encoder which has

the potential for significant savings in size, weight, and power while at the

same time providing higher reliability over an RS encoder implemented in discrete

logic circuits.

This document introduces a symbol-sliced logic structure suitable for a VLSI implementation of RS encoders. By cascading and properly interconnecting a group of such VLSI chips, each consisting of a fixed portion of the encoder, it is possible to obtain an RS encoder with any desired error-correcting capability

and interleaving level. As a design example, it is shown that a (255,223) RS encoder requiring 40 discrete CMOS IC's may be replaced by an RS encoder consisting of four identical interconnected VLSI encoder chips. It is also shown that these VLSI RS encoder chips can be paralleled to improve the encoding speed.

#### SECTION II

#### BASIC CONCEPTS OF FINITE FIELDS

A field is a set of elements, including 0 and 1, any pair of which may be added or multiplied (denoted by + and \*) to give a unique result in the field. The addition and multiplication are associative and commutative, and multiplication distributes over addition in the usual way, i.e.,

$$u * (v+w) = u*v+u*w$$

Every field element u has a unique negative element -u in the same field such that

$$u + (-u) = 0$$

Every nonzero field element u has a unique reciprocal field element l/u, such that

For every field element u

and

If the number of elements in a field is infinite, then it is called an infinite field. Examples of infinite fields are:

- (a) The rational number field.

- (b) The real number field.

- (c) The complex number field.

If the number of elements in a field is finite, then it is called a finite field or a Galios field GF(q), where q is the number of elements in the field. Two examples of finite fields are given as follows. The first example is the finite field GF(p) which is formed by integers modulo p, where p is a prime. If p=2, then the field is called GF(2). GF(2) contains only two elements, i.e., 0 and 1. The addition and multiplication tables of GF(2) are given as below:

$$\begin{array}{c|cc}

0 & 1 \\

0 & 0 \\

1 & 0 & 1

\end{array}$$

Addition

Multiplication

The second example is the finite field formed by polynomials modulo and irreducible polynomial of degree m with coefficients in GF(p), where p is a prime. The definition of an irreducible polynomial is given as follows. A polynomial

$$p(x) = \sum_{i=0}^{m} a_i x^i$$

with  $a_1 \in GF(p)$  is called irreducible over GF(p) if there exists no polynomials A(x) and B(x) with coefficients from GF(p) such that

$$p(x) = A(x) B(x)$$

where

$1 \le Degree of A(x) \le m-1$

As an example, if p = 2, then the polynomials

$$x^8 + x^4 + x^3 + x^2 + 1$$

and

$$x^4 + x + 1$$

are irreducible over GF(2).

Now the multiplicative structure of finite fields will be discussed. If a field contains an element  $\alpha$ , then the least positive integer N for which  $\alpha^N=1$  is called the order of  $\alpha$ . In a finite field of q elements, GF(q), there is a primitive element  $\alpha$ , i.e., an element of order q-1. Every nonzero element of GF(q) can be expressed as a power of  $\alpha$ .

Next the vector space structure of finite fields will be presented. To do it, one needs the following definition of a primitive polynomial. An irreducible polynomial of degree m over GF(q) is called primitive if it has a primitive element of  $GF(q^m)$  as a root. A finite field of  $q^m$  elements,  $GF(q^m)$ , can be considered as an m-dimensional vector space over GF(q). A choice for a basis of  $GF(q^m)$  over GF(q) is the set

$$\left\{1, \alpha, \alpha^2, ---, \alpha^{m-1}\right\}$$

which is called the canonical basis, where  $\alpha$  is a root of a primitive polynomial of degree m over GF(q). In vector form

$$\left\{1, \alpha, \alpha^2, ---, \alpha^{m-1}\right\}$$

is represented as

$$1 \leftrightarrow (0, 0, ---, 0, 0, 1)$$

$$\alpha \leftrightarrow (0, 0, ---, 0, 1, 0)$$

$\alpha^{2} \leftrightarrow (0, 0, ---, 1, 0, 0)$

$$\alpha^{m-1} \leftrightarrow (1, 0, ---, 0, 0, 0)$$

whereas 0 is mapped to (0, 0, ---, 0). Thus all elements in  $GF(q^m)$  except 0 can be formed by linear combinations of the canonical basis

1,

$$\alpha$$

,  $\alpha^2$ , ---,  $\alpha^{m-1}$

As an example, the Galois field of  $2^4$  elements,  $GF(2^4)$ , may be formed as the field of polynomials over GF(2) modules  $(x^4 + x + 1)$ , which is a primitive polynomial of degree 4. Let  $\alpha$  be a root of  $x^4 + x + 1$ , i.e.,

$$\alpha^4 + \alpha + 1 = 0$$

Then by the definition of the primitive polynomial, all elements of  $GF(2^4)$  except 0 are powers of  $\alpha$ . The representation of  $\alpha^i$  for  $4 \le i \le 15$  can be determined by the primitive polynomial. In this example  $\alpha$  is a root of  $x^4 + x + 1$  over GF(2). Thus

$$\alpha^4 + \alpha + 1 = 0$$

It follows that

$$\alpha^4 = -\alpha - 1$$

Since -1 = 1 in GF(2), one has

$$\alpha^4 = \alpha + 1$$

The rest of the element  $\alpha^{i}$  for  $5 \le i \le 15$  can be obtained likewise. The 15 nonzero field elements of  $GF(2^4)$  are shown below in both multiplicative and vector space forms.

Another example is the finite field  $\mathrm{GF}(2^8)$  generated by the primitive polynomial

$$x^{8} + x^{4} + x^{3} + x^{2} + 1$$

The exponents versus elements and elements versus exponents tables for this  ${\tt GF(2^8)}$  are shown in Table 1 and Table 2, respectively.

Exponents versus elements in a finite field GF(2<sup>8</sup>) generated by the primitive polynomial  $x^8+x^4+x^3+x^2+1$ . Table 1.

| महाराज्य | м   |     |     |     |     |     |     |     |     |     |     |     |     |     |     |     |     |     |     |     |     |     |     |     |     |     |     |             |      |     |     |     |            |     |     |     |     |     |     |     |     |            |     |

|----------|-----|-----|-----|-----|-----|-----|-----|-----|-----|-----|-----|-----|-----|-----|-----|-----|-----|-----|-----|-----|-----|-----|-----|-----|-----|-----|-----|-------------|------|-----|-----|-----|------------|-----|-----|-----|-----|-----|-----|-----|-----|------------|-----|

| EXPONENT | 255 |     |     |     |     |     |     |     |     |     |     |     |     |     |     |     |     |     |     |     |     |     |     |     |     |     |     |             |      |     |     |     |            |     |     |     |     |     |     |     |     |            |     |

| ध्यया    | 133 | 26  | 218 | 158 | 132 | 78  | 7.  | 164 | 73  | 114 | 61  | 203 | 138 | 126 | 215 | 246 | 227 | 75  | 86  | 55  | 165 | 65  | S.  | 141 | 28  | 224 | 60  | 162         | 121  | 239 | 43  | 69  | 18         | 144 | 777 | 243 | 203 | 22  | 176 | 233 | 27  | 216        | 142 |

| EXPONENT | 128 | 131 | 134 | 137 | 140 | 143 | 146 | 149 | 152 | 155 | 158 | 161 | 164 | 167 | 170 | 173 | 176 | 179 | 182 | 185 | 188 | 191 | 194 | 197 | 200 | 203 | 276 | 503         | 2172 | 215 | 218 | 221 | 777        | 227 | 230 | 233 | 236 | 239 | 242 | 245 | 248 | 251        | 254 |

| ELENCAT  | 707 | 97  | 103 | 79  | Z   | 77  | 7.7 | 82  | 170 | 57  | 213 | 230 | 66  | 63  | 229 | 123 | 255 | 171 | 67  | 149 | 220 | 174 | 25  | 200 | 77  | 112 | 167 | 81          | 178  | 249 | 155 | 172 | ወ          | 72  | 122 | 247 | 235 | #   | 88  | 250 | 131 | 108        | 71  |

| EXPONENT | 127 | 130 | 133 | 136 | 139 | 142 | 145 | 148 | 151 | 154 | 157 | 160 | 163 | 166 | 169 | 172 | 175 | 178 | 181 | 184 | 187 | 190 | 193 | 156 | 199 | 202 | 205 | <b>8</b> 02 | 111  | 214 | 217 | 220 | 223        | 226 | 525 | 232 | 235 | 238 | 241 | 777 | 247 | 250        | 253 |

| ELEMENT  | 102 | 23  | 184 | 169 | 33  | 21  | 168 | 77  | 85  | 146 | 228 | 115 | 191 | 145 | 252 | 179 | 241 | 219 | 150 | 196 | 110 | 87  | 130 | 100 | 7   | 56  | 221 | 166         | 68   | 242 | 195 | 86  | 138        | 36  | 61  | 245 | 25. | 139 | 77  | 125 | 207 | 24         | 173 |

| EXPONENT | 126 | 129 | 132 | 135 | 138 | 141 | 177 | 147 | 150 | 153 | 156 | 159 | 162 | 165 | 168 | 171 | 174 | 177 | 180 | 183 | 186 | 189 | 192 | 195 | 198 | 201 | 707 | 207         | 210  | 213 | 216 | 219 | 222        | 225 | 228 | 231 | 234 | 237 | 240 | 243 | 246 | 249        | 252 |

| EL ENENT | -4  | 32  | 29  | 232 | 19  | 152 | 180 | 201 | S   | 87  | 157 | 156 | 148 | 212 | 238 | 35  | \$  | 64  | 93  | 210 | 222 | 190 | 153 | 188 | 137 | 3   | 253 | 187         | 111  | 225 | 16  | 226 | <i>L</i> 9 | ጟ   | 13  | 104 | 103 | 31  | 248 | 147 | 236 | <b>2</b> . |     |

| EXPORENT | 7   | S   | 00  | 11  | 77  | 17  | 20  | 23  | 26  | 52  | 32  | 35  | 38  | 41  | 77  | 47  | 20  | 53  | 56  | 59  | 62  | 65  | 38  | 71  | 77  | 77  | 80  | 83          | 86   | 89  | 92  | 95  | 98         | 101 | 104 | 107 | 110 | 113 | 116 | 119 | 122 | 125        |     |

| ELEVENT  | 7   | 16  | 128 | 116 | 135 | 76  | 96  | 23. | (*1 | 14  | 192 | 9   | 7.7 | 106 | 119 | 159 | 140 | 20  | 160 | 105 | 111 | 95  | 194 | 96  | 202 | 30  | 240 | 211         | 214  | 254 | 163 | 113 | 175        | 17  | 136 | 52  | 189 | 129 | 124 | 199 | 118 | 151        |     |

| EXPONENT | П   | 4   | 7   | 16  | 13  | 16  | 19  | 22  | 25  | 28  | 31  | 75  | 37  | 07  | 73  | 95  | 67  | 52  | 55  | 28  | 61  | Z   | 19  | 70  | 7.3 | 92  | 79  | 82          | 85   | 88  | 91  | 76  | 16         | 100 | 103 | 106 | 109 | 112 | 115 | 118 | 121 | 124        |     |

| ELEMENT  | -   | œ)  | 3   | 58  | 205 | 38  | 45  | 117 | 143 | 77  | 96  | 39  | 37  | 53  | 181 | 193 | 70  | 10  | 80  | 186 | 185 | 161 | 97  | 47  | 101 | 15  | 120 | 231         | 107  | 127 | 223 | 182 | 217        | 134 | 88  | 76  | 208 | 206 | 62  | 237 | 59  | 197        |     |

| EXPONENT | 0   | m   | 9   | 6   | 12  | 15  | 18  | 21  | 57  | 27  | 30  | 33  | 36  | 39  | 42  | 45  | 87  | 51  | 25  | 57  | 09  | 63  | 99  | 69  | 72  | 75  | 78  | 81          | 84   | 87  | 90  | 93  | 96         | 66  | 102 | 105 | 108 | 111 | 114 | 117 | 120 | 123        |     |

Tab

| nial                    | EXPONENT | 112         | 140 | 13  | 222 | 197 | 227 | 119 | 180 | 89  | 35        | 97  | 509 | 188 | 747 | 178 | 190 | 98  | 20  | 158 | 27  | 109 | 31  | 216 | 164 | 23              | 127 | 246              | 9C . | 25.      | 177      | 62  | 88  | 156 | 81  | 22  | 117<br><u>.</u> | 6/ 6 | 553 | 1/3 | 168  | 175           |

|-------------------------|----------|-------------|-----|-----|-----|-----|-----|-----|-----|-----|-----------|-----|-----|-----|-----|-----|-----|-----|-----|-----|-----|-----|-----|-----|-----|-----------------|-----|------------------|------|----------|----------|-----|-----|-----|-----|-----|-----------------|------|-----|-----|------|---------------|

| e polynomial            | ELEMENT  | 129         | 132 | 135 | 138 | 141 | 144 | 147 | 150 | 153 | 156       | 159 | 162 | 165 | 168 | 171 | 174 | 177 | 180 | 183 | 186 | 789 | 192 | 195 | 198 | 201             | 204 | 20/              | 210  | 217      | 219      | 222 | 225 | 228 | 231 | 234 | 237             | 240  | 243 | 246 | 243  | 255           |

| primitive               | EXPONENT | 7           | 247 | 66  | 74  | 67  | 77  | 153 | 184 | 17  | 217       | 137 | 63  | 149 | 205 | 151 | 252 | 242 | 171 | 93  | 09  | 71  | 162 | 67  | 123 | 196             | 236 | 111              | 191  | 170      | 134      | 204 | 203 | 176 | 160 | 245 | 122             | 215  | 213 | 231 | 237  | 88            |

| ed by the               | ELEMENT  | 128         | 131 | 134 | 137 | 140 | 143 | 146 | 149 | 152 | 155       | 158 | 191 | 164 | 167 | 170 | 173 | 176 | 179 | 182 | 185 | 188 | 191 | 194 | 197 | 200             | 203 | 206              | 607  | 212      | 218      | 221 | 224 | 227 | 230 | 233 | 720             | 239  | 242 | 245 | 251  | 254           |

| generated               | EXPONENT | 87          | 192 | 128 | 103 | 237 | 254 | 165 | 38  | 124 | 146       | 32  | 55  | 91  | 207 | 135 | 220 | 26  | 211 | 42  | 132 | 83  | 65  | 4.5 | 183 | $\frac{118}{1}$ | 73  | 12               | 80T  | 85<br>85 | 96       | 187 | 90  | 95  | 169 | 11  | 235             | 747  | 174 | 230 | 777  | 80            |

| 1d GF(2 <sup>0</sup> )  | ELEMENT  | 127         | 130 | 133 | 136 | 139 | 142 | 145 | 148 | 151 | 154       | 157 | 160 | 163 | 166 | 169 | 172 | 175 | 178 | 181 | 184 | 187 | 190 | 193 | 196 | 199             | 202 | 205              | 20g  | 211      | 217      | 220 | 223 | 226 | 229 | 232 | 235             | 238  | 241 | 244 | 747  | 253           |

| finite field            | EXPONENT | 25          | 26  | 223 | 27  | 7.5 | 224 | 141 | 28  | 248 | 9/        | 138 | 225 | 33  | 142 | 18  | 29  | 125 | 546 | 154 | 77  | 166 | 139 | 221 | 226 | 179             | 34  | 208              | 143  | 109      | 13<br>56 | 30  | 163 | 126 | 28  | 250 | 61              | 155  | 21  | 78  | 7/7  | 707           |

| in a                    | ELEMENT  | m           | 9   | 6   | 12  | 15  | 18  | 21  | 77  | 27  | 30        | 33  | 36  | 39  | 42  | 45  | 48  | 51  | 54  | 57  | 09  | 63  | 99  | 69  | 72  | 75              | 78  | 81               | 84   | 000      | ) E      | 96  | 66  | 102 | 105 | 108 | 111             | 114  | 117 | 120 | 123  | 971           |

| s exponents $x^2 + 1$ . | EXPONENT | <b>,</b> -1 | 20  | ٣   | 238 | 199 | 100 | 52  | 129 | 105 | <b>60</b> | S   | 47  | 15  | 147 | 240 | 69  | 194 | 39  | 201 | 120 | 114 | 191 | 102 | 253 | 37              | 145 | , <del>,</del> , | 206  | 917      | 131      | 79  | 182 | 72  | 107 | 84  | 186             | 76   | 10  | 43  | 67.7 | 243           |

| versus                  | ELEMENT  | 2           | S   | œ   | 11  | 14  | 17  | 07  | 23  | 26  | 29        | 32  | 35  | 38  | 41  | 77  | 7.7 | 20  | 53  | 26  | 59  | 62  | 65  | 89  | 7.1 | 74              | 7.7 | 80               | 83   | 0 0      | 93       | 95  | 86  | 101 | 104 | 107 | 110             | 113  | 116 | 119 | 122  | 571           |

| Elements $x^8 + x^4 +$  | EXPONENT | 0           | 7   | 198 | 51  | 104 | 7   | 14  | 239 | 193 | 200       | 113 | 101 | 36  | 53  | 218 | 130 | 181 | 106 | 185 | 6   | 228 | 9   | 86  | 84  | 152             | 16  | 136              | 148  | 057      | 74T      | 70  | 99  | 195 | 110 | 40  | 133             | 202  | 159 | 121 | 212  | <del>CT</del> |

| Table 2.                | ELEMENT  | -           | 77  | 7   | 10  | 13  | 16  | 19  | 22  | 25  | 28        | 31  | 34  | 37  | 70  | 43  | 97  | 67  | 52  | 55  | 58  | 61  | 79  | 57  | 70  | 73              | 9/  | 79               | 82   | ۵<br>د د | 0 F      | 96  | 97  | 100 | 103 | 106 | 109             | 112  | 115 | 118 | 121  | †7T           |

The addition of two field elements in  $GF(2^n)$  is performed by component-wise addition in the vector representations of the two elements. For example in  $GF(2^8)$ ,  $\alpha^{26}+\alpha^{238}$  is given by

$$6 = (0,0,0,0,0,1,1,0) \leftrightarrow \alpha^{26}$$

$$+ 11 = (0,0,0,0,1,0,1,1) \leftrightarrow \alpha^{238}$$

$$13 = (0,0,0,0,1,0,1) \leftrightarrow \alpha^{104}$$

The multiplication of two field elements in  $\mathrm{GF(2}^n)$  is performed by a modulo  $(2^n-1)$  addition on the exponents of the two elements. For example in  $\mathrm{GF(2}^8)$ ,  $\alpha^{26}*\alpha^{238}$  is given by

$$6 = (0,0,0,0,0,1,1,0) \qquad \Rightarrow \quad \alpha^{26}$$

\*)  $11 = (0,0,0,0,1,0,1,1) \qquad \Rightarrow \quad \alpha^{238}$

$$58 = (0,0,1,1,1,0,1,0) \qquad \Rightarrow \quad \alpha^{(26} + 238) \text{ MOD } 255$$

$$= \alpha^{9}$$

#### SECTION III

#### REED-SOLOMON ENCODING PROCEDURES

An RS code word has  $(2^J-1)$  symbols, where each symbol has J bits. Of the  $(2^J-1)$  symbols there are  $(2^J-1-2E)$  information symbols and 2E parity-check symbols, where E is the number of symbols an RS code is able to correct. If one treats the  $(2^J-1-2E)$  information symbols as the coefficients of the polynomial

$$f(x) = x^{2E} \left( s_{2^{J}-1-2E} + s_{2^{J}-2-2E} + s_{2^{X^{J}-2-2E}} + s_{1^{X^{2^{J}-1-2E}}} \right)$$

where  $\mathbf{s}_{i}$  is the ith transmitted symbol, then the 2E parity-check symbols can be obtained as the coefficients of the remainder of

where g(x) is the generator polynomial (Ref. 9) of the code. Usually g(x) is defined as

$$g(x) = \prod_{i=1}^{2E} (x-\alpha^i) = \sum_{j=0}^{2E} g_j x^j$$

where  $\alpha$  is a primitive element of the Galois field  $GF(2^J)$ , and  $g_j$ 's are the coefficients of g(x) with  $g_{2E}=1$ . The generator polynomial defined above does not have symmetrical coefficients, i.e.,

$$g_{i} \neq g_{2E-i}$$

for  $j = 0, 1, 2, ---, 2E$ .

A block diagram of an RS encoder which generates the remainder of f(x)/g(x) is given in Fig. 1. The switches in Fig. 1 are normally in the "ON" position until the last information symbol gets into the encoder. At this

J-bit Shift Register.

11

S

moment all switches are switched to the "OFF" position and the encoder is behaving like a long shift register. The output of the encoder is then taken from the output of the last shift register. Note that in Fig. 1, 2E multipliers are needed in the encoder.

To reduce the number of multipliers needed, a special class of the generator polynomial which has symmetrical coefficients was proposed by Berlekamp (Ref. 10). This generator polynomial is defined as

$$g(x) = \prod_{i=2}^{2^{J-1}+E-1} (x-\alpha^i) = \sum_{j=0}^{2E} g_j x^j$$

where

$$g_j = g_{2E-j}$$

and  $g_o = g_{2E} = 1$ .

Note that since  $g_0 = 1$ , only E multipliers are needed (see Fig. 2). Thus using this new generator polynominal will reduce the number of multipliers required by one-half. As an example, the coefficients of all generator polynomials of the form

$$g(x) = \prod_{i=112}^{143} (x - \alpha^{ij})$$

for a 16-error-correcting RS code with 8-bit per symbol are shown in Table 3 for  $\alpha$  = 2, 128, 232, 135, 201, 90, 74, 119, respectively.

There are several schemes for interleaving the RS codes (Ref. 5). One scheme illustrated in Fig. 3 as "Interleave B" requires memory only for the parity-check symbols in the encoder is described as follows. In this scheme the input bits are grouped into J-bit symbols and transmitted in their natural order. However every I<sup>th</sup> symbol belongs to the same code word, where I is the interleaving

ORIGINAL PACE 13 OF POOR QUALITY

|     |                                    | 2=119          | 7 | 73  | 192 | 158 | 246 | 160 | 76  | 159 | 171 | Ŋ   | 240  | 129  | 124 | 188 | 242 | 173 | 80  | 173 | 242            | 188 | 124 | 129 | 240 | Ŋ   | 171 | 159 | 94  | 160 | 246 | 158 | 192 | 73  | · =        |

|-----|------------------------------------|----------------|---|-----|-----|-----|-----|-----|-----|-----|-----|-----|------|------|-----|-----|-----|-----|-----|-----|----------------|-----|-----|-----|-----|-----|-----|-----|-----|-----|-----|-----|-----|-----|------------|

|     | (x-3 <sup>1</sup> )                | 3=74           | Т | ∞   | 135 | 138 | 187 | 65  | 130 | 123 | 198 | 77  | 102  | 117  | 7.7 | 138 | 214 | 106 | 125 | 106 | 214            | 138 | 77  | 117 | 102 | 77  | 198 | 123 | 130 | 65  | 187 | 138 | 135 | ∞   | H          |

| 143 | []<br>i = 112                      | α=90           | ٦ | 169 | 247 | 73  | 171 | 80  | 53  | 59  | 129 | 106 | 103  | 18   | 7.7 | 184 | 64  | 83  | 168 | 83  | <del>7</del> 9 | 184 | 47  | 18  | 103 | 106 | 129 | 59  | 53  | 80  | 177 | 73  | 247 | 169 | H          |

|     | s for g(x) =                       | $\alpha = 201$ | 1 | 139 | 11  | 140 | 63  | 43  | 223 | 26  | 236 | 41  | 88   | 156  | 102 | 145 | 86  | 31  | 220 | 31  | 86             | 145 | 102 | 156 | 88  | 41  | 236 | 26  | 223 | 43  | 63  | 140 | 11  | 139 | <b>-</b> I |

|     | Coefficients                       | a=135          | н | 174 | 158 | 204 | 153 | 68  | 77  | 91  | 154 | 158 | 188  | 234  | 191 | 72  | 226 | 59  | 78  | 59  | 226            | 72  | 191 | 254 | 188 | 158 | 154 | 91  | 77  | 89  | 153 | 204 | 158 | 174 | <b></b>    |

|     | r Polynomial Coefficients for g(x) | y=232          | 1 | 213 | 184 | 106 | 132 | 36  | 144 | 194 | 6   | 59  | 67   | 81   | 56  | 158 | 204 | 74  | 135 | 7.4 | 204            | 158 | 56  | 81  | 29  | 59  | 6   | 194 | 144 | 36  | 132 | 106 | 184 | 213 | П          |

|     | 3. Generator                       | .=128          | н | 227 | 151 | 109 | 47  | 104 | 26  | 184 | 213 | •   | 1.53 | 1.74 | 238 | 25  | 157 | 232 | 9   | 232 | 157            | 26  | 238 | 174 | 133 | 7   | 213 | 184 | 26  | 104 | 74  | 109 | 151 | 227 | щ          |

|     | Table 3                            | α=2            | Н | 236 | 244 | 220 | 133 | 238 | 137 | 201 | 7   | 141 | 11   | 226  | 34  | 252 | 209 | 22  | 78  | 22  | 209            | 252 | 34  | 226 | 11  | 141 | 7   | 201 | 137 | 238 | 133 | 220 | 244 | 236 | 1          |

|     |                                    | DEG(x)         | 0 | Т   | 2   | ٣   | 4   | 5   | 9   | 7   | 80  | 6   | 10   | 11   | 12  | 13  | 14  | 15  | 16  | 17  | 18             | 19  | 20  | 21  | 22  | 23  | 24  | 25  | 26  | 27  | 28  | 29  | 30  | 31  | 32         |

## OFIGINAL PACE IS OF POOR QUALITY

| 2E PARITY-CHECK SYMBOLS                    | P <sub>1</sub> , P <sub>2</sub> ,                   | p <sub>1</sub> <sup>2</sup> p <sub>2</sub> <sup>2</sup> , ————— p <sub>2</sub> <sup>2</sup> |

|--------------------------------------------|-----------------------------------------------------|---------------------------------------------------------------------------------------------|

| (2 <sup>J</sup> -1-2E) INFORMATION S'MBOLS | 1, 191, 2141, ———————— , (2 <sup>J</sup> -2-2E) 191 | 2, H2, 2H2, —————, (2 <sup>J</sup> -2-2E) H2                                                |

|                                            | CODEWORD 11                                         | CODEWORD #2                                                                                 |

ORDER OF SYMBOL TRANSMISSION

1, 2, — — — , I, ₱1, — — — , 2I, 2₱1, — — — , (2<sup>J</sup>-2-2E) ₱·1 , (2<sup>J</sup>-2-2E) ₱·2,

$----, (2^{J_{-1}-2E)}L_{-p_1}^{-1}, p_1^{-2}, ---, p_1^{-1}, p_2^{-1}, ---, p_2^{-1}, ---,$

P<sub>2E</sub>', P<sub>2E</sub>', ———, P<sub>2I</sub>

Code Array Structure and Order of Symbol Transmission For Type B Interleaving, Where Interleaving Level = I  $\,$ Figure 3.

depth used. Thus I code words make up such an interleaved code block. After the information symbols are transmitted, the parity-check symbols of each interleaved code word are then transmitted.

If interleaving is used, then the encoder logic structure is the same as shown in Fig. 1, except now each J-bit shift register is replaced by an I x J-bit shift register. As an example, a block diagram of a (255,223) RS encoder with interleaving level I and generator polynomial

$$g(x) = \prod_{i=1}^{143} (x-\alpha^{i})$$

where  $\alpha = 2$  in GF(2<sup>8</sup>), which is generated by the primitive polynomial

$$x^8 + x^4 + x^3 + x^2 + 1$$

,

is shown in Figure 4. Note that a generator polynomial with symmetrical coefficients is used here to save multipliers.

# ORIGINAL PAGE IS OF POOR QUALITY

Figure 4. A Block Diagram of a (255,223) RS Encoder With Interleaving Level I and

$$g(x) = \prod_{i=112}^{143} (x-a^i)$$

#### SECTION IV

#### SYMBOL-SLICE VLSI RS ENCODER ARCHITECTURE

A finite field multiplication is a quite complicated operation. There are basically three techniques for implementing a finite field multiplication.

The first technique is to use log and antilog tables stored in read-only memories (ROM's) (Ref. 4). The second technique is to use a linear feedback shift register type of approach (Ref. 10). The third technique is to use the property of the trace in a finite field to form a smaller ROM look-up table (Ref. 11). Due to the advent of LSI ROM technology, techniques 1 and 3 are usually used in an RS encoder design optimized for discrete IC's. As an example a 400 KHZ (255,233) RS encoder using the Berlekamp's approach (Ref. 11) requires only around 40 CMOS IC's.

When one is interested in further drastic reduction of the power and size of an RS encoder for high speed applications, one has to consider VLSI implementations. An RS encoder design optimized for discrete IC's usually does not have a modular structure. Hence when one uses such an architecture for VLSI layout, one has the following problems:

- (1) The design is too big to be put on one chip.

- (2) If a multichip approach is used, then one needs several chip designs, where each chip has an impractical number of input/ output pins.

- (3) The design is not modular. Therefore the design is not easy to adapt to other RS code parameters.

Hence there is a need to find a VLSI logic structure which can alleviate the above problems.

The repetitive architecture of the RS encoders shown in Figs. 1, 2, and 4, suggested that a symbol-slice type of VLSI chips, each one consisting of a fixed portion of the encoder, may be cascaded to form a complete RS encoder. Also to reduce the VLSI chip size, RS encoders using generator polynomials with symmetrical coefficients are preferred. Hence we will put emphasis on this type of VLSI RS encoder.

As an example, we will design a VLSI encoder chip for a 255-symbol, 8-bit per symbol, 16-error-correcting, RS code with an interleaving level of 5. The primitive polynomial used is

$$x^{8} + x^{4} + x^{3} + x^{2} + 1$$

The generator polynomial for this RS code is

$$g(x) = \prod_{i=112}^{143} (x-\alpha^{i})$$

where  $\alpha = 2$ . The coefficients of this g(x) are given in the first column of Table 3. The encoder logic structure for the above RS code parameter is identical to the one shown in Fig. 4, except now I = 5. There are several ways of partitioning the RS encoder into four sections. One way which requires a minimum of input/output pins is to include four rows of logic shown in Fig. 4 into one section. Each section is then realized by a universal VLSI RS encoder chip. Another way to partition the RS encoder shown in Fig. 4 into four sections is to include 8 rows of logic in each column into one section. Each section is then realized by

a universal VLSI RS encoder chip. These VLSI RS encoder configurations are described as follows.

#### 4.1 VLS1 RS ENCODER USING THE ROW PARTITIONING TECHNIQUE

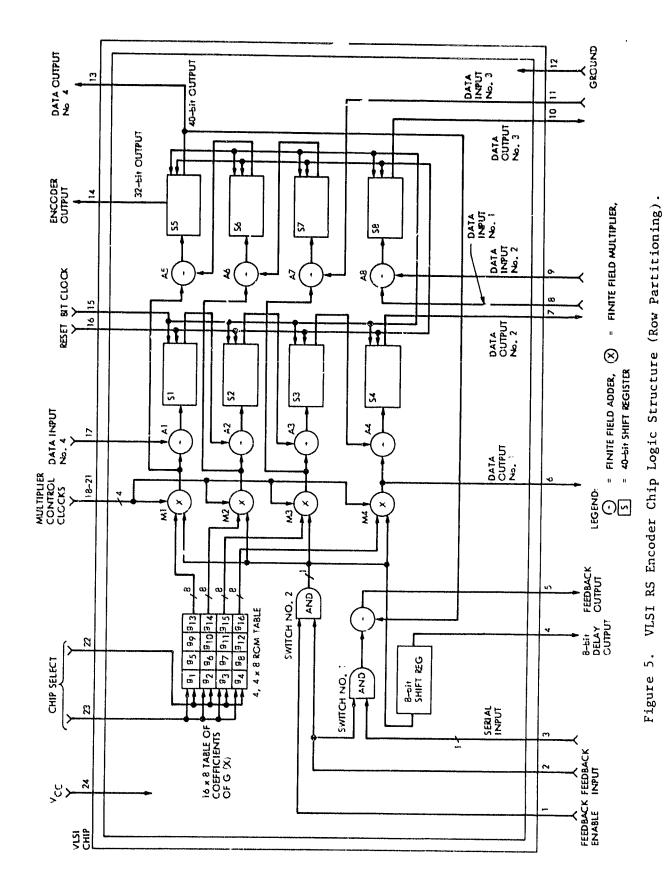

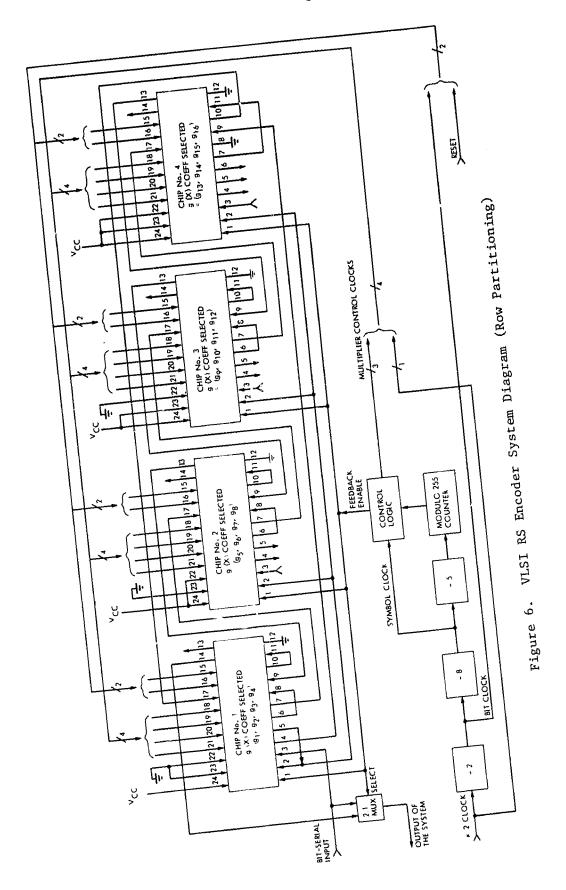

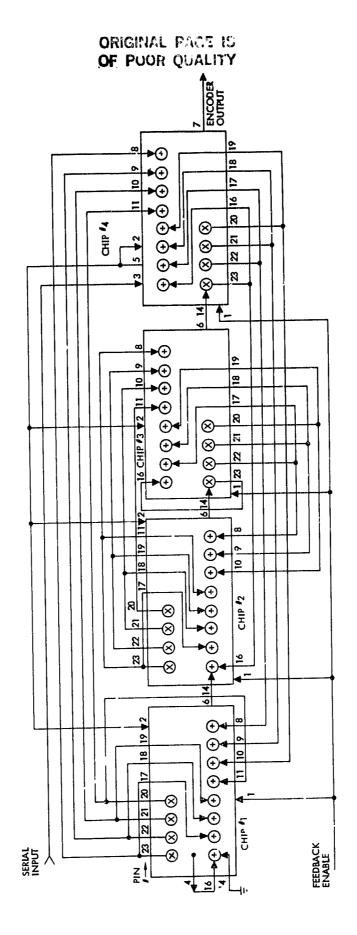

The logic structure of the universal VLS1 RS encoder chip using the row partitioning technique is shown in Fig. 5. The entire VLSI encoder system, which consists of four identical VLS1 RS encoder chips cascaded and properly interconnected together is shown in Fig. 6. Each VLS1 RS encoder chip has 24 pins. A detailed description of the VLS1 RS encoder chip and the entire VLS1 RS encoder system is describe as follows:

#### 4.1.1 Generator Polynomial Coefficients Table

Since a generator polynomial g(x) with symmetrical coefficients is used, the coefficients of  $x^0$  is always 1. Hence there is no need for a multiplier to operate on this coefficient (see Fig. 4). Consequently if the new generator polynomial is used, then one only needs E/N multipliers on each VLS1 chip, where E is the error correcting capability of the code and N is the total number of chips required in a VLS1 encoder system. In the design example, E=16 and N=4. Hence 4 multipliers are used on each VLS1 RS encoder chip. To make the VLS1 chip universal, all distinct coefficients except 1 of the generator polynomial are stored in a read-only memory on the chip. In general, an ExJ-bit table is needed. In the design example E=16, J=8. Hence a  $16 \times 8$ -bit table is selected. The outputs of an ExJ-bit table is ted into N, E/N-to-one multiplexors. The outputs of the multiplexors are selected by  $\log_2 N$  input pins called the "chip select" or "G select" pins. These outputs are then fed into the inputs of the E/N multipliers. In the design example two "G select" pins (pins 22 and 23) and four, four-to-one multiplexors are used. The  $16 \times 8$  table and the multiplexors can easily be

## ORIGINAL PAGE IS OF POOR QUALITY

4-4

# ORIGINAL PAGE IS OF POOR QUALITY

implemented by four,  $4 \times 8$  ROM, with G select signals as the address control lines of each ROM. The coefficients of g(x) selected on each chip are shown in Fig. 6.

#### 4.1.2 Finite Field Multiplier

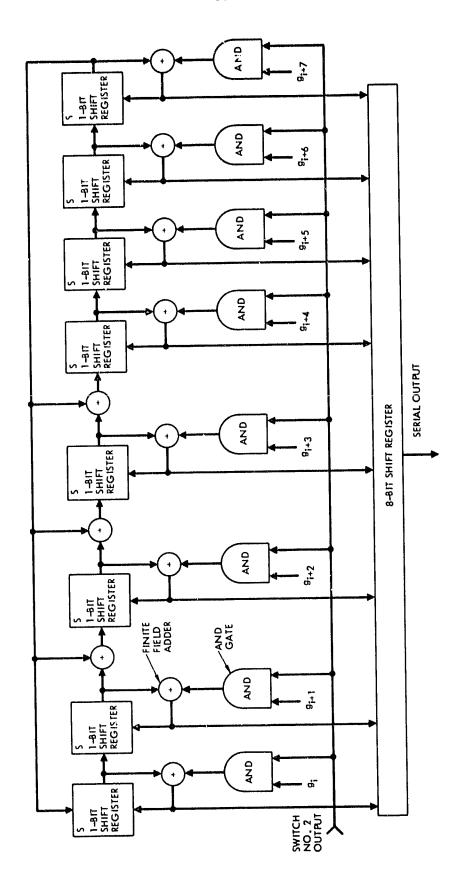

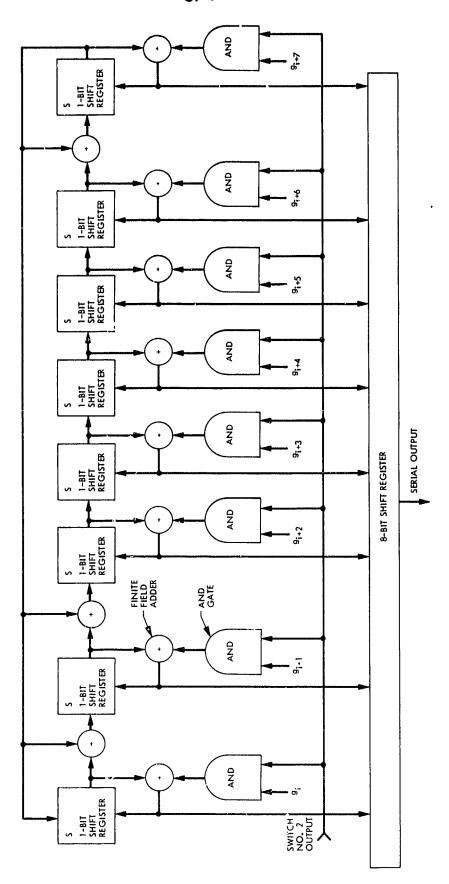

Next we will discuss the architecture of the finite field multiplier. To connect the multiplier properly between chips and at the same time minimize the number of input/output pins used, a linear feedback shift register type of multiplier (Ref. 9) rather than a ROM table look up type of multiplier (Ref. 4) is adopted. The multiplier used is of a serial-parallel type. The logic structure of the multiplier is shown in Fig. 7. The J-bit generator polynomial coefficient is read out from the ExJ-bit ROM table and fed into the multiplier J-bit in parallel whereas the other input, generated by the feedback input (pin 2) "ANDed" with the feedback enable (pin 1), is fed into the multiplier bit-by-bit in serial.

The output of the multiplier is loaded into an 8-bit shift register in parallel at the end of every 8th bit clock (1 symbol clock time). The parallel data is serialized by this shift register. The most significant bit (MSB) output of this shift register is added with the MSB of the 40-bit shift register, which is either on the same chip or on a different chip, and the resulting data is shifted into the least significant bit (LSB) of the next 40-bit shift register. The adder is implemented by a two-input EXCLUSIVE-OR gate (there are eight EXCLUSIVE-OR gates on each chip). Each adder takes an input from a multiplier output which is either on the same chip or on a different chip, depending on the coefficients of the generator polynomial.

#### 4.1.3 Input and Feedback Control Switches

The switch #1 shown in Fig. 4 is implemented by an AND gate on the chip with the bit-serial data input (pin 3) and the feedback enable signal as the

# ORIGINAL PAGE IS OF POOR QUALITY

Logic Structure of a Serial-Parallel Finite Field Multiplier Which Performs  $\alpha^i+\alpha^j$  modulo  $\alpha^a+\alpha^4+\alpha^3+\alpha^2+1$ Figure 7.

two inputs. The feedback enable signal is provided by an external modulo 255 counter which is driven by a clock equal to the bit clock divided by 40 (see Fig. 6). This signal is true when the counter is counting from 1 to 223; otherwise it is talse. The output of switch #1 is added with the MSB of the 40-bit shift register S5 output on the same chip to generate the feedback output signal (pin 5). This signal is redundant in all but the first chip (see Fig. 6).

The switch #2 shown in Fig. 4 is implemented by an AND gate on the chip with the feedback enable and feedback input signals as the two inputs. The teedback input signals on all chips (pin 2) are connected to the feedback output signal (pin 5) on the first VLSI chip. The output of switch #2 is fed into all multipliers on the chip bit-by-bit in serial.

#### 4.1.4 Input/Output Data Connections

There are eight input/output lines on each chip. Of these eight lines, four lines (pins 8, 9, 11, 17) are input lines and the remaining are output lines (pins 6, 7, 10, 13). Pin 8 is normally connected to pin 6 on the same chip except for the last chip, where pin 8 is grounded. Pins 7 and 9 are normally connected to pins 17 and 13, respectively on the next chip except for the last chip, where pin 7 is connected to pin 11 on the same chip and pin 9 is connected to pin 4 on the first chip. Thus one has a railroad type of data connections between chips. The reason for connecting pin 4 on the first chip to pin 9 on the last chip is a consequence of an inherent 8-bit multiplier delay. To replace the multiplier on the x position by the switch #1 output, one needs to delay this output also by 8 bits to line up the bits. For other chips besides the first chip, the 8-bit register outputs are not used.

The encoder output is taken 8 bits earlier from the MSB of the last 40-bit shift register on the first chip. This is because when the last bit of the last symbol in the information part of the code is shifted into the encoder, the contents of each multiplier are loaded into the 8-bit output shift registers waiting to be added with the MSB of the 40-bit shift registers. These 8-bit symbols in the multiplier output registers actually belong to the fifth code word in the interleaved code array. However the parity-check symbol of the first code word is already being computed and now sitting 8 bits from the MSBs of each 40-bit shift registers. Hence the 32-bit output (pin 14) of the Past 40-bit shift register on the last chip is the output of the VLSI RS encoder system. This output is taken when the external modulo 255 counter is counting from 224 to 255. Since at these times switches #1 and #2 are turned off, the entire VLSI encoder system is behaving like an lx2ExJ-bit (e.g., 5 x 32 x 8-bit in the design example) shift register. Thus the 5 x 32, 8-bit parity-check symbols are read out from the VLSI RS encoder bit-by-bit in serial and appended to the 5 x 223, 8-bit information symbols.

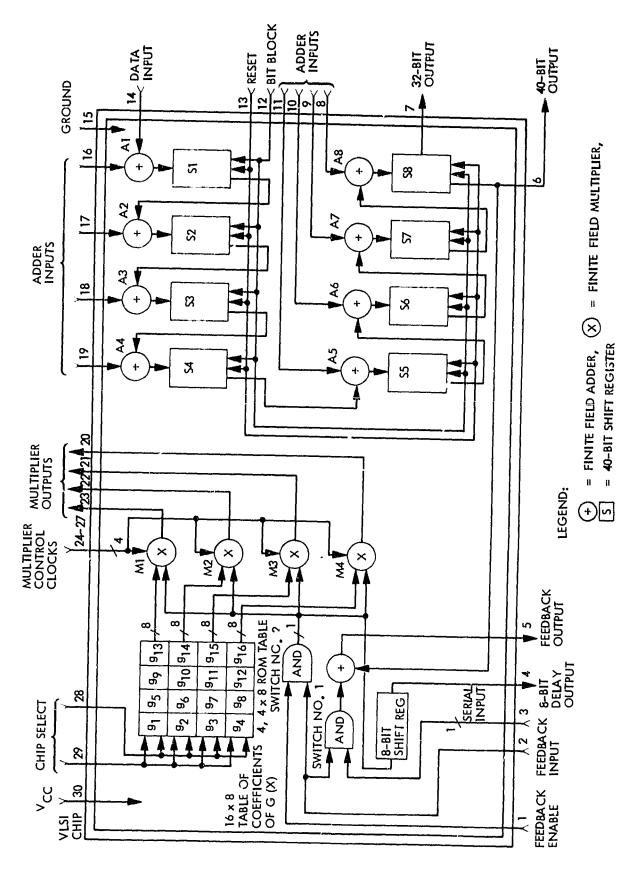

#### 4.2 VLSI RS ENCODER USING THE COLUMN PARTITIONING TECHNIQUE

The logic structure of the universal VLSI RS encoder chip using the column partitioning technique is shown in Fig. 8. Note that this chip is very similar to the one shown in Fig. 5 except now one has to provide output pins to all multipliers and input pins to all adders on the chip. Hence this chip uses 6 more input/output pins than the one shown in Fig. 5. The entire VLSI RS encoder system using this logic structure is similar to the one shown in Fig. 6 except now the interchip connections between adders and multipliers are of the pyramid type shown in Fig. 9.

# ORIGINAL PAGE IS OF POOR QUALITY

VLSI RS Encoder Chip Logic Structure (Column Partitioning). Figure 8.

Figure 9. Inter-Chip Connection Diagram (Column Partitioning).

The 40-bit shift registers in the above two versions of the VLSI RS encoder chips can be replaced by random access memories (RAMs). In this case, a write-after-read operation should be performed during each bit time from the same location just read out from the RAM to simulate the shift register operation. Consequently, this version will not operate as fast as the shift register version. The first advantage of using the RAM approach is that interleaving level control can easily be incorporated into the RAM address control logic. Of course, input pins must be provided to select the interleaving level. Hence a more flexible VLSI RS encoder chip can be obtained using the RAM approach.

The second advantage of using the RAM approach is that a RAM cell usually occupies a smaller chip area than that of a static shift register. Hence a smaller VLSI RS encoder chip size can be obtained using the RAM approach. It is estimated that it is impossible to put the entire shift register version of the VLSI RS encoder chip design on a 235x235 mils CMOS/bulk VLSI chip using a 7 µm standard cell approach on all logic. However, if one uses custom RAM and ROM cells design to implement the 40-bit static shift registers and the 16x8 table and 7 µm standard cell design for the rest of the logic, then it is possible to have a one-chip design. Of course, the entire RS encoder chip design can easily be put on a smaller chip if a VLSI technology (say 3 µm standard cell approach) is used.

#### SECTION V

#### PERFORMANCE OF THE VLSI RS

#### ENCODER SYSTEM

For design verification, both the shift register version and the RAM version of the VLSI RS encoder chip and VLSI RS encoder system are implemented using discrete CMOS IC's and are now operational. The throughputs of these two versions are 800K bits/sec for the shift register version and 200K bits/sec for the RAM version. These throughputs are expected to go much higher if the actual VLSI encoder chips are used.

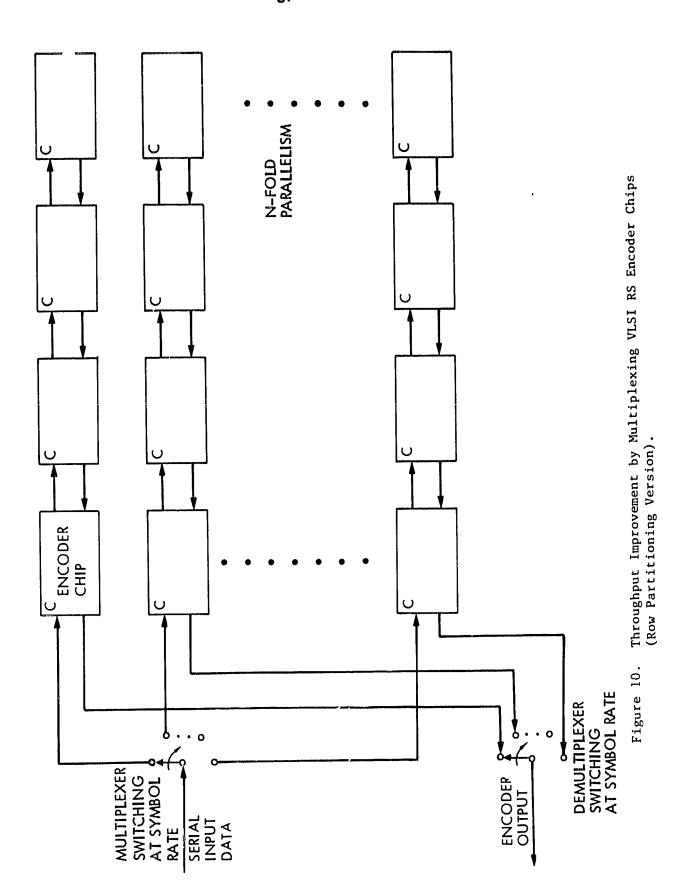

One technique to improve the VLSI RS encoding speed is to multiplex the RS encoder chips. One type of multiplexing is to set the RS encoder chip interleaving level selection in the RAM approach to 1 (no interleaving) such that for a N-level of interleaving, a N-fold parallelism can be achieved. This scheme is illustrated in Fig. 10. Note that each row of the RS encoder chips in Fig. 10 are used to encode a RS code word corresponding to the one shown in each row of the code array structure in Fig. 3.

Another type of multiplexing is to use the relationship that if

$$f(x) = f_1(x) + f_2(x) + --- + f_N(x)$$

then

$$\frac{f(x)}{g(x)} = \frac{f_1(x)}{g(x)} + \frac{f_2(x)}{g(x)} + --- + \frac{f_N(x)}{g(x)}$$

can be realized by implementing  $f_i(x)/g(x)$  for i=1, 2, ---, N in parallel and then summing the results from these parallel operations. Thus if one treats each

$f_i(x)$  as a polynomial, whose coefficients are selected from every  $N^{th}$  incoming symbols starting from the  $i^{th}$  symbol, where i=1, 2, ---, N, then one can select the encoder chip interleaving level to 1 and use the logic structure similar to the one shown in Fig. 10 to realize the  $f_i(x)/g(x)$  operation. The output of each row of encoder chips in this case needs to be properly delayed and summed to generate the encoder output f(x)/g(x).

Another technique to improve the VLSI RS encoding speed is to process the J-bit incoming symbols in parallel. Parallel adders and multipliers are needed in this configuration. A throughput improvement of J times can be achieved using this approach. The disadvantages of this technique are:

- (1) A lot of input/output pine are needed for the parallel data paths.

- (2) A larger chip size is required to implement the VLSI RS encoder.

#### SECTION VI

#### CONCLUSIONS

We have just shown the logic structure of a symbolic-slice VLSI RS encoder chip and the VLSI RS encoder system built by these chips. A design example has been given for a (255,223) VLSI RS encoder chip and VLSI RS encoder system. It has been shown that an RS encoder consisting of four identical CMOS VLSI RS encoder chips connected together may replace around 40 CMOS IC's required by an encoder design optimized for discrete IC's. Besides the size advantage, the VLSI kS encoder also has the potential advantages of requiring less power and having a higher reliability. Finally, it is shown that such chips can easily be multiplexed to improve the encoding speed. The symbol-sliced logic structure presented in the report could also be applied to design VLSI RS decoders [12]. A separate report on this subject will be provided.

#### REFERENCES

- [1] Reed, I.S., and Solomon, G., "Polynomial Codes Over Certain Finite Fields,"

J. Soc. Indust. Appl. Math., 8, pp. 300-304.

- [2] Forney, G.D., Concatenated Codes, The MIT Press, Cambridge, Mass., 1966.

- [3] Odenwalder, J.P., "Optimum Decoding of Convolutional Codes," Ph.D. dissertation, Syst. Sci. Dept., Univ. of Calif., Los Angeles, 1970.

- [4] Odenwalder, J.P., et al. "Hybrid Coding System Study," submitted to NASA Ames Research Center by Linkabit Co., San Diego, Calif., Final Report, Contract No. NAS-2-6722, Sept. 1972.

- [5] Rice, R.F., "Channel Coding and Data Compression System Considerations for Efficient Communication of Planetary Imaging Data," <u>Technical Memorandum</u> 33-695, Jet Propulsion Laboratory, Pasadena, CA., June 1974.

- [6] Rice, R.F., "Potential End-to-End Imaging Information Rate Advantages of Various Alternative Communication Systems," JPL Publication 78-52, June 15, 1978.

- [7] Hauptschein, A., "Practical, High Performance Concatenated Coded Spread Spectrum Channel for JTIDS," NTC '77, pp. 35:4-1 to 4-8.

- [8] Liu, K.Y., and Lee, J., "An Experimental Study of the Concatenated Reed-Solomon/Viterbi Channel Coding System Performance and its Impact on Space Communications," JPL Pub. 81-58, Pasadena, CA, Aug. 15, 1981; also in Proc. Nat. Telecommun. Conf., 1981.

- [9] Liu, K.Y., and Woo, K.T., "The Effects of Receiver Tracking Phase Error on the Performance of the Concatenated Reed-Solomon, Viterbi Channel Coding System," in Proc. Nat. Telecommun. Conf., 1980, pp. 51.5.1-51.5.5; also JPL Pub. 81-62, Pasadena, CA, September 1, 1981.

- [10] Peterson, W.W., and Weldon, E.J., Jr., Error Correcting Codes, The MIT Press, 1972.

- [11] Berlekamp, E.R., "Better Reed-Solomon Encoders," presented at Calif. Inst. of Tech. EE Seminar, Pasadena, CA., Dec. 12, 1979.

- [12] Liu, K.Y., "Architectures for VLSI Design of Reed-Solomon Decoders," presented at IEEE 1st Int. Workshop on VLSI in Commun., Sauta Barbara, CA, Sept. 1-4, 1981.

### APPENDIX

VLS1 REED-SOLOMON ENCODER FOR THE PROPOSED NASA/ESA

TELEMETRY CHANNEL CODING STANDARD

After the completion of the VLSI RS encoder project, the following set of RS code parameters have been proposed in the NASA/ESA telemetry channel coding standard (Ref. Al):

(1) primitive polynomial

$$x^8 + x^7 + x^2 + x + 1$$

.

(2) generator polynomial

$$g(x) = \prod_{i=1}^{143} \left[ x - (x^{11})^i \right]$$

where  $\alpha$  satisfies the equation

$$x^8 + x^7 + x^2 + x + 1 = 0.$$

- (3) Number of bits per symbol (J) = 8.

- (4) Number of symbols per code word (N) = 255.

- (5) Number of correctable symbol errors (E) = 16.

- (6) Interleaving depth (I) = 5.

Note that the foregoing RS code parameters are those used in the design example in Section IV with two exceptions. These are the primitive polynomial (i.e., the field generator polynomial over GF(2) and the code generator polynomial. These polynomials were selected by Berlekamp in an architecture which minimizes the discrete ICs. Reference A2 provides a detailed description of such an architecture. To adapt to this new set of PS code parameters, one

needs to use a new field element table as well as a new table of generator polynomial coefficients. These are given in Tables Al and A2 respectively.

Thus, to design a VLSI RS encoder for the new code parameters, one only needs to replace the generator polynomial coefficients ROM table shown in Figure 5 by the coefficients given in Table A2 under the heading  $\alpha^{11}$ . Also one needs to replace the finite field multiplier shown in Figure 7 by the multiplier shown in Figure A1.

ORIGINAL PAGE IS OF POOR QUALITY

a finite field  $\mathrm{GF(2}^8$ ) generated by the primitive polynomial EXPONENT ELEMENT EXPONENT EXPONENT Elements versus exponents in ELEMENT EXPONENT × + **ELEMENT** × + EXPONENT A1. Table ELEMENT

# ORIGINAL PAGE IS OF POOR QUALITY.

135 135 135 135 135 135 137 137 137 137 137 138 139 139 139 139 139 Generator Polynomial Coefficients for Table A2.

## ORIGINAL PAGE IS OF POOR QUALITY

Logic structure of a serial-parallel finite field multiplier which performs  $i^{-1} * x^{-1} \mod \log x + x^{-1} + x^{-2} + x + 1$ . ı' modulo Figure Al.

### REFERENCES

- [A1] "Guidelines for Data Communications Standards: Space Telemetry Channel Coding (Issue-3)," prepared by the NASA/ESA Working Group for space data system standardization (NEWG), Jan. 1982.

- [A2] Perlman, M. and Lee, J., "Reed-Solomon Encoders Conventional Versus Berlekamp's Architecture," JPL IOM 3610-81-119 (internal document), July 10, 1981 (also to appear as JPL publication).