#### MODULAR DESIGN OF HIGH-THROUGHPUT, LOW-LATENCY SORTING UNITS

by

Amin Farmahini-Farahani

A dissertation submitted in partial fulfillment of the requirements for the degree of

Master of Science

(Electrical and Computer Engineering)

at the

UNIVERSITY OF WISCONSIN-MADISON

To my mother and father

I have been lucky to have the possibility of working with two advisors. My advisors are Professor Michael Schulte and Professor Katherine Compton, who have always been most generous with their time and encouragement. I wish to express my greatest thanks to them to give me the opportunity of learning from two different perspectives.

I thank Professor Wesley Smith and Engineer Thomas Gorski for giving me a chance to work on intriguing projects for the Large Hadron Collider and letting me have the privilege of living in the high-energy physics world. I would like to extend my gratitude to Robert Fobes for technical, cultural, and amusing things he taught me.

I also thank my fellow graduate students at the Madison Embedded Systems and Architecture (MESA) and Predictive High-Performance Architecture Research Mavens (PHARM) labs for creating and sharing an excellent group atmosphere. I have made many friends in the past four years. Jake Adriaens, Paula Aguilera, Ben Buchli, Daniel Chang, Henry Duwe, Philip Garcia, Syed Zohaib Gilani, Tony Gregerson, Mitch Hayenga, Jung-Seob Lee, Steve Naumov, Andrew Nere, David Palframan, Kyle Rupnow, Charles Tsen, and Hsiang-Kuo Tang are a few, but there are more than I can name.

I thank my fellow Iranian friends for sharing this experience with me, particularly Hamid Reza Ghasemi, Peiman Hematti, Shayda Malekpour, Shirin Malekpour, Shirzad Malekpour, Somayeh Sardashti, and Arsham Shahlari.

Finally, I would like to express my deep gratitude to my mother, father, and brother for supporting me. Their encouragement and love were the great power for me to overcome all troubles I faced.

#### CONTENTS

| Co       | ontent  | ts iii                                                                           |    |

|----------|---------|----------------------------------------------------------------------------------|----|

| Li       | st of   | Tables v                                                                         |    |

| Li       | st of I | Figures vii                                                                      |    |

| Αl       | ostrac  | et ix                                                                            |    |

| 1        | Intr    | oduction 1                                                                       |    |

| <b>2</b> | Para    | allel Sorting Networks 5                                                         |    |

|          | 2.1     | Bitonic Sorting Networks 6                                                       |    |

|          | 2.2     | Odd-even Merge Sorting Networks 9                                                |    |

|          | 2.3     | Designing Large Sorting Networks 12                                              |    |

| 3        | Proj    | posed Partial Sorting and Max-set-selection Units 14                             |    |

|          | 3.1     | 4-Output Max-set-selection and Partial Sorting Units 15                          |    |

|          |         | 3.1.1 8-to-4 Max-set-selection Units                                             | 15 |

|          |         | 3.1.2 BM-8-to-4 and 8-to-4 Partial Sorting Units                                 | 17 |

|          |         | $3.1.3$ $2^{n}$ -to-4 Max-set-selection and Partial Sorting Units .              | 20 |

|          | 3.2     | 2 <sup>n</sup> -to-2 <sup>m</sup> Max-set-selection and Partial Sorting Units 28 |    |

|          |         | 3.2.1 Modular Max-set-seletion Units                                             | 28 |

|          |         | 3.2.2 Modular Partial Sorting Units                                              | 29 |

|          | 3.3     | Other Extensions 30                                                              |    |

|          |         | 3.3.1 Other Input Quantities                                                     | 30 |

|          |         | 3.3.2 Other Output Quantities                                                    | 30 |

|          | 3.4     | Analysis 31                                                                      |    |

| 4        | Resi    | ılts 35                                                                          |    |

|          | 4.1     | ASIC Implementation 35                                                           |    |

|    | 4.2                                  | FPGA Implementation 39                                    |  |  |  |

|----|--------------------------------------|-----------------------------------------------------------|--|--|--|

|    | 4.3                                  | Comparison with Other Approaches 39                       |  |  |  |

|    | 4.4                                  | Customized Units Used in the CMS L1 Trigger 41            |  |  |  |

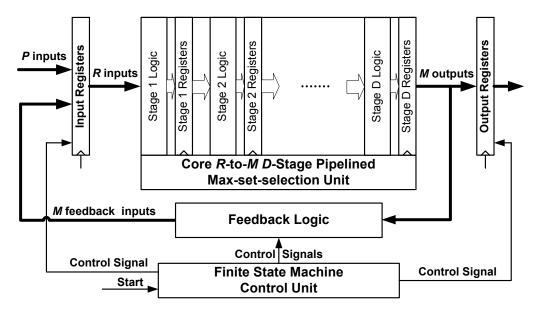

| 5  | Iterative Max-set-selection Units 45 |                                                           |  |  |  |

|    | 5.1                                  | Discussion 47                                             |  |  |  |

|    |                                      | 5.1.1 Comparison with Parallel Max-set-selection Units 49 |  |  |  |

|    |                                      | 5.1.2 Iterative Partial Sorting Units 49                  |  |  |  |

|    | 5.2                                  | Results 50                                                |  |  |  |

| 6  | Rela                                 | ted Research 52                                           |  |  |  |

|    | 6.1                                  | Sorting Networks 53                                       |  |  |  |

|    | 6.2                                  | Partial Sorting and Max-set-selection Units 54            |  |  |  |

| 7  | Con                                  | clusions 57                                               |  |  |  |

| Re | eferen                               | ces 59                                                    |  |  |  |

#### LIST OF TABLES

| 2.1 | The required number of CAE blocks and CAE stages for 2 <sup>n</sup> -input bitonic and odd-even merge sorting units | 12    |

|-----|---------------------------------------------------------------------------------------------------------------------|-------|

|     |                                                                                                                     |       |

| 3.1 | Sub-units used in $2^n$ -to-4 max-set-selection and $2^n$ -to- $2^n$ sorting                                        |       |

|     | units (10-bit unsigned data width)                                                                                  | 25    |

| 3.2 | Structure and number of CAE stages and CAE blocks for 2 <sup>n</sup> -to-4                                          |       |

|     | and $2^n$ -to-8 bitonic and odd-even merge max-set-selection units                                                  |       |

|     | made up of smaller merging units. The numbers in parentheses                                                        |       |

|     | under "Structure" show the required number of each unit                                                             | 26    |

| 3.3 | The structure, the number of CAE stages, and resource require-                                                      |       |

|     | ments for 256-to-4 max-set-selection units made up of smaller                                                       |       |

|     | max-set-selection units. The numbers in parentheses show the                                                        |       |

|     | required number of each max-set-selection unit                                                                      | 27    |

| 4.1 | Performance and resource requirements of 2 <sup>n</sup> -to-4 bitonic and                                           |       |

| 1.1 | odd-even merge max-set-selection units with 10-bit unsigned                                                         |       |

|     | CAE blocks using a TSMC 65-nm standard-cell library                                                                 | 36    |

| 4.2 | Performance and resource requirements of $2^n$ -to-8 bitonic and                                                    | 50    |

| 4.2 | odd-even merge max-set-selection units with 10-bit unsigned                                                         |       |

|     |                                                                                                                     | 27    |

| 4.0 | CAE blocks using a TSMC 65-nm standard-cell library                                                                 | 37    |

| 4.3 | Performance and resource requirements of 2 <sup>n</sup> -to-4 bitonic max-                                          | . 40T |

|     | set-selection units with 10-bit unsigned CAE blocks on an XC5VTX2                                                   |       |

|     | 2FF1759 FPGA                                                                                                        | 40    |

| 4.4 | Performance and resource requirements of customized 2 <sup>n</sup> -to-4                                            |       |

|     | max-set-selection units with 10-bit unsigned energy vectors on                                                      |       |

|     | an XC5VTX240T-2FF1759 FPGA. Each of the $2^n$ inputs has an                                                         |       |

|     | associated n-bit position vector (index)                                                                            | 44    |

| 5.1 | Performance and resource requirements of iterative max-set-                                                                         |    |

|-----|-------------------------------------------------------------------------------------------------------------------------------------|----|

|     | selection units used to find the four largest data values from                                                                      |    |

|     | N = 256 data inputs with 10-bit unsigned CAE blocks using a                                                                         |    |

|     | TSMC 65-nm standard-cell library                                                                                                    | 51 |

| 6.1 | Complexity of sorting algorithms ( $N$ : Total number of inputs, $M$ : Number of outputs, $P$ : Number of new elements per cycle) . | 56 |

#### LIST OF FIGURES

| 2.1 | The high-level implementation (left) and schematic symbol (right)      |    |

|-----|------------------------------------------------------------------------|----|

|     | of building blocks for sorting networks                                | 6  |

| 2.2 | An increasing 8-input bitonic merging unit ( $\oplus BM-8$ ) that is   |    |

|     | composed of four parallel CAE blocks followed by two parallel          |    |

|     | BM-4 units. The bitonic input sequence $\{2, 3, 6, 7, 5, 4, 1, 0\}$ is |    |

|     | the concatenation of the increasing sequence $\{2, 3, 6, 7\}$ and the  |    |

|     | decreasing sequence $\{5, 4, 1, 0\}$                                   | 7  |

| 2.3 | The CAE network for an 8-input bitonic sorting unit with six           |    |

|     | CAE stages and 24 CAE blocks, made up of increasing $(\oplus)$         |    |

|     | and decreasing $(\ominus)$ bitonic merging units. Arrows point in the  |    |

|     | direction of increasing values                                         | 8  |

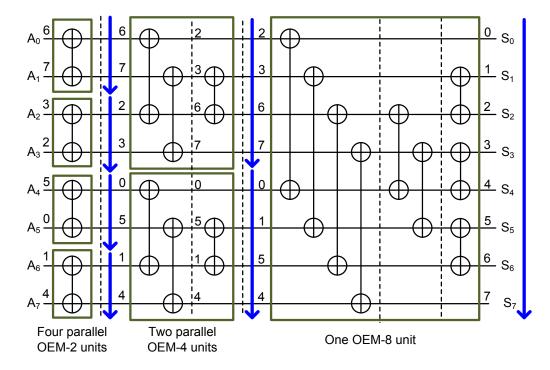

| 2.4 | An 8-input odd-even merge unit (OEM-8) that is composed of             |    |

|     | two OEM-4 units and a level of three parallel CAE blocks               | 10 |

| 2.5 | The CAE network for an 8-input odd-even merge sorting unit             |    |

|     | with six CAE stages and 19 CAE blocks                                  | 11 |

| 3.1 | The CAE network for an 8-to-4 bitonic max-set-selection unit           |    |

|     | with four CAE stages and 16 CAE blocks                                 | 16 |

| 3.2 | The CAE network for an 8-to-4 odd-even merge max-set-selection         |    |

|     | unit with four CAE stages and 14 CAE blocks                            | 17 |

| 3.3 | The CAE network for an 8-to-4 bitonic partial sorting unit with        |    |

|     | six CAE stages and 20 CAE blocks                                       | 18 |

| 3.4 | The CAE network for an 8-to-4 odd-even merge partial sorting           |    |

|     | unit with six CAE stages and 18 CAE blocks                             | 19 |

| 3.5 | A 16-to-4 bitonic max-set-selection unit                               | 20 |

| 3.6 | A 32-to-4 bitonic max-set-selection unit                               | 21 |

| 3.7 | A 32-to-32 bitonic sorting unit                                        | 21 |

| 3.8 | A 32-to-4 odd-even merge may-set-selection unit                        | 22 |

| 3.9  | A 32-to-4 bitonic partial sorting unit                                                 | 22  |

|------|----------------------------------------------------------------------------------------|-----|

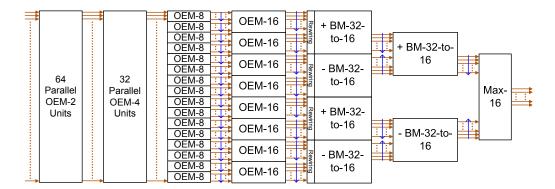

| 3.10 | A 128-to-16 odd-even merge max-set-selection unit                                      | 28  |

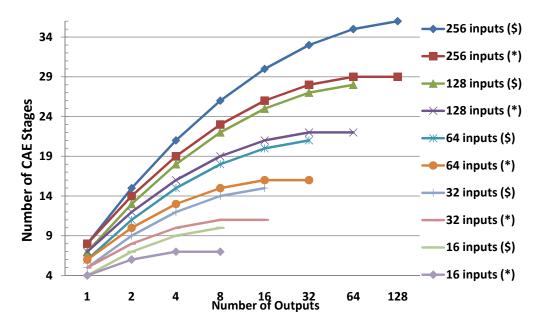

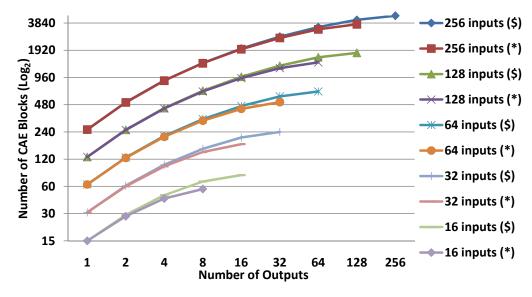

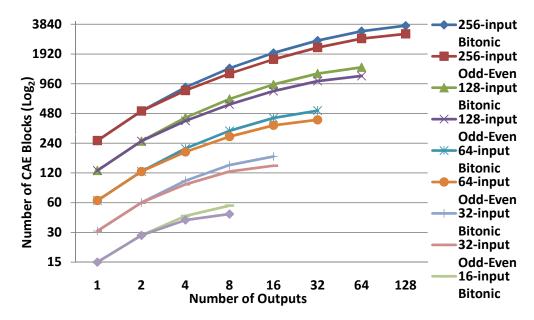

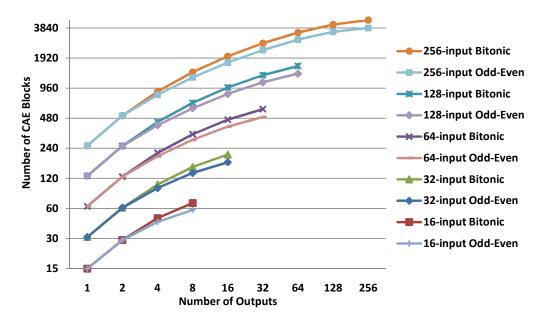

| 3.11 | The number of CAE stages for $2^n$ -to- $2^m$ partial sorting (\$) and                 |     |

|      | max-set-selection (*) units                                                            | 31  |

| 3.12 | The number of CAE blocks for 2 <sup>n</sup> -to-2 <sup>m</sup> bitonic partial sorting |     |

|      | (\\$) and max-set-selection (*) units                                                  | 32  |

| 3.13 | The number of CAE blocks for $2^n$ -to- $2^m$ bitonic and odd-even                     |     |

|      | merge max-set-selection units                                                          | 33  |

| 3.14 | The number of CAE blocks for $2^n$ -to- $2^m$ bitonic and odd-even                     |     |

|      | merge partial sorting units                                                            | 34  |

| F 1  | Tr                                                                                     | 4 - |

| 5.1  | Iterative max-set-selection unit                                                       | 47  |

#### ABSTRACT

High-throughput and low-latency sorting is a key requirement in many applications that deal with large amounts of data. Searching and highenergy physics systems require a considerable number of sorting units. The particle detectors in CERN's Large Hadron Collider require hundreds of fast sorting units. To provide the performance and flexibility needed in high-energy physics experiments, these sorting units are often implemented using high-end FPGA devices. This thesis presents efficient techniques for designing high-throughput, low-latency sorting units. Our sorting architectures utilize modular design techniques that hierarchically construct large sorting units from smaller building blocks. The sorting units are optimized for situations in which only the M largest numbers from N inputs are needed, since this situation commonly occurs in many applications for scientific computing, data mining, network processing, digital signal processing, and high-energy physics. We utilize our proposed techniques to design parameterized, pipelined, and modular sorting units. A detailed analysis of these sorting units indicates that as the number of inputs increases their resource requirements scale linearly, their latencies scale logarithmically, and their frequencies remain almost constant. When synthesized to a 65-nm TSMC technology, a single pipelined 256-to-4 sorting unit with 19 stages can perform more than 2.7 billion sorts per second with a latency of about 7 ns per sort. When implemented on a Virtex-5 FPGA, the same sorting unit can perform roughly 200 million sorts per second with a latency of about 95 ns per sort. We also propose iterative sorting techniques, in which a small sorting unit is used several times to find the largest values.

Sorting is an important operation in a wide range of applications including data mining, databases [7, 19, 31], digital signal processing [47, 48], network processing, communication switching systems [4, 58], scientific computing [15], searching, scheduling [51], pattern recognition, robotics [10], image and video processing [11, 12, 17, 49], and high-energy physics (HEP) [23, 55]. For applications that require very high-speed sorting, hardware sorting units are often implemented using either ASICs or FPGAs to meet performance requirements [13, 28, 31, 33, 38, 41, 49]. Based on target applications, hardware sorting units vary greatly not only in architecture but also in the number of inputs and the width of inputs that they can process. For instance, only 9 to 25 inputs need to be processed in certain filters [11, 12], while the number of inputs can vary from 25 to 81 (or even higher) in certain image processing applications [45]. High-speed sorters on FPGAs in HEP applications deal with 128 to 256 data samples in 100 ns processing cycles [18, 23]. Thousands of inputs are sorted in video [49] and database applications [20, 31]. In general, inputs can be b-bit integers (8  $\leq$  b  $\leq$  64), floating-point numbers, or even compressed data values.

Most previous research on sorting units has focused on the situation in which the sorting unit must produce all of its inputs in sorted (increasing or decreasing) order. In many applications, however, only the M largest (or smallest) output values need to be selected from a total of N input values, where M < N. For example, in many HEP applications, only the M most energetic particles may be of interest. Similarly, in signal processing applications, only the M strongest signals or M closest points in space may need to be analyzed. In data mining, searching, and database systems, only top query outputs that score the most with respect to a given search key may need further processing. Furthermore, depending on the application, the M largest (smallest) outputs may not need to be in order. We refer to units

that only return the M largest (smallest) outputs, but do not guarantee that these M outputs are sorted, as max(min)-set-selection units. We refer to units that only return the M largest (smallest) outputs in sorted order as partial sorting units.

This thesis focuses on the design of partial sorting and max-set-selection units that return the  $M=2^m$  largest values from  $N=2^n$  inputs, where m and n are each whole numbers and  $1 \leq M < N^1$ . We refer to these units as N-to-M partial sorting and max-set-selection units. Our units discard small inputs as early as possible to reduce the sorting units' latency and hardware complexity. We investigate the design and VLSI implementations of partial sorting and max-set-selection units with low latency, high throughput, and modest resource requirements. Our designs are based on Batcher's bitonic and odd-even merge sorting networks [8, 21], which are widely used in VLSI and FPGA implementations due to their simplicity, regularity, and parallelism. The proposed units are scalable in terms of both the number of inputs and the number of outputs. We also present a generalized platform-independent methodology for designing high-performance pipelined partial sorting and max-set-selection units for which the width of the data to be sorted and the pipeline depth can easily be varied.

This research is an extension of our previous work on FPGA-based sorting units in the Large Hadron Collider (LHC) [18]. The main contributions of this dissertation and [18] are:

Modular techniques for designing N-to-M partial sorting and maxset-selection units. The units are composed of small and regular building blocks connected in a modular fashion, thereby reducing verification time and simplifying the design process. Our designs have low latency, high throughput, and modest resource requirements, can

<sup>&</sup>lt;sup>1</sup>Straightforward modifications to our designs allow the M smallest values, rather than the M largest values, to be output. It is also feasible to remove the current restriction that M and N are integer powers of two using techniques similar to those presented in [4, 25, 32, 37, 40].

be pipelined easily, have parameterized pipeline depth and data widths, and scale well to large values of N and M. Moreover, our techniques are independent of the bit-width and type of input values.

- A detailed analysis of our proposed partial sorting and max-set-selection units that includes both theoretical and synthesis estimates of our units' latency, throughput, and resource requirements. This analysis indicates that for a given number of outputs, resource requirements scale linearly with the number of inputs, latency scales logarithmically with the number of inputs, and the frequency remains nearly constant. Compared to conventional sorting units, which return all of their inputs in sorted order, our N-to-M partial sorting and max-set-selection units have much lower latency and area.

- A discussion of how the proposed max-set-selection units may be utilized iteratively to find the largest values from a set of data. This approach may lower resource requirements, storage cost, and I/O requirements at the cost of increased latency and decreased throughput.

To the best of our knowledge, this is the first time that N-to-M partial sorting networks have been presented and analyzed. In this work, we propose fast parallel sorting algorithms for finding/sorting the M largest values from N inputs and then design scalable architectures based on the proposed algorithms. Our N-to-M partial sorting networks have lower latency than any previous sorting designs when producing only the M largest values. Furthermore, our N-to-M max-set-selection units further decrease the latency and resource requirements by not producing their outputs in sorted order. Our parallel units target applications that require very low-latency sorting. Our iterative units target applications that require moderate-latency sorting by trading increased latency for reduced area and I/O bandwidth. Although our sorting units were originally designed for HEP experiments in the Large Hadron Collider, our methodology can be

utilized to design high-speed sorting and max-set selection units for a wide range of applications.

The remainder of this dissertation is organized as follows. Chapter 2 describes previous sorting networks and provides background information for our work. Chapter 3 presents our new partial sorting and max-set-selection units. Chapter 4 gives synthesis results for our proposed units. Chapter 5 shows how these units are used iteratively to sort data. Chapter 6 discusses related research on sorting algorithms and architectures. Chapter 7 concludes the dissertation.

A sorting network is a collection of interconnected compare-and-exchange (CAE) blocks that guides a parallel set of inputs to a parallel set of outputs in sorted order. Each CAE block has two inputs and two outputs. If the input values are already in order, they are directed to the corresponding outputs; otherwise, they are swapped.

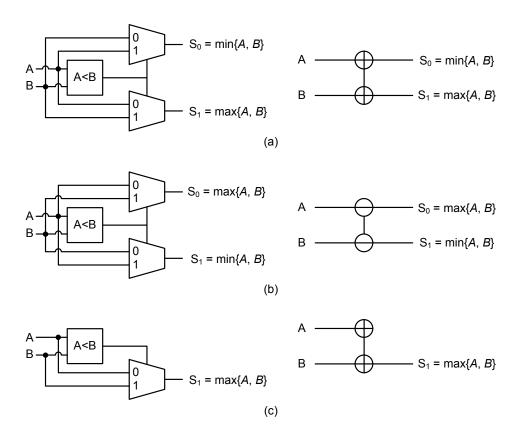

There are two types of CAE blocks, called increasing and decreasing CAE blocks, used in hardware-based sorting units. Fig. 2.1 shows the high-level implementations (left) and schematic symbols (right) for three building blocks used in previous sorting units and in our designs. Fig. 2.1(a) shows an increasing CAE block, which outputs its two inputs in ascending order. A decreasing CAE block, shown in Fig. 2.1(b), outputs its inputs in descending order. Decreasing and increasing CAE blocks are identical, except for their wiring. Each CAE block contains a comparator and two multiplexers. We also define Max units which are used in our designs. A Max unit, shown in Fig. 1(c), takes two inputs and returns the larger input. Note that the  $\oplus$  and  $\ominus$  symbols determine the type of the block in Fig. 2.1.

A sorting network usually consists of a series of stages in which each stage contains a number of CAE blocks that operate in parallel. The latency of a sorting network is proportional to its depth (the number of consecutive CAE blocks). Two popular parallel sorting networks that currently have the lowest known latency for hardware implementation are the bitonic and odd-even merge sorting networks proposed by Batcher [8]. The structure of a sorting network is fixed, regardless of the value of the numbers being sorted and the results of the comparisons. Sorting networks are a common solution for hardware-based sorting. Their parallel nature allows them to perform sorting much faster than the  $O(N \times \log(N))$  time achievable by the fastest sequential software-based sorting algorithms. A sorting network may also be pipelined to further increase throughput.

Figure 2.1: The high-level implementation (left) and schematic symbol (right) of building blocks for sorting networks.

## 2.1 Bitonic Sorting Networks

Concatenating an ascending and a descending sequence forms a single bitonic sequence. A bitonic sorting network recursively merges an ascending and a descending sequences each of length N/2 to make a sorted sequence of length N [8]. Each bitonic sorting network is composed of a number of bitonic merging units to merge bitonic sequences.

A K-input bitonic merging unit (denoted as BM-K) contains  $\log_2(K)$  stages of parallel CAE blocks, where each stage corresponds to a CAE stage with K/2 CAE blocks. Therefore, a BM-K requires  $\log_2(K) \times K/2$

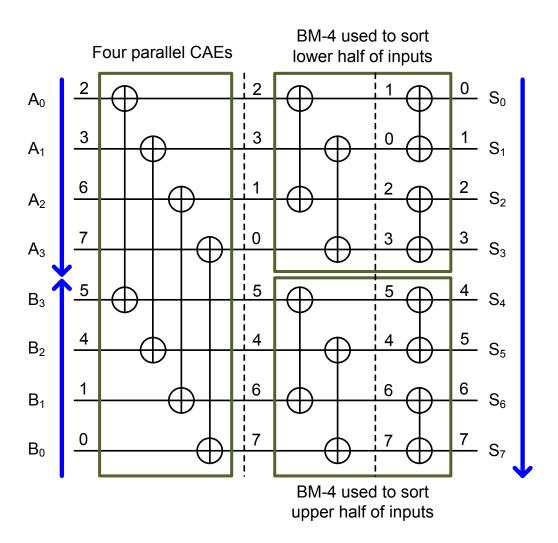

Figure 2.2: An increasing 8-input bitonic merging unit ( $\oplus$ BM-8) that is composed of four parallel CAE blocks followed by two parallel BM-4 units. The bitonic input sequence  $\{2, 3, 6, 7, 5, 4, 1, 0\}$  is the concatenation of the increasing sequence  $\{2, 3, 6, 7\}$  and the decreasing sequence  $\{5, 4, 1, 0\}$ .

Figure 2.3: The CAE network for an 8-input bitonic sorting unit with six CAE stages and 24 CAE blocks, made up of increasing  $(\oplus)$  and decreasing  $(\ominus)$  bitonic merging units. Arrows point in the direction of increasing values.

CAE blocks. For instance, an increasing BM-8 (denoted as  $\oplus$ BM-8) unit has three CAE stages and requires  $3 \times (8/2) = 12$  CAE blocks, as shown in Fig. 2.2. In this figure, the arrows point in the direction of increasing numbers and the dashed lines separate CAE stages. A BM-K unit is itself composed of a level of K/2 parallel CAE blocks followed by two parallel BM-(K/2) units. The  $\oplus$ BM-8 is constructed from a level of four parallel CAE blocks followed by two parallel BM-4 units that have four CAE blocks each. A decreasing BM-8 (denoted as  $\oplus$ BM-8) has a similar structure to an increasing BM-8, but it is only constructed from decreasing CAE blocks and the sorted outputs are in descending order.

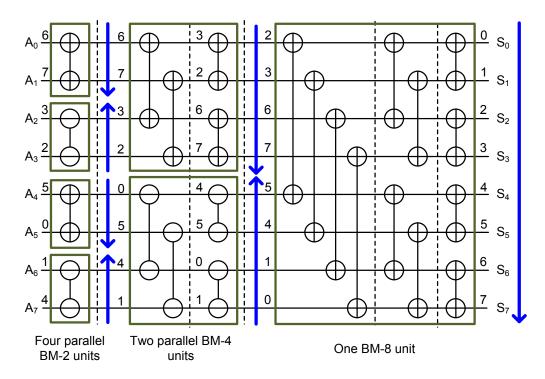

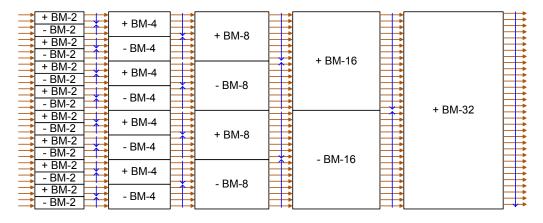

An 8-input bitonic sorting unit has four parallel BM-2 units, two parallel

BM-4 units, and one BM-8 unit, as shown in Fig. 2.3. Thus, this sorting unit has 1+2+3=6 CAE stages. Assuming the unit is pipelined so each stage takes one clock cycle, it can generate the sorted outputs in 6 cycles and can begin a new sort each cycle. In an N-input bitonic sorting unit, there are equal numbers of increasing and decreasing BM units in each level, excluding the last level, which has only either an increasing BM-N unit or a decreasing BM-N unit. In general, an N-input bitonic sorting unit is composed of N/2 BM-2 units, N/4 BM-4 units, N/8 BM-8 units, ..., two BM-N/2 units, and one BM-N unit. In this design, BM-K units are followed by BM-(2K) unit(s), where  $K = 2, 4, 8, ..., N/2, N, 2 \leq K \leq N$  and K and N are integer powers of 2. Therefore, since an N-input bitonic sorting unit has  $\log_2(N)$ consecutive BM-K units, where each BM-K unit has  $\log_2(K)$  CAE stages, an N-input bitonic sorting unit has  $\log_2(N) \times (\log_2(N) + 1)/2$  CAE stages. Since each stage has N/2 CAE blocks, the total number of CAE blocks in an N-input bitonic sorting unit is  $N \times \log_2(N) \times (\log_2(N) + 1)/4$ . For example, 16-input, 32-input, and 256-input bitonic sorting units require 10, 15, and 36 CAE stages and have 80, 240, and 4,608 CAE blocks, respectively.

### 2.2 Odd-even Merge Sorting Networks

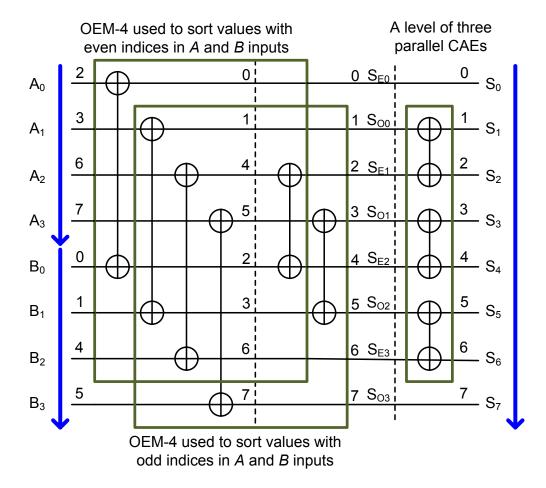

An odd-even merge sorting network recursively merges two ascending sequences of length K/2 to make a sorted sequence of length K. Each odd-even merge sorting network is composed of a number of odd-even merging units. A K-input odd-even merging unit (OEM-K) merges two ascending input sequences into a single ascending output sequence. It contains  $\log_2(K)$  CAE stages, where each stage has between K/4 and K/2 CAE blocks. An OEM-K takes two length K/2 ascending sequences, K and K and K are observed the input values having odd indices in K and K and K and K having even indices. The result is a sorted sequence of values with odd indices (K0) and

Figure 2.4: An 8-input odd-even merge unit (OEM-8) that is composed of two OEM-4 units and a level of three parallel CAE blocks.

a sorted sequence of values with even indices  $(S_E)$ .  $S_O$  and  $S_E$  are generated recursively, separately, and in parallel. In the final stage, the  $S_O$  and  $S_E$  sequences are merged to generate a sorted sequence with K values,  $S_O$  to  $S_{K-1}$ . The merging process is simply a compare-and-exchange of values in the  $S_O$  and  $S_E$  sequences.

An 8-input odd-even merging unit is shown in Fig. 2.4. An OEM-K unit is composed of two parallel OEM-K/2 units, followed by a level of (K/2-1) parallel CAE blocks. Unlike BM units, OEM units are only built from

Figure 2.5: The CAE network for an 8-input odd-even merge sorting unit with six CAE stages and 19 CAE blocks.

increasing CAE blocks. The total number of CAE blocks for an OEM-K unit is  $(K/2) \times (\log_2(K) - 1) + 1 = \log_2(K/2) \times (K/2) + 1$ . Thus, an OEM-8 unit has three CAE stages and  $2 \times 4 + 1 = 9$  CAE blocks. It is constructed from two parallel OEM-4 units that each have three parallel CAE blocks followed by a level of three parallel CAE blocks.

An 8-input odd-even merge sorting unit has four OEM-2 units, two OEM-4 units, and one OEM-8 unit, as shown in Fig. 2.5. It requires four parallel OEM-2 units, two parallel OEM-4 units, and a single OEM-8 unit, leading to a sorting unit with 1+2+3=6 CAE stages. Assuming the unit is pipelined with one stage per clock cycle, it can generate the sorted outputs in six cycles. In general, an N-input odd-even merge sorting unit is

| # of inputs and outputs | # of<br>CAE | # of CAE blocks |          |            |  |

|-------------------------|-------------|-----------------|----------|------------|--|

| $(N=M=2^n)$             | Stages      | Bitonic         | Odd-even | Difference |  |

| 8                       | 6           | 24              | 19       | 5          |  |

| 16                      | 10          | 80              | 63       | 17         |  |

| 32                      | 15          | 240             | 191      | 49         |  |

| 64                      | 21          | 672             | 543      | 129        |  |

| 128                     | 28          | 1,792           | 1,471    | 321        |  |

|                         |             |                 |          |            |  |

4.608

36

256

3,839

769

Table 2.1: The required number of CAE blocks and CAE stages for  $2^n$ -input bitonic and odd-even merge sorting units

composed of N/2 OEM-2 units<sup>1</sup>, N/4 OEM-4 units, N/8 OEM-8 units, ..., two OEM-N/2 units, and one OEM-N unit. In this design, OEM-K units are followed by OEM-2K unit(s), where K = 2, 4, 8, ..., N/2, N, and K and N are integers power of 2. Therefore, since an N-input odd-even merge sorting unit is composed of  $\log_2(N)$  consecutive OEM-K units, where each OEM-K unit has  $\log_2(K)$  CAE stages, an N-input odd-even merge sorting unit has  $(\log_2(N)) \times (\log_2(N) + 1)$  stages. This is equivalent to the number of CAE stages in an N-input bitonic sorting unit. In addition, since an OEM-K has  $\log_2(K/2) \times (K/2) + 1$  CAE blocks, an N-input odd-even merge sorting unit has  $N/4 \times (\log_2(N)) \times (\log_2(N) - 1) + N - 1$  CAE blocks.

## 2.3 Designing Large Sorting Networks

Based on the idea behind the bitonic and odd-even merge algorithms, large sorting units can be built using large merging units [8] that consist of multiple

<sup>&</sup>lt;sup>1</sup>BM-2 and OEM-2 units have the same structure.

CAE stages of increasingly larger size. Table 2.1 summarizes the required number of CAE blocks and stages for bitonic and odd-even merge sorting units. Both N-input bitonic and odd-even merge sorting units have a time complexity (depth) of  $O(\log_2^2(N))$  CAE stages and have an area complexity of  $O(N \times \log_2^2(N))$  CAE blocks. An N-input, N-output bitonic or odd-even merge complete sorting unit is composed of  $(\log_2 N) \times (\log_2 N + 1)/2$  CAE stages, where  $N = 2^n$ . However, the required number of CAE blocks differs for each type of sorting unit. Bitonic and odd-even merge sorting unit with  $2^n$  inputs and  $2^n$  outputs have  $2^{n-2} \times n \times (n+1)$  and  $2^{n-2} \times n \times (n-1) + 2^n - 1$  CAE blocks, respectively. Thus, odd-even merge sorting units have lower resource requirements than bitonic sorting units, but may have more complex wiring. The difference in the number of CAE blocks between bitonic and odd-even merge sorting units is  $2^{n-1} \times (n-2) + 1$ , which shows that the difference in the number of CAE blocks increases linearly with the number of inputs.

#### 3 PROPOSED PARTIAL SORTING AND

#### MAX-SET-SELECTION UNITS

In many applications, it is not necessary to return all of the sorted inputs. Applications often only need to determine the M largest or M smallest numbers from N inputs, where M < N and M and N are both integer powers of two  $(M = 2^m, N = 2^n)$ . Partial sorters provide the  $2^m$  largest values in sorted order, and max-set-selection units provide the 2<sup>m</sup> largest values in arbitrary order. Partial sorters and max-set-selection units are key components in many applications such as HEP and multimedia applications. For example, in the Large Hadron Collider [35], built by the European Organization for Nuclear Research (CERN), low-latency max-set-selection units identify important particle interactions that correspond to high-energy collisions [18, 55]. In multimedia applications, partial sorting units speed up data sorting algorithms [17]. Moreover, auxiliary max-set-selection units can cooperate with general-purpose processing units in embedded and database management systems to accelerate data search and sort algorithms. In cases such as this, Batcher's algorithms can be optimized to generate only the 2<sup>m</sup> largest numbers from 2<sup>n</sup> inputs with less latency and fewer CAE blocks than a complete sorting network.

In this chapter, we propose a modular technique based on Batcher's algorithms to design units that return only the 2<sup>m</sup> largest values from 2<sup>n</sup> inputs. In Chapter 3.1, we focus on the case that only the four largest values are produced by the max-set-selection unit without regard to output order. We also extend our technique to partial sorting units to return outputs in ascending order. In Chapter 3.2, we generalize our method so the proposed algorithm is applicable for any number of outputs that is an integer power of two and where results can be returned either in arbitrary or ascending order.

# 3.1 4-Output Max-set-selection and Partial Sorting Units

We first discuss 8-to-4 max-set-selection units and then extend our technique to larger  $2^n$ -to-4 max-set-selection and partial sorting units. To design  $2^n$ -to-4 max-set-selection units, we take advantage of the fact that only the four largest inputs are needed, in no particular order, to decrease the resource requirements and the number of CAE stages.

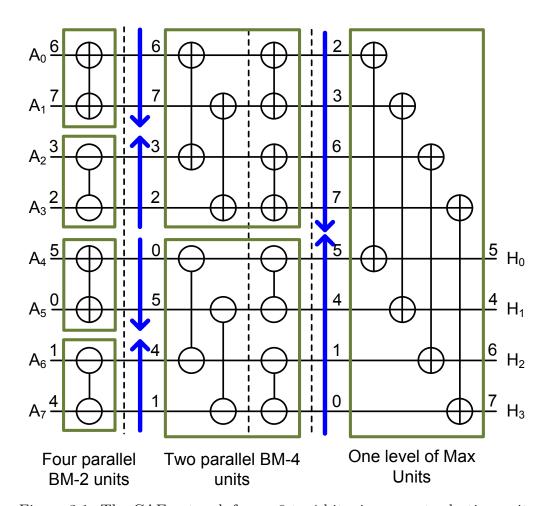

#### 3.1.1 8-to-4 Max-set-selection Units

To illustrate our technique, we first present the design of a refined 8-input bitonic sorting unit, called an 8-to-4 bitonic max-set-selection unit, that only returns the four largest numbers. A special feature of bitonic sequences is that performing Max operations on two sorted sequences (one increasing and the other one decreasing) each of K numbers, generates two new sequences of K numbers in which numbers in one sequence are all less than numbers in the other sequence. In BM-K units, the first level of parallel CAE blocks partitions the input numbers into two (K/2)-number sub-sets: the smaller numbers and the larger numbers. However, the first level of parallel CAE blocks in OEM units must be rewired to correctly generate the smaller and larger subsets of numbers. Figs. 3.1 and 3.2 show 8-to-4 max-set-selection units that use bitonic and odd-even merge algorithms, respectively. As shown in Fig. 3.1, the BM-8 unit in Fig. 2.3 is replaced with a level of Max units that has the same wiring as the first level of parallel CAE blocks in the BM-8 unit. Fig. 3.2 illustrates that the OEM-8 unit in Fig. 2.5 is replaced with a level of Max units with wirings that differ from the first level of parallel CAE blocks in the OEM-8 unit. These modifications decrease the required number of CAE stages from six in 8-input sorting units to four in 8-to-4 max-set-selection units.

Figure 3.1: The CAE network for an 8-to-4 bitonic max-set-selection unit with four CAE stages and 16 CAE blocks.

Figure 3.2: The CAE network for an 8-to-4 odd-even merge max-set-selection unit with four CAE stages and 14 CAE blocks.

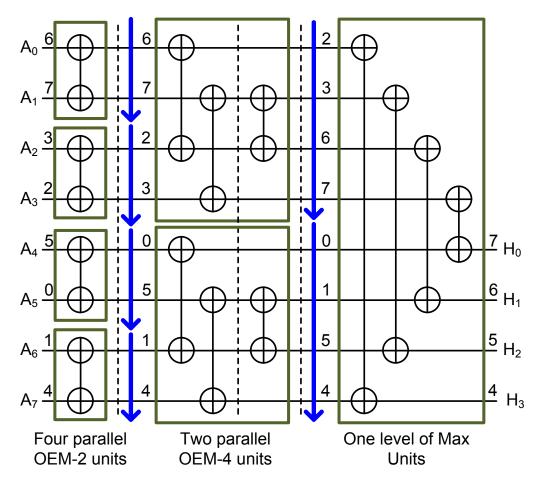

## 3.1.2 BM-8-to-4 and 8-to-4 Partial Sorting Units

The 8-to-4 max-set-selection units, however, cannot be used directly to form larger sorting or max-set-selection units, because the outputs of the 8-to-4 max-set-selection units in Fig. 3.1 and Fig. 3.2 are not in a specific order. Since inputs to BM units should be a bitonic sequence and inputs to OEM units should be two ascending sequences, these designs cannot be connected directly to other BM or OEM units when designing larger sorters.

Figure 3.3: The CAE network for an 8-to-4 bitonic partial sorting unit with six CAE stages and 20 CAE blocks.

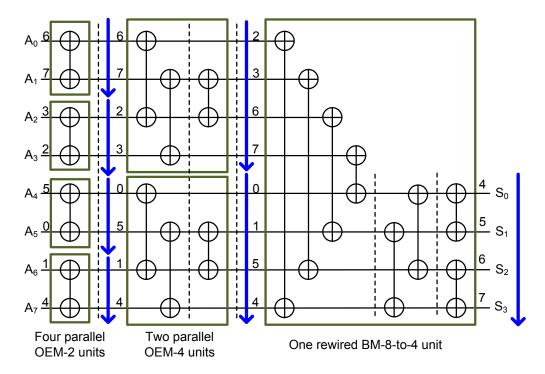

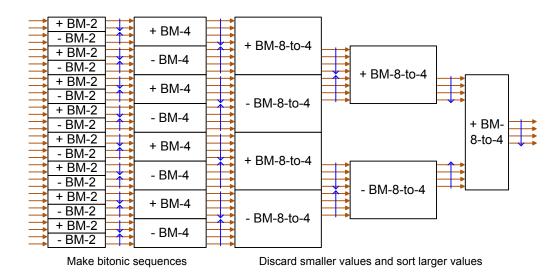

To solve this problem, we have designed a new merging unit called a BM-8-to-4 unit, shown as the right-most block in Figs. 3.3 and 3.4. A BM-8-to-4 unit is an 8-input bitonic merging unit that outputs only the four largest values in either ascending  $\oplus$  or descending  $\ominus$  order. Fig. 3.3 depicts our proposed 8-to-4 bitonic partial sorting unit that returns the four largest values from its eight inputs in ascending order. Compared to the 8-input bitonic sorting unit shown in Fig. 2.3, it needs fewer CAE blocks and the BM-8 unit is replaced with a BM-8-to-4 unit. A descending 8-to-4 partial sorting unit has a similar structure. A BM-8-to-4 unit has a level of four parallel CAE blocks followed by a BM-4 unit. With this approach, the output of an 8-to-4 bitonic partial sorting unit can be fed to other bitonic merging units.

Figure 3.4: The CAE network for an 8-to-4 odd-even merge partial sorting unit with six CAE stages and 18 CAE blocks.

Fig. 3.4 depicts our proposed 8-to-4 odd-even merge partial sorting unit that returns the four largest values from its eight inputs in ascending order. Compared to the 8-input odd-even merge sorting unit in Fig. 2.5, it needs fewer CAE blocks and the OEM-8 unit is replaced with a BM-8-to-4 unit. In fact, the partial sorting unit shown in Fig. 3.4 is a hybrid unit composed of bitonic and odd-even merging units. Since a bitonic merging unit takes only a bitonic sequence, the inputs to the BM-8-to-4 unit in Fig. 3.4 are rewired to convert the two sorted sequences to a bitonic sequence. This way, the output of odd-even merging units can be fed to bitonic merging units. We could also propose an OEM-8-to-4 unit to avoid the rewiring technique. However, since an OEM-8-to-4 unit requires more registers than a BM-8-to-4, only BM-2<sup>k+1</sup>-to-2<sup>k</sup> units are used throughout the thesis. Note

Figure 3.5: A 16-to-4 bitonic max-set-selection unit.

that only increasing BM-8-to-4 units are used in our proposed odd-even merge sorting unit, while both increasing and decreasing BM-8-to-4 units are used in the bitonic sorting unit.

## 3.1.3 2<sup>n</sup>-to-4 Max-set-selection and Partial Sorting Units

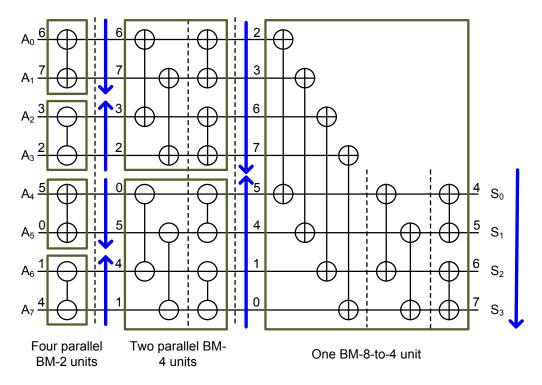

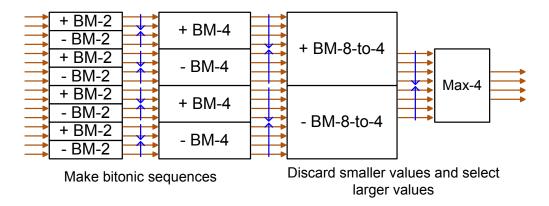

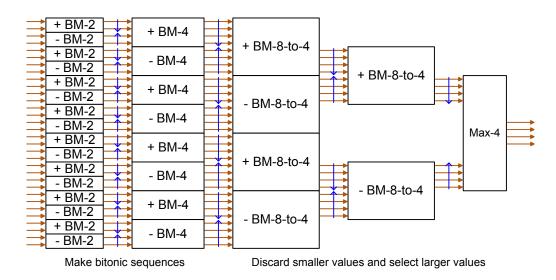

To design larger  $\mathcal{Z}^n$ -to-4 max-set-selection units, we can take advantage of the fact that BM-8-to-4 units can be combined to make larger units. Since BM-8-to-4 units generate sorted outputs, these outputs can feed other BM-8-to-4 units. We can build larger  $2^n$ -to-4 bitonic max-set-selection units using BM-2, BM-4, BM-8-to-4, and Max-4 units. We can also build larger  $2^n$ -to-4 odd-even merge max-set-selection units using OEM-2, OEM-4, BM-8-to-4, and Max-4 units. BM-2, BM-4, BM-8, BM-8-to-4, and Max-4 units require 1, 4, 12, 8, and 4 CAE blocks, respectively. OEM-4 and OEM-8 units require 3 and 9 CAE blocks, respectively.

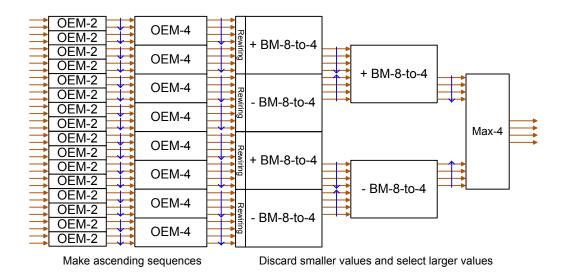

Figs. 3.5 shows the structures of 16-to-4 bitonic max-set-selection units that utilize multiple BM-8-to-4 units. Fig. 3.6 shows the structure of a 32-to-4 bitonic max-set-selection unit that has 10 CAE stages. Fig. 3.7 shows the structure of a 32-to-32 bitonic sorting unit that has 15 CAE

Figure 3.6: A 32-to-4 bitonic max-set-selection unit.

Figure 3.7: A 32-to-32 bitonic sorting unit.

Figure 3.8: A 32-to-4 odd-even merge max-set-selection unit.

Figure 3.9: A 32-to-4 bitonic partial sorting unit.

stages. In these designs, smaller numbers are discarded in stages as early as possible to reduce the total number of CAE stages and CAE blocks. A 16-to-4 bitonic max-set-selection unit has one level of parallel BM-8-to-4 units, while a 32-to-4 bitonic max-set-selection unit employs two levels of parallel BM-8-to-4 units.

Fig. 3.8 depicts the high-level structure of a 32-to-4 odd-even merge maxset-selection unit that utilizes several OEM and BM-8-to-4 units. Unlike bitonic max-set-selection and partial sorting units, odd-even merge units only use increasing merging units, which is an advantage in terms of simplicity of design. On the other hand, as shown in Fig. 3.8, the outputs of OEM-4 units are rewired to feed BM-8-to-4 units, which is a disadvantage. In general,  $2^n$ -to-4 max-set-selection units have n-3 levels of parallel BM-8-to-4 units for n>3.

To make a 2<sup>n</sup>-to-4 partial sorting unit, the last level of a 2<sup>n</sup>-to-4 maxset-selection unit, which is a Max-4 unit, is replaced by a BM-8-to-4 unit to generate outputs in sorted order. This increases the number of CAE stages and the number of CAE blocks by 2 and 4, respectively. Fig. 3.9 shows the structure of a 32-to-4 bitonic partial unit (compare this with Fig. 3.6).

Table 3.1 compares the resource requirements of sub-units used in  $2^n$ -to-4 max-set-selection and  $2^n$ -to- $2^n$  sorting units. Table 3.2 shows the resource requirements and the number of CAE stages for our proposed  $2^n$ -to-4 and  $2^n$ -to-8 max-set-selection units. The required number of CAE stages for a  $2^n$ -to-4 bitonic max-set-selection unit can be calculated based on the fact that it is composed of a level of parallel BM-2 units, a level of parallel BM-4 units, n-3 levels of parallel BM-8-to-4 units, and a Max-4 unit. Similarly, the required number of CAE blocks can be calculated based on the fact that there are  $2^{n-1}$  BM-2 units,  $2^{n-2}$  BM-4 units,  $2^{n-2}-2$  BM-8-to-4 units, and one Max-4 unit in a  $2^n$ -to-4 bitonic max-set-selection unit. Both  $2^n$ -to-4 bitonic and odd-even merge max-set-selection units

require  $7 \times 2^{n-1} - 12$  and  $13 \times 2^{n-2} - 12$  CAE blocks, respectively. Thus,  $2^n$ -to-4 max-set-selection and partial sorting units require many fewer CAE stages and CAE blocks than conventional  $2^n$ -input complete sorting units for large values of  $\mathfrak{n}$ . For example, while a 256-input sorting unit has 36 CAE stages, a 256-to-4 max-set-selection unit has 19 CAE stages, and a 256-to-4 partial sorting unit has 21 CAE stages. As shown in Table 2.1, a 256-input bitonic sorting units requires 4,608 CAE blocks. However, a 256-to-4 bitonic max-set-selection unit and a 256-to-4 bitonic partial sorting unit require 884 and 888 CAE blocks, respectively. Similarly, as shown in Table 2.1, a 256-input odd-even merge sorting unit requires 3,839 CAE blocks. However, a 256-to-4 odd-even merge max-set-selection unit and a 256-to-4 odd-even merge partial sorting unit require 820 and 824 CAE blocks, respectively. This indicates significant improvements of max-set-selection compared to the conventional sorting units in terms of both the number of CAE stages and the required number of CAE blocks.

Table 3.2 shows how max-set-selection units can be built from BM/OEM and Max units. For instance, to implement a 256-to-4 max-set-selection unit, 128 BM-2/OEM-2 units, 64 BM-4/OEM-4 units, 62 BM-8-to-4 units, and a Max-4 unit are needed. In general, odd-even merge max-set-selection units need fewer CAE blocks than the corresponding bitonic max-set-selection units, but bitonic max-set-selection units have more regular structures and are easier to design. Table 3.2 indicates that the fastest 256-to-4 max-set-selection units have a latency of 19 clock cycles (assuming each CAE stage takes one clock cycle). In comparison, conventional 256-input sorting units require 36 clock cycles to sort all 256 data values.

We also investigated constructing 256-to-4 max-set-selection units using 8-to-4, 16-to-4, 32-to-4, 64-to-4, and 128-to-4 max-set-selection units, as shown in Table 3.3. Tables 3.2 and 3.3 indicate that the fastest 256-to-4 max-set-selection units have a latency of 19 clock cycles (assuming each stage takes one clock cycle). In comparison, conventional 256-input sorting

Table 3.1: Sub-units used in  $2^n$ -to-4 max-set-selection and  $2^n$ -to- $2^n$  sorting units (10-bit unsigned data width)

| Sub-unit  | CAE Blocks | CAE Stages | Slice LUTs | Slice Regs |

|-----------|------------|------------|------------|------------|

| BM-2      | 1          | 1          | 30         | 20         |

| Max-4     | 4          | 1          | 60         | 40         |

| BM-4      | 4          | 2          | 100        | 80         |

| BM-8      | 12         | 3          | 300        | 240        |

| BM-8-to-4 | 8          | 3          | 160        | 120        |

| BM-16     | 32         | 4          | 800        | 640        |

| BM-32     | 80         | 5          | 2,000      | 1,600      |

| BM-64     | 192        | 6          | 4,800      | 3,840      |

| BM-128    | 448        | 7          | 11,200     | 8,960      |

| BM-256    | 1,024      | 8          | 25,600     | 20,480     |

units require 36 clock cycles to sort all 256 data values. In addition, the oddeven merge max-set-selection unit design shown in the last row of Table 3.2 requires fewer CAE blocks than the designs introduced in Table 3.3. In general, odd-even merge max-set-selection units need fewer CAE blocks than bitonic max-set-selection units, but bitonic max-set-selection units have more regular structures and are easier to design.

Table 3.2: Structure and number of CAE stages and CAE blocks for  $2^{n}$ -to-4 and  $2^{n}$ -to-8 bitonic and odd-even merge max-set-selection units made up of smaller merging units. The numbers in parentheses under "Structure" show the required number of each unit.

| Max-set-  | Structure                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |                                                                                                                                                                                                                                        | Jo#                         | # of CAE Blocks | Blocks       |

|-----------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------|-----------------|--------------|

| selection | Bitonic Odd-even                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |                                                                                                                                                                                                                                        | $\operatorname{CAE}$ Stages | Bitonic         | Odd-<br>even |

| 8-to-4    | $BM-2(4) \rightarrow BM-4(2) \rightarrow Max-4(1)$ OEM-2                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | $OEM-2(4) \rightarrow OEM-4(2) \rightarrow Max-4(1)$                                                                                                                                                                                   | 4                           | 16              | 14           |

| 16-to-4   | $\begin{array}{cccccccccccccccccccccccccccccccccccc$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |                                                                                                                                                                                                                                        | 2                           | 44              | 40           |

| 16-to-8   | $BM-4(4) \rightarrow B$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | $2(8) \rightarrow \text{OEM-4}(4) \rightarrow \text{OEM-8}(2) \rightarrow (1)$                                                                                                                                                         | 7                           | 56              | 46           |

| 32-to-4   | $\rightarrow$ BM-4(8) $\rightarrow$ I(2) $\rightarrow$ Max-4(1)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | $\begin{array}{c c} \mathrm{BM-8-to-4(4)} \rightarrow \mathrm{OEM-2(16)} \rightarrow \mathrm{OEM-4(8)} \rightarrow \mathrm{BM-8-to-4(4)} \rightarrow \\ \mathrm{BM-8-to-4(2)} \rightarrow \mathrm{Max-4(1)} \\ \end{array} \boxed{10}$ | 10                          | 100             | 92           |

| 32-to-8   | $  \text{BM-2}(16) \rightarrow \text{BM-4}(8) \rightarrow \text{BM-8}(4) \rightarrow \text{BM-16-}   \text{OEM-2}(16) \rightarrow \text{OEM-4}(8) \rightarrow   \text{to-8}(2) \rightarrow \text{Max-8}(1) \\   \text{DM-16-to-8}(2) \rightarrow \text{DM-16-to-8}(2) \\   \text{DM-16-to-8}(2$                                                                                                                                                                                                                                                                                                       | OEM-8(4) $\rightarrow$                                                                                                                                                                                                                 | 11                          | 144             | 124          |

| 64-to-4   | $\rightarrow$ BM-4(16) $\rightarrow$ BM-8-to-4(8) $\rightarrow$ (4) $\rightarrow$ BM-8-to-4(2) $\rightarrow$ Max-4(1)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | OEM-2(32) $\rightarrow$ OEM-4(16) $\rightarrow$ BM-8-to-4(2) $\rightarrow$ Max-4(1)                                                                                                                                                    | 13                          | 212             | 196          |