# Integrated Radio-Frequency Receivers for RF-to-Digital Converters

Faizan UI Haq

# Integrated Radio-Frequency Receivers for RF-to-Digital Converters

Faizan UI Haq

A doctoral dissertation completed for the degree of Doctor of Science (Technology) to be defended, with the permission of the Aalto University School of Electrical Engineering, at a public examination held at the lecture hall TU1 of the school on 17 October 2019 at 1200.

Aalto University

School of Electrical Engineering

Department of Electronics and Nanoengineering

#### Supervising professor

Prof. Jussi Ryynänen, Aalto university, Finland

#### Thesis advisor

Dr. Kari Stadius, Aalto university, Finland

### **Preliminary examiners**

Prof. Andrea Neviani, University of Padua, Italy Prof. Domenico Zito, Aarhus University, Denmark

### Opponent

Prof. Dag T. Wisland, University of Oslo, Norway

Aalto University publication series **DOCTORAL DISSERTATIONS** 167/2019

© 2019 Faizan UI Haq

ISBN 978-952-60-8718-4 (printed)

ISBN 978-952-60-8719-1 (pdf)

ISSN 1799-4934 (printed)

ISSN 1799-4942 (pdf)

http://urn.fi/URN:ISBN:978-952-60-8719-1

Unigrafia Oy Helsinki 2019

Finland

#### **Author**

| Faizan   | IJ           | Hag  |

|----------|--------------|------|

| 1 uizuii | $\mathbf{c}$ | TIUG |

| ☐ Monograph ☐ Article dissertati                                                          | on $oxedsymbol{\square}$ Essay dissertation |

|-------------------------------------------------------------------------------------------|---------------------------------------------|

| Permission for public defence granted (date) 26                                           | August 2019 Language English                |

| Manuscript submitted 10 June 2019                                                         | Date of the defence 17 October 2019         |

| Field of research Micro- and Nanoelectonic Circuit                                        | Design                                      |

| Series Aalto University publication series DOCTORA                                        | L DISSERTATIONS 167/2019                    |

| Unit Department of Electronics and Nanoengineering                                        | ·                                           |

| Publisher School of Electrical Engineering                                                |                                             |

| Name of the doctoral dissertation<br>Integrated Radio-Frequency Receivers for RF-to-Digit | al Converters                               |

| raizan UI Haq                                                                             |                                             |

### **Abstract**

The widespread usage of mobile communication in recent decades has crowded the frequency spectrum with multiple bands and communication standards. An ideal wireless receiver for such a scenario will need to cover all frequency bands/standards with the possibility of instant reconfigurability through software control. The receiver should also be entirely integrated to gain the advantages of mobility and cheaper production costs. The ultimate goal of an ideal receiver is encapsulated in the concept of software-defined radio (SDR).

An attractive approach to realize an SDR is an RF-to-digital converter. In best case, an RF-todigital converter consists of an analog-to-digital converter (ADC) which is directly connected to a wideband antenna. This means that the received signal on the antenna is immediately converted in the digital domain where reconfigurability is easy to achieve. However, such a complete RF-todigital converter has so far proved to be an elusive goal due to impractically high power consumption requirements of ADC in the GHz range. Therefore, a practical RF-to-digital converter is followed by an RF front-end which reduces the power consumption requirements of an ADC by signal amplification, filtering, and frequency down-conversion. SDR research for such a practical case is focused towards reconfigurable, wideband and digital intensive RF front-ends. It is also targetted at reducing the number of parallel receiver front-ends by implementing a single wideband and fully integrated front-end capable of receiving all frequency bands/standards. To design receiver solutions for such a practical RF-to-digital converter, new techniques are needed to overcome the design challenges.

This thesis focuses on finding new solutions to four of these design challenges related to the goal of RF-to-digital converters: 1) Blocker tolerance in wideband RF front-ends; 2) harmonic rejection RF-front ends with on-chip N-path filtering; 3) transmitter self leakage cancellation, and; 4) blocker rejection and sensitivity issues in direct delta sigma receivers.

Starting from the detailed description of these challenges, research outcomes on both theoretical and experimental fronts are presented. In particular, a harmonic-rejection receiver was fabricated in 28nm fully-depleted silicon-on-insulator (FDSOI) technology. The receiver attempts to resolve many of the above-mentioned challenges through higher-order on-chip filtering, simple localoscillator clocking, and a two-stage harmonic-rejection implementation. The receiver front-end also includes a novel transmitter signal-leakage cancellation technique through buried-gate signaling in an FDSOI process. In addition to the fabricated receiver, the thesis incorporates two new blocker attenuation techniques at the input of the low-noise amplifier in the receiver chain. On the theoretical front, sensitivity issues in direct delta sigma receivers are analyzed with detailed theoretical modeling leading to simple design guidelines. Details of all these contributions can be found in the author's publications I-IX.

#### Keywords

| ISBN (printed) 978-952-60-8718- | 4 <b>ISBN (pdf)</b> 978-952-60-8719-1        |

|---------------------------------|----------------------------------------------|

| ISSN (printed) 1799-4934        | ISSN (pdf) 1799-4942                         |

| Location of publisher Helsinki  | Location of printing Helsinki Year 2019      |

| Pages 209                       | urn http://urn.fi/URN:ISBN:978-952-60-8719-1 |

### **Preface**

This dissertation is based on work that was performed in 2015-2019 in the department of electronics and nanoengineering, Aalto university Finland. The work was funded by Academy of Finland under the projects named IROC and 5GTRX. I also received a small study-exchange travel grant from the foundation TIES in 2018 for my research collaboration visit in University of Toronto, Canada.

I was honored to have professor Jussi Ryynänen as my supervising professor, who gave me the opportunity to pursue PhD degree in his research group. I especially value his friendly and encouraging attitude along with his willingness to entertain new ideas. My immediate advisor Dr. Kari Stadius deserves a strong acknowledgment for his efforts that guided me in each and every step of my PhD. He was always helpful and shedded light on many things that were previously a mystery to me. I would also like to share my warmest gratitude to my colleagues in Aalto university especially Dr. Mikko Englund with whome I started working as a group from 2015 to 2017. I sincerely value his strong knowledge in the field of receiver design. A strong collaboration, endless discussion and sharing ideas made the project a success. I would also like to thanks my other colleagues Dr. Marko Kosunen, Mr. Olli Viitala, Mr. Tero Tikka, Ms Zahra Khonsari, Mr. Yury Antonov, Dr. Enrico Roverato, Mr. Miikka Tenhunen for close coordination and support on technical matters in different phases of my PhD degree.

In addition to the above mentioned colleagues, Dr. Kimmo Koli from Huawei technologies deserves my thanks for providing useful ideas for further research and Dr. Antonio Liscidini from University of Toronto, for support and guidance during my exchange studies period in University of Toronto, Canada.

Of course, none of this would have been possible without the help and

Preface

detailed guidance of Dr. Kim Bertel Östman. Starting from the beginning, Dr. Östman guided me in all areas of research. I would particularity like to thank his contribution in improving my scientific writing and theoretical analysis skills.

My warmest regards to my parents who have always been there for me. It is because of their love and support that I have been able to come up to this level. I remember the countless efforts of my mother and father teaching me in my childhood days. Finally, I would like to express my deepest gratitude to my wife. Especially during the past three years she suffered due to my long working hours in university and had to take care of son single-handedly. Without your support, achieving this goal would not have been possible.

Espoo, September 5, 2019,

Faizan Ul Haq

### **Contents**

| Pr                                     | етасе   |                              |                                            | 111  |

|----------------------------------------|---------|------------------------------|--------------------------------------------|------|

| Co                                     | ntent   | s                            |                                            | v    |

| Lis                                    | st of F | Publicat                     | ions                                       | vii  |

| Au                                     | thor's  | s Contri                     | bution                                     | ix   |

| Lis                                    | st of A | Abbrevia                     | ations                                     | xiii |

| Lis                                    | st of S | Symbols                      |                                            | xvii |

| 1.                                     | Intr    | oductio                      | n                                          | 1    |

|                                        | 1.1     | Backgr                       | ound                                       | 1    |

|                                        | 1.2     | Object                       | ives of the work                           | 2    |

|                                        | 1.3     | Main s                       | cientific merits                           | 2    |

|                                        | 1.4     | Conter                       | ats and organization of the thesis         | 3    |

| 2. Wideband integrated receiver design |         |                              |                                            | 5    |

|                                        | 2.1     | Overvi                       | ew                                         | 5    |

|                                        | 2.2     | Major receiver architectures |                                            |      |

|                                        | 2.3     | Performance requirements     |                                            |      |

|                                        |         | 2.3.1                        | Input impedance matching                   | 9    |

|                                        |         | 2.3.2                        | Sensitivity and noise performance          | 10   |

|                                        |         | 2.3.3                        | Blocker noise figure and reciprocal mixing | 11   |

|                                        |         | 2.3.4                        | Linearity: Intermodulation                 | 12   |

|                                        |         | 2.3.5                        | Linearity: Compression                     | 14   |

| 2.4 Research trend                     |         |                              | ch trends: From present to future          | 15   |

|                                        | 2.5     | Blocke                       | r-tolerant receivers                       | 17   |

| 3.                                     | Bloc    | ker-tole                     | erant RF front-ends                        | 21   |

|                                          | 3.1                                | Overvie                                               | w                                                   | 21 |  |

|------------------------------------------|------------------------------------|-------------------------------------------------------|-----------------------------------------------------|----|--|

|                                          | 3.2                                | F 8                                                   |                                                     |    |  |

|                                          | 3.3                                |                                                       |                                                     |    |  |

|                                          |                                    | 3.3.1                                                 | Proposed capacitive feedback low-noise amplifier    |    |  |

|                                          |                                    |                                                       | (LNA)                                               | 27 |  |

|                                          |                                    | 3.3.2                                                 | Analysis, modeling and simulations                  | 29 |  |

|                                          | 3.4                                | Self-inte                                             | erference cancellation in full-duplex transmission  | 35 |  |

| 4.                                       | Harmonic-Rejection RF front-ends 4 |                                                       |                                                     | 41 |  |

|                                          | 4.1                                | Overvie                                               | w                                                   | 41 |  |

|                                          | 4.2                                | Propose                                               | d harmonic-rejection receiver                       | 43 |  |

|                                          |                                    | 4.2.1                                                 | Architecture                                        | 43 |  |

|                                          |                                    | 4.2.2                                                 | Implementation and measurements                     | 44 |  |

| <b>5.</b>                                | Direct delta-sigma receivers       |                                                       |                                                     |    |  |

|                                          | 5.1                                | Overvie                                               | w                                                   | 51 |  |

|                                          | 5.2                                | Direct delta-sigma receivers: Benefits and challenges |                                                     |    |  |

| 5.3 Improving dynamic range: Upper limit |                                    |                                                       | ng dynamic range: Upper limit                       | 53 |  |

|                                          |                                    | 5.3.1                                                 | Reduced gain                                        | 53 |  |

|                                          |                                    | 5.3.2                                                 | Blocker rejection at direct delta-sigma receiver    |    |  |

|                                          |                                    |                                                       | (DDSR) input                                        | 55 |  |

|                                          | 5.4                                | 5.4 Improving dynamic range: Lower limit              |                                                     |    |  |

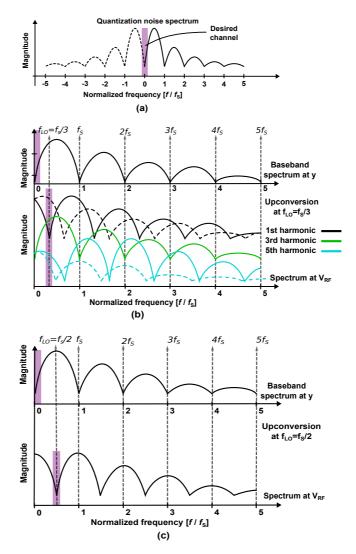

|                                          |                                    | 5.4.1                                                 | Modeling of quantization noise upconversion $\ \ .$ | 59 |  |

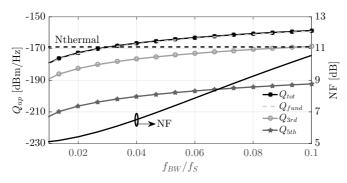

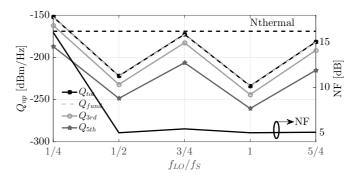

|                                          |                                    | 5.4.2                                                 | Model evaluation and design guidelines              | 62 |  |

|                                          | 5.5                                | Summa                                                 | ry                                                  | 66 |  |

| 6.                                       | Conc                               | lusions                                               |                                                     | 67 |  |

| Re                                       | ferenc                             | es                                                    |                                                     | 71 |  |

| Pu                                       | Publications                       |                                                       |                                                     |    |  |

### **List of Publications**

This thesis consists of an overview and of the following publications which are referred to in the text by their Roman numerals.

- I F. Ul Haq, M. Englund, K. Stadius, M. Kosunen, K. B. Östman, K. Koli, and J. Ryynänen. A wideband blocker resilient RF front-end with selective input-impedance matching for direct delta sigma receiver architectures. In *IEEE NORCAS Conference*, pp. 1-4, Copenhagen, Denmark, November 2016.

- II F. Ul Haq, M. Englund, K. Stadius, M. Kosunen, K. B. Östman, K. Koli, and J. Ryynänen. A wideband blocker resilient direct delta sigma receiver with selective input-impedance matching. In *IEEE ISCAS Conference*, pp. 1-4, Baltimore, MD USA, May 2017.

- III F. Ul Haq, M. Englund, Y. Antonov, K. Stadius, M. Kosunen, K. B. Östman, K. Koli, and J. Ryynänen. Full-duplex wireless transceiver self-interference cancellation through FD-SOI buried-gate signaling. In *IEEE ISCAS Conference*, pp. 1-5, Florence, Italy, May 2018.

- IV F. Ul Haq, M. Englund, Y. Antonov, K. Stadius, M. Kosunen, K. B. Östman, K. Koli, and J. Ryynänen. A blocker-tolerant two-stage harmonic-rejection RF front-End. In *IEEE RFIC symposium*, Boston, USA, June 2019.

- V F. Ul Haq, K. B. Östman, M. Englund, K. Stadius, M. Kosunen, K. Koli, and J. Ryynänen. A common-gate common-source low noise amplifier

based RF front-end with selective input impedance matching for blockerresilient receivers. *Wiley journal of circuit theory and applications*, pp. 1427-1442 Vol. 46, Issue. 8, August 2018.

- VI F. Ul Haq, M. Englund, K. Stadius, M. Kosunen, K. B. Östman, K. Koli, and J. Ryynänen. Quantization noise upconversion effects in mixer first direct delta-sigma receivers. Accepted for publication in *Wiley journal of circuit theory and applications*, 2019.

- VII M. Englund, F. Ul Haq, K. Stadius, M. Kosunen, K. B. Östman, K. Koli, and J. Ryynänen. A systematic design method for direct delta-sigma receivers. *IEEE transactions on Circuits and Systems I*, pp. 2389-2402 Vol. 65, Issue. 8, August 2018.

- VIII F. Ul Haq, M. Englund, Y. Antonov, M. Tenhunen, K. Stadius, M. Kosunen, K. B. Östman, K. Koli, and J. Ryynänen. A blocker-tolerant two-stage harmonic-rejection receiver. Submitted to *IEEE transcations on Microwave theory and techniques*, 2019.

- **IX** F. Ul Haq, M. Englund, K. Stadius, M. Kosunen, K. B. Östman, K. Koli, and J. Ryynänen. A wideband blocker resilient direct delta sigma receiver with selective input-impedance matching. Submitted to *Springer journal* of analog integrated circuits and signal processing, 2019.

### **Author's Contribution**

# Publication I: "A wideband blocker resilient RF front-end with selective input-impedance matching for direct delta sigma receiver architectures"

The author proposed the selective input impedance concept for blocker rejection. The author developed the idea and circuits with guidance from other authors, performed simulations, wrote the manuscript and presented the work at the conference.

# Publication II: "A wideband blocker resilient direct delta sigma receiver with selective input-impedance matching"

The author further extended the selective input-impedance concept for a complete direct delta-sigma receiver. The author performed simulations, wrote the manuscript and presented the work at the conference.

# Publication III: "Full-duplex wireless transceiver self-interference cancellation through FD-SOI buried-gate signaling"

The presented RF front-end was fabricated in 28nm technology. The author was responsible for the front-end design, excluding the LO chain. The author conducted all measurements, wrote the manuscript and presented the work at the conference.

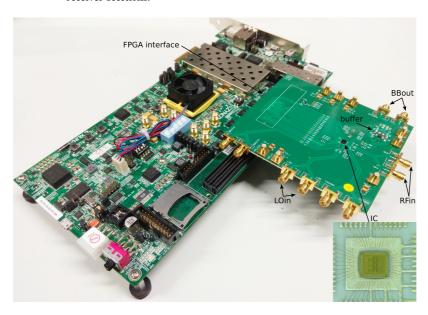

## Publication IV: "A blocker-tolerant two-stage harmonic-rejection RF front-End"

The presented RF front-end was designed collaboratively with the coauthors. The author was responsible for the front-end design, excluding the LO chain. The author made the prototype PCB, conducted all the measurements, wrote the manuscript and presented the work at the conference.

# Publication V: "A common-gate common-source low noise amplifier based RF front-end with selective input impedance matching for blocker-resilient receivers"

The author developed the original concept of Dr. Östman, derived the theoretical analysis and design guidelines, performed simulations and wrote the manuscript.

## Publication VI: "Quantization noise upconversion effects in mixer first direct delta-sigma receivers"

In co-operation with the other authors, the author developed the mixer-first DDSR model for analyzing the quantization noise upconversion effects, derived the design guidelines based on analytical and simulated results and implemented a transistor level prototype of the mixer first DDSR, except the quantizer and LO chain. The author also wrote the manuscript.

## Publication VII: "A systematic design method for direct delta-sigma receivers"

The paper presents a systematic design method for gmC-based direct delta sigma receivers. The author co-developed the RF front-end specifications and circuits for the envisioned design method with the main author of paper.

## Publication VIII: "A blocker-tolerant two-stage harmonic-rejection receiver"

The author was responsible for design of the RF front-end, PCB design, and measurements for the whole receiver including both analog front-end and digital quantizer output measurements. The author was the main writer of the submitted manuscript.

# Publication IX: "A wideband blocker resilient direct delta sigma receiver with selective input-impedance matching"

This publication was an extended version of the previous ISCAS 2017 conference publication II. The author extended the previous work through supporting theoretical analysis, design guidelines, in-depth literature review and a gain requirement comparison between Nyquist-based ADCs and DDSR. The author was the main writer of the manuscript.

### **List of Abbreviations**

4G fourth generation

ADC analog-to-digital converter

AWGN additive white guassian noise

BAW bulk acoustic wave

BB baseband

BCP blocker compression point

BER bit error rate

BNF blocker noise figure

CG common gate

CMOS complementary metal-oxide semiconductor

CS common source

CW continuous wave

DAC digital-to-analog converter

DDSR direct delta-sigma receiver

DR dynamic range

F noise factor

FD full-duplex

FDD frequency-division duplex

FDSOI fully-depleted silicon-on-insulator

I in-phase

IC integrated circuit

ICP input compression point

IDAC current output digital-to-analog converter

IF intermediate frequency

IFA intermediate frequency amplifier

IIP2 input second-order intercept point

IIP3 input third-order intercept point

LNA low-noise amplifier

LNTA low-noise transconductance amplifier

LO local oscillator

LTE long-term evolution

LTE-A long-term evolution advanced

LTI linear time invariant

LVDS low-voltage differential signaling

NF noise figure

NRZ non return to zero

NTF noise transfer function

OB out of band

OFDM orthogonal frequency division multiple access

PCB printed-circuit board

PN phase noise

Q quadrature

Qn quantization noise

QPSK quadrature phase-shift keying

RF radio frequency

S sensitivity

SAW surface acoustic wave

SDR software-defined radio

SI self interference

SNDR signal-to-noise and distortion ratio

SNR signal-to-noise ratio

TRF tuned radio-frequency receiver

TX transmitter

### **List of Symbols**

$A open dB \hspace{1cm} \textbf{required voltage gain of third-order integrator} \\$

$A_{\mathrm{vRF}}$  RF voltage gain of proposed LNA

$C_1$  feedback capacitance of proposed LNA from drain to

gate of common-gate transistor

$C_2$  feedback capacitance of proposed LNA from gate to

ground of common-gate transistor

$C_{

m F}$  third-order feedback capacitor

$C_{\mathrm{GD}}$  gate-to-drain parasitic capacitance

$C_{\rm in}$  combined input parasitic capacitance of proposed LNA

$C_{

m L}$  gyrator capacitor  $C_{

m NP}$  N-path capacitor

$C_{

m out}$  combined output parasitic capacitance of proposed LNA

$Z_{\rm COUT}$  equivalent impedance of  $C_{\rm out}$

$f_1$  first input tone frequency

$f_2$  second input tone frequency

$f_{\mathrm{BW}}$  baseband bandwidth

F<sub>i</sub> noise factor of ith stage

G<sub>i</sub> gain of ith stage

$f_{LO}$  local oscillator frequency

$f_{\rm ns}$  noise-shaping pole frequency

$f_{\rm s}$  sampling frequency

$f_z$  third-order resonance zero frequency

$gm_1$  common-gate amplifier transconductance

$gm_2$  common-source amplifier transconductance

$g_{

m m,BB}$  baseband amplifier transconductance

$g_{m,FB}$  effective transconductance of first IDAC

$Z_{\rm RF}$  impedance connected to RF side of passive mixer

$g_{

m mL}$  trasnconductance of gyrator transconductors

$G_{\mathsf{Q}}$  quantizer gain

$G_{\rm rel}$  relative gain: ratio between gate and buried-gate input

powers

$H_{\mathrm{FB}}$  transfer function from DDSR output to baseband input

$H_{\mathrm{FB,upn}}$  transfer function from DDSR output to RF input at n-th

harmonic

$H_{

m I}$  integrator transfer function

$H_{\mathbb{Q}}$  quantizer transfer function

IMD2 second-order intermodulation product

IMD3 third-order intermodulation product

k Boltzman's constant

L power loss

$P_1$  first input test signal power

$P_2$  second input test signal power

$P_{

m blocker}$  blocker power

$P_{

m buriedgate}$  input signal power at buried-gate

$P_{\rm gate}$  input signal power at gate

$P_{\mathrm{IMD3}}$  third-order intermodulation product power

$P_{\text{max}}$  maximum input power

$P_{\rm FS}$  ADC full-scale input signal power

$P_{\rm S}$  minimum sampling power of ADC

$SNR_{

m tar}$  target SNR

$Z_{IN}$  LNA input impedance

$Q_{\rm up}$  upconverted quantization noise

$R_{\rm c}$  complex feedback resistance to compensate N-path pha-

se/frequency shift

$R_{

m L}$  resistance in third-order feedback

$R_{\rm in}$  equivalent output impedance of mixer and LNA

$R_{\mathrm{obb}}$  baseband transconductor output resistance

$ro_{\mathrm{CG}}$  common-gate amplifier output resistance

$ro_{\mathrm{CS}}$  common-source amplifier output resistance

$R_{\rm oL}$  gyrator transconductor output impedance

$R_{oLNA}$  LNA output impedance

$R_{\rm S}$  source resistance

$R_{\rm SH}$  equivalent impedance representing mixer harmonic los-

ses

$R_{\rm SW}$  mixer switch resistance

$S_{11}$  input scattering parameter

slopedB desired slope of third-order integrator

$SNR_{in}$  input signal signal-to-noise ratio  $SNR_{min}$  minimum signal-to-noise ratio

SNR<sub>out</sub> output signal signal-to-noise ratio

SNR<sub>peak</sub> peak signal-to-noise ratio

T temperature

$V_{

m DSAT}$  transistor saturation voltage

$V_{\rm FS}$  upper voltage swing limit

$V_{

m out}$  output voltage

$V_{

m S}$  supply voltage

$Z_{\mathrm{BB}}$  baseband amplifier input impedance

$Z_{\text{CNP}}$  equivalent impedance of N-path capacitor  $C_{\text{NP}}$

$Z_{\rm i}$  input impedance

$Z_{

m L}$  equivalent load impedance of propose LNA

$Z_{

m NP}$  equivalent input impedance of quadrature N-path filter

from RF side

$Z_0$  source impedance

$\beta$  feedback factor of proposed LNA

$\gamma$  constant mosfet noise parameter

$\Delta \hspace{1.5cm} \text{quantization step}$

$\zeta$  frequency scaling factor in N-path LTI model

### 1. Introduction

### 1.1 Background

From the very beginning of recorded time, mankind has communicated with each other in some form or another. Over time these means of communication evolved to cope with the ever-growing demand for sending information over long distances in a fast and a reliable manner. The discovery of electromagnetic waves in the late 19th century as a mean of fast and long distance communications opened a new era of wireless communications [1,2]. Fueled by new inventions in the field on electricity, the 21st century witnessed a rapid evolution of wireless communication. Starting from the invention of the radio, right up to the development of modern fourth generation (4G) mobile phone receivers, wireless communication technology has come a long way [3]. Today's communication receivers need to operate under the presence of multiple nearby interfering signals while at the same time should be able to tune into a particular reception band. Another parallel trend that has greatly impacted the design of communication receivers has been the on-going process of electronics integration which has occurred in the past few decades. The ultimate goal is to include all needed electronics in a single integrated circuit (IC) resulting in increased speed and cheaper production costs [4]. Accelerated by the development of smaller and faster complementary metal-oxide semiconductor (CMOS) process generations that are needed to fabricate the IC's, the miniaturization trend of wireless receivers is shifting towards more digital intensive solutions. This is because the newer CMOS processes are generally more digital friendly. All these technology trends dictate that an ideal wireless receiver should be able to receive any signal frequency, while at the same time be completely integrated with no external components [5]. Such a

receiver should also be able to cope with strong interfering signals from nearby transmitters while still receiving the desired signal. Unfortunately, such a receiver does not exist in reality. Nevertheless, if we take a more practical approach to these requirements, a great deal of modern wireless receiver research focuses on making such receivers more reconfigurable, interference-tolerant, digital intensive, energy efficient and smaller [6–10].

### 1.2 Objectives of the work

The objective of this thesis is to find innovative solutions towards the goal of completely integrated, interference-tolerant and reconfigurable wideband receivers. First, the integration is required to increase the mobility, speed and reduce production costs of wireless receivers. Second, interference tolerance is needed when a single receiver covers a broad frequency range. Inevitably, such a receiver will pick up the desired signals as well as unwanted interferers from surrounding transmitters which needs to be filtered. Third, reconfigurability is a result of strong demand for a single receiver to be able to receive multiple frequency standards/bands. Such a receiver will eliminate the need for parallel receive chains, each dedicated to a specific standard/band.

### 1.3 Main scientific merits

To achieve the target objectives of this work, research was carried on both theoretical and experimental fronts. A full radio frequency (RF) receiver with two-stage harmonic rejection was fabricated and measured while, at the same time, various theoretical investigations were conducted on new innovative circuits for wireless receivers. The details of all these research outcomes are embodied in publications I-IX. The most important contributions to the scientific community are summarized below:

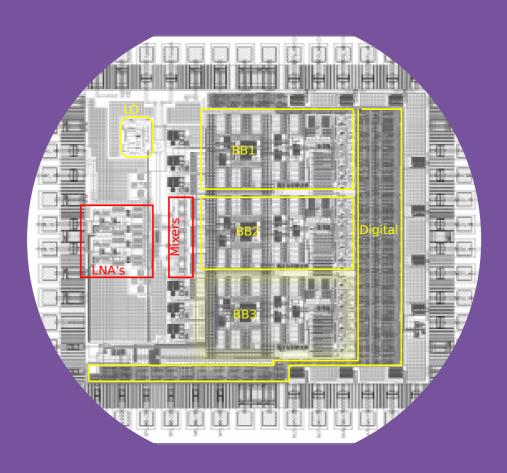

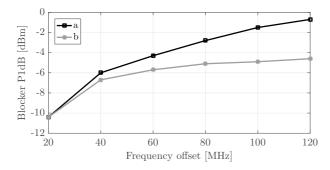

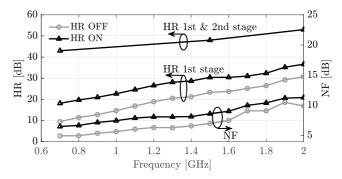

1. A two-stage blocker-tolerant harmonic-rejection receiver was fabricated and measured. The receiver also incorporated third-order N-path filtering for the suppression of near-band blockers. At the time of publication, the measurement results demonstrated impressive blocker rejection for blockers present at the third harmonic of the local-oscillator frequency. The results are detailed in publications IV and VIII.

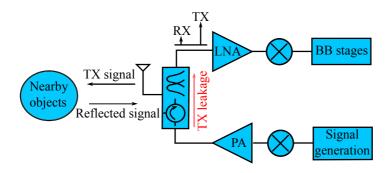

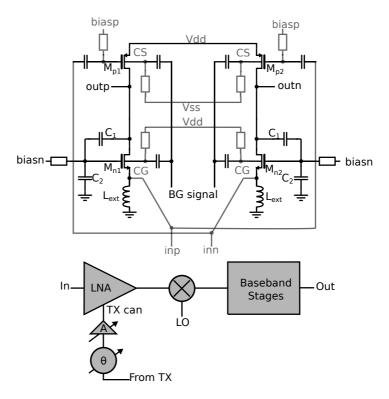

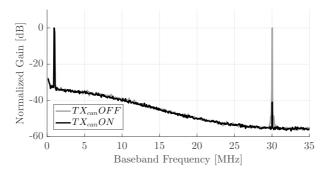

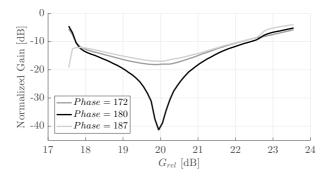

- 2. A novel approach for transmitter signal leakage cancellation was proposed through buried-gate signaling in fully-depleted silicon-on-insulator (FDSOI) technology. A test RF front-end was fabricated and measured to validate the chosen approach. Details can be found in publication III.

- 3. A capacitive feedback based LNA was proposed which achieved blocker rejection both at the input and output nodes of the LNA. Detailed theoretical analysis was carried out resulting in design guidelines. Details can be found in publication V.

- 4. A blocker rejection positive feedback DDSR was proposed and simulated. Blocker tolerance was achieved by attenuating blockers already at the input of the receiver through selective impedance matching. Details can be found in publications I,II and IX.

- Quantization noise upconversion effects in mixer-first DDSR on receiver sensitivity were analyzed. Systematic modeling of upconverted quantization noise was carried out in VI.

- 6. Design guidelines for mixer-first DDSR were formulated in VI.

- 7. A method to improve blocker rejection through the reduced gain method in DDSRs was proposed in II, IX, and VII.

### 1.4 Contents and organization of the thesis

This thesis is organized into two parts. The first part is introductory and provides an overview of the target research field with a summary of the key research findings by the author. The second part consists of a compilation of scientific publications I-IX by the author.

Chapter 2 starts with an overview of the target research field. It builds up the necessary background and technical definitions needed to understand the given research field. Once the reader is familiar with the background knowledge, it is easier to follow the research contributions by the author detailed in chapters 3 to 6.

Specifically, chapter 3 deals with new solutions for blocker-tolerant RF front-ends. Three solutions are presented here: 1) A third-order N-path

filter implementation in 28nm for near-band blocker suppression; 2) a new capacitive feedback LNA with blocker attenuation at both of its input and output nodes, and; 3) a novel transmitter leakage cancellation technique using a buried-gate in an FDSOI process.

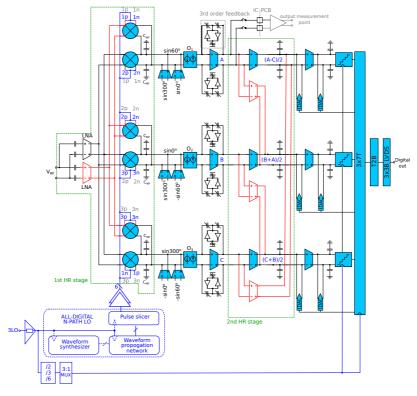

Chapter 4 presents an implementation of a 6-phase two-stage harmonic-rejection receiver in 28nm FDSOI technology. The proposed receiver uses simpler local oscillator (LO) clocking and reduced baseband paths compared to 8-phase harmonic-rejection architectures and uses simple  $\pm 1$  gain coefficients.

Chapter 5 addresses the research outcomes in the field of direct  $\Delta\Sigma$  receivers. First, a positive feedback technique from the DDSR output provides blocker attenuation at the DDSR input. Second, a reduced gain design method is proposed for blocker-tolerance in DDSRs and, third the degrading effects of quantization noise upconversion on mixer-first DDSR sensitivity are analyzed.

### 2. Wideband integrated receiver design

This chapter provides background information to the field of wireless receiver design. The aim is not to provide an in-depth description of the research field but rather an overview is given which will then serve as a basis for understanding the research outcomes in later chapters. The chapter starts with the overview of wireless communication in today's world and description of some of the widely used receiver architectures such as superheterodyne and direct-conversion receivers. This description is followed by an explanation of performance matrices for a receiver with a discussion on current and future research trends in wireless receiver design. At the end, an overview of current state-of-the-art blocker-tolerant and fully-integrated receivers is provided.

### 2.1 Overview

Imagine sitting in a room with only two people. The person who is talking is analogous to a wireless transmitter while the person listening bears a resemblance to a wireless receiver. Such a scenario is quite simple as the listing person only needs to focus his/her attention on the speaker. There are no other speaking persons in the room who can interfere with the oral communication. Therefore, the ears of the listener just need to focus on a single audio reception. On the other hand, if the same gathering would have been occupied with multiple people having a conversation, then the listener's ears will not only need to focus on the desired talking person but will also have to distinguish between strong interfering audio signals which are nearby. Today's wireless communication scenario is no different from the above analogy. Multiple wireless communications at different transmit frequencies and standards overcrowd the environment, and the wireless receiver task is to not only faithfully pick up the desired signal

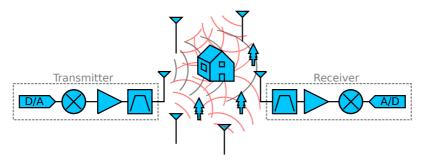

Figure 2.1. Wireless communications scenario.

but also to filter out large unwanted interferers.

Fig. 2.1 shows a simplified scenario of wireless data transmission. A transmitter does some signal processing with the transmitted signal and then radiates it through the air as electromagnetic waves from the antenna. The antenna at the receiver ends receives this electromagnetic wave and then it is the receiver's job to discriminate the desired transmitted signal from multiple other interfering signals. In this regard, the receiver should be selective in receiving the desired signal while at the same time filtering out the non-desired interferers. The receiver should also be highly sensitive to receive weak electromagnetic signals attenuated by environmental effects and obstacles. Such requirements are challenging to implement due to rapidly increasing wireless communications standards and frequency bands. Nonetheless, a few widely implemented receiver architectures which have partially served these requirements will be highlighted next.

#### 2.2 Major receiver architectures

The following section covers some of the major wireless receiver architectures. The discussion is not meant to provide an exhaustive study. Rather, a brief overview is given which is intended to familiarize the reader with the most widely used implementations. This serves as a basis for understanding the research outcomes from the author in the later chapters. For detailed reading on receiver architectures, the reader may please refer to previous works from the author's research group [11–13].

In the beginning of wireless communications, radio receivers were just a detector connected directly to the antenna [14,15]. Further improvements were achieved with a tuned radio-frequency receiver (TRF) which was composed of one or more tuned radio frequency amplifier stages followed

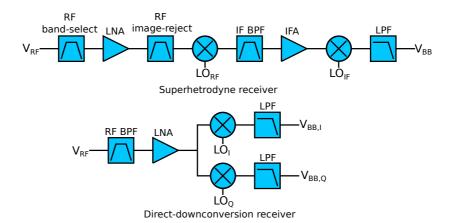

Figure 2.2. Basic block diagram of superheterodyne and direct-downconversion receivers.

by a detector. TRFs however had the drawback of tedious operation when tuning to a different station. Each receiver stage had to be individually adjusted to the station frequency.

The tuning problems related to TRF receivers were solved by the development of a revolutionary receiver architecture called the superheterodyne [16, 17]. Developed in the early 20th century by Armstrong, the superheterodyne receiver has been one of the most widely manufactured receivers to date. Fig 2.2 shows the block diagram of a superheterodyne receiver. An input signal from the antenna first passes through an RF band-select filter followed by an LNA which amplifies it. The amplified signal is then passed through an image-reject bandpass filter, a downconverting mixer to convert the RF signal to lower intermediate frequency (IF), an IF bandpass filter, and an IF amplifier. In some modified superheterodyne architectures, an additional downconverting mixer can also be used after the intermediate frequency amplifier (IFA) to relax an inherent compromise between channel-selection and image-rejection [18].

The advantages of the superheterodyne architecture are many, one of the distinct advantages being the ease of circuit design for lower IF signals in comparison to RF circuits. Downconversion to low IF also makes it possible to implement high-quality sharp filters as they are easier to implement at lower frequencies. These advantages of the superheterodyne architecture led to it becoming the commercial receiver architecture of choice for several decades. However, despite the advantages, the superheterodyne architecture has some serious problems with regard to image-rejection and integrability. The problem of integrability arises due to limitations in implementing high-quality RF bandpass filters on ICs. The need for com-

pletely integrated receivers has become even more critical with the advent of mobile cellular radio systems. Users desire every new generation of mobile receivers to be smaller yet still packed with more and more demanding functions. In addition, integration brings additional benefits of less expensive and mass-marketable user equipment. Towards this end, some major attempts to provide image-rejection without high-quality bandpass filters are the Hartley and Weaver image-rejection receivers [19–21]. Additionally, some recent attempts to implement fully-integrated superheterodyne receivers with discrete-time filtering have been reported in [22–25], while in [26] a superheterodyne receiver with an integrated high-Q bandpass filter has been presented.

Another receiver architecture which emerged as an integration-friendly alternative to the superheterodyne is known as a direct conversion or homodyne receiver architecture [18,27,28]. The block diagram of a typical direct-conversion receiver is shown in Fig. 2.2. An RF bandpass filter attenuates the out-of-band interferers received at the antenna. An LNA then amplifies the filtered signal which is directly down-converted to zero-IF frequency through passive mixers. The mixer and post-mixer circuits are divided into an in-phase (I) and quadrature (Q) branches with 90° phase difference. The quadrature downconversion prevents the self-corruption of downconverted spectrum for asymmetrically-modulated signals [18]. These I and Q signals are then digitized for further processing.

Downconversion to zero-IF frequency has multiple advantages. First, zero-IF downconversion eliminates the problem of image frequency as is present in superheterodyne receivers. This means that the image-rejection filter can be eliminated which would otherwise have to be implemented with non-integrated components. Further, the post-mixer IF filter is replaced from a bandpass filter to a low-pass filter which is also more straightforward to implement on IC. Therefore, apart from the first band-select filter before the LNA, all other circuits can be easily integrated on-chip.

The main benefit of integrability is counterbalanced by several problems inherent to the direct-conversion receiver [11, 18, 29]. Some of the most important ones can be mentioned as: dc offsets generated by LO frequency leakage to an antenna, flicker noise effects, and second-order intermodulation effects.

The first problem of dc-offsets can be quite severe in the direct-conversion receiver. These offsets are generated by LO signal leakage to the antenna. The leaked LO signal will then self-mix with the LO and downconvert

to dc at the input of the baseband chain. As the baseband amplifier as generally an active structure, any dc offsets present at their input when amplified with baseband gain can overload the baseband amplifiers and, consequently, the analog-to-digital converter (ADC) converter that follows it. Second, flicker noise is a type of noise exhibited by the transistors at very low frequencies. It decreases with a slope of 10dB/decade with increasing frequencies and eventually falls lower than the thermal noise level of the transistors. This noise can potentially reduce the sensitivity of the direct-conversion receiver for the lowest frequency contents of the desired signal. Finally, the second-order intermodulation products created by the interferers present at the input of the receiver can appear in the downconverted baseband signal by the direct-feedthrough of the mixers, therefore, desensitizing the receiver [30].

From the above discussion it is evident that neither the superheterodyne nor direct-conversion receiver is a clear winner over the other in terms of performance. Each architecture has its advantages and disadvantages. Nevertheless, the clear advantage of integrability has led to the wide-spread adoption of the direct-conversion receiver in recent years though attempts for a superheterodyne comeback have been made [22–26, 31]. Superheterodyne architecture also seems to be a more reasonable choice in millimeter-wave frequencies due to practical limitations in high-frequency quadrature local-oscillator signal generation [32–34].

In which direction is the design of wireless receiver likely to head? An attempt to answer this question requires a more thorough understanding of receiver performance parameters. In the following section, the essential performance matrix related to a wireless receiver is explained briefly. Once the reader is more familiar with this matrix, it becomes easier to attempt an explanation for current and future research trends of wireless receivers.

#### 2.3 Performance requirements

### 2.3.1 Input impedance matching

Input impedance matching is an important requirement at the antenna receiver interface. The need for impedance matching arises in order to prevent the signal reflecting from the receiver input. Signal reflections can occur if the distance between the source and load is larger than  $\lambda/4$  [35].

Here  $\lambda$  is the wavelength of the signal in question, at 5GHz and for a substrate permittivity of 4, this distance becomes 7.5mm which is easily comparable to the printed-circuit board (PCB) dimensions.

The level of input matching is usually quantified in terms of scattering parameter  $S_{11}$  which tells how well the input impedance  $Z_i$  is matched with the reference source impedance  $Z_0$  [36].

$$S_{11} = \frac{Z_i - Z_o}{Z_i + Z_o} \tag{2.1}$$

In the design process,  $S_{11}$  is usually targeted to be < -10dB at the receiver input interface. From  $S_{11}$ , the power loss L due to impedance mismatch can be defined as

$$L = 10log(1 - |S_{11}|^2) (2.2)$$

### 2.3.2 Sensitivity and noise performance

The sensitivity (S) of the receiver is defined by the minimum signal level that can be detected by the receiver with a sufficiently low bit error rate (BER). For a proper reception, the signal received at the receiver input should be sufficiently higher than the integrated noise of the receiver. In other words, this means that there is a minimum signal-to-noise ratio  $SNR_{min}$  requirement which will ensure sufficiently low BER. The exact value of  $SNR_{min}$  is dependent on the used modulation scheme and is generally fixed for a given communication standard. Therefore, if we want to increase receiver sensitivity, then the receiver itself should ideally add no additional noise inside the reception band. In reality, however, every receiver will add some noise on top of the integrated thermal noise of the receiver, consequently decreasing the signal-to-noise ratio (SNR) at the output of the receiver.

The deterioration of receiver SNR is quantified by the noise factor (F) or noise figure (NF) given by:

$$F = \frac{SNR_{IN}}{SNR_{OUT}} = 1 + \frac{\overline{e_{out}^2}}{4kTR_S(\frac{V_{out}}{V_S})^2},$$

(2.3)

$$NF = 10log(F) \tag{2.4}$$

where k is the Boltzmann constant, T is the temperature in Kelvin,  $R_{\rm S}$  is the source resistance,  $V_{\rm out}$  and  $V_{\rm S}$  are the output and source voltages,

$SNR_{in}$  and  $SNR_{out}$  are the signal-to-noise ratios at the input and output, and  $\overline{e_{out}^2}$  is the output noise power density.

Generally, for a given communication standard, sensitivity and  $SNR_{min}$  are predefined. The designer need to then calculate the target NF of the receiver from these specs as:

$$NF = 174dBm - 10log(f_{BW}) - SNR_{min} + S$$

(2.5)

where  $f_{\rm BW}$  is the receiver baseband bandwidth. An example of such a calculation can be given for the long-term evolution (LTE) communication standard. The LTE standard occupies a majority of its frequency bands ranging from 700MHz to 2700MHz with the channel-bandwidths from 1.4 to 20MHz. If we take 20MHz channel bandwidth as an example, then the LTE specifications [37] define a target sensitivity between -94dBm and -90dBm. This level of input power should be able sustain data throughput with a maximum BER of 5%. The BER can be linked to SNR<sub>min</sub> for a given modulation scheme. For example, LTE uses orthogonal frequency division multiple access (OFDM) as a modulation scheme and for OFDM with quadrature phase-shift keying (QPSK) and additive white guassian noise (AWGN) channel, 5% BER relates to a minimum theoretical SNR<sub>min</sub> of 6dB [38,39]. For these specifications, the required NF of the receiver from Eq. 2.5 results in 4dB for a sensitivity level of -94dBm.

The overall NF of the receiver is a result of noise contribution from each receiver stage. Typically, gain is applied in the first stage of the receiver to reduce the noise contribution of later stages. In the presence of gain, the contribution of noise from later stages on overall receiver NF is characterized by the Friss equation given by [18]:

$$F_{RX} = F_1 + \frac{F_2 - 1}{G_1} + \frac{F_3 - 1}{G_2} + \dots$$

(2.6)

where the  $F_i$  is the noise factor on ith stage while  $G_i$  represents the power gain of each stage.

#### 2.3.3 Blocker noise figure and reciprocal mixing

The NF of the receiver, when it is exposed to a strong blocker signal of a given power  $P_{\rm blocker}$  is known as the blocker noise figure (BNF). The BNF is generally higher than NF for two reasons. First, due to reciprocal mixing and second due to 2nd and 3rd-order non-linearities [40].

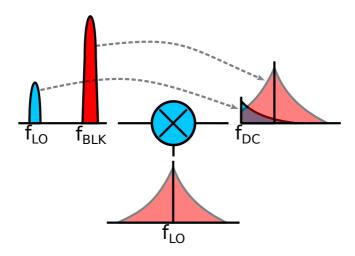

Reciprocal mixing is a phenomena when a high power blocker gets do-

**Figure 2.3.** Reciprocal mixing with the blocker signal causing LO phase noise to appear inside the desired channel.

wnconverted with a noisy local-oscillator LO source to increase the NF of the receiver. Fig. 2.3 explains the reciprocal mixing where the phase noise (PN) of an LO signal mixes with the blocker and falls inside the desired band. This increases the in-band noise of the receiver. In order minimize the impact of blocker on receiver NF, the local-oscillator PN should be lower than integrated thermal noise floor of receiver. Analytically PN can be calculated as [41]:

$$PN + 10log(f_{BW}) + P_{blocker} < S - SNR_{min}$$

(2.7)

where  $P_{blocker}$  is the blocker input power. For example, for LTE specifications of S=-94dBm,  $SNR_{min}=6dB$ ,  $f_{BW}=10MHz$  and  $P_{blocker}=-15dBm$  at an 85MHz offset, one can derive the target LO phase-noise lower than -155dBc/Hz at the 85MHz offset.

### 2.3.4 Linearity: Intermodulation

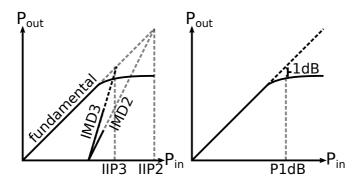

The non-linear relationship between the output and input of a transistor gives rise of intermodulation products in the output spectrum. These products can cause problems in the reception of a weak desired signal and, therefore, targeted to be much lower than the thermal noise floor of the receiver. The level of these intermodulation products is defined mainly by input third-order intercept point (IIP3) and input second-order intercept point (IIP2) small signal matrices. These are obtained by exposing the

receiver input to two RF tones at  $f_1$  and  $f_2$ . These frequencies will result in intermodulation products at  $2f_1$ - $f_2$ ,  $2f_2$ - $f_1$  and  $|f_1 \pm f_2|$ . The first two terms are used to define the third-order intermodulation product while the last term refers to the second-order intermodulation product.

When the input test signal power increases, these intermodulation products increase with the slope of three and two in comparison to the fundamental signal power. The values of IIP3 and IIP2 can then be calculated by extrapolating the slopes of the fundamental as well as second and third intermodulation products. The fictitious point where these slopes meet defines the IIP3 and IIP2 as shown in Fig. 2.4. These parameters can also be derived through calculations as:

$$IIP3 = P_1 + \frac{P_2}{2} - \frac{1}{2}(P_{IMD3} - G),$$

(2.8)

$$IIP2 = P_1 + P_2 - (P_{IMD2} - G), (2.9)$$

where  $P_1$  and  $P_2$  are the test signal powers in dBm at the input, IMD3 is the third order intermodulation product in dBm, IMD2 is the second order intermodulation product in dBm, and G is the small-signal gain of the system at the frequency of the intermodulation product.

IIP3 and IIP2 specifications become more critical in certain reception scenarios. For instance, one difficult scenario where IIP3 needs to be high is when a strong signal  $f_1$  is located between the received signal and transmitter signal  $f_2$ . This will generate third-order intermodulation tone at  $2f_1$ - $f_2$ , i.e., on top of the down-converted desired signal. Another example case when IIP2 specifications need to be high can be given for a frequency-division duplex (FDD) system. In FDD systems, transmission and reception occur at same the time creating a problem of high transmitter (TX) signal leakage at the receiver input. This TX signal will cause second order distortion at the receiver output due to the intermodulation of the TX signal with itself. The generated second-order distortion may fall in the desired channel and degrade receiver sensitivity [42].

An example of deriving the receiver IIP3 specification for a communication standard, can be given for LTE specifications [37]. The standard specifies a maximum in-band input power  $P_{\rm max}$  of -25dBm while a blocker of -15dBm can be tolerated at a 85MHz offset from the desired channel. Further, the required peak SNR for most of the modulation schemes is below 30dB [43]. Assuming a required 40dB SNR<sub>peak</sub> for safety margin, the target IIP3 value of the receiver can be calculated by making sure

Figure 2.4. Linearity measures: IIP2, IIP3 and P1dB.

$P_{\rm IMD3}$  remains below the thermal noise floor. For such a case minimum IIP3 can be calculated as:

$$IIP3 = P_{max} + \frac{SNR_{peak}}{2} = -5dBm \tag{2.10}$$

Similarly, for an out-of-band maximum blocker power of -15dBm, the out-of-band IIP3 can be derived as +5dBm.

#### 2.3.5 Linearity: Compression

When the test input signal power of the receiver increases, the output power stops increasing beyond a certain point. This is called compression, and the matrix that defines the receiver compression behavior is called the compression point. An input compression point (ICP) can be defined as the input test signal power at which the output power drops 1dB below its nominal value determined by small-signal gain. In contrast to IIP3 and IIP2 matrices, the ICP is a large-signal matrix because the input test signal power is high. The ICP can be defined for both an in-channel or out-of-channel signal. The latter is usually referred to as the blocker compression point (BCP).

The BCP is more interesting, in a wideband receiver scenario because it dictates how well the receiver is able to amplify a weak signal under the presence of a strong out-of-channel blocker. These blockers can either be from the device own transmitter or from the transmitters of other coexisting devices. These can also be from other standards in the same device. For example, coexistence of WiFi, Bluetooth and LTE transceivers in the same device [44, 45].

#### 2.4 Research trends: From present to future

As detailed earlier, today's wireless receivers need to operate over a wide frequency range while covering multiple communication standards. The majority of the wireless receivers achieve this task by implementing parallel front-end paths each tuned to a particular reception band/standard. Obviously, this is not an optimum solution due to an increased number of components leading to higher production costs and complexity. What is ideally needed is a single wideband receiver which should be able to receive all reception bands/standards with the possibility of instant software reconfigurability. On top of it, the receiver should be completely integrated with no off-chip components to gain advantages of mobility and lower manufacturing costs. The ultimate goal of further receiver development is encapsulated by the concept of software-defined radio (SDR) [5, 46].

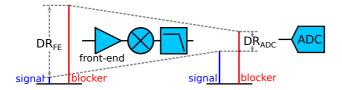

An attractive way to implement the SDR paradigm is an RF-to-digital converter implementation where an ADC is directly connected to a wideband antenna to immediately digitize the received signal [47]. Once the signal is in the digital domain, all functions of programmability can be attained by utilizing the inherent advantages of digital technology. However, such an RF-to-digital converter will be exposed to various high power interferers leading to very high dynamic range (DR) requirements of up to 100dB [48,49]. Moreover, the reception frequencies in the GHz range require high GHz sampling frequencies of the ADC. Both the dynamic range and higher sampling frequency requirements of the needed ADC lead to highly impractical power consumption requirements from the ADC. For example, according to [50], the minimum sampling power  $P_{\rm S}$  required by the ADC is given as:

$$P_S = 48kT f_s 2^{2N} (2.11)$$

where N is the number of bits and  $f_s$  is the ADC sampling frequency. [50] shows that the high speed Nyquist ADCs still burn 50-100 times more than the above limit. As a practical example, a reception frequency of 1.5GHz ( $f_s = 3 \text{GHz}$ ) and N = 13bits will lead to  $P_S$  of at least 2W.

Some emerging ADC architectures such as band-pass continuous-time  $\Delta\Sigma$  ADC's have tried to address the problem of high power consumption. The reported band-pass  $\Delta\Sigma$  ADC center frequencies extend up to a few GHz, with power consumption ranging from 40mW to 1600mW and dynamic ranges up to 73dB [51–56]. These specifications lie within the desired

Figure 2.5. Conceptual representation of reduction in ADC dynamic range from the frontend.

range for many GHz communication standards. However, the estimated NF of such structures is quite high ranging from 20 to 40dB. Moreover, most of the band-pass  $\Delta\Sigma$  ADCs are implemented with bulky on-chip inductors which makes it difficult to attain a wide tuning range.

The limitations mentioned above have so far prevented the practical implementation of complete RF-to-digital converters in the GHz range even though the SDRs in MHz range have been reported [57]. Rather, the SDR research has changed its direction towards the goal of trying to come up with solutions that serve the objective of reconfigurability, complete integration, and digital intensive receiver architectures. Towards this end, one promising digital-intensive architecture is the direct  $\Delta\Sigma$  receiver DDSR [58–60]. Chapter 5 of this thesis will discuss the DDSR in little more detail.

To achieve the above mentioned goals, today's practical SDR implementations consist of an analog front-end between the antenna and the ADC [9, 10, 61]. The purpose is to relax the required specifications of ADC. This is done by front-end through amplification, downconversion and filtering. Amplification increase the signal and noise level at the input of the ADC so that it requires a lower number of bits; and downconversion brings the received signal to lower frequencies so that a lower sampling rate is required from the ADC. Finally, filtering of unwanted signals reduces the dynamic range requirements of the ADC. The reduction of ADC dyamic range requirements is visually presented in Fig. 2.5. Consequently, a typical RF front-end proceeding the ADC consists of a low-noise amplifier (LNA), downconversion mixer and baseband filtering stages. Further, it is intended that these analog front-end circuits are designed with as much digitally assisted reconfigurability as possible. This aims at the target of completely digital solutions, one step at a time, taking advantage of every new generation of digital friendly CMOS technology. At the same time, fully integrated solutions that focus on reducing the number of parallel receiver paths are desired [62-65].

Covering the details of all the research targets for RF-to-digital converters is quite broad in nature and is not within the scope of this thesis. Rather, a narrower research field is chosen, targeted towards completely integrated blocker-resilient receivers with the exception of one publication which focuses on sensitivity requirements in the mixer-first direct  $\Delta\Sigma$  receivers. In following section an overview of current blocker-resilient receiver solutions will be presented. Again, this is not meant to be a comprehensive summary but rather serving to introduce the research field to the reader.

#### 2.5 Blocker-tolerant receivers

Blocker-tolerance is needed in wireless receivers because high power blockers can cause input and output compression of active devices in the receive chain. Even if these blockers are weak, they can cause intermodulation products due to the non-linear transfer characteristics of active devices thus reducing the sensitivity of a receiver. To overcome this, receivers incorporate filtering which is mostly off-chip as it is difficult to create completely integrated high-quality bandpass filters. However, poor tunability of off-chip filters has led to the development of various on-chip filtering solutions.

One such widely studied on-chip filtering solution is N-path filtering [66,67]. The technique offers moderate quality factors with wide tunability as the center frequency of the filter can be altered by changing the LO frequency. Over the years, various N-path filtering architectures have been implemented in different configurations. For example, [59, 68–71] use N-path filtering at the output of the LNA, [72–75] implement N-path filtering in the feedback path and [76,77] show examples of N-path filtering in the feedforward path. These N-path implementations in general have certain limitations. First, the blocker filtering is limited by the mixer switch resistance which cannot be reduced indefinitely due to excessive LO power consumption. Second, N-path filtering downconverts signals present at the LO harmonics as well. To solve the second problem, various harmonic rejection N-path filtering techniques have been proposed [78–83]. However, these techniques implement harmonic rejection with a higher number of paths leading to increased area and LO power consumption. Moreover, harmonic rejection is usually implemented later in the receiver chain when gain has already been applied.

Another useful blocker-tolerant topology is a mixer-first architecture

[80,84–87]. Mixer-first architecture achieves this resilience by completely eliminating active RF stages which are one of the main sources of receiver non-linearity. Some recent mixer-first implementations have demonstrated excellent linearity specs with an out of band (OB) IIP3 and BCP between 39-44dBm and 12-13dBm respectively [85,88]. However, as always there are some limitations. Mixer-first receivers require the first baseband amplifier to be low-noise which leads to higher current consumption in the first baseband stage. Additionally, mixer-first receivers suffer from down-conversion of the input signal around the LO harmonic and LO leakage at the RF nodes.

The LO leakage problem in a mixer-first receiver can be solved by implementing a low-noise low-noise transconductance amplifier (LNTA) [89–93]. The output of a LNTA is in the current domain thereby reducing the voltage swings at the output of an LNTA. This means that high power blockers will not be able to compress the LNTA output due to reduced voltage swings. The current signal produced by the LNTA is converted to voltage after downconversion where filtering is more easy to achieve. LNTA operation requires huge mixer switches to reduce voltage swings at the output of the LNTA. In addition, the lack of RF gain necessitates that the first baseband amplifier needs to be quite low noise. Both of these issues lead to increased power consumption in LNTA-based receivers. Table 2.1 presents performance comparison of some recent blocker tolerant wideband receivers.

For cases when the blocker frequency is known, some works have proposed an N-path notch filter response at the blocker frequencies [10,94–96]. Other works [97–102] create a 180° version of the blocker signal and sum this with the received input for blocker cancellation. This kind of cancellation is generally implemented for transmitter signal leakage with a phase and frequency which are known a priori.

Table 2.1. Performance comparison of recent blocker-resilient receives.

| Reference        | Architecture | Architecture Frequency [GHz] | $f_{ m BW}  [{ m MHz}]$ | $\mathrm{BCP}\left[\mathrm{dBm}\right]$ | BNF [dB]                        | OB IIP3 [dBm]                        | NF [dB]      | Gain         | Process                         |

|------------------|--------------|------------------------------|-------------------------|-----------------------------------------|---------------------------------|--------------------------------------|--------------|--------------|---------------------------------|

| RFIC'17 [85]     | Mixer first  | 0.2 to 8                     | 20                      | $12@4f_{\rm BW}$                        | 4.7@0  m dBm                    | $39@4f_{\rm BW}$                     | 2.3 to 5.4   | 21           | 45nm SOI                        |

| ISSCC'17 [88]    | Mixer first  | 0.1 to 2                     | 13                      | $13@6.15f_{\rm BW}$                     | 6 to 8@0dBm                     | $44@6.15f_{\rm BW}$                  | 6.3          | 16           | 28nm                            |

| JSSC'12 [103]    | Mixer first  | 0.08  to  2.7                | 4                       | $-2@20f_{ m BW}$                        | 4.1@0 dBm                       | $13.5@20f_{\rm BW}$                  | 1.9          | 72           | 40nm                            |

| ISSCC'15 [104]   | Mixer first  | 0.1  to  1.5                 | 23                      | $-6@20f_{\rm BW}$                       | $13.5@0 \mathrm{dBm}$           | $13.5@20f_{\rm BW}$                  | 1.5  to  2.9 | 37           | 65nm                            |

| $JSSC'15\ [105]$ | Mixer first  | 0.1 to 3.3                   |                         | -6 to -2.5                              | $5 	ext{ to } 13@0 	ext{dBm}$   | 10 to 11.5                           | 1.7 to 3     |              | 28nm                            |

| ESSCIRC'18 [83]  | LNA~first    | 0.7  to  1.4                 | 10                      | $-8.5$ to $10.5~@10f_{\mathrm{BW}}$     | $5.8 	ext{ to } 8.1$ @- $9$ dBm | $1~\mathrm{to}~20.5@10f_\mathrm{BW}$ | 1.5 to 15.5  | 20.8 to 36.8 | 65nm                            |

| JSSC'18 [96]     | LNA first    | 0.7 to 1                     |                         | 9 to 12                                 | 9 to 12                         | 26.7  to  35.1                       | 8.7 to 11.7  | 1.1  to  5.5 | 65nm                            |

| JSSC'14 [106]    | LNA first    | 0.4 to 6                     | 0.5 to $50$             | -13 to -9                               | 10  to  14@0 dBm                | 3 to 8                               | 1.8 to 3.1   | 58 to 70     | 28nm                            |

| JSSC'11 [107]    | LNA first    | 0.4  to  0.9                 |                         | >-8@20MHz                               | $10 	ext{ to } 12@-4 	ext{dBm}$ | $10@20 \mathrm{MHz}$                 | က            | 70           | 40nm                            |

| JSSC'14 [108]    | LNA first    | 0.05  to  2.5                | 0.35 to 20              | 1                                       | 5.1@0  m dBm                    | 10                                   | 2.9          | 38           | 65nm                            |

| JSSC'18 [81]     | LNA first    | $0.2 	ext{ to } 1$           |                         | -2.4                                    | 1                               | 6                                    | 5.4 to 6     | 36           | 65nm                            |

| ISSCC'15 [10]    | LNTA first   | $0.5 	ext{ to } 3$           | 0 to 100                | 1-                                      | 1                               | 10                                   | 3.8 to 4.8   | 20 to 50     | $65 \mathrm{nm} \; \mathrm{LP}$ |

| ISSCC'13 [90]    | LNTA first   | 1.8  to  2.1                 | ı                       | $-1.5@20 \mathrm{MHz}$ offset           | 1                               | >16                                  | 1.9 to 2.7   | 44.5 to 45.5 | 40nm                            |

| ISSCC'14 [109]   | LNTA first   | 0.3 to 1.7                   | 2 to 76                 | >2 offset                               | •                               | 12 to 33                             | 4.2          | 19 to 34     | 65nm                            |

All of the above-mentioned blocker-tolerant techniques have limitations, making no single technique a clear winner in terms of performance. The following chapters will cover some of the author's contributions in an attempt to solve the current limitations of the above blocker-tolerant techniques. Specifically, the discussion will be devoted to the following research targets: 1) To create higher-order on-chip N-path filtering for near-band blocker suppression; 2) To create simpler harmonic rejection N-path filtering which achieves harmonic rejection with a reduced number of paths and simple gain coefficients; 3) To attain blocker rejection as early as possible in the receiver chain as implementing blocker rejection later in the chain may already increase the non-linearity of the beginning stages of receiver, and; 4) To achieve transmitter leakage cancellation without adding any additional noisy circuitry at the receiver input. One exception to the above-mentioned targets of blocker resilience is the work in publication VI which addresses the sensitivity issues in the mixer-first direct  $\Delta\Sigma$  receivers.

## 3. Blocker-tolerant RF front-ends

#### 3.1 Overview

The widespread deployment of new communication standards and frequency bands in recent decades has resulted in the increased demand for blocker-resilient wireless receivers. This is because the communication receivers of today not only receive the desired signals but also the interfering high power blockers from nearby transmitters. One widely used technique to attenuate these high power blockers is to use pre-select bandpass filters which are implemented with either surface acoustic wave (SAW) or bulk acoustic wave (BAW) technologies [110, 111]. However, filters based on these technologies are difficult to implement on chip, and their lack of tunability has so far prevented completely integrated and tunable solutions. Rather what is done is to use multiple off-chip band-select filters to cover various communication standards/frequencies [49, 112, 113]. Obviously, this is not an efficient solution. Therefore, in order to eliminate or alleviate the performance requirements of these filters, on-chip filtering techniques need to be adopted. This chapter will focus on two on-chip blocker filtering techniques proposed by the author. The first one deals with implementing a 3rd-order tunable on-chip bandpass filter for near-band blocker suppression while the second one is related to provide blocker filtering at the LNA input interface. The presented research outcomes of these two techniques are based on publications IV, V, and VIII.

High power interfering blockers can also arise from a transmitter present on the same IC. This transmitter signal leaking to the receiver input is also known as self-interference (SI). This chapter also covers a novel self-interference cancellation technique through buried-gate signaling in a fully-depleted silicon-on-insulator FDSOI process. The key measurement

results from publication III which validate the proposed approach are presented.

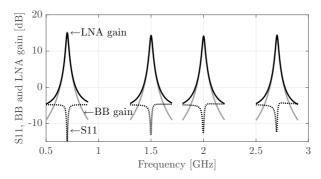

### 3.2 Third-order on-chip filtering

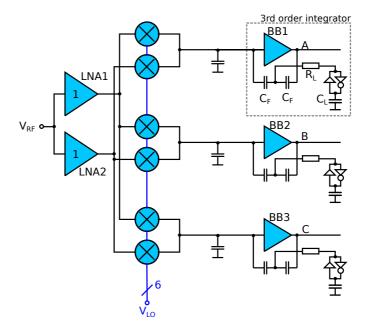

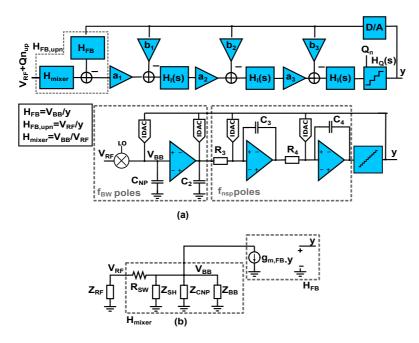

N-path filtering is one widely studied on-chip filtering techniques [66, 67, 73]. The technique offers widely tunable on-chip filtering with moderate quality factors. However, the majority of N-path implementations in today's receivers provide only a first-order filtering response at RF nodes [67,73,79–83,105,114]. This limits the amount of attenuation for near-band blockers. To increase the attenuation of near-band blockers, a 3rd-order baseband integrator is proposed here which acts in conjunction with N-path passive mixers. As a result, a 3rd-order filtering response is created at RF nodes which can be tuned to the desired frequency by changing mixer local-oscillator frequency.

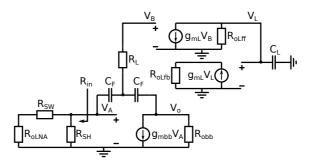

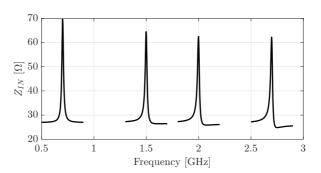

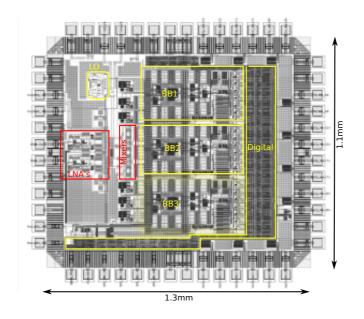

The proposed 3rd-order N-path filtering was fabricated and measured in a 28nm FDSOI process as a part of a harmonic-rejection RF frontend. The output from the 3rd-order integrator was routed outside the IC where it was measured through an external opamp buffer. Figure 3.1 shows the implemented 3rd-order integrator with harmonic-rejection N-path filtering. The response is created by a 3rd-order impedance in the integrator feedback path that is comprised of capacitors  $C_{\rm F}$ ,  $R_{\rm L}$ , gyrator transconductors, and  $C_{\rm L}$ .

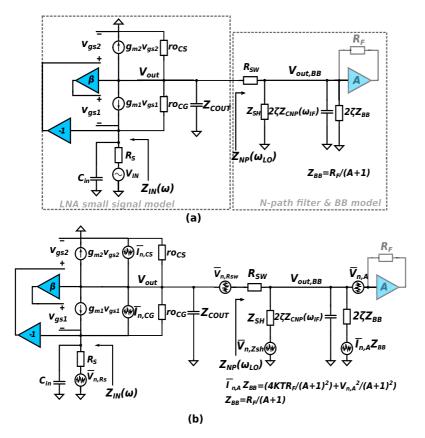

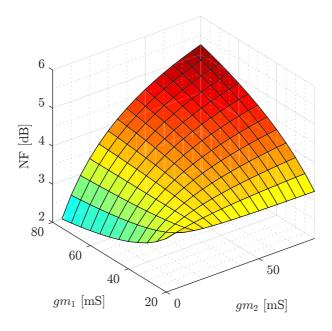

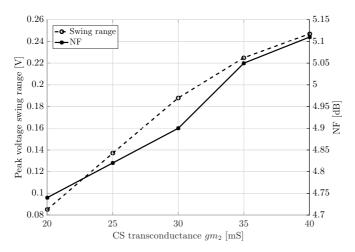

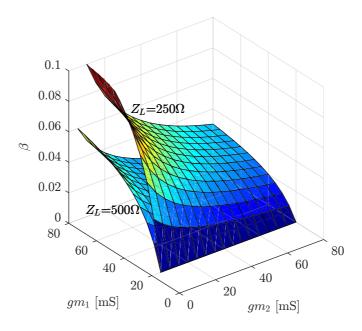

In order to calculate the desired values of the circuit parameters  $C_{\rm F}$ ,  $C_{\rm L}$ , and  $R_{\rm L}$ , a small-signal equivalent model can be used. Figure 3.2 shows the small-signal equivalent model of the proposed 3rd-order integrator together with the linear time invariant (LTI) passive mixer model [84]. The exact analysis of this small-signal model results in a complicated 3rd-order transfer function. Such a transfer function does not lead to any intuitive design guidelines. Therefore, an approximate approach, inferred from the pole-zero analysis of the exact transfer function in Matlab, was taken.

The pole-zero analysis of the 3rd-order exact transfer function reveals that the 3rd-order response is mainly due to one real and two complex poles. There is also an additional zero pair in the system whose proximity with complex poles affects the response as well. To attain the desired response, the poles should be selected at the required baseband bandwidth  $f_{\rm BW}$ . By selecting a real pole at  $f_{\rm BW}$ , the approximate value of  $C_{\rm F}$  can be

Figure 3.1. Implemented 3rd-order integrator with N-path filtering.

Figure 3.2. Small signal model of 3rd-order integrator and N-path filter.

calculated as:

$$C_F \approx \frac{1}{\pi f_{bw}(R_{obb} + R_{in})},\tag{3.1}$$

where  $R_{\rm obb}$  represents the baseband transconductor output resistance and  $R_{\rm in}$  represents the equivalent output impedance of the mixer and LNA, as shown in Figure 3.2, given as:

$$R_{in} = \frac{R_{SH}(R_{oLNA} + R_{SW})}{R_{oLNA} + R_{SW} + R_{SH})},$$

(3.2)

where  $R_{\rm SH}$  represents the power lost due to upconversion by the harmonics of the LO.  $R_{\rm SH}$  can be derived for our proposed 6-phase harmonic rejection

mixers as  $R_{SH} = 2.65(R_{SW} + R_{LNA})$  [84].

Similarly, by selecting the complex pole pair at  $f_{\rm BW}$ , the  $C_{\rm L}$  value can be calculated. However, finding an exact equation for a complex pole pair is not straightforward. Therefore, we use an indirect method by tuning the complex pole-pair frequency to  $f_{\rm BW}$  by controlling the integrator complex zero pair frequency. As these pole and zero pair frequencies lie in close proximity, changing one will also modify the other with reasonable accuracy. The complex zero pair frequency can be derived as:

$$f_z = \frac{1}{2\pi\sqrt{2C_F C_L/g_{mL}^2}}. (3.3)$$

The integrator will only be able to maintain a 3rd-order slope in the frequency range located before its unity gain frequency. Therefore, if we place  $f_{\rm z}$  around the integrator unity gain frequency then the position of the complex pole pair can be adjusted to the required  $f_{\rm BW}$  by changing  $f_{\rm z}$ . For such a case, the value of  $C_{\rm L}$  can be approximated as:

$$C_L \approx \frac{g_{mL}^2}{8C_f(\pi f_{BW}(2AopendB/slopedB))^2},$$

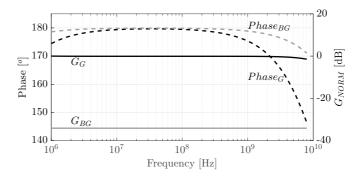

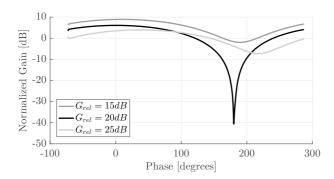

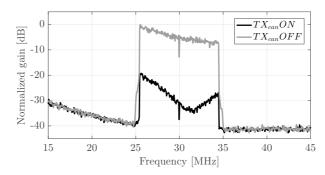

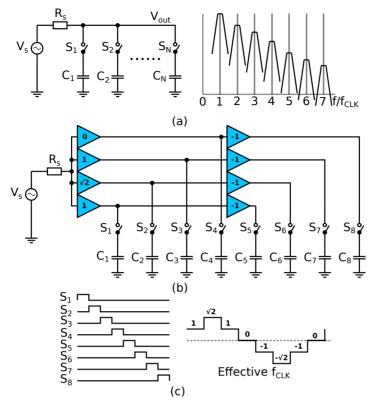

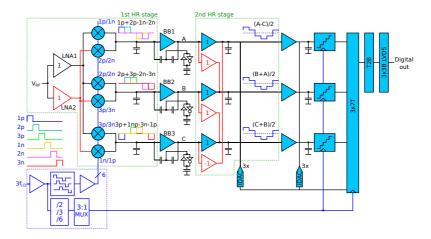

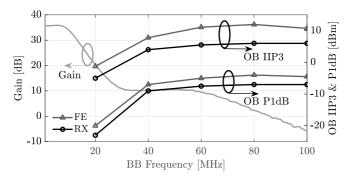

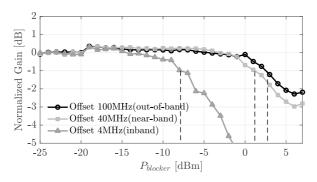

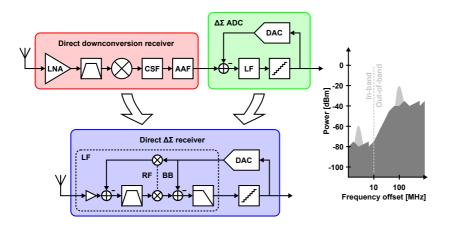

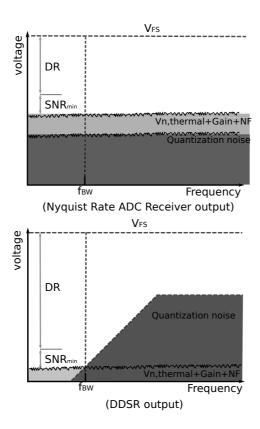

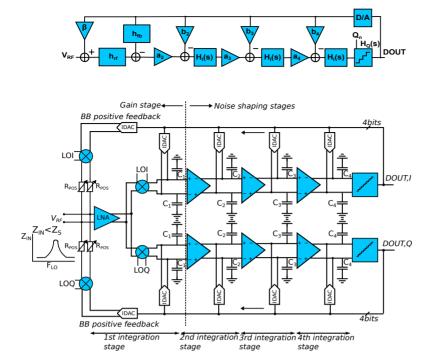

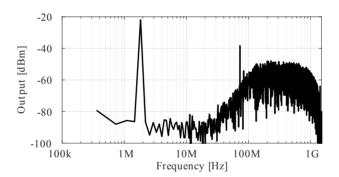

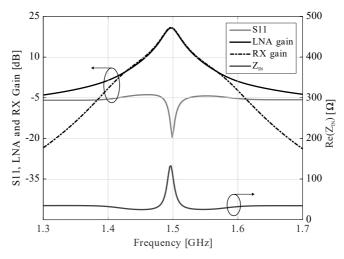

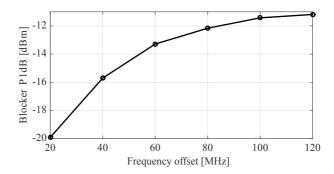

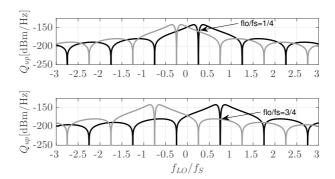

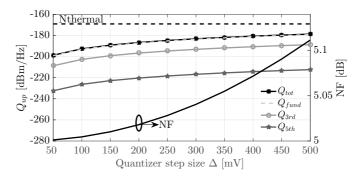

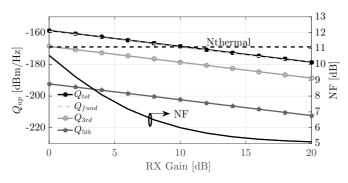

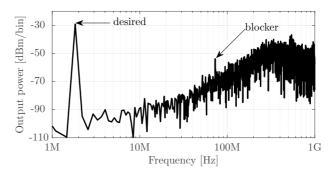

(3.4)