# ADEPOS: A Novel Approximate Computing Framework for Anomaly Detection Systems and its Implementation in 65nm CMOS

Sumon Kumar Bose, Student Member, IEEE, Bapi Kar, Member, IEEE, Mohendra Roy, Member, IEEE, Pradeep Kumar Gopalakrishnan, Senior Member, IEEE, Zhang Lei, Aakash Patil, Member, IEEE, and Arindam Basu, Senior Member, IEEE

Abstract—To overcome the energy and bandwidth limitations of traditional IoT systems, "edge computing" or information extraction at the sensor node has become popular. However, now it is important to create very low energy information extraction or pattern recognition systems. In this paper, we present an approximate computing method to reduce the computation energy of a specific type of IoT system used for anomaly detection (e.g. in predictive maintenance, epileptic seizure detection, etc). Termed as Anomaly Detection Based Power Savings (ADEPOS), our proposed method uses low precision computing and low complexity neural networks at the beginning when it is easy to distinguish healthy data. However, on the detection of anomalies, the complexity of the network and computing precision are adaptively increased for accurate predictions. We show that ensemble approaches are well suited for adaptively changing network size. To validate our proposed scheme, a chip has been fabricated in UMC 65nm process that includes an MSP430 microprocessor along with an on-chip switching mode DC-DC converter for dynamic voltage and frequency scaling. Using NASA bearing dataset for machine health monitoring, we show that using ADEPOS we can achieve 8.95X saving of energy along the lifetime without losing any detection accuracy. The energy savings are obtained by reducing the execution time of the neural network on the microprocessor.

Index Terms—Edge computing, Predictive maintenance, approximate computing, Anomaly detection, buck converter.

#### I. INTRODUCTION

NOMALY detection can be stated as the identification or separation of unusual and abnormal data distribution from the normal one. Early detection of anomaly alerts us about the unusual neuronal activities in patients with an epileptic seizure, the preliminary stage of machine breakdown [1] or the credit card fraud and network intrusion. In this paper, we will focus on anomaly detection in the context of predictive maintenance of the machine and epileptic seizure.

Machine breakdown laggards the throughput and productivity of industries eventually leading to losses in revenue.

This work was supported by Delta Electronics Inc. and the National Research Foundation Singapore under the Corp Lab @University scheme.

- S. K. Bose, B. Kar, P. K. Gopalakrishnan and A. Basu are with the Delta-NTU Corporate Laboratory for Cyber-Physical Systems, School of EEE, NTU, Singapore 639798. (e-mail: bose0003@e.ntu.edu.sg; arindam.basu@ntu.edu.sg).

- M. Roy is with PDPU, Gandhinagar, India 382007 (e-mail: mohendra.roy@sot.pdpu.ac.in).

- Z. Lei is with the Centre of Excellence in IC Design (VIRTUS), School of EEE, NTU, Singapore 639798 (e-mail: CharlesZhang@ntu.edu.sg).

- A. Patil is associated with Tork Motors, Pune, India 411026.

Periodic maintenance of machines reduces the downtime due to unexpected machine failure but causes over maintenance. On the contrary, predictive maintenance (PdM) keeps a balance between unnecessary maintenance and run to failure of machines. Typically vibrations [2], [3], temperature [4], humidity, etc. signals are sensed to monitor the machine health condition in the PdM approach. Due to the slow dynamics of temperature or humidity signal, it can be sampled once every second and the amount of generated data is quite low. However, the sampling rate is much higher for detecting machine vibrations. Even though the vibration signal is acquired in a duty cycled approach, most of the energy and bandwidth have to be allocated to send a large chunk of vibration data from the sensing node to the cloud. This conventional way of data processing poses two issues in battery-powered sensor nodes: 1) excessive drainage of battery energy which limits the lifetime of sensor nodes 2) latency to get the decision of processed data from cloud servers. These issues can be resolved by edge computing [5], [6] framework where the data processing tasks are offloaded from the cloud to IoT nodes.

In this paper, we present an edge computing framework which reduces the power consumption of the sensor node exploiting the output of the anomaly detector by dynamic voltage and network scaling (DVNS). Dynamic voltage scaling (DVS) is one of the popular methods to achieve energy optimization in electronics system by supplying power at the optimum energy point. Wide supply range on-chip switched capacitor (SC) converter [7] has been implemented for DVS but it suffers from low efficiency and on-chip area overhead. However, for lithium or button cell battery powered IoT nodes where the area is limited by the battery volume, inductor based switching converter is suitable due to its higher efficiency and wide supply range [8].

The energy requirement of the system can be brought down further by approximate computing where slight errors in calculation either do not change the final outcome or can be ignored by human perception [9]. Approximations in the computation are introduced from the basic building block of a circuit such as an adder [10], [11] or multiplier [12], [13] to the system level [14], [15], [16]. Since the neural network is good approximator, in this work, we have introduced approximation in the calculation at the system level using dynamic network expansion (DNS) where we have dynamically varied the number of neurons in the system based on anomaly detector

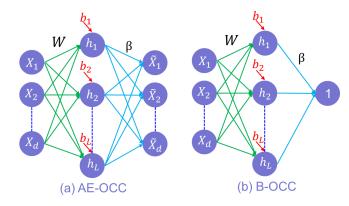

Fig. 1. (a) Autoencoder (AE) Architectures: In reconstruction based one class classification (OCC), AE is trained using healthy data to learn input statistics and to reconstruct the input vector at the output. (b) Boundary-based OCC is trained to produce a value of 1 at the output for healthy data. During testing when either reconstructed output deviates from the input (reconstruction based OCC) or from 1 (boundary based OCC) by a threshold amount, the machine can be declared as faulty.

#### decision.

Machine learning (ML) methods have been applied previously for machine health monitoring such as for fault detection of aero-engine control system sensor [17], and fault diagnostics of the rotary machine [18]. However, insufficiency of machine failure data is one of the main bottlenecks of machine health monitoring employing ML [19] for different types of fault detection. Generation of failure signatures of the machine by intentionally putting the machine in the faulty condition is not cost effective since the data collection process will completely destroy the machine. Moreover, it is very unlikely that the failure signatures of different machines and different failure cases are similar. Therefore, learning from a generic dataset is not a feasible solution. However, an overabundance of healthy data from the machine can be utilized to train PdM sensor node as one class classifier (OCC) and any deviation from the healthy data can be treated as an anomaly [20].

Our major contributions in this paper are summarized as follows: 1) Application of boundary-based extreme learning machine (ELM-B) computational framework for machine health monitoring and anomaly detection 2) Adaptive usage of approximate computing (ADEPOS) along the lifetime of machine based on the anomaly detector output for low energy computation 3) Hardware demonstration of ADEPOS algorithm using dynamic voltage and network scaling (DVNS). Our proposed ADEPOS algorithm has the benefit of reducing energy in both microprocessor-based systems (this work) as well as ASIC implementations where parts of the chip can be turned OFF when unused. Compared to our earlier algorithmic work [21], we present hardware results from a fabricated chip for the first time that quantifies energy savings afforded by ADEPOS in actual hardware. Since most IoT systems rely on microprocessor based implementations, we demonstrate our results on such a system.

We arrange the remaining part of the paper is as follows. In section II, we review the basics of boundary and autoencoder based extreme learning machine (ELM-B and ELM-AE) as one class classifier (OCC) in the application of machine health monitoring whereas we present the proposed ADEPOS algo-

rithm for energy saving in section III. Section IV presents the hardware implementation for DVS and ADEPOS. In section V, we show the results of our experiment on NASA bearing dataset. Section VI captures the results of seizure detection using EEG dataset followed by conclusions in the last section.

#### II. ELM-AE AND ELM-B BASED OCC

#### A. Autoencoder (AE)

Single layer autoencoder (AE) is the simplest form of autoencoder consisting of an input layer, an output layer, and a single hidden layer. Fig. 1(a) captures the basic architecture of single layer autoencoder whose input weights W and biases  $b = [b_1, b_2, \cdots, b_L]^T$  encode the input data distribution  $X = [x_1, x_2, \cdots, x_d]^T$  into L hidden neurons  $h = [h_1, h_2, \cdots, h_L]^T$  whereas output weights  $\beta$  decodes the latent features hidden into h to output neurons  $\tilde{X} = [\tilde{x_1}, \tilde{x_2}, \cdots, \tilde{x_d}]^T$ . In autoencoder, input and output dimension are same since autoencoder always attempts to reconstruct the input data at its output. Eq. (1) and (2) represent the basic encoding and decoding operations occurring in an autoencoder.

$$h_j = g\left(\sum_{i=1}^d W_{ji}x_i + b_j\right); \quad j = 1, 2, ..., L$$

(1)

$$\tilde{x}_k = \sum_{j=1}^L \beta_{jk} h_j; \quad k = 1, 2, ..., d$$

(2)

$$\tilde{R} = \sum_{j=1}^{L} \beta_j h_j; \tag{3}$$

Figure 1(b) depicts the architecture of boundary mode single hidden layer feed-forward network (SLFN) where input features X are being projected into L dimensional hidden space using weights W and biases b and output is targeted at 1 (or any real number R). Basic operations of boundary mode SLFN are highlighted in Eq. (1) and (3). We prefer absolute value as nonlinear activation function over sigmoid or tanh since it is easier to implement in hardware and no performance degradation was observed.

In traditional autoencoder (TAE) or artificial neural network (ANN), optimal weights W,  $\beta$ , and biases b are learned using back-propagation in an iterative way. Even though back-propagation produces state-of-the-art accuracy, it requires a large number of data samples to converge and experiences high computational overhead. On the contrary, an alternative computing paradigm based on a random high dimensional projection of input data [22], [23], [24] provides faster convergence and needs to tune only hidden layer to output layer weights  $\beta$ . The other parameters, input to hidden layer weights, W and biases, b are taken randomly from a continuous probability distribution. In this paper, we use the term extreme learning machine (ELM) to refer to these algorithms, but any other algorithm in this class is equally applicable in our case.

In ELM framework, the optimal output layer weights  $\beta^*$  in Eq. (4) are found by minimizing error  $(\epsilon)$  in the least square sense where the error  $(\epsilon)$  is defined in Eq. (5).  $H^{\dagger}$  in Eq. (4) denotes the Moore-Penrose generalized inverse [25] of H.

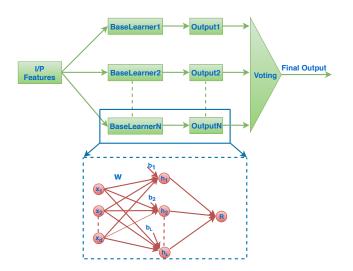

Fig. 2. Ensemble of N-base learners (BL). Each BL has L hidden neurons and the final output is dependent on all intermediate BLs output on the basis of majority voting.

$$\beta^* = H^{\dagger} X \tag{4}$$

$$\epsilon = \begin{cases} \|X - \tilde{X}\|^2, & \text{if ELM-AE} \\ \|R - \tilde{R}\|^2, & \text{if ELM-B} \end{cases}$$

(5)

As discussed earlier, training the PdM sensors from a generic dataset and deploying on the machine is not a viable solution since the neural network model parameters are dependent on machine and sensor position and orientation. To mitigate these issues, online sequential learning of the PdM sensors deploying on the machine is necessary. ELM based online sequential learning algorithms OPIUM, OSELM have been presented in [26], [27] respectively. However, OSELM demands matrix inverse operation which is costly in terms of memory and computes. Hence, keeping in mind the real practical application scenario of PdM sensor, we have opted for OPIUM as the learning framework for ELM based autoencoder and boundary methods since it requires less computation.

Equations for the online update of  $\beta$  are shown in Eq. (6) and (7) using  $\theta = C \cdot I$  where C is constant and I is LxL identity matrix [28].

$$\eta_k = \frac{\theta \cdot h_k}{1 + h_k^T \cdot \theta \cdot h_k} \tag{6}$$

$$\beta_k = \beta_{k-1} + \eta_k (X_k - \beta_{k-1} h_k) \tag{7}$$

# B. One Class classifier (OCC)

Since the failure data from the machine is rare, we trained ELM-AE and ELM-B model as one class classifier using healthy data from the machine at the very early stage of machine life. As soon as the training of machine learning model stops, the system enters into inference mode. When the reconstructed output has error exceeding a pre-defined threshold, we can schedule the machine for maintenance.

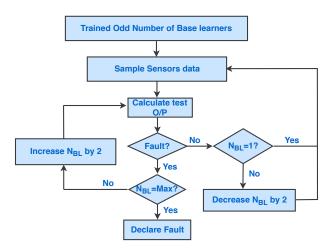

Fig. 3. Flowchart for ADEPOS: Approximate computing is achieved by adapting the number of hidden neurons in an Ensemble Learning architecture [21].

#### III. ALGORITHMIC IMPROVEMENTS FOR ENERGY SAVING

In this section, we will discuss two algorithmic enhancements for energy saving - a) exploiting approximate computing along the lifetime of machine based on anomaly detector output (ADEPOS) and b) generation of hidden neurons with lowest counts of multiply and accumulate (MAC) operations possible. The first approach towards energy saving is generic to any machine learning model and hardware platform whereas the second approach is only applicable to randomized first layer based computing framework.

# A. ADEPOS: Anomaly Detector based Power Saving

In this paper, we proposed to use imprecise/ approximate computing [29] along the lifetime of the machine to save energy of the anomaly detection system. At a very early stage of machine life, changes of input data distribution are minimal and anomaly detector output is far from the threshold. Hence, errors or inaccuracies introduced in the computation due to approximate computing will be lower than the margin. Once the anomaly detector raises alarm, accuracy in the computation is elevated gradually on the same input data to scrutinize whether it is truly an anomaly or a false alarm due to the approximate computing. Approximation in the calculation can be added in many ways such as by varying data path bit precision [30] during computation, changing network size or reducing accuracy in feature extraction part, the voltage over scaling [31] and so on. In this paper, we only discuss the dynamic changing of effective neurons in the network (DNS) and lowering supply voltage to the near-threshold region as representative parameters tuned by ADEPOS.

The most naive implementation of DNS is to train and keep multiple networks of varying size on the chip with the appropriate network being ON based on the ADEPOS control. While this enables power savings, it is very wasteful of chip area. Hence, it will be best if we can train a bigger network in the learning phase and shut down parts of the network dynamically. However, training a larger ELM network of dimension L and pruning some neurons dynamically lead to erroneous result since during training value of  $i^{th}$  neuron weights are dependent on remaining neurons in the network. One of the

ways to mitigate this problem is to train N such mini-ELMs each having L hidden neurons and ensemble [32] outputs using majority voting to get the final output (see figure 2). We call each of these mini-ELM as a base learner (BL). In related work, [33] has applied AdaBoost to increase the resiliency of the overall system but has not explored in the energy reduction perspective. Moreover, the idea of DNS is completely different from neurons and weights pruning [34] performed during the training phase of the network to reduce the number of redundant neurons and parameters. Nevertheless, we can apply such methods to reduce each BL size.

The flowchart in Fig. 3 shows the steps involved in adaptive network expansion using an ensemble of multiple base learners. At any instance of time, the effective number of neurons in the network is  $L_{eff}$ , is given by:

$$L_{eff} = L \times N_{BL} \tag{8}$$

Where  $N_{BL}$  is the number of active base learners in the network. We trained all BLs using healthy data from machine but with different random weights in the first layer. At the beginning of the inference phase, we start with an odd number of BLs. Based on the output of majority voting of all the BLs, we add or remove 2 more BLs from the network since an odd number of BLs are required for majority voting. If at an intermediate step the voting indicates an anomaly, we increase the number of BLs to check whether it is a false alarm due to inaccuracies of approximate computing or a true warning. If all the BLs are deployed and the anomaly detector still raises alarm, we schedule the maintenance. For ASIC implementation, the power supply of all the inactive BLs can be lowered to a point  $V_{retention}$  where it can retain its memory content. However, in our present design, all the BLs are implemented in program memory where we modulate the execution time and energy drawn from the battery based on the number of selected BLs.

# B. Hidden Neuron Generation using the minimum number of MAC operations

We define a list of symbols in the following that will be used throughout this subsection:

Number of # d# input features BLBase learner L# neurons in each BL  $N_{BL,Max}$ Maximum # BLs in the network Neuron generation NG $OP_{orig}^1$  $OP_{orig}^2$ # operations in the input layer without NG # operations in the output layer  $OP_{orig}$ Total # operations without NG  $OP_{NG}^{1}$ # operations in the input layer with NG  $OP_{NG}$ Total # operations with NG # physical neurons  $L_{phy}$

ADEPOS should be applied over and above other optimization schemes to improve neural network implementation efficiency. Here, we use a NG technique from a recently reported ELM chip [35] and show that it can provide benefits in microprocessor-based implementations as well. As

mentioned earlier, we randomly choose input layer parameters for ELM computing framework. In general, we require  $OP_{orig}^1 = 2N_{BL,Max} \cdot d \cdot L$  multiply and addition operations in the input layer (see Eq. (1)) and  $OP_{orig}^2 = N_{BL,Max} \cdot L + (L-1) \cdot N_{BL,Max}$  multiply and addition operations (see Eq. (3)) in the output layer calculation. Here we assume that the system is operating in boundary mode and ignore the calculation related to activation function implementation. Hence, the total number of multiply and addition operations,  $OP_{orig}$ , is given by:

$$OP_{orig} = OP_{orig}^{1} + OP_{orig}^{2}$$

$$= N_{BL,Max}(2dL + 2L - 1)$$

(9)

Following NG scheme, we can generate activation of a virtual neuron by subtracting Eq. (10) and (11) as shown in Eq. (12).

$$h_j = \sum_{i=1}^{d} W_{ji} x_i + b_j \tag{10}$$

$$h_k = \sum_{i=1}^{d} W_{ki} x_i + b_k \tag{11}$$

$$h_{jk} = \sum_{i=1}^{d} (W_{ki} - W_{ji})x_i + b_k - b_j$$

(12)

The operation in Eq. (12) only changes the variance of random weight and bias distribution which does not have any impact on classifier as long as weights and biases are random. The advantage of this method is that by selecting and subtracting any two out of  $L_{phy}$  physical neurons, we can create  $\frac{L_{phy} \cdot (L_{phy}-1)}{2}$  virtual neurons. In other words, to generate  $N_{BL,Max} \cdot L$  virtual neurons, we need approximately  $L_{phy}$  physical neurons which is presented in Eq. (14).

$$L_{phy} = \left\lceil \frac{1 + \sqrt{1 + 8 \cdot N_{BL,Max} \cdot L}}{2} \right\rceil \tag{13}$$

$$\approx \sqrt{2 \cdot N_{BL,Max} \cdot L}$$

(14)

At  $2 \cdot N_{BL,Max} \leq L$ , we can conclude from Eq. (14) that  $L_{phy} \leq L$ . Therefore, the operations required in the first layer,  $OP_{NG}^1$ , as represented in Eq. (15) changes drastically. However, the number of calculation in the output layer does not change. Therefore, overall multiply and addition operations,  $OP_{NG}$  are needed as shown in Eq. (16) which surely reduces program execution time and burden on multiply and accumulate (MAC) block provided  $N_{BL,Max}$  is greater than 1

$$OP_{NG}^{1} = 2L_{phy} \cdot d + N_{BL,Max} \cdot L \tag{15}$$

$$OP_{NG} = OP_{NG}^{1} + OP_{orig}^{2}$$

=  $2L_{phy} \cdot d + 3 \cdot N_{BL,Max} \cdot L - N_{BL,Max}$  (16)

# IV. HARDWARE ARCHITECTURE

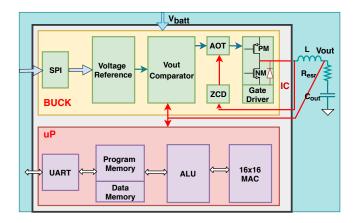

The hardware designed to test ADEPOS consists of two main components: (1) a uP following the OpenMSP430 architecture [36] and (2) a DC-DC converter for applying DVS to

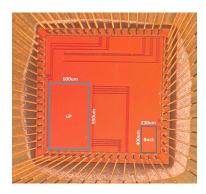

Fig. 4. Block diagram of our fabricated integrated circuit which have been used to demonstrate the ADEPOS algorithm. The lower part shows the uP that runs the code for implementing the ELM-B based OCC and ADEPOS controller for DNS, while the upper part depicts the DC-DC converter for DVS.

the uP. Figure 4 depicts the overall architecture of the chip while Fig. 5 shows a die photo. The details of these blocks are described next.

# A. Microprocessor(uP) Core

Along with the basic building blocks of a microprocessor, we have incorporated 16x16 multiply and accumulation block (MAC) in the design which is capable of doing 16bit signed and unsigned MAC operation. The 16x16 MAC block works in parallel with ALU and reduces the executable code size. The program related to all BLs and ADEPOS algorithm are stored in program memory using UART communication protocol and executed serially based on the number of BLs selected out of  $N_{BL,Max}$ . The uP core has been implemented in UMC 65nm CMOS process using core devices.

# B. DC-DC Converter

The DC-DC converter is designed using IO CMOS devices to mitigate the reliability issue due to 3.3V battery supply. The output of DC-DC converter is configurable from 500mV to 1250mV in steps of 50mV by programming voltage references via SPI communication port. To reduce the overall standby power of the switching converter, we adopted leakage based

Fig. 5. Die photograph of 2mmX2mm chip showing two major blocks-microprocessor(uP) and buck converter.

voltage reference [37] and bias current design approach. Once  $V_{out}$  voltage falls below the reference voltage,  $V_{out}$  comparator turns ON the PMOS switch (PM in Fig. 4) inside the gate driver to charge the output capacitor. Synchronous buck converter topology is followed to minimize power loss in free wheel diode (body diode of NM in Fig. 4). The zero current detector (ZCD) turns OFF the NMOS parallel to free wheel diode whenever the inductor current crosses zero. The ZCD output signal goes to adaptive on time (AOT) block for further processing.

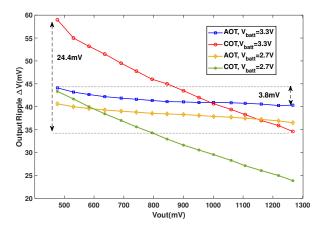

Since the load current requirement of ADEPOS digital core is less than 1mA, we choose the discontinuous mode of operation (DCM) for the buck converter. Lower supply ripple at the near-threshold region is one of the major design parameters for any system design. On the contrary, buck converter operating at DCM and having constant on time (COT) topology exhibits the maximum output ripple at the maximum battery voltage and the minimum output voltage due to the highest inductor peak current. The output voltage ripple of the buck converter is represented as:

$$\Delta V = \left(R_{esr} + \frac{T_{on} \cdot V_{batt}}{2C_{out} \cdot V_{out}}\right) \cdot \frac{\left(V_{batt} - V_{out}\right) \cdot T_{on}}{L} \quad (17)$$

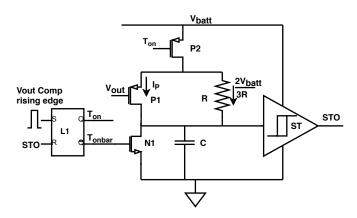

where  $R_{esr}$  is the equivalent series resistor of output capacitor  $C_{out}$ ,  $T_{on}$  denotes the charging time of  $C_{out}$  which is constant for COT topology and  $V_{batt}$  and  $V_{out}$  are the battery and output voltage of buck converter respectively. Opamp based adaptive on time (AOT) [38], background calibration technique [39] have been proposed to take care of the output voltage ripple. Similarly, [40] proposed NMOS and current mirror-based AOT circuit which only takes care of the effect of  $V_{batt}$  variation on the output ripple. But a battery-operated system which employs dynamic output voltage scaling should mitigate the effect of both  $V_{batt}$  and  $V_{out}$  variation on the output ripple. In this design, we suggested single PMOS transistor based adaptive on time (see Fig. 6),  $T_{on}$ , which follows Eq. (18) and keeps the output ripple almost constant

Fig. 6. Adaptive on time circuit (AOT) to modulate inductor peak current. Upper and lower threshold of Schmitt trigger are  $\frac{2\cdot V_{batt}}{3}$  and  $\frac{V_{batt}}{3}$  respectively. Rising edge of the  $V_{out}$  comparator output sets the latch and turns ON P2 to enable the charging of C and the rising edge of Schmitt trigger output (STO) resets the latch.

Fig. 7. Simulated output voltage ripple of the buck converter with AOT and COT circuit at  $R_{esr}$ =100m $\Omega$ , and  $C_{out}$ =10 $\mu$ F. Output voltage ripple,  $\Delta V$  increases drastically when the system operates at lower  $V_{out}$  in constant on time mode.

as highlighted in Fig.7 and consumes very low power.

$$T_{on} = \frac{k1 \cdot V_{batt}}{(k2 \cdot V_{batt} - k3 \cdot V_{out}) + k4}$$

(18)

Parameters k1, k2, k3 and k4 are dependent on process, transistor aspect ratio, resistor, R, and capacitor, C. We discuss the derivation of Eq. (18) and its related parameter in appendix.

The current through P1 and R charges the capacitor C. Whenever the voltage across the capacitor C crosses the upper threshold voltage  $(\frac{2 \cdot V_{batt}}{3})$  of the Schmitt trigger (ST), its output voltage goes high and resets the latch. The process variation of PMOS can be taken care by varying the aspect ratio of P1 and resistor R.

The circuit is simulated in SPICE using UMC 65nm models. In Fig. 7, we have plotted output voltage ripple for AOT and COT (constant on time) approaches at  $R_{esr}$ =100m $\Omega$ ,  $C_{out}$ =10 $\mu$ F, L=2.2 $\mu$ H and  $V_{batt}$  = 3.3V and 2.7V across different  $V_{out}$  voltages. It can be seen that the output ripple variation is 24.4mV across  $V_{out}$  and even twice if we consider  $V_{batt}$  variation in COT approach. On the contrary, the proposed AOT circuit keeps the output ripple almost constant across  $V_{batt}$  and  $V_{out}$  and draws only 50nA dynamic current when the load is 1mA.

#### V. RESULTS

# A. Dataset

In order to validate the proposed ADEPOS algorithm, we use NASA bearing dataset [41] provided by the Center for Intelligent Maintenance Systems (IMS), University of Cincinnati. The bearing vibration data was sampled at 20KHz for 1s duration in an interval of 10 minutes. Out of twelve bearings, two bearings faced outer race failure and two of them suffered inner race and roller element defect respectively. The summary of time series data of bearings is captured in Table I.

Statistical features such as mean, root mean square (RMS), kurtosis [42] from the time domain, FFT of fixed sub-band frequencies [43] from the frequency domain and wavelet packet transformation (DWT) [44] from the time–frequency domain are popular in the literature as intermediate data for

TABLE I

SUMMARY OF NASA BEARING TIME SERIES DATASET

| Test     |          |         | # Data    |         |

|----------|----------|---------|-----------|---------|

|          | Bearings | # Files | point in  | Remarks |

|          |          |         | each file |         |

|          | Bearing1 | 2156    | 20480     | Healthy |

| Dataset1 | Bearing2 | 2156    | 20480     | Healthy |

| Datascti | Bearing3 | 2156    | 20480     | Faulty  |

|          | Bearing4 | 2156    | 20480     | Faulty  |

|          | Bearing1 | 984     | 20480     | Faulty  |

| Dataset2 | Bearing2 | 984     | 20480     | Healthy |

| Datasctz | Bearing3 | 984     | 20480     | Healthy |

|          | Bearing4 | 984     | 20480     | Healthy |

| Dataset3 | Bearing1 | 6324    | 20480     | Healthy |

|          | Bearing2 | 6324    | 20480     | Healthy |

|          | Bearing3 | 6324    | 20480     | Faulty  |

|          | Bearing4 | 6324    | 20480     | Healthy |

|          |          |         |           |         |

machine health monitoring. In this work, we conduct our experiments on five time domain features extracted from the raw vibration data contained in NASA dataset, such as (a) RMS, (b) Kurtosis, (c) Peak-Peak, (d) Crest factor, and (e) Skewness since we have validated that this is a minimal set of features that are the most informative. Moreover, the time complexity of calculating m such features is  $m \cdot \mathcal{O}(n)$  where n denotes the number of data points in each file.

# B. A comparative study of ELM-based algorithms and traditional AEs

A comparative convergence study of online training among ELM and traditional methods in bearings [41] health monitoring is summarized in Table II. In this analysis, we train below mentioned ML models in MATLAB using a few hundred samples of bearing data and when the convergence of  $\beta$  is reached, we use the remaining samples for calculating testing error ( $\epsilon$ ). We use boundary and reconstruction OCC framework for OSELM and OPIUM based online learning approach and are termed as OSELM-B, OSELM-AE, OPIUM-B, and OPIUM-AE respectively. Since OSELM method demands matrix inverse operation, its computational complexity  $(\mathcal{O}(L^3))$ is higher than OPIUM ( $\mathcal{O}(L^2)$ ). Hence, OSELM-B needs 2.27X number of operations (operations/sample X Number of samples) and 2.6X higher SRAM memory to converge using the LU decomposition method than its counterpart (OPIUM-B). In terms of the number of operations and SRAM memory requirement, the performance of OPIUM-B is comparable with both variants of traditional autoencoder - (a) traditional untied autoencoder (TAE-Un) [45] and (b) tied autoencoder (TAE-Ti) [46]. We use ADAM [47] optimizer to train the TAEs.

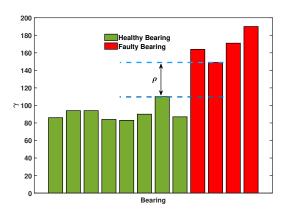

In order to further compare all the algorithms, we define robustness margin  $(\rho)$  as shown in Fig. 8 that indicates the separation margin between healthy and faulty bearings and the feasibility of placing threshold to completely separate the faulty bearings from a healthy one. Parameter  $\gamma$  in Fig. 8 is defined by:

$$\gamma_i = \frac{|\epsilon^{test}|_{max}}{\langle |\epsilon^{train}| \rangle}; \quad i = 1, 2, ..., 12$$

(19)

TABLE II

CONVERGENCE STUDY OF DIFFERENT OCC METHODS

|                      | ELM     |          |         | Traditional AE(TAE) |        |        |

|----------------------|---------|----------|---------|---------------------|--------|--------|

|                      | OSELM-B | OSELM-AE | OPIUM-B | OPIUM-AE            | TAE-Un | TAE-Ti |

| Operation(Million)   | 0.59    | 1.08     | 0.26    | 0.61                | 0.97   | 0.24   |

| Data Memory          | 1262    | 1350     | 482     | 570                 | 310    | 310    |

| Robustness Margin(ρ) | 94      | 127      | 56      | 163                 | 20     | 1.9    |

Fig. 8. Robustness  $(\rho)$  margin indicates the separation margin between healthy and faulty bearings and the feasibility of placing threshold to completely separate the faulty bearings from a healthy one. Parameter  $\gamma$  is defined in Eq. (19).

where  $< |\epsilon^{train}| >$  is the indication of average noise in the data during healthy operation and  $\gamma$  indicates how much deviation can happen due to degradation of condition. Ideally, the healthy bearings should have low values of  $\gamma$ .

In terms of robustness margin  $(\rho)$  OPIUM-B shows better performance than both TAEs. Hence, we choose OPIUM-B algorithm as OCC for machine health monitoring.

# C. Threshold Selection

Due to the limitation of unhealthy bearing data and time stamp of failure, we follow the leave-one-out (LOO) approach to calculate the threshold value  $(\lambda)$  using Eq. (20). We divide 12 bearings into two groups, 11 bearings for threshold calculation and the remaining bearing for testing deploying the calculated threshold  $(\lambda)$ . Errors  $(\epsilon)$  (difference of expected value and output of boundary-OCC) from good bearings out of all 11 training bearings data are used for threshold calculation. We carry out the LOO strategy for each of the 12 bearings keeping one bearing data for testing.

$$\lambda = Max(\epsilon) + 0.5 \times c \times \sigma_{\epsilon} \tag{20}$$

$Max(\epsilon)$  and  $\sigma_{\epsilon}$  are the maximum and standard deviation of  $\epsilon$  values of good bearings in the training set. We choose c=1, since at this value AUC (area under the curve) of ROC curve is one.

# D. Optimal Neurons (L) and $N_{BL,Max}$ Selection

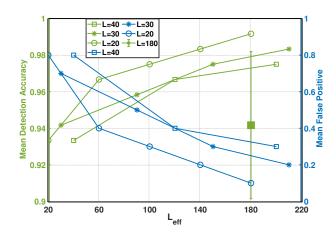

It is shown in [21] that at L=20 and  $N_{BL,Max}=9$ , the mean detection accuracy is almost 100% over 10 trials

Fig. 9. Mean detection accuracy and mean false positive vs. effective number of hidden neurons  $(L_{eff})$  in the network. Detection accuracy increases with  $L_{eff}$  and smaller value of L.

(for 10 different random seeds). The experimental results are also plotted in Fig. 9 for different L = (20, 30, 40) and  $N_{BL,Max} = (9,7,5)$  values using ensemble of BLs. It is apparent from Fig. 9 that mean detection accuracy is monotonically increasing with an effective number of hidden neurons  $L_{eff}$  in the network and smaller values of L. Furthermore, the mean false positive over 10 trials decreases if higher number of BLs are ensemble together. The vertical green line at L=180shows the detection accuracy (mean±SD) of a single large classifier. It can be seen that the mean detection accuracy of a single large classifier having L=180 neurons is lower than that of an ensemble of BLs with a smaller number of neurons. Hence, an ensemble of BLs not only increases the detection accuracy but also provides an opportunity to increase the energy saving of the system by leveraging the proposed ADEPOS algorithm. Since at L = 20 and  $N_{BL,Max} = 9$ , mean detection accuracy is almost 100%, we choose this configuration for showing the energy saving of our ADEPOS algorithm in uP. Before going into the details of energy saving of the proposed ADEPOS algorithm, we will discuss the characterization of uP and DC-DC converter separately.

#### E. Chip Characterization

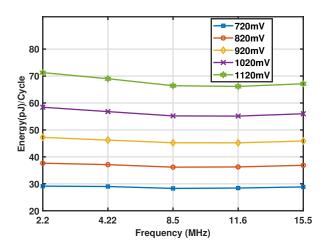

In Fig. 10, we show the energy per clock cycle of uP at different operating voltages and frequencies. As expected, energy scales with supply voltages but remains almost constant with frequencies. The minimum energy operating point occurs at 720mV and 8.5MHz. Although the memory can retain its value till 190mV, uP core generates fallacious output below 700mV at higher operating frequencies due to SRAM read or write failure.

Fig. 10. Energy per clock cycle of uP across different operating frequencies and voltages.

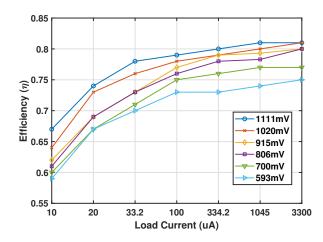

The Fig. 11 indicates that the efficiency of the DC-DC converter increases with load current. Since there are hardly any changes in energy per cycle between 8.5MHz and 15.5MHz and dynamic current of uP increases at higher frequencies, it will be beneficial to operate the system at 15.5MHz. The efficiency of the buck converter is lower than expected due to high inductor peak current and higher metal resistance from external pads to the NMOS and PMOS transistor of the gate driver. Since the DC-DC converter supports more than 10mA load current and the required maximum processor current is 1mA, we can increase the inductor from  $2.2\mu\text{H}$  to  $10\mu\text{H}$  to reduce the peak inductor current which in turns reduces conduction loss across NMOS and PMOS switch of the gate driver.

The overall energy consumption by the predictive maintenance system can be written as:

$$Energy = \frac{V_{out,sta} \cdot I_{core,sta} \cdot T_{sleep}}{\eta_{sta}} + \frac{V_{out,dyn} \cdot I_{core,dyn} \cdot T_{active}}{\eta_{dyn}}$$

(21)

where  $V_{out,sta}$  and  $I_{core,sta}$  are the output voltage of DC-DC converter and static current of processor respectively when the system is in sleep and  $V_{out,dyn}$  and  $I_{core,dyn}$  are the output voltage of DC-DC converter and static current of processor respectively when the system is active.  $\eta_{sta}$  and  $\eta_{dyn}$  are the efficiency of the DC-DC converter at two different operating conditions and function of the output voltage and load current. The static and dynamic power of the DC-DC converter is taken into account during the efficiency calculation.

Although the system can operate down to  $720 \mathrm{mV}$ , we choose the optimal operating voltage of the system as  $750 \mathrm{mV}$  to have some margin. At  $750 \mathrm{mV}$ , we will lose around 5% energy due to lower efficiency of DC-DC converter compared to  $1111 \mathrm{mV}$  which is apparent from Fig. 11. However, voltage scaling can save around 53% energy at  $15.5 \mathrm{MHz}$  due to the lower voltage and dynamic current (see Fig. 10) leading to better system level efficiency.

Fig. 11. Efficiency of DC-DC converter across load current at different output voltages.

The performance of the designed buck converter is comparable with recently published work as presented in Table III. In general, parasitic losses are lower at the higher output voltage,  $V_o$ , lower input voltage,  $V_{in}$ , and higher value of inductor due to the lower inductor peak current at this operating condition. Hence, the efficiency is better for [48] and [49]. Since we are using a lower inductor value of L=2.2 $\mu$ H, there is room to improve efficiency using higher inductor value at the cost of lower load current. Lower output ripple is another benefit of using higher inductance.

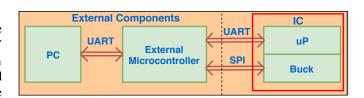

#### F. Experimental setup for Validation of ADEPOS algorithm

In Fig. 12, we present the experimental setup for validating ADEPOS. A PC is used to visualize the output of base learners and send data using Matlab. The external controller acts as an interface between uP and other modules (PC and buck converter). It handles data transfer to and from the on-chip uP and also sets the DC-DC converter to 750 mV during operation, and 600 mV during inactive periods. Since the SRAM can retain its value until 190 mV, we can power the uP following HYPNOS technique [51] and bring down the power consumption further in the nW range.

Since the uP performs integer operations, the extracted feature from raw bearing data is converted to a 6bit integer value. The first layer random weight, bias and learned second layer weights for 9 base learners (selection of L=20 and  $N_{BL,Max}=9$  have been discussed in section V-D) are stored in the program memory of uP core. Once the data transfer is

Fig. 12. Experimental setup for validating ADEPOS algorithm. A PC is used to visualize the output of base learners and send data using Matlab. The external controller acts as an interface between uP and PC and buck converter.

|                                   | [48]                        | [49]                        | [50]                      | This Work                   |

|-----------------------------------|-----------------------------|-----------------------------|---------------------------|-----------------------------|

| Control Method                    | Hysteresis & PFM            | Hysteresis & AMOT           | PFM                       | PFM & AOT                   |

| Input Voltage( $V_{in}$           | 2-5.5V                      | 1.8-4.2V                    | 1.2-3.3V                  | 2.3-3.5V                    |

| Output Voltage( $V_o$ )           | 1.3-5V                      | 0.9-1.4V                    | 0.7-0.9V                  | 0.47-1.25V                  |

| Max Load Current                  | 50mA                        | 40mA                        | 1mA                       | 10mA                        |

| Output Ripple                     | 20mV                        | 30mV                        | 20mV                      | 41mV                        |

| Quiescent Current                 | 380nA                       | 12uA                        | 100pA                     | 700nA                       |

| Inductor (L)                      | $10\mu H$                   | $4.7\mu\mathrm{H}$          | $47\mu\mathrm{H}$         | $2.2\mu\mathrm{H}$          |

| Efficiency at $I_L = 1 \text{mA}$ | $V_{in}$ =3.3V, $V_o$ =1.3V | $V_{in}$ =3.3V, $V_o$ =1.2V | $V_{in}$ =3V, $V_o$ =0.8V | $V_{in}$ =3.3V, $V_o$ =0.8V |

|                                   | 87%                         | 83%                         | 80%                       | 78.3%                       |

TABLE III

PERFORMANCE COMPARISON OF BUCK CONVERTER WITH PUBLISHED WORKS

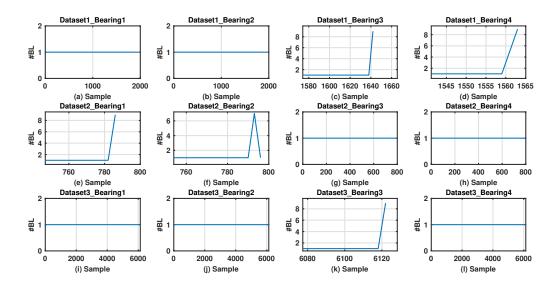

Fig. 13. Number of active base learners along the lifetime of all 12 bearings time series data for seed value = 10. Bearings in (c), (d), (e) and (k) failed at the end of their lifetime which is indicated by utilization of all base learners (9) in the system. Healthy bearings in (a), (b), (g), (h), (i), (j), and (l) deploys single base learner except bearing in (f) uses 7 base learners on sample data to get the correct decision.

completed between the external controller and data memory, the external controller enables the uP, and when the execution is over, the uP goes back to sleep again. We generate random weight and bias for 10 different seeds to validate the proposed ADEPOS algorithm on NASA bearings dataset.

Figure 13 shows the number of active base learners along the lifetime of all 12 bearings time series data. Bearings in (c), (d), (e) and (k) failed at the end of their lifetime which is indicated by utilization of all base learners (9) available in the system. Healthy bearings in (a), (b), (g), (h), (i), (j), and (l) deploy single base learner along the age of the bearings except bearing in Fig. 13(f) which deploys 7 base learners on sample data to get the correct decision.

Based on the adaptive usage of the number of ensembles, we find that the average value of  $L_{eff}$  (over 10 trials) throughout the lifetime of all the bearings is only 20.11 without sacrificing the accuracy obtained by using  $L_{eff}=180$  for  $N_{BL}=9$  networks in the ensemble. Thus compared to the case of using a fixed value of L=180 neurons, ADEPOS enables  $8.95\mathrm{X}$  reduction in an effective number of neurons. This reduction in neurons translates to the energy reduction in computation as shown next.

#### G. Energy Measurement

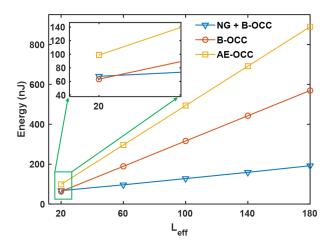

We use INA210 [52] IC from Texas instruments to measure the exact execution time of each base learner. In order to calculate the energy consumed by the algorithms(AE-OCC, B-OCC, B-OCC+NG), we measure the execution time of the algorithms employing INA210 and the power drawn by the uP to execute these algorithms. Subsequently, we multiply the power and the execution time to get the final energy number. Fig. 14 shows the impact of hidden neurons  $(L_{eff})$  on energy consumption for different algorithms at 750mV and 15.5MHz frequency. In system level, these number will scale up by the same factor if we take into account the efficiency of the DC-DC converter at that operating condition. As expected, energy consumption increases linearly with hidden neurons in the network but the slope depends on the algorithm. Energy consumption of the boundary-based OCC(B-OCC) is lower than autoencoder-based OCC (AE-OCC) since B-OCC requires less number of computation at the output layer than AE-OCC does. In neuron generation(NG) approach, replacement of multiplication operation by subtraction operation results in a reduction of execution time and a number of operation of each base learner. The combining effect of execution time and a number of operation reduction results in 3X energy reduction

Fig. 14. Impact of Hidden neurons  $(L_{eff})$  on energy consumption for different algorithms. As expected energy consumption increases linearly with hidden neurons in the network but the slope depends on the algorithm.

for  $L_{eff}=180$  in B-OCC. Since, in neuron generation method, we need multiplication along with subtraction for the first base learner, 6.7% more energy is required for the single base learner (L=20) which is magnified and shown in the inset.

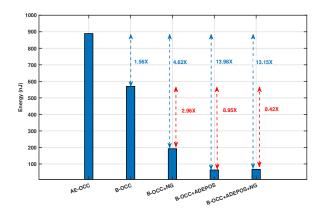

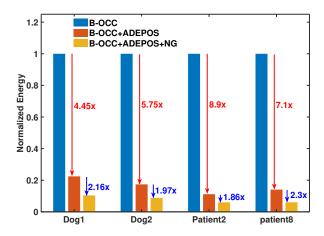

Figure 15 shows the energy saving by use of the appropriate algorithm and ADEPOS on NASA bearing time series data. B-OCC and B-OCC along with NG enable 1.56X and 4.62X energy reduction respectively compare to AE-OCC for  $L_{eff} = 180$ . Moreover, combining ADEPOS algorithm with B-OCC helps us to achieve 13.98X less energy consumption than AE-OCC. This is due to a combination of the reduction in number of neurons (Section V-F) along with reduced number of operations due to the choice of algorithm (B-OCC as opposed to AE-OCC). Energy saving of ADEPOS along with NG is slightly less due to two reasons a) L is small (20 here for each BL). It can be shown that the energy consumption of single BL at L> 24 generated using NG method is lower than that without using NG approach. b) The average number of neurons for NASA bearing dataset is 20.11 whereas the break-even point is 22.22 neurons. Even though the energy benefit of neurons generation is not visible here, it requires 64% less flash memory to implement 9 base learners than B-OCC, since, in B-OCC method, random weights and biases are used as an immediate operand.

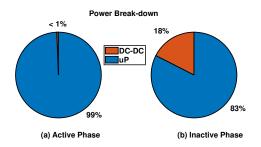

Considering the efficiency factor of DC-DC converter into account, the overall system combining the uP and the buck draws  $744\mu$ W power in the active and  $12\mu$ W power in the inactive period. Power break-down for DC-DC and uP subblock are shown in Fig. 16. It is apparent that the contribution of DC-DC to the overall energy consumption in the active period is insignificant. Further, if we consider a duty cycled operation where the inactive periods are fixed by the NASA bearings sampling timings and active time by single BL execution time, the overall system power calculated based on the Eq. (21) is similar to the inactive power of the system  $(12\mu\text{W})$ . The overall system power is limited by the inactive

Fig. 15. Energy saving by use of appropriate algorithm and ADEPOS on NASA bearing time series data. ADEPOS with B-OCC enables 8.95X saving in energy.

power due to the high duty cycle ratio ( $114\mu$ s: 600s). This demands the improvement of the efficiency and lowering the inactive power of the system to further increase the longevity of the battery operated system.

Table IV highlights the comparison of our work with other published works on NASA bearing data. None of the work supports online training except for our work. Most of the works used 1 or 2 faulty bearings for multi-class defect classification and achieved 97.5% detection accuracy. Whereas we achieved 100% detection accuracy on both healthy and faulty bearing.

Several works on run time configurable system based on the output quality are captured in Table V. Energy saving in the table largely depends on the algorithm, input data, level of approximation, and approximation among different subsystems. Approximation in three subsystems- sensors, memory and processor are introduced in [14]. Signal sub-sampling at the sensor (camera) reduces the data to be stored and data to be processed, and has immense impact on energy saving. Likewise, [53] tunes threshold dynamically and reduces the pixels to be processed at the subsequent stages and achieved 2.85X energy improvement. Most of the approximation works in the literature are on multimedia application and show their results on existing FPGA board. Whereas, we implement the PdM system in ASIC which can be powered by a single battery cell. To the best of our knowledge, this is the first work

Fig. 16. Power drawn by DC-DC and uP sub-block in (a) active and (b) inactive phase. In the active period, contribution of DC-DC converter to the overall power consumption is only 0.6%.

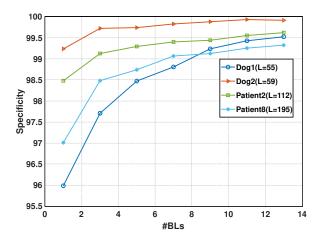

Fig. 17. Specificity curves of EEG dataset [58] for different number of BLs in the network. Sensitivity of 100% is achieved for all the datasets.

which discusses the application of approximate computing throughout the lifetime of the machine.

# VI. CASE STUDY: SEIZURE DETECTION

In order to show that the proposed ADEPOS algorithm is generic, we choose EEG dataset for seizure detection from the UPenn and Mayo Clinics Seizure Detection Challenge database [58]. The database contains 12 EEG datasets among which 8 of those are from human and 4 are from canine subject. Each dataset has 1—second EEG clips labeled "Ictal" for seizure data segments and "Interictal" for non-seizure data segments. The canine data are recorded continuously at 400Hz deploying 16 implanted subdural electrodes. Whereas, the human data are from patients undergoing evaluation for epilepsy surgery sampled at 500Hz or 5000Hz and have varying numbers of electrodes. Despite the dataset has both training and testing data, we choose the training data for training and testing the ADEPOS algorithm because the training data from the dataset are labeled.

We model the seizure detection as a binary classification problem and randomly select 50% interictal and ictal data for training the model and remaining data are used for testing. Although RMS feature is extracted from each EEG clip for training and testing, other statistical features can also be used. In order to show the generalization of ADEPOS algorithm, we choose two canine and two human datasets having 16 electrodes. The specificity curves of four EEG datasets in Figure 17 shows that the specificity increases with a higher number of BLs are ensemble together and exceeds 99.5% when the number of BL is 13. Moreover, we achieve 100% sensitivity for all the four datasets. The best value of L of each BL for each dataset is found out using a linear search.

We apply the proposed ADEPOS algorithm on the EEG dataset and find out the average number of BLs for all the test samples of Dog1, Dog2, Patient2 and Patient8 are 2.92, 2.26, 1.45 and 1.83 respectively. We have estimated the energy consumption of different algorithms and approaches based on Fig. 14 and plotted the normalized energy for different datasets in Fig. 18. It can be seen from Fig. 18 that the ADEPOS enables 6.56X average energy saving on EEG dataset and NG

Fig. 18. Normalized energy saving on EEG dataset deploying ADEPOS and NG algorithm. ADEPOS enables 6.56X average energy saving over B-OCC. NG further reduces the energy requirement by a factor of 2.

approach further reduces the energy consumption by a factor of 2. Moreover, compared to standalone B-OCC, NG reduces 69% program memory footprint for the EEG dataset.

Table VI shows the comparison of the proposed work with other works on the EEG dataset. Both [59] and [60] are using absolute spectral power, relative spectral power and spectral power ratio as features which are more expensive in terms of computation than the RMS feature. The specificity of the proposed method is 99.93% which is higher than the previously reported specificity on the EEG dataset. Moreover, the proposed method achieves 13.1X energy saving.

# VII. CONCLUSION

Aiming at industry 4.0, we have proposed to use OPIUM-B OCC for predictive maintenance deployed in machine health monitoring. OPIUM-B OCC not only consumes lesser energy during learning and inference phase but also has a lower memory footprint than existing AE-OCC. To reduce the energy consumption of PdM sensor further, we have suggested to introduce approximate computing adaptively throughout the lifetime of the machine, since at the early stage of the machine, there will be less degradation in the data. We have shown that the proposed ADEPOS and B-OCC enable an average energy saving of 8.95X without losing any detection accuracy. We have also achieved 13.1X energy saving on the EEG dataset using ADEPOS and NG method together. Moreover, NG enables 64%-69% reduction of the program memory requirement to execute the proposed ADEPOS algorithm. Finally, the synergy between the processor and DC-DC converter helps to reduce the energy further leveraging voltage scaling. The whole system can be powered by a single lithium-ion battery cell and directly deployed for machine health monitoring.

# $\begin{array}{c} {\rm Appendix} \\ {\rm Derivation\ of\ Adaptive\ On\ Time,} \ T_{on} \end{array}$

In the following derivation, we use Figure 6 and all the notations are annotated in the figure.

Once the latch, L1, is set by the rising edge of the  $V_{out}$  comparator output, the capacitor, C, start charging through

TABLE IV COMPARISON WITH OTHER PUBLISHED WORKS ON NASA BEARING DATA

|                    | [54]           | [55]                           | [56]                       | [57]                       | This Work |

|--------------------|----------------|--------------------------------|----------------------------|----------------------------|-----------|

| Algorithm          | SVM-OCC        | WPD and MoG-HMM                | LNPP                       | LAD                        | ELM-OCC   |

| Online Learning    | No             | No                             | No                         | No                         | Yes       |

| #Bearing Used      | 1              | 12                             | 1                          | 2                          | 12        |

| Classification/RUL | OCC            | RUL                            | Multi-class classification | Multi-class classification | OCC       |

| Detection Accuracy | Noise analysis | Estimate remaining useful life | 97.22%                     | 97.5%                      | 100%      |

TABLE V

COMPARISON WITH OTHER PUBLISHED WORKS ON APPROXIMATE COMPUTING

|                                | [9]                                  | [14]                                                                 | [53]                                                            | This Work                  |

|--------------------------------|--------------------------------------|----------------------------------------------------------------------|-----------------------------------------------------------------|----------------------------|

| Approximation level            | Circuit                              | System                                                               | system                                                          | Software                   |

| Approach                       | Reconfigurable<br>Adder & subtractor | adaptive image subsampling, DRAM refresh rate & Computation skipping | Adaptive threshold, keypoint and keypoint description reduction | Dynamic Network<br>Scaling |

| Implementation details & Tech. | FPGA                                 | FPGA                                                                 | ASIC, 40nm CMOS                                                 | ASIC, 65nm CMOS            |

| Application Area               | Multimedia                           | Smart Camera                                                         | IoT Vision                                                      | PdM                        |

| Energy Saving                  | 1.6X                                 | 7.5X                                                                 | 2.85X & 5.7X (Voltage scaling)                                  | 8.95X                      |

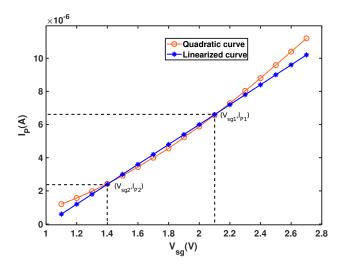

Fig. 19. Linearization of P1 drain current between 1.1V to 2.7V of  $V_{sg}$ . Error in the derivation of overall charging current of capacitor C due to the approximation is less than 9% at  $V_{sg}=1.1\mathrm{V}$  where the resistor current is dominant

P1 and R until the voltage across C reaches  $\frac{2 \cdot V_{batt}}{3}$ . Since the initial and final voltages across R are  $V_{batt}$  and  $\frac{V_{batt}}{3}$  respectively, the average current through R,  $I_R$ , during  $T_{on}$  follows Eq. (22).

$$I_R = \frac{2 \cdot V_{batt}}{3 \cdot R} \tag{22}$$

On the other hand, the current through P1 is quadratic in

TABLE VI

COMPARISON WITH OTHER PUBLISHED WORKS ON EEG DATASET

|               | [59]           | [60]           | This work |  |

|---------------|----------------|----------------|-----------|--|

| Features      | Spectral power | Spectral power | RMS       |  |

| reatures      | and ratios     | and ratios     | KWIS      |  |

| Sensitivity   | 100            | 98.2           | 100       |  |

| Specificity   | 99.9           | 98.88          | 99.93     |  |

| Energy saving | 1X             | 1.53X          | 13.1X     |  |

nature and shown in Eq. (23) where k depends on the process and the aspect ratio of P1 and  $V_{th}$  denotes the threshold voltage of P1.

$$I_P = k \cdot (V_{sg} - |V_{th}|)^2$$

(23)

Since the  $V_{sg}$  of P1 varies between 1.1V to 2.7V based on the  $V_{batt}$  and  $V_{out}$  variation, we linearize Eq. (23) in this range which follows Eq. (24) and is also shown in Fig. 19.

$$I_P = k_3 \cdot V_{sq} + k_4 \tag{24}$$

$$k_3 = k \cdot (V_{sq1} + V_{sq2} - 2|V_{th}|) \tag{25}$$

$$k_4 = I_{P1} - k \cdot V_{sq1} \cdot (V_{sq1} + V_{sq2} - 2|V_{th}|) \tag{26}$$

TABLE VII PVT VARIATION OF  $T_{on}$

| $V_{batt} = 3.3 V$ |              | $V_{batt} = 2.5 V$ |              |  |

|--------------------|--------------|--------------------|--------------|--|

| P/T                | $T_{on}(nS)$ | P/T                | $T_{on}(nS)$ |  |

| tt/27              | 317          | tt/27              | 416          |  |

| ss/125             | 393          | ss/125             | 480          |  |

| ff/-40             | 267          | ff/-40             | 352          |  |

Hence, the adaptive on time,  $T_{on}$ , can be derived as follows

$$T_{on} = \frac{k1 \cdot V_{batt}}{(k2 \cdot V_{batt} - k3 \cdot V_{out}) + k4} \tag{27}$$

$$k1 = \frac{2C}{3} \tag{28}$$

$$k2 = k_3 + \frac{2}{3R} \tag{29}$$

Table VII captures the simulation results of PVT variation of  $T_{on}$  at  $V_{batt}=3.3\mathrm{V}$  and 2.5V. At lower  $V_{batt}, T_{on}$  increases which in turn reduces output voltage variation. Across process and temperature  $T_{on}$  shows -23% to 19% variation which can be corrected by trimming R and P1.

#### ACKNOWLEDGMENT

This work was conducted within the Delta-NTU Corporate Lab for Cyber-physical Systems with funding support from Delta Electronics Inc. and the National Research Foundation (NRF) Singapore under the Corp Lab @University scheme.

#### REFERENCES

- V. M. Janakiraman and D. Nielsen, "Anomaly detection in aviation data using extreme learning machines," in 2016 International Joint Conference on Neural Networks (IJCNN), pp. 1993–2000, July 2016.

- [2] H. Qiu, J. Lee, J. Lin, and G. Yu, "Wavelet filter-based weak signature detection method and its application on rolling element bearing prognostics," *Journal of Sound and Vibration*, vol. 289, no. 4-5, pp. 1066–1090, 2006.

- [3] P. Girdhar and C. Scheffer, "1 Predictive maintenance techniques: Part 1 predictive maintenance basics," *Practical Machinery Vibration Analysis and Predictive Maintenance*, pp. 1–10, 2004.

- [4] S. Porotsky and Z. Bluvband, "Remaining useful life estimation for systems with non-trendability behaviour," PHM 2012 - 2012 IEEE Int. Conf. on Prognostics and Health Management: Enhancing Safety, Efficiency, Availability, and Effectiveness of Systems Through PHM Technology and Application, Conference Program, 2012.

- [5] J. Lin, W. Yu, N. Zhang, X. Yang, H. Zhang, and W. Zhao, "A survey on internet of things: Architecture, enabling technologies, security and privacy, and applications," *IEEE Internet of Things Journal*, vol. 4, pp. 1125–1142, Oct 2017.

- [6] A. Basu, J. Acharya, T. Karnik, H. Liu, H. Li, J. S. Seo, and C. Song, "Low-Power, Adaptive Neuromorphic Systems: Recent Progress and Future Directions," *IEEE Journal on Emerging and Selected Topics in Circuits and Systems*, vol. 8, no. 1, pp. 6–27, 2018.

- [7] R. Jain, B. M. Geuskens, S. T. Kim, M. M. Khellah, J. Kulkarni, J. W. Tschanz, and V. De, "A 0.451 v fully-integrated distributed switched capacitor dc-dc converter with high density mim capacitor in 22 nm trigate cmos," *IEEE Journal of Solid-State Circuits*, vol. 49, pp. 917–927, April 2014.

- [8] R. Want, B. N. Schilit, and S. Jenson, "Enabling the internet of things," *Computer*, vol. 48, pp. 28–35, Jan 2015.

- [9] A. Raha, H. Jayakumar, Raghunathan, and Vijay, "Input-Based Dynamic Reconfiguration of Approximate Arithmetic Units for Video Encoding," *IEEE Transactions on Very Large Scale Integration (VLSI) Systems*, pp. 1–12, 2015.

- [10] S. L. Lu, "Speeding up processing with approximation circuits," Computer, vol. 37, no. 3, pp. 67–73, 2004.

- [11] A. Lingamneni, A. Basu, C. Enz, K. V. Palem, and C. Piguet, "Improving energy gains of inexact dsp hardware through reciprocative error compensation," in 2013 50th ACM/EDAC/IEEE Design Automation Conference (DAC), pp. 1–8, May 2013.

- [12] P. Kulkarni, P. Gupta, and M. Ercegovac, "Trading accuracy for power with an underdesigned multiplier architecture," *Proceedings of the IEEE International Conference on VLSI Design*, pp. 346–351, 2011.

- [13] A. Gupta, S. Mandavalli, V. J. Mooney, K. Ling, A. Basu, H. Johan, and B. Tandianus, "Low power probabilistic floating point multiplier design," in 2011 IEEE Computer Society Annual Symposium on VLSI, pp. 182–187, July 2011.

- [14] A. Raha and V. Raghunathan, "Towards Full-System Energy-Accuracy Tradeoffs," Proceedings of the 54th Annual Design Automation Conference 2017 on - DAC '17, pp. 1–6, 2017.

- [15] A. Raha and V. Raghunathan, "Approximating beyond the Processor: Exploring Full-System Energy-Accuracy Tradeoffs in a Smart Camera System," *IEEE Transactions on Very Large Scale Integration (VLSI)* Systems, vol. 26, no. 12, pp. 2884–2897, 2018.

- [16] S. Kadiyala, A. Sen, S. Mahajan, Q. Wang, A. Lingamneni, J. German, H. Xu, K. V. Palem, and A. Basu, "An Optimum Inexact Design for an Energy Efficient Hearing Aid," *Journal of Low Power Electronics*, vol. 15, no. 2, pp. 129–143, 2019.

- [17] A. Rao, "Application of auto associative neural network for aero engine control system sensor fault detection, isolation and accommodation," *DRDO Science Spectrum*, pp. 12–15, Mar. 2009.

- [18] J. Sanz, R. Perera, and C. Huerta, "Fault diagnosis of rotating machinery based on auto-associative neural networks and wavelet transforms," *Journal of Sound and Vibration*, vol. 302, no. 4, pp. 981 – 999, 2007.

- [19] S. S. Khan and M. G. Madden, "One-class classification: taxonomy of study and review of techniques," *The Knowledge Engineering Review*, vol. 29, no. 3, p. 345374, 2014.

- [20] M. Roy, S. K. Bose, B. Kar, P. K. Gopalakrishnan, and A. Basu, "A Stacked Autoencoder Neural Network based Automated Feature Extraction Method for Anomaly detection in On-line Condition Monitoring," Proceedings of the 2018 IEEE Symposium Series on Computational Intelligence, SSCI 2018, pp. 1501–1507, 2019.

- [21] S. K. Bose, B. Kar, M. Roy, P. K. Gopalakrishnan, and A. Basu, "Adepos: Anomaly detection based power saving for predictive maintenance using edge computing," in *Proceedings of the 24th Asia and South Pacific Design Automation Conference*, ASPDAC '19, (New York, NY, USA), pp. 597–602, ACM, 2019.

- [22] G.-B. Huang, Q.-Y. Zhu, and C.-K. Siew, "Extreme learning machine: Theory and applications," *Neurocomputing*, vol. 70, no. 1, pp. 489 – 501, 2006. Neural Networks.

- [23] Y. Zhang, J. Wu, Z. Cai, B. Du, and P. S. Yu, "An unsupervised parameter learning model for RVFL neural network," *Neural Networks*, vol. 112, pp. 85–97, 2019.

- [24] A. Rahimi and B. Recht, "Weighted sums of random kitchen sinks: Replacing minimization with randomization in learning," *Advances in neural information processing*..., vol. 1, no. 1, pp. 1–8, 2009.

- [25] R. Penrose, "A generalized inverse for matrices," Mathematical Proceedings of the Cambridge Philosophical Society, vol. 51, pp. 406–413, July 1954.

- [26] J. Tapson and A. van Schaik, "Learning the pseudoinverse solution to network weights," *Neural Networks*, vol. 45, pp. 94 – 100, 2013. Neuromorphic Engineering: From Neural Systems to Brain-Like Engineered Systems.

- [27] N. Liang, G. Huang, P. Saratchandran, and N. Sundararajan, "A fast and accurate online sequential learning algorithm for feedforward networks," *IEEE Transactions on Neural Networks*, vol. 17, pp. 1411–1423, Nov 2006.

- [28] A. van Schaik and J. Tapson, "Online and adaptive pseudoinverse solutions for elm weights," *Neurocomputing*, vol. 149, pp. 233 – 238, 2015. Advances in neural networks Advances in Extreme Learning Machines.

- [29] V. K. Chippa, S. Venkataramani, S. T. Chakradhar, K. Roy, and A. Raghunathan, "Approximate computing: An integrated hardware approach," in 2013 Asilomar Conference on Signals, Systems and Computers, pp. 111–117, Nov 2013.

- [30] B. Moons and M. Verhelst, "An energy-efficient precision-scalable convnet processor in 40-nm cmos," *IEEE Journal of Solid-State Circuits*, vol. 52, pp. 903–914, April 2017.

- [31] D. Mohapatra, V. K. Chippa, A. Raghunathan, and K. Roy, "Design of voltage-scalable meta-functions for approximate computing," in 2011 Design, Automation Test in Europe, pp. 1–6, March 2011.

- [32] L. K. Hansen and P. Salamon, "Neural network ensembles," *IEEE Trans. Pattern Anal. Mach. Intell.*, vol. 12, pp. 993–1001, Oct. 1990.

- [33] S. H. Wang, H. T. Li, and A. Y. A. Wu, "Error-resilient reconfigurable boosting extreme learning machine for ecg telemonitoring systems," in 2018 IEEE International Symposium on Circuits and Systems (ISCAS), pp. 1–5, May 2018.

- [34] F. Moya Rueda, R. Grzeszick, and G. A. Fink, "Neuron pruning for compressing deep networks using maxout architectures," *Lecture Notes* in Computer Science (including subseries Lecture Notes in Artificial Intelligence and Lecture Notes in Bioinformatics), vol. 10496 LNCS, pp. 177–188, 2017.

- [35] Y. Chen, Z. Wang, A. Patil, and A. Basu, "A 2.86-TOPS/W Current Mirror Cross-Bar-Based Machine-Learning and Physical Unclonable Function Engine For Internet-of-Things Applications," *IEEE Transac*tions on Circuits and Systems 1: Regular Papers, vol. PP, pp. 1–13, 2019

- [36] "openmsp430 :: Overview." https://opencores.org/projects/openmsp430.

- [37] M. Seok, G. Kim, D. Blaauw, and D. Sylvester, "A portable 2-transistor picowatt temperature-compensated voltage reference operating at 0.5 v," *IEEE Journal of Solid-State Circuits*, vol. 47, pp. 2534–2545, Oct 2012.

- [38] H. Nam, Y. Ahn, and J. Roh, "A buck converter with adaptive on-time pfm control and adjustable output voltage," *Analog Integrated Circuits* and Signal Processing, vol. 71, pp. 327–332, May 2012.

- [39] M. A. Khalil, E. Hegazi, and M. El-Nozahi, "Low-ripple pfm buck converter employing background calibration," in 2018 IEEE International Symposium on Circuits and Systems (ISCAS), pp. 1–4, May 2018.

- [40] B. Sahu and G. A. Rincón-Mora, "An accurate, low-voltage, CMOS switching power supply with adaptive on-time pulse-frequency modulation (PFM) control," *IEEE Transactions on Circuits and Systems 1: Regular Papers*, vol. 54, no. 2, pp. 312–321, 2007.

- [41] "Nasa dataset." https://ti.arc.nasa.gov/tech/dash/groups/pcoe/prognostic-data-repository/.

- [42] H. Martin and F. Honarvar, "Application of statistical moments to bearing failure detection," *Applied Acoustics*, vol. 44, no. 1, pp. 67 77, 1995.

- [43] M. E. H. Benbouzid, "A review of induction motors signature analysis as a medium for faults detection," *IEEE Transactions on Industrial Electronics*, vol. 47, pp. 984–993, Oct 2000.

- [44] Z. Peng and F. Chu, "Application of the wavelet transform in machine condition monitoring and fault diagnostics: a review with bibliography," *Mechanical Systems and Signal Processing*, vol. 18, no. 2, pp. 199 – 221, 2004.

- [45] S. Chandar A P, S. Lauly, H. Larochelle, M. Khapra, B. Ravindran, V. C. Raykar, and A. Saha, "An autoencoder approach to learning bilingual word representations," in *Advances in Neural Information Processing Systems* 27 (Z. Ghahramani, M. Welling, C. Cortes, N. D. Lawrence, and K. Q. Weinberger, eds.), pp. 1853–1861, Curran Associates, Inc., 2014

- [46] A. Droniou and O. Sigaud, "Gated Autoencoders with Tied Input Weights," in *International Conference on Machine Learning*, (United States), pp. 1–9, 2013.

- [47] D. P. Kingma and J. Ba, "Adam: A method for stochastic optimization," CoRR, vol. abs/1412.6980, 2014.

- [48] "TPS62736 datasheet." http://www.ti.com/lit/ds/symlink/tps62737.pdf.

- [49] W. Fu, S. T. Tan, M. Radhakrishnan, R. Byrd, and A. A. Fayed, "A DCM-Only Buck Regulator With Hysteretic-Assisted Adaptive Minimum-On-Time Control for Low-Power Microcontrollers," *IEEE Transactions on Power Electronics*, vol. 31, no. 1, pp. 418–429, 2016.

- [50] A. Paidimarri and A. P. Chandrakasan, "A Wide Dynamic Range Buck Converter with Sub-nW Quiescent Power," *IEEE Journal of Solid-State Circuits*, vol. 52, no. 12, pp. 3119–3131, 2017.

- [51] H. Jayakumar, A. Raha, and V. Raghunathan, "Hypnos: An ultralow power sleep mode with SRAM data retention for embedded microcontrollers," 2014 International Conference on Hardware/Software Codesign and System Synthesis, CODES+ISSS 2014, 2014.

- [52] "INA210 datasheet." http://www.ti.com/lit/ds/symlink/ina210.pdf.

- [53] A. B. Alvarez, G. Ponnusamy, and M. Alioto, "EQSCALE: Energy-quality scalable feature extraction engine for Sub-mW real-time video processing with 0.55 mm2area in 40nm CMOS," 2017 IEEE Asian Solid-State Circuits Conference, A-SSCC 2017 Proceedings, vol. 2017-Janua, no. 2015, pp. 241–244, 2017.

- [54] D. Martinez-Rego, O. Fontenla-Romero, and A. Alonso-Betanzos, "Power wind mill fault detection via one-class ν-SVM vibration signal analysis," Proceedings of the International Joint Conference on Neural Networks, no. July, pp. 511–518, 2011.

- [55] D. A. Tobon-Mejia, K. Medjaher, N. Zerhouni, and G. Tripot, "A data-driven failure prognostics method based on mixture of Gaussian hidden Markov models," *IEEE Transactions on Reliability*, vol. 61, no. 2, pp. 491–503, 2012.

- [56] J. Yu, "Local and nonlocal preserving projection for bearing defect classification and performance assessment," *IEEE Transactions on Industrial Electronics*, vol. 59, no. 5, pp. 2363–2376, 2012.

- [57] S. Yacout, "Logical analysis of maintenance and performance data of physical assets, ID34," *Proceedings - Annual Reliability and Maintain-ability Symposium*, pp. 1–6, 2012.

- [58] "Upenn and mayo clinics seizure detection challenge. USA." https://www.kaggle.com/c/seizure-detection.

- [59] Z. Zhang and K. K. Parhi, "Seizure detection using regression tree based feature selection and polynomial SVM classification," *Proceedings of the Annual International Conference of the IEEE Engineering in Medicine and Biology Society, EMBS*, vol. 2015-Novem, pp. 6578–6581, 2015.

- [60] S. Koteshwara and K. K. Parhi, "Incremental-precision based feature computation and multi-level classification for low-energy internet-ofthings," *IEEE Journal on Emerging and Selected Topics in Circuits and* Systems, vol. 8, no. 4, pp. 822–835, 2018.