# A Fully Synthesizable Fractional-*N* MDLL With Zero-Order Interpolation-Based DTC Nonlinearity Calibration and Two-Step Hybrid Phase Offset Calibration

Bangan Liu<sup>®</sup>, Member, IEEE, Yuncheng Zhang<sup>®</sup>, Graduate Student Member, IEEE,

Junjun Qiu, Graduate Student Member, IEEE, Huy Cu Ngo<sup>®</sup>, Member, IEEE,

Wei Deng<sup>10</sup>, Senior Member, IEEE, Kengo Nakata, Toru Yoshioka, Jun Emmei,

Jian Pang<sup>(D)</sup>, Member, IEEE, Aravind Tharayil Narayanan<sup>(D)</sup>, Senior Member, IEEE,

Haosheng Zhang<sup>10</sup>, Member, IEEE, Teruki Someya<sup>10</sup>, Member, IEEE,

Atsushi Shirane, Member, IEEE, and Kenichi Okada<sup>10</sup>, Senior Member, IEEE

Abstract—In this paper, a fully-synthesizable digital-to-time (DTC)-based fractional-N multiplying delay-locked loop (MDLL) is presented. Noise and linearity of synthesizable DTCs are analyzed, and a two-stage synthesizable DTC is proposed in which a path-selection DTC is used as the coarse stage and a variable-slope DTC is used as the fine stage. To calibrate the DTC nonlinearity, a highly robust zero-order interpolation based nonlinearity calibration is proposed. Besides, the static phase offsets (SPO) between bang-bang phase detector (BBPD) and multiplexer (MUX) are calibrated by a proposed hybrid analog/digital phase offset calibration, while the dynamic phase offsets (DPO) are removed by a proposed complementary switching scheme. The co-design of the analog circuits and digital calibrations enable excellent jitter and spur performance. The MDLL achieves 0.70 and 0.48 ps root-mean-square (RMS) jitter in fractional-N and integer-N modes, respectively. The fractional spur is less than -59.0 dBc, and the reference spur is -64.5 dBc. The power consumptions are 1.85 mW and 1.22 mW, corresponding to figures of merit (FOM) of -240.4 dB and -245.5 dB.

*Index Terms*—Multiplying delay-locked loop (MDLL), phase-locked loop (PLL), injection locking, fully-synthesizable, digital-to-time converter (DTC), nonlinearity calibration, variable-slope DTC, path-selection DTC, phase offset, bang-bang phase detector (BBPD).

Manuscript received April 26, 2020; revised August 16, 2020 and September 28, 2020; accepted October 27, 2020. Date of publication November 16, 2020; date of current version January 12, 2021. This work was supported by the New Energy and Industrial Technology Development Organization (NEDO). This article was recommended by Associate Editor N. Krishnapura. (*Corresponding author: Bangan Liu.*)

Bangan Liu, Yuncheng Zhang, Junjun Qiu, Huy Cu Ngo, Kengo Nakata, Toru Yoshioka, Jun Emmei, Jian Pang, Aravind Tharayil Narayanan, Haosheng Zhang, Atsushi Shirane, and Kenichi Okada are with the Department of Electrical and Electronic Engineering, Tokyo Institute of Technology, Tokyo 152-8550, Japan (e-mail: liub@ssc.pe.titech.ac.jp).

Wei Deng is with the Department of Microelectronics and Nanoelectronics, Tsinghua University, Beijing 100084, China.

Teruki Someya is with the Electronic Instrumentation Laboratory, Delft University of Technology, 2628 Delft, The Netherlands.

Color versions of one or more of the figures in this article are available online at https://ieeexplore.ieee.org.

Digital Object Identifier 10.1109/TCSI.2020.3035373

## I. INTRODUCTION

S CMOS processes reach sub-20nm scales, various challenges complicate the analog/mixed-signal circuit design, such as low supply, high variations and limited model accuracy [1]. Therefore fully-synthesizable designs are becoming more attractive. Significant efforts have been devoted to realizing fully synthesizable PLLs [2]–[12], data converters [13], and wireless transceivers [14]–[16].

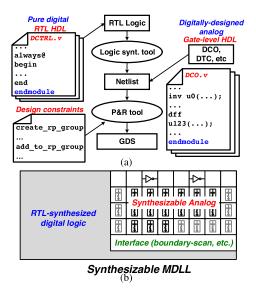

Fig. 1(a) shows the design and implementation flow of a fully-synthesizable MDLL as a "soft" intellectual property (IP). Digitally designed analog circuits such as digitally controlled oscillator (DCO), digital-to-time converter (DTC) are designed with standard cells and are described in a gate-level netlist. Whereas the digital control logic is described in register-transfer level (RTL) hardware description language (HDL) code. The physical implementation is carried out using the standard digital place and route (P&R) tools. Such a flow eliminates the burden of manual layout design with complex design rules, which is especially problematic in sub-20 nm FinFET processes. However, high systemic mismatches from P&R have severely constrained the fully-synthesizable designs, making their performance inferior to their manually designed counterparts. While techniques such as relative placement [17] and region constraints can be used to reduce the P&R systemic mismatches, as shown in Fig. 1(b), the mismatches from routing cannot be eliminated. Therefore, new circuit topologies that are friendly for digital synthesis must be devised. Besides, efficient calibrations are required to mitigate the non-idealities in synthesizable circuits.

In this paper, a fully-synthesizable fractional-*N* DTC-based MDLL is presented. A synthesizable DTC architecture is proposed, with a thorough analysis and optimization of jitter, power, and nonlinearity. A robust digital nonlinearity calibration that is suitable for the synthesizable DTC is proposed. Besides, to reduce the reference spurs, hybrid analog-digital calibrations are proposed to reduce both static and dynamic phase offsets to levels sufficiently below thermal noise floor.

This work is licensed under a Creative Commons Attribution 4.0 License. For more information, see https://creativecommons.org/licenses/by/4.0/

Fig. 1. Design of a fully-synthesizable MDLL, (a) digital compatible design process, (b) synthesized layout with relative placement and region constraints.

The remainder of this paper is organized as follows. Section II presents the system overview of the proposed fractional-*N* MDLL. Design considerations and optimizations of the fully-synthesizable DTC are explained in Section III, and the proposed DTC nonlinearity calibration is presented in Section IV. Phase offset calibration in MDLL is presented in Section V. Detailed circuit implementations are explained in Section VI, and measurement results are presented and analyzed in Section VII. Section VIII concludes the paper.

## II. FULLY-SYNTHESIZABLE MDLL System Architecture

A variety of injection-locked PLLs (IL-PLLs) and MDLLs have been developed in recent years [3], [5], [7]–[9], [11], [12], [18]–[32]. Due to the high bandwidth offered by the IL-PLLs/MDLLs, excellent jitter performance has been achieved. However, inherently ILPLLs/MDLLs are limited to integer-N operation, whereas in many applications fractional-Noperation is desired. To extend injection locking to fractional-N operation, various architectures have been proposed [7], [18], [33]. In this study, a DTC-based MDLL architecture is adopted. The DTC is placed on the reference path to introduce a time-varying delay to the injection signal, thereby enabling the realization of fractional-N injection locking.

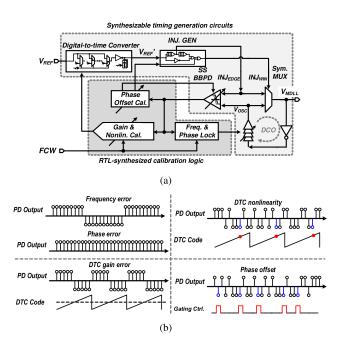

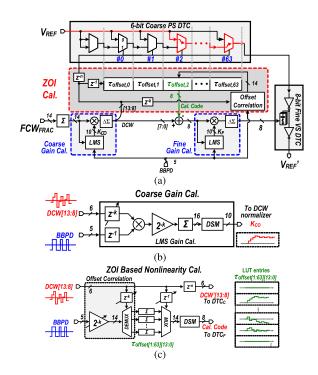

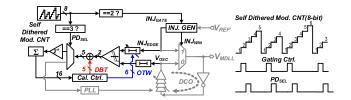

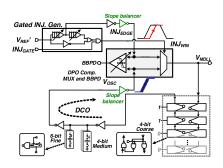

The system diagram of the proposed fractional-N MDLL is shown in Fig. 2(a). The upper part contains the synthesizable timing generation blocks, which consists of a DTC, an injection edge and window generator, a DCO, a symmetrical MUX, and a sub-sampling (SS) BBPD. However, the MDLL has various non-idealities which degrade the performance. Therefore, extensive digital background calibrations are integrated, which are shown in the bottom part of Fig. 2(a). First of all, the DCO frequency and phase error are calibrated by the frequency lock loop (FLL) and PLL to ensure correct frequency and phase alignment. Besides, the DTC gain, which is defined as the output delay versus input digital control code, is calibrated by a least-mean-square (LMS) based gain calibration. The DTC nonlinearity, which causes in-band fractional spurs, is calibrated with a proposed zero-order interpolation based nonlinearity calibration. Moreover, the phase offsets between the MUX and BBPD cause large reference spurs and needed to

Fig. 2. (a) System diagram of proposed fully-synthesizable DTC-based fractional-*N* MDLL, and (b) conceptual waveform of simultaneous calibration operations.

be minimized. The phase offsets include both static ones which are caused by systemic mismatch from P&R and dynamic ones which are caused by the time-varying injection control signal. The static phase offsets are calibrated by a two-step analog/digital hybrid offset calibration schemes, in which the offset can be calibrated with arbitrarily fine resolution. For the dynamic phase offsets, a complementary-switching MUX/BBPD is proposed.

All of the calibrations utilize the same BBPD output, which ensures the calibration results are consistent and free of mismatch. The system nonidealities, such as frequency/phase error, DTC gain error and nonlinearity, and phase offset exhibit different statistic distribution, and are correlative to different control signal sequences, as shown in Fig. 2(b). By setting independent calibration control signal sequences and proper bandwidths, all the calibration could operate simultaneously in background.

#### III. MULTI-STAGE FULLY-SYNTHESIZABLE DTC

DTCs have found extensive usage in high performance PLLs. Many different DTC implementations have been devised, such as constant-slope (CS) [34]–[38], variable-slope (VS) [39]–[42], and path-selection (PS) based topologies [10], [19], [43], [44]. Considering the feasibility of standard cell implementation, VS and PS DTCs are preferred. However, these two DTC architectures have different noise and nonlinearity characteristics, which merit careful examinations to find the optimal architecture.

#### A. Jitter-Power Analysis

The jitter variance  $J_{\text{DTC,VS}}$  (unit is s<sup>2</sup>) and power  $P_{\text{DTC,VS}}$  (unit is mW) product of a VS DTC can be expressed as [45]

$$J_{\text{DTC,VS}} \cdot P_{\text{DTC,VS}} = 4kT \cdot \left[1 + \frac{2\gamma V_{\text{DD}}}{V_{\text{OV,N}}}\right] \cdot f_{\text{REF}} \cdot t_{\text{TOT,VS}}^2$$

$$= C \cdot t_{\text{TOT,VS}}^2 \tag{1}$$

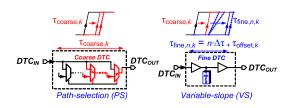

Fig. 3. Synthesizable path-selection DTC and variable-slope DTC.

where k is the Boltzmann constant, T is the temperature,  $t_{\text{TOT, VS}}$  is the total delay of VS DTC,  $f_{\text{REF}}$  is the reference frequency. The  $\gamma$  is the excessive noise factor,  $V_{\text{DD}}$  is the supply voltage,  $V_{\text{OV,N}}$  the over-drive voltage of NMOS transistor, and C is  $4kT \cdot [1 + \frac{2\gamma V_{\text{DD}}}{V_{\text{OV,N}}}] \cdot f_{\text{REF}}$ . However, the full scale tunable range of VS DTC  $t_{\text{FS, VS}}$  is a fraction of the total delay  $t_{\text{TOT, VS}}$ . Effects such as the limited ON/OFF capacitance ratio of digital varactors causes considerable fixed delay offset. For synthesizable not-and (NAND)-3 based digital varactors, the ON/OFF ratio  $k_{\text{ON/OFF}}$  is approximately 3/2 [11], thus

$$J_{\text{DTC,VS}} \cdot P_{\text{DTC,VS}} = C \cdot (k_{\text{var}} \cdot t_{\text{FS,VS}})^2$$

(2)

$$k_{var} = \frac{t_{\text{TOT,VS}}}{t_{\text{FS,VS}}} = \frac{k_{\text{ON/OFF}}}{k_{\text{ON/OFF}} - 1} \approx 3 \quad (3)$$

where  $k_{\text{var}}$  is ratio between  $t_{\text{TOT}}$  and  $t_{\text{FS}}$ .

On the other hand, PS DTCs tune delay by selecting N delay cells, and the delay offset is negligible, therefore the full scale tunable range  $t_{\text{FS,PS}}$  is approximately equal to total delay  $t_{\text{TOT,PS}}$ . Assuming the noise of each delay cell is independent, the jitter-power product of PS DTC can be expressed as

$$J_{\text{DTC,PS}} \cdot P_{\text{DTC,PS}} = (N \cdot J_{\text{DTC,PS,0}}) \cdot (N \cdot P_{\text{DTC,PS,0}})$$

$$= N^2 \cdot C \cdot (\frac{t_{\text{FS,PS}}}{N})^2 = C \cdot t_{\text{FS,PS}}^2 \quad (4)$$

Thus, the jitter-power product of a VS DTC is  $k_{var}^2$  times worse than a PS DTC.

However, the PS DTC resolution  $t_{\text{RES,PS}}$  is larger than 20 ps in a 65 nm CMOS process. Therefore, a two-stage PS + VS DTC is proposed, as shown in Fig. 3. The proposed two-stage DTC provides a better jitter/power tradeoff. For a given delay range  $t_{\text{FS}}$  and jitter  $J_{\text{DTC}}$ , the power consumption of a one-stage VS DTC can be expressed as

$$P_{\text{DTC,one-stage}} = \frac{C \cdot (k_{\text{var}} \cdot t_{\text{FS}})^2}{J_{\text{DTC}}}$$

(5)

On the other hand, assuming the VS DTC range  $t_{\text{FS,VS}}$  equals to  $n \cdot t_{\text{RES,PS}}$ , in which *n* is a over-design factor larger than 1 to account for margins for PVT and nonlinearity calibration. The PS DTC and VS DTC contribute  $(1 - k_{\text{jitter}}) \cdot J_{\text{DTC}}$  and  $k_{\text{jitter}} \cdot J_{\text{DTC}}$  respectively, in which  $k_{\text{jitter}}$  is the jitter contribution ratio. The power consumption of proposed two-stage DTC is

$$P_{\text{DTC,two-stage}} = P_{\text{DTC,PS}} + P_{\text{DTC,VS}}$$

$$= \frac{1}{1 - k_{\text{jitter}}} \cdot \frac{C \cdot t_{\text{FS}}^2}{J_{\text{DTC}}} + \frac{1}{k_{\text{jitter}}}$$

$$\cdot \frac{C \cdot (k_{\text{var}} \cdot n \cdot t_{\text{RES,PS}})^2}{J_{\text{DTC}}}$$

(6)

The optimal  $k_{\text{jitter,opt}}$  for the minimum power consumption  $P_{\text{DTC,two-stage,min}}$  can be expressed as

k

$$z_{\text{jitter,opt}} = \frac{1}{1 + \frac{t_{\text{FS}}}{k_{\text{var}} \cdot n \cdot t_{\text{RES,PS}}}}$$

(7)

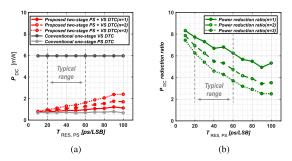

Fig. 4. Power consumption (a) and ratio (b) of one-stage VS DTC and the proposed two-stage PS-VS DTC at different  $T_{\text{RES,PS}}$  and over-design factor *n*. The  $t_{\text{FS}}$  is 1 ns,  $J_{\text{DTC}}$  is  $(0.1 \text{ ps})^2$ , and  $k_{\text{var}}$  is 3.

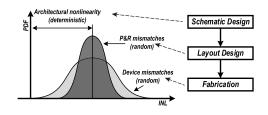

Fig. 5. Conceptual composition of DTC nonlinearities.

$$P_{\text{DTC,two-stage,min}} = \frac{C \cdot t_{\text{FS}}^2}{J_{\text{DTC}}} \cdot (1 + \frac{k_{\text{var}} \cdot n \cdot t_{\text{RES,PS}}}{t_{\text{FS}}})^2 \quad (8)$$

$$\frac{P_{\text{DTC,two-stage,min}}}{P_{\text{DTC,one-stage}}} = \left(\frac{1}{k_{\text{var}}} + \frac{n \cdot t_{\text{RES,PS}}}{t_{\text{FS}}}\right)^2 \tag{9}$$

Since  $k_{var}$  is determined by technology, and  $t_{FS}$  is determined by MDLL system architecture, only  $t_{RES,PS}$  and *n* are available for optimization. The relationship between power consumption and  $t_{RES,PS}$  with different *n* is shown in Fig. 4. The proposed two-stage DTC reduces the power consumption by about than 7.3 times from 6 mW to 0.817 mW when  $t_{RES,PS}$  is 30 ps/LSB and *n* equals to 1. Even in consideration of margins for PVT variations and calibrations, in which a large over-design factor *n* equals to 3 is adopted, the power saving is 5.4 times with 30 ps/LSB  $t_{RES,PS}$ , validating the advantage in the power efficiency.

## B. Nonlinearity Analysis

The jitter analysis predicts the minimum power consumption required for a given jitter. However, practical DTCs often have much higher power consumption to meet linearity requirements [42]. The major nonlinearity sources of DTCs include 1) device mismatches, 2) systemic mismatches from P&R, and 3) architectural nonlinearity from circuit effects such as nonlinear slope-dependent propagation delay [39], [41], [42], [46]. These nonlinearity sources come from different design phases, and have different properties, as shown in Fig. 5. The architectural nonlinearity is deterministic and can be predicted with schematic simulation. On the other hand, nonlinearities from device mismatches and systemic mismatches from P&R are statistical and follow normal distribution [47]. The systemic mismatches from P&R are introduced during layout design, whereas the device mismatches are introduced in chip fabrication. Therefore, the nonlinearity of a fabricated DTC can be expressed as

$$\mu_{\rm INL,tot} = \mu_{\rm INL,Arch.} \tag{10}$$

$$\sigma_{\rm INL,tot} = \sqrt{\sigma_{\rm INL,Dev.}^2 + \sigma_{\rm INL,P\&R}^2}$$

(11)

TABLE I IMPLEMENTATION OF DTCs AND ASSOCIATED NONLINEARITY CALIBRATION

|              | Synth.?             | DTC design          | INL/DNL before Cal.* | Cal.             | INL/DNL after Cal.* |

|--------------|---------------------|---------------------|----------------------|------------------|---------------------|

| JSSC'14 [39] | No                  | 6-bit VS + 6-bit VS | 1.2%/0.1%            | 4-bit 1st-order  | 0.1%/0.1%           |

| JSSC'15 [19] | No                  | 7-bit PS + 6-bit VS | NA                   | 4-bit 1st-order  | NA                  |

| JSSC'16 [48] | No                  | 10-bit VS           | 0.2%/0.05%           | 5-bit 1st-order  | NA                  |

| This work    | Yes                 | 6-bit PS + 8-bit VS | 0.75%/1.5%           | 6-bit 1st-order  | 0.75%/1.5%          |

| THIS WOLK    | 103 0-01113 + 8-011 | 0-0115 - 0-011 45   | 0.15/0/1.5/0         | 6-bit zero-order | 0.05%/0.05%         |

Normalized to DTC full-scale range.

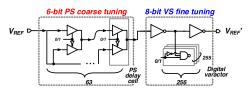

Fig. 6. Simulated peak INL of (a) PS DTC (b) VS DTC. The PS DTC has 6-bit with resolution of 33.2 ps, and VS DTC has 8-bit with resolution of 0.43 ps. The peak INLs due to device mismatches and P&R systemic matches are  $3\sigma$  values. Both PS and VS DTC INL are normalized to VS DTC resolution (0.43 ps/LSB).

where  $\mu_{\text{INL,tot}}$  is the mean of total DTC integral nonlinearity (INL),  $\mu_{\text{INL,Arch.}}$  is the mean of INL from architectural nonlinearity. The  $\sigma_{\text{INL,tot}}$  is the total standard deviation of DTC INL, and  $\sigma_{\text{INL,Dev.}}$  and  $\sigma_{\text{INL,P&R}}$  are standard deviations of INL from device mismatches and P&R respectively.

In conventional custom-designed DTCs, the  $\sigma_{INL,P\&R}$ is minimized by meticulous layout design. The  $\sigma_{INL,Dev.}$ can be reduced by increasing device sizes and thus power consumption. Therefore, the  $\mu_{INL,Arch.}$  dominates the overall nonlinearity. However, the synthesizable DTCs have different nonlinearity characteristic when used as soft IPs. The  $\sigma_{\text{INL},\text{P&R}}$  and  $\sigma_{\text{INL},\text{Dev.}}$  have contradicting trends with regard to device sizes. To see the difference, the simulated  $\sigma_{INL,P\&R}$ ,  $\sigma_{\rm INL, Dev.}$  and  $\mu_{\rm INL, Arch.}$  of PS DTCs and VS DTCs at different sizes are shown in Fig. 6. As clear from the figure, the VS DTC has large  $\mu_{INL,Arch.}$ . Besides, the  $\sigma_{INL,Dev.}$  is inversely proportional to device size, whereas the  $\sigma_{INL,P\&R}$  is proportional. To the first order, longer routing lines are used in larger devices, which have larger resistance and variations. Therefore, there is an optimal device size which gives the minimum  $\sigma_{INL,tot}$ . For PS DTC, similar trends are observed, except that the  $\mu_{INL,Arch.}$  is much smaller than  $\sigma_{INL,Dev.}$ and  $\sigma_{INL,P\&R}$ . Besides, the peak INL PS DTC is larger than 20 LSBs, which is much larger than the fine VS DTCs. Therefore, the nonlinearity of the proposed two-stage PS+VS DTC is dominated by the PS stage. Consequently, the scaling trend and the optimal device sizing of proposed two-stage DTC are basically the same as the PS DTC, and VS DTC only marginally degrade the overall INL.

## IV. ZERO-ORDER INTERPOLATION NONLINEARITY CALIBRATION

## A. Calibration of Mismatch Dominated DTC

Look-up table (LUT) based piece-wise linear interpolation (PWLI) are widely used to calibrate DTC nonlinearity

Fig. 7. (a) Delay characteristics of synthesizable PS+VS DTC and custom-design DTC (b) concept of FOI and ZOI based nonlinearity calibration for synthesizable PS+VS DTC with mismatch dominated nonlinearity, and (c) the INL after calibration with both FOI and ZOI based nonlinearity calibration.

in PLLs and MDLLs [19], [39], [48]. In this work, the proposed synthesizable DTC nonlinearity is dominated by random mismatches, instead of the architectural nonlinearity [10]. Therefore, the conventional PWLI is modified in two ways to accommodated the mismatch-dominated DTC, which is summarized in Table I. Firstly, the number of LUT entries is designed to match the number of the coarse DTC stages, and each coarse DTC code is calibrated individually. Secondly, zero-order interpolation (ZOI) is adopted instead of the first-order interpolation (FOI) used in previous works [19], [39], [48]. The ZOI effectively applied an offset to each coarse code. The difference of FOI and ZOI is illustrated in Fig. 7. The code 0 of fine VS DTC corresponds to the middle of the delay range, and the fine DTC can realize both positive and negative relative delays. Assume the INL of coarse PS DTC code n and n + 1 are  $INL_C[n]$  and  $INL_C[n + 1]$  respectively, and the maximum of the fine VS DTC is  $INL_{F,max}$ , the maximum calibration error  $\epsilon_{max,FOI}$ with FOI calibration occurred at the border of two neighboring coarse codes, and can be expressed as

$$\epsilon_{\max,FOI} = \frac{INL_C[n] + INL_C[n+1]}{2}$$

$$= \frac{INL_C[n] + INL_{F,max}}{2} - (INL_C[n] + INL_{F,max})$$

$$= \frac{INL_C[n+1] - INL_C[n]}{2} - INL_{F,max} \quad (12)$$

On the other hand, the ZOI based calibration utilize the known information that which coarse code is actually used to generate the delay. The maximum calibration error  $\epsilon_{max,ZOI}$  with ZOI calibration can be expressed as

$$\epsilon_{\max,ZOI} = INL_C[n] - (INL_C[n] + INL_{F,max})$$

= -INL<sub>F,max</sub> (13)

For conventional custom-designed DTCs with continuous nonlinearity characteristic, such as the one in Fig. 7(a), suppose the  $INL_C[n] = 10$ LSBs,  $INL_C[n + 1] = 15$ LSBs, and  $INL_{F,max} = 2$ LSBs,  $\epsilon_{max,FOI}$  and  $\epsilon_{max,ZOI}$  are 0.5LSBs and -2LSBs respectively. However, for mismatch-dominated synthesizable DTCs, suppose the  $INL_C[n] = 10$ LSBs,  $INL_C[n+1] = -15$ LSBs, and  $INL_{F,max} = 2$ LSBs,  $\epsilon_{max,FOI}$ and  $\epsilon_{max,ZOI}$  are -14.5LSBs and -2LSBs respectively, as shown in Fig. 7(c). Therefore, the ZOI based calibration is more effective for mismatch-dominated synthesizable DTCs employed in this work.

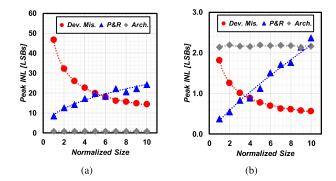

To validate the effectiveness of the proposed ZOI based calibration, time-domain behavioral simulations were performed. The DTC is modeled as a two-stage implementation with 6-bit PS DTC coarse stage and 8-bit VS DTC fine stage. The resolutions of coarse and fine DTC resolution are 30 ps and 0.3 ps respectively. The fixed delay offset is 100 ps. To stress-test the proposed calibration algorithm, the DTC was modeled with random INLs as large as 15 ps and DNLs as large as 30 ps.

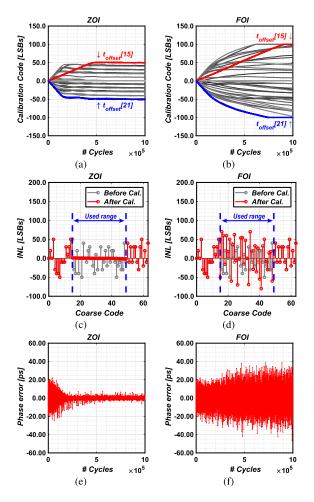

The calibration results with both proposed ZOI and FOI based nonlinearity calibrations are shown in Fig. 8. The modeled DTC INL is shown as the grey dots in Fig. 8(c), which has large DNLs to stress test the proposed ZOI calibration. Fig. 8(a-b) showed the time-domain plot of the calibration codes. With the same 6-bit LUT, the ZOI based calibration converged to correct value, whereas the FOI based calibration failed to converge and saturate at the calibration limit, which is 100 LSBs in this design. Fig. 8(c-d) showed the INL before and after calibration. The proposed ZOI based calibration effectively removed the nonlinearity within the used DTC range, and reduced the phase error. On the contrary, the FOI based calibration introduced larger error and degrade the INL, which contributes to the increased phase error in Fig. 8(f). The phase noise of the MDLL with and without ZOI based nonlinearity calibration is shown in Fig. 9. With the calibration, the nonlinearity induced spur and noise folding are greatly reduced, validating the effectiveness of proposed calibration.

#### B. Hardware Implementation

The implementation of the DTC calibration logic is shown in Fig. 10(a), which includes both gain calibration and nonlinearity calibration. 1st-order delta-sigma modulator (DSM) is used to reduce the required DTC range. Besides, with highly nonlinear DTC, 1st-order DSM could provide better noise performance than higher order ones [36]. Admittingly the 1st-order DSM could slow the gain calibration speed with very small fractional FCWs. However, for the target applications of this MDLL, such as SoC clocking, techniques such as spread-spectrum clocking introduces a modulated FCW which effectively obviates the operation with very small fractional FCWs. The bandwidth of nonlinearity calibration is smaller than that of gain calibration, and bandwidth of both calibrations is smaller than the phase lock path to avoid race condition. The implementation of coarse stage LMS

Fig. 8. Behaviorial simulations of the proposed ZOI(a,c,e) and FOI based calibration (b,d,f). The FCW =  $10+2^{-6}+2^{-12}$ ,  $f_{\rm REF} = 100$  MHz and DSM order is 1. Plots (a-b) are time-domain plot of calibration codes, (c-d) are INL before and after calibration, and (e-f) are phase error present at the BBPD input.

Fig. 9. Simulated phase noise of fractional-*N* MDLL (a) with perfect linear DTC, (b) with nonlinear DTC and without nonlinearity calibration, and (c) with nonlinear DTC and ZOI nonlinearity calibration.

gain calibration is shown in Fig. 10(b). and the ZOI PWLI implementation is shown in Fig. 10(c).

To save the power consumption and area, several techniques are employed in the digital logic implementation. The DTC gain calibrations employ sign-error LMS algorithm to avoid full precision multipliers 10(b). Besides, the LMS gain calibration step and PLL loopfilter coefficients are designed be power of 2, so the multiplication can be realized as shift operation. What is more, pipeline is inserted to relax the timing constraints. The depth of pipeline is adjustable with

Fig. 10. Implementation of DTC gain and nonlinearity calibrations, (a) system architecture, (b) gain calibration and (c) ZOI nonlinearity calibration.

Fig. 11. System diagram of proposed MDLL phase offset calibration.

the variable delay k in the calibration logic in Fig. 10. And extensive clock gating is used in blocks such as LUTs to avoid unnecessary update and save power consumption.

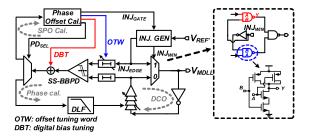

## V. MDLL PHASE OFFSET CALIBRATION

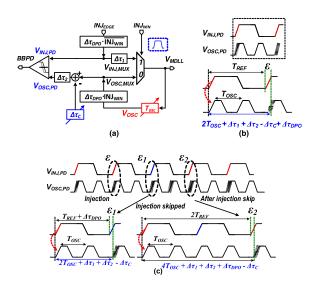

In this work, the reference signal is used for both edge replacement and phase calibration, as shown in Fig. 11. It is commonly known that any phase offsets between these two paths would raise the reference spur [19], [49]. The time domain model is shown in Fig. 12(a). INJEDGE and VOSC are reference edge and oscillation edge respectively.  $\Delta \tau_1$  and  $\Delta \tau_2$ are static phase offsets (SPO) caused by device mismatches and P&R systemic mismatches, which is time-invariant during MDLL operation. On the other hand, conventional NAND2based multiplexer presents different load capacitance to the two input signals INJ<sub>EDGE</sub> and V<sub>OSC</sub>, as shown in Fig. 11. The load difference is dependent on the  $INJ_{WIN}$ , and introduces dynamic phase offsets (DPO)  $\Delta \tau_{\text{DPO}}$ . In this model, the  $\Delta \tau_{\text{DPO}}$  is used to represent the value of  $(\tau_{\text{B}=0} - \tau_{\text{B}=1})$ , in which  $\tau_{B=1}$  and  $\tau_{B=0}$  are delays when the signal at terminal B of NAND2 is logic 1 and 0 respectively. When  $INJ_{WIN}$ equals to 1, the B terminal of NAND2 on the  $INJ_{EDGE}$  path is 1, whereas the B terminal of NAND2 on the  $V_{OSC}$  path

Fig. 12. MDLL phase offset calibration (a) time domain model, (b) waveform of conventional operation and (c) waveform of proposed gated edge replacement.

Fig. 13. Simulation results of proposed phase offset calibration (a) time-domain waveforms of calibration codes and (b) phase noise after calibration. Simulation conditions: Integer-*N* mode with  $f_{\rm OUT} = 1$  GHz,  $f_{\rm REF} = 100$  MHz,  $\Delta \tau_1 + \Delta \tau_2 = 10$  ps, and  $K_{\rm DTC} = 0.3$  ps/LSB.

is 0. Therefore,  $\Delta \tau_{\text{DPO}}$  presents on the  $V_{\text{OSC}}$  path, which is represented as  $\Delta \tau_{\text{DPO}} \cdot \overline{INJ_{\text{WIN}}}$ . Conversely,  $\Delta \tau_{\text{DPO}}$  presents on the  $INJ_{\text{EDGE}}$  path when  $INJ_{\text{WIN}}$  equals to 0, and denoted as  $\Delta \tau_{\text{DPO}} \cdot INJ_{\text{WIN}}$ . Depending on the  $INJ_{\text{WIN}}$  state,  $\Delta \tau_{\text{DPO}}$ appears on  $INJ_{\text{EDGE}}$  path or  $V_{\text{OSC}}$  path in a time-interleave manner.

To analyze their effects on MDLL operation, an integer-*N* operation with a frequency multiplication ratio *N* of 2 is used for simplicity. Note that the BBPD detects the time difference of  $V_{\text{INJ,PD}}$  and  $V_{\text{OSC,PD}}$ . While  $V_{\text{INJ,PD}}$  is updated at every reference period,  $V_{\text{INJ,PD}}$  is a delayed version of the preceding injected edge  $INJ_{\text{EDGE}}$ . And the delay is affected by not only the DCO delay  $T_{\text{OSC}}$ , but also SPOs  $\Delta \tau_{1,2}$  and DPOs and  $\Delta \tau_{\text{DPO}}$ . When  $V_{\text{OSC}}$  is replaced continuously, the phase error  $\epsilon$  present at BBPD is

$$\epsilon = T_{\text{REF}} - [\Delta \tau_1 + N \cdot T_{\text{OSC}} + \Delta \tau_{\text{DPO}} + \Delta \tau_2]$$

=  $[T_{\text{REF}} - N \cdot T_{\text{OSC}}] - [\Delta \tau_1 + \Delta \tau_2 + \Delta \tau_{\text{DPO}}] = 0$  (14)

where  $T_{\text{REF}}$  is the reference period,  $T_{\text{OSC}}$  is the oscillator period. Therefore, if the  $\Delta \tau_1 + \Delta \tau_{\text{DPO}} + \Delta \tau_2$  is not zero, the  $[T_{\text{REF}}$  cannot match  $N \cdot T_{\text{OSC}}]$ . As a result, the PLL output would have a period distortion at the rate of  $f_{\text{REF}}$ , which translates into reference spurs. In this work, the  $\Delta \tau_{\text{DPO}}$  is eliminated with a proposed complementary-switched MUX and BBPD, which will be explained in more detail in VI-B. The  $\Delta \tau_1 + \Delta \tau_2$  is removed by a compensation delay  $\Delta \tau_C$ . By gating the edge replacement, three different phase errors can be detected, as shown in Fig. 12(c). The phase errors during continuous edge replacement, at the gating cycle and immediately after gating are expressed as is  $\epsilon$ ,  $\epsilon_1$  and  $\epsilon_2$ respectively, and can be expressed as

$$\epsilon = [T_{\text{REF}} - N \cdot T_{\text{OSC}}] - [\Delta \tau_1 + \Delta \tau_2 - \Delta \tau_{\text{C}} + \Delta \tau_{\text{DPO}}] \quad (15)$$

$$\epsilon_1 = [T_{\text{REF}} - N \cdot T_{\text{OSC}}] - [\Delta \tau_1 + \Delta \tau_2 - \Delta \tau_{\text{C}} - \Delta \tau_{\text{DPO}}] \quad (16)$$

$$\epsilon_2 = 2[T_{\text{REF}} - N \cdot T_{\text{OSC}}] - [\Delta \tau_1 + \Delta \tau_2 - \Delta \tau_{\text{C}} + \Delta \tau_{\text{DPO}}]$$

(17)

The  $\epsilon$  and  $\epsilon_1$  are used for phase lock, whereas the  $\epsilon_2$  is used for offset calibration. Since all the three phase errors are forced to zero on average and  $\Delta \tau_{\text{DPO}}$  is zero by circuit design, the  $\Delta \tau_{\text{C}}$  must be equal to  $\Delta \tau_1 + \Delta \tau_2$ .

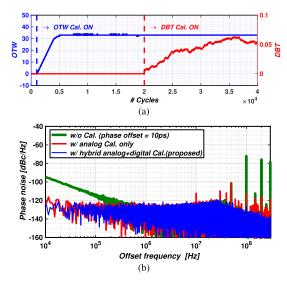

Gating injection technique has been proposed in [50], [51] to calibrate the static phase offset. Yet the DPO also contributes to the DCO period distortion and interferes with SPO calibration, as demonstrated in above analysis. Moreover,  $\Delta \tau_{\rm C}$ is realized with DTCs as an analog domain delay in [50], [51]. However, the residue reference spur is limited by the finite DTC resolution [29]. Besides, the gating operation introduces fractional spurs to the PLL output [27], [50]. Therefore,  $\Delta \tau_{\rm C}$ is realized as a hybrid of analog domain delay and digital domain digital bias to BBPD output in this work In the first step, an offset tuning word (OTW) is calculated and applied to DTCs at BBPD input to reduce the SPO into the linear region of BBPD. Delay difference of two DTCs are used to compensate both positive and negative SPOs. Then a digital bias tuning (DBT) code is added to BBPD output to remove residue offset in digital domain. In this way, the  $\Delta \tau_{\rm C}$  can be realized with arbitrarily fine resolution. To ensure the correct operation, the residue offset  $\Delta \tau_{\text{residue}}$  must be smaller than the linear region of BBPD. Under worst case, the  $\Delta \tau_{\text{residue}}$  is about half of DTC residue  $t_{res}$ , which is 0.2 ps. On the other hand, with  $\geq 0.48$  ps RMS jitter, this requirement is easily met. The DBT value is automatically found by the type-I feedback loop, and is not sensitive to the exact BBPD gain. The simulated OTW and DBT waveforms are shown in Fig.13(a), and the simulated phase noise with and without proposed calibration are shown in Fig.13(b). With the proposed hybrid offset calibration, both the reference spurs and gating-induced fractional spurs can be greatly suppressed. Besides, proposed calibration creates one additional feedback loop, which helps to suppress the flicker noise at low offset frequency. The proposed offset calibration compensates the differential mode delay between the edge replacement and phase calibration paths. It is independent from the DTC gain and nonlinearity calibrations, which control the common mode delay. Besides, the phase offset calibration uses gating control signal to correlate with BBPD error, which is independent from the DTC control word. Therefore, the phase offset calibration and DTC calibrations will not interfere with each other.

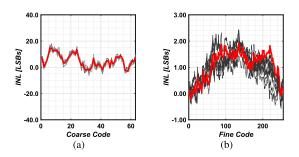

Fig. 14 shows the implementation of the proposed SPO calibration. For simplicity, only the offset calibration logic part is shown. A programmable counter with a self-dithered

Fig. 14. Implementation of proposed two-step hybrid offset calibration.

Fig. 15. Implementation details of proposed two-stage PS-VS DTC.

modulus value is used to generate the  $PD_{SEL}$  and gating control signal INJGATE. A one-cycle pulse is generated when the counter value is 2, which is used as  $INJ_{GATE}$ . The  $PD_{SEL}$ is generated in a similar way with the trigger value set to 3. The self-dithered modulus counter dynamically changes the instantaneous frequency of  $INJ_{GATE}$  and  $PD_{SEL}$ , thus avoid idle tones at PLL output. Phase error  $\epsilon_2$  is accumulated. In the first step, the 6-bit MSBs of the accumulator is used as OTW to tune the delay of  $INJ_{EDGE}$ . A calibration controller monitors the OTW value variation to freeze the OTW value after settle and starts the DBT adaptation. To ensure the residue error is within the BBPD linear region, the calibration DTC resolution  $K_{\text{DTC}}$  is designed to 0.3ps/LSB, and the whole calibration range is around  $\pm 10$  ps. The accumulator is reset and used to generate a 5-bit DBT. The 2-bit BBPD output is expanded to a signed 5-bit number and added with the DBT, which has been validated to be sufficient by system simulations. The calibration DTCs add about 30 ps delay to BBPD input, which negligibly affects BBPD gain and quantization noise. Since the MDLL output noise dominated by the reference injection path [11], the calibration will have very small effect on the MDLL output jitter.

## VI. CIRCUIT IMPLEMENTATION

## A. Design and Optimization Procedure

With the standard cell only circuit design, the MDLL is designed and optimized follows a procedure that only uses the timing library [52]. Among the MDLL building blocks, DCO and DTC contribute most to the overall MDLL noise [11]. Both DTC and DCO noise can be estimated with delay, power consumption, and supply voltage obtained from the timing library [53]. Therefore, a rough estimation of the noise of DTC, DCO and MDLL noise is possible. Transistor-level analog simulations are only required for accurate noise characterizations. Thus, circuit design and optimization can be carried out before analog process design kit (PDK) is available, easing design in new processes.

# B. Synthesizable Timing Generation Circuits

The implementation of the proposed two-stage DTC is shown in Fig. 15, and the details about delay and range are summarized in Table II. The coarse stage delay cells are

TABLE II SIMULATED IMPLEMENTATION DETAILS OF PROPOSED TWO-STAGE SYNTHESIZABLE DTC

| Control bits | PVT condition | Range [ps]                                                                                                                                                | Resolution [ps]                                                                                                                                                               |  |

|--------------|---------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

|              | TT*           | 2090.0                                                                                                                                                    | 33.2                                                                                                                                                                          |  |

| 6-bit        | 55            | 3374.6                                                                                                                                                    | 53.6                                                                                                                                                                          |  |

|              | FF***         | 1355.1                                                                                                                                                    | 21.5                                                                                                                                                                          |  |

|              | TT*           | 108.5                                                                                                                                                     | 0.43                                                                                                                                                                          |  |

| 8-bit        | SS**          | 155.2                                                                                                                                                     | 0.61                                                                                                                                                                          |  |

|              | FF***         | 78.0                                                                                                                                                      | 0.31                                                                                                                                                                          |  |

|              | 6-bit         | $\begin{array}{c} & TT^{*} \\ \hline 6\text{-bit} & SS^{**} \\ \hline FF^{***} \\ \hline FF^{***} \\ \hline TT^{*} \\ 8\text{-bit} & SS^{**} \end{array}$ | $\begin{array}{c cccc} & TT^* & 2090.0 \\ \hline & SS^{**} & 3374.6 \\ \hline & FF^{***} & 1355.1 \\ \hline & TT^* & 108.5 \\ \hline & SS^{**} & 155.2 \\ \hline \end{array}$ |  |

\* TT corner, temp. =  $27^{\circ}$ ,  $V_{DD} = 1.2 \text{ V}$  \*\* SS corner, temp. =  $80^{\circ}$ ,  $V_{DD} = 1.1 \text{ V}$  \*\*\* FF corner, temp. =  $-20^{\circ}$ ,  $V_{DD} = 1.3 \text{ V}$

Fig. 16. Two-stage synthesizable DTC nonlinearity characteristics under typical corner with different automatic P&R trials, (a) DNL of coarse stage and (b) INL of coarse stage, (c) DNL of fine stage and (d) INL of fine stage.

implemented with tristate buffers, and the fine stage delay cells are implemented with NAND3 based varactors. The DTC range is designed to be more than 1 ns under PVT variations. Besides, the fine stage VS DTC range is designed to ensure continuous coverage and nonlinearity calibration. The DNL and INL of both coarse and fine stage DTCs are obtained from LPE simulations, with 5 different P&R trials. Each P&R trial is with 50 Monte-Carlo runs to reflect device mismatches. Increasing the Monte-Carlo run number from 50 to 200 changes the standard deviation by less than 1%. Therefore, a run number of 50 is adopted to reduce the simulation time. The results are shown in Fig. 16. As evident from the simulations, the nonlinearity of the coarse stage PS DTC is dominated by systemic mismatches from automatic P&R and device mismatches. On the other hand, the nonlinearity of fine stage VS DTC is dominated by deterministic architectural nonlinearity, which is similar to those custom-designed VS DTCs [39], [40]. The simulated DTC nonlinearity under voltage and temperature variations are shown in Fig. 17(a). The PS DTC nonlinearity does not change much, which is expected since all the delay elements' driving strength and loads are changed in the same way. On the other hand, the PS DTC has larger variations, because the driving strength and load has different temperature and supply sensitivity. However, since the fine DTC VS nonlinearity is

Fig. 17. Two-stage synthesizable DTC nonlinearity characteristics under different voltages (1.1/1.2/1.3 V) and temperatures  $(-20/27/80^{\circ}\text{ C})$ , (a) INL of coarse stage, (b) INL of fine stage.

Fig. 18. Proposed DPO compensated BBPD (a) circuit implementation, (b) simulated capacitance variation, (c) simulated DPO of conventional BBPD and (d) simulated DPO of proposed BBPD.

relatively small compared to coarse PS DTC, the overall DTC nonlinearity does not change much.

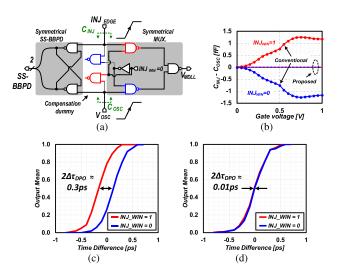

The proposed DPO-compensated MUX and BBPD are shown in Fig. 18(a). Two complementary-switched dummy NAND2 gates are added to remove the load capacitance modulation by  $INJ_{WIN}$ . Fig. 18 shows the simulated difference between load capacitance  $C_{INJ}$  and  $C_{OSC}$  when  $INJ_{WIN}$  is "0" and "1". In conventional implementation [11], the peak capacitance difference is about 2.6 fF, which affects the signal slope and the propagation delay. On the other hand, with the proposed complementary switching, the capacitance difference is effectively eliminated. The simulated effective dynamic phase offset at BBPD output is shown in Fig. 18(c) and Fig. 18(d). With the proposed complementary switch, the dynamic delay offset is reduced from 150 fs to 5 fs, which has a negligible effect on reference spur.

The implementation of DCO and gated injection edge and window generator are shown in Fig. 19. The DCO tuning is separated into three banks, including a 4-bit PS coarse bank, 4-bit VS medium bank and 6-bit VS fine bank. The DCO implementation is similar to the one presented in [11], but a wider fine tuning range is used to facilitate the fractional-*N* phase locking. The DCO delay range and resolution of each bank are shown in Table III. The gated injection generator derives injection edge and window signal, and ensures the injection edge is around the middle of injection window. Besides, two identical inverters are added on the *INJ*<sub>EDGE</sub> and

Fig. 19. Implementation of the DCO and the gated injection edge and window generator.

| IABLE III                               |

|-----------------------------------------|

| SIMULATED IMPLEMENTATION DETAILS OF DCO |

|        | Control bits | PVT condition | Range [ps] | Resolution [ps] |  |

|--------|--------------|---------------|------------|-----------------|--|

|        |              | TT*           | 1030.9     | 68.7            |  |

| Coarse | 4-bit        | SS**          | 1591.3     | 106.1           |  |

|        |              | FF***         | 699.4      | 46.6            |  |

|        |              | TT*           | 90.0       | 6.0             |  |

| Medium | 4-bit        | SS**          | 121.8      | 8.1             |  |

|        |              | FF***         | 69.3       | 4.6             |  |

|        |              | TT*           | 22.5       | 0.36            |  |

| Fine   | 6-bit        | SS**          | 30.2       | 0.48            |  |

|        |              | FF***         | 17.5       | 0.28            |  |

<sup>\*</sup> TT corner, temp. =  $27^{\circ}$ ,  $V_{DD} = 1.2 V$  <sup>\*\*</sup> SS corner, temp. =  $80^{\circ}$ ,  $V_{DD} = 1.1 V$  <sup>\*\*\*</sup> FF corner, temp. =  $-20^{\circ}$ ,  $V_{DD} = 1.3 V$

TABLE IV Measured Power Consumption of Proposed MDLL

|              | DCO*  | DTC*  | INJ. Gen.* | Dig. Logic* | Total* |

|--------------|-------|-------|------------|-------------|--------|

| Fractional-N | 1.068 | 0.456 | 0.072      | 0.252       | 1.85   |

| Integer-N    | 1.068 | 1     | 0.072      | 0.084       | 1.22   |

| * all in mW. |       |       |            |             |        |

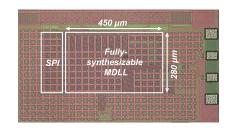

Fig. 20. Chip micro-graph of the fully-synthesizable fractional-N MDLL.

$V_{\text{OSC}}$  paths to ensure the same drive strength. Together with the DPO compensated MUX and BBPD, the same signal-slope is ensured.

## VII. MEASUREMENT RESULTS

The entire MDLL is synthesized using commercial digital design tools with a non-modified standard cell library. The core area of the MDLL is 0.126 mm<sup>2</sup>, which is fabricated in TSMC 65 nm LP CMOS process. The active area of DTC, DCO and digital logic is 0.0042 mm<sup>2</sup>, 0.0051 mm<sup>2</sup>, and 0.0244 mm<sup>2</sup> respectively. The total active area is 0.0337 mm<sup>2</sup>. The rest of the core area is occupied by decoupling capacitors and filler cells, which are used to provide sufficient decoupling. The nominal supply voltage is 1.2 V, and is used across all measurements unless otherwise stated. Fig. 20 shows the die photo. The phase noise is measured by a signal source analyzer (Keysight E5052B), the spectrum is measured by a

TABLE V Measured Range and Resolution of DCO and DTC

|             |             | DCO       | DTC       |             |            |

|-------------|-------------|-----------|-----------|-------------|------------|

| Temp.[°C]   | Coarse      | Medium    | Fine      | Coarse      | Fine       |

| /Voltage[V] | [ps]        | [ps]      | [ps]      | [ps]        | [ps]       |

| -20/1.3     | 940.8/62.7  | 85.6/5.7  | 21.6/0.34 | 1911.9/30.3 | 102.4/0.40 |

| -20/1.2     | 1086.2/72.4 | 95.5/6.4  | 24.8/0.39 | 2220.2/35.2 | 119.6/0.47 |

| -20/1.1     | 1217.4/81.2 | 106.6/7.1 | 27.1/0.43 | 2567.9/40.8 | 130.9/0.51 |

| 27/1.3      | 899.3/59.9  | 83.0/5.5  | 20.7/0.33 | 1846.4/29.3 | 96.4/0.38  |

| 27/1.2      | 1051.5/70.1 | 91.8/6.1  | 23.3/0.37 | 2161.1/34.3 | 110.8/0.44 |

| 27/1.1      | 1150.1/76.7 | 102.8/6.9 | 26.0/0.41 | 2404.7/38.2 | 122.6/0.48 |

| 80/1.3      | 860.3/57.4  | 78.5/5.2  | 19.2/0.30 | 1811.3/28.8 | 96.6/0.38  |

| 80/1.2      | 977.8/65.2  | 85.9/5.7  | 21.9/0.35 | 2004.9/31.8 | 105.3/0.41 |

| 80/1.1      | 1085.7/72.4 | 97.6/6.5  | 24.8/0.39 | 2292.5/36.4 | 117.8/0.46 |

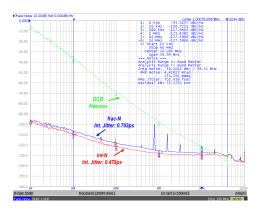

Fig. 21. Measured phase noise in (a) DCO free-run mode (b) integer-*N* mode and (c) fractional-*N* mode.

spectrum analyzer (Anritsu MS2830A), and the reference is provided by a signal generator (Rhode&Schwartz SMA100). The core power consumption excluding IO buffers of proposed MDLL is shown in Table IV. The total power consumption is 1.85 mW in the fractional-*N* mode. The power consumption in the integer-*N* mode can be reduced to 1.22 mW by bypassing DTC and gating off part of calibration logic. The measured range and resolution of DCO and DTC are shown in Table V. The measured DCO coarse/medium/fine resolution under 1.2V/27°C are 70.1/6.1/0.37 ps/LSB respectively, and the DTC coarse/fine resolution are 34.3/0.44 ps/LSB respectively, which are close to TT case simulated results in Table III and Table II.

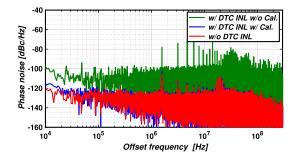

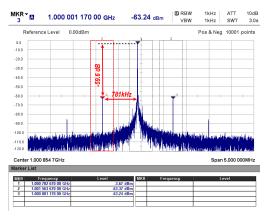

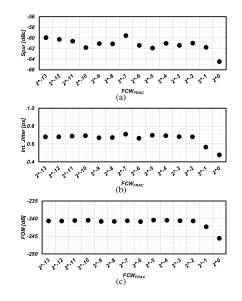

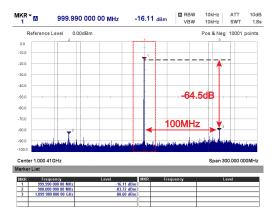

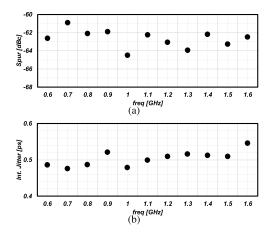

Fig. 21 shows the measured phase noise with a 100 MHz reference clock. The DCO free-run mode phase noise is -97.6 dBc/Hz at 1 MHz offset frequency, and the power consumption is 1.068 mW at 1 GHz. The MDLL achieves 0.48 ps jitter at 1 GHz output in integer-N mode, and 0.70 ps jitter in fractional-N mode, both integrated from 10kHz to 40MHz. The fractional spur and integrated jitter across different fractional channels are shown in Fig. 23(a) and Fig. 23(b). The worst-case fractional spur is lower than  $-59.0 \, dBc$ , as shown in Fig. 22, and the worst-case jitter is 0.70 ps. Assume the residual INL after calibration is sinusoidal, the peak-to-peak INL magnitude  $\Delta t_{\rm INL}$  can be estimated by  $\Delta t_{\rm INL} = 2/\pi$ .  $T_{\rm DCO} \cdot 10^{\mathcal{L}_{spur/20}}$  [39], in which  $T_{\rm DCO}$  is the DCO period. The estimated INL is about 0.7ps, which agrees well with the simulation results, validating the effectiveness of proposed ZOI-based calibration.

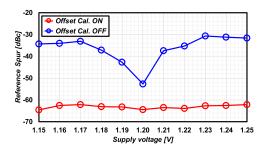

The measured reference spur at 1.2 V is -64.5 dB, and reference spurs across different supply voltage is shown in Fig. 25. Lower than -60 dBc reference spur is achieved

TABLE VI Performance Summary and Comparison With Ring Oscillator Based Integer-N IL-PLLs/MDLLs

|                                            | JSSC'13  | JSSC'15 | JSSC'19   | JSSC'19   | ISSCC'19 | VLSIC'18 | ISSCC'17  | SSCL'18   | SSCL'19    | This     |

|--------------------------------------------|----------|---------|-----------|-----------|----------|----------|-----------|-----------|------------|----------|

|                                            | [49]     | [19]    | [54]      | [29]      | [55]     | [27]     | [9]       | [56]      | [11]       | Work     |

|                                            |          |         | Custor    | -design   |          |          |           | Fully-syn | thesizable |          |

| Architecture                               | MDLL     | MDLL    | ILCM      | MDLL      | ILCM     | BBDPLL   | IL-PLL    | TDC-PLL   | MDLL       | MDLL     |

| Osc. Type                                  | Ring     | Ring    | Ring      | Ring      | Ring     | Ring     | Ring      | Ring      | Ring       | Ring     |

| CMOS Tech.                                 | 130 nm   | 65 nm   | 65 nm     | 28 nm     | 65 nm    | 7 nm     | 65 nm     | 14 nm     | 65 nm      | 65 nm    |

| Area [mm <sup>2</sup> ]                    | 0.25     | 0.09    | 0.16      | 0.0056    | 0.055    | 0.018    | 0.028     | 0.009     | 0.035      | 0.126    |

| f <sub>OUT</sub> [GHz]                     | 0.8~2.0  | 1.6~1.9 | 2.6~5.2   | 1.55~3.35 | 2.2~2.5  | 0.48~4   | 0.52~1.15 | 1.0~5.5   | -          | 0.6~1.6  |

| f <sub>REF</sub> [MHz]                     | 375      | 50      | 54**      | 200       | 100      | 30~250   | 150       | 50        | 100        | 100      |

| P <sub>DC</sub> /f <sub>OUT</sub> [mW/GHz] | 0.89/1.5 | 2.4/1.6 | 6.5/4.752 | 1.45/3.0  | 11.0/2.4 | 6.3/4    | 3.8/0.9   | 9.7/5.0   | 1.2/1.0    | 1.22/1.0 |

| Int. Jitter [ps]                           | 0.4      | 0.47    | 0.366     | 0.292     | 0.14     | 0.427    | 0.42      | 4.71      | 0.4        | 0.48     |

| Int. BW [Hz]                               | 1M~100M  | 30k~30M | 10k~30M   | 10k~40M   | 10k~40M  | 100k~1G  | 10k~10M   | -         | 10k~10M    | 10k~40M  |

| FOM†[dB]                                   | -248.5   | -242.7  | -240.6    | -249.1    | -246.7   | -239.4   | -241.7    | -216.8    | -247.2     | -245.5   |

| Ref. Spur [dBc]                            | -55.6    | -55.3   | -53       | -44       | -72      | -61      | -         | -40*      | -52        | -64.5    |

| DJ <sub>RMS</sub> †† [ps]                  | 0.25     | 0.24    | 0.11      | 0.47      | 0.02     | 0.05     | -         | 0.41      | 0.57       | 0.13     |

\* estimated from figure \*\* with ref

\*\* with reference quadrupler

<sup>†</sup> FOM =  $10 \cdot \log_{10}[(Int.Jitter/1s)^2(P_{DC}/1mW)]$

<sup>††</sup>  $DJ_{RMS} = 10^{L_S pur/20} / (\sqrt{2}\pi f_{OUT})$  [57]

## TABLE VII

PERFORMANCE SUMMARY AND COMPARISON WITH DTC-BASED AND SYNTHESIZABLE FRACTIONAL-N PLLS/MDLLS

|                                            | JSSC'14   | JSSC'18   | JSSC'18       | JSSC'19   | JSSC'19   | ISSCC'15  | JSSC'19    | CICC'18          | SSCL'20   | This      |

|--------------------------------------------|-----------|-----------|---------------|-----------|-----------|-----------|------------|------------------|-----------|-----------|

|                                            | [39]      | [36]      | [51]          | [42]      | [30]      | [7]       | [47]       | [10]             | [12]      | Work      |

|                                            |           |           | Custom-design | n         |           |           | F          | ully-synthesizal | ole       |           |

| Architecture                               | DTC +     | DTC +     | DTC +         | DTC +     | DTC +     | Soft-inj. | DI-TDC     | DTC +            | DTC +     | DTC +     |

| Atenticeture                               | BBDPLL    | TDC-PLL   | ILCM          | Samp. PLL | MDLL      | IL-PLL    | PLL        | MDLL             | MDLL      | MDLL      |

| Osc. Type                                  | LC        | LC        | LC            | LC        | Ring      | Ring      | Ring       | Ring             | Ring      | Ring      |

| CMOS Tech.                                 | 65 nm     | 65 nm     | 65 nm         | 28 nm     | 65 nm     | 65 nm     | 28 nm      | 65 nm            | 5 nm      | 65 nm     |

| Area [mm <sup>2</sup> ]                    | 0.2       | 0.23      | 0.27          | 0.45      | 0.0275    | 0.05      | 0.0043     | 0.12             | 0.0036    | 0.126     |

| f <sub>OUT</sub> [GHz]                     | 3~4       | 2.0~2.8   | 6.75~8.25     | 5.5~7.3   | 1.6~3.0   | 0.8~1.7   | 0.1~2.01   | 0.6~1.7          | 0.4~1.5   | 0.6~1.6   |

| f <sub>REF</sub> [MHz]                     | 40        | 26†       | 115           | 52†       | 100       | 380       | 80         | 100†             | 100       | 100       |

| P <sub>DC</sub> /f <sub>OUT</sub> [mW/GHz] | 4.2/3.6   | 0.98/2.44 | 3.25/7.36     | 18.9/6.33 | 2.5/1.65  | 3.0/1.5   | 6.95/2.056 | 2.5/0.97         | 0.95/1.0  | 1.85/1.0  |

| Frac. Spur [dBc]                           | -63*/     | -75*/     | -59*/         | -68.2*/   | -53*/     |           | -50*/      | -58.5            | -49.2/    | -61.9/    |

| (best/worst)                               | -51.7     | -56       | -42.4         | -64       | -51.5     | _         | -24*       | -58.5            | -44.3     | -59.6     |

| Int. Jitter [ps]                           | 0.7       | 0.53/     | 0.11/         | 0.075/    | 0.395     | 3.6       | 2.13       | 1.2              | 0.97/     | 0.56/     |

| (best/worst)                               | 0.7       | 0.59      | 0.17          | 0.085*    | 0.395     | 5.0       | 2.15       | 1.2              | 1.9       | 0.70      |

| Int. BW [Hz]                               | 100k~10M  | 10k~10M   | 10k~30M       | 10k~10M   | 30k~30M   | 1k~100M   | 10k~100M   | 10k~10M          | 10k~10M   | 10k~40M   |

| FOM [dB]                                   | -236.9    | -246/     | -254/         | -249.7/   | -244.0    | -224.2    | -225.0     | -234.4           | -240.5/   | -242.3/   |

| (best/worst)                               | -230.9    | -245      | -250          | -248.6    | -244.0    | -224.2    | -225.0     | -234.4           | -234.7    | -240.4    |

| Ref. Spur [dBc]                            | -         | -72       | -52           | -70.2     | -56       | -         | -52        | -                | -30.9     | -64.5     |

| DTC Cal.                                   | Gain +INL | Gain      | Gain          | Gain      | Gain +INL | -         | -          | Gain +INL        | Gain +INL | Gain +INL |

\* estimated from figures \* w

figures <sup>†</sup> w/ reference doubler

Fig. 22. Measured fractional spurs of a near-integer (FCW =  $10 + 2^{-7}$ ) channel.

across 1.15-1.25 V supply voltage. The measured reference spur is measured with input reference signal power of 7 dBm, and is limited by parasitic coupling through IO pads and supply/substrate. Reducing the reference signal power to 5 dBm improves the reference spur by 1-2 dB, but the in-band phase noise is much elevated. And further reducing the power below 5 dBm causes the IO pad fail to work. In comparison, when the phase offset calibration is disabled, the lowest reference

Fig. 23. Measured (a) fractional spur, (b) integrated jitter and (c) FOM at different fractional FCWs with FCW<sub>INT</sub> = 10 and  $f_{REF} = 100$  MHz.

spur is  $-52.7 \,\text{dBc}$  at 1.2 V nominal supply, which corresponds to 2.3 ps phase offset. The reference spur degrades as supply deviates from 1.2 V, as the slope mismatch becomes larger

Fig. 24. Measured reference spur with phase offset calibration ON.

Fig. 25. Measured reference spur versus supply voltage with phase offset calibration ON and OFF at 1 GHz.

Fig. 26. Measured (a) reference spur, (b) integrated jitter at different integer-N channels.

and the phase offset increases. The measured reference spur and integrated jitter at different integer-N channels are shown in Fig. 26. Consistent reference spur performance is observed across different frequencies. The DCO measured supply sensitivity is about 1 GHz/V at 1 GHz carrier frequency. However, thanks to the wide bandwidth, the MDLL supply sensitivity is attenuated by 20 dB at 3 MHz frequency offset, which greatly improved the overall supply sensitivity

Table VI and Table VII summarize the measured performance of the proposed MDLL in integer-*N* and fractional-*N* modes respectively, and compare with the state-ofthe-art PLLs/MDLLs. Compared to other fully-synthesizable PLLs/MDLLs, proposed MDLL achieved the best jitter and spur performance. Besides, the results are compared favorably to those of custom-designed digital PLLs/MDLLs, validating the effectiveness of the proposed synthesizable circuits and digital calibrations.

## VIII. CONCLUSION

A fully-synthesizable fully calibrated fractional-*N* MDLL is presented in this paper. Based on noise and linearity analysis of different DTC architectures, a low-power, high-performance synthesizable DTC is proposed and implemented, along with the proposed digital nonlinearity calibration optimized for the synthesizable design. Besides, both SPO and DPO are calibrated to reduce the reference spur. The SPO is calibrated by a two-step hybrid with arbitrarily fine resolution, and the DPO is calibrated by a proposed complementary switched MUX and BBPD. The MDLL achieves worst-case 0.70 ps RMS jitter and  $-59.6 \,\text{dBc}$  fractional spur with 1.85 mW power consumption in the fractional-*N* mode, corresponding to  $-240.4 \,\text{dB}$  FOM. Besides, both SPO and DPO are compensated, resulting in less than  $-60 \,\text{dBc}$  reference spur is achieved across  $1.15-1.25 \,\text{V}$ .

#### ACKNOWLEDGMENT

This article is based on the results obtained from a project commissioned by the New Energy and Industrial Technology Development Organization (NEDO).

#### REFERENCES

- A. L. S. Loke, C. K. Lee, and B. M. Leary, "Nanoscale CMOS implications on analog/mixed-signal design," in *Proc. IEEE Custom Integr. Circuits Conf. (CICC)*, Apr. 2019, pp. 1–57.

- [2] Y. Park and D. D. Wentzloff, "An all-digital PLL synthesized from a digital standard cell library in 65nm CMOS," in *Proc. IEEE Custom Integr. Circuits Conf. (CICC)*, Sep. 2011, pp. 1–4.

- [3] W. Deng, A. Musa, T. Siriburanon, M. Miyahara, K. Okada, and A. Matsuzawa, "A 0.022 mm<sup>2</sup> 970μW dual-loop injection-locked PLL with -243dB FOM using synthesizable all-digital PVT calibration circuits," in *IEEE Int. Solid-State Circuits Conf. (ISSCC) Dig. Tech. Papers*, Feb. 2013, pp. 248–249.

- [4] M. Faisal and D. D. Wentzloff, "An automatically placed-and-routed ADPLL for the medradio band using PWM to enhance DCO resolution," in *Proc. IEEE Radio Freq. Integr. Circuits Symp. (RFIC)*, Jun. 2013, pp. 115–118.

- [5] W. Deng et al., "A 0.0066 mm<sup>2</sup> 780μW fully synthesizable PLL with a current-output DAC and an interpolative phase-coupled oscillator using edge-injection technique," in *IEEE Int. Solid-State Circuits Conf.* (*ISSCC*) Dig. Tech. Papers, Feb. 2014, pp. 266–267.

- [6] W. Kim, J. Park, H. Park, and D.-K. Jeong, "Layout synthesis and loop parameter optimization of a low-jitter all-digital pixel clock generator," *IEEE J. Solid-State Circuits*, vol. 49, no. 3, pp. 657–672, Mar. 2014.

- [7] W. Deng et al., "14.1 A 0.048 mm<sup>2</sup> 3 mW synthesizable fractional-N PLL with a soft injection-locking technique," in *IEEE Int. Solid-State Circuits Conf. (ISSCC) Dig. Tech. Papers*, Feb. 2015, pp. 252–253.

- [8] D. Yang, W. Deng, B. Liu, T. Siriburanon, K. Okada, and A. Matsuzawa, "An LC-DCO based synthesizable injection-locked PLL with an FoM of -250.3dB," in *Proc. ESSCIRC Conf., 42nd Eur. Solid-State Circuits Conf.*, Sep. 2016, pp. 197–200.

- [9] H. C. Ngo, K. Nakata, T. Yoshioka, Y. Terashima, K. Okada, and A. Matsuzawa, "A 0.42ps-jitter –241.7dB-FOM synthesizable injection-locked PLL with noise-isolation LDO," in *IEEE Int. Solid-State Circuits Conf. (ISSCC) Dig. Tech. Papers*, Feb. 2017, pp. 150–151.

- [10] B. Liu et al., "A 1.2ps-jitter fully-synthesizable fully-calibrated fractional-N injection-locked PLL using true arbitrary nonlinearity calibration technique," in Proc. IEEE Custom Integr. Circuits Conf. (CICC), Apr. 2018, pp. 1–4.

- [11] B. Liu *et al.*, "A 0.4-ps-Jitter –52-dBc-spur synthesizable injectionlocked PLL with self-clocked nonoverlap update and slope-balanced subsampling BBPD," *IEEE Solid-State Circuits Lett.*, vol. 2, no. 1, pp. 5–8, Jan. 2019.

- [12] B. Liu *et al.*, "A fully-synthesizable fractional-N injection-locked PLL for digital clocking with triangle/sawtooth spread-spectrum modulation capability in 5-nm CMOS," *IEEE Solid-State Circuits Lett.*, vol. 3, pp. 34–37, 2020.

[13] S. Weaver, B. Hershberg, and U.-K. Moon, "Digitally synthesized

- [13] S. Weaver, B. Hershberg, and U.-K. Moon, "Digitally synthesized stochastic flash ADC using only standard digital cells," *IEEE Trans. Circuits Syst. I, Reg. Papers*, vol. 61, no. 1, pp. 84–91, Jan. 2014.

- [14] Y. Park and D. D. Wentzloff, "An all-digital 12 pJ/Pulse IR-UWB transmitter synthesized from a standard cell library," *IEEE J. Solid-State Circuits*, vol. 46, no. 5, pp. 1147–1157, May 2011.

- [15] Y. Li et al., "A novel fully synthesizable all-digital RF transmitter for IoT applications," *IEEE Trans. Comput.-Aided Design Integr. Circuits* Syst., vol. 37, no. 1, pp. 146–158, Jan. 2018.

- [16] B. Liu *et al.*, "An HDL-described fully-synthesizable sub-GHz IoT transceiver with ring oscillator based frequency synthesizer and digital background EVM calibration," in *Proc. IEEE Custom Integr. Circuits Conf. (CICC)*, Apr. 2019, pp. 1–4.

- [17] P. Madoglio et al., "A 2.4GHz WLAN digital polar transmitter with synthesized digital-to-time converter in 14nm trigate/FinFET technology for IoT and wearable applications," in *IEEE Int. Solid-State Circuits Conf. (ISSCC) Dig. Tech. Papers*, Feb. 2017, pp. 226–227.

- [18] G. Marucci, A. Fenaroli, G. Marzin, S. Levantino, C. Samori, and A. L. Lacaita, "A 1.7GHz MDLL-based fractional-N frequency synthesizer with 1.4ps RMS integrated jitter and 3 mW power using a 1b TDC," in *IEEE Int. Solid-State Circuits Conf. (ISSCC) Dig. Tech. Papers*, Feb. 2014, pp. 360–361.

- [19] S. Levantino, G. Marucci, G. Marzin, A. Fenaroli, C. Samori, and A. L. Lacaita, "A 1.7 GHz fractional-N frequency synthesizer based on a multiplying delay-locked loop," *IEEE J. Solid-State Circuits*, vol. 50, no. 11, pp. 2678–2691, Nov. 2015.

[20] M. Kim, S. Choi, T. Seong, and J. Choi, "A low-jitter and fractional-

- [20] M. Kim, S. Choi, T. Seong, and J. Choi, "A low-jitter and fractionalresolution injection-locked clock multiplier using a DLL-based real-time PVT calibrator with replica-delay cells," *IEEE J. Solid-State Circuits*, vol. 51, no. 2, pp. 401–411, Feb. 2016.

- [21] S. Choi, S. Yoo, Y. Lim, and J. Choi, "A PVT-robust and lowjitter ring-vco-based injection-locked clock multiplier with a continuous frequency-tracking loop using a replica-delay cell and a dual-edge phase detector," *IEEE J. Solid-State Circuits*, vol. 51, no. 8, pp. 1878–1889, Aug. 2016.

[22] S. Yoo, S. Choi, J. Kim, H. Yoon, Y. Lee, and J. Choi, "A low-

- [22] S. Yoo, S. Choi, J. Kim, H. Yoon, Y. Lee, and J. Choi, "A lowintegrated-phase-noise 27–30-GHz injection-locked frequency multiplier with an ultra-low-power frequency-tracking loop for mm-Wave-band 5G transceivers," *IEEE J. Solid-State Circuits*, vol. 53, no. 2, pp. 375–388, Feb. 2018.

- [23] H. Yoon *et al.*, "A –31dBc integrated-phase-noise 29GHz fractional-N frequency synthesizer supporting multiple frequency bands for backward-compatible 5G using a frequency doubler and injection-locked frequency multipliers," in *IEEE Int. Solid-State Circuits Conf. (ISSCC) Dig. Tech. Papers*, Feb. 2018, pp. 366–368.

- [24] S. Yang, J. Yin, P.-I. Mak, and R. P. Martins, "A 0.0056 mm<sup>2</sup> alldigital MDLL using edge re-extraction, dual-ring VCOs and a 0.3 mW block-sharing frequency tracking loop achieving 292FSRMS jitter and -249dB FOM," in *IEEE Int. Solid-State Circuits Conf. (ISSCC) Dig. Tech. Papers*, Feb. 2018, pp. 118–120.

- [25] S. Kim *et al.*, "A 2 GHz synthesized fractional-N ADPLL with dual-referenced interpolating TDC," *IEEE J. Solid-State Circuits*, vol. 51, no. 2, pp. 391–400, Feb. 2016.

[26] H. Kim, Y. Kim, T. Kim, H.-J. Ko, and S. Cho, "A 2.4-GHz 1.5-mW

- [26] H. Kim, Y. Kim, T. Kim, H.-J. Ko, and S. Cho, "A 2.4-GHz 1.5-mW digital multiplying delay-locked loop using pulsewidth comparator and double injection technique," *IEEE J. Solid-State Circuits*, vol. 52, no. 11, pp. 2934–2946, Nov. 2017.

[27] T.-K. Kuan, C.-Y. Wu, R.-P. Shen, C.-H. Chang, K. Hsieh, and

- [27] T.-K. Kuan, C.-Y. Wu, R.-P. Shen, C.-H. Chang, K. Hsieh, and M. Chen, "A digital bang-bang phase-locked loop with background injection timing calibration and automatic loop gain control in 7nm FinFET CMOS," in *Proc. IEEE Symp. VLSI Circuits*, Jun. 2018, pp. 1–2.

- [28] J. Gong et al., "A 1.33 mW, 1.6psrms-integrated-jitter, 1.8-2.7 GHz ring-oscillator-based fractional-N injection-locked DPLL for Internet-of-Things applications," in Proc. IEEE Radio Freq. Integr. Circuits Symp. (RFIC), Jun. 2018, pp. 44–47.

- [29] S. Yang, J. Yin, P.-I. Mak, and R. P. Martins, "A 0.0056-mm<sup>2</sup> –249dB-FoM all-digital MDLL using a block-sharing offset-free frequencytracking loop and dual multiplexed-ring VCOs," *IEEE J. Solid-State Circuits*, vol. 54, no. 1, pp. 88–98, Jan. 2019.

[30] A. Santiccioli, M. Mercandelli, A. L. Lacaita, C. Samori, and

- [30] A. Santiccioli, M. Mercandelli, A. L. Lacaita, C. Samori, and S. Levantino, "A 1.6-to-3.0-GHz fractional – N MDLL with a digitalto-time converter range-reduction technique achieving 397-fs jitter at 2.5-mW power," *IEEE J. Solid-State Circuits*, vol. 54, no. 11, pp. 3149–3160, Nov. 2019.

- [31] Y. Lee, M. Kim, T. Seong, and J. Choi, "A low phase noise injection-locked programmable reference clock multiplier with a two-phase PVT-calibrator for ΔΣ PLLs," *IEEE Trans. Circuits Syst. I, Reg. Papers*, vol. 62, no. 3, pp. 635–644, Mar. 2015.

[32] S.-Y. Cho *et al.*, "A 2.5–5.6 GHz subharmonically injection-locked all-

- [32] S.-Y. Cho et al., "A 2.5–5.6 GHz subharmonically injection-locked alldigital PLL with dual-edge complementary switched injection," *IEEE Trans. Circuits Syst. I, Reg. Papers*, vol. 65, no. 9, pp. 2691–2702, Sep. 2018.

- [33] A. Elkholy, A. Elmallah, M. Elzeftawi, K. Chang, and P. K. Hanumolu, "A 6.75-to-8.25GHz, 250fsrms-integrated-jitter 3.25 mW rapid on/off PVT-insensitive fractional-N injection-locked clock multiplier in 65nm CMOS," in *IEEE Int. Solid-State Circuits Conf. (ISSCC) Dig. Tech. Papers*, Jan. 2016, pp. 192–193.

- [34] J. Z. Ru, C. Palattella, P. Geraedts, E. Klumperink, and B. Nauta, "A high-linearity digital-to-time converter technique: Constant-slope charging," *IEEE J. Solid-State Circuits*, vol. 50, no. 6, pp. 1412–1423, Jun. 2015.

- [35] P. Chen, F. Zhang, Z. Zong, H. Zheng, T. Siriburanon, and R. B. Staszewski, "A 15-μW, 103-fs step, 5-bit capacitor-DAC-based constant-slope digital-to-time converter in 28nm CMOS," in *Proc. IEEE Asian Solid-State Circuits Conf. (A-SSCC)*, Nov. 2017, pp. 93–96.

- Asian Solid-State Circuits Conf. (A-SSCC), Nov. 2017, pp. 93–96.

[36] H. Liu, D. Tang, Z. Sun, W. Deng, H. C. Ngo, and K. Okada, "A submW fractional-N ADPLL with FOM of -246 dB for IoT applications," *IEEE J. Solid-State Circuits*, vol. 53, no. 12, pp. 3540–3552, Dec. 2018.

- [37] P. Chen, F. Zhang, Z. Zong, S. Hu, T. Siriburanon, and R. B. Staszewski, "A 31-μW, 148-fs step, 9-bit capacitor-DAC-based constant-slope digital-to-time converter in 28-nm CMOS," *IEEE J. Solid-State Circuits*, vol. 54, no. 11, pp. 3075–3085, Nov. 2019.

- Circuits, vol. 54, no. 11, pp. 3075–3085, Nov. 2019.

[38] H. Liu *et al.*, "A 265-μW fractional-N digital PLL with seamless automatic switching sub-sampling/sampling feedback path and duty-cycled frequency-locked loop in 65-nm CMOS," *IEEE J. Solid-State Circuits*, vol. 54, no. 12, pp. 3478–3492, Dec. 2019.

- [39] S. Levantino, G. Marzin, and C. Samori, "An adaptive pre-distortion technique to mitigate the DTC nonlinearity in digital PLLs," *IEEE J. Solid-State Circuits*, vol. 49, no. 8, pp. 1762–1772, Aug. 2014.

- [40] N. Markulic, K. Raczkowski, P. Wambacq, and J. Craninckx, "A 10-bit, 550-fs step digital-to-time converter in 28nm CMOS," in *Proc. 40th Eur. Solid State Circuits Conf. (ESSCIRC)*, Sep. 2014, pp. 79–82.

[41] A. Elkholy, S. Saxena, G. Shu, A. Elshazly, and P. K. Hanumolu, "Low-

- [41] A. Elkholy, S. Saxena, G. Shu, A. Elshazly, and P. K. Hanumolu, "Lowjitter multi-output all-digital clock generator using DTC-based open loop fractional dividers," *IEEE J. Solid-State Circuits*, vol. 53, no. 6, pp. 1806–1817, Jun. 2018.

- [42] W. Wu et al., "A 28-nm 75-fs<sub>rms</sub> analog fractional-N sampling PLL with a highly linear DTC incorporating background DTC gain calibration and reference clock duty cycle correction," *IEEE J. Solid-State Circuits*, vol. 54, no. 5, pp. 1254–1265, Mar. 2019.

- [43] Y. Wu, M. Shahmohammadi, Y. Chen, P. Lu, and R. B. Staszewski, "A 3.5–6.8-GHz wide-bandwidth DTC-assisted fractional-N all-digital PLL with a MASH ΔΣ-TDC for low in-band phase noise," *IEEE J. Solid-State Circuits*, vol. 52, no. 7, pp. 1885–1903, Jul. 2017.

- [44] A. Santiccioli, M. Mercandelli, A. L. Lacaita, C. Samori, and S. Levantino, "A 1.6-to-3.0-GHz fractional-N MDLL with a digitalto-time converter range-reduction technique achieving 397fs jitter at 2.5-mW power," in *Proc. IEEE Custom Integr. Circuits Conf. (CICC)*, Apr. 2019, pp. 1–4.

- [45] A. Santiccioli, C. Samori, A. L. Lacaita, and S. Levantino, "Power-jitter trade-off analysis in digital-to-time converters," *Electron. Lett.*, vol. 53, no. 5, pp. 306–308, Mar. 2017.

- [46] M. Rezzoug, J. M. Daga, and D. Auvergne, "Signal transition time effect on CMOS delay evaluation," *IEEE Trans. Circuits Syst. I, Fundam. Theory Appl.*, vol. 47, no. 9, pp. 1362–1369, Sep. 2000.

[47] M. Lee, S. Kim, H.-J. Park, and J.-Y. Sim, "A 0.0043-mm<sup>2</sup> 0.3–

- [47] M. Lee, S. Kim, H.-J. Park, and J.-Y. Sim, "A 0.0043-mm<sup>2</sup> 0.3–1.2-V frequency-scalable synthesized fractional-N digital PLL with a speculative dual-referenced interpolating TDC," *IEEE J. Solid-State Circuits*, vol. 54, no. 1, pp. 99–108, Jan. 2019.

[48] N. Markulic *et al.*, "A DTC-based subsampling PLL capable of self-

- [48] N. Markulic *et al.*, "A DTC-based subsampling PLL capable of self-calibrated fractional synthesis and two-point modulation," *IEEE J. Solid-State Circuits*, vol. 51, no. 12, pp. 3078–3092, Dec. 2016.

[49] A. Elshazly, R. Inti, B. Young, and P. K. Hanumolu, "Clock multiplica-

- [49] A. Elshazly, R. Inti, B. Young, and P. K. Hanumolu, "Clock multiplication techniques using digital multiplying delay-locked loops," *IEEE J. Solid-State Circuits*, vol. 48, no. 6, pp. 1416–1428, Jun. 2013.

[50] A. Elkholy, M. Talegaonkar, T. Anand, and P. Kumar Hanumolu,

- [50] A. Elkholy, M. Talegaonkar, T. Anand, and P. Kumar Hanumolu, "Design and analysis of low-power high-frequency robust sub-harmonic injection-locked clock multipliers," *IEEE J. Solid-State Circuits*, vol. 50, no. 12, pp. 3160–3174, Dec. 2015.

- [51] A. Elkholy, A. Elmallah, M. G. Ahmed, and P. K. Hanumolu, "A 6.75–8.25-GHz –250-dB FoM rapid ON/OFF fractional-N injectionlocked clock multiplier," *IEEE J. Solid-State Circuits*, vol. 53, no. 6, pp. 1818–1829, Jun. 2018.

- [52] K. Okada, "Quick start guide of digital PLL for digital designers," in Proc. Asia and South Pacific Design Automation Conf., Jan. 2017.

- [53] A. A. Abidi, "Phase noise and jitter in CMOS ring oscillators," *IEEE J. Solid-State Circuits*, vol. 41, no. 8, pp. 1803–1816, Aug. 2006.

[54] K. M. Megawer, A. Elkholy, M. G. Ahmed, A. Elmallah, and

- [54] K. M. Megawer, A. Elkholy, M. G. Ahmed, A. Elmallah, and P. K. Hanumolu, "Design of crystal-oscillator frequency quadrupler for low-jitter clock multipliers," *IEEE J. Solid-State Circuits*, vol. 54, no. 1, pp. 65–74, Jan. 2019.

- [55] S. Yoo, S. Choi, Y. Lee, T. Seong, Y. Lim, and J. Choi, "A 140fsrms-jitter and -72dBc-reference-spur ring-VCO-based injection-locked clock multiplier using a background triple-point frequency/phase/slope calibrator," in *IEEE Int. Solid-State Circuits Conf. (ISSCC) Dig. Tech. Papers*, Feb. 2019, pp. 490–492.

- [56] D. M. Moore, T. Xanthopoulos, S. Meninger, and D. D. Wentzloff, "A 0.009 mm<sup>2</sup> wide-tuning range automatically placed-and-routed ADPLL in 14-nm FinFET CMOS," *IEEE Solid-State Circuits Lett.*, vol. 1, no. 3, pp. 74–77, Mar. 2018.

- [57] (Jan. 2020). Application Note on Integrated Phase Noise. [Online]. Available: https://www.silabs.com/documents/public/applicationnotes/AN256.pdf

**Huy Cu Ngo** (Member, IEEE) received the B.Eng. degree in electrical and electronic engineering and the M.Eng. degree in physical electronics from the Tokyo Institute of Technology, Tokyo, Japan, in 2015 and 2017, respectively.

He is currently with Kioxia Corporation, Kawasaki, Japan, where he is involved in the design of analog mixed-signal circuits and architectures for advanced high-speed wireline communication. His current interests include high-speed wireline transceivers and analog to digital converters.

Wei Deng (Senior Member, IEEE) received the B.S. and M.S. degrees in electronic engineering from the University of Electronic Science and Technology of China (UESTC), Chengdu, China, in 2006 and 2009, respectively, and the Ph.D. degree in electronic engineering from the Tokyo Institute of Technology, Tokyo, Japan, in 2013.

From 2013 to 2014, he was a Post-Doctoral Researcher with the Tokyo Institute of Technology. From 2015 to 2019, he was with Apple Inc., Cupertino, CA, USA, working on radio frequency

(RF), millimeter-wave (mm-wave), and mixed-signal IC design for wireless transceivers and Apple A-series processors. Since 2019, he has been a Faculty Member of the Department of Microelectronics and Nanoelectronics, Tsinghua University, Beijing, China. He has authored or coauthored over 100 IEEE journal and conference articles. He holds four issued U.S. patents. His research interests include RF, mm-wave, terahertz, and mixed-signal integrated circuits and system for wireless communications, radars, and imaging systems.

Dr. Deng currently serves as a Technical Program Committee Member of the IEEE International Solid-State Circuits Conference (ISSCC), the IEEE Symposium on VLSI Circuits, and the IEEE European Solid-State Circuits Conference (ESSCIRC).

Kengo Nakata received the B.Eng. degree in electrical and electronic engineering and the M.Eng. degree in physical electronics from the Tokyo Institute of Technology, Tokyo, Japan, in 2014 and 2016, respectively.

**Toru Yoshioka** received the B.Eng. degree in electrical and electronic engineering and the M.Eng. degree in physical electronics from the Tokyo Institute of Technology, Tokyo, Japan, in 2015 and 2017, respectively.

**Jun Emmei** received the B.Eng. degree from the Tokyo University of Science, Tokyo, Japan, in 2015, and the M.Eng. degree from the Tokyo Institute of Technology, Tokyo, in 2017.

**Bangan Liu** (Member, IEEE) received the B.Eng. degree from Northwestern Polytechnical University, Xian, China, in 2011, the M.S. degree from the University of Science and Technology of China, Hefei, China, in 2014, and the Ph.D. degree from the Tokyo Institute of Technology, Tokyo, Japan.

He was an Intern at Apple Japan Design Center, Tokyo, in 2019. He is currently with Qualcomm Inc., San Diego, CA, USA, where he is involved in the development of high-performance cellular communication systems. His research inter-

ests include high-performance frequency synthesizers, fully synthesizable analog/RF circuits, high-performance wireless transceivers, and digitalintensive/digitally assisted mixed-signal systems.

Yuncheng Zhang (Graduate Student Member, IEEE) received the B.S. and M.E. degrees in electrical engineering from the University of Science and Technology of China (USTC) in 2013 and 2016, respectively. He is currently pursuing the Ph.D. degree with the Tokyo Institute of Technology.

His research interests include power efficient wireless transceivers, all-digital phase-locked-loops, and analog to digital converters.

**Junjun Qiu** (Graduate Student Member, IEEE) received the B.Sc. degree in electrical and electronic engineering from the East China University of Science and Technology, Shanghai, China, in 2016, and the M.E. degree in electrical and electronic engineering from the Tokyo Institute of Technology, Tokyo, Japan, in 2018, where she is currently pursuing the Ph.D. degree in electrical and electronic engineering.

She was focusing on fully synthesizable digital baseband circuit design for sub-GHz wireless trans-

ceiver system. Her current research interests include high performance phase locked loop design and mixed signal wireless communication system design for Bluetooth low energy. She was a recipient of the IEEE SSCS Student Travel Grant Award in 2020.