# Flicker Phase-Noise Reduction Using Gate–Drain Phase Shift in Transformer-Based Oscillators

Xi Chen<sup>®</sup>, *Graduate Student Member, IEEE*, Yizhe Hu<sup>®</sup>, *Member, IEEE*, Teerachot Siriburanon<sup>®</sup>, *Senior Member, IEEE*, Jianglin Du<sup>®</sup>, *Member, IEEE*,

Robert Bogdan Staszewski<sup>®</sup>, Fellow, IEEE, and

KODEIT DOGUAII STASZEWSKI<sup>–</sup>, *Fellow*, *IEEE*, all

Anding Zhu<sup>D</sup>, Senior Member, IEEE

Abstract-This article presents a wide-band suppression technique of flicker phase noise (PN) by means of a gate-drain phase shift in a transformer-based complementary oscillator. We identify that after naturally canceling its second-harmonic voltage by the complementary operation itself, third-harmonic current entering the capacitive path is now the main cause of asymmetry in the rising and falling edges, leading to the 1/f noise upconversion. A complete  $1/f^3$  PN analysis for the transformer-based complementary oscillator is discussed. By tuning gate-drain capacitance ratio, a specific phase-shift range is introduced at the gate and drain nodes of the cross-coupled pair to mitigate the detrimental effects of ill-behaved third-harmonic voltage, thus lowering the flicker PN. To further reduce the area and improve the PN in the thermal region, we introduce a new triple-8-shaped transformer. Fabricated in 22-nm FDSOI, the prototype occupies a compact area of 0.01 mm<sup>2</sup> and achieves  $1/f^3$ PN corner of 70kHz, PN of -110dBc/Hz at 1MHz offset, figureof-merit (FoM) of -182 dB at 9 GHz, and 39% tuning range (TR). It results in the best FoM with normalized TR and area (FoM<sub>TA</sub>) of -214dB at 1MHz offset.

*Index Terms*— Transformer-based oscillator, gate–drain phase shift, passive gain, complementary oscillator, flicker noise upconversion, electromagnetic interference, compact area, FDSOI.

#### I. INTRODUCTION

W ITH the CMOS devices scaling down, their worsening 1/f noise [1], [2] leads to the increase of flicker phase noise (PN) in oscillators. This has become a serious problem, attracting extensive research [3]–[14]. Hajimiri and Lee [3] first explained the 1/f noise upconversion mechanisms using

Manuscript received June 22, 2021; revised September 15, 2021; accepted November 28, 2021. Date of publication December 7, 2021; date of current version February 25, 2022. This work was supported in part by the Science Foundation Ireland under Grant 14/RP/I2921 and Grant 17/NSFC/4850, in part by the Marie Sklodowska-Curie Actions under Grant 746142, and in part by the Microelectronic Circuits Centre Ireland (MCCI) through Enterprise Ireland under Grant TC-2015-0019. This article was recommended by Associate Editor L. Ye. (*Corresponding authors: Yizhe Hu; Teerachot Siriburanon.*)

Xi Chen, Teerachot Siriburanon, Jianglin Du, and Anding Zhu are with the School of Electrical and Electronic Engineering, University College Dublin, Dublin 4, D04 V1W8 Ireland (e-mail: xi.chen@ucdconnect.ie; teeracthot. siriburanon@ucd.ie; jianglin.du@ucdconnect.ie; anding.zhu@ucd.ie).

Yizhe Hu and Robert Bogdan Staszewski are with the School of Electrical and Electronic Engineering, University College Dublin, Dublin 4, D04 V1W8 Ireland, and also with the Microelectronic Circuits Centre Ireland (MCCI), Dublin 4, D04 V1W8 Ireland (e-mail: yhu@ucd.ie; robert.staszewski@ucd.ie).

Color versions of one or more figures in this article are available at https://doi.org/10.1109/TCSI.2021.3131968.

Digital Object Identifier 10.1109/TCSI.2021.3131968

10000 Yang JSSC 19 Seong-JSSC'19 1/f<sup>3</sup> Noise Corner(kHz) 00 00 Δ MWCL'15 n-TCAS-||'19 Abudu|-Baylon-TMTT1 JSSC'12 TCAS-II'18 ee-TCAS-II'19 Yuan-TCAS-I'19 Vagner-TMTT'19 ISSC'18 -Ximenes-TMTT17 Guo-/SSCC'19 Hu-JSSC'18 El-Aassar-RFIC'19 -C/CC'19 LC-OSC This Wor 🛆 Ring-OSC 220 -215 -210 -205 -200 -195 -190 -185 -180 FoM<sub>TA</sub> @1MHz (dB)

\*FoM<sub>TA</sub> = PN - 20log<sub>10</sub>( $f_0/\Delta f$ ) + 10log<sub>10</sub>( $P_{DC}/1$ mW) - 20log<sub>10</sub>(TR/10) + 10log<sub>10</sub>(Area/1mm<sup>2</sup>) Fig. 1 Survey of 1/ $f^3$  PN corper versus FoM<sub>T2</sub> (emphasizing tuning range

Fig. 1. Survey of  $1/f^3$  PN corner versus FoM<sub>TA</sub> (emphasizing tuning range and area) in *LC*-tank and ring oscillators.

an impulse sensitivity function (ISF), which suggests that a symmetric oscillation waveform could suppress any 1/f noise from upconversion. The original ISF theory works well in explaining flicker PN in ring oscillators [4], [15], [16], but does not clearly explain the origins of the asymmetric waveform in *LC*-tank oscillators and their flicker PN mechanisms.

Bonfanti *et al.* [7] and Pepe *et al.* [8] claimed that the  $1/f^3$ PN in LC-tank oscillators is caused by the third-harmonic current (i.e., I<sub>H3</sub>) entering the capacitive path of LC-tank, while Shahmohammadi et al. [9] demonstrated that it is the second-harmonic current (i.e.,  $I_{H2}$ ), rather than  $I_{H3}$ , entering the non-resistive path, causing waveform asymmetries, which ultimately leads to the flicker PN. Recently, these two pioneering but obviously conflicting explanations were unified in [12] concluding that both ill-behaved second- and third-harmonic voltages (i.e.,  $V_{H2}$  and  $V_{H3}$ ) result in the flicker noise upconversion, but  $V_{H2}$  dominates over  $V_{H3}$  in nMOS-only oscillators, while in complementary oscillators,  $V_{\rm H3}$  is an order-of-magnitude larger than  $V_{\rm H2}$ . Compared with its nMOS-only counterpart, the complementary oscillator is more favorable for applications requiring low-power consumption, limited swing (avoiding thick-oxide devices), elimination of additional biasing, and supporting standard supply voltages [14]. However, a detailed quantitative analysis of a common-mode (CM) return path and flicker noise upconversion in a conventional complementary oscillator is still missing.

This work is licensed under a Creative Commons Attribution 4.0 License. For more information, see https://creativecommons.org/licenses/by/4.0/

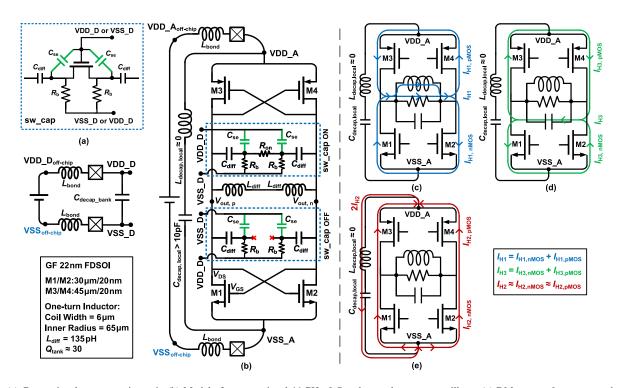

Fig. 2. (a) Conventional sw-cap tuning unit. (b) Model of a conventional 11 GHz *LC*-tank complementary oscillator. (c) DM current  $I_{H1}$  return path. (d) DM current  $I_{H2}$  return path. (e) CM current  $I_{H2}$  return path.

Several flicker PN reduction mechanisms have been identified [12]: 1) second-harmonic resonance [9], [10], [17]–[20]; 2) narrowing of the conduction angle (i.e., class-C) [11], [21]–[25]; 3) gate–drain phase shift based on an *RC* delay [8], [26]. However, the second-harmonic resonance is a narrow-band suppression technique, the narrowing of a conduction angle needs a careful consideration of start-up, and the gate–drain phase shift based on an *RC* delay suffers from process, voltage, and temperature (PVT) variations. Thus, a new flicker PN suppression technique that is wideband and PVT-robust would be highly sought, especially for supporting 5G/6G communications or other emerging applications [27]–[37].

Concurrently, saving the silicon area has always been desired by IC designers. This is especially true for *LC*-tank oscillators since the passive devices cannot scale down with the technology advancements [31], [38]-[42]. Although some researchers put active devices underneath the inductive structures at the cost of quality (Q)-factor degradation [31], [41], [42], customarily, a sufficient separation between the inductive devices and other sensitive blocks should be kept to mitigate the electromagnetic interference (EMI). An 8-shaped inductor is a favorable solution to relieve the EMI, but at the cost of a larger area and the Q-factor degradation [43]. In [38] and [40], an ultra-compact 8-shaped transformer-based oscillator was proposed with the switchedcapacitor (sw-cap) banks placed in the EMI-free regions to save the area, but the long and ill-defined differential-mode (DM) return path of the transformer significantly worsens its Q-factor. On the other hand, ring oscillators benefit from the CMOS technology scaling, occupying a compact area

with a wide TR, and are not susceptible to magnetic pulling. However, both their thermal and flicker PN are much worse than in the LC oscillators, and they are highly susceptible to the supply noise (i.e., high supply pushing).

In this article, we propose a complementary oscillator using a triple-8-shaped transformer, simultaneously featuring a compact area of 0.01 mm<sup>2</sup>, wide tuning range (TR) of 39%,  $1/f^3$  PN corner of 70kHz, and electromagnetic compatibility, combining both benefits of *LC*-tank-based and inverter-ringbased oscillators (see the survey in Fig. 1) [14]. The rest of the paper is organized as follows. Section II discusses in detail the CM return path in a conventional complementary *LC* oscillator and analyzes quantitatively its flicker noise upconversion mechanism.

Section III presents a complete theory of the transformer's gain and phase shift. Section IV discloses the proposed transformer-based complementary oscillator design, fully clarifying the flicker noise upconversion mechanism in a complementary class-F operation, and reveals how the gate–drain phase shift can suppress it. Experimental results are shown in Section V.

# II. FLICKER NOISE UPCONVERSION AND CM RETURN PATH IN COMPLEMENTARY OSCILLATORS

For the purpose of fully clarifying the mechanism of flicker noise upconversion in complementary oscillators, a conventional 11 GHz complementary class-B oscillator was designed in 22-nm FDSOI CMOS, as shown in Fig. 2(b). It comprises the complementary cross-coupled switching pairs (M1-M2 & M3-M4) providing transconducance  $G_m$ , main inductor  $L_{diff}$ ,

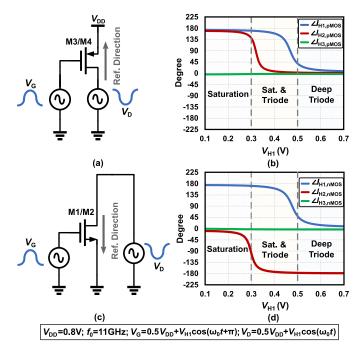

Fig. 3. Effect of oscillating amplitude on phase shift of various harmonic currents in nMOS and pMOS transistors mimicking M1 (or M2) and M3 (or M4) in Fig. 2(b). (a)(c) Simulation test-benches for pMOS and nPMOS transistor, respectively. (b)(d) Simulated phase shifts for pMOS and nPMOS transistor, respectively, for  $V_{\text{DD}} = 0.8$ V (phase degrees are calculated from cosines).

and switched-capacitor (sw-cap) banks [see Fig. 2(a)], modeled by  $C_{\text{diff}}$  and the parasitic single-ended capacitance  $C_{\text{se}}$  (shown in both ON and OFF modes). The  $C_{\text{decap}}$ ,  $L_{\text{decap}}$ , and  $L_{\text{bond}}$ components model the decoupling capacitor with its parasitic inductance, and bonding-wire inductance, respectively. Two off-chip supplies are used: VDD\_Aoff-chip, VDD\_Doff-chip, sharing the global ground VSSoff-chip. The "analog" power domain (VDD\_A/VSS\_A) is for the  $G_{\text{m}}$  transistors, while the "digital" power domain (VDD\_D/VSS\_D) is for the swcap banks. The separation of two power domains intends to avoid unwanted coupling from the sw-cap banks to the oscillator's core when incorporating this oscillator in a PLL. It could further improve thermal PN by reducing parasitic CM capacitance of sw-cap banks seen by an nMOS-only oscillator's CM path [10].

#### A. CM Return Path in Complementary Oscillators

Since the non-resistive terminations of CM currents (e.g.,  $I_{H2}$ ) are the main contributor to the flicker noise upconversion in nMOS-only class-B oscillators [10], [44], it would be interesting to study the CM return path in its complementary counterparts by figuring out the relationship between the CM currents generated by the pMOS and nMOS coupled-pairs.

A test-bench [see Fig. 3(a) and (c)] is set up where the pMOS and nMOS transistors [modeling M3 & M1 in Fig. 2(b)] are given similar operating conditions as in Fig. 2(b). For example, assuming  $V_D \approx 0.5V_{DD} + V_{H1}\cos(\omega_0 t)$  and  $V_G \approx 0.5V_{DD} + V_{H1}\cos(\omega_0 t + \pi)$ , Fig. 3(b) and (d) reveal the phase

of each harmonic current at the drain nodes of pMOS and nMOS (i.e.,  $\angle I_{H1-3,pMOS}$  and  $\angle I_{H1-3,nMOS}$ ), respectively. Due to the oscillator's complementary configuration in Fig. 2,  $V_{\rm H1}$ is saturated at around  $0.5V_{DD}$  (i.e.,  $\approx 0.4V$ ), resulting in a railto-rail output swing for the single-ended output of  $V_{out,p}$  or  $V_{\text{out,n}}$ . As shown in Fig. 3(b) and (d), when  $V_{\text{H1}} = 0.4$  V, both I<sub>H1,pMOS</sub> and I<sub>H1,nMOS</sub> in the pMOS and nMOS coupled-pairs are out-of phase of  $V_{\rm DS}$ , demonstrating that the coupled-pairs will behave like "negative"  $G_m$  in the oscillator. Interestingly, the phase  $\angle I_{\text{H2,pMOS}}$  is around 0° (see Fig. 3(b)), while phase  $\angle I_{\text{H2,nMOS}}$  is  $-180^{\circ}$  (see Fig. 3(d)), when  $V_{\text{H1}} = 0.4$  V. With the consideration of their own opposite reference directions, their CM current will be ultimately in-phase, as shown in Fig. 2(e). In other words, the CM current generated by the nMOS cross-coupled pair will be almost entirely absorbed by the pMOS cross-coupled pair with proper sizing of the transistor width ratio  $W_{\rm pMOS}/W_{\rm nMOS}$ .

Furthermore, the complementary oscillator provides a welldefined CM return path due to the short physical distance between the local supplies of VDD\_A and VSS\_A, resulting in the parasitic inductance (i.e.,  $L_{decap}$ ) of decoupling capacitor (i.e.,  $C_{decap}$ ) close to zero. Considering that  $C_{decap}$ can be large and also thanks to the low impedance of  $1/G_m$  of M1–M4, the CM voltage (e.g.,  $V_{H2}$ ) is an order-ofmagnitude smaller than in an nMOS-only oscillator. Thus, the ill-behaved  $V_{H2}$  is no longer the main contributor to the flicker noise upconversion, while the  $I_{H3}$  entering the capacitive path<sup>1</sup> (see Fig.2(d)), generating  $V_{H3}$ , now starts playing a critical role.

#### B. Flicker Noise Upconversion and Numerical Verification

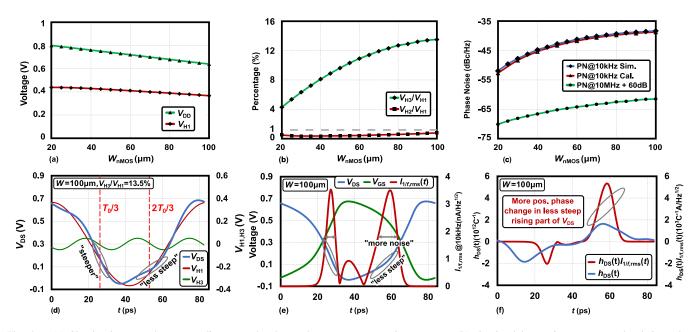

To quantitatively study how  $V_{\text{H3}}$  affects the flicker noise upconversion in the complementary oscillator of Fig.2, we increase the width  $W_{n\text{MOS}}$  from 20  $\mu$ m to 100  $\mu$ m, while properly sizing  $W_{p\text{MOS}}/W_{n\text{MOS}}$  to fully suppress  $V_{\text{H2}}$  and reducing the power supply level [see Fig.4(a)] to maintain the same power consumption. As shown in Fig.4(b), the  $V_{\text{H3}}/V_{\text{H1}}$ ratio increases from 4% to 13%, but  $V_{\text{H2}}/V_{\text{H1}}$  remains much lower than 1% and  $V_{\text{H1}}$  keeps relatively constant [around  $V_{\text{DD}}/2 = 0.4$  V, see subfigure (a)]. The waveform shaping of  $V_{\text{DS}}$  caused by  $I_{\text{H3}}$  entering the capacitive nature of the DM tank can be modeled by [12] and [13]

$$V_{\rm DS} \approx V_{\rm H0} + V_{\rm H1} \cos(\omega_0 t) + V_{\rm H3} \cos(3\omega_0 t + \frac{\pi}{2})$$

(1)

which models  $V_{\rm DS}$  at the representative point:  $W_{\rm nMOS} = 100 \,\mu {\rm m}$  [see Fig. 4(d)]. Obviously, the strong  $V_{\rm H3}$  will cause steeper falling edges and less steep rising edge, introducing waveform asymmetries. The actual simulated  $V_{\rm GS}$  and  $V_{\rm DS}$  of M1 in Fig. 4(e) (including all harmonics) for the point confirm the observation.

Fig. 4(c) shows that PN at 10kHz offset gets worsened significantly with the increase in  $V_{\text{H3}}/V_{\text{H1}}$ . Thus, the claim in [9] and [45] that the capacitive terminations of  $I_{\text{H3}}$  do

<sup>&</sup>lt;sup>1</sup>Interestingly,  $I_{\text{H1}}$  will partially enter the inductive path (see Fig. 2(c)), generating a little positive imaginary energy to balance the negative imaginary energy due to  $I_{\text{H3}}$  entering capacitive path (i.e., "Law of Conservation of Energy").

Fig. 4. (a) Simulated  $V_{\text{H1}}$  and corresponding  $V_{\text{DD}}$  that keeps the power consumption constant, (b) simulated harmonic contents at the drain nodes, and (c) calculated and simulated PN at 10 kHz offset with increasing  $W_{\text{nMOS}}$  (Conditions: for each  $W_{\text{nMOS}}$ ,  $W_{\text{pMOS}}$  is sized properly to suppress  $V_{\text{H2}}$ ). (d) Characterization of  $V_{\text{DS}}$  using only  $V_{\text{H1}}$  and  $V_{\text{H3}}$  [see (1)]. (e) Waveforms of  $V_{\text{GS}}$ ,  $V_{\text{DS}}$  (including all harmonics) and the corresponding rms value of flicker current noise  $I_{1/f, \text{rms}}(t)$  at a 10 kHz offset. (f) Non-normalized ISF  $h_{\text{DS}}$  and  $h_{\text{DS}} \cdot I_{1/f, \text{rms}}$ .

not contribute to the flicker noise upconversion is clearly not applicable to the complementary oscillator. To quantitatively study the flicker noise upconversion, we employ the theory framework in [10]–[13], where the flicker PN could be calculated by

$$\mathcal{L}_{1/f^3}(\Delta\omega) = \left(\frac{1}{2} \cdot \frac{\sqrt{2}}{\Delta\omega T_0} \int_0^{T_0} h_{\mathrm{DS}}(t) \cdot I_{1/f,\,\mathrm{rms}}(t)dt\right)^2 \quad (2)$$

where  $I_{1/f, rms}(t)$  is the periodically modulated rms value of flicker noise current at a low offset frequency  $\Delta \omega$  (e.g.,  $2\pi \times 10$  kHz),  $T_0 (= 2\pi/\omega_0)$  is the oscillation period, and  $h_{DS}(t)$  is the non-normalized ISF associated with  $V_{DS}$  of M1–M4 in Fig. 2(b). As shown in Fig. 4(f), the "less steep" rising part of  $V_{DS}$  is more vulnerable to the noise impulse injection than is its falling part. Thus, the flicker noise  $I_{1/f, rms}(t)$  introduces more positive phase change in its rising part (i.e., more positive area of effective non-normalized ISF  $h_{DS}(t) \cdot I_{1/f, rms}(t)$ ) than in its falling part, leading to the flicker noise upconversion. The above analysis is numerically verified with simulations covering different transistor widths of  $W_{nMOS}$  and  $W_{pMOS}$ , as shown in Fig. 4(c), thus proving the effectiveness of the method.

# III. GATE–DRAIN PHASE SHIFT IN TRANSFORMER-BASED COMPLEMENTARY OSCILLATORS

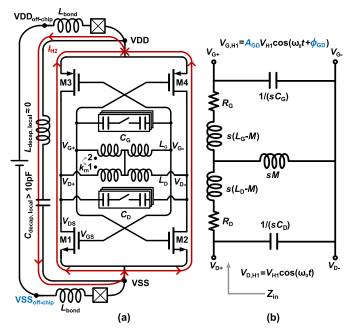

To be able to further improve both the thermal and flicker PN in the complementary oscillator, we replace the inductor in the conventional topology of Fig. 2(b) with a transformer (e.g., its turns ratio = 1:2), as shown in Fig. 5(a). A "2-port" topology is employed to avoid two possible oscillation modes (i.e., low-frequency mode at  $\omega_{\rm L}$  and high-frequency mode at  $\omega_{\rm H}$ ) in a transformer-based "1-port" topology [46]–[49].

Fig. 5. (a) Schematic of the proposed transformer-based complementary oscillator and its CM return path. (b) *T*-model of the transformer-based resonator for the DM signal  $(M = k_m \sqrt{L_D L_G})$ .

That is, the drain tank (i.e.,  $L_D$ ,  $C_D$ ) is connected to the drainnodes of M1–4, while the gate tank (i.e.,  $L_G$ ,  $C_G$ ) is crossconnected to their gate-nodes. Both tanks are coupled by a coupling factor  $k_m$ .  $L_{bond}$ ,  $C_{decap,local}$ , and  $L_{decap,local}$  ( $\approx 0$ ) model the wire-boning inductance, local decoupling capacitor and its parasitic inductance, respectively. To provide the dc operating points for M1–4, the center taps of the primary coil  $L_D$  and of the secondary coil  $L_G$  are connected. The oscillation frequency  $\omega_0$  (=  $\omega_L$ ) of the proposed topology can be

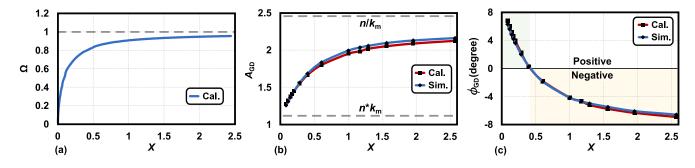

Fig. 6. (a) Calculated normalized oscillation frequency  $\Omega$ . Calculated and simulated (b) gate-drain passive gain  $A_{GD}$  and (c) phase shift  $\phi_{GD}$  of the proposed transformer-based resonator ( $n \approx 1.65$ ,  $k_{\rm m} \approx 0.67$ ).

expressed as [50], [51]

$$\omega_0 = \sqrt{\frac{1 + n^2 X - \sqrt{(1 + n^2 X)^2 - 4n^2 X (1 - k_{\rm m}^2)}}{2(1 - k_{\rm m}^2)}} \omega_{\rm G} \quad (3)$$

where  $\omega_{\rm G} \ (= 1/\sqrt{L_{\rm G}C_{\rm G}})$  represents the resonating frequency of the gate tank (i.e., secondary tank),

$$n = \sqrt{\frac{L_{\rm G}}{L_{\rm D}}} \tag{4}$$

is the "effective turns ratio" (different from the "turns ratio"), and

$$X = \frac{C_{\rm G}}{C_{\rm D}} \tag{5}$$

is the gate-drain capacitance ratio, which adds a degreeof-freedom and a critical "knob" to affect the oscillator's performance for a given transformer and oscillating frequency range. For example, some specific X will enable a class-F operation [52] for third-harmonic extraction to generate low-PN mmW carrier [10], [53]. Besides, the passive gain  $A_{GD}$ and gate–drain phase shift  $\phi_{GD}$  for the fundamental oscillating waveform in the transformer-based resonator [see Fig. 5(b)] also depend on X, which has a large influence on both thermal PN and flicker PN of oscillators.

# A. Gate–Drain Passive Gain A<sub>GD</sub>

Compared with an inductor-based oscillator, the passive gain in a transformer-based oscillator could amplify the effective negative resistance " $-G_{\rm m}$ " by  $A_{\rm GD}$  times. Thus, for the same start-up condition, the thermal PN part caused by  $4kT\gamma g_{\rm m}$ noise in a transformer-based oscillator is  $A_{GD}$  times smaller than that in an inductor-based oscillator. The relationship between  $A_{\text{GD}}$  and X is derived based on a T-model [54] of the transformer-based resonator [see Fig. 5(b)], where M  $(= k_{\rm m} \sqrt{L_{\rm D} L_{\rm G}})$  is the mutual inductance,  $V_{\rm G}$  and  $V_{\rm D}$  are assumed as DM ac ground. Applying Kirchhoff's law, the voltage transfer function of  $V_{\rm G}/V_{\rm D}$  can be derived as [52]

$$H(s) = \frac{V_{\rm G}}{V_{\rm D}} = \frac{Ms}{\alpha_3 s^3 + \alpha_2 s^2 + \alpha_1 s + \alpha_0} \tag{6}$$

where  $\alpha_3 = C_{\rm G} L_{\rm D} L_{\rm G} (1 - k_{\rm m}^2), \ \alpha_2 = C_{\rm G} (L_{\rm G} R_{\rm D} + L_{\rm D} R_{\rm G}),$  $\alpha_1 = L_{\rm D} + C_{\rm G} R_{\rm D} R_{\rm G}$ , and  $\alpha_0 = R_{\rm D}$ .

Substituting  $s = j\omega_0$  and the quality factors of two coils at  $\omega_0$  as  $Q_{\rm D} = \omega_0 L_{\rm D}/R_{\rm D}$  and  $Q_{\rm G} = \omega_0 L_{\rm G}/R_{\rm G}$  into (6), the frequency response of the transformer-based resonator for the drain fundamental waveform  $V_{D,H1}$  can be written as

$$H(j\omega_0) = \frac{n\kappa_{\rm m}}{(1 - k_{\rm m}^2 - \frac{1}{Q_{\rm D}Q_{\rm G}})\Omega^2 - 1 + j(\frac{1}{Q_{\rm D}} - \frac{Q_{\rm D} + Q_{\rm G}}{Q_{\rm D}Q_{\rm G}}\Omega^2)}$$

(7)

where

$$\Omega(X) = \frac{\omega_0}{\omega_G} = \sqrt{\frac{1 + n^2 X - \sqrt{(1 + n^2 X)^2 - 4n^2 X (1 - k_m^2)}}{2(1 - k_m^2)}}$$

(8)

is the normalized oscillation frequency on  $\omega_{\rm G}$ , and<sup>2</sup>

. . . . .

$$\lim_{\substack{X \to 0 \\ \lim_{X \to \infty} \Omega(X) = 1.}} \Omega(X) = 1.$$

(9)

Fig. 6(a) shows the relationship between  $\Omega$  and X for the given transformer's *n* (e.g.,  $\sqrt{L_G/L_D} \approx 1.7$ ) and  $k_m \approx 0.7$ ). Once X is large enough (e.g., > 2),  $\Omega$  is close to 1, meaning the oscillation frequency will be dominated by the resonance frequency of the gate tank (i.e.,  $\omega_0 \approx \omega_G$ ). Accordingly, the amplitude response  $A_{GD}$  for the drain's fundamental waveform  $V_{\text{D,H1}}$  is given by [see Fig. 5(b)]

$$A_{\rm GD}(X) = |H(j\omega_0)|$$

$$= \frac{nk_{\rm m}}{\sqrt{\left(\left(\frac{1}{Q_{\rm D}Q_{\rm G}} + k_{\rm m}^2 - 1\right)\Omega^2 + 1\right)^2 + \left(\frac{1}{Q_{\rm D}} - \frac{Q_{\rm D} + Q_{\rm G}}{Q_{\rm D}Q_{\rm G}}\Omega^2\right)^2}}$$

$$\approx \frac{nk_{\rm m}}{1 - (1 - k_{\rm m}^2)\Omega^2} \tag{10}$$

where the terms related to  $1/Q_D^2$ ,  $1/Q_G^2$ , and  $1/(Q_DQ_G)$  could be disregarded since they are inversely proportional to the square of the quality factors of the coils. It can be proven that  $A_{\text{GD}}$  would increase with  $\Omega$  and X, and

$$\begin{cases} \lim_{X \to 0, \, \Omega \to 0} A_{\rm GD} \approx n k_{\rm m} \\ \lim_{X \to 1/n^2, \, \Omega \to 1/\sqrt{1+k_{\rm m}}} A_{\rm GD} \approx n \\ \lim_{X \to \infty, \, \Omega \to 1} A_{\rm GD} \approx \frac{n}{k_{\rm m}}. \end{cases}$$

(11)

<sup>2</sup>See Appendix for the proof of  $\lim_{X\to\infty} \Omega(X) = 1$ .

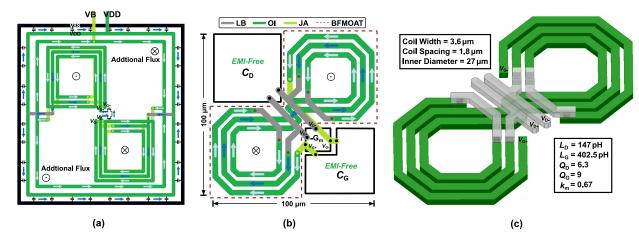

Fig. 7. (a) Transformer layout introduced in [40]. (b) Proposed triple-8-shaped transformer layout and (c) its 3-D illustration with parameters.

Fig. 6(b) visualizes (10) for a given *n* and  $k_m$  of the transformer. Note that when X > 2,  $A_{GD}$  is almost saturated. The transformer-based oscillator can thus operate in the passive gain saturation region.

#### B. Gate–Drain Phase Shift $\phi_{GD}$

The transformer could also introduce a phase shift  $\phi_{GD}$  between  $V_{G,H1}$  and  $V_{D,H1}$  [see Fig. 5(b)], which is associated with a potential reduction in the flicker PN in [14].  $\phi_{GD}$  can be expressed as

$$\phi_{\rm GD}(X) = \angle H(j\omega_0)$$

=  $\arctan\left(\frac{\frac{1}{Q_{\rm D}} - \frac{Q_{\rm D} + Q_{\rm G}}{Q_{\rm D}Q_{\rm G}}\Omega^2}{\left(\frac{1}{Q_{\rm D}Q_{\rm G}} + k_{\rm m}^2 - 1\right)\Omega^2 + 1}\right).$  (12)

Similarly, we get

$$\lim_{\substack{X \to 0, \ \Omega \to 0}} \phi_{\rm GD} = \arctan\left(\frac{1}{Q_{\rm D}}\right) > 0$$

$$\lim_{\substack{X \to X_0, \ \Omega \to 0}} \phi_{\rm GD} = 0$$

$$\lim_{\substack{X \to \infty, \ \Omega \to 1}} \phi_{\rm GD} \approx -\arctan\left(\frac{1}{k_{\rm m}^2 Q_{\rm G}}\right) < 0$$

(13)

where

$$X_0 = \frac{k_{\rm m}^2 Q_{\rm G}^2 + Q_{\rm D} Q_{\rm G}}{n^2 (Q_{\rm D}^2 + Q_{\rm D} Q_{\rm G})} \approx \frac{1}{n^2} \frac{1 + k_{\rm m}^2}{2} \le \frac{1}{n^2}$$

(14)

with an assumption of  $Q_{\rm D} \approx Q_{\rm G}$ .

Clearly, the transformer-induced phase shift is mainly caused by its limited quality factors of  $Q_D$  and  $Q_G$  achievable in CMOS radio-frequency integrated circuits (RFICs). As shown in Fig. 6(c) and (13), either a positive or negative phase shift of  $\phi_{GD}$  can be implemented in the transformer by tuning X. Intuitively, with large capacitance at the gate nodes, the phase of the fundamental waveform is delayed from the primary coil coupling to the secondary coil. In summary, for a given transformer,  $A_{GD}$  and  $\phi_{GD}$  can be well-controlled by gate–drain capacitance ratio X (i.e.,  $= C_G/C_D$ ) in the resonator, which is independent of the tuned oscillation frequency  $\omega_0$ . Simulation (based on EMX S-parameter model) and theoretical results reach a good agreement as shown in Fig. 6, demonstrating the efficacy of the above analysis.

# IV. PROPOSED OSCILLATOR WITH A COMPACT TRIPLE-8-SHAPED TRANSFORMER

In this section, we propose an ultra-compact complementary oscillator based on a triple-8 shaped transformer. Its flicker PN is suppressed by inducing a positive phase shift in the transformer.

## A. Design of Triple-8 Shaped Transformer With Compact Area

An 8-shaped transformer was proposed in [38] and [40] to substantially reduce the DCO area. However, its actual DM return path, including its  $V_{\text{DD}}$ ,  $V_{\text{B}}$  lines, was neglected in the analysis in [40], see Fig. 7(a). The excessively long  $V_{\text{DD}}$ ,  $V_{\text{B}}$  lines significantly limit the DM quality factors of both the primary and secondary coils. Furthermore, they may also introduce an additional magnetic flux, as shown in Fig.7(a).

The proposed 1:2 triple-8-shaped transformer-based oscillator is revealed in Fig.7(b). 3D view and parameters of the transformer are shown in Fig.7(c). There are no surrounding  $V_{DD}$  and  $V_B$  lines, thereby ensuring a well-defined DM return path and high Q for the compact occupied area (i.e.,  $0.01 \text{ mm}^2$ ). The proposed transformer is constructed in a coplanar interwound manner with three thick metal layers (called JA, OI, and LB in FDSOI), and a native layer (BFMOAT) is used to increase the high resistivity of the substrate, decreasing the eddy currents and further increasing the Q. Its coil width of 3.6  $\mu$ m and inner space of 1.8  $\mu$ m are optimized in a  $100 \times 100 \,\mu m^2$  area, yielding the primary quality factor  $Q_{\rm p} \approx 9$ , the secondary quality factor  $Q_{\rm s} \approx 6.5$ , and  $k_{\rm m} \approx 0.7$  for the intended frequency range. Two swcap banks are placed on the EMI-suppressed area, where the magnetic fluxes cancel each other due to the property of 8-shaped coils.

To further save the area and provide a defined local CM return path, the required minimum capacitance for the onchip decoupling capacitors should be considered. For a ring oscillator, a large decoupling capacitance (e.g.,  $\sim 100 \,\text{pF}$ ) may

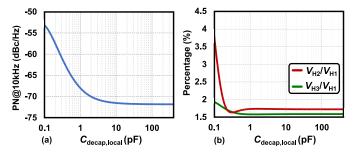

Fig. 8. Simulated (a) PN at 10kHz and (b)  $V_{\text{H2}}/V_{\text{H1}}$ ,  $V_{\text{H3}}/V_{\text{H1}}$  with different local decoupling capacitance  $C_{\text{decap,local}}$  for X = 0.2.

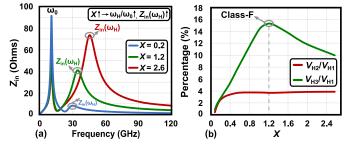

Fig. 9. (a) Simulated input impedance  $Z_{in}$  of the transformer-based resonator with different X. (b) Simulated  $V_{H3}/V_{H1}$ ,  $V_{H2}/V_{H1}$  with different X.

be required to prevent the supply noise (especially, lowfrequency components) from converting to PN due to the ring oscillator's considerable supply pushing effects (typically, several GHz/V) [15], [55], [56]. However, in transformer-based oscillators, since they naturally feature low supply pushing (typically <100 MHz/V) [52], [57], the on-chip decoupling capacitance is mainly to provide the local CM return path. Fig.8 suggests that once the local decoupling capacitance  $C_{\text{local,decap}}$  for the proposed transformer-based complementary oscillator is larger than ~10 pF, it can effectively suppress the second-harmonic voltage  $V_{\text{H2}}$  (also resulting in lower  $V_{\text{H3}}$ ), thus improving the flicker PN.

# B. $1/f^3$ Phase Noise in Complementary Class-F Oscillators

As per conclusions in Section II, the flicker PN in complementary oscillators is mainly caused by the third-harmonic current entering the capacitive path, while  $V_{\text{H2}}$  is suppressed by the complementary operation itself. Thus, to reduce the flicker PN, we *may* force the third-harmonic current  $I_{\text{H3}}$  to enter a resistive load, resulting in a complementary class-F topology (i.e.,  $\omega_{\text{H}} \approx 3\omega_0$ ). The additional resonance frequency  $\omega_{\text{H}}$  of the transformer-based resonator as [48]

$$\frac{\omega_{\rm H}}{\omega_0} = \sqrt{\frac{1 + n^2 X + \sqrt{(1 + n^2 X)^2 - 4n^2 X (1 - k_{\rm m}^2)}}{1 + n^2 X - \sqrt{(1 + n^2 X)^2 - 4n^2 X (1 - k_{\rm m}^2)}}}.$$

(15)

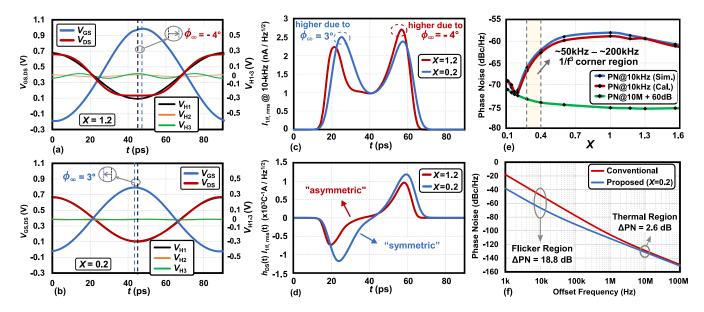

To study how X affects the PN of the proposed oscillator, we sweep X from 0.2 to 1.6 while maintaining the same oscillation frequency  $\omega_0$  and power consumption for a fair PN comparison. Fig. 9(a) plots the resonator's input impedance  $Z_{in}$  for three values of X while Fig. 9(b) shows the harmonic voltage ratios (i.e.,  $V_{H2}/V_{H1}$ ,  $V_{H3}/V_{H1}$ ) across X. Both  $\omega_H$  and  $Z_{in}(\omega_H)$  increase with rising X; specifically, when  $X \approx 1.2$ , the class-F operation is achieved. The simulated thermal PN (e.g., PN at 10MHz offset) and flicker PN (e.g., PN at 10kHz offset) across X are plotted in Fig. 10(e).

Interestingly, the exact class-F operation (i.e.,  $\omega_{\rm H} = 3\omega_0$ ) is not necessary to help improve PN, but it will be useful for the third harmonic extraction at mm-wave frequencies [10], [29], [53]. As shown in Fig. 10(e), the PN at 10MHz offset keeps almost constant from X = 0.6 to X = 1.6, not significantly improved by enhancing  $V_{\text{H3}}$  (i.e., X = 1.2). This phenomenon can be explained by our analysis in the previous section that the improvement of thermal PN in the transformerbased oscillators depends on the reduction in  $4kT\gamma g_{\rm m}$  noise by the gate-drain passive gain  $A_{GD}$  (rather than by class-F itself), which would be saturated when X is large enough. On the other hand, there is a sudden, and rather unexpected, flicker PN degradation in the complementary class-F oscillator, even though its  $V_{DS}$  waveform becomes squarish and symmetric [see Fig. 10(a)] due to the class-F operation and the ill-behaved  $V_{\rm H2}$  (the main contributor of flicker noise upconversion in nMOS-only class-F oscillators [9], [10]) being minimized by the complementary topology. To understand this special 1/f noise upconversion mechanism, we simulate the corresponding  $I_{1/f,rms}$  and the effective non-normalized ISF  $h_{\rm DS} \cdot I_{1/f,\rm rms}$  when X = 1.2 (i.e., class-F operation), as shown in Fig. 10(c) and (d). Due to the negative phase shift  $\phi_{\rm GD}$ of  $V_{\rm GS}$  against  $V_{\rm DS}$  by the transformer [i.e.,  $\phi_{\rm GD} = -4^\circ$ , see Fig. 6(c) and Fig. 10(a)], the peak of  $V_{GS}$  moves a bit closer to the rising edge of  $V_{\text{DS}}$ , leading to the higher  $I_{1/f,\text{rms}}$ [see Fig. 10(c)] getting exposed to the rising edge of  $V_{\rm DS}$ . Ultimately, it causes more positive area of effective ISF,  $h_{\rm DS} \cdot I_{1/f,\rm rms}$ , see Fig. 10(d), resulting in the flicker noise upconversion.

# C. $1/f^3$ Phase Noise Reduction by the Deliberate $\phi_{GD}$

To compensate for the more positive phase change caused by  $I_{1/f,\text{rms}}$  in the complementary class-B [see Fig. 4(f)] or class-F oscillator [see Fig. 10(d)], we could introduce a positive gate-drain phase shift<sup>3</sup> (i.e.,  $\phi_{GD}$ ) in the transformer (see Fig. 6(c)). Per (12), with X decreasing, the peak of  $V_{\rm GS}$  moves towards the falling edges of  $V_{\rm DS}$  [see Fig. 10(b)], increasing the exposure of  $I_{1/f,rms}$  to the falling edges of  $V_{\text{DS}}$  [see Fig. 10(b)], consequently resulting in a null area of effective ISF  $h_{\text{DS}} \cdot I_{1/f,\text{rms}}$  [i.e., no flicker noise upconversion, see Fig. 10(d) and (e)]. It is worth noting that to get a positive drain-to-gate phase shift, some passive gain needs to be sacrificed (see Fig. 6(b) and (c)), which is the reason that PN at 10 MHz offset is worsened in the small X region (e.g. X < 0.15). Practically, the proposed complementary oscillator operates in the region of X < 0.3, achieving low PN, low flicker PN, and wide TR, simultaneously. Fig. 10(e) also illustrates the numerical verification of PN at 10kHz with different X. The agreement between the calculations based on (2) and simulations demonstrates the efficacy of the above analysis. Furthermore, Fig. 11 shows the post-layout simulated

<sup>&</sup>lt;sup>3</sup>Further, we predict that a negative phase shift of  $V_{\text{GS}}$  against  $V_{\text{DS}}$  could suppress the  $1/f^3$  PN in an oscillator with steeper rising edges of  $V_{\text{DS}}$  (e.g.  $I_{\text{H2}}$  entering the inductive termination) [12].

Fig. 10. Simulated full cycle of  $V_{GS}$ ,  $V_{DS}$  of M1/2, and the harmonic contents of  $V_{DS}$  with: (a) X = 1.2 (i.e., class-F operation) and (b) X = 0.2. (c) Simulated rms value of periodically modulated flicker current noise at 10kHz,  $I_{1/f,rms}(t)$ . (d) Effective non-normalized ISF,  $h_{DS}(t) \cdot I_{1/f,rms}(t)$ . (e) PN vs. X (keeping the same frequency and power consumption) and its numerical verification. (f) Simulated PN profile comparison between the conventional complementary class-B oscillator and the proposed oscillator.

\*FoM = PN -  $20\log_{10}(f_0/\Delta f)$  +  $10\log_{10}(P_{\rm DC}/1\rm{mW})$ ;  $V_{\rm DD}$  = 1V for SS corner, 0.9V for other corners

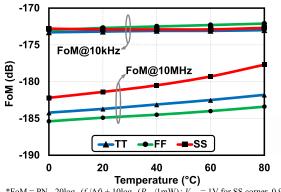

Fig. 11. Post-layout simulations of FoM at 10 kHz and FoM at 10 MHz with different process corners and temperature.

FoM at 10 kHz and at 10 MHz with different process corners and across temperature. FoM at 10 kHz varies much less than FoM at 10 MHz, demonstrating the robustness of the proposed flicker phase noise suppressing technique against process and temperature variations.

To further demonstrate the benefits of the proposed technique, the simulated PN profile comparison between the proposed transformer-based complementary oscillator and the conventional inductor-based complementary oscillator is shown in Fig. 10(f). The proposed oscillator can achieve 19 dB better PN in the flicker PN region (e.g., PN at 10 kHz), while 2.6 dB improvement in the thermal PN region (e.g., PN at 10 MHz).

# V. EXPERIMENTAL RESULTS

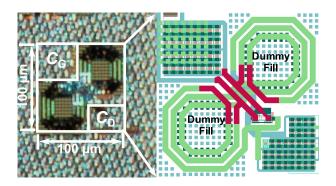

The prototype of the proposed oscillator is fabricated in GlobalFoundries 22-nm FDSOI. The chip microphotograph

Fig. 12. Chip micrograph and zoomed-in view of the layout.

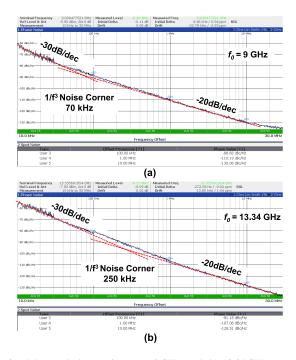

is shown in Fig. 12, occupying a core area of  $0.01 \text{ mm}^2$ . Its PN is evaluated using an R&S 2-Hz–85-GHz FSW Signal and Spectrum Analyzer. The 5-bit coarse tuning bank at the drain nodes of the oscillator, covering the measured TR from 9 to 13.34 GHz (39%), while the fine-tuning bank locates at the gate nodes. When operating at 9GHz [see Fig. 13(a)], the measured PN is -110.2 dBc/Hz at 1 MHz offset, with an excellent  $1/f^3$  PN corner of 70 kHz, while consuming only 6 mW. At the highest frequency of 13.34 GHz, as shown in Fig. 13(b), it achieves -107.1 dBc/Hz at 1 MHz offset, with 250 kHz flicker PN corner, while consuming 5mW, consequently resulting in FoM of -182.6 dB at 1MHz offset. Compared with [40], the proposed oscillator achieves 9 dB improvement in the FoM at 10 MHz offset with occupying 30% smaller area.

Fig. 14(a) and (b) show the measured  $1/f^3$  noise corner and PN at 1 MHz offset across the whole 39% TR, respectively, demonstrating that the proposed gate–drain phase shift technique is wide-band in suppressing the flicker PN. The measured  $1/f^3$  PN corner and PN at 1 MHz offset versus

|                                 |        | This Work         |        | [57] El-Aassar-<br>JSSC'21 | [42] Sharkia-<br>JSSC'18 | [40] Ximenes-<br><i>TMTT</i> 17 | [15] Yin-<br>JSSC'16 |        | [56] Tohidian-<br>MWCL'15 | [55] Abdul-Latif-<br>JSSC'12 |

|---------------------------------|--------|-------------------|--------|----------------------------|--------------------------|---------------------------------|----------------------|--------|---------------------------|------------------------------|

| Туре                            |        | Transformer-Based |        | Dual-Core Tri-Band         | Inductor-Based           | Transformer-Based               | Dual-Mode TI-RVCO    |        | Series LC                 | Cyclic-Coupled Ring          |

| EM Compatibility?               |        | Yes               |        | No                         | No                       | Yes                             | Yes                  |        | No                        | Yes                          |

| <i>f</i> <sub>0</sub> [GHz]     |        | 9 – 13.34 (39%)   |        | 8 – 17 (72%)               | 4.6 – 5.6 (20%)          | 9.4 – 14.8 (45%)                | 1.7 – 3.47 (69%)     |        | 2.66 – 4.97 (61%)         | 1 – 2.56, 3.16 – 12.8 (163%) |

| <i>V</i> <sub>DD</sub> [V]      |        | 0.9               |        | 0.45                       | 0.8                      | 1                               | 0.7 – 1              |        | 0.9 – 1.1                 | 0.7                          |

| Power [mW]                      |        | 5.98              | 5      | 17 – 33                    | 0.53                     | 12 – 20                         | 0.65                 | 2.51   | 8.5 – 16                  | 13 - 200                     |

| 1/f <sup>3</sup> PNCorner [kHz] |        | 70                | 250    | 3000 <sup>&amp;</sup>      | 200&                     | 300&                            | 90                   | 150    | 3000 <sup>&amp;</sup>     | N/A                          |

| Phase<br>Noise<br>[dBc/Hz]      | 1 MHz  | -110.2            | -107.1 | -112.3 119.1               | -108.3                   | -103.5                          | -100.4               | -98.7  | N/A                       | -105.5                       |

|                                 | 10 MHz | -130.1            | -128.5 | -134.7 143.1               | N/A                      | -124                            | -120.5               | -119.3 | -132.2                    | N/A                          |

| FoM*[dB]                        | 1 MHz  | -181.5            | -182.6 | N/A                        | -185.1                   | N/A                             | -166.9               | -161.7 | N/A                       | -160 166                     |

|                                 | 10 MHz | -181.4            | -184   | -180.65191.65              | N/A                      | -175                            | -167                 | -165.6 | -173176.9                 | N/A                          |

| FoM <sub>T</sub> **<br>[dB]     | 1 MHz  | -193.3            | -194.4 | N/A                        | -191.1                   | N/A                             | -183.6               | -178.4 | N/A                       | -184.2 190.2                 |

|                                 | 10 MHz | -193.2            | -195.8 | -197.8208.8                | N/A                      | -188                            | -183.7               | -182.3 | -188.7192.6               | N/A                          |

| FoM <sub>4</sub> ***<br>[dB]    | 1 MHz  | -201.5            | -202.6 | N/A                        | -205.1                   | N/A                             | -192.1               | -186.9 | N/A                       | -168 174                     |

|                                 | 10 MHz | -201.4            | -204   | -184.75 195.75             | N/A                      | -193                            | -192.2               | -190.8 | -195 — -198.9             | N/A                          |

| FoM <sub>TA</sub> ****<br>[dB]  | 1 MHz  | -213.3            | -214.4 | N/A                        | -211.1                   | N/A                             | -208.8               | -203.6 | N/A                       | -192.8 198.8                 |

|                                 | 10 MHz | -213.2            | -215.8 | -201.9212.9                | N/A                      | 206.4                           | -208.9               | -207.5 | -210.7214.6               | N/A                          |

| Supply Pushing [MHz/V]          |        | 80                |        | 0 – 60                     | N/A                      | 80                              | 4070                 |        | N/A                       | 18461                        |

| Core Area[mm <sup>2</sup> ]     |        | 0.01              |        | 0.39                       | 0.01#                    | 0.0144                          | 0.003                |        | 0.0063                    | 0.145                        |

| Technology                      |        | 22-nm FD-SOI      |        | 22-nm FD-SOI               | 65-nm CMOS               | 40-nm CMOS                      | 65-nm CMOS           |        | 40-nm CMOS                | 90-nm CMOS                   |

TABLE I PERFORMANCE SUMMARY AND COMPARISON WITH STATE-OF-THE-ART

<sup>8</sup>Estimated from PN plot \*FoM = PN – 20log( $f_0/\Delta f$ ) + 10log( $P_{DC}/1mW$ ), \*\*FoM<sub>T</sub> = FoM – 20log(TR/10) \*\*\*FoM<sub>A</sub> = FoM + 10log(Area/1mm<sup>2</sup>) \*\*\*FoM<sub>TA</sub> = FoM – 20log(TR/10) + 10log(Area/1mm<sup>2</sup>)

\*\*\*FoM<sub>A</sub> = FoM + 10log(Area/1mm²) \*\*\*\*FoM

Including the synthesizer underneath the inductor

Fig. 13. Measured phase noise at (a) 9 GHz, and (b) 13.34 GHz.

supply voltage are illustrated in Fig. 14(c) and (d), demonstrating its robustness against supply variation from 0.85 V to 0.95 V. The supply frequency pushing effect is measured at two carrier frequencies, as shown in Fig. 14(e) and (f). The proposed oscillator exhibits a great supply pushing around 80 MHz/V, which is two orders-of-magnitude better than that in any ring oscillator [15].

The performance of the proposed oscillator is summarized in Table I and compared with other recently published

Fig. 14. Measured (a)  $1/f^3$  PN corner, and (b) PN at 1 MHz offset over TR. Measured (c)  $1/f^3$  PN corner, and (d) PN at 1 MHz offset over supply voltage at 9.13 GHz carrier. Measured frequency pushing (e) at 9.13 GHz carrier, and (f) 10.43 GHz carrier.

state-of-the-art oscillators featuring a small area. To the best of the authors' knowledge, it achieves a record FoM with normalized TR and area (FoM<sub>TA</sub> [58], [59]) of -214 dB at 1 MHz offset.

## VI. CONCLUSION

In this paper, we establish that in a complementary class-B oscillator, the ill-behaved second-harmonic voltage can be fully suppressed by the complementary operation itself, while the third-harmonic current entering the capacitive path is now the main contributor to the flicker noise upconversion. For the complementary class-F oscillator, it is the negative gate-drain phase shift causing excess of flicker noise  $I_{1/f,rms}$ exposure to the rising parts of  $V_{DS}$ , leading to the flicker phase noise. A robust and wide-band (39% TR) flicker PN suppressing technique was proposed, employing a gate-drain phase shift (adjusted by the capacitance ratio) in a compact (i.e., 0.01 mm<sup>2</sup>), triple-8-shaped transformer-based complementary oscillator. The prototype achieves best FoM with normalized TR and area (FoM<sub>TA</sub>) of -214 dB at 1 MHz offset, combining both benefits of LC-tank-based and inverter-ring-based oscillators.

## APPENDIX: PROOF OF $\lim_{X\to\infty} \Omega(X) = 1$

The upper limit of the numerator in the square root of (8) is expressed as

$$\lim_{X \to \infty} \left( 1 + n^2 X - \sqrt{(1 + n^2 X)^2 - 4n^2 X (1 - k_m^2)} \right)$$

$$= \lim_{X \to \infty} \left( 1 + n^2 X - (1 + n^2 X) \sqrt{1 - \frac{4n^2 X (1 - k_m^2)}{(1 + n^2 X)^2}} \right).$$

(16)

When  $X \to \infty$ ,  $4n^2 X (1 - k_m^2)/(1 + n^2 X)^2 \to 0$ , we have the following Taylor series as:

$$\sqrt{1 - \frac{4n^2 X (1 - k_{\rm m}^2)}{(1 + n^2 X)^2}} = 1 - \frac{1}{2} \frac{4n^2 X (1 - k_{\rm m}^2)}{(1 + n^2 X)^2} + \cdots$$

(17)

Substituting (17) into (16), we get

$$\lim_{X \to \infty} \left( 1 + n^2 X - (1 + n^2 X) \left( 1 - \frac{1}{2} \frac{4n^2 X (1 - k_{\rm m}^2)}{(1 + n^2 X)^2} + \cdots \right) \right)$$

$$= \lim_{X \to \infty} \left( \frac{2n^2 X (1 - k_{\rm m}^2)}{1 + n^2 X} \right) = 2(1 - k_{\rm m}^2). \tag{18}$$

Therefore,

$$\lim_{X \to \infty} \Omega(X) = \sqrt{\frac{2(1 - k_{\rm m}^2)}{2(1 - k_{\rm m}^2)}} = 1.$$

(19)

## ACKNOWLEDGMENT

The authors would like to thank GlobalFoundries University Program for chip fabrication, Erik Staszewski and Paulo Vieira for lab support. Xi Chen would also like to express his appreciation to Dr. Cagri Cetintepe, Enis Kobal, Hieu Minh Nguyen, and Dr. Yue Li for the inspiring technical discussions.

#### References

- E. Ioannidis, C. Theodorou, T. Karatsori, S. Haendler, C. Dimitriadis, and G. Ghibaudo, "Drain-current flicker noise modeling in nMOSFETs from a 14-nm FDSOI technology," *IEEE Trans. Electron Devices*, vol. 62, no. 5, pp. 1574–1579, May 2015.

- [2] P. Kushwaha *et al.*, "Characterization and modeling of flicker noise in FinFETs at advanced technology node," *IEEE Electron Device Lett.*, vol. 40, no. 6, pp. 985–988, Jun. 2019.

- [3] A. Hajimiri and T. H. Lee, "A general theory of phase noise in electrical oscillators," *IEEE J. Solid-State Circuits*, vol. 33, no. 2, pp. 179–194, Feb. 1998.

- [4] A. Hajimiri, S. Limotyrakis, and T. H. Lee, "Jitter and phase noise in ring oscillators," *IEEE J. Solid-State Circuits*, vol. 34, no. 6, pp. 790–804, Jun. 1999.

- [5] T. H. Lee and A. Hajimiri, "Oscillator phase noise: A tutorial," *IEEE J. Solid-State Circuits*, vol. 35, no. 3, pp. 326–336, Mar. 2000.

- [6] A. Bevilacqua and P. Andreani, "An analysis of 1/f noise to phase noise conversion in CMOS harmonic oscillators," *IEEE Trans. Circuits Syst. I, Reg. Papers*, vol. 59, no. 5, pp. 938–945, May 2012.

- [7] A. Bonfanti, F. Pepe, C. Samori, and A. L. Lacaita, "Flicker noise upconversion due to harmonic distortion in Van der Pol CMOS oscillators," *IEEE Trans. Circuits Syst. I, Reg. Papers*, vol. 59, no. 7, pp. 1418–1430, Jul. 2012.

- [8] F. Pepe, A. Bondanti, S. Levantino, C. Samori, and A. L. Lacaita, "Suppression of flicker noise up-conversion in a 65-nm CMOS VCO in the 3.0-to-3.6 GHz band," *IEEE J. Solid-State Circuits*, vol. 48, no. 10, pp. 2375–2389, Oct. 2013.

- [9] M. Shahmohammadi, M. Babaie, and R. B. Staszewski, "A 1/f noise upconversion reduction technique for voltage-biased RF CMOS oscillators," *IEEE J. Solid-State Circuits*, vol. 51, no. 11, pp. 2610–2624, Sep. 2016.

- [10] Y. Hu, T. Siriburanon, and R. B. Staszewski, "A low-flicker-noise 30-GHz class-F<sub>23</sub> oscillator in 28-nm CMOS using implicit resonance and explicit common-mode return path," *IEEE J. Solid-State Circuits*, vol. 53, no. 7, pp. 1977–1987, Jul. 2018.

- [11] Y. Hu, T. Siriburanon, and R. B. Staszewski, "Intuitive understanding of flicker noise reduction via narrowing of conduction angle in voltagebiased oscillators," *IEEE Trans. Circuits Syst. II, Exp. Briefs*, vol. 66, no. 12, pp. 1962–1966, Dec. 2019.

- [12] Y. Hu, T. Siriburanon, and R. B. Staszewski, "Oscillator flicker phase noise: A tutorial," *IEEE Trans. Circuits Syst. II, Exp. Briefs*, vol. 68, no. 2, pp. 538–544, Feb. 2021.

- [13] Y. Hu, "Flicker noise upconversion and reduction mechanisms in RF/millimeter-wave oscillators for 5G communications," Ph.D. dissertation, School Elect. Electron. Eng., Univ. College Dublin, Dublin, Ireland, 2019. [Online]. Available: http://hdl.handle.net/10197/11459

- [14] X. Chen, Y. Hu, T. Siriburanon, J. Du, R. B. Staszewski, and A. Zhu, "A tiny complementary oscillator with 1/f<sup>3</sup> noise reduction using a triple-8-shaped transformer," *IEEE Solid-State Circuits Lett.*, vol. 3, pp. 162–165, 2020.

- [15] J. Yin, P. Mak, F. Maloberti, and R. P. Martins, "A time-interleaved ring-VCO with reduced 1/f<sup>3</sup> phase noise corner, extended tuning range and inherent divided output," *IEEE J. Solid-State Circuits*, vol. 51, no. 12, pp. 2979–2991, Sep. 2016.

- [16] F. Pepe and P. Andreani, "An accurate analysis of phase noise in CMOS ring oscillators," *IEEE Trans. Circuits Syst. II, Exp. Briefs*, vol. 66, no. 8, pp. 1292–1296, Aug. 2019.

- [17] E. Hegazi, H. Sjoland, and A. A. Abidi, "A filtering technique to lower LC oscillator phase noise," *IEEE J. Solid-State Circuits*, vol. 36, no. 12, pp. 1921–1930, Dec. 2001.

- [18] D. Murphy, H. Darabi, and H. Wu, "Implicit common-mode resonance in LC oscillators," *IEEE J. Solid-State Circuits*, vol. 52, no. 3, pp. 812–821, Mar. 2017.

- [19] H. Guo, Y. Chen, P. Mak, and R. P. Martins, "A 0.083-mm<sup>2</sup> 25.2-to-29.5 GHz multi-LC-tank class-F<sub>234</sub> VCO with a 189.6-dBc/Hz FoM," *IEEE Solid-State Circuits Lett.*, vol. 1, no. 4, pp. 86–89, Jun. 2018.

- [20] C. C. Lim, H. Ramiah, J. Yin, P.-I. Mak, and R. P. Martins, "An inverseclass-F CMOS oscillator with intrinsic-high-Q first harmonic and second harmonic resonances," *IEEE J. Solid-State Circuits*, vol. 53, no. 12, pp. 3528–3539, Dec. 2018.

- [21] A. Mazzanti and P. Andreani, "Class-C harmonic CMOS VCOs, with a general result on phase noise," *IEEE J. Solid-State Circuits*, vol. 43, no. 12, pp. 2716–2729, Dec. 2008.

983

- [22] W. Deng, K. Okada, and A. Matsuzawa, "Class-C VCO with amplitude feedback loop for robust start-up and enhanced oscillation swing," *IEEE J. Solid-State Circuits*, vol. 48, no. 2, pp. 429–440, Feb. 2013.

- [23] C. H. Hong, C. Y. Wu, and Y. T. Liao, "Robustness enhancement of a class-C quadrature oscillator using capacitive source degeneration coupling," *IEEE Trans. Circuits Syst. II, Exp. Briefs*, vol. 62, no. 1, pp. 16–20, Jan. 2015.

- [24] F. Wang and H. Wang, "A noise circulating oscillator," *IEEE J. Solid-State Circuits*, vol. 54, no. 3, pp. 696–708, Mar. 2019.

- [25] A. Franceschin, P. Andreani, F. Padovan, M. Bassi, and A. Bevilacqua, "A 19.5-GHz 28-nm class-C CMOS VCO, with a reasonably rigorous result on 1/f noise upconversion caused by short-channel effects," *IEEE J. Solid-State Circuits*, vol. 55, no. 7, pp. 1842–1853, Jul. 2020.

- [26] S. Levantino, M. Zanuso, C. Samori, and A. Lacaita, "Suppression of flicker noise upconversion in a 65 nm CMOS VCO in the 3.0-to-3.6 GHz band," in *IEEE Int. Solid-State Circuits Conf. (ISSCC) Dig. Tech. Papers*, Feb. 2010, pp. 50–51.

- [27] C.-C. Li et al., "A 0.2 V trifilar-coil DCO with DC–DC converter in 16 nm FinFET CMOS with 188 dB FOM, 1.3 kHz resolution, and frequency pushing of 38 MHz/V for energy harvesting applications," in *IEEE Int. Solid-State Circuits Conf. (ISSCC) Dig. Tech. Papers*, Feb. 2017, pp. 332–333.

- [28] W. Wu *et al.*, "A 28-nm 75-fs<sub>rms</sub> analog fractional-*N* sampling PLL with a highly linear DTC incorporating background DTC gain calibration and reference clock duty cycle correction," *IEEE J. Solid-State Circuits*, vol. 54, no. 5, pp. 1254–1265, Mar. 2019.

- [29] Y. Hu et al., "A 21.7-to-26.5 GHz charge-sharing locking quadrature PLL with implicit digital frequency-tracking loop achieving 75 fs jitter and -250 dB FoM," in *IEEE Int. Solid-State Circuits Conf. (ISSCC) Dig. Tech. Papers*, Feb. 2020, pp. 276–278.

- [30] Y. Hu *et al.*, "A charge-sharing locking technique with a general phase noise theory of injection locking," *IEEE J. Solid-State Circuits*, early access, Sep. 6, 2021, doi: 10.1109/JSSC.2021.3106237.

- [31] J. Du, Y. Hu, T. Siriburanon, and R. B. Staszewski, "A 0.3 V, 35% tuning-range, 60 kHz 1/f<sup>3</sup>-corner digitally controlled oscillator with vertically integrated switched capacitor banks achieving FoM<sub>T</sub> of -199 dB in 28-nm CMOS," in *Proc. IEEE Custom Integr. Circuits Conf. (CICC)*, Apr. 2019, pp. 1–4.

- [32] J. Du et al., "A compact 0.2–0.3-V inverse-class-F<sub>23</sub> oscillator for low 1/f<sup>3</sup> noise over wide tuning range," *IEEE J. Solid-State Circuits*, early access, Aug. 2, 2021, doi: 10.1109/JSSC.2021.3098770.

- [33] J. Du, T. Siriburanon, Y. Hu, V. Govindaraj, and R. B. Staszewski, "A 2.02–2.87-GHz –249-dB FoM 1.1-mW digital PLL exploiting reference-sampling phase detector," *IEEE Solid-State Circuits Lett.*, vol. 3, pp. 158–161, 2020.

- [34] J. Du, T. Siriburanon, Y. Hu, V. Govindaraj, and R. B. Staszewski, "A reference-waveform oversampling technique in a fractional-N ADPLL," *IEEE J. Solid-State Circuits*, vol. 56, no. 11, pp. 3445–3457, Nov. 2021.

- [35] J. Du et al., "A 24–31 GHz reference oversampling ADPLL achieving FoM<sub>jitter-N</sub> of –269.3 dB," in Proc. Symp. VLSI Circuits (VLSI-Circuits), 2021, pp. 1–2.

- [36] J. Du et al., "A millimeter-wave ADPLL with reference oversampling and third-harmonic extraction featuring high FoM<sub>jitter-N</sub>," *IEEE Solid-State Circuits Lett.*, vol. 4, pp. 214–217, 2021.

- [37] H. Liu, D. Tang, Z. Sun, W. Deng, H. C. Ngo, and K. Okada, "A submw fractional-N ADPLL with FOM of -246 dB for IoT applications," *IEEE J. Solid-State Circuits*, vol. 53, no. 12, pp. 3540–3552, Dec. 2018.

- [38] C. Li et al., "A 0.034 mm<sup>2</sup>, 725 fs RMS jitter, 1.8%/V frequencypushing, 10.8–19.3 GHz transformer-based fractional-N all-digital PLL in 10 nm FinFET CMOS," in Proc. Symp. VLSI Circuits (VLSI-Circuits), 2016, pp. 1–2.

- [39] C.-C. Li et al., "A compact transformer-based fractional-N ADPLL in 10-nm FinFET CMOS," IEEE Trans. Circuits Syst. I, Reg. Papers, vol. 68, no. 5, pp. 1881–1891, May 2021.

- [40] A. R. Ronchini Ximenes, G. Vlachogiannakis, and R. B. Staszewski, "An ultracompact 9.4–14.8-GHz transformer-based fractional-N alldigital PLL in 40-nm CMOS," *IEEE Trans. Microw. Theory Techn.*, vol. 65, no. 11, pp. 4241–4254, Nov. 2017.

- [41] F.-W. Kuo *et al.*, "A Bluetooth low-energy transceiver with 3.7-mW alldigital transmitter, 2.75-mW high-IF discrete-time receiver, and TX/RX switchable on-chip matching network," *IEEE J. Solid-State Circuits*, vol. 52, no. 4, pp. 1144–1162, Apr. 2017.

- [42] A. Sharkia, S. Mirabbasi, and S. Shekhar, "A type-I sub-sampling PLL with a  $100 \times 100 \ \mu m^2$  footprint and -255-dB FoM," *IEEE J. Solid-State Circuits*, vol. 53, no. 12, pp. 3553–3564, Jun. 2018.

- [43] L. Fanori, T. Mattsson, and P. Andreani, "A 2.4-to-5.3 GHz dual-core CMOS VCO with concentric 8-shaped coils," in *IEEE Int. Solid-State Circuits Conf. (ISSCC) Dig. Tech. Papers*, Feb. 2014, pp. 370–371.

- [44] Y. Hu, T. Siriburanon, and R. B. Staszewski, "A 30-GHz class-F<sub>23</sub> oscillator in 28 nm CMOS using harmonic extraction and achieving 120 kHz 1/f<sup>3</sup> corner," in *Proc. 43rd IEEE Eur. Solid State Circuits Conf. (ESSCIRC)*, Sep. 2017, pp. 87–90.

- [45] F. Pepe and P. Andreani, "A general theory of phase noise in transconductor-based harmonic oscillators," *IEEE Trans. Circuits Syst. I, Reg. Papers*, vol. 64, no. 2, pp. 432–445, Feb. 2017.

- [46] S. Rong and H. C. Luong, "Analysis and design of transformer-based dual-band VCO for software-defined radios," *IEEE Trans. Circuits Syst. I, Reg. Papers*, vol. 59, no. 3, pp. 449–462, Mar. 2012.

- [47] A. Mazzanti and A. Bevilacqua, "Second-order equivalent circuits for the design of doubly-tuned transformer matching networks," *IEEE Trans. Circuits Syst. I, Reg. Papers*, vol. 65, no. 12, pp. 4157–4168, Dec. 2018.

- [48] A. Bevilacqua and A. Mazzanti, "Doubly-tuned transformer networks: A tutorial," *IEEE Trans. Circuits Syst. II, Exp. Briefs*, vol. 68, no. 2, pp. 550–555, Feb. 2021.

- [49] A. Bevilacqua, "Fundamentals of integrated transformers: From principles to applications," *IEEE Solid State Circuits Mag.*, vol. 12, no. 4, pp. 86–100, Nov. 2020.

- [50] A. Bevilacqua, F. P. Pavan, C. Sandner, A. Gerosa, and A. Neviani, "Transformer-based dual-mode voltage-controlled oscillators," *IEEE Trans. Circuits Syst. II, Exp. Briefs*, vol. 54, no. 4, pp. 293–297, Apr. 2007.

- [51] A. Mazzanti and A. Bevilacqua, "On the phase noise performance of transformer-based CMOS differential-pair harmonic oscillators," *IEEE Trans. Circuits Syst. I, Reg. Papers*, vol. 62, no. 9, pp. 2334–2341, Sep. 2015.

- [52] M. Babaie and R. B. Staszewski, "A class-F CMOS oscillator," *IEEE J. Solid-State Circuits*, vol. 48, no. 12, pp. 3120–3133, Dec. 2013.

- [53] Z. Zong, M. Babaie, and R. B. Staszewski, "A 60 GHz frequency generator based on a 20 GHz oscillator and an implicit multiplier," *IEEE J. Solid-State Circuits*, vol. 51, no. 5, pp. 1261–1273, May 2016.

- [54] T. H. Lee, The Design CMOS Radio-Frequency Integrated Circuits. Cambridge, U.K.: Cambridge Univ. Press, 2004.

- [55] M. M. Abdul-Latif and E. Sanchez-Sinencio, "Low phase noise wide tuning range N-push cyclic-coupled ring oscillators," *IEEE J. Solid-State Circuits*, vol. 47, no. 6, pp. 1278–1294, Jun. 2012.

- [56] M. Tohidian, S. A.-R. Ahmadi-Mehr, and R. B. Staszewski, "A tiny quadrature oscillator using low-Q series LC tanks," *IEEE Microw. Wireless Compon. Lett.*, vol. 25, no. 8, pp. 520–522, Aug. 2015.

- [57] O. El-Aassar and G. M. Rebeiz, "Octave-tuning dual-core folded VCO leveraging a triple-mode switch-less tertiary magnetic loop," *IEEE J. Solid-State Circuits*, vol. 56, no. 5, pp. 1475–1486, May 2021.

- [58] A. Jha et al., "Approaches to area efficient high-performance voltagecontrolled oscillators in nanoscale CMOS," *IEEE Trans. Microw. Theory Techn.*, vol. 69, no. 1, pp. 147–156, Jan. 2021.

- [59] S.-A. Yu and P. R. Kinget, "Scaling LC oscillators in nanometer CMOS technologies to a smaller area but with constant performance," *IEEE Trans. Circuits Syst. II, Exp. Briefs*, vol. 56, no. 5, pp. 354–358, May 2009.

Xi Chen (Graduate Student Member, IEEE) received the B.E. degree in information engineering from Southeast University, Nanjing, China, in 2018. He is currently pursuing the Ph.D. degree in microelectronics with University College Dublin (UCD), Dublin, Ireland.

He is also with the RF and Microwave Research Group, UCD. His current research interest is mmwave/mixed-signal CMOS integrated circuits for wireless communications, with an emphasis on frequency/clock generation techniques. He also serves

as a Reviewer for conferences and journals, including the IEEE VLSI Symposium on Technology and Circuits, IEEE International Symposium on Circuits and Systems, IEEE TRANSACTIONS ON CIRCUITS AND SYSTEMS—I: REG-ULAR PAPERS, IEEE TRANSACTIONS ON CIRCUITS AND SYSTEMS—II: EXPRESS BRIEFS, and IEEE ACCESS.

**Yizhe Hu** (Member, IEEE) was born in Chenzhou, Hunan, China, in December 1990. He received the B.Sc. degree (*summa cum laude*) in microelectronics from the Harbin Institute of Technology, Harbin, China, in 2013, and the Ph.D. degree in microelectronics from University College Dublin, Dublin, Ireland, in 2019.

From 2013 to 2014, he was a Post-Graduate Researcher with Fudan University, Shanghai, China, where he was involved in the radio-frequency integrated circuits (RFICs) design. From 2016 to 2017,

he was consulting for the PLL Group of HiSilicon, Huawei Technologies, Shenzhen, China, designing 16-nm digitally controlled oscillators (DCOs) and all-digital phase-locked loops (ADPLLs). From 2019 to 2020, he was a Post-Doctoral Researcher with the Prof. Staszewski's Group, University College Dublin. Since 2018, he has been consulting for the Mixed-Signal Design Department, TSMC, Hsinchu, Taiwan, for a new type of PLL design in 5-nm CMOS. He is currently a Principal Investigator with the Microelectronic Circuits Centre Ireland (MCCI), Dublin. His research interests include RF/mmwave integrated circuits and systems for wireless/wireline communications.

Dr. Hu also serves as a Reviewer for the IEEE JOURNAL OF SOLID-STATE CIRCUITS, IEEE TRANSACTIONS ON CIRCUITS AND SYSTEMS—I: REG-ULAR PAPERS, IEEE TRANSACTIONS ON CIRCUITS AND SYSTEMS—II: EXPRESS BRIEFS, and IEEE TRANSACTIONS ON MICROWAVE THEORY AND TECHNIQUES.

Teerachot Siriburanon (Senior Member, IEEE) received the B.E. degree in telecommunications engineering from the Sirindhorn International Institute of Technology (SIIT), Thammasat University, Pathumthani, Thailand, in 2010, and the M.E. and Ph.D. degrees in physical electronics from the Tokyo Institute of Technology, Tokyo, Japan, in 2012 and 2016, respectively.

In 2016, he joined University College Dublin (UCD), Dublin, Ireland, as a Post-Doctoral Researcher under the European Union's Marie

Skłodowska-Curie Individual Fellowship Program. Since 2019, he has been an Assistant Professor with UCD. His research interests are CMOS wireless transceiver systems and clock/frequency generations for wireless and wireline communications. He was a recipient of the Japanese Government (MEXT) Scholarship, the Young Researcher Best Presentation Award at Thailand–Japan Microwave in 2013, the ASP-DAC Best Design Award in 2014 and 2015, the IEEE SSCS Student Travel Grant Award in 2014, the IEEE SSCS Predoctoral Achievement Award in 2016, and the Tejima Research Award in 2016. He was a Guest Editor of IEEE TRANSACTIONS ON CIRCUITS AND SYSTEMS—I: REGULAR PAPERS from 2019 to 2020. He has been an Associate Editor of IEEE ACCESS since 2020, and serves as a Reviewer for the IEEE JOURNAL OF SOLID-STATE CIRCUITS (JSSC). He also serves on the Technical Program Committee of the IEEE Radio-Frequency Integrated Circuits (RFIC) Symposium.

**Jianglin Du** (Member, IEEE) was born in Changchun, China. He received the B.Sc. degree in microelectronics and the M.Sc. degree in physical electronics from Jilin University, Changchun, in 2013 and 2016, respectively. He defended his Ph.D. thesis at University College Dublin (UCD), Dublin, Ireland, in September 2021.

He is currently working as a Post-Doctoral Researcher with UCD on a project with Equal1 Labs designing cryogenic CMOS high-speed data links for quantum computers. His current research

interests include low-power frequency synthesizer design, low-power receiver design, grating couplers for silicon photonics, and cryogenic circuit design for quantum computer applications.

**Robert Bogdan Staszewski** (Fellow, IEEE) was born in Bialystok, Poland. He received the B.Sc. (*summa cum laude*), M.Sc., and Ph.D. degrees in electrical engineering from The University of Texas at Dallas, Richardson, TX, USA, in 1991, 1992, and 2002, respectively.

From 1991 to 1995, he was with Alcatel Network Systems, Richardson, involved in SONET cross-connect systems for fiber optics communications. He joined Texas Instruments Inc., Dallas, TX, USA, in 1995, where he was an Elected Dis-

tinguished Member of Technical Staff (limited to 2% of technical staff). From 1995 to 1999, he was engaged in advanced CMOS read channel development for hard disk drives. In 1999, he co-started the Digital RF Processor (DRP) Group, Texas Instruments, with a mission to invent new digitally intensive approaches to traditional RF functions for integrated radios in deeply-scaled CMOS technology. He was appointed as a CTO of the DRP Group from 2007 to 2009. In 2009, he joined the Delft University of Technology, Delft, The Netherlands, where he currently holds a guest appointment of Full Professor (Antoni van Leeuwenhoek Hoogleraar). Since 2014, he has been a Full Professor with University College Dublin (UCD), Dublin, Ireland. He is also the Co-Founder of a startup company, Equal1 Labs, with design centers located in Silicon Valley and Dublin, aiming to produce single-chip CMOS quantum computers. He has authored or coauthored six books, 11 book chapters, and 150 journal and 210 conference publications, and holds 210 issued U.S. patents. His research interests include nanoscale CMOS architectures and circuits for frequency synthesizers, transmitters and receivers, and quantum computers. He was a recipient of the 2012 IEEE Circuits and Systems Industrial Pioneer Award. He also serves on the Technical Program Committee of the IEEE VLSI Symposium on Circuits and IEEE European Solid-State Circuits Conference (ESSCIRC).

Anding Zhu (Senior Member, IEEE) received the Ph.D. degree in electronic engineering from University College Dublin (UCD), Dublin, Ireland, in 2004.

He is currently a Professor with the School of Electrical and Electronic Engineering, UCD. He has published more than 170 peer-reviewed journal and conference papers. His research interests include high-frequency nonlinear system modeling and device characterization techniques, high-efficiency power amplifier design, wireless transmitter archi-

tectures, digital signal processing, and nonlinear system identification algorithms.

Prof. Zhu is an Elected Member of MTT-S AdCom, the Chair of the Electronic Information Committee, and the Vice Chair of the Publications Committee. He is also the Chair of the MTT-S Microwave High-Power Techniques Committee. He served as the Secretary for MTT-S AdCom in 2018. He was the General Chair of the 2018 IEEE MTT-S International Microwave Workshop Series on 5G Hardware and System Technologies (IMWS-5G) and a Guest Editor of the IEEE TRANSACTIONS ON MICROWAVE THEORY AND TECHNIQUES on 5G Hardware and System Technologies. He is also an Associate Editor of the *IEEE Microwave Magazine* and a Track Editor of the IEEE TRANSACTIONS ON MICROWAVE THEORY AND TECHNIQUES.