# Optimized MASH-SR Divider Controller for Fractional-*N* Frequency Synthesizers

Dawei Mai<sup>®</sup>, Member, IEEE, and Michael Peter Kennedy<sup>®</sup>, Fellow, IEEE

Abstract—The divider controller in a conventional phase-locked loop fractional-N frequency synthesizer modulates the instantaneous division ratio of the feedback divider. The divider controller is typically a digital circuit that performs quantization of its input signal. Multi-stage noise shaping digital delta-sigma modulators (MASH DDSMs) and successive requantizer (SRs) are two representative divider controller architectures offering lower complexity and better spur performance, respectively. The MASH-SR, as a hybrid of these two classes of divider controllers, can achieve both lower hardware cost than the SR and better performance against spurs than a MASH DDSM. In this work, we present an optimized MASH-SR hybrid and compare the design with its conventional MASH DDSM and SR counterparts.

Index Terms—Multi-stage noise shaping structure-successive requantizer (MASH-SR) divider controllers, MASH-SQ divider controllers, phase locked loops, phase noise, quantization noise, nonlinearity, spurious tones.

#### I. INTRODUCTION

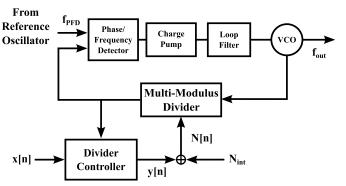

DIVIDER-BASED phase-locked loop (PLL) is commonly used to implement fractional-N frequency synthesis, as shown in Fig. 1. The divider controller output y[n] modulates the instantaneous division ratio of the multi-modulus divider (MMD) around an integer value  $N_{int}$  [1]. When the divider controller input x[n] is constant, the expected value of the output of the divider controller is a desired fraction  $\alpha$ , giving:

$$E(N_{int} + y[n]) = N_{int} + \alpha. \tag{1}$$

The instantaneous integer division ratio deviates from the exact fractional value, but has the correct long-term average value. This modulation of the MMD introduces a phase noise contribution that can be observed in the output spectrum of the synthesizer.

The quantization error of the divider controller is typically required to be at least second-order high-pass shaped; this minimizes the in-band phase noise contribution from division ratio

Manuscript received 24 August 2022; revised 14 November 2022; accepted 5 December 2022. Date of publication 26 December 2022; date of current version 27 February 2023. This work was supported in part by the Science Foundation Ireland and Enterprise Ireland under Grant 20/FFP-A/8371 and Grant TC-2015-0019. This article was recommended by Associate Editor H. Sjoland. (Corresponding author: Dawei Mai.)

The authors are with the School of Electrical and Electronic Engineering, University College Dublin, Belfield, Dublin 4, D04 V1W8 Ireland, and also with the Microelectronic Circuits Centre Ireland (MCCI), Dublin 4, D04 V1W8 Ireland (e-mail: dawei.mai@ucd.ie; peter.kennedy@ucd.ie).

Color versions of one or more figures in this article are available at https://doi.org/10.1109/TCSI.2022.3230634.

Digital Object Identifier 10.1109/TCSI.2022.3230634

modulation [2]. Conventionally, digital delta-sigma modulators (DDSMs) are used to generate the control sequence y[n] for the divider [3]. A multistage noise shaping structure (MASH) is often preferred due to the inherent stability of higher-order DDSMs of this kind. MASH DDSM can be constructed using simple first-order accumulators.

Every physical PLL contains nonlinearities, e.g., the nonlinear transfer characteristic of the phase-frequency detector (PFD) and charge pump (CP) [4], [5], [6]. The phase deviation introduced by a DDSM-based divider controller will be distorted by the nonlinearity, resulting in spectral regrowth. This leads to additional noise and periodic components in the output phase noise [7], [8], [9]. The periodic components are termed spurious tones or spurs. These can cause unwanted noise in a communication system due to the additional upor down-conversion when the synthesizer is used as a local oscillator.

In order to optimize the spur immunity in the presence of nonlinear distortion, successive requantizers (SRs)<sup>1</sup> were introduced as an alternative to DDSM-based divider controllers [10], [11], [12], [13]. SRs introduce a controlled and shaped quantization error that is tailored for the presence of know static nonlinearities based on prescribed state transition matrices. By choosing the state transition matrices appropriately, a SR can achieve different degrees of spur immunity as well as noise levels. Since a SR quantizes its input using identical cascaded stages and relatively complex structures are required to implement the quantization noise generator, it has a significantly higher hardware cost than the relatively simple conventional accumulator-based MASH DDSM divider controllers.

The MASH-SR is a hybrid between these two classes of divider controllers. It has a nested-cascaded structure that consists of a MASH DDSM and cascaded quantization blocks [14], [15], [16], [17]. The input to the divider controller is partitioned and quantized by a MASH and a SR. Consequently, fewer quantization blocks are needed to perform the quantization of the divider controller input. Due to the dominance of the phase noise contribution from the SR stages that quantize the most significant bits (MSBs) and the output of the MASH DDSM, the performance of the MASH-SR, both in terms of spur immunity and noise contribution, is close to that of the full-length cascaded SR [14], [15]. Similar to the SR, a MASH-SR can be optimized by choosing the state transition matrices.

<sup>1</sup>Successive requantizer was originally abbreviated as SQ in [10] and later as SR in [11].

Fig. 1. Block diagram representation of a CP-PLL fractional-N frequency synthesizer.

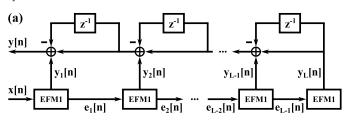

Fig. 2. (a) A MASH DDSM and (b) a constituent error feedback modulator.

In this work, we describe the design of a MASH-SR hybrid that achieves optimal spur performance in the presence of a static nonlinearity and low accumulated quantization noise at low frequencies. Simulation results for the MASH-SR divider controller are compared with DDSMs and SRs.

The architectures of MASH DDSM and SR are reviewed in Sec. II and the MASH-SR hybrid structure is described in Sec. III. The design methodology for the proposed MASH-SR is described in detail in Sec. IV. The simulated performance of the divider controllers is presented in Sec. V, followed by conclusions in Sec. VI.

# II. STATE-OF-ART DIVIDER CONTROLLER ARCHITECTURES: MASH DDSM AND SR

#### A. MASH DDSM

The most commonly used MASH DDSM divider controller is shown schematically in Fig. 2. This MASH DDSM consists of identical first-order error feedback modulator (EFM1) stages, which are inherently stable. The input of the MASH DDSM x[n] is applied to the first EFM1 stage. Each subsequent EFM1 stage accepts the quantization error signal  $e_i[n]$ , i = 1, 2, ..., L from the previous stage as its input. The outputs of the stages are combined in the error cancellation network, which outputs the control signal y[n].

The output of the MASH DDSM comprises the desired scaled input and a high-pass shaped quantization error. For an Lth-order MASH DDSM that consists of L EFM1 stages

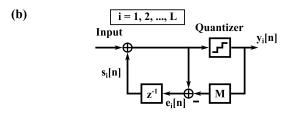

Fig. 3. Schematic of (a) a K-bit SR, (b) a quantization block.

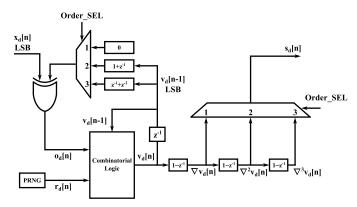

Fig. 4. Block diagram of a  $s_d[n]$  sequence generator which can generate first, second and third-order high-pass shaped  $s_d[n]$ .

and has an N-bit input, the output is

$$Y(z) = \left(\frac{X(z)}{M} - (1 - z^{-1})^{L} E_{L}(z)\right),\tag{2}$$

where Y(z), X(z),  $E_L(z)$  are the z-transform of the output signal, the input signal to the MASH DDSM, and the quantization error signal of the Lth EFM stage, respectively, and  $M=2^N$  is the modulus. Since an EFM1 stage can be implemented using simple digital accumulators, the MASH DDSM has a low cost in terms of hardware and power. However, MASH DDSM-based divider controllers are prone to cause spurious tones in the output of the fractional-N frequency synthesizer when nonlinearities are present [18].

## B. SR

The SR has been designed to quantize its input by introducing a controlled quantization error. A K-bit SR consists of K identical cascaded quantization blocks, as shown in Fig. 3 [10], [13]. The quantization error signal of the dth block  $s_d[n]$  is derived from a sequence generator. The block diagram in Fig. 4 shows a general  $s_d[n]$  sequence generator. This structure provides a quantization error signal  $s_d[n]$  which can be first, second, or third-order high-pass shaped, based on the selection signal  $Order\_SEL$ . The combinatorial logic output  $v_d[n]$  is generated based on the past output  $v_d[n-1]$ , the parity control signal  $o_d[n]$ , and the output of the pseudo-random number generator (PRNG)  $r_d[n]$ . For different d and n values,  $r_d[n]$  can be regarded as independent, identically, and uniformly distributed random variables. The combinatorial logic implements a pair of state transition matrices,  $A_e$  and  $A_o$ , which dictate

the probabilities of its output when  $o_d[n]$  is even and odd, respectively. Denoting the output range of the combinatorial logic as  $[-N_v, N_v]$ , the entries of  $\mathbf{A_e}$  and  $\mathbf{A_o}$  of a are defined as [13]

$$\mathbf{A_e}(i, j) = P(v_d[n] = \mathbf{v}(j) | v_d[n-1] = \mathbf{v}(i), o_d[n] = 0),$$

(3)

$$\mathbf{A_0}(i, j) = P(v_d[n] = \mathbf{v}(j) | v_d[n-1] = \mathbf{v}(i), o_d[n] = 1),$$

(4)

where  $A_x(i, j)$  is the element at *i*th row and *j*th column of matrix  $A_x$ , x = e or x = o, and

$$\mathbf{v} = \begin{pmatrix} -N_v - (N_v - 1) \dots N_v \end{pmatrix}^T. \tag{5}$$

The value of the 1-bit  $o_d[n]$  sequence controls the parity of  $v_d[n]$ : when  $o_d[n] = 0$ , only values of the same parity as  $v_d[n-1]$  are allowed; when  $o_d[n] = 1$ , only values of the opposite parity to  $v_d[n-1]$  are allowed. Thus,

$$o_d[n] = (v_d[n] - v_d[n-1]) \bmod 2.$$

(6)

As the result [13],

$$\mathbf{A_e}(i, j) = 0 \ \forall \ i + j : \text{odd}, \ \mathbf{A_o}(i, j) = 0 \ \forall \ i + j : \text{even}.$$

(7)

In Fig. 4, the outputs of the first-order difference blocks are denoted as  $\nabla v_d[n]$ ,  $\nabla^2 v_d[n]$ , and  $\nabla^3 v_d[n]$ , respectively; they can be expressed as

$$\nabla v_d[n] = v_d[n] - v_d[n-1],\tag{8}$$

$$\nabla^2 v_d[n] = v_d[n] - 2v_d[n-1] + v_d[n-2], \tag{9}$$

$$\nabla^3 v_d[n] = v_d[n] - 3v_d[n-1] + 3v_d[n-2] - v_d[n-3].$$

(10)

For a kth-order  $s_d[n]$  generator, the quantization error  $s_d[n]$  is generated by passing  $v_d[n]$  through k consecutive first-order difference blocks. When the generator is of first order,  $s_d[n] = \nabla v_d[n]$ ; for a second-order generator,  $s_d[n] = \nabla^2 v_d[n]$ ; when the generator is third-order,  $s_d[n] = \nabla^3 v_d[n]$ . In a practical application as a divider controller, we require  $s_d[n]$  to be at least second-order high-pass shaped in order to achieve a low in-band phase noise contribution.

For a first-order  $s_d[n]$  generator, to achieve lossless quantization,

$$(x_d[n] + s_d[n]) \bmod 2 \tag{11}$$

$$= (x_d[n] + v_d[n] - v_d[n-1]) \bmod 2$$

(12)

$$= (x_d[n] + o_d[n]) \bmod 2 = 0. \tag{13}$$

It follows that, in a first-order  $s_d[n]$  generator,

$$o_d[n] = (x_d[n]) \bmod 2. \tag{14}$$

For a second-order  $s_d[n]$  generator,

$$(x_d[n] + s_d[n]) \mod 2$$

$$= (x_d[n] + v_d[n] - 2v_d[n-1] + v_d[n-2]) \mod 2$$

(16)

$$= (x_d[n] + o_d[n] + v_d[n-1] + v_d[n-2]) \mod 2 = 0.$$

(17)

TABLE I

Naming Convention of Signals in  $s_d[n]$  Sequence Generator [13]

|              | $v_d[n]$ | $\nabla v_d[n]$ | $\nabla^2 v_d[n]$ | $\nabla^3 v_d[n]$ |

|--------------|----------|-----------------|-------------------|-------------------|

| First-Order  | $t_d[n]$ | $s_d[n]$        | N/A               | N/A               |

| Second-Order | $u_d[n]$ | $t_d[n]$        | $s_d[n]$          | N/A               |

| Third-Order  | $v_d[n]$ | $u_d[n]$        | $t_d[n]$          | $s_d[n]$          |

Therefore, in a second-order  $s_d[n]$  generator

$$o_d[n] = (x_d[n] + v_d[n-1] + v_d[n-2]) \mod 2.$$

(18)

In a third-order  $s_d[n]$  generator,

$$(x_d[n] + s_d[n]) \mod 2$$

$$= (x_d[n] + v_d[n] - 3v_d[n-1]$$

$$+ 3v_d[n-2] - v_d[n-3]) \mod 2$$

(20)

$$= (x_d[n] + o_d[n] + v_d[n-2] + v_d[n-3]) \mod 2 = 0.$$

(21)

Thus, for a third-order  $s_d[n]$  generator,

$$o_d[n] = (x_d[n] + v_d[n-2] + v_d[n-3]) \mod 2.$$

(22)

Since the generation of  $o_d[n]$  is carried out by a modulo two operation, the LSBs of the signals involved are sufficient to generate  $o_d[n]$ .

In the literature, the naming of the internal signals of a  $s_d[n]$  sequence generator differs, depending on its order [10], [12], [13]. This is because the signal of interest within a quantization block when the SR is used as a divider controller is the one that enters the *last* difference block to generate  $s_d[n]$ . This signal is conventionally denoted  $t_d[n]$ . Table I shows the naming convention for signals within the  $s_d[n]$  sequence generators of different orders in the literature in reference to the general structure in Fig. 4 [13].

With an appropriate choice of the state transition matrices, the accumulated quantization error of the SR can be immune to a certain order of nonlinear distortion [12], [13]. Furthermore, the low-frequency accumulated quantization error, which corresponds to the low-frequency phase noise contribution when the synthesizer is linear, can be optimized [13].

Due to the complex structure that is required in every single quantization block, an SR divider controller has a much higher hardware cost than a MASH DDSM with the same input word length and noise shaping order. For example, the gate count and area of a 16-bit second-order SR are 12.5 and 6.5 times those of a DDSM with the same input word length and order [19].

#### III. MASH-SR ARCHITECTURE

#### A. Nested MASH-SR Hybrid

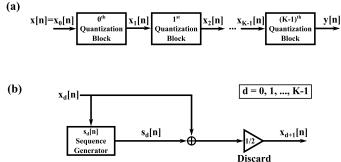

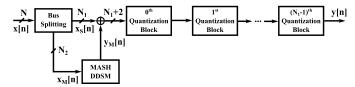

The nested MASH-SR hybrid architecture can be represented by the block diagram in Fig. 5. The N-bit binary input x[n] is partitioned into two parts. The  $N_2$  LSBs of the input

Fig. 5. Schematic of an N-bit MASH-SR with  $N_1$  cascaded quantization blocks and an  $N_2$ -bit MASH DDSM.

comprise the input to the MASH DDSM  $x_M[n]$ . The  $N_1$  most significant bits (MSBs), represented by  $x_S[n]$ , are combined with the MASH DDSM output  $y_M[n]$  and the sum is the input to the chain of  $N_1$  quantization blocks. Denoting the modulus of the SR and the MASH DDSM within the MASH-SR as  $M_1 = 2^{N_1}$  and  $M_2 = 2^{N_2}$ , respectively, the modulus of the divider controller is  $M = M_1 M_2$ . The input can be expressed by a weighted sum of the inputs to the MASH DDSM and the SR as

$$x[n] = x_M[n] + M_2 x_S[n]. (23)$$

The phase deviation caused by the divider controller is related to its accumulated quantization error in the analytical model for a fractional-*N* frequency synthesizer [2]. The accumulated quantization error of a MASH-SR can be expressed as [15]

$$t[n] = \sum_{m=0}^{n} \left( y[m] - \frac{x[m]}{M} \right) = t_M[n] + t_S[n], \quad (24)$$

where

$$t_M[n] = \frac{1}{M_1} \sum_{m=0}^{n} \left( y_M[m] - \frac{x_M[m]}{M_2} \right)$$

(25)

and

$$t_S[n] = \sum_{m=0}^{n} \sum_{d=0}^{N_1 - 1} \frac{1}{2^{N_1 - d}} s_d[m]$$

(26)

are the accumulated quantization errors of the MASH DDSM and the SR, respectively. In a local oscillator (LO) application, x[n] = X is a constant and this is assumed in the following analysis. This gives a fractional division ratio of  $\alpha = X/M$ .

Notice that the contribution of the accumulated quantization error from the MASH DDSM part is scaled by a factor  $1/M_1$ . As a result, the accumulated quantization error from the SR typically dominates the spectral performance [15]. To achieve a t[n] spectrum that is similar to that of a full SR implementing the same pair of state transition matrices, it is required that the order of the MASH DDSM be greater than or equal to that of the SR [15]. As simulations suggest, with a sufficient number of quantization blocks, the MASH-SR can achieve a similar effect in terms of the suppression of fixed spurs induced by the divider controller, when compared with a MASH DDSM divider controller [15].

### B. Advantages of MASH-SR Hybrid

A MASH-SR hybrid has several benefits over a full SR as a divider controller.

- 1) Spur Suppression With Less Hardware: Firstly, compared with the MASH DDSM of a similar order, the hybrid can achieve better spur suppression owing to the dominance of the spectral contribution of the SR [15]. Also, compared with a conventional SR, the MASH DDSM in a MASH-SR replaces the front quantization blocks, leading to a significant reduction in hardware. Considering a 20-bit divider controller, the MASH-SR implementation with a 16-bit MASH 1-1-1 DDSM and a 4-bit SR is estimated to require only about 22% the hardware of a full-length 20-stage SR [15].

- 2) Phase Alignment/Adjustment: In modern synthesizer products, phase alignment/adjustment is a preferred function, especially for beam steering applications. Due to the implementation of the divide-by-two function in the SR, it is difficult to set an initial condition accurately to realize the phase adjustment function. Thanks to the MASH DDSM within the MASH-SR hybrid, phase adjustment can be carried out simply by setting the initial condition of the MASH.

When a MASH 1-1-1 DDSM is used in a MASH-SR hybrid, the accumulated quantization error contribution can be expressed as

$$t_M[n] = \frac{1}{M_1 M_2} \left( e_1[-1] - e_3[n] + 2e_3[n-1] - e_3[n-2] \right),$$

(27)

where  $e_1[-1]$  is the initial condition of the register in the first stage EFM1. By setting the value of  $e_1[-1]$ , the DC offset of the accumulated quantization error of the MASH-SR can be adjusted. To achieve a change of unity in the DC value of t[n], which corresponds to a phase offset value of  $2\pi$  or  $360^{\circ}$ , the initial condition should be able to change between 0 and  $M_1M_2$ . This range is greater than that of  $e_1[n]$ , which is  $[0, M_1)$ , implying that the corresponding bus widths in the MASH DDSM and the SR should be increased in order to perform this function.

3) Lower Latency: In the implementation of an SR quantization block, pipelining is typically applied due to the long propagation delay of the chain. This results in a latency that is proportional to the number of quantization blocks of the SR. Using a MASH-SR can decrease the number of SR stages needed; this reduces the delay caused by the quantization blocks compared to a standard SR structure.

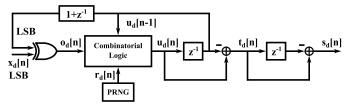

# IV. DESIGN OF AN OPTIMIZED MASH-SR DIVIDER CONTROLLER

In this section, the design of an optimized 20-bit MASH-SR hybrid divider controller with second-order quantization blocks is presented. For convenience, we consider the signal notations of a second-order  $s_d[n]$  signal generator as shown in Fig. 6, i.e., the notations in the second row of Table I. Thus,

$$u_d[n] \equiv v_d[n], \ t_d[n] \equiv \nabla v_d[n], \ s_d[n] \equiv \nabla^2 v_d[n]. \tag{28}$$

To ensure the spectral dominance of the SR stages, a third-order MASH 1-1-1 DDSM is employed in the MASH-SR; this corresponds to the MASH DDSM in Fig. 2 with L=3. The output range of the MASH 1-1-1 is  $y_M[n] \in [-3, 4]$ .

Fig. 6. Block diagram of a second-order  $s_d[n]$  sequence generator.

The quantization error of the SR can be expressed as

$$s_s[n] = \sum_{d=0}^{N_1 - 1} \frac{1}{2^{N_1 - d}} s_d[n].$$

(29)

For  $u_d[n] \in [-N_u, N_u]$ , we have  $s_d[n] \in [-4N_u, 4N_u]$ . The quantization error, which typically dominates the output, has the range  $s_s[n] \in (-4N_u, 4N_u)$ . For a moderate range of output and a sufficient number of pairs of state transition matrices for optimization,  $N_u = 2$  is chosen in this design. This leads to  $5 \times 5$   $\mathbf{A_e}$  and  $\mathbf{A_o}$  matrices.

For the consideration of hardware cost, each quantization block in the SR has a PRNG that generates a 4-bit  $r_d[n]$  sequence, i.e.,  $M_r = 16$  and  $r_d[n] \in [0, 15]$ .

#### A. Input Split of the Nested-Cascade Structure

As introduced in Sec. III, the MASH-SR exploits the spur immunity of the SR's accumulated quantization error contribution. In order to achieve this, a sufficient number of quantization blocks is needed. As discussed in [15], at least four quantization blocks are needed to ensure spectral separation between the SR contribution and the MASH DDSM-related contributions, in both the linear case and in the presence of a strong nonlinearity. Accordingly, the 20-bit MASH-SR is partitioned into a MASH 1-1-1 DDSM with a 16-bit input and four SR quantization blocks, i.e.,  $N_1 = 4$  and  $N_2 = 16$ . In this MASH-SR hybrid, the input to the SR has a range  $y_M[n]+x_S[n] \in [-3,19]$ . This, together with the range of SR quantization error of  $S_S[n] \in (-8,8)$ , gives an output range of

$$y[n] = \frac{y_M[n] + x_S[n]}{2^4} + S_s[n] \in [-7, 8]. \tag{30}$$

By comparison, the output ranges for a 20-bit MASH 1-1 DDSM and a second-order SR are [-1, 2] and [-7, 8], respectively.

#### B. Finding State Transition Matrices

The state transition matrices can be designed to achieve spur immunity of  $t_S[n]$  in the presence of nonlinear distortions. Such pairs of state transition matrices are of interest and the SR can be optimized by selecting state transition matrices among these candidates [13]. The quantization error  $t_S[n]$  can be expressed as a weighted sum of  $t_d[n]$ :

$$t_S[n] = \sum_{d=0}^{N_1 - 1} \frac{1}{2^{N_1 - d}} t_d[n]$$

(31)

with  $t_d[n] = 0$  for  $n \le 0$ . Since the combinatorial logic does not directly generate  $t_d[n]$ , transition matrices from  $u_d[n-1]$  to  $t_d[n]$  are required and they are defined as [13]

$$\mathbf{T}_{\mathbf{e}}(i, j) = P(t_d[n] = \mathbf{t}(j) | u_d[n-1] = \mathbf{u}(i), o_d[n] = 0),$$

(32)

$$\mathbf{T_o}(i, j) = P(t_d[n] = \mathbf{t}(j) | u_d[n-1] = \mathbf{u}(i), o_d[n] = 1),$$

(33)

where

$$\mathbf{u} = \begin{pmatrix} -N_u - (N_u - 1) \dots N_u \end{pmatrix}^T, \tag{34}$$

$$\mathbf{t} = (-2N_u - (2N_u - 1) \dots 2N_u)^T. \tag{35}$$

With (8) and (28), [13]

$$\begin{cases}

\mathbf{A}_{\mathbf{X}}(i, j) \\

\mathbf{A}_{\mathbf{X}}(i, i + j - 2N_u - 1), & \text{if } 2N_u + 2 - i \leq j \text{ and} \\

j \leq 4N_u + 2 - i, & (36) \\

0, & \text{otherwise}

\end{cases}$$

where  $\mathbf{x} = \mathbf{e}$  or  $\mathbf{x} = \mathbf{o}$ . For  $N_u = 2$ ,  $\mathbf{T_e}$  and  $\mathbf{T_o}$  are  $5 \times 9$  matrices.

Consider  $t_S^p[n]$ , which is the  $t_S[n]$  sequence after distortion by a simple pth-order nonlinearity. Two conditions, which are for odd and even order of distortion p respectively, can ensure spurious-free performance for all p less than or equal to an integer  $h_t$  [13].

Firstly, for spur immunity to *odd-order* distortion, i.e., odd integer p, the  $\mathbf{A_e}$  and  $\mathbf{A_0}$  matrices are designed to be centrosymmetric, i.e.,  $\mathbf{A_x}(i,j) = \mathbf{A_x}(2N_u + 2 - i, 2N_u + 2 - j)$  for  $\mathbf{x} = \mathbf{e}$  and  $\mathbf{x} = \mathbf{o}$  [12], [13]. Each row of the matrices should have a sufficient number of non-zero terms. As (7) suggests, for a row vector in  $\mathbf{A_e}$  and  $\mathbf{A_0}$ , every other entry is forced to be zero. For the jth row of  $\mathbf{A_x}(i,j)$ , if  $\mathbf{A_x}(i,j) = 0$  for  $i = 1, 3, \ldots$ , then it is termed an even-entries row; if  $\mathbf{A_x}(i,j) = 0$  for  $i = 2, 4, \ldots$ , then it is called an odd-entries row. For an odd-entries row, there should be at least  $\lfloor 1 + (N_u + 1)/2 \rfloor = 2$  non-zero entries. For an even-entries row, there should be at least  $\lfloor 1 + N_u/2 \rfloor = 2$  non-zero entries.

To ensure that the periodogram of  $t_S^p[n]$  is immune to spurious tones for all *even* positive integer  $p \le h_t$ , it is required that [10], [12], [13]

$$\mathbf{A_e T_e t}^{(p)} = \mathbf{A_e T_o t}^{(p)}$$

$$= \mathbf{A_o T_e t}^{(p)} = \mathbf{A_o T_o t}^{(p)} = c_p \mathbf{1}_{2N_u+1}, \quad (37)$$

where  $c_p$  is a constant,  $\mathbf{1}_{2N_u+1}$  is a vector of ones which has a length  $(2N_u+1)$ , and

$$\mathbf{t}^{(p)} = ((-2N_u)^p \ (-2N_u + 1)^p \ \dots \ (2N_u)^p)^T \ . \tag{38}$$

With the requirement for odd-order  $t_S[n]$  spur immunity and (7), the  $\mathbf{A_e}$  and  $\mathbf{A_o}$  are populated with variables as (39), shown at the bottom of the next page.

For different  $h_t$  values, the number of solutions is different. As proven in [12], the highest order of distortion to which  $t_S[n]$  can be immune is  $h_t = (4N_u - 3) = 5$ . In this case, we require (37) to hold for p = 2 and p = 4, given the spur immunity in odd-p cases due to the structures of the  $A_e$

and  $A_0$ . Two valid sets of state transition matrices are found using an algebraic equation solver,<sup>2</sup> namely,

$$\mathbf{A_e} = \begin{pmatrix} 1/4 & 0 & 3/4 & 0 & 0 \\ 0 & 5/8 & 0 & 3/8 & 0 \\ 1/8 & 0 & 3/4 & 0 & 1/8 \\ 0 & 3/8 & 0 & 5/8 & 0 \\ 0 & 0 & 3/4 & 0 & 1/4 \end{pmatrix},$$

$$\mathbf{A_o} = \begin{pmatrix} 0 & 3/4 & 0 & 1/4 & 0 \\ 3/16 & 0 & 3/4 & 0 & 1/16 \\ 0 & 1/2 & 0 & 1/2 & 0 \\ 1/16 & 0 & 3/4 & 0 & 3/16 \\ 0 & 3/4 & 0 & 1/4 & 0 \end{pmatrix}$$

$$(40)$$

and

$$\mathbf{A_e} = \begin{pmatrix} 3/4 & 0 & 1/4 & 0 & 0 \\ 0 & 5/8 & 0 & 3/8 & 0 \\ 3/8 & 0 & 1/4 & 0 & 3/8 \\ 0 & 3/8 & 0 & 5/8 & 0 \\ 0 & 0 & 1/4 & 0 & 3/4 \end{pmatrix},$$

$$\mathbf{A_o} = \begin{pmatrix} 0 & 11/12 & 0 & 1/12 & 0 \\ 11/16 & 0 & 1/4 & 0 & 1/16 \\ 0 & 1/2 & 0 & 1/2 & 0 \\ 1/16 & 0 & 1/4 & 0 & 11/16 \\ 0 & 1/12 & 0 & 11/12 & 0 \end{pmatrix}. (41)$$

The pair of matrices in (40) was presented in [10], [12], and [13]. Notice that (41) contains probabilities with a denominator of 12. When quantizing to 4 bits based on the requirement imposed by  $r_d[n]$ , errors will be introduced. The limited number of pairs of  $A_e$  and  $A_o$  when  $h_t = 5$  does not permit efficient optimization.

In order to increase the number of candidate matrices for selection, we relax the requirement to  $h_t = 3$  and only consider the set of equations with p = 2. By elimination and substitution,  $A_e$  and  $A_o$  can be represented by just two variables  $x_1$  and  $x_2$ , as shown in (42) and (43), shown at the bottom of the page. Note that it still has to be ensured that each row of  $A_e$  and  $A_o$  contains at least two non-zero values. For (42) and (43), one can simply let  $A_e(i, j) \in [0, 1)$  and  $\mathbf{A_0}(i, j) \in [0, 1)$  to satisfy this requirement.

Notice that  $x_1$  and  $x_2$  appear alone as entries in (42) and (43), respectively. To find valid state transition matrices, a brute-force search with a step size of  $1/M_r = 1/16$  in  $x_1$ and  $x_2$  is performed. A thorough search can be conducted by applying the ranges  $x_1 \in [0, 15/16]$  and  $x_2 \in [0, 15/16]$ . In total, 56 valid pairs of matrices are found. It should be noted that entries may not be integer multiples of 1/16 in these matrices, e.g.,  $A_e(1, 1)$  in (42). Further rounding may be needed in order to implement some of the matrices.

# C. Calculation of $t_S[n]$ Distribution

With a given pair of state transition matrices, the distribution of  $t_d[n]$  can be estimated. Knowing the distribution of  $t_d[n]$ , the distribution of  $t_S[n]$  can then be estimated.

Since  $t_d[n]$  is the first-order difference of the  $u_d[n]$  sequence in a second-order  $s_d[n]$  generator, we consider the distribution of  $u_d[n]$  first. The current state  $u_d[n]$  is a function of the parity sequence  $\{o_d[m], m = 0, 1, ..., n\}$ , the pseudo-random sequence  $\{r_d[m], m = 0, 1, ..., n\}$ , and its initial condition  $u_d[-1]$ , which is assumed zero. As introduced in Sec. II,  $r_d[n]$  and  $r_{(d+\Delta)}[n]$  are independent sequences with  $\Delta \neq 0$ . Thus,  $u_d[n]$  and  $u_{(d+\Delta)}[n]$  are conditioned on independent

$$\mathbf{A_e} = \begin{pmatrix} x_{e1} & 0 & x_{e2} & 0 & 1 - x_{e1} - x_{e2} \\ 0 & x_{e3} & 0 & 1 - x_{e3} & 0 \\ x_{e4} & 0 & 1 - 2x_{e4} & 0 & x_{e4} \\ 0 & 1 - x_{e3} & 0 & x_{e3} & 0 \\ 1 - x_{e1} - x_{e2} & 0 & x_{e2} & 0 & x_{e1} \end{pmatrix},$$

$$\mathbf{A_0} = \begin{pmatrix} 0 & x_{o1} & 0 & 1 - x_{o1} & 0 \\ x_{o2} & 0 & x_{o3} & 0 & 1 - x_{o2} - x_{o3} \\ 0 & 1/2 & 0 & 1/2 & 0 \\ 1 - x_{o2} - x_{o3} & 0 & x_{o3} & 0 & x_{o2} \\ 0 & 1 - x_{o1} & 0 & x_{o1} & 0 \end{pmatrix}.$$

$$(39)$$

$$\mathbf{A_{e}} = \begin{pmatrix} -\frac{8x_{1}^{2} - 16x_{1} + 8x_{2} + 7}{16(x_{1} - 1)} & 0 & x_{1} & 0 & \frac{-8x_{1}^{2} + 16x_{1} + 8x_{2} - 9}{16(x_{1} - 1)} \\ 0 & 2x_{1} + 2x_{2} - \frac{5}{4} & 0 & \frac{9}{4} - 2x_{2} - 2x_{1} & 0 \\ \frac{1}{2} - \frac{x_{1}}{2} & 0 & x_{1} & 0 & \frac{1}{2} - \frac{x_{1}}{2} \\ 0 & \frac{9}{4} - 2x_{2} - 2x_{1} & 0 & 2x_{1} + 2x_{2} - \frac{5}{4} & 0 \\ \frac{-8x_{1}^{2} + 16x_{1} + 8x_{2} - 9}{16(x_{1} - 1)} & 0 & x_{1} & 0 & -\frac{8x_{1}^{2} - 16x_{1} + 8x_{2} + 7}{16(x_{1} - 1)} \end{pmatrix}, \tag{42}$$

$$\mathbf{A_{0}} = \begin{pmatrix} 0 & -\frac{x_{2}}{x_{1} - 1} & 0 & \frac{x_{1} + x_{2} - 1}{x_{1} - 1} & 0 \\ x_{2} & 0 & x_{1} & 0 & 1 - x_{2} - x_{1} \\ 0 & \frac{1}{2} & 0 & \frac{1}{2} & 0 \\ 1 - x_{2} - x_{1} & 0 & x_{1} & 0 & x_{2} \\ 0 & \frac{x_{1} + x_{2} - 1}{x_{1} - 1} & 0 & -\frac{x_{2}}{x_{1} - 1} & 0 \end{pmatrix}. \tag{43}$$

$$\mathbf{A_0} = \begin{pmatrix} 0 & -\frac{x_2}{x_1 - 1} & 0 & \frac{x_1 + x_2 - 1}{x_1 - 1} & 0\\ x_2 & 0 & x_1 & 0 & 1 - x_2 - x_1\\ 0 & \frac{1}{2} & 0 & \frac{1}{2} & 0\\ 1 - x_2 - x_1 & 0 & x_1 & 0 & x_2\\ 0 & \frac{x_1 + x_2 - 1}{x_1 - 1} & 0 & -\frac{x_2}{x_2 - 1} & 0 \end{pmatrix}. \tag{43}$$

<sup>&</sup>lt;sup>2</sup>For this work, the MATLAB solve function was used for solving and simplifying the sets of equations.

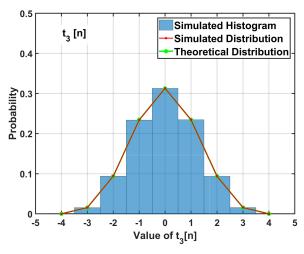

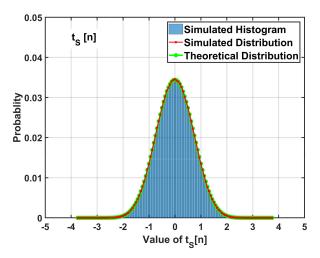

Fig. 7. Estimated and simulated distribution of  $t_3[n]$  and  $t_S[n]$  of the SR within a 20-bit MASH-SR with a 16-bit MASH 1-1-1 and a 4-bit SR. State transition matrices in (40) are used.

sequences  $\{r_d[m], m = 0, 1, ..., n\}$  and  $\{r_{(d+\Delta)}[m], m = 0, 1, ..., n\}$ . Since the value of  $o_d[n]$  is partly determined by the quantization block input  $x_d[n], u_d[n]$  and  $u_{(d+\Delta)}[n]$  are not strictly independent; this imposes constraints on the analysis of the  $t_S[n]$  distribution.

For a full SR structure, due to the constant input in the LO application, the  $u_d[n]$  distributions are affected by the input x[n] = X or the output of the preceding stage. However, in a MASH-SR, the input to the SR quantization blocks comprises two parts, namely the MASH DDSM output  $y_M[n]$ and the MSBs of the input. The output  $y_M[n]$  contains a high-pass shaped quantization error; as the result, the input of the SR is not constant. This gives alternating parities for all  $x_d[n]$ . Therefore, in the following analysis, it is assumed that the  $o_d[n]$  sequence is a balanced 1-bit sequence with equal probabilities of zeros and ones with  $\{o_d[n], n =$  $0, 1, \ldots$  and  $\{o_{(d+\Delta)}[n], n = 0, 1, \ldots\}$  being statistically independent when  $\Delta \neq 0$ . Hence,  $\{u_d[n], n = 0, 1, ...\}$  and its difference sequence  $\{t_d[n], n = 0, 1, ...\}$  are independent of  $\{u_{(d+\Delta)}[n], n = 0, 1, ...\}$  and  $\{t_{(d+\Delta)}[n], n = 0, 1, ...\}$ when  $\Delta \neq 0$  under this assumption, respectively.

The distribution of  $u_d[n]$  is first estimated. Since the  $o_d[n]$  sequence is assumed to have equal probabilities of zeros and ones,  $P(o_d[n] = 0) = P(o_d[n] = 1) = 0.5$ . The overall state transition matrix **A** can be defined as [13]

$$\mathbf{A}(i, j) = P(u_d[n] = \mathbf{u}(j) \mid u_d[n-1] = \mathbf{u}(i))$$

$$= P(u_d[n] = \mathbf{u}(j) \mid u_d[n-1] = \mathbf{u}(i), o_d[n] = 0)$$

$$\times P(o_d[n] = 0) +$$

$$P(u_d[n] = \mathbf{u}(j) \mid u_d[n-1] = \mathbf{u}(i), o_d[n] = 1)P(o_d[n] = 1)$$

$$= \frac{\mathbf{A_e}(i, j) + \mathbf{A_o}(i, j)}{2}.$$

(44)

This definition implies that **A** is stochastic. The vector of stationary probabilities of the discrete-valued Markov random sequence  $u_d[n]$ , denoted  $\mathbf{p_u}$ , can be found by solving

$$\mathbf{p_u}\mathbf{A} = \mathbf{p_u}.\tag{45}$$

Here  $\mathbf{p_u}(i) = P(u_d[n-1] = \mathbf{u}(i)) = P(u_d[n] = \mathbf{u}(i))$ . Similarly, the overall state transition matrix from  $u_d[n-1]$  to

$t_d[n]$  can be defined as

$$\mathbf{T}(i,j) = P(t_d[n] = \mathbf{t}(j) \mid u_d[n-1] = \mathbf{u}(i))$$

$$= \frac{\mathbf{T_e}(i,j) + \mathbf{T_o}(i,j)}{2}.$$

(46)

The probability distribution for  $t_d[n]$ , which is denoted  $\mathbf{p_t}$ , can be evaluated by solving

$$\mathbf{p_t} = \mathbf{p_u} \mathbf{T}.\tag{47}$$

By definition,  $\mathbf{p_t}(i) = P(t_d[n] = \mathbf{t}(i))$ .

Under the assumption that  $t_d[n]$  of different stages are independent, the distribution of the output accumulated quantization error of the SR  $t_S[n]$  can be computed by the method described in Appendix A, based on (31). The probability vector  $\mathbf{P_{tout}}$  for  $t_S[n]$  can be expressed as

$$\mathbf{P_{tout}}(i) = P\left(t_S[n] = -2N_u \left(\frac{M_1 - 1}{M_1}\right) + \frac{i - 1}{M_1}\right), i \in [1, 4(M_1 - 1)N_u + 1]. (48)$$

Fig. 7 shows the estimated probability distributions for  $t_d[n]$  (d=3) and  $t_S[n]$  and the simulation results of the 4-bit SR within the 20-bit MASH-SR. The estimated distributions match well with the simulation results.

#### D. Spectra of $t_d[n]$ and $t_S[n]$

The spectral contribution of  $t_S[n]$  dominates the accumulated quantization error of the divider controller. As (31) suggests, the  $t_d[n]$  signals from quantization blocks, which are assumed to be independent, contribute to the  $t_S[n]$  spectrum. Therefore, the spectrum of  $t_d[n]$  is estimated first.

The power spectral density of the  $u_d[n]$  is computed as

$$S_{u_d}(F) = \lim_{L \to \infty} \mathbb{E}\left(\sum_{m=-L+1}^{L-1} R_{uu,L}[m]e^{-j2\pi Fm}\right)$$

(49)

where F = k/L, k = 0, 1, ..., L - 1 and

$$R_{uu,L}[m] = \frac{1}{L} \sum_{n=0}^{L-1} u_d[n] u_d[n+m]$$

(50)

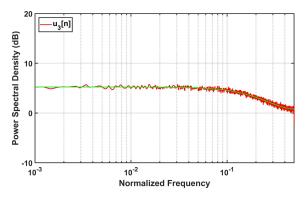

Fig. 8. Estimated (green) and simulated spectra of  $u_3[n]$ ,  $t_3[n]$ , and  $t_S[n]$  of the SR within a 20-bit MASH-SR with a 16-bit MASH 1-1-1 and a 4-bit SR. State transition matrices in (40) are used.

is the autocorrelation of  $u_d[n]$  and L is the length of  $u_d[n]$  sequence. Thus,  $u_d[n] = 0$  when n < 0 and n > L - 1. Furthermore, the limit for  $\mathbb{E}(R_{uu,L}[k])$  as  $L \to \infty$  is [13]

$$R_{uu}[m] = \lim_{L \to \infty} \mathbf{E} \left( R_{uu,L}[m] \right) = \mathbf{E}(u_d[n]u_d[n+m])$$

$$= \sum_{l=1}^{2N_u+1} \left( \mathbf{A}^{|m|} \mathbf{u} \right) (l) \cdot \mathbf{u}(l) \cdot \mathbf{p_u}(l). \tag{51}$$

This gives

$$S_{u_d}(F) = \lim_{L \to \infty} \sum_{m = -L+1}^{L-1} \left( \lim_{L \to \infty} \mathbf{E}(R_{uu,L}[m]) \right) e^{-j2\pi Fm}$$

$$= \lim_{L \to \infty} \sum_{m = -L+1}^{L-1} R_{uu}[m] e^{-j2\pi Fm}$$

(52)

Practically, a finite sequence length L is used to estimate  $S_{u_d}(k/L)$ :

$$S_{u_d,L}\left(\frac{k}{L}\right) = \sum_{m=-L+1}^{L-1} R_{uu}[m]e^{\frac{-j2\pi km}{L}}$$

$$= \sum_{m=-L+1}^{L-1} \left(\sum_{l=1}^{2N_u+1} \left(\mathbf{A}^{|m|}\mathbf{u}\right)(l) \cdot \mathbf{u}(l) \cdot \mathbf{p_u}(l)\right)$$

$$\times e^{\frac{-j2\pi km}{L}}$$

(53)

Since  $u_d[n]$  is a Markov process that has a stationary distribution, the autocorrelation of  $u_d[n]$  typically decreases in amplitude with the absolute value of the lag m. Therefore,  $R_{uu}[m]$  can be approximated by an impulse at m=0 and the spectrum  $S_{u_d}(F)$  can be approximated by white noise.

The spectrum of  $t_d[n]$  can then be estimated by

$$S_{t_d,L}\left(\frac{k}{L}\right) = \left|1 - e^{\frac{-j2\pi k}{L}}\right|^2 S_{u_d,L}\left(\frac{k}{L}\right). \tag{54}$$

Under the assumption that  $t_d[n]$  sequences from different quantization blocks are independent, the cross-correlation between the  $t_d[n]$  and  $t_{(d+\Delta)}[n]$  is zero for  $\Delta \neq 0$ . The power spectral density for  $t_S[n]$  can be estimated by

$$S_{t_S,L}\left(\frac{k}{L}\right) = \left(\sum_{d=0}^{N_1-1} \left(\frac{1}{2^{(N_1-d)}}\right)^2\right) S_{t_d,L}\left(\frac{k}{L}\right).$$

(55)

In this particular design with  $N_1 = 4$ , the spectral contribution from  $t_S[n]$  dominates the spectrum of t[n],

$$S_{t,L}\left(\frac{k}{L}\right) \approx S_{t_S,L}\left(\frac{k}{L}\right).$$

(56)

Since a MASH 1-1-1 is employed in this MASH-SR design, first-order shaped LSB dither can be applied to it, which will lead to a flat spectral contribution of low amplitude at low frequencies in the t[n] spectrum.

Examples of simulated and estimated spectra of  $u_d[n]$ ,  $t_d[n]$ , and  $t_S[n]$  of the 4-bit SR within the 20-bit MASH-SR are shown in Fig. 8. The estimates (53), (54), and (55) can provide good predictions for the simulated spectra.

#### E. Optimization of the SR Stages

In the linear case, the contribution of the SR to t[n] is dominant, as (56) suggests. When a nonlinearity is present, the  $t_S[n]$  related spectrum is expected to have a significant impact on the overall spectral performance. Consider a memoryless nonlinearity that can be approximated by a polynomial. The distorted t[n] of the MASH-SR can be written as

$$t^{NL}[n] = \mathcal{NL}(t[n]) = \sum_{k=0}^{p} C_k(t[n])^k$$

$$= \mathcal{NL}(t_S[n]) + \mathcal{NL}(t_M[n]) + r_c[n], \quad (57)$$

where  $r_c[n]$  contains the cross terms. In the MASH-SR with at least four SR stages, the amplitude of  $t_S[n]$  is significantly larger than that of  $t_M[n]$ . The autocorrelation of  $\mathcal{NL}(t_S[n])$  is therefore a significant contribution to the autocorrelation of  $t^{NL}[n]$ , yielding a major spectral component associated with it. Optimizing the performance of  $t_S[n]$  can hence improve the overall spectral performance of the MASH-SR hybrid.

With the valid state transition matrices found under the constraint  $h_t = 3$ , the distributions as well as the spectra of  $t_d[n]$  and  $t_S[n]$  can be estimated when each pair of state transition matrices is applied. The SR stages are optimized by selecting the state transition matrices based on consideration of the performance in terms of spurs and noise.

The first aspect of the optimization is the distribution of  $t_d[n]$  and  $t_S[n]$ . The range of  $t_S[n]$  affects the potential immunity of the SR contribution to nonlinear distortion. The maximum order of nonlinear distortion to which  $t_S[n]$  can be

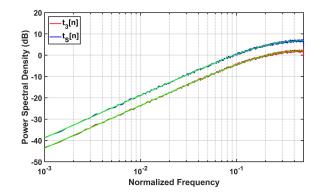

Fig. 9. Estimated criteria for candidate state transition matrices: (a)  $Var(t_d[n])$ , (b)  $Var(t_d[n])$ , (c)  $Var(t_d[n])$ , (d)  $Var(t_d[n])$ , calculated from (58), (e)  $Var(t_d[n])$ , and (f)  $Var(t_d[n])$  given in (60).

immune is related to its range [20]. However,  $t_S[n]$  with the same range but different distributions can behave differently in the presence of nonlinear distortion. With a given length of the  $t_S[n]$  sequence, the  $t_S[n]$  with a distribution that has probabilities concentrated around zero will appear to have a lower range. This leads to a direct degradation of the performance in terms of spurs. Therefore, instead of selecting the state transition matrices for the range of  $t_S[n]$ , the variance of  $t_S[n]$  is chosen as one of the criteria for optimization. Since  $t_d[n]$  of different quantization blocks are assumed independent, (31) indicates that the ratio between the variances of  $t_d[n]$  and  $t_S[n]$  is a constant. This means that the variance of  $t_d[n]$  can be used as a criterion without computing that of  $t_S[n]$ . Specifically, matrices giving larger variances of  $t_d[n]$  and  $t_S[n]$  are preferred.

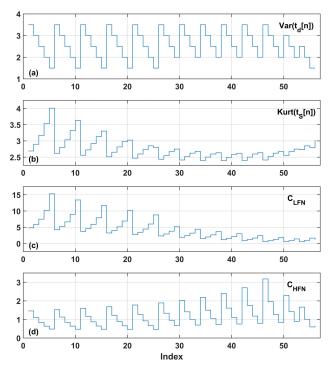

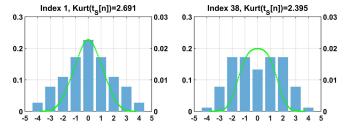

The estimated variances of  $t_d[n]$  for the valid state transition matrices, which are indexed based on the order in which they are found in the brute-force search, are shown in Fig. 9(a). Note that different pairs of matrices can lead to identical variances of  $t_d[n]$  and  $t_S[n]$ . To have an identical variance, the distribution could have high probabilities for  $t_S[n]$  values with small absolute values; alternatively, the probabilities for all values are more evenly distributed, which results in higher probabilities for  $t_S[n]$  values with large absolute values. Fig. 10 shows the  $t_d[n]$  and  $t_S[n]$  distributions given by the pairs of matrices indexed 1 and 38, which both lead to  $Var(t_d[n]) = 3.5$ ; they are examples of the two kinds. Therefore, the kurtosis of the  $t_S[n]$  distribution is used as another criterion for the distribution. It is defined

$$\operatorname{Kurt}(t_{S}[n]) = \frac{\mathbf{E}\left(\left(t_{S}[n] - \mathbf{E}(t_{S}[n])\right)^{4}\right)}{(\operatorname{Var}(t_{S}[n]))^{2}}.$$

(58)

Fig. 10. Estimates of  $t_d[n]$  and  $t_S[n]$  distributions of the pairs state transition matrices with index 1 and 38 that give  $Var(t_d[n]) = 3.5$ .

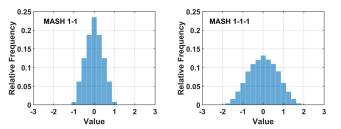

Fig. 11. Simulated histograms of t[n] of a MASH 1-1 and a MASH 1-1-1.

A  $t_S[n]$  distribution with a low kurtosis value is less tailed and therefore tends to have more evenly distributed probabilities for  $t_S[n]$  values. Such a distribution is hence preferred.

Typically, a lower-order MASH DDSM has a narrow range and the distribution of the accumulated quantization error with high probabilities for values with small absolute values. In contrast, a higher-order MASH DDSM has a wider distribution of the accumulated quantization error with higher probabilities for values with larger absolute values. Example t[n] histograms of a MASH 1-1 and a MASH 1-1-1 DDSM are shown in Fig. 11. As the order of the MASH DDSM increases, the spur performance is improved. By selecting matrices based on the values of  $Var(t_S[n])$  and  $Var(t_S[n])$ , the  $Var(t_S[n])$  can emulate the higher-order MASH DDSM in terms of its distribution.

Furthermore, the spectral traits of  $t_S[n]$  will provide other criteria for optimization. The  $t_S[n]$  spectral amplitude at low-frequencies is a concern since it determines the envelope of  $t_S[n]$ , given the white noise assumption for  $S_{u_d}(F)$ . Equation (54) suggests that, at a given frequency, the estimated amplitude of the spectrum of the  $S_{t_d,L}(F)$  can be related to  $S_{u_d,L}(F)$  by a fixed factor. The low-frequency noise of  $S_{t_d,L}(F)$  can therefore be characterized by the criterion [13]

$$C_{LFN} = S_{u_d, L}(0).$$

(59)

Also, the high-frequency noise of  $t_S[n]$ , which can be related to the noise floor due to folding [6], is considered as another criterion for the SR and it is defined as the amplitude of the spectrum around 0.5 normalized frequency, i.e.,

$$C_{HFN} = S_{u_d,L}\left(\frac{1}{2}\right). \tag{60}$$

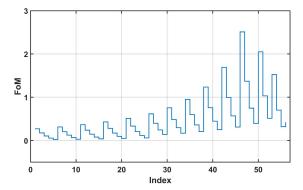

In this work, a  $t_S[n]$  distribution which leads to better potential performance regarding spurs is preferred. According to the analysis presented,  $t_S[n]$  distribution with a large variance and low kurtosis is desirable. Among the pairs of matrices that lead to similar  $t_S[n]$  distribution, lower  $t_S[n]$  power spectral density

Fig. 12. Figures of merit calculated using (61) for the candidate matrices.

at low frequencies is favored since it allows lower phase noise contribution from the divider controller around the synthesizer bandwidth. Therefore, the figure of merit used to select the valid candidate matrices is defined as

$$FoM = \frac{\text{Var}(t_d[n])}{\text{Kurt}(t_S[n])C_{LFN}}.$$

(61)

Values of the figure of merit for all candidate matrices are shown in Fig. 12. The matrices indexed 46, which are

$$\mathbf{A_e} = \begin{pmatrix} 5/48 & 0 & 5/8 & 0 & 13/48 \\ 0 & 1/8 & 0 & 7/8 & 0 \\ 3/16 & 0 & 5/8 & 0 & 3/16 \\ 0 & 7/8 & 0 & 1/8 & 0 \\ 13/48 & 0 & 5/8 & 0 & 5/48 \end{pmatrix},$$

$$\mathbf{A_o} = \begin{pmatrix} 0 & 1/6 & 0 & 5/6 & 0 \\ 1/16 & 0 & 5/8 & 0 & 5/16 \\ 0 & 1/2 & 0 & 1/2 & 0 \\ 5/16 & 0 & 5/8 & 0 & 1/16 \\ 0 & 5/6 & 0 & 1/6 & 0 \end{pmatrix}, \quad (62)$$

yield the highest value of this figure of merit. In order to implement the probabilities with a 4-bit pseudo-random number, the matrices are rounded as

$$\mathbf{A_e} = \begin{pmatrix} 1/8 & 0 & 5/8 & 0 & 1/4 \\ 0 & 1/8 & 0 & 7/8 & 0 \\ 3/16 & 0 & 5/8 & 0 & 3/16 \\ 0 & 7/8 & 0 & 1/8 & 0 \\ 1/4 & 0 & 5/8 & 0 & 1/8 \end{pmatrix},$$

$$\mathbf{A_o} = \begin{pmatrix} 0 & 3/16 & 0 & 13/16 & 0 \\ 1/16 & 0 & 5/8 & 0 & 5/16 \\ 0 & 1/2 & 0 & 1/2 & 0 \\ 5/16 & 0 & 5/8 & 0 & 1/16 \\ 0 & 5/6 & 0 & 1/6 & 0 \end{pmatrix}, (63)$$

Notice that this pair of matrices leads to the highest high-frequency noise, as shown in Fig. 9(d). The power spectral density of  $t_S[n]$  around the Nyquist frequency can be related to the noise floor caused by folding in the presence of nonlinearity [6]. Therefore, the selected state transition matrices may incur high nonlinearity-induced in-band noise.

#### V. COMPARISON OF SIMULATED PERFORMANCE

In this section, the simulated performances of the MASH-SR with the optimized state transition matrices and

Fig. 13. The t[n] spectra of a MASH 1-1 DDSM, a MASH 1-1-1 DDSM, and MASH-SR with state transition matrices with index 5 and index 46.

its counterparts are presented. For the purpose of comparison, the matrices giving the minimum figure of merit, which are indexed 5, namely

$$\mathbf{A_e} = \begin{pmatrix} 29/32 & 0 & 0 & 0 & 3/32 \\ 0 & 5/8 & 0 & 3/8 & 0 \\ 1/2 & 0 & 0 & 0 & 1/2 \\ 0 & 3/8 & 0 & 5/8 & 0 \\ 3/32 & 0 & 0 & 0 & 29/32 \end{pmatrix},$$

$$\mathbf{A_o} = \begin{pmatrix} 0 & 15/16 & 0 & 1/16 & 0 \\ 15/16 & 0 & 0 & 0 & 1/16 \\ 0 & 1/2 & 0 & 1/2 & 0 \\ 1/16 & 0 & 0 & 0 & 15/16 \\ 0 & 1/16 & 0 & 15/16 & 0 \end{pmatrix}, (64)$$

are also considered. To permit the use of a 4-bit  $r_d[n]$ , the  $\mathbf{A_e}$  matrix is rounded to

$$\mathbf{A_e} = \begin{pmatrix} 15/16 & 0 & 0 & 0 & 1/16 \\ 0 & 5/8 & 0 & 3/8 & 0 \\ 1/2 & 0 & 0 & 0 & 1/2 \\ 0 & 3/8 & 0 & 5/8 & 0 \\ 1/16 & 0 & 0 & 0 & 15/16 \end{pmatrix}. \tag{65}$$

A 20-bit second-order SR in [13] implementing state transition matrices quantized for a 10-bit  $r_d[n]$

$$\mathbf{A_e} = \begin{pmatrix} 0 & 0 & \frac{333}{512} & 0 & \frac{179}{512} \\ 0 & \frac{7}{128} & 0 & \frac{121}{128} & 0 \\ \frac{179}{1024} & 0 & \frac{333}{512} & 0 & \frac{179}{1024} \\ 0 & \frac{121}{128} & 0 & \frac{7}{128} & 0 \\ \frac{179}{512} & 0 & \frac{333}{512} & 0 & 0 \end{pmatrix},$$

$$\mathbf{A_o} = \begin{pmatrix} 0 & \frac{7}{1024} & 0 & \frac{1017}{1024} & 0 \\ \frac{1}{512} & 0 & \frac{333}{512} & 0 & \frac{89}{256} \\ 0 & \frac{1}{2} & 0 & \frac{1}{2} & 0 \\ \frac{89}{256} & 0 & \frac{333}{512} & 0 & \frac{1}{512} \\ 0 & \frac{1017}{1024} & 0 & \frac{7}{1024} & 0 \end{pmatrix}. \tag{66}$$

is also simulated as a reference.

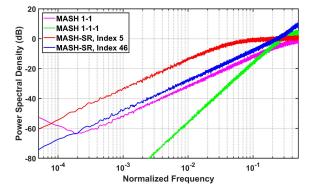

#### A. Spectra of t[n]

The spectra of t[n] of a MASH 1-1 DDSM, MASH 1-1-1 DDSM, and MASH-SR with matrices index 5 and 46 are show in Fig. 13. The MASH-SR with state transition matrices indexed 5 has high low-frequency noise in comparison to the other architectures. The t[n] spectrum of the MASH-SR

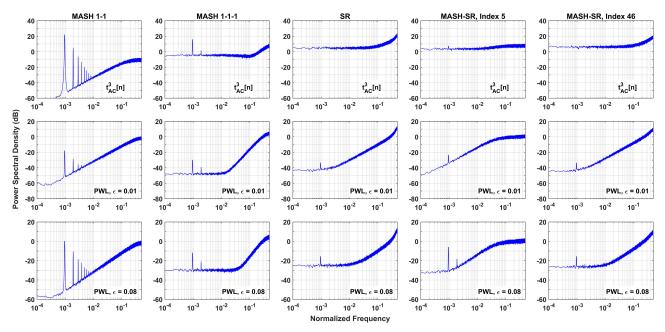

Fig. 14. The spectra when  $t_{AC}[n]$  of MASH 1-1, MASH 1-11, and MASH-SR with state transition matrices indexed 5 and 46 experience third-order distortion, a PWL nonlinearity with 1% mismatch, and a PWL nonlinearity with 8% mismatch.

with matrices indexed 46 is about 3.8 dB higher than that of a MASH 1-1 at mid and low frequencies. Comparing the case where matrices with index 5 are applied, the optimized MASH-SR has a low-frequency t[n] power spectral density that is about 14.5 dB lower. Notice the -20 dB/decade spectral contribution of the zeroth-order shaped LSB dither at very low frequencies in the spectrum of the MASH 1-1. The MASH-SR with matrices indexed 46 has the highest power spectral density around the 0.5 normalized frequency, even higher than that of the third-order MASH 1-1-1.

#### B. Spectra of t[n] in the Presence of Nonlinear Distortions

Next, we consider t[n] in the presence of nonlinear distortions. It should be noted that the t[n] of a MASH DDSM and MASH-SR will contain a DC component as the effect of the initial condition. In a practical synthesizer, the DC component will have no effect or only affect the local nonlinearity with which the phase deviation caused by the divide controller interacts [5]. To avoid the extra effect of the DC component, the nonlinearity consider is only applied to the AC component of t[n], which is

$$t_{AC}[n] = t[n] - \mathbb{E}(t[n]) \approx t[n] - \frac{1}{n+1} \sum_{m=0}^{n} t[m].$$

(67)

The range  $t_{AC}[n]$  of the MASH-SRs is (-3.875, 3.875). For the full SR,  $t_{AC}[n] \in (-4, 4)$ . The ranges of  $t_{AC}[n]$  of the MASH 1-1 and the MASH 1-1-1 are (-1, 1) and (-2, 2), respectively.

Two types of nonlinearities are considered in the simulations. Since the optimized state transition matrices were selected from those that are immune to third-order distortion, spectra of  $t_{AC}^3[n]$  for all divider controllers are presented. The mismatch of charge pump current sources generally exists and the transfer characteristic of a PFD/CP can be modeled

by a piecewise-linear (PWL) nonlinearity [4]. To represent minor and severe nonlinearity, mismatches of 1% and 8% are considered. The simulated PWL nonlinearity can be expressed by

$$t_{AC}^{NL}[n] = t_{AC}[n] + \frac{\epsilon}{2} |t_{AC}[n]|$$

(68)

where  $\epsilon$  is the mismatch and  $t_{AC}^{NL}[n]$  is the nonlinearly distorted  $t_{AC}[n]$ . Fig. 14 shows the nonlinearly distorted  $t_{AC}[n]$  spectra.

In the presence of a third-order nonlinear distortion, the second and third-order MASH DDSM both lead to obvious spurs. In contrast, the MASH-SR hybrid with matrices indexed 5 shows a spur with low amplitude due to the rounding error of the matrix, while the MASH-SR with matrices indexed 46 does not shown any obvious spurs. When a PWL nonlinearity with 1% mismatch is present, the MASH-SR with matrices indexed 46 leads to a most significant spur that is more than 15 and 3 dB lower than those induced by a MASH 1-1 and MASH 1-1-1 respectively, with no harmonic spurs observed. Compared with the MASH-SR hybrid with matrices indexed 5, the application of optimized matrices indexed 46 reduces the most significant spur by about 10 dB. When the mismatch of the PWL nonlinearity is increased to 8%, the spur reduction observed in the 1% case is preserved. The noise floor introduced by the MASH-SR with matrices indexed 46 increases by about 18 dB as the mismatch is increased. In the presence of the PWL nonlinearity of 1% and 8% mismatches, the optimized MASH-SR has a noise floor that is about 3.8 dB higher that that of a MASH 1-1-1 DDSM. Comparing with the standard 20-bit SR, the spur performance of the MASH-SR is not compromised. Due to a lower power spectral density around 0.5 normalized frequency, the noise floor caused by the MASH-SR is about 1.5 dB lower that of the SR.

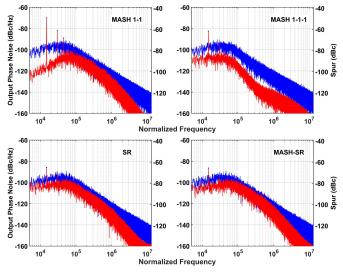

Fig. 15. Simulated synthesizer output phase noise spectra (blue) when a MASH 1-1, a MASH 1-1-1, SR, and a MASH-SR with the optimized state transition matrices (index 46) is employed, respectively. Output phase noise contribution from the divider controller (red) is overlapped on top. Divider controllers are 20-bit and the input is X = 605. Square markers highlight the overlapped spurs in the output phase noise spectra.

#### C. Fractional-N Mode Fixed Spurs

The spur performance of the optimized MASH-SR divider controller and its counterparts was simulated using a closed-loop behavioral model [15], [21]. A Type-II synthesizer with a third-order loop filter has the parameters listed in Table II has been simulated and results are shown in Fig. 15 [13].

When the MASH 1-1 is used in the synthesizer, a primary integer boundary spur of -49 dBc and harmonic tones of -61 and -68 dBc are observed in the output phase noise spectrum. The integer boundary spur is reduced to -62 dBcwith an insignificant harmonic spur at -70 dBc when a MASH 1-1-1 is employed. When an optimized MASH-SR is applied, the corresponding integer boundary spur is -65 dBc, with no apparent harmonic tones; this spur performance is equivalent to that of the full 20-bit SR in the simulation. Simulations indicate that MASH-SR divider controller will cause a higher noise floor compared to its MASH DDSM counterparts. Hence, in a wideband synthesizer whose in-band noise is significantly affected by the output phase noise contribution from the MASH-SR divider controller, appropriate linearization techniques should be applied to obtain the optimum spectral performance.

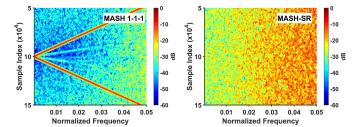

## D. Wandering Spurs

Wandering spurs is a time-varying phenomenon observed in the short-term output spectrum of a DDSM-based fractional-*N* frequency synthesizer [22], [23]. Wandering spurs arise from the double accumulation of a constant in the DDSM-based divider controller [21].

Since the SR quantization block does not perform accumulation, the quantization error of a SR is free of wandering spurs. The dominance of the noise contribution of the SR quantization blocks in the proposed MASH-SR divider controller

Fig. 16. Spectrograms of  $t_{AC}[n]$  of 20-bit MASH 1-1-1 DDSM and the optimized MASH-SR with state transition matrices index 46 in the presence of PWL nonlinearity with 8% mismatch when input X=1.

TABLE II

TABLE OF SIMULATION PARAMETERS

| Parameter                       | Value                  |  |

|---------------------------------|------------------------|--|

| Reference Frequency             | 26 MHz                 |  |

| Up/Down Current Mismatch        | 1%                     |  |

| Nominal Charge Pump Current     | 1 mA                   |  |

| Loop Bandwith                   | 45  kHz                |  |

| Loop Gain                       | $4.6425 \times 10^{8}$ |  |

| Pole 1 Frequency                | $111.20~\mathrm{kHz}$  |  |

| Pole 2 Frequency                | 719.84  kHz            |  |

| Zero Frequency                  | 9.0876  kHz            |  |

| VCO Gain                        | 5 MHz/V                |  |

| Division Ratio, Integer Part    | 137                    |  |

| Reference Phase Noise           | $-150~\mathrm{dBc/Hz}$ |  |

| VCO Phase Noise at 1 MHz offset | $-125~\mathrm{dBc/Hz}$ |  |

structure leads to similar spectral performance. Moreover, the MASH 1-1-1 DDSM in the MASH-SR has a smaller number of bits for its input, which leads to faster-moving, lower-amplitude wandering spurs compared with those arise from a standard MASH 1-1-1 with a similar input. Fig. 16 shows the simulated spectrogram of  $t_{AC}[n]$  in the presence of a PWL nonlinearity of 8% mismatch when the MASH 1-1-1 DDSM input is X = 1. The proposed MASH-SR with the optimized state transition matrices does not exhibit any wandering spurs.

## VI. CONCLUSION

A MASH-SR divider controller is a hybrid of a conventional MASH DDSM and an SR and it possesses the advantages of both structures. It can achieve similar spur performance to a full SR implementing identical state transition matrices with sufficient number of SR quantization blocks present in the structure. Compared with a full SR, a MASH-SR counterpart reduces the amount of hardware needed. Furthermore, a MASH-SR can be used to perform phase alignment and adjustment, which cannot be done with a conventional full length SR. Also, a MASH-SR can also lead to less latency compared to a full SR.

The spur performance of a MASH-SR can be optimized by selecting an appropriate pair of state transition matrices. In this work, the state transition matrices are optimized for 4-bit pseudorandom number generators which are included in a 20-bit MASH-SQ that consists of a 16-bit MASH 1-1-1 DDSM and four second-order SR quantization blocks. The selection of the state transition matrices is based on estimates for the distribution and spectrum of the accumulated quantization noise contribution of the SR quantization blocks. The state transition matrices that lead to an accumulated quantization noise contribution that is of greater variance and ketosis

are preferred. In terms of accumulated quantization noise, pairs of matrices that give less low-frequency accumulated quantization noise are favored.

As simulations indicate, the optimized state transition matrices achieve similar performance in terms of spur and noise floor to the state-of-art full SR implementing state transition matrices for 10-bit pseudorandom number generators. It reduces the primary integer boundary spur by about 15 and 3 dB when compared to a standard MASH 1-1 and MASH 1-1-1 DDSM in the spectra of the distorted accumulated quantization error in the presence of a PWL nonlinearity. Closed-loop behavior model simulations confirm the effectiveness of the proposed MASH-SR divider controller. The simulated spectral performance of the proposed MASH-SR is close to that of a reference standard full SR. Furthermore, the proposed MASH-SR hybrid can effectively mitigate wandering spurs that occur when using MASH DDSM divider controllers.

# APPENDIX A COMPUTING THE DISTRIBUTION OF $t_S[n]$

Consider two independent discrete random variables X and Y which have sample space

$$X \in \{x_1, x_2, \dots, x_M\}, Y \in \{y_1, y_2, \dots, y_N\}$$

(69)

where

$$x_k - x_{k-1} = y_l - y_{l-1} = c > 0, \ k \in [1, M], \ l \in [1, N].$$

(70)

The sample space of X + Y is then

$$X + Y \in \{x_1 + y_1, x_1 + y_1 + c, \dots, x_M + y_N\}.$$

(71)

The probability of the sum of two variables can be evaluated by the convolution of stochastic vectors

$$\mathbf{V_x} = (P(X = x_1) \quad P(X = x_2) \quad \dots \quad P(X = x_M)) \quad (72)$$

and

$$\mathbf{V_y} = (P(Y = y_1) \ P(Y = y_2) \dots P(Y = y_N)).$$

(73)

Thus.

$$P(X + Y = x_1 + y_1 + (l - 1)c)$$

$$= \sum_{k=\max\{l+1-M,1\}} \mathbf{V_x}[l+1-k]\mathbf{V_y}[k],$$

$$l \in [1, M+N-1].$$

(74)

The distribution of  $t_S[n]$  can be computed by repeatedly applying this conclusion. Equation (31) can be written as

$$t_{S}[n] = \left(\cdots \left(\left(\frac{t_{K-1}[n]}{2^{1}} + \frac{t_{K-2}[n]}{2^{2}}\right) + \frac{t_{K-3}[n]}{2^{3}}\right) + \cdots + \frac{t_{1}[n]}{2^{K-1}}\right) + \frac{t_{0}[n]}{2^{K}}.$$

(75)

Define

$$t_{c,d}[n] = \frac{t_d[n]}{2^{K-d}}$$

(76)

and the stochastic describing it as

$$\mathbf{V}_{d} = \left(P\left(t_{c,d}[n] = -\frac{N_{t}}{2^{K-d}}\right) \quad P\left(t_{c,d}[n] = -\frac{N_{t}+1}{2^{K-d}}\right)$$

$$\dots P\left(t_{c,d}[n] = \frac{N_{t}}{2^{K-d}}\right) = \mathbf{p_{t}}$$

$$(77)$$

where  $N_t = 2N_u$  for a second-order  $s_d[n]$  generator.

To start the iteration of the convolution, a vector to represent the sum that is to be added to  $t_{c,d}[n]$  in the (K-1-d)th set of brackets starting from inside in (75) is defined as  $\mathbf{V}_{t,(K-1-d)}$ . Therefore,  $\mathbf{V}_{t,1} = \mathbf{V}_{K-1} = \mathbf{p_t}$ .

Consider the sum in the first set of brackets starting from inside in (75). To establish sample spaces that have identical increments, padding of zeroes is performed to  $V_{t,1}$ :

$$V'_{t,1} = \left( P\left( t_{c,(K-1)}[n] = -\frac{2N_t}{4} \right) \right.$$

$$P\left( t_{c,(K-1)}[n] = -\frac{2N_t - 1}{4} \right)$$

$$\dots P\left( t_{c,(K-1)}[n] = \frac{2N_t}{4} \right)$$

(78)

where  $P\left(t_{c,(K-1)}[n] = (-2N_t + k)/4\right) = 0$  for all odd integers k. Now the sum of  $\mathbf{V}'_{t,1}$  and  $\mathbf{V}_{K-2}$ , which is by definition  $\mathbf{V}_{t,2}$ , can be computed by convolution following (74):

$$\mathbf{V}_{t,2}(l) = P\left(t_{c,(K-1)}[n] + t_{c,(K-2)}[n] = \frac{-3N_t + l - 1}{4}\right)$$

$$= \sum_{k=\max\{l-2N_t,1\}}^{\min\{l,2N_t+1\}} \mathbf{V}_{K-2}[l+1-k]\mathbf{V}'_{t,1}[k],$$

$$l \in [1, 6N_t + 1]. \quad (79)$$

The step is repeated to compute the distribution of  $t_S[n]$ . Consider the summation in the (m-1)th set of brackets. The zero-padded vector  $\mathbf{V}'_{t,(m-1)}$  can be expressed as

$$\mathbf{V}'_{t,(m-1)} = \left(P\left(\sum_{p=1}^{m-1} t_{c,(K-p)}[n] = -\frac{(2^m - 2)N_t}{2^m}\right) \\ P\left(\sum_{p=1}^{m-1} t_{c,(K-p)}[n] = -\frac{(2^m - 2)N_t - 1}{2^m}\right) \\ \dots P\left(\sum_{p=1}^{m-1} t_{c,(K-p)} = \frac{(2^m - 2)N_t}{2^m}\right)\right). (80)$$

$\mathbf{V}'_{t,(m-1)}$  is convolved with  $\mathbf{V}_{K-m}$  to generate  $\mathbf{V}_{t,m}$ :

$$\mathbf{V}_{t,m}(l) = P\left(\sum_{p=1}^{m} t_{c,(K-p)}[n] = \frac{(2^{m}-1)N_{t} + l - 1}{2^{m}}\right)$$

$$= \sum_{k=\max\{l-2N_{t},1\}}^{\min\{l,(2^{m+1}-4)N_{t}+1\}} \mathbf{V}_{K-m}[l+1-k]\mathbf{V}'_{t,(m-1)}[k],$$

$$l \in [1, (2^{m+1}-2)N_{t}+1].$$

(81)

The distribution of the  $t_S[n]$  is found when m = K, i.e.,

$$\mathbf{P_{tout}} = \mathbf{V}_{t.K} \tag{82}$$

and it can be expressed as (48).

#### REFERENCES

- [1] B. Miller and R. J. Conley, "A multiple modulator fractional divider," *IEEE Trans. Instrum. Meas.*, vol. 40, no. 3, pp. 578–583, Jun. 1991.

- [2] M. Perrott, M. Trott, and C. Sodini, "A modeling approach for Σ-Δ fractional-N frequency synthesizers allowing straightforward noise analysis," *IEEE J. Solid-State Circuits*, vol. 37, no. 8, pp. 1028–1038, Aug. 2002.

- [3] T. A. D. Riley, M. A. Copeland, and T. A. Kwasniewski, "Delta-sigma modulation in fractional-N frequency synthesis," *IEEE J. Solid-State Circuits*, vol. 28, no. 5, pp. 553–559, May 1993.

- [4] H. Arora, N. Klemmer, J. C. Morizio, and P. D. Wolf, "Enhanced phase noise modeling of fractional-N frequency synthesizers," *IEEE Trans. Circuits Syst. I, Reg. Papers*, vol. 52, no. 2, pp. 379–395, Feb. 2005.

- [5] M. P. Kennedy and V. S. Sadeghi, "Observations concerning PFD/CP operating point offset strategies for combatting static charge pump mismatch in fractional-N frequency synthesizers with digital delta-sigma modulators," Nonlinear Theory Appl., vol. 5, no. 3, pp. 349–364, 2014.

- [6] B. Razavi, "An alternative analysis of noise folding in fractional-N synthesizers," in Proc. IEEE Int. Symp. Circuits Syst. (ISCAS), May 2018, pp. 1–4.

- [7] B. De Muer and M. S. J. Steyaert, "On the analysis of Δ–Σ fractional-N frequency synthesizers for high-spectral purity," *IEEE Trans. Circuits Syst. II, Analog Digital Signal Process.*, vol. 50, no. 11, pp. 784–793, Nov. 2003.

- [8] P.-E. Su and S. Pamarti, "Mismatch shaping techniques to linearize charge pump errors in fractional-N PLLs," *IEEE Trans. Circuits Syst. I, Reg. Papers*, vol. 57, no. 6, pp. 1221–1230, Jun. 2010.

- [9] K. Hosseini, B. Fitzgibbon, and M. P. Kennedy, "Observations concerning the generation of spurious tones in digital delta-sigma modulators followed by a memoryless nonlinearity," *IEEE Trans. Circuits Syst. II, Exp. Briefs*, vol. 58, no. 11, pp. 714–718, Nov. 2011.

- [10] A. Swaminathan, A. Panigada, E. Masry, and I. Galton, "A digital requantizer with shaped requantization noise that remains well behaved after nonlinear distortion," *IEEE Trans. Signal Process.*, vol. 55, no. 11, pp. 5382–5394, Nov. 2007.

- [11] K. J. Wang, A. Swaminathan, and I. Galton, "Spurious tone suppression techniques applied to a wide bandwidth 2.4 GHz fractional-N PLL," IEEE J. Solid-State Circuits, vol. 43, no. 12, pp. 2787–2797, Dec. 2008.

- [12] E. Familier, C. Venerus, and I. Galton, "A class of quantizers with DC-free quantization noise and optimal immunity to nonlinearityinduced spurious tones," *IEEE Trans. Signal Process.*, vol. 61, no. 17, pp. 4270–4283, Sep. 2013.

- [13] E. Familier and I. Galton, "Second and third-order noise shaping digital quantizers for low phase noise and nonlinearity-induced spurious tones in fractional-N PLLs," *IEEE Trans. Circuits Syst. I, Reg. Papers*, vol. 63, no. 6, pp. 836–847, Jun. 2016.

- [14] Z. Li, H. Mo, and M. P. Kennedy, "Comparative spur performance of a fractional-N frequency synthesizer with a nested MASH-SQ3 divider controller in the presence of memoryless piecewise-linear and polynomial nonlinearities," in Proc. Irish Signals Syst. Conf. China-Ireland Int. Conf. Inf. Commun. Technol. (ISSC/CIICT), Jun. 2014, pp. 374–379.

- [15] D. Mai and M. P. Kennedy, "A design method for nested MASH-SQ hybrid divider controllers for fractional-N frequency synthesizers," *IEEE Trans. Circuits Syst. I, Reg. Papers*, vol. 65, no. 10, pp. 3279–3290, Oct. 2018.

- [16] M. P. Kennedy et al., "16.9 4.48 GHz 0.18μm SiGe BiCMOS exact-frequency fractional-N frequency synthesizer with spurious-tone suppression yielding a –80dBc in-band fractional spur," in IEEE Int. Solid-State Circuits Conf. (ISSCC) Dig. Tech. Papers, Feb. 2019, pp. 272–274.

- [17] Y. Donnelly et al., "4.48-GHz fractional-N frequency synthesizer with spurious-tone suppression via probability mass redistribution," *IEEE Solid-State Circuits Lett.*, vol. 2, no. 11, pp. 264–267, Nov. 2019.

- [18] D. Mai, A. Dahlan, and M. P. Kennedy, "MASH DDSM-induced spurs in a fractional-N frequency synthesizer," in Proc. 26th IEEE Int. Conf. Electron., Circuits Syst. (ICECS), Nov. 2019, pp. 13–16.

- [19] E. Familier and I. Galton, "Second and third-order successive requantizers for spurious tone reduction in low-noise fractional-N PLLs," in Proc. IEEE Custom Integr. Circuits Conf. (CICC), Apr. 2017, pp. 1–4.

- [20] E. Familier and I. Galton, "A fundamental limitation of DC-free quantization noise with respect to nonlinearity-induced spurious tones," *IEEE Trans. Signal Process.*, vol. 61, no. 16, pp. 4172–4180, Aug. 2013.

- [21] D. Mai and M. P. Kennedy, "Analysis of wandering spur patterns in a fractional-N frequency synthesizer with a MASH-based divider controller," *IEEE Trans. Circuits Syst. I, Reg. Papers*, vol. 67, no. 3, pp. 729–742, Mar. 2020.

- [22] D. Mai, H. Mo, and M. P. Kennedy, "Observations and analysis of wandering spurs in MASH-based fractional-N frequency synthesizers," *IEEE Trans. Circuits Syst. II, Exp. Briefs*, vol. 65, no. 5, pp. 662–666, May 2018.

- [23] D. Mai, X. Li, and M. P. Kennedy, "Experimental confirmation of wandering spurs in a commercial fractional-N frequency synthesizer with a MASH 1–1–1 divider controller," in *Proc. 30th Irish Signals* Syst. Conf. (ISSC), Jun. 2019, pp. 1–6.

Dawei Mai (Member, IEEE) received the B.E. and M.E. degrees in electrical and electronic engineering from University College Cork (UCC) in 2015 and 2018, respectively, and the Ph.D. degree from University College Dublin (UCD) in 2021. He is currently a Post-Doctoral Research Fellow at UCD. His research interests include the design, analysis, and modeling of high-performance frequency synthesizers.

Michael Peter Kennedy (Fellow, IEEE) received the B.E. degree in electronics from the National University of Ireland, Dublin, in 1984, the M.S. and Ph.D. degrees from the University of California at Berkeley (UC Berkeley), Berkeley, in 1987 and 1991, respectively, the D.Eng. degree from the National University of Ireland in 2010, and the D.Sc. (Eng.) (Hons.) from Queen's University Belfast in 2020

He has been a Professor in microelectronic engineering at University College Dublin since 2017.

He was elected as a fellow of IEEE in 1998 for his contributions to the study of neural networks and nonlinear dynamics. He was elected to membership of the Royal Irish Academy (RIA) in 2004, served as the RIA Policy and International Relations Secretary from 2012 to 2016, and as the President from 2017 to 2020. He was the Vice President for Region 8 of the IEEE Circuits and Systems Society (CASS) from 2005 to 2007, a CASS Distinguished Lecturer from 2012 to 2013 and in 2022, and the Chair of the CASS Distinguished Lecturer Program from 2017 to 2020. He served on the IEEE Fellows Committee and the IEEE Gustav Robert Kirchhoff Award Committee. He received the Honoris Causa Award for D.Sc. (Eng.) degree.